#### **Aalborg Universitet**

### Performance Evaluations of Four MAF-Based PLL Algorithms for Grid-Synchronization of Three-Phase Grid-Connected PWM Inverters and DGs

Han, Yang; Luo, Mingyu; Chen, Changging; Jiang, Aiting; Zhao, Xin; Guerrero, Josep M.

Published in: Journal of Power Electronics

DOI (link to publication from Publisher): 10.6113/JPÉ.2016.16.5.1904

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA): Han, Y., Luo, M., Chen, C., Jiang, A., Zhao, X., & Guerrero, J. M. (2016). Performance Evaluations of Four MAF-Based PLL Algorithms for Grid-Synchronization of Three-Phase Grid-Connected PWM Inverters and DGs. *Journal of Power Electronics*, *16*(5), 1904-1917. https://doi.org/10.6113/JPE.2016.16.5.1904

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

JPE ??-?-?

http://dx.doi.org/10.6113/JPE.2014.14.1.??? ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Performance Evaluations of Four MAF-Based PLL Algorithms for Grid-Synchronization of Three-Phase Grid-Connected PWM Inverters and DGs

Yang Han<sup>†</sup>, Mingyu Luo<sup>\*</sup>, Changqing Chen<sup>††</sup>, Aiting Jiang<sup>\*</sup>, Xin Zhao<sup>\*\*</sup>, and Josep M. Guerrero<sup>\*\*</sup>

†,\* Department of Power Electronics, School of Mechatronics Engineering, University of Electronic Science and Technology of China (UESTC), Chengdu, China

†† Panzhihua Power Supply Company, State Grid Sichuan Electric Power Company, Panzhihua, China \*\* Department of Energy Technology, Aalborg University, Aalborg, Denmark

#### **Abstract**

The moving average filter (MAF) is widely utilized to improve the disturbance rejection capability of the phase-locked loops (PLLs), which is of vital significance for the grid-integration and stable operation of power electronic converters to the electric power systems. However, the open-loop bandwidth is drastically reduced after incorporating MAF into the PLL structure, which makes the dynamic response sluggish. To overcome this shortcoming, some new techniques were proposed recently to improve the transient response of MAF-based PLLs. In this paper, a comprehensive performance comparison among the advanced MAF-based PLL algorithms is presented, which includes HPLL, MPLC-PLL, QT1-PLL, and DMAF-PLL. Various grid voltage disturbance scenarios, such as grid voltage sag, voltage flicker, and harmonics distortion, phase-angle and frequency jumps, DC offsets and noise, are considered to experimentally test the dynamic performances of these PLL algorithms. Finally, an improved positive sequence extraction method for HPLL under frequency jumps scenario is presented to compensate the steady-state error caused by the non-frequency adaptive DSC, and a satisfactory performance has been achieved.

Key words: Grid-synchronization, moving average filter (MAF), phase-locked loop (PLL), transient response.

#### I. Introduction

Three-phase phase-locked loop (PLL) technique is widely used for the accurate estimation of phase-angle, frequency, and sequence components extraction of grid voltages in power systems, which is crucial for the grid-integration of the distributed generation (DG) systems, such as wind, PV, and flexible ac transmission systems (FACTS), and active power filters (APFs) [1-3]. However, a great challenge associated with the PLLs is the accurate and fast estimation of phase angle and frequency under adverse grid voltage disturbance scenarios. According to European standard EN50160, the

typical voltage disturbance scenarios include voltage sag, flicker, and harmonics distortion, phase-angle and frequency jumps, dc offsets and noise contaminations [4]. In order to achieve the purpose of accurate grid-synchronization under various grid disturbance scenarios, several new structures to enhance the performance of the PLL have been presented [5-14].

In addition to the use of these new structures, a more general approach to improve the performance of a PLL is to combine with the filters [15-36], such as the extended Kalman filters (EKFs) [15], the space vector filters (SVFs) [16], the notch filters [17], the digital filters [18], the complex-coefficient filter (CCF) [19], the delayed signal cancellation (DSC) block [20-24], and the MAF-based methods [25-36]. Among these filtering techniques, the DSC and the MAF show the similar filtering characteristic, which can almost block the specific frequency signal completely. From the view point of the discrete implementation of the DSC and MAF, they are both composed of some particular delay blocks. However, the DSC is often used to improve the

Manuscript received December 31, 2015; accepted April 20, 2016. Recommended for publication by Associate \*\*\*\*\*\*

<sup>&</sup>lt;sup>†</sup>Corresponding Author: hanyang\_facts@hotmail.com

Tel: +86-13730606846, Fax: +86-28-6183-0229, UESTC

<sup>\*</sup> Dept. of Power Electronics, School of Mechatronics Eng., University of Electronic Science and Technology of China (UESTC), China

<sup>††</sup>Panzhihua Power Supply Company, State Grid Sichuan Electric Power Company, Panzhihua, China

<sup>\*\*</sup> Dept. of Energy Technology, Aalborg University, Denmark

performance of the PLL under adverse grid conditions [23]. And in [24], a comparison of the MAF and DSC, as well as their derived methods, was presented from the aspects of dynamic response, steady-state performance, required data size, and harmonic and noise immunity ability. In [25], the dqCDSC-PLL and the MAF-PLL algorithms were proved to be mathematically equivalent under certain conditions.

The MAF technique is most popular and widely used technique (can be used in natural abc coordinates,  $\alpha\beta$  coordinates and dq coordinates) owing to its simple digital realization, low computational burden, and effectiveness under grid disturbance conditions [26]. However, the open-loop bandwidth of the PLL is drastically reduced after incorporating MAF into its structure, which may be beneficial for the stability, but degrades the dynamic performance of the PLL. To solve this problem, some advanced MAF-based PLL algorithms are presented recently [27-36].

In [26], the detailed analysis and design guideline of the MAF-PLL and its frequency adaptive implementation were presented, in which the performance comparison of the well-tuned MAF-based PLL with PI controller and the PID controller was presented. It was shown that the PID-type MAF-PLL has a higher bandwidth which means a faster dynamic response while decreasing the noise immunity and disturbance rejection capability, and in [27] a critical comparison among the PLL and FLL based on the MAF, CDSC and DSOGI filtering techniques was presented. It is shown that these kinds of filtering techniques all can effectively remove the noise, harmonic and negative sequence which the initial phase angle detector with MAF-based PLL shows the best performance under frequency and phase angle jump scenarios. A novel MAF-based PLL consists of a frequency detector and an initial phase was presented in [28], in which the effect of discrete sampling on MAF is analyzed and a linear interpolation is employed to enhance the performances of the MAF. And in [29], an enhanced MAF (EMAF) algorithm was presented, which shows superior performance in terms of response time, transient overshoot, computational load, harmonic and noise immunity compared with the DSC algorithm.

In [30], a MAF and a weighted least squares estimation (WLSE) scheme based PLL was proposed, in which the MAF was used to filter out all the odd-order harmonics and help the WLSE to detect the fundamental positive-sequence components accurately even under heavily distorted grid conditions. In [31], the MAF was used as a perfiltering stage in the *dq*-frame (PMAF-PLL) to remove the negative sequence and odd-order harmonic components, and then an enhanced method was proposed to improve the steady-state performance under frequency varying conditions. Furthermore, the small-signal model of the PMAF-PLL was

presented and it has been proved that the PMAF-PLL and space-vector Fourier transform- based PLL (SVFT-PLL) are theoretically equivalent, and in [32], a novel design of low-gain PLL with introducing an adaptive MAF before the loop-filter (LF) and its discrete domain model was presented. Compared with the conventional high gain SRF-PLL, the phase and voltage frequency error is reduced and the phase angle tracking is faster and more accurate.

In [33], a quasi-type-1 PLL (QT1-PLL) was presented. In this structure, the proportional integral (PI) controller was replaced by a simple gain, thus, a larger open-loop bandwidth can be realized. However, QT1-PLL cannot filter out the dc offset and even order harmonics. In order to tackle this problem, hybrid PLL (HPLL) was presented in [34]. In HPLL, the delayed signal cancellation (DSC) is used in the  $\alpha\beta$  axis to eliminate the dc offset and even order harmonics. The phase error compensation (PEC) method was adopted for QT1-PLL and HPLL to achieve zero steady-state error when frequency jump occurs. In [35], the MAF-PLL with a phase-lead compensator (MPLC-PLL) was presented. With the phase-lead compensator in the control loop, the dynamic response of the standard MAF-PLL can be effectively improved without deteriorating its disturbance rejection capabilities. A differential MAF-PLL (DMAF-PLL) was presented in [36]. Under this approach, a special loop filter structure was used to eliminate the negative sequence 2<sup>nd</sup> order harmonics in order to reduce the window length of the MAF and significantly improves the dynamic performance of the PLL.

The main objective of this paper is to provide performance evaluations (including the transient response and disturbance rejection capabilities) of the four MAF-based PLLs (QT1-PLL, HPLL, MPLC-PLL, and DMAF-PLL) by analytical comparison and experimental results. The steady-state and dynamic performance of these algorithms are compared in terms of settling time, phase tracking error and overshoots. Experimental results show that the QT1-PLL and MPLC-PLL lack the rejection capabilities of dc offset and even order harmonics, which are the shortcomings of these algorithms, and it can be overcome by employing the DSC in the  $\alpha\beta$  coordinates or MAF in the abc coordinates. In the last Section, the amplitude error compensation (AEC) method is proposed to achieve zero steady-state error for the positive sequence amplitude estimation under frequency jump scenario. The extensive experimental results are provided for validation, which facilitates the practical application of these MAF-based PLLs to achieve an accurate synchronization for the three-phase grid-connected PWM inverters and the distributed generators (DGs) in smart grid.

#### II. OVERVIEW OF THE MAF-BASED PLLS

In this Section, a brief overview of MAF is outlined, and four MAF-based PLL algorithms and discrete models are

described.

#### A. Moving Average Filter (MAF)

The transfer function of MAF can be simply obtained in *s*-domain and *z*-domain as [19]

$$G_{MAF}(s) = \frac{\overline{x}(s)}{x(s)} = \frac{1 - e^{-T_{\omega}s}}{T_{\omega}s} \approx \frac{2}{T_{\omega}s + 2}$$

(1)

$$G_{MAF}(z) = \frac{\overline{x}(z)}{x(z)} = \frac{1}{N} \frac{1 - z^{-N}}{1 - z^{-1}}$$

(2)

where  $T_{\omega}$  represents the window length, and  $T_{\omega}$ = $NT_s$ ,  $T_s$  is the sample time and is set to be 0.0001 s, and N is an integer. The transfer function (1) shows that MAF requires a time equals to its window length to gather the data and reach the steady-state conditions. Therefore, a smaller window length would result in a faster dynamic response of the MAF-based PLL algorithms.

As shown in (2), the application of the MAF in z-domain computationally efficient with simple delay blocks [26], which is shown in Fig. 1. From the aforementioned analysis, the delay factor N can be set to be a constant to remove the fix frequency signal or to be frequency adaptive according to the equation N=round ( $m\pi/\omega_0 T_s$ ), in which the MAF is used to remove the odd-order harmonic for m=1, and the MAF is used to remove the dc offset for m=2. The detailed discrete-time realization was discussed in [26].

Fig. 1. The realization of MAF in z-domain.

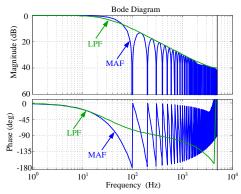

Fig. 2. Bode diagram comparison of MAF and first-order LPF.

Using the transfer functions (1) and (2), the bode diagram of MAF and low-pass filter (LPF) is shown in Fig. 2, in which  $T_{\omega}$  is set to be 0.01 s (N=100) and the corresponding cutoff frequency in LPF is 200 rad/s. It shows that the even order harmonics are eliminated effectively since the MAF has a high attenuation at these harmonic frequencies.

B. OT1-PLL

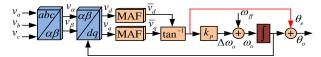

Fig. 3. Block diagram of the QT1-PLL proposed in [33].

Fig. 3 shows the general structure of the QT1-PLL, in which a MAF cascading a proportional controller act as the loop filter. Thus, from the view point of the structure, the QT1-PLL is a type-I PLL, which has a high stability margin compared with the typical MAF-PLL (in which a MAF and a PI controller act as the loop filter). However, the main disadvantage of a conventional type-I PLL lies on the phase tracking error under grid frequency step condition.

As shown in Fig. 3, the three-phase grid voltages with dc offset and harmonics can be defined as (here, the symmetrical load is taken into consideration, which corresponding to the  $-5^{th}$ ,  $+7^{th}$ ,  $-11^{th}$ , and  $+13^{th}$  order harmonics)

$$\begin{cases} v_{a} = V_{a,dc} + \sum_{h=1,-5,7,\dots} [V_{h}^{+} \cos(\theta_{h}^{+}) + V_{h}^{-} \cos(\theta_{h}^{-})] \\ v_{b} = V_{b,dc} \sum_{h=1,-5,7,\dots} [V_{h}^{+} \cos(\theta_{h}^{+} - \frac{2\pi}{3}) + V_{h}^{-} \cos(\theta_{h}^{-} + \frac{2\pi}{3})] \end{cases}$$

$$v_{c} = V_{c,dc} + \sum_{h=1,-5,7,\dots} [V_{h}^{+} \cos(\theta_{h}^{+} + \frac{2\pi}{3}) + V_{h}^{-} \cos(\theta_{h}^{-} - \frac{2\pi}{3})]$$

$$(3)$$

where  $V_h^+$  ( $V_h^-$ ) and  $\theta_h^+$  ( $\theta_h^-$ ) are the amplitude and the phase-angle of the hth harmonic components of the positive-(negative-) sequence of the input voltages, respectively.  $V_{a,dc}$ ,  $V_{b,dc}$  and  $V_{c,dc}$  are the dc offset added into the phase-a, phase-b and phase-c voltage, respectively.

Applying the Clarke transformation to (3),  $v_{\alpha}$  and  $v_{\beta}$  can be written as

$$\begin{cases} v_{\alpha} = V_{\alpha,dc} + \sum_{h=1,-5,7...} [V_h^+ \cos(\theta_h^+) + V_h^- \cos(\theta_h^-)] \\ v_{\beta} = V_{\beta,dc} + \sum_{h=1,-5,7...} [V_h^+ \sin(\theta_h^+) - V_h^- \sin(\theta_h^-)] \end{cases}$$

(4)

$$\begin{cases} V_{\alpha,dc} = (V_{a,dc} - 0.5V_{b,dc} - 0.5V_{c,dc}) \\ V_{\beta,dc} = \frac{\sqrt{3}}{2} (V_{b,dc} - V_{c,dc}) \end{cases}$$

(5)

Then, applying the Park transformation to (4),  $v_d$  and  $v_q$  can be written as

$$\begin{cases} v_{d} = g(\theta'_{0}) + \sum_{h=1,-5,7...} [V_{h}^{+} \cos(\theta_{h}^{+} - \theta'_{0}) + V_{h}^{-} \cos(\theta_{h}^{-} + \theta')] \\ v_{q} = h(\theta'_{0}) + \sum_{h=1,-5,7...} [V_{h}^{+} \sin(\theta_{h}^{+} - \theta'_{0}) - V_{h}^{-} \sin(\theta_{h}^{-} + \theta')] \end{cases}$$

(6)

where the  $g(\theta_0)$  and  $h(\theta_0)$  are the oscillating term caused by the grid voltage dc offset, where

$$\begin{cases} g(\theta_0') = V_{\alpha,dc} \cos(\theta_0') + V_{\beta,dc} \sin(\theta_0') \\ h(\theta_0') = -V_{\alpha,dc} \sin(\theta_0') + V_{\beta,dc} \cos(\theta_0') \end{cases}$$

(7)

Under quasi-locked condition  $(\theta_1^+ = \theta_0^-)$ , (6) can be rewritten

$$\begin{cases} v_d = V_1^+ + f(\omega_n, 2\omega_n, 6\omega_n ...) \\ v_q = V_1^+ (\theta_1^+ - \theta_0') + f(\omega_n, 2\omega_n, 6\omega_n ...) \end{cases}$$

(8)

where  $\omega_n$  is the fundamental angular frequency. Through the use of MAF, the oscillating term  $f(\omega_n, 2\omega_n, 6\omega_n...)$  can be almost removed. As mentioned earlier, a type-I PLL cannot achieve zero steady-state error when the frequency jump

occurs. Hence the phase tracking error of a type-I PLL under frequency jump is expressed as [33]

$$\theta_e = \frac{\Delta \omega_i}{k_p} \tag{9}$$

From equation (9), by selecting a sufficient high value for  $k_p$ , the phase error  $\theta_e$  can be reduced to a very small value. However, this selection will increase the PLL's bandwidth remarkably which is not preferred under the distorted and unbalanced grid voltage condition. Notice that the average value of  $\Delta\omega_o$  is equal to  $\Delta\omega_i$  under the locked conditions. Thus, as highlighted in Fig. 3, the phase tracking error is added to output of the PLL to realize zero steady-state tracking error when frequency jump occurs.

Fig. 4. Small-signal model of the QT1-PLL [33].

Fig. 4 shows the small signal model of the QT1-PLL. Since the s-domain transfer function has been expressed in [33], and considering the practical application, the open-loop transfer function in z-domain is expressed as:

$$G_{ol}^{QT1}(z) = \left(\frac{G_{MAF}(z)}{1 - G_{MAF}(z)}\right) \left(\frac{z - 1 + T_s k_p}{z - 1}\right)$$

(10)

As shown in (8), the lowest oscillating frequency is  $\omega_n$ =50 Hz (in the 50 Hz system), by selecting  $T_{\omega}$ =0.02 s (i.e., N=200), the oscillating term can be removed completely. However, this selection may lead to a slow dynamic response, in order to make a tradeoff between the response speed and filtering capability, the window length of the MAF is set to be 0.01 s (i.e., N=100), which means the MAF block cannot remove the fundamental frequency oscillation caused by the dc offset.

#### C. HPLL

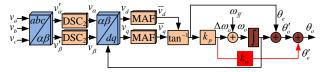

Fig. 5. Block diagram of the HPLL proposed in [34].

Fig. 5 shows the general structure of the HPLL which was presented in [34] to overcome the main drawback of the QT1-PLL under dc offset and even-order harmonics scenarios. The main difference between HPLL and QT1-PLL is the application of the delay signal cancellation (DSC) in  $\alpha\beta$  axis ( $\alpha\beta$ DSC). From Fig. 5, the  $\alpha\beta$ DSC input signal  $v_{\alpha}$  and  $v_{\beta}$  is shown in (4), in order to filter out the dc offset ( $V_{\alpha,dc}$ ,  $V_{\beta,dc}$ ), the transfer function of  $\alpha\beta$ DSC applied in HPLL can be defined in the Laplace-domain as [23]

$$G_{\alpha\beta \text{DSC}_2}(s) = \frac{1}{2}(1 - e^{-\frac{r}{2}s})$$

(11)

where T=0.02 s is the fundamental period of grid voltages.

By substituting  $s=j\omega$  into (11), yields

$$G_{\alpha\beta \text{DSC}_2}(j\omega) = \left| \sin(\frac{\omega T}{4}) \right| \angle (\frac{\pi}{2} - \frac{\omega T}{4})$$

(12)

From (12), it can be observed that the  $\alpha\beta$ DSC<sub>2</sub> operator has unity gain and zero phase-shift at 50 Hz, and provides zero gain at zero frequency and all the even order harmonic frequencies, which imply that the  $G_{\alpha\beta$ DSC<sub>2</sub> blocks all the dc offset and even order harmonics.

Therefore,  $v_{\alpha}$  and  $v_{\beta}$  can be written as

$$\begin{cases} v_{\alpha} = \sum_{h=1,-5,7...} [V_{h}^{+} \cos(\theta_{h}^{+}) + V_{h}^{-} \cos(\theta_{h}^{-})] \\ v_{\beta} = \sum_{h=1,-5,7...} [V_{h}^{+} \sin(\theta_{h}^{+}) - V_{h}^{-} \sin(\theta_{h}^{-})] \end{cases}$$

(13)

Generally, the  $G_{\alpha\beta DSC2}$  can be designed to be frequency adaptive to achieve zero steady-state error under frequency jump scenario. This feedback loop, however, makes it rather difficult to ensure system stability. In order to solve this problem, the phase error is compensated to the PLL output. In order to compensate the phase shift caused by the  $G_{\alpha\beta DSC2}$  block under frequency jump scenarios, assuming that  $\Delta\omega_i$  is the deviation value of the grid frequency from the nominal grid frequency, the phase shift can be obtained as

$$\angle \alpha \beta DSC_2(j\omega_i) = -\frac{T}{4} \Delta \omega_i$$

(14)

This phase-error can be easily compensated as highlighted in Fig. 5, where  $k_{\varphi}$ =T/4 can be selected.

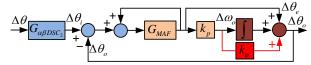

Fig. 6. Small-signal model of the HPLL [34].

The small signal model of the HPLL is shown in Fig. 6. The open-loop transfer function in z-domain can be derived as

$$G_{ol}^{HPLL}(z) = \left(\frac{G_{MAF}(z)}{1 - G_{MAF}(z)}\right) \left(1 + k_p k_{\varphi} + \frac{T_s k_p}{z - 1}\right)$$

(15)

Since the dc offset has been removed by the  $G_{\alpha\beta DSC2}$ , the lowest frequency needs to be filtered out is  $2\omega_n$ =100 Hz, therefore, the window length of MAF is set to be  $T_{\omega}$ =0.01 s.

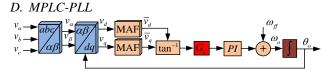

Fig. 7. Block diagram of the MPLC-PLL proposed in [35].

Fig. 7 shows the general structure of the MPLC-PLL derived from the conventional MAF-PLL. The phase-lead compensator, as highlighted by  $G_c$  in Fig. 7, is applied in the control loop to effectively compensate the control delay caused by the MAF. The expression of  $v_d$  and  $v_q$  are shown in (8). The transfer function of this compensator can be derived

$$G_c(z) = k \frac{1 - rz^{-1}}{1 - r^N z^{-N}}$$

(16)

where *r* is the attenuation factor, *N* is defined in equation (2), and  $k=(1-r^N)/(1-r)$ .

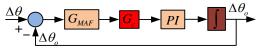

Fig. 8. Small-signal model of the MPLC-PLL [35].

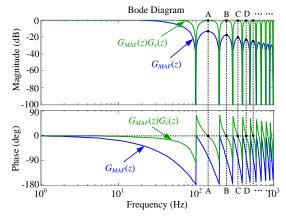

Fig. 9. Bode diagram of the MAF and the cascade connection of MAF and phase-lead compensator.

The small signal model of the MPLC-PLL is shown in Fig. 8. The open-loop transfer function in z-domain can be derived as

$$G_{ol}^{MPLC}(z) = G_{MAF}(z)G_{c}(z)PI(z)\frac{T_{s}}{z-1}$$

(17)

where the window length  $T_{\omega}$  is set to be 0.01 (i.e., N=100, this selection also ignores the dc offset), and the attenuation factor r is set to be 0.99.

From Fig. 9, it can be observed that the MAF with or without the phase-lead compensator have a similar filtering feature in frequency f = 100n (n = 1, 2, 3, ...). However, under other grid frequencies, especially in frequency point A, B, C, D, and so on, the MAF with phase-lead compensator may almost pass all these frequency signals without any change compared with the typical MAF, which means the phase-lead compensator actually amplify the frequency signal  $f \neq 100n$  (n = 1, 2, 3, ...) and this feature will decrease the frequency adaptive of the MPLC-PLL under harmonic with off-nominal frequency scenario.

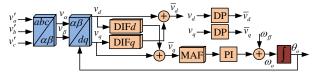

#### E. DMAF-PLL

Fig. 10. Block diagram of the DMAF-PLL proposed in [36].

Fig.11. Block diagram of DMAF-PLL used in the experiment.

Fig. 10 shows the general structure of the DMAF-PLL. The 'DP' represents the decoupling transfer function. The expression of  $v_{\alpha}$  and  $v_{\beta}$  is shown in (13). Fig. 11 shows the block diagram of PLL structure used in the experiment, in which one additional MAF (hereafter called *a*MAF) is added before the DMAF-PLL. Therefore, the DMAF-PLL input signal  $v_{abc}$  is free of dc offset.

In [36], the *a*MAF block is designed to be frequency-adaptive using the rounding-down method N=round ( $m\pi/\omega_0 T_s$ ), which m=2. Although this structure can effectively filter out the dc offset, the *a*MAF requires a time interval of 0.02 s to reach the steady-state condition. In Fig. 10, the transfer functions of DIF*d* and DIF*q* are

$$G_{DIFd}(s) = -\frac{s}{2\omega_n}, G_{DIFq}(s) = \frac{s}{2\omega_n}$$

(18)

Since  $v_q$  has a 90 ° phase lag compared with  $v_d$ , it can be obtained that  $v_d / v_q = j$ . Thus, substituting  $s = j\omega$  into (18) and performing simple mathematical operation [36], we get

$$G_{DP}(j\omega) = 1 + \frac{j(-j\omega)}{2\omega_n} = 1 + \frac{\omega}{2\omega_n}$$

(19)

Substituting  $\omega$ =-2 $\omega_n$  into (19), the value of DP is zero, which implies that the DP eliminates the negative sequence  $2^{\rm nd}$  order harmonics. Therefore, from (4),  $\overline{v}_d$  and  $\overline{v}_q$  can be expressed as

$$\begin{cases} \overline{v}_d = V_1^+ + f(6\omega_n \dots) \\ \overline{v}_q = V_1^+(\theta_h - \theta_0') + f(6\omega_n \dots) \end{cases}$$

(20)

From (20), the lowest order harmonics needed to be blocked is the  $6^{th}$  order harmonic. Then, the  $T_{\omega}$  is reduced to 1/300 s from 0.01 s, which significantly improves the response speed.

Fig. 12. Small-signal model of the DMAF-PLL [36].

The small signal model of DMAF-PLL is shown in Fig. 11. The decoupling transfer function *DP* in *z*-domain can be denoted as

$$G_{DP}(z) = \mathbb{Z}\{G_{DP}(s)\}\$$

(21)

Therefore, the open-loop transfer function of DMAF-PLL in z-domain can be written as:

$$G_{ol}^{DMAF}(z) = G_{DP}(z)G_{MAF}(z)PI(z)\frac{T_s}{z-1}$$

(22)

It should be noticed that the window length  $T_{\omega}$  in MAF is calculated as 1/300, which results in approximately N=33. Thus, when the grid voltages are contaminated by harmonics, a small ripple may exist in the estimated frequency and phase angle.

#### III. PARAMETERS DESIGN GUIDELINES

In this Section, the control parameters design method of the MAF-based PLL is presented. And then, the frequency domain analysis of these PLL algorithms is outlined.

In order to simplify the parameters design procedure, the parameters  $k_p$  and  $k_i$  is designed in s-domain, and then the discrete model and z-domain bode diagrams are used to test and adjust the control parameters. Therefore, the stability and disturbance rejection capability of the PLLs are ensured. The expression of MAF is approximated by the LPF, as shown in (1), and the PI regulator is denoted as  $k_p+k_i/s$ . Thus, for QT1-PLL, the open-loop transfer function can be derived as

$$G_{ol}(s) \approx \frac{2}{T_{oo}} \frac{(s+k_p)}{s^2}$$

(23)

From (23), the proportional gain  $k_p$  is the only parameter that needs to be designed in QT1-PLL and HPLL, since the MAF window length have already been selected. Hence, the closed-loop transfer function can be derived as

$$G_{cl}(s) \approx \frac{2}{T_{\omega}} \frac{(s + k_p)}{s^2 + (2/T_{\omega})s + 2k_p/T_{\omega}}$$

(24)

By comparing to the standard second order system, we get

$$2/T_{\omega} = 2\xi\omega'_{n}, \ 2k_{n}/T_{\omega} = \omega'^{2}_{n}$$

(25)

where  $\xi$  is the damping factor, and  $\omega_n$  is the natural frequency.

Substituting  $T_{\omega}$ =0.01 s and  $\xi$ =0.707 into (25), yields  $k_p \approx 100$ . Next step is to adjust  $k_p$  on the basis of the real transfer function in z-domain, as shown in (10) and (15). Since the  $k_{\varphi}$  in (15) is small, the expression (10) and (15) are almost identical to each other.

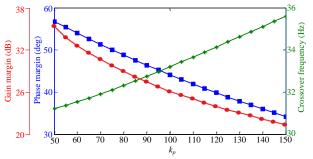

Thus, the phase margin (PM), crossover frequency (CF), and gain margin (GM) of (10) as the function of  $k_p$  are derived, as shown in Fig. 13. It can be seen that when  $k_p$  varies from 50 to 150, the PM (blue line) varies from 56.7 ° to 34.2 °, and the GM (red line) varies from 35.9 dB to 21.9 dB, which is suitable to ensure sufficient stability margin. The CF (green line) shows relatively smooth change (from 31.2 Hz to 35.5 Hz), which is much higher than the conventional PLLs and a fast dynamic response can be guaranteed. Therefore,  $k_p$ =92 is selected for QT1-PLL and  $k_p$ =94 is selected for HPLL.

As for MPLC-PLL, since the cascade connection of the MAF and phase-lead compensator provides a close gain to unity with a near zero phase shift at low frequency range [35]. Therefore, the transfer function (17) can be approximated by

Fig. 13. The PM, CF, and GM of (5) as a function of  $k_p$  in z-domain.

a typical type-2 system. It can be obtained that

$$k_n = 2\xi \omega_n', \ k_i = {\omega_n'}^2 \tag{26}$$

In (26), by selecting  $\xi$ =0.707 and  $\omega_n$  =2 $\pi$ 20rad/s,  $k_p$  and  $k_i$  can be calculated.

For DMAF-PLL, the DP is ignored at first, and when MAF is replaced by the LPF, the standard design procedure presented in [38] can be applied to design the parameters of DMAF-PLL. Therefore, the transfer function of DMAF-PLL is derived as

$$G_{ol}^{DMAF} \approx \frac{2}{T_{oi}} \frac{(k_p s + k_i)}{s^2 (s + 2/T_{oi})}$$

(27)

According to the symmetrical optimum method,  $k_p$  and  $k_i$  can be expressed as

$$2/T_{\omega} = b\omega_c, \ k_p = \omega_c, \ k_i = \omega_c^2/b \tag{28}$$

where  $\omega_c$  is the cutoff angle-frequency and b is a constant which is suggested to be 2.4 in [37]. In [36],  $T_\omega$ =0.0033 s, and  $\omega_c$  is set to be 250 rad/s. Therefore,  $k_p$  and  $k_i$  can be calculated. According to the aforementioned parameters design method, the control parameters of the four MAF-based PLL algorithms are summarized in Table I.

TABLE I

CONTROL PARAMETERS OF THE MAF-BASED PLL

ALGORITHMS

|                      | QT1-PLL | HPLL  | MPLC-PLL | DMAF-PLL                    |

|----------------------|---------|-------|----------|-----------------------------|

| N(MAF)               | 100     | 100   | 100      | 33                          |

| $k_p$                | 92      | 94    | 177.71   | 250                         |

| $k_i$                |         |       | 15791    | 26041                       |

| r                    |         |       | 0.99     |                             |

| $k_{arphi}$          |         | 0.005 |          |                             |

| N(aMAF)              |         |       |          | round $(2\pi/\omega_0 T_s)$ |

| $n(\alpha\beta DSC)$ |         | 2     |          |                             |

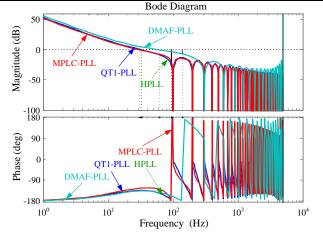

Fig. 14. Bode diagram of open-loop transfer functions of the MAF-based PLLs.

The bode diagram of the QT1-PLL, HPLL, MPLC-PLL, and DMAF-PLL is obtained by using open-loop transfer function of (10), (15), (17), and (22), as shown in Fig. 14. It can be noticed from Fig. 14 that the QT1-PLL (blue solid line) and HPLL (green dot line) show almost the same frequency response, because the difference between QT1-PLL and

HPLL mainly lies on coordinate transformation instead of the control loop. The crossover frequencies (CFs) of QT1-PLL and HPLL are both 32.9 Hz, which ensures a relatively fast dynamic response. The GM and PM are both 27.6 dB and 45.5°, respectively, which ensures a sufficient stability margin of these PLLs.

The MPLC-PLL (red solid line) shows a similar frequency response compared with QT1-PLL and HPLL. And the CF of MPLC-PLL is approximately 30.7 Hz, which is much higher compare with the conventional MAF-based PLL. The GM and PM are 20.4 dB and 55°, respectively, which is the desired stability margin. However, the DMAF-PLL shows a different frequency response compared with other three PLL algorithms due to the difference between the MAF window lengths. The CF of DMAF-PLL is the highest (about 62 Hz) due to the small window length and the high proportional gain. And the system GM and PM are 6.61 dB and 37.7°, respectively.

In the high frequency range, the four PLLs show similar amplitude-frequency characteristics. The DMAF-PLL algorithm almost blocks the high frequency components of integer multiples of 300 Hz, however, for other three PLLs, that is 100 Hz.

#### SEQUENCE COMPONENTS EXTRACTION **METHODS**

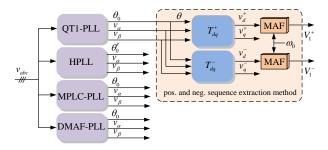

Fig. 15. Block diagram of the fundamental frequency positive and negative sequence amplitude extraction.

Fig. 15 shows the block diagram of the fundamental frequency positive (pos.) negative (neg.) sequence amplitude extraction. The extraction method is shown in the dotted frame in which four input signals  $\theta$ ,  $v_{\alpha}$ ,  $v_{\beta}$ , and  $\omega_0$  are required. For HPLL, it should be noticed that the phase-angle used for amplitude extraction is  $\theta_d$  (not  $\theta_0$ ). If use  $\theta_0$ , the input voltage should be  $v_a$  and  $v_b$  (not  $v_a$ , and  $v_b$ ). However, this selection will make the extraction procedure sluggish. The signal mentioned in this Section are all shown in corresponding block diagram of each PLL. transformation matrix to extract the positive and negative sequence is expressed a

$$T_{dq}^{+} = \begin{bmatrix} \cos(\theta) & \sin(\theta) \\ -\sin(\theta) & \cos(\theta) \end{bmatrix}, T_{dq}^{-} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{bmatrix}$$

(29)

Thus,  $v_d^+$  and  $v_d^-$  can be expressed as

$$v_{d}^{+} = \begin{cases} V_{1}^{+} + f(2\omega_{n}, 6\omega_{n}...) & \text{HPLL, DMAF-PLL} \\ V_{1}^{+} + f(\omega_{n}, 2\omega_{n}, 6\omega_{n}...) & \text{QT1-PLL, MPLC-PLL} \end{cases}$$

(30)

$$v_{d}^{-} = \begin{cases} V_{1}^{-} + f(2\omega_{n}, 6\omega_{n}...) & \text{HPLL, DMAF-PLL} \\ V_{1}^{-} + f(\omega_{n}, 2\omega_{n}, 6\omega_{n}...) & \text{QT1-PLL, MPLC-PLL} \end{cases}$$

(31)

$$v_{d}^{-} = \begin{cases} V_{1}^{-} + f(2\omega_{n}, 6\omega_{n}...) & \text{HPLL, DMAF-PLL} \\ V_{1}^{-} + f(\omega_{n}, 2\omega_{n}, 6\omega_{n}...) & \text{QT1-PLL, MPLC-PLL} \end{cases}$$

(31)

where f is the oscillating term caused by unbalance grid voltage, harmonics, and dc offset.

The MAF window length is set to be frequency adaptive (the estimated period is  $2\pi/\omega_0$ ). Therefore, the accuracy of the frequency estimation affects the accuracy for the positive and negative sequence components extraction to a large extent.

#### EXPERIMENTAL RESULTS AND DISCUSSIONS

The aim of this section is to evaluate the performance of the four PLLs under different grid voltage disturbance scenarios which is generated by the grid simulator by using a three-phase voltage source inverter (VSI) controlled in the voltage control mode (VCM) [38]. To validate the analysis, the experimental prototype was based on the 2.2 kW Danfoss inverter controlled in VCM using LCL output filter with resistive load, the capacitor voltage of the LCL filter was controlled to synthesize the virtual grid conditions. The inverter PWM frequency was set to be 10 kHz in order to evaluate the PLL algorithms with a discrete time-step of 100 microseconds, as analyzed in the paper.

Fig. 16. Photo of the experimental set-up [38, 39].

The dSPACE1006 platform was utilized to implement the Simulink-based control algorithms and the compiled executable file was downloaded to the dSPACE1006 controller to extract the real-time grid-synchronization signals. The binary word size was only several kilobytes (kB) when the VCM was adopted for inverter control and the four PLL algorithms were implemented, which facilities the practical implementation in both fixed point and floating point digital signal processors (DSPs) [see Fig. 16] [39]. The detailed comparison of the four PLL under different grid disturbance scenarios are shown in Table II and Table III.

Case1. Performance Comparison Under 90 ° Phase-Angle

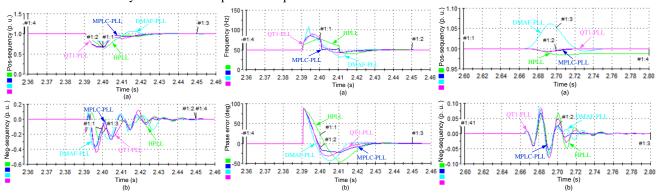

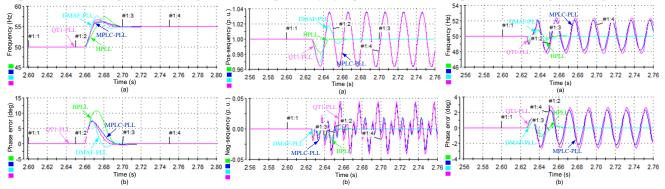

Fig. 17 shows the pos. and neg. sequence amplitudes and Fig. 18 illustrates the estimated frequency and the phase estimation error under phase-angle jump of +90°. It can be noticed all the PLLs can achieve zero steady-state error of all amplitude, frequency and phase in 2.5 cycles. However, the DMAF-PLL shows an overshoot of 60 Hz in the estimated frequency, and HPLL shows the smallest overshoot of about 28 Hz. In terms of the phase-angle estimation, the HPLL shows an overshoot of about 50°, and the MPLC-PLL shows the smallest overshoot of about 20°.

Case2. Performance Comparison Under +5 Hz Frequency Jump

Fig. 19 shows the pos. and neg. sequence amplitudes under frequency jump of +5 Hz. It can be seen that all of the PLLs can achieve zero steady-state error in positive sequence

except for HPLL, where the steady-state error is caused by the non-frequency adaptive DSC. In negative sequence frame, all the PLLs can achieve zero steady-state error in about 3 cycles.

Fig. 20 illustrates the estimated frequency and the phase estimation error under frequency jump of +5 Hz. For the four PLLs, similar results are achieved, and the estimated frequency is locked to the rated value in about 2 cycles. The HPLL and DMAF-PLL show similar overshoots of about 2.5 Hz. In terms of phase-angle estimation, HPLL has the largest overshoot of 12°, and other three PLLs show an overshoot of about 8°.

Fig. 17. Estimated pos. and neg. sequence Fig. 18. Estimated frequency and phase error amplitudes under +90 °phase-angle jump.

under +90 °phase-angle jump.

Fig. 19. Estimated pos. and neg. sequence amplitudes under frequency jump of +5 Hz.

Fig. 20. Estimated frequency and phase error Fig. 21. Estimated pos. and neg. sequence Fig. 22. Estimated frequency and phase error under frequency jump of +5 Hz.

amplitudes under dc offset.

under dc offset.

#### Case3. Performance Comparison Under DC Offset

Fig. 21 shows the pos. and neg. sequence amplitudes under dc offset. Due to the application of aMAF in DMAF-PLL and DSC in HPLL, the two PLL can achieve zero steady state error in pos. and neg. sequence amplitudes. However, for QT1-PLL and MPLC-PLL, the noticeable fundamental frequency oscillation can be observed in positive and negative sequence amplitudes. Fig. 22 illustrates the estimated frequency and the phase estimation error under dc offset. Because the MAF in QT1-PLL and MPLC-PLL cannot filter out the fundamental frequency oscillations caused by dc offset, the two PLLs show similar fluctuations both in the estimated frequency and phase angle. For HPLL, the estimated frequency is locked to the rated value in about one cycle. For DMAF-PLL, however, longer response time is needed (about 2 cycles) to achieve a zero steady-state error due to the large window length of aMAF.

Case4. Performance Comparison Under 0.4 p. u. Single-Phase Voltage Sag

Fig. 23 shows the pos. and neg. sequence amplitudes under 0.4 p. u. single-phase voltage sag. It shows that all PLLs achieve zero steady-state error in both positive and negative sequence amplitudes, which show the fastest dynamic response. However, DMAF-PLL algorithm shows the slowest transient response due to the use of aMAF.

Fig. 24 illustrates the estimated frequency and the phase estimation error under 0.4 p. u. single-phase voltage sag. It can be seen that QT1-PLL shows the shortest response time (less than one cycle), but for DMAF-PLL, response time is greater than 2 cycles. For HPLL and MPLC-PLL, the setting time is about 2 cycles. Similar transient overshoots in

frequency can be observed in QT1-PLL, DMAF-PLL and MPLC-PLL (about 3 Hz), and HPLL shows a frequency overshoot of about 1.8 Hz.

Fig. 26. Estimated frequency and phase error under two-phase voltage sag.

Fig. 27. Estimated pos. and neg. sequence amplitudes under three-phase voltage sag.

ce Fig. 28. Estimated frequency and phase error under three-phase voltage sag.

Case5. Performance Comparison Under 0.4 p. u. Two-Phase Voltage Sag

Fig. 25 shows the estimated pos. and neg. sequence amplitudes and Fig. 26 illustrates the estimated frequency and the phase estimation error under 0.4 p. u. two-phase voltage sag. Similar to the case of single-phase voltage sag, all PLLs can achieve zero steady-state error in the positive and negative sequence amplitudes, frequency and phase, and the QT1-PLL and DMAF-PLL show the fastest and slowest dynamic response, respectively. The highest and lowest overshoot in frequency is found in MPLC-PLL (about 3.5 Hz) and HPLL (about 1.5 Hz), respectively.

Case6. Performance Comparison Under 0.4 p. u. Three-Phase Voltage Sag

Fig. 27 shows the pos. and neg. sequence amplitudes and Fig. 28 illustrates the estimated frequency and the phase estimation error under 0.4 p. u. three-phase voltage sag. In positive and negative sequence amplitudes, the experimental waveforms are similar to the case of the single-phase and two-phase voltage sag. The estimated frequency and phase error of QT1-PLL, MPLC-PLL and HPLL is not affected by three-phase voltage sag. However, a high overshoot of about 6 Hz in the estimated frequency and slow dynamic response of about 3 cycles is found in DMAF-PLL, which is mainly because of the highly

nonlinear system caused by the aMAF.

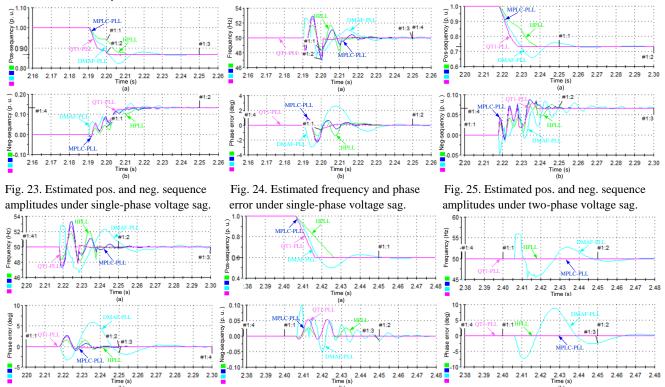

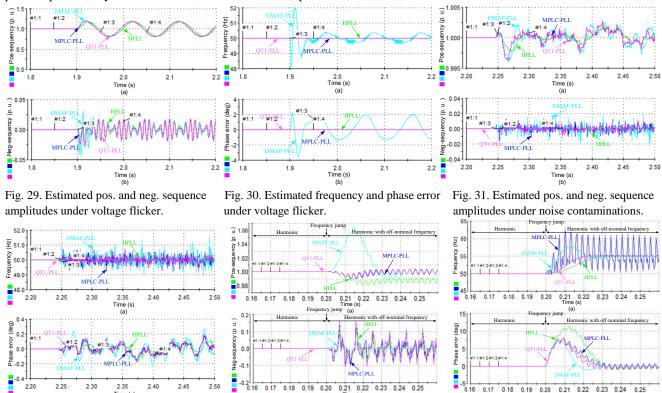

Case7. Performance Comparison Under Voltage Flicker

Fig. 29 shows the pos. and neg. sequence amplitudes under voltage flicker. It can be observed that all the PLLs fail to achieve zero steady-state error and obvious ripple is found both in pos. and neg. sequence amplitude.

Fig. 30 illustrates the estimated frequency and the phase estimation error under voltage flicker. Similar to the case of three-phase voltage sag, all PLLs are not affected by voltage flicker except for the DMAF-PLL, which shows steady-state oscillations both in the estimated frequency of about 1.5 Hz and the estimated phase angle of about 3.5  $^{\circ}$ , which may also caused by the *a*MAF.

Case8. Performance Comparison Under Noise Contaminations

To evaluate the noise immunity of PLLs, a zero-mean Gauss white noise of variance  $\sigma^2$ =0.01 is added to the input. The signal-to-noise-ratio (SNR) is  $10 \log (1/2\sigma^2) = 17$  dB. The noisy waveform is sampled at a rate of 100 kHz, and is then fed to a digital anti-aliasing filter. This high sampling rate is used to avoid the aliasing effects and increase the accuracy. A digital first-order LPF with cutoff frequency of 4 kHz is considered as the anti-aliasing filter. The output of anti-aliasing filter is down sampled to 10 kHz and is fed to the PLL.

Fig. 31 shows the pos. and neg. sequence amplitudes, and Fig. 32 illustrates the estimated frequency and the phase estimation error. It can be seen that all PLLs have similar peak to peak steady-state oscillation, for the estimated pos.

and neg. sequence amplitude, that is about 0.005 p. u. and 0.04 p. u., respectively, for estimated frequency and phase, that is about 2 Hz and 0.4  $^\circ$ , respectively.

Fig. 32. Estimated frequency and phase error under noise contamination.

Fig. 33. Estimated pos. and neg. sequence amplitudes under harmonic with frequency jump.

Fig. 34. Estimated frequency and phase error under harmonic with frequency jump.

## Case9. Performance Comparison Under Harmonics with Frequency Jump

In order to analyze the frequency-adaptive performances of the four MAF-based PLLs, the harmonic (0.1 p. u. of -5th, and 0.05 p. u. of +7th, -11th, and +13th harmonics) with frequency jump (+5 Hz) scenario is subjected to the grid voltage.

Fig. 33 shows the estimated pos. and neg. sequence amplitude and Fig. 34 illustrates the estimated frequency and the phase estimation error. It can be seen that when the grid voltage only suffer from the harmonic (before 0.2s), the four MAF-based PLL all can achieve the zero steady-state error in amplitude, frequency and phase estimation. When the frequency jump occurs (0.2s), the DMAF-PLL shows the best steady-state performance with lowest oscillation. However, the MPLC-PLL shows the biggest oscillation in estimated frequency mainly because of the phase-lead compensator which will actually amplify the error signal under harmonic with off-nominal frequency condition. The detail steady-state oscillation amplitude is shown in Table III.

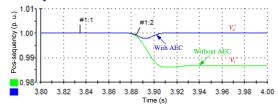

#### VI. PERFORMANCE IMPROVEMENT OF HPLL BY USING AMPLITUDE ERROR COMPENSATION METHOD

From the previously performance comparison, the four PLL all have satisfactory performance under various disturbances. For HPLL, when frequency jump occurs, some improvement method should be made to eliminate the steady-state error in the positive sequence amplitude estimation since extraction of positive sequence of fundamental components is critical for grid-connected inverters for grid synchronization. Therefore, inspired by the phase-error compensation (PEC) in HPLL, the amplitude error compensation (AEC) is proposed herein. From (12), the  $\alpha\beta$ DSC<sub>2</sub> output signal amplitude can be written as:

$$A = \sin(\frac{\omega + \Delta\omega_i}{\Delta})T \tag{32}$$

Thus, the amplitude error caused by  $\alpha\beta DSC_2$  operator can be expressed as:

$$\Delta A = 1 - \cos(\frac{\Delta \omega_i T}{4}) \tag{33}$$

Since the average value of  $\Delta\omega_o$  is equal to  $\Delta\omega_i$  under locked condition, the amplitude error at the output of HPLL can be compensated by online calculation of (33). The block diagram of HPLL with AEC is shown in Fig. 35. The  $V_d^+$  indicates the positive sequence amplitude after AEC and  $k_a=T/4$ . It should be noticed that the AEC is not connected to

the control loop and the dynamics of HPLL is unaffected. Therefore, from Fig. 35,  $V_d^+$  can be expressed as

$$V_{d}^{+} = 1 + V_{1}^{+} - \cos(\frac{\Delta \omega_{l}T}{4})$$

$$V_{d}^{-} = 1 + V_{1}^{+} - \cos(\frac{\Delta \omega_{l}T}{4})$$

$$V_{d}^{+} = 1 + V_{1}^{+} - \cos(\frac{\Delta \omega$$

Fig. 35. Block diagram of HPLL with the proposed AEC.

The experimental result with and without AEC is shown in Fig. 36. It shows that the AEC effectively compensates the amplitude error and achieves a zero steady-state error in about 1.5 cycles.

Fig. 36. Estimated positive sequence amplitude with and/or without AEC under frequency jump of +5 Hz.

#### VII. CONCLUSION

In this paper, a detailed analysis and performance comparison of the four MAF-based PLLs is presented. For the QT1-PLL, the introduction of the quasi-type-1 control structure effectively improves the dynamic response of the MAF-PLL. The lack of dc offset and even harmonic rejection is the main disadvantages of this PLL algorithm. Apart from this, the QT1-PLL shows a satisfactory steady-state and dynamic performance, and disturbance rejection capability under others grid voltage disturbance conditions.

The HPLL can be perceived as the improved version of the QT1-PLL algorithm. The application of the  $\alpha\beta$ DSC<sub>2</sub> block can effectively overcome the shortcomings of QT1-PLL without jeopardizing its dynamic performance and filtering capability. However, the disturbance rejection capability of the HPLL and QT1-PLL decreases with the frequency deviation from its nominal value under harmonic scenario caused by the non-frequency adaptive MAF and DSC, then a

associated drawback of the HPLL is the amplitude tracking error [see Fig. 19] and the to tackle this problem, the amplitude error compensation (AEC) method is proposed in last Section, which effectively compensates the amplitude error and ensures the accuracy of the positive sequence component extraction.

For the MPLC-PLL, the cascading of the MAF and phase-lead compensator results in the fast dynamic response of the SRF-PLL and the disturbance rejection capability of the MAF-PLL while increasing the frequency estimation error under harmonic with off-nominal frequency scenario. Similar to the QT1-PLL, however, the MPLC-PLL is also not suitable for grid-synchronization when the grid voltages contains the dc offset and even order harmonics, and under other grid voltage disturbance scenarios, the MPLC-PLL can be a good choice.

For the DMAF-PLL, the window length of the MAF in control loop is drastically reduced through the use of 'DP' which significantly improves the system dynamic response. The frequency adaptive aMAF (n=2 shown in Section II Part A) ensure the best steady-state performance under harmonic with off-nominal frequency scenario while making the dynamic response sluggish and may even lead to system instability under some circumstances like voltage sag and flicker. Hence, it can be concluded that the DMAF-PLL can be used for grid-synchronization when the grid voltage is free from sag and flicker. The research findings of this paper may provide some useful guidelines for grid-synchronization of the three-phase grid-connected PWM inverters and distributed generators (DGs) in the smart grid.

#### ACKNOWLEDGMENT

This work was supported in part by the National Natural Science Foundation of China under Grant 51307015, and in part by the State Key Laboratory of Power Transmission Equipment & System Security and New Technology under Grant 2007DA10512713405, and in part by the Open Research Subject of Sichuan Province Key Laboratory of Power Electronics Energy-Saving Technologies & Equipment under Grant szjj2015-067, and in part by the Open Research Subject of Artificial Intelligence Key Laboratory of Sichuan Province under Grant 2015RZJ02, and in part by the Fundamental Research Funds of Central Universities of China under Grant ZYGX2015J087.

TABLE II COMPARISON OF THE MAF-BASED PLLS UNDER PHASE/FREQUENCY JUMP AND VOLTAGE SAG

|                                    | QT1-PLL |        | HF    | HPLL   |       | MPLC-PLL |       | DMAF-PLL |  |

|------------------------------------|---------|--------|-------|--------|-------|----------|-------|----------|--|

|                                    | (a)     | (b)    | (a)   | (b)    | (a)   | (b)      | (a)   | (b)      |  |

| Phase-Angle Jump of +90 $^{\circ}$ | 36 ms   | 40 Hz  | 45 ms | 25 Hz  | 38 ms | 35 Hz    | 40 ms | 60 Hz    |  |

| Frequency Jump of +5 Hz            | 35 ms   | 1.7 Hz | 37 ms | 2.5 Hz | 38 ms | 1.3 Hz   | 40 ms | 2.8 Hz   |  |

| 0.4 p. u. Single-Phase Voltage Sag | 10 ms   | 2.5 Hz | 20 ms | 1.8 Hz | 10 ms | 3.2 Hz   | 43 ms | 2.8 Hz   |  |

| 0.4 p. u. Two-Phase Voltage Sag    | 10 ms   | 2.8 Hz | 20 ms | 2.1 Hz | 10 ms | 3.4 Hz   | 41 ms | 3.8 Hz   |  |

| 0.4 p. u. Three-Phase Voltage Sag  | 20 ms   | 0 Hz   | 20 ms | 0 Hz   | 10 ms | 0 Hz     | 42 ms | 7.2 Hz   |  |

Note: (a) and (b) represent setting time and frequency overshoot, respectively.

| TABLE III COMPARISON OF THE MAF-BASED PLLS UNDER DC OFFSET, FLICKER, NOISE AND HARMONIC |

|-----------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------|

|                             | QT1-PLL  |          | HPLL     |             | MPLC-PLL  |          | DMAF-PLL    |                       |

|-----------------------------|----------|----------|----------|-------------|-----------|----------|-------------|-----------------------|

|                             | (a)      | (b)      | (a)      | (b)         | (a)       | (b)      | (a)         | (b)                   |

| DC Offset                   | 4.6 Hz   | 5.2 °    | 0 Hz     | 0 °         | 4.0 Hz    | 4.5 °    | 0 Hz        | 0 °                   |

| Voltage Flicker             | 0 Hz     | 0 °      | 0 Hz     | 0 °         | 0 Hz      | 0 °      | 1.5 Hz      | 3.3 °                 |

| Noise                       | 1.5 Hz   | 0.3 °    | 1.5 Hz   | $0.2^\circ$ | 1.3 Hz    | 0.3 °    | 1.9 Hz      | 0.5 °                 |

| Harmonics without/with +5Hz | 0/0.4 Hz | 0 %1.6 ° | 0/0.2 Hz | 0 %1.5 °    | 0/10.5 Hz | 0 %1.4 ° | 0.04/0.6 Hz | 0.01 %0.05 $^{\circ}$ |

Note: (a) and (b) represent peak-to-peak frequency error and peak-to-peak phase error, respectively.

#### REFERENCES

- [1] A. Cataliotti, V. Cosetino, D. D. Cara, S. Guaiana, N. Panzavecchia, G. Tine, "A new solution for low-voltage distributed generation interface protection system," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 8, pp. 2086-2095, Aug. 2015.

- [2] Z. X. Zou, K. L. Zhou, Z. Wang, and M. Cheng, "Frequency-adaptive fractional-order repetitive control of shun active power filter," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1659-1668, Mar. 2015.

- [3] B. Ando, S. Baglio, A. Pistorio, G. M. Tina, and C. Ventura, "Sentinella: smart monitoring of photovoltaic systems at panel level," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 8, pp. 2188-2199, Aug. 2015.

- [4] European Standard EN50160 (2007) "Voltage characteristics of electricity supplied by public distribution system", CENELEC, Brussels, Belgium, 2007.

- [5] L. Hadjidemetriou, E. Kyriakides, and F. Blaabjerg, "A roubust synchronization to enhance the power quality of renewable energy systems," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 4858-4868, Aug. 2015.

- [6] B. Q. Liu, F. Zhao, Y. X. Zhu, H. Yi, and F. Wang, "A three-phase PLL algorithm based on signal reforming under distorted grid condition," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 5272-5238, Sep. 2015.

- [7] L. Hadjidemetriou, and F. Blaabjerg, "An adaptive tuning mechanism for phase-locked loop algorithms for faster time performance of interconnected renewable energy sources", *IEEE Trans. Ind. App.*, vol. 52, no. 1, pp. 1792-1804, Mar. 2015.

- [8] S. Golestan, M. Ramezani, and J. M. Gurrero, "An analysis of the PLLs with secondary control path," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4824-4828, Sep. 2014.

- [9] M. Kaimi-Ghartemani, S. A. Khajehoddin, P. K. Jain, and A. Bakhshai, "Derivation and design of in-loop filters in phase-locked loop systems," *IEEE Trans. Instrum. Meas.*, vol. 61, no. 4, pp. 930-940, Apr. 2012.

- [10] F. D. Freijedo, A. G. Yepes, O. Lopez, P. Fernandez-Comesana, J. Doval-Gandoy, "An optimized implementation of phase locked loops for grid applications," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 9, pp. 3110-3119, Sep. 2012.

- [11] J. A. de la O Serna, "Synchrophasor measurement with polynomial phase-locked loop taylor-fourier filters," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 2, pp. 328-337, Feb. 2015.

- [12] L. Feola, R. Langella, and A. Testa, "On the effects of unbalances, harmonic and interharmonics on PLL systems," *IEEE Trans. Instrum. Meas.*, vol. 62, no. 9, pp. 2399-2409, Sep. 2015.

- [13] C. Subramanian, and R. Kanagaraj, "Rapid tracking of grid variable using prefiltered synchronous reference frame PLL," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 7, pp. 1826-1836, Jul. 2015.

- [14] S. Golestan, M. Monfared, and F. D. Freijedo, and Guerrero, "Performance improvement of a prefiltered synchronous reference frame PLL by using a PID-type loop filter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3469-3479, Jul. 2014.

- [15] M. S. Reza, M. Ciobotaru, and V. G. Agelidis, "Instantaneous power quality analysis using frequency adaptive Kalman filter technique," in *Proc. IEEE Int. Power Elect. Motion Cont. Conf.*, 2012, pp. 81–87.

- [16] J. Svensson, "Synchronisation methods for grid-connected voltage source converters," *Proc. Inst. Electr. Eng. Gener. Transm. Distrib.*, vol. 148, no. 3, pp. 229-235, May 2001.

- [17] K. J. Lee, J. P. Lee, D. Shin, D. W. Yoo, and H. J. Kim, "A novel grid synchronization PLL method based on adaptive low-pass notch filter for grid-connected PCS," *IEEE Trans. Ind. Electron.*, vol. 61, no. 1, pp. 292-301, Jan. 2014.

- [18] F. A. S. Neves, H. E. P. de Souza, M. C. Cavalcanti, F. Bradaschia, and E. Bueno, "Digital filters for fast harmonic sequence

- components separation of unbalanced and distorted three-phase signals," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3847-3859, Oct. 2012.

- [19] W. Li, X. Ruan, C. Bao, D. Pan, and X.Wang, "Grid synchronization systems of three-phase grid-connected power converters: A complex vector filter perspective," *IEEE Trans. Ind. Electron.*, vol. 61, no. 4, pp. 1855-1870, Apr. 2014.

- [20] R. Cardenas, M. Diaz, F. Rojas, and J. Clare, "Fast convergence delayed signal cancellation method for sequence component separation," *IEEE Trans. Power Deli.*, vol. 30, no. 4, pp. 2055-2057, Aug. 2015.

- [21] Y. N. Batista, H. E. P. Souza, F. A. S. Neves, R. F. D. Filho, and F. Bradaschia, "Variable-structure generalized delayed signal cancellation PLL to improve convergence time," *IEEE Trans. Ind. Electron.*, vol. 62, no. 11, pp, 7146-7150, Nov. 2015.

- [22] S. Golestan, F. D. Freijedo, A. Vidal, A. G. Yepes, J. M. Guerrero, and J. Doval-Gandoy, "An efficient implementation of generalized delayed signal cancellation PLL," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1085-1094, Feb. 2016.

- [23] Y. F. Wang, and Y. W. Li, "Three-phase cascaded delay signal cancellation PLL for fast selective harmonic detection, *IEEE Trans. Ind. Electron.*, vol. 61, no. 4, pp. 1452-163, Apr. 2013.

- [24] L. S. Xiong, F. Zhuo, X. K. Liu, and M. H. Zhu, "Research on typical harmonic elimination algorithms in phase synchronization control," in 17th European Conf. on Power Electronics and Application (EPE'15 ECCE-Europe), 2015, pp. 1-10.

- [25] S. Golestan, M. Ramezani, J. M. Guerrero, and M. Monfared, "dq-Frame cascaded delayed signal cancellation-based PLL: analysis, design, and comparison with moving average filter-based PLL," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1618-1632, Mar. 2015.

- [26] S. Golestan, M. Ramezani, F. D. Freijedo, M. Monfared, and J. M. Guerrero, "Moving average filter based phase-locked loop: performance analysis and design guidelines," *IEEE Trans. Power Electron.*, vol. 29, no, 6, pp. 2750-2763, Jul. 2013.

- [27] V. Valouch, P. Simek, and J. Skramlik, "New three phase PLL and FLL techniques for converters used in distributed sources," in Proc. IEEE 16th Int. Scientific Conf. on Electric Power Engineering, May. 2015, pp. 94-99.

- [28] L. Wang, Q. R. Jiang, and L. C. Hong, "A novel three-phase software phase-lock loop based on frequency-locked loop and initial phase angle detection phase-locked loop," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4538-4549, Oct. 2013.

- [29] L. S. Xiong, F. Zhuo, and X. K. Liu, "Optimal design of moving average filter and its application in distorted grid synchronization," in IEEE Conf. on Energy Conversion Congress and Exposition (ECCE), 2015, pp. 3449-3454.

- [30] L. R. Zheng, H. Geng, and G. Yang, "Improved phase-locked loop under heavily distorted grid condition," in 41st Annual Conference of the IEEE Industrial Electronics Society, IECON. 2015, pp. 4778-4783.

- [31] S. Golestan, J. M. Guerrero, A. Vidal, A. G. Yepes, and J. D. Gandoy, "PLL with MAF-based prefiltering stage: small-signal modeling and performance enhancement," *IEEE Trans. Power Electron.*, vol.31, no.6, pp.4013-4019, Jun. 2016.

- [32] S. A. Lakshmanan, A. Jain, and B. S. Rajpourhit, "Analysis and design of adaptive moving average filters based low-gain PLL for grid connected solar power converters," *IEEE Power and Energy Society General Meeting*, 2015, pp.1-5.

[33] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero and J. D.

- [33] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero and J. D. Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6264-6270, Dec. 2014.

- [34] S. Golestan, J. M. Guerrero, A. M. Abusorrah, and Y. A. Turki, "Hybrid synchronous/stationary reference frame filter based PLL," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 5018-5022, Aug. 2015.

- [35] S. Golestan, J. M. Guerrero, and A. M. Abusorrah, "MAF-PLL with phase-lead compensator", *IEEE Trans. Ind. Electron.*, vol. 62, no. 6, pp. 3691-3695, Jun. 2015.

- [36] J. Y. Wang, J. Liang, F. Gao, L. Zhang, and Z. D. Wang, "A method to improve the dynamic performance of moving average filter based PLL," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5978-5990, Oct. 2015.

- [37] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Dynamics assement of advanced single-phase PLL structures," *IEEE Trans. Ind. Electron.*, vol. 60, no. 6, pp, 2167-2177, Jun. 2013.

- [38] J. E. Garcia, J. G. Vasquez, and J. M. Guerrero, "Grid simulator for power quality assessment of micro-grids," *IET Power Electron.*, vol. 6, no. 4, pp. 700-709, Apr. 2013.

- [39] Aalborg University. Microgrid Research Programme. [Online]. Available: www.microgrids.et.aau.dk.

Yang Han (S'08-M'10) was born in Chengdu, China. He received his Ph.D. in Electrical Engineering from Shanghai Jiaotong University (SJTU), Shanghai, China, in 2010. He joined the Department of Power Electronics, School of Mechatronics Engineering, University of Electronic Science and Technology of China (UESTC) in 2010, and where he has been an Associate Professor since 2013. From March 2014 to March 2015, he was a Visiting Scholar at the Department of Energy

Technology, Aalborg University, Aalborg, Denmark. His research interests include AC/DC microgrids, grid-connected converters for renewable and DGs, phase-locked loop (PLL), power quality, active power filters and static synchronous compensators (STATCOMs). He has authored more than 20 ISI-indexed journal papers and one book chapter in the area of power electronics, power quality conditioners, and smart grid. He received Best Paper Awards from 2013 Annual Conference of HVDC and Power Electronics Committee of Chinese Society of Electrical Engineers (CSEE) in Chongqing, China, and the 4th International Conference on Power Quality in 2008, in Yangzhou, China. He has five issued and eight pending patents. He is an active reviewer for IEEE Transactions on Power Electronics, IEEE Transactions on Smart Grid, IEEE Transactions on Industrial Electronics, IEEE Transactions on Sustainable Energy and IEEE Transactions on Energy Conversion.

Mingyu Luo was born in Sichuan, China, in 1992. He received the B. S. degree in Electrical Engineering and Automation from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2014, where he is currently working toward the M. S. degree in Power Electronics and Electric Drives.

His research interests include phase-locked loop, power quality, power converters, and DFIG-based

wind power generation system.

Changqing Chen was the deputy director in the regulation and control center of the Panzhihua Power Supply Company, State Grid Sichuan Electric Power Company, Panzhihua, China, in 2008. He has been the deputy director of operation and maintenance department of the Panzhihua Power Supply Company since 2014.

vehicle.

Aiting Jiang was born in Chongqing, China, in 1994. She will receive the B. S. degree in Electrical Engineering and Automation from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2016, where she will further working toward the M. S. degree in Power Electronics and Electric Drives.

Her research interests include phase-locked loop, power quality, power converters, and electric

Xin Zhao received the B.S. and M.S. degree in Power Electronics & Electrical Drives from Northwestern Polytechnical University, Xi'an, China, in 2010 and 2013, respectively. He is currently working toward the Ph.D. degree at Department of Energy Technology, Aalborg University, Denmark. His research interests include control of power converters, power quality and microgrids.

Josep M. Guerrero (S'01-M'04-SM'08-FM'15) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000 and 2003, respectively. Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where

he is responsible for the Microgrid Research Program. From 2012 he is a guest Professor at the Chinese Academy of Science and the Nanjing University of Aeronautics and Astronautics; from 2014 he is chair Professor in Shandong University; from 2015 he is a distinguished guest Professor in Hunan University; and from 2016 he is a visiting professor fellow at Aston University, UK.

His research interests is oriented to different microgrid aspects, including power electronics, distributed energy-storage systems, hierarchical and cooperative control, energy management systems, smart metering and the internet of things for AC/DC microgrid clusters and islanded minigrids; recently specially focused on maritime microgrids for electrical ships, vessels, ferries and seaports. Prof. Guerrero is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, and the IEEE Industrial Electronics Magazine, and an Editor for the IEEE TRANSACTIONS on SMART GRID and IEEE TRANSACTIONS on ENERGY CONVERSION. He has been Guest Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS Special Issues: Power Electronics for Wind Energy Conversion and Power Electronics for Microgrids; the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS Special Sections: Uninterruptible Power Supplies systems, Renewable Energy Systems, Distributed Generation and Microgrids, and Industrial Applications and Implementation Issues of the Kalman Filter; the IEEE TRANSACTIONS on SMART GRID Special Issues: Smart DC Distribution Systems and Power Quality in Smart Grids; the IEEE TRANSACTIONS on ENERGY CONVERSION Special Issue on Energy Conversion in Next-generation Electric Ships. He was the chair of the Renewable Energy Systems Technical Committee of the IEEE Industrial Electronics Society. He received the best paper award of the IEEE Transactions on Energy Conversion for the period 2014-2015. In 2014 and 2015 he was awarded by Thomson Reuters as Highly Cited Researcher, and in 2015 he was elevated as IEEE Fellow for his contributions on "distributed power systems and microgrids."