# **Aalborg Universitet**

## Full-bridge MMC DC fault ride-through and STATCOM operation in multi-terminal HVDC grids

Kontos, E.; Tsolaridis, Georgios; Teodorescu, Remus; Bauer, Pavol

Published in:

Bulletin of the Polish Academy of Sciences - Technical Sciences

DOI (link to publication from Publisher): 10.1515/bpasts-2017-0070

Creative Commons License CC BY-NC-ND 4.0

Publication date: 2017

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Kontos, E., Tsolaridis, G., Teodorescu, R., & Bauer, P. (2017). Full-bridge MMC DC fault ride-through and STATCOM operation in multi-terminal HVDC grids. *Bulletin of the Polish Academy of Sciences - Technical Sciences*, *65*(5), 653 - 662. https://doi.org/10.1515/bpasts-2017-0070

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES, Vol. 65, No. 5, 2017 DOI: 10.1515/bpasts-2017-0070

# Full-bridge MMC DC fault ride-through and STATCOM operation in multi-terminal HVDC grids

E. KONTOS<sup>1\*</sup>, G. TSOLARIDIS<sup>2</sup>, R. TEODORESCU<sup>2</sup>, and P. BAUER<sup>1</sup>

<sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>Aalborg University, Aalborg, Denmark

Abstract. This paper investigates a control structure to enhance the DC fault ride-through capability of a full-bridge modular multilevel converter (MMC) station, while ensuring a stable controlled operation as a STATCOM during DC faults without the need for fault isolation. Taking advantage of the switching states of a full-bridge submodule, a DC current controller is proposed, which provides the DC voltage reference for the modulation when a DC fault is detected. By changing the outer controllers strategy from DC voltage or active power control to converter energy control during a fault, the decoupling of the converter operation from the DC side dynamics is realized. In this paper, the focus is on the control methodology at all times of operation and the evaluation of the STATCOM control during a fault. To this end, extensive simulations were performed on a three-terminal high voltage direct current (HVDC) grid in radial configuration and a pole-to-pole DC fault case was investigated. The results showed that the AC voltage and current were controlled within limits at all times, while the full-bridge MMC was able to provide reactive power support to the AC grid. Moreover, using the proposed control methodology, the transients at the operation transition points between STATCOM and inverter/rectifier operation were minimized and the stations were able to safely ride through the fault.

Key words: DC current control, DC fault, HVDC converters, HVDC transmission, MMC, multiterminal networks, STATCOM.

#### 1. Introduction

Recent developments on the multilevel modular converter (MMC) technology qualify it as an important building block of high voltage direct current (HVDC) connections. Its design offers many advantages, such as low AC filter requirements, high efficiency, high modularity and controllability, which enable the realization of multi-terminal HVDC (MTDC) networks. However, there are still several challenges that need to be addressed before HVDC networks are safely implemented.

The main problem in HVDC networks stems from DC faults. Due to their inherent characteristics, such as fast transients (<1 ms), high peak currents and absence of natural zero crossing, it is not possible to interrupt DC fault currents by using traditional breakers/disconnectors [1]. As a result, many studies have focused on investigating the DC fault current characteristics [2, 3] and the stages of the grid natural response to the fault [1]. Moreover, research has been conducted on the design of DC breakers [4, 5], as well as on the design of different MMC submodules [6, 7], as adaptations to the main half-bridge valve concept, to ride through a DC fault.

In the case of DC faults, apart from the equipment protection, a grid needs to be designed in a way to ensure uninterrupted controllability of the MMC stations at all times. As a result, there is a need for operation isolation of the AC and the DC grid during faults. This becomes more apparent when weak grids, such as wind farms, need to be connected. In this

Bull. Pol. Ac.: Tech. 65(5) 2017

Manuscript submitted 2017-02-28, initially accepted for publication 2017-06-22, published in October 2017.

case, it is necessary to be able to provide AC voltage support and reactive power compensation to the AC grid continuously.

Overall there are two prevalent concepts for DC fault ridethrough in case of an HVDC network [8]: 1) combination of half-bridge MMC with DC breakers; 2) full-bridge MMC with simple mechanical disconnectors for the isolation of the DC fault part of the grid. In the first case, additional equipment, i.e. the DC breakers, has to be installed to protect the station. Unless the breaker total interruption time is lower than the DC fault travelling wave time from the fault point to to the converter station, the half-bridge valves experience a high overcurrent and block their control operation for protection [1]. As a result, the MMC operates as a diode-bridge rectifier, losing its control capability. In the second case, no additional equipment is necessary. As soon as the fault occurs, the full-bridge MMC is able to block the developing DC fault current in different ways, either maintaining [9, 10] or losing controllability [8, 11].

Several studies have investigated different aspects of the full-bridge MMC response to DC faults using single stations or point-to-point HVDC connections as case studies. The coupling between capacitor voltage variation and the maximum modulation index for full-bridge and hybrid MMC configuration was analysed in [9], while the relationship between ac/DC voltages and ac/DC side power, the arm current, as well as the capacitor voltage ripple in each submodule were investigated, in case the submodules adopt the negative voltage switching state. Moreover, in [10], the operation of different submodule topologies with fault-blocking capability was studied and a new leg capacitor energy balancing method by common-mode voltage injection was proposed. Alternate operation of the MMC arms between conducting and blocked mode when the DC voltage drops to zero, using clamp double submodules (CDSM-MMC),

<sup>\*</sup>e-mail: e.kontos@tudelft.nl

was proposed in [12]. However, in this case the DC current was not controlled to zero and thus, simple disconnectors could not be used for the fault isolation in case of permanent faults. Finally, a new control strategy to allow the operation of the MMC when the DC link voltage drops during different fault types was proposed in [13]. In this study the manipulation of insertion function DC bias to enable reduced DC voltage operation was presented. However, the energy balancing and STATCOM operation of the MMC during the fault were not investigated.

The main contribution of this paper is the proposal of a control structure of the full-bridge MMC station to allow its operation as a quasi-STATCOM during a DC fault in an MTDC grid. Taking advantage of the four switching states it offers (positive voltage, negative voltage, bypassed and blocked), a DC current control method is proposed and explained in detail. In this way, the MMC is able to drive the DC current to zero in a controlled manner, as soon as the fault is detected, protecting the DC grid assets and enabling the DC fault isolation by means of simple mechanical disconnectors. At the same time, the MMC is able to operate as a STATCOM, in full-bridge double-star (FB-DS) configuration, maintaining continuous control of the reactive power that it exchanges with the AC grid, providing reactive power compensation and AC voltage support. Unlike previous studies [9, 10, 13, 14], this paper investigates the maintenance of the internal balance of the STATCOM as the most important aspect at this stage of operation. By using arm and leg energy balancing controllers, which are analytically presented hereby, the MMC stations manage to ride through the fault maintaining their energy at nominal level and limiting the transients at the transition between STATCOM and inverter/rectifier operation. Finally, as soon as the DC fault is cleared, the converters are able to resume operation at their prefault state, after the DC voltage is ramped up to its nominal level through the internal control operation of the MMC.

The paper structure is as follows: Section 2 presents the main characteristics of the full-bridge MMC response during a DC fault and the proposed DC current controller is explained in detail. In Section 3, the developed MMC control structure is explained at the different stages of the DC fault, while Section 4 elaborates on the main controllers needed for the internal balance of the MMC. To verify the operation of the control, two case studies are described in Section 5, and the obtained results verifying the effectiveness of the proposed control structure are presented in Section 6. Finally, the most important findings are summarized and conclusions are drawn in Section 7.

### 2. Full-bridge DC fault operation

A full-bridge-based MMC is primarily designed with focus on reliability. In normal operation, the full-bridge submodules are modulated like half-bridge submodules, with only two of the switch valves operating at each moment.

The main difference in operation appears in case of a DC fault. During a DC fault, high overcurrents develop on the DC grid. As soon as a DC fault is detected, the AC side can be isolated from the DC side by inhibiting the control operation of the submodules. Once the control operation is blocked, un-

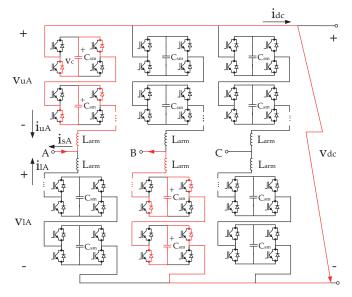

Fig. 1. Full-bridge MMC in short-circuit DC fault [11]

like the half-bridge submodules, which are bypassed by the antiparallel diodes of the IGBTs or the thyristors and continue feeding the fault, the full-bridge submodules are connected as shown in Fig. 1. In this case, no DC fault current can circulate, as it is directed through the capacitors of the submodules, which are connected in series and in opposing polarity to the current direction. As the total series capacitor voltage is higher than the peak line-to-line voltage of the AC grid, the current drops to zero. However, the disadvantage of this method is that controllability is lost and therefore, the MMC station cannot provide support to the AC side.

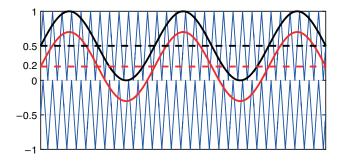

The usable range of the insertion index of each arm in half-bridge MMCs is limited to  $0 < n_{u,1} < 1$ . However, full-bridge MMC has the capability to work in the region  $-1 < n_{u,1} < 0$  as well, with its DC link voltage reversed [13]. Because of its structure, the full-bridge submodule is capable of creating three voltage levels at any given moment of operation, i.e.  $+v_c$ , 0 and  $-v_c$ . To achieve that through modulation, two carrier signals are generated for each submodule as shown in Fig. 2, controlling the two switch combinations (diagonal), which are switched on to produce the respective voltage level, depending on the arm current direction.

Fig. 2. Carrier signals (blue) of one submodule and the continuous insertion index signals (black and red solid lines) at two DC voltage offset values (black and red dashed lines) for one arm

During a DC fault, it was observed that by changing the polarity of the voltage in the submodules through control of the modulation index, zero-crossings of the DC current  $(i_{DC})$  were created. This polarity reversal is made possible through control of the DC voltage offset used to create the voltage reference signal for the modulation.

The PWM reference signals for the upper and lower arms of phase j = A, B, C ( $v_{uj}^*$  and  $v_{lj}^*$  respectively) are given by the following equations:

$$v_{\rm uj}^* = \frac{v_{\rm dc}^*}{2} - v_{\rm sj}^* - v_{\rm cj}^* \tag{1}$$

$$v_{lj}^* = \frac{v_{dc}^*}{2} + v_{sj}^* - v_{cj}^*$$

(2)

where  $v_{DC}^*$  is the DC voltage reference,  $v_{sj}^*$  is the output voltage reference and  $v_{cj}^*$  is the circulating voltage reference. Although, in normal operation the DC voltage is controlled by the outer DC voltage controller, during faults it can be controlled by the internal controllers of the MMC.

Hereby a controller is proposed to drive the  $i_{\rm DC}$  to zero. In fact, the controller creates the DC voltage offset of the reference signal  $v_{\rm DC}^*$  based on the  $i_{\rm DC}$  measurement and is activated once the DC fault is detected. More specifically, the  $i_{\rm DC}$  is compared to a zero reference and the error is driven through a PI controller, whose output determines the DC voltage offset. In normal operation, the DC voltage offset is set at 0.5 pu. Changing the DC voltage offset, the reference signal moves as shown in Fig. 2 and the respective virtual  $v_{\rm DC}$  is synthesized. Based on that observation, in case of a DC fault, the  $i_{\rm DC}$  can also be controlled to zero by controlling the synthesized  $v_{\rm DC}$ .

This controller needs to be fast to avoid a high overcurrent on the DC line and also on the valves, which would lead to

Fig. 3. DC current controller

the blocking of the control for their protection. Moreover, it needs to be accurate, as the  $i_{\rm DC}$  needs to drop to zero before the faulty line can be successfully isolated by a common mechanical disconnector. Therefore, the tuning of the controller is made based on those two objectives. The  $i_{\rm DC}$  controller is presented in Fig. 3.

### 3. Control structure

In case of a DC fault, three time periods can be distinguished in the converter operation: 1) before the fault; 2) during the fault and 3) after the fault. In this Section, this chronological order is followed to explain the converter control modes and the transition between the different stages.

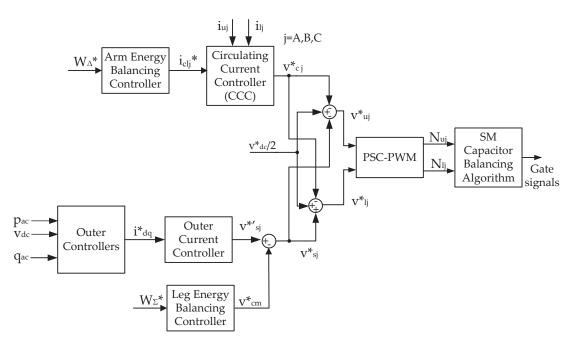

**3.1. Before the fault.** During normal operation the MMC is able to control either the  $v_{\rm DC}$  or the  $p_{\rm ac}$  through the outer controllers. Moreover, it can control the  $q_{\rm ac}$  depending on the needs of the connected AC grid. At the same time, internally, a circulating current controller is used to suppress the second harmonic of the circulating current, while arm and energy balancing controllers ensure the internal balance of the converter. Finally, PWM modulation, in this case phase-shifted carrier modulation (PSC-PWM), and a sorting algorithm are used to balance the submodule capacitor voltages, as shown in Fig. 4.

Fig. 4. Basic control structure of MMC

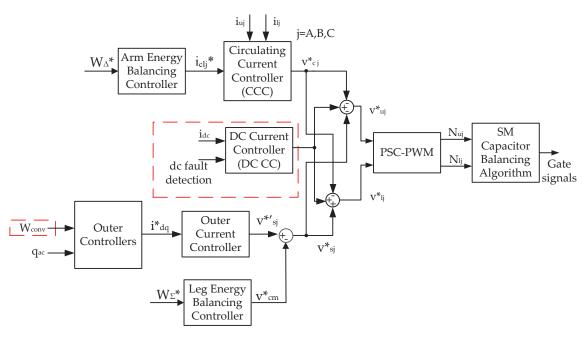

- **3.2. During the fault.** As soon as a DC fault occurs, overcurrents develop in the DC grid lines. The DC fault detection is triggered at a certain DC current threshold, usually at 2 pu [8]. If there is a short-circuit DC fault, the  $v_{\rm DC}$  collapses to zero and the converter can no longer maintain control of the  $v_{\rm DC}$  or  $p_{\rm ac}$ . To avoid that the energy of the converter collapses, the following control actions need to be followed:

- First, the v<sub>DC</sub> or p<sub>ac</sub> control mode needs to change to converter energy (W<sub>conv</sub>) control. Although the control of the v<sub>DC</sub> is lost as it drops to zero, the voltage of the submodules v<sub>c</sub> can be controlled independently. In fact, the control of the (W<sub>conv</sub>) and the capacitor balancing algorithm which is used after the employed modulation technique, ensure that the submodule capacitors remain charged at their nominal voltage level independent of the DC grid state of operation. By decoupling the DC grid voltage level from the submodule capacitor voltage levels, each arm can act as a virtual DC link even during a DC fault and thus, the MMC remains controllable [13]. In this way, the MMC is able to operate as STATCOM and provide reactive power support to the AC grid.

- Second, the i<sub>DC</sub> controller described in Section 2 is necessary to drive the i<sub>DC</sub> to zero and decouple the AC from DC side operation.

- Third, the arm and leg energy controllers are necessary for STATCOM operation and are explained in Section 4.

The control structure during STATCOM operation is shown in Fig. 5, where the differences to the control structure employed in normal operation are highlighted.

**3.3.** After the fault. After the  $i_{DC}$  is brought to zero, simple mechanical disconnectors can be used to isolate the faulty line. However, if the MMC station is only connected to the grid through the faulty line segment, it cannot resume operation in the DC grid, until the line has been replaced. As a result,

it is important that it keeps its controllability in order to continue supporting the AC grid. For the "healthy" part of the grid, the MMCs need to return to their normal pre-fault operation control. This transition is made by slowly ramping up the  $\nu_{\rm DC}$  level energizing the DC grid lines, before active power can be exchanged. In this study, a rate of rise of 0.5 pu/1 ms was used.

## 4. Energy balancing controllers

The converter energy balancing is essential for the MMC, especially for STATCOM operation [15], not only for internal parameter mismatches, but mainly in case of AC and DC contingency cases which can create imbalances between the arms and legs of the MMC. For this purpose, two controllers are described hereby, which ensure the decoupled leg and arm energy balancing.

**4.1.** Leg energy balancing controller. The leg energy balancing controller ensures that the total energy in the converter is equally distributed between its legs. From the mathematical analysis of the MMC operation, it can be deduced that the upper and lower arm power for phase j = A, B, C are expressed as [15, 16]:

$$p_{\rm uj} = i_{\rm cj} \frac{v_{\rm dc}}{2} - i_{\rm cj} v_{\rm j} + \frac{i_{\rm sj}}{2} \frac{v_{\rm dc}}{2} - \frac{i_{\rm sj}}{2} v_{\rm j}$$

(3)

$$p_{lj} = i_{cj} \frac{v_{dc}}{2} + i_{cj} v_j - \frac{i_{sj}}{2} \frac{v_{dc}}{2} - \frac{i_{sj}}{2} v_j$$

(4)

where  $i_{cj}$  is the circulating current in phase j,  $v_{DC}$  is the DC voltage,  $v_i$  is the phase j grid voltage and  $i_{si}$  is the phase j output current.

From the sum of the arm power terms, the derivative of the phase *j* leg energy sum is calculated as follows, neglecting the oscillating terms:

Fig. 5. Control structure of MMC in STATCOM operation

$$\frac{\partial W_{\Sigma,j}}{\partial t} = i_{\text{c0j}} v_{\text{dc}} - \hat{v}_{\text{sj}} \hat{i}_{\text{sj}} cos(\phi_{\text{ij}})$$

(5)

where  $i_{c0j}$  is the DC component of the circulating current in phase j,  $v_{sj}$  is the output voltage of phase j and  $\varphi_{ij}$  is the phase angle of the output current vector in phase j.

Usually, the DC component of the circulating current  $i_{c0j}$  is controlled to exchange active power between the converter legs. However, in case of a short-circuit DC fault,  $v_{DC}^*$  drops to zero driving the DC current to zero and thus, the first term of (5) is zero. Therefore, an adjustment to the  $v_{sj}^{*'}$ , which comes from the outer controllers, is needed to achieve leg energy balancing.

In [10], a method is proposed in which by controlling the common-mode voltage (CMV), the leg energies can be balanced. More specifically, the CMV in an MMC can be expressed as [17]:

$$v_{\rm cm} = \frac{1}{6} \sum_{\rm j = A,B,C} (v_{\rm lj} - v_{\rm uj})$$

(6)

To get the reference for the CMV, each leg's energy is controlled to 1/3 of the total converter energy at each moment of operation using a PI controller. This gives a reference signal  $p_j^{\Sigma*}$ , which is the sum of the active power that flows into upper and lower arm of each leg of the three-phase converter. The resulting  $p_j^{\Sigma*}$  is then tranformed into dq reference frame.

The reference for the CMV is given by [10]:

$$v_{\rm cm}^* = \operatorname{Re} \left\{ \frac{p_{\rm d}^{\Sigma*} + j p_{\rm q}^{\Sigma*}}{\frac{1}{2} (i_{\rm dc} + i i_{\rm cc})} \right\} \tag{7}$$

where Re is the real part of the expression between  $\{\}$ ,  $p_{\rm d}^{\Sigma*}$  and  $p_{\rm q}^{\Sigma*}$  are respectively the d and q components of the sum of powers that flow into upper and lower converter arms.

The CMV reference is subsequently subtracted from the  $v_{sj}^*$  reference resulting in a new reference as follows:

$$v_{\rm sj}^* = v_{\rm sj}^{*'} - v_{\rm cm}^* \tag{8}$$

**4.2. Arm energy balancing controller.** The arm energy balancing controller ensures that the total energy of each leg is equally distributed between the upper and lower arm. To achieve this, the energy difference between upper and lower arms should be controlled to zero.

The difference of the arm power terms from (3) and (4) is equal to the differential of the arm energy difference. Neglecting the oscillating terms, for phase *j* this can be expressed as [15, 16]:

$$\frac{\partial W_{\Delta,j}}{\partial t} = -\hat{v}_{sj}\hat{i}_{c1j}cos(\phi_{cj}) \tag{9}$$

where  $\hat{i}_{\text{clj}}$  is the peak value of the first fundamental of the circulating current in phase j and  $\phi_{\text{cj}}$  is the phase angle of the circulating current vector in phase j. Based on (9), it can be concluded that by controlling the injection of a fundamental

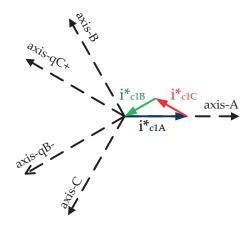

Fig. 6. Arm energy balancing controller current vectors for decoupled operation [15]

component in the circulating current, active power can be exchanged between the arms of each converter leg. To achieve this, a simple PI controller is implemented.

To avoid the active power coupling between the arms of different legs, a decoupling method is used as explained in [15]. If an unbalance in phase A is considered, an active current in phase with the voltage of phase A should be applied, as shown in Fig. 6. Assuming that there is no current flow to the DC side, the fundamental components of the circulating current should sum up to zero:

$$i_{c1A} + i_{c1B} + i_{c1C} = 0$$

(10)

To respect this condition, reactive current vectors in the other two phases are applied, as shown in Fig. 6. The magnitude of the vectors of phase B and phase C to be applied is a result of basic trigonometry and the law of cosines and is estimated as  $\sqrt{3}$  times smaller than the vector of phase A.

Due to the high degree of symmetry, the results can be extended to all three phases. Therefore, using a simple PI controller, the final current references for all phases are given by the following equations Arm energy balancing controller current vectors for decoupled operation [15]:

$$i_{c1a}^{*} = (K_{p,arm} + K_{i,arm} \int_{dt}) (e_{A}cos(\omega_{1}t) + \frac{1}{\sqrt{3}} e_{B}cos(\omega_{1}t + \frac{\pi}{2}) + \frac{1}{\sqrt{3}} e_{C}cos(\omega_{1}t - \frac{\pi}{2}))$$

$$i_{c1b}^{*} = (K_{p,arm} + K_{i,arm} \int_{dt}) (e_{B}cos(\omega_{1}t - \frac{2\pi}{3}) + \frac{1}{\sqrt{3}} e_{A}cos(\omega_{1}t - \frac{7\pi}{6}) + \frac{1}{\sqrt{3}} e_{C}cos(\omega_{1}t - \frac{\pi}{6}))$$

$$i_{c1c}^{*} = (K_{p,arm} + K_{i,arm} \int_{dt}) (e_{C}cos(\omega_{1}t + \frac{2\pi}{3}) + \frac{1}{\sqrt{3}} e_{A}cos(\omega_{1}t + \frac{7\pi}{6}) + \frac{1}{\sqrt{3}} e_{B}cos(\omega_{1}t + \frac{\pi}{6}))$$

$$(11)$$

where  $e_A$ ,  $e_B$  and  $e_C$  are the errors fed to the PI of each phase.

From the above equations, it becomes clear that an unbalance in the arm energies of phase A creates an error  $e_A$  and the controller commands the injection of a fundamental component of the circulating current in phase A, as well as a fundamental component in the other two phases aligned with their reactive axes in order to eliminate the unbalance. It has to be noted that, since two PI controllers are cascaded (arm energy controller and circulating current controller), in order to avoid interactions between them, the energy balancing control loop is tuned with a high phase margin and a relatively small bandwidth for stability reasons (approximately 10 times lower than the bandwidth of the circulating current controller) [16].

#### 5. Case studies

To test the performance of the proposed control structure for the MMC station and the effectiveness of the fault ride-through methodology during a pole-to-pole DC fault, two case studies were considered:

- 1. Case study (i): Single MMC station with a DC fault at its DC output;

- 2. Case study (ii): Three-terminal HVDC grid with a DC fault at the node of the radial connection.

A pole-to-pole fault, although rare, is the most severe DC fault case a DC connection can be subjected to. In this case, an almost solid pole-to-pole fault was tested with a fault resistance of 1 u $\Omega$ . The simulation models for the case studies were implemented in Matlab/Simulink.

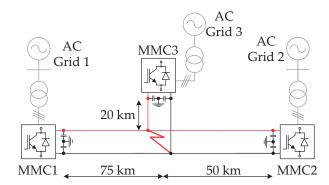

In case study (i) the full-bridge MMC is subjected to a poleto-pole DC fault at 1 m away from its DC connection point, as presented in Fig. 7. This is the worst-case scenario for a converter station as the valves are directly subjected to high overcurrents. The DC cable on each pole is simulated as a single pi-equivalent section.

Case study (ii) includes the HVDC connection of three AC grids in radial configuration, as shown in Fig. 8. The symmetrical monopole grid configuration is preferred as it is the most commonly used in HVDC connections. It has to be noted that the capacitors depicted at each station in Fig. 7 and Fig. 8 are part of the simulation pi-section model and are only shown to present the grounding points of the conductor shields.

All converter stations use full-bridge MMC technology. The main parameters of the grid and the converter stations are summarized in Table 1 and Table 2 respectively. In normal operation, MMC1 controls the  $v_{\rm DC}$ , while the other two stations directly control their respective  $p_{\rm ac}$ .

Fig. 7. Case study (i) – MMC1 with a pole-to-pole DC fault at its DC output

Fig. 8. Case study (ii) – Layout of the analyzed radial MTDC network with 3 terminals

Table 1 MTDC network parameters

| Network parameters                                | Unit                 | Value                      |

|---------------------------------------------------|----------------------|----------------------------|

| MMC rated power $(S_{MMC})$                       | MVA                  | 1200/1200/1200             |

| $\overline{\text{MTDC voltage } (V_{\text{DC}})}$ | kV                   | ±320                       |

| DC cable resistance $(R_{cable})$                 | $\Omega/\mathrm{km}$ | 0.0195                     |

|                                                   | mH/km                | 0.2                        |

| DC cable capacitance $(C_{cable})$                | nF/km                | 220                        |

| DC cable length (d1/d2/d3)                        | km                   | 75/50/20                   |

| Transformer voltage ratio                         | kV                   | $380/160 \ (Y_0 - \Delta)$ |

| Transformer rated power $(S_T)$                   | MVA                  | 1200/1200/1200             |

| Transformer leakage inductance $(L_T)$            | pu                   | 0.05                       |

Table 2 MMC simulation parameters

| MMC specifications          | Unit | Value |

|-----------------------------|------|-------|

| Cell capacitance $(C_{sm})$ | mF   | 5     |

| Arm inductance $(L_{arm})$  | mH   | 10    |

| Arm resistance $(R_{arm})$  | Ω    | 0.1   |

| Number of SMs per arm (N)   | =    | 8     |

| Carrier frequency $(f_c)$   | Hz   | 600   |

| Sampling frequency $(f_s)$  | kHz  | 20    |

## 6. Results

In this Section, the results for the two case studies are presented and the operation dynamics are explained.

**6.1. Case study (i).** In this case, a single MMC station, controlling the  $v_{\rm DC}$  at its DC output, is subjected to a DC fault at a distance of 1 m. The short cable segment is used to introduce

a small capacitance and a small impedance between the converter and the fault point. Table 3 presents the course of events.

Table 3

Case study (i) timeline

| Time (s)        | 0.1   | 0.2 | 0.4  |

|-----------------|-------|-----|------|

| DC Fault        | Apply | X   | X    |

| $q_{ac}^*$ (pu) | 0     | 0.5 | -0.8 |

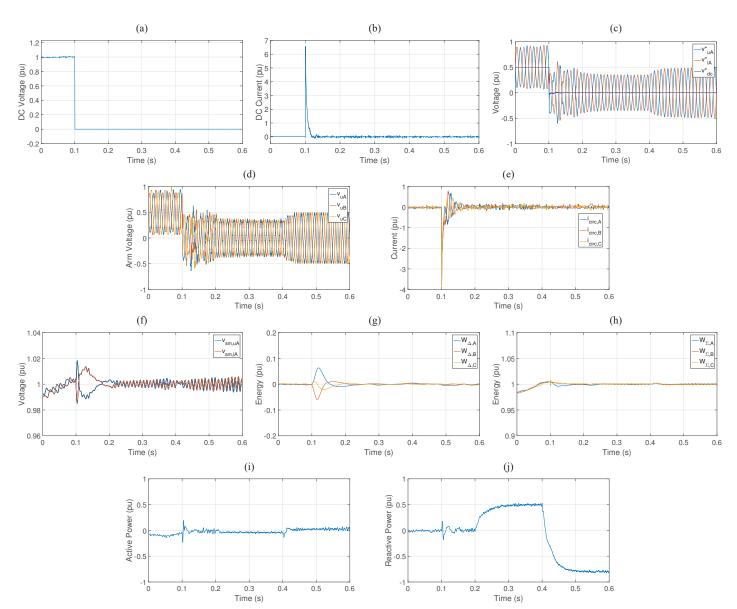

As expected, once the DC fault occurs, the  $v_{\rm DC}$  drops almost immediately to zero as presented in Fig. 9(a). The high DC current is a result of the discharge of the DC cable capacitance through the fault and the voltage gradient between the equivalent leg voltage of the MMC and the fault point voltage. The

fault current initially circulates through the legs of the MMC (see Fig. 9(e)) and the AC grid does not experience high currents. As soon as the overcurrent threshold for the DC fault detection is surpassed, in this case 0.7 ms after the fault occurrence, the control changes as described in Section 3 and the DC fault current reaches its peak and stops increasing. Consequently, the  $i_{\rm DC}$  is actively controlled below 1 pu within 8 ms and drops to zero within 19 ms, as shown in Fig. 9(b), while the circulating current does not experience a DC offset during the fault as depicted in Fig. 9(e).

When the fault is detected, the outer  $V_{\rm DC}$  control strategy changes to  $W_{\rm conv}$  control and the  $v_{\rm DC}^*$  reference for the modulation is given by the  $i_{\rm DC}$  controller as shown in Fig. 9(c). The upper and lower arm voltages of each phase  $(v_{\rm uj}$  and  $v_{\rm lj})$  follow the references as presented in Fig. 9(d) for phase A, exhibiting a fast response to the control change. An imbalance in the leg energies

Fig. 9. Fault operation – Case study (i): (a) – DC voltage, (b) – Positive pole DC current, (c) – Voltage reference for modulation, (d) – Upper arm voltage for phase A, (e) – Circulating current, (f) – Upper and lower arm capacitor voltages for phase A, (g) – Energy difference between phase arms of MMC1, (h) – Leg energies, (i) – AC active power, (j) – AC reactive power

appears initially for 0.1 s after the fault and the effect of the CMV voltage reference on the  $v_{ui}$  and  $v_{li}$  is evident, while trying to restore the balance. As shown in Fig. 9(h), the leg energies manage to remain balanced during the fault, while the difference of the arm energies, presented in Fig. 9(g), is kept at zero after the first transient. Moreover, the submodule capacitor voltages remain balanced at 1 pu during the fault with only a short transient of  $\pm 2\%$  at the moment of the fault. Therefore, the MMC station is able to operate as a FB-DS STATCOM. To test this operation, we apply steps in the reactive power exchange with the AC grid. It can be concluded that despite the DC fault, the DC side dynamics do not affect the AC side and therefore, the  $p_{ac}$  is kept at zero as shown in Fig. 9(i), while Fig. 9(j) shows that the reactive power reference  $(q_{ac}^*)$  is followed accurately. It has to be noted that at the moment of the fault the effect on the active and reactive power of the AC side is very small. This happens because the fault detection is fast and thus, the control mode change takes place before high transients are experienced on the AC side.

**6.2.** Case study (ii): In this case study, the response of three stations to a DC fault, their STATCOM operation during the fault and the return to normal operation post-fault are evaluated within the MTDC grid as shown in Fig. 8. The timeline of Case study (ii) is presented in Table 4.

Table 4

Case study (ii) timeline

| Time (s)             | 0.1   | 0.2 | 0.4  | 0.7   |

|----------------------|-------|-----|------|-------|

| DC Fault             | Apply | X   | X    | Clear |

| MMC1 $q_{ac}^*$ (pu) | 0     | 0.7 | -0.6 | -0.6  |

| MMC2 $q_{ac}^*$ (pu) | 0     | 0.3 | -0.4 | -0.4  |

| MMC3 $q_{ac}^*$ (pu) | 0     | 0.5 | -0.8 | -0.8  |

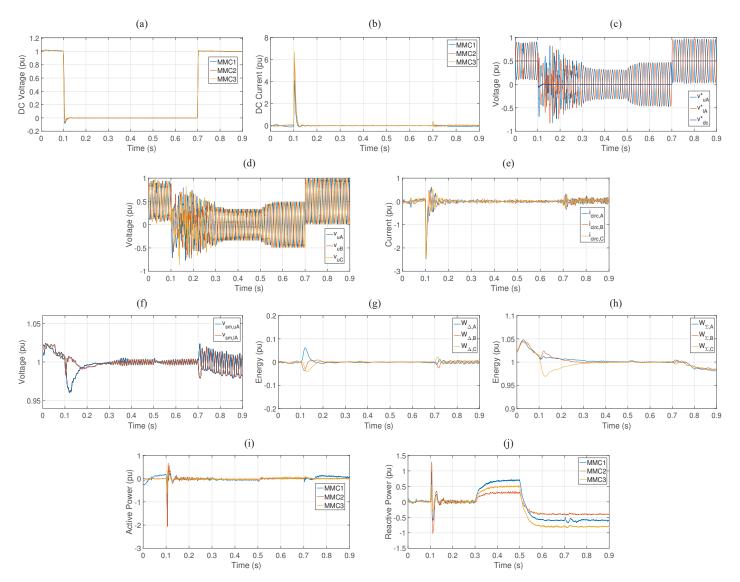

In this case, the  $v_{\rm DC}$  at the DC output of each MMC drops slower than in case (i) because of the long HVDC lines, as shown in Fig. 10(a). The travel time of the fault transient to

Fig. 10. Fault operation – Case study (ii): (a) – DC voltage, (b) – Positive pole DC current, (c) – Voltage reference for modulation at MMC1, (d) – Upper arm voltage for phase A of MMC1, (e) – Circulating current of MMC1, (f) – Upper and lower arm capacitor voltages for phase A of MMC1, (g) – Energy difference between phase arms of MMC1, (h) – Leg energies of MMC1, (i) – AC active power, (j) – AC reactive power

the line ends depends on the LC parameters of the cables. Because of the DC cables, the fault detection occurs slower (e.g.  $1.8~\mathrm{ms}$  for MMC1 compared to  $0.7~\mathrm{ms}$  in Case study (i)) and thus, the capacitors of the inserted submodules have more time than in case (i) to get discharged through the fault as shown in Fig. 10(f). Moreover, the cable inductance affects the rate of rise of the fault current, while the added series RL impedance affects the peak fault current experienced at the DC output of each station. The DC current as measured at each MMC station is depicted in Fig. 10(b). The highest  $i_{DC}$  peak is experienced at MMC3 which is located closer to the fault and for this reason the  $i_{DC}$  takes more time to drop to zero. The  $i_{DC}$  drops below 1 pu within 13 ms and to zero within 22 ms for all terminals, depending on the distance from the fault point.

The peak of the circulating current occurs at the same time as the peak of the DC current (3.3 ms after the fault for MMC1) (see Fig. 10(e)). However, the AC side is not affected yet by the DC fault, as the fault current only circulates through the legs of the MMC. Once the DC fault is detected the control changes to STATCOM operation. The reference for the upper and lower arms of phase A of MMC1 as well as the upper arm voltages of MMC1 are presented in Fig. 10(c) and (d) respectively. The transient effect of the CMV voltage reference on the  $v_{uj}$  and  $v_{lj}$ is evident for 0.2 s after the fault occurrence in this case study, while the converter is trying to balance the leg energies. While the outer energy controller makes sure that the MMC energy remains constant, the arm and leg energy balancing controllers also make sure to keep the difference of the arm energies at zero and the leg energies at the nominal level as shown in Fig. 10(g) and (h) respectively.

Because of the initial discharge of the capacitors, more current is necessary to increase the submodules energy to the nominal level and thus, a peak in the  $p_{ac}$  is observed at 5.5 ms after the fault (see Fig. 10(i)). During the DC fault, the  $p_{ac}$  is maintained at zero in all MMC stations in Fig. 10(i), while the  $q_{ac}^*$  (both positive and negative) is followed accurately in Fig. 10(j). Based on this result, it can be concluded that the full-bridge MMC is able to operate as STATCOM during a DC fault without the need to isolate the faulty line.

Assuming that the DC fault is cleared at 0.7 s, a control signal is sent to the stations and the  $v_{\rm DC}$  is ramped up to its nominal level using a rate of rise limiter of the DC voltage reference (in this case study it was set at 0.5 pu/1 ms). In this way, overshoot of voltage is avoided, while at the same time the inrush DC current to the discharged DC cables is kept low. Once  $v_{\rm DC}$  is restored, the stations return to their pre-fault control structure (MMC1 uses  $V_{\rm DC}$  control, while MMC2 and MMC3 control  $P_{\rm ac}$ ). The smooth transition to the new operating level is made sure by resetting the PI controllers.

The  $p_{\rm ac}$  and the  $i_{\rm DC}$  of MMC1 slightly increase post-fault, as it is the only station that is not actively controlling its  $p_{\rm ac}$  and therefore, it is responsible to re-energize the DC cables post-fault and maintain the grid at its nominal voltage level. It has to be highlighted that each station is able to keep the control of the  $q_{\rm ac}$  post-fault at the reference level it was operating during the DC fault. As a result, the reactive power support of the respective AC grid is not affected by the restoration process.

Bull. Pol. Ac.: Tech. 65(5) 2017

## 7. Conclusions

This paper presented a control structure to enhance the DC fault ride-through capability of a full-bridge MMC, while operating as a STATCOM towards the respective AC grid, without the need to isolate the faulty line. During a DC fault the outer controllers change their control objective trying to maintain the MMC energy constant at nominal level. To achieve that the AC and MMC internal dynamics are also decoupled from the DC side using a controller to drive the DC current to zero.

The effectiveness of the proposed methodology was demonstrated using two case studies. In the first case, an MMC station was tested with a pole-to-pole DC fault at its DC output. Despite the severe fault and the high initial circulating currents, the MMC maintained controllability and was able to bring the DC fault current below the nominal 1 pu limit within 8 ms, while the AC side did not experience high transient currents. In the second case, more attention was paid on the HVDC grid response to the fault and on the post-fault grid recovery. In this case the fault detection at each station depended on the distance from the fault point. As a result, a network-based DC fault detection method would be recommended to detect the fault faster. The results showed that all stations were able to operate as STATCOM providing support to their respective AC grid, while they maintained their internal energy balance and the DC current was controlled to zero. Post-fault the DC voltage was ramped up to its nominal level within 2 ms using the DC current controller with a rate of rise limiter to ensure the smooth re-energization of the DC lines and to avoid high inrush DC currents and DC voltage overshoot. Overall, the main challenge is the control response at the transition moments between STATCOM and inverter/ rectifier operation, i.e. when the fault is detected and when it is cleared. At these moments, the control of the MMC stations should be coordinated to maintain grid stability.

### REFERENCES

- [1] E. Kontos, R.T. Pinto, S. Rodrigues, and P. Bauer, "Impact of HVDC transmission system topology on multiterminal DC network faults," *IEEE Transactions on Power Delivery* 30 (2), 844–852, (2015).

- [2] S. Ademi, D. Tzelepis, A. Dysko, S. Subramanian, and H. Ha, "Fault current characterisation in VSC-based HVDC systems," in 13th International Conference on Development in Power System Protection 2016 (DPSP), March 2016, 1–7 (2016).

- [3] M.K. Bucher and C.M. Franck, "Comparison of fault currents in multiterminal HVDC grids with different grounding schemes," in 2014 IEEE PES General Meeting | Conference Exposition, July 2014, 1–5 (2014).

- [4] M.K. Bucher and C.M. Franck, "Fault current interruption in multiterminal HVDC networks," *IEEE Transactions on Power Delivery* 31 (1), 87–95, (2016).

- [5] D. Peftitsis, A. Jehle, and J. Biela, "Design considerations and performance evaluation of hybrid DC circuit breakers for HVDC grids," in 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), Sept 2016, 1–11 (2016).

- [6] A. Zapico, M. Lopez, A. Rodriguez, and F. Briz, "Fault tolerant cell design for MMC-based multiport power converters," in 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Sept 2016, 1–8 (2016).

- [7] J. Zhang and C. Zhao, "The research of SM topology with DC fault tolerance in MMC-HVDC," *IEEE Transactions on Power Delivery* 30 (3), 1561–1568, (2015).

- [8] E. Kontos, R.T. Pinto, and P. Bauer, "Fast DC fault recovery technique for H-bridge MMC-based HVDC networks," in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Sept 2015, 3351–3358 (2015).

- [9] R. Zeng, L. Xu, L. Yao, and D.J. Morrow, "Precharging and DC fault ride-through of hybrid MMC-based HVDC systems," *IEEE Transactions on Power Delivery* 30 (3), 1298–1306, (2015).

- [10] S. Cui, S. Kim, J.J. Jung, and S.K. Sul, "Principle, control and comparison of modular multilevel converters (MMCs) with DC short circuit fault ride-through capability," in 2014 IEEE Applied Power Electronics Conference and Exposition – APEC 2014, March 2014, 610–616 (2014).

- [11] E. Kontos, R.T. Pinto, and P. Bauer, "Providing DC fault ridethrough capability to H-bridge MMC-based HVDC networks," in 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), June 2015, 1542–1551 (2015).

- [12] X. Yu, Y. Wei, and Q. Jiang, "STATCOM Operation Scheme of the CDSM-MMC During a Pole-to-Pole DC Fault," *IEEE Transactions on Power Delivery* 31 (3, pp. 1150–1159, June 2016.

- [13] G.P. Adam and I.E. Davidson, "Robust and generic control of full-bridge modular multilevel converter high-voltage DC transmission systems," *IEEE Transactions on Power Delivery* 30 (6, pp. 2468–2476, Dec 2015.

- [14] X. Yu, Y. Wei, and Q. Jiang, "STATCOM Operation Scheme of the CDSM-MMC During a Pole-to-Pole DC Fault," *IEEE Transactions on Power Delivery* 31 (3, pp. 1150–1159, June 2016.

- [15] G. Tsolaridis, E. Kontos, S.K. Chaudhary, P. Bauer, and R. Teodorescu, "Internal Balance during Low-Voltage-Ride-Through of the Modular Multilevel Converter STATCOM," *Energies* 10 (7, 2017.

- [16] G. Tsolaridis, E. Kontos, H. Parikh, R.M. Sanchez-Loeches, R. Teodorescu, and S.K. Chaudhary, "Control of a Modular Multilevel Converter STATCOM under internal and external unbalances," in *IECON 2016 – 42nd Annual Conference of the IEEE Industrial Electronics Society*, Oct 2016, pp. 6494–6499.

- [17] A. Dekka, B. Wu, V. Yaramasu, and N.R. Zargari, "Model Predictive Control With Common-Mode Voltage Injection for Modular Multilevel Converter," *IEEE Transactions on Power Electronics* 32 (3, pp. 1767–1778, March 2017.