#### **Aalborg Universitet**

#### **Multidisciplinary Modelling Tools for Power Electronic Circuits**

with Focus on High Power Modules Bahman, Amir Sajjad

Publication date: 2015

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Bahman, A. S. (2015). *Multidisciplinary Modelling Tools for Power Electronic Circuits: with Focus on High Power Modules*. Department of Energy Technology, Aalborg University.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Multidisciplinary Modelling Tools for Power Electronic Circuits

with Focus on High Power Modules

by

Amir Sajjad Bahman

Dissertation submitted to Faculty of Engineering, Science, and Medicine at Aalborg University

Center of Reliable Power Electronics (CORPE)

Department of Energy Technology

Aalborg University, Denmark

October 2015

Thesis submitted: October 5, 2015

PhD supervisor: Prof. FREDE BLAABJERG,

Aalborg University

Assistant PhD supervisor: Prof. FRANCESCO IANNUZZO,

Assistant Prof. KE MA, Aalborg University

PhD committee: Prof. FABRIZIO MARIGNETTI, University of Cassino

and Southern Lazio

Prof. SURESH PERINPANAYAGAM, Cranfield

University

Prof. CLAUS LETH BAK, Aalborg University

PhD Series: Faculty of Engineering, Science, and Medicine, Aalborg

University

ISBN: 978-87-92846-70-9

Published by:

Aalborg University Press Skjernvej 4A, 2nd floor DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright by Amir Sajjad Bahman

Printed in Denmark by Rosendahls, 2015

# **Copyright Statements**

Thesis Title: Multidisciplinary Modelling Tools for Power Electronic Circuits

(With Focus on High Power Modules)

Name of the PhD student: Amir Sajjad Bahman

Name of supervisor: Prof. Frede Blaabjerg

Name of co-supervisors: Assistant Prof. Ke Ma and Prof. Francesco Iannuzzo

List of Publications: Listed in § 1.4

This present report combined with the above listed scientific papers has been submitted for assessment in partial fulfilment of the PhD degree. The scientific papers are not included in this version due to copyright issues. Detailed publication information is provided above and the interested reader is referred to the original published papers. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science, Aalborg University.

#### CV

Amir Sajjad Bahman received the B.Sc. degree from Iran University of Technology, Tehran, Iran, in 2008, and the M.Sc. degree from Chalmers University of Technology, Gothenburg, Sweden, in 2011, both in electrical engineering. He joined the Center of Reliable Power Electronics (CORPE) at Aalborg University in 2012. He is currently pursuing toward the Ph.D. degree in the Department of Energy Technology, Aalborg University. His current research interests include reliability, thermal management, power module packaging, and power electronics applications in renewable energy systems.

### **Preface**

This thesis is a summary of the PhD project entitled "Multidisciplinary Modelling Tools for Power Electronic Circuits (With Focus on High Power Modules)". This work has been made possible by the Center of Reliable Power Electronics (CORPE) at the Department of Energy Technology, Aalborg University, Denmark. Acknowledgements are given to the above-mentioned institution that financially supported me through my PhD study.

This research project was done under supervision of Prof. Frede Blaabjerg, Prof. Francesco Iannuzzo, and Assistant Prof. Ke Ma from the Department of Energy Technology in Aalborg University. First and foremost, I would like to express my deepest gratitude to my supervisor, Prof. Frede Blaabjerg, for his for setting me on this journey through such a wide range of material and his leadership throughout the project. Dr. Ke Ma has mentored me step by step through several meetings helping to dispel uncertainty and promote understanding. Prof. Francesco Iannuzzo also mentored me throughout this project and spent many hours working out problems with me very friendly. Prof. Poh Chiang Loh also supervised me throughout the beginning of this project learning the control strategies for power electronic circuits. Dr. Huai Wang also mentored me from the beginning of this project to get insight into design for reliability approach. Furthermore, thanks to Pramod Ghimire for significant assistance with experimental works and discussions on numerous topics.

Also, I place on record, my gratitude to Prof. Alan Mantooth for his kindness and professional supervision during my study abroad at the Mixed Signal Computer Aided Design (MSCAD) Lab, University of Arkansas, AR, USA and also to my friends who I met at the University of Arkansas for their tremendous assistance.

The industry advisory board of this institute has provided me many insights into what is truly needed to improve the engineering of power electronics. Klaus Olesen at Danfoss Silicon Power GmbH provided key information on the thermal design process of power modules and many interesting discussions during my internship. Additionally, I would like to thank specialists at ANSYS, Inc., Jens Uwe Friemann and Vinayak Kamat, for significant assistance with solving problems in FEM simulations.

In particular, I take this opportunity to thank staff at the Department of Energy Technology, Aalborg University, Denmark, for their assistance and advices to smooth my PhD study in Aalborg, especially Casper Jørgensen, Ann Louise Henriksen, Corina Busk Gregersen, Mette Skov Jensen and Tina Larsen. I would also like thank my friends Qobad Shafiee, Pooya Davari, Hamid Soltani, Reza Ahmadi and Alireza Rezania. I would like to thank everyone mentioned above and anyone else who has helped me through this process.

Finally, I wish to express my most sincere gratitude to my family for their exceptional love, support, concern, understanding and encouragement through my life.

Niels Bohr, a Danish physicist, ever said, "Every great and deep difficulty bears in itself its own solution. It forces us to change our thinking in order to find it". After this three-year Ph.D. study, I found out that most of the important things in the world have been accomplished by people who have kept on trying when there seemed to be no hope at all. I do my best to be as brave as to make a wonderful life with what I have learnt from all of you. Wish the best for all of us.

Amir Sajjad Bahman

October 2015, Aalborg

#### **Abstract**

This thesis presents multidisciplinary modelling techniques in a Design For Reliability (DFR) approach for power electronic circuits. With increasing penetration of renewable energy systems, the demand for reliable power conversion systems is becoming critical. Since a large part of electricity is processed through power electronics, highly efficient, sustainable, reliable and cost-effective power electronic devices are needed. Reliability of a product is defined as the ability to perform within its predefined functions under given conditions in a specific time. Because power electronic devices are applied in a wide range of loads and frequencies, the reliability of a power device may face to challenges to perform within the product specification in different application where high electrical/thermal stresses are experienced. Moreover, with the integration of power electronic devices in a compact package, e.g. power module, DFR approach meets trade-offs in electrical, thermal and mechanical design of the device.

Today, virtual prototyping of power electronic circuits using advanced simulation tools is becoming attractive due to cost/time saving in building potential designs. With simulations, the designer can test new concepts and optimize design layouts before the physical components and systems are built up. Moreover, if a failure occurs, there will be no destruction, but valuable data is obtained to modify and to optimize the product as part of an iterative design process. A key requirement to this process is to quickly generate compact and simple models describing the electrical and thermal performance of a potential design. Even though, numerical tools based on Finite Element Analysis (FEA) are powerful in studying the physical behavior of power devices, they are time consuming and demand for expensive computation facilities in DFR approach. Therefore, in this thesis focus is placed on the generation of accurate, simple and generic models to study and assess thermal and electrical behavior of power electronic circuits (especially power modules).

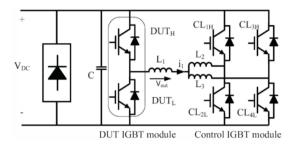

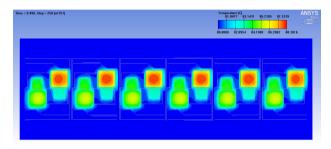

In this thesis, different power electronic converter topologies and control strategies are investigated with focus on reducing the number of active components and increasing the efficiency of converter. Several power converter topologies are discussed and compared with alternative solutions from power dissipation and efficiency point of view. By understanding the methods gain to identify power dissipation in the power modules, FEM simulations are utilized to investigate thermal behavior of power module in normal (e.g. power cycling) as well as abnormal (e.g. short-circuit) conditions. By knowing the challenges and shortcomings in FEM simulation in reliability assessment of power modules, a three-dimensional lumped thermal network is proposed to be used for fast, accurate and detailed temperature estimation of power module in dynamic operation and different boundary conditions.

Since an important issue in the reliability of power electronics is the thermal management of power devices, efficient cooling system design will be aimed in the following. Due to better performance of direct liquid cooling systems compared to forced air cooling systems, they will be utilized to cool down the power module. A design tool is presented with a user friendly

environment to be used for optimization of cooling system layout with respect to thermal resistance and pressure drop reductions.

Finally extraction of electrical parasitics in the multi-chip power modules will be investigated. As the switching frequency of power devices increases, the size of passive components are reduced considerably that leads to increase of power density and cost reduction. However, electrical parasitics become more challenging with increasing the switching frequency and paralleled chips in the integrated and denser packages. Therefore, electrical parasitic models are analyzed based on micro-strip structures and partial inductances to predict parasitic parameters according to varied layouts.

Some of the presented models in this thesis are verified by FEM simulations and experimental results in real world applications. The power losses, thermal and electrical parasitic models are generic and valid to be used in circuit simulators or any programing software. These models are important building blocks for the reliable design process or performance assessment of power electronic circuits. The models can save time and cost in power electronics packaging and power converter to evaluate new designs and to assess products in normal, abnormal, and harsh environments.

#### **Dansk Abstrakt**

I denne afhandling præsenteres en række multi-disciplinære modelleringsteknikker indenfor "Design For Reliability (DFR)" – design som er målrettet med pålidelighed indenfor effektelektronik. Med en stigende vækst i udnyttelsen af vedvarende energi følger også et øget behov for pålidelige effektomformnings-systemer. Da effektelektronik er involveret i størstedelen omformningen af elektrisk energi er der specielt behov for effektelektronikteknologier, der har høj effektivitet, er bæredygtige, pålidelige og billige. Et givet produkts pålidelighed defineres ved dets evne til at opretholde sin funktion indenfor dets arbejdsområde i et givet tidsrum under veldefinerede betingelser. Da effektelektronik anvendes indenfor en række varierende belastninger, kan dette give udfordringer, hvis produktet anvendes i andre områder, hvor det udsættes for en stor elektrisk og termiske belastning. Derudover skal det tages i betragtning, at hvis effektelektroniske komponenter integreres i kompakte enheder, såsom i effektmoduler, kan man i DFR tilgangen tage nødvendige afvejninger imellem elektrisk, termisk, og mekanisk design-hensyn.

Brugen af virtuelle prototyper til effektelektroniske kredsløb ved hjælp af avancerede simulerings værktøjer er attraktivt, da det er en tids- og omkostningseffektiv måde at udvikle nye, potentielle designs på. Ved hjælp af simuleringer kan designeren teste nye koncepter og optimere design layouts inden de virkelige systemer realiseres. Endvidere, hvis et design skulle vise sig at lede til fejlhændelser, er der ingen reelle destruktive hændelser i virtuelle prototyper, men derimod mulighed for at få vigtig information, der kan bruges til yderligere justeringer og optimeringer i en iterativ design proces. I den forbindelse er det afgørende at kunne udvikle simple og kompakte modeller, der kan beskrive den elektriske og termiske studere opførslen af et givet design. Selvom numeriske metoder såsom Finite Element Method (FEM) er særdeles velegnet til at undersøge fysikken i effektelektronik, så er de tidskrævende og kræver omfattende computerberegninger, når de skal anvendes til DFR. Derfor er der i denne afhandling fokus på at udvikle nøjagtige, simple og bredt anvendelige modeller, der kan anvendes til at undersøge og vurdere den termiske og elektriske opførsel i effektelektroniske kredsløb (specielt høj-effekt moduler)

I afhandlingen undersøgelses forskellige effektelektroniske kredsløbs topologier, hvor der fokuseres på at reducere antallet af aktive komponenter og øge effektiviteten af topologien. Adskillige effektelektroniske omformer topologier diskuteres og sammenlignes med alternative løsninger i forhold til energitab og effektivitet. Baseret på erfaringerne med udfordringerne og begrænsningerne, som er forbundet med FEM simuleringer til at estimere pålidelighed, foreslås en model, som er baseret på et 3-dimensionelt simpelt termisk netværk, der kan anvendes til en hurtig, nøjagtig og detaljeret estimering af temperature i effekt moduler under forskellige testbetingelser. Da køling er specielt vigtigt for effektelektronik, behandles dernæst design af effektive kølesystemer. Køling ved hjælp af direkte kontakt med kølevæsker er mere effektivt end luftbaserede kølesystemer og de anvendes i til afhandlingen køling af effektmoduler.

Som det sidste emne præsenteres undersøgelser af parasitiske komponenter i effekt moduler med adskillige effektelektroniske komponenter. Ved at øge switch-frekvensen, kan størrelsen af de passive komponenter i omformerne reduceres, hvilket muliggør en øget effekttæthed og en lavere pris. Men dette leder samtidigt til en øget udfordring for de kompakte kredsløb med mange komponenter i forhold til de parasitiske komponenter, der bliver betydningsfulde ved højere frekvenser. For at imødegå dette er der udviklet modeller der ud fra micro-strip strukturerer kan bestemme de parasitiske parametre i forskellige layouts og som derved kan optimeres i forhold til dette hensyn.

En række af de modeller, der er præsenteret i afhandlingen, er blevet testet og verificeret i forhold til numeriske FEM simuleringer og eksperimentelle resultater udviklede. Modeller for energitab, termiske køling og de parasitiske elektriske parametre er bredt anvendelige og kan anvendes i kredsløbssimulerings-programmer eller andre programmeringsværktøjer. Modellerne er vigtige elementer i designprocesser målrettet med bedre pålidelighed eller forøgelse af virkningsgraden i effektelektronik. De kan spare tid og penge i udviklingen af nye designs til fremstilling af effektelektroniske enheder og kan bruges til at vurdere produkterne under typiske, atypiske og sågar ekstreme anvendelser

# **Table of Contents**

| Preface                                                           | V      |

|-------------------------------------------------------------------|--------|

| Abstract                                                          | vii    |

| Dansk Abstrakt                                                    | ix     |

| Table of Contents                                                 | xi     |

| Chapter 1 Introduction                                            | 1      |

| 1.1 Introduction and background                                   | 1      |

| 1.2 Hypothesis and objectives                                     | 9      |

| 1.3 Thesis outline                                                | 9      |

| 1.4 List of publications                                          | 11     |

| References                                                        | 12     |

| Chapter 2 Power module applications in high power converte        | ers 15 |

| 2.1 Application of power modules in multi-level inverters         | 15     |

| 2.2 Application of power modules in reduced switch converters     | 29     |

| 2.3 Conclusions                                                   | 40     |

| References                                                        | 41     |

| Chapter 3 Thermal modelling of high power IGBT modules .          | 43     |

| 3.1 Structure of IGBT module and conditions for analysis          | 43     |

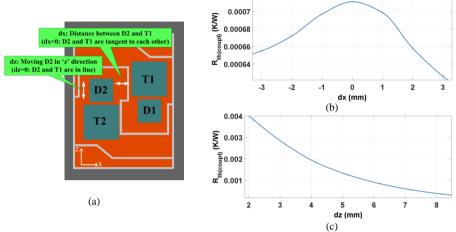

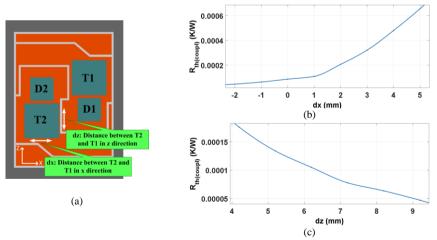

| 3.2 Thermal coupling effects                                      | 45     |

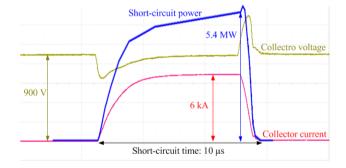

| 3.3 FEM modelling of power modules in abnormal operation          | 52     |

| 3.4 Conclusions                                                   | 59     |

| References                                                        | 59     |

| Chapter 4 3D thermal network for high power IGBT module           | s 61   |

| 4.1 Proposed structure of 3D thermal model                        | 63     |

| 4.2 Extraction of 3D thermal network                              | 65     |

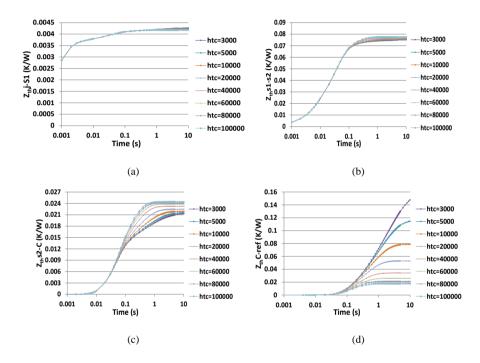

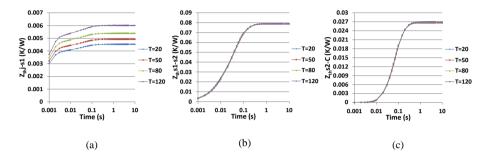

| 4.3 Characterization of boundary conditions in 3D thermal network | 69     |

|                                                                   |        |

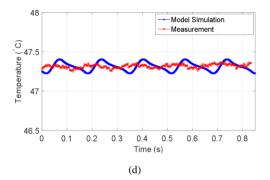

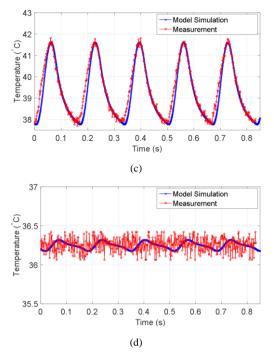

| 4.4 3D thermal model verifications                                                                      | 75                |

|---------------------------------------------------------------------------------------------------------|-------------------|

| 4.5 Conclusions                                                                                         | 88                |

| References                                                                                              | 89                |

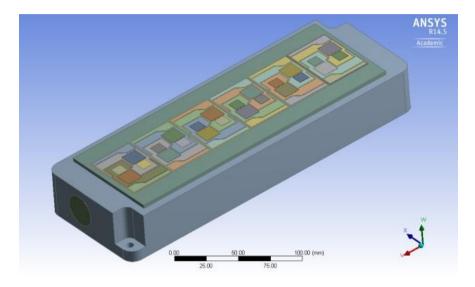

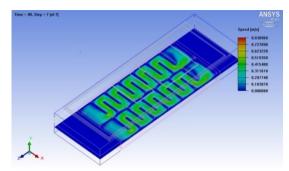

| Chapter 5 Design of cooling system for high power IGBT                                                  | modules 91        |

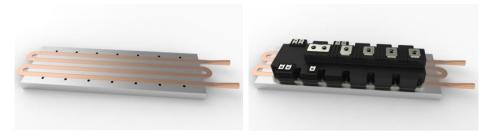

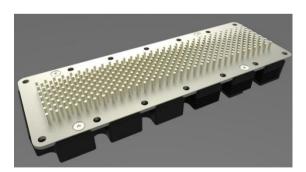

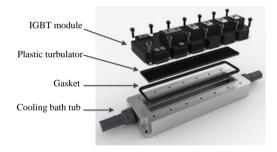

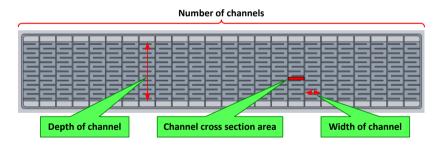

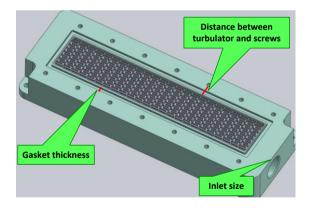

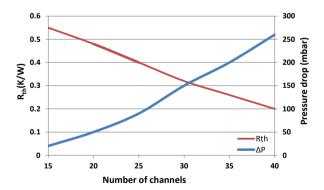

| 5.1 ShowerPower <sup>®</sup> cooling system                                                             | 93                |

| 5.2 Considerations in the design of cooling system                                                      | 95                |

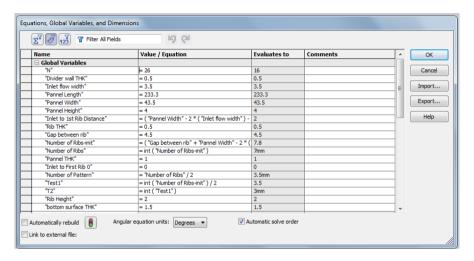

| 5.3 Optimization design tool for ShowerPower® cooling system                                            | n 96              |

| 5.4 CFD verification                                                                                    | 99                |

| 5.5 Conclusions                                                                                         | 101               |

| References                                                                                              | 101               |

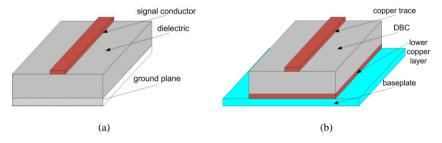

| Chapter 6 Electrical parasitics modelling of power modu                                                 | les103            |

| 6.1 Electrical parasitics in power modules                                                              | 103               |

| 6.2 Extraction of Electrical parasitics                                                                 | 104               |

| 0.2 Extraction of Electrical parasities                                                                 |                   |

| 6.3 Reduced parasitics design example                                                                   | 108               |

|                                                                                                         |                   |

| 6.3 Reduced parasitics design example                                                                   | 112               |

| 6.3 Reduced parasitics design example                                                                   | 112<br>114        |

| 6.3 Reduced parasitics design example 6.4 Conclusions References                                        | 112<br>114<br>115 |

| 6.3 Reduced parasitics design example 6.4 Conclusions References Chapter 7 Conclusions and future works | 112<br>114<br>115 |

#### Introduction

This chapter presents the background, motivation and organization of the work presented in this thesis. The state of the art approaches in reliable design of power electronics are discussed and future trends and requirements for design tools will be explained. Finally, the objectives and structure of this thesis are outlined.

#### 1.1 Introduction and background

#### 1.1.1 Reliability of power electronics

The increasing demand for electrical energy, exhausting fossil energy reserves and the increase in energy prices have necessitated the use of current energy resources in a more efficient way. Power electronic converters are finding increased use as the essential equipment to convert and control electrical power in the wide power range from milliwatts to gigawatts with the help of power semiconductor devices [1].

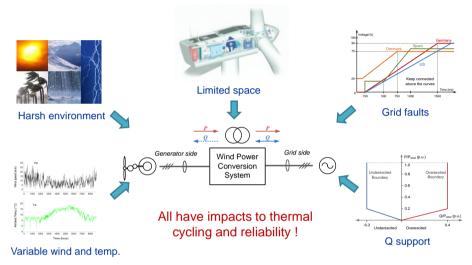

Today, more than 70% of all electricity is processed through power electronics; therefore, highly efficient, sustainable, reliable and cost-effective power electronic systems are needed to reduce the waste of energy, to improve power quality and also to reduce costs in power generation, power transmission/distribution and end-user application [2]. As the power densities are increasing, the challenges for the reliability of power electronic systems have been more significant. For example, in one project [3], 290 cases of failures of wind turbines produced by different manufacturers were studied. In this study, 31,500 downtime events showed the second most significant contribution of 12% was caused by power electronics.

Thermal management, exposure to moisture, vibration, dust, chemicals, high voltage and deformation caused by temperature are important parameters since power electronic converters are often applied in harsh environments. The mission profiles for the converters exposed to these stressors should be known and taken into account during the design process to predict the lifetime of the converter. Today industries may use standard handbook calculation for each component in order to design the power

electronic system and with a low risk of failure rating, which may overrate the system in a costly way. However, standard handbooks do not show the root cause of failures in the optimization process of the products [4]-[9]. To solve these problems, design tools based on physics of failure methods should be developed in order to promote the industries enhancing the reliability of their power electronics converters.

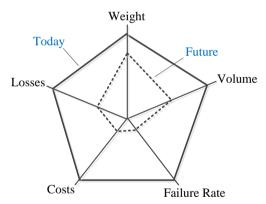

In recent years, the reliability of power electronic systems has attracted more attention. The development of power electronics demands higher efficiency, stability and reliability. On the other hand, it demands also less weight, volume and cost (Fig. 1.1). In applications such as smart grid or renewable energy systems, the reliability of power electronic systems is very important, since the power system is always in operation and the power electronic converter plays a vital rule to produce the power to the grid. Moreover, in application such as powertrains, traction systems or other harsh environments, the life time of power electronic devices and circuits is a major performance factor considered in the design process [5].

Fig. 1.1. Important performance indexes of power electronic systems and future design requirements .

#### 1.1.2 Concept of design for reliability

Today, power electronics is experiencing the development of reliability from classic handbook-based reliability prediction and qualification testing to a systematical Design for Reliability (DFR) approach [10]. The related research works have been directed in analyzing various reliability aspects [11]-[15]. In order to analyze the reliability of power electronic systems, mathematical models to predict reliability are needed. Many

efforts have been directed to develop mathematical and simulation models at component-level for studying electrical, electro-thermal and thermo-mechanical behaviors [16], [17]. Besides, many significant methodologies have been proposed to develop system-level models in order to achieve a predictable lifetime models for power electronic systems [18]-[19].

However, the design tools used for improving the reliability of power electronic systems are not at an acceptable level for the following reasons [4]:

- I. The DFR approach is not considered in state-of-the-art cases. Power electronic systems have a wide range of specific failure mechanisms as well as complicated mission profiles, and the design tools are not customized for power electronics.

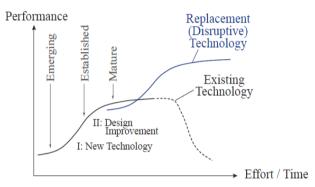

- II. The bathtub curve [4], which shows the failure rate of a device or system as a function of time, divides the life time of a device or system into three periods: Burn-in, Useful Life, and Wear-out (Fig. 1.2). The limitations of the curves are that: 1) the assumption of constant failure rate during useful life is not valid for many application cases, and 2) the wear out of power electronic components could start since the beginning of the operation.

Fig. 1.2. Typical failure rate curve as a function of time (bathtub curve).

III. Most industries use models based on reliability handbooks to design their products and predict the failure rates in power electronic systems. However, handbooks do not consider temperature cycling, combined environments, failure rate changes with material and the quality or technology, which is used in the product. Moreover, the models addressed in handbooks do not indicate the root causes of a failure to improve the reliability of the device or the system.

When a product is used, the performance of the product will wear out over time (Fig. 1.3) [4]. Only the performance improvement will be obtained by assigning optimal values to the parameters in the design stage. In other words, the reliability of a system can be enhanced by comprehensive multi-objective optimization of the system [5]. A diagram for optimization process in a power electronic system design is shown in (Fig. 1.4).

Fig. 1.3. Product performance as a function of time.

#### 1.1.3 Design tools for power electronics

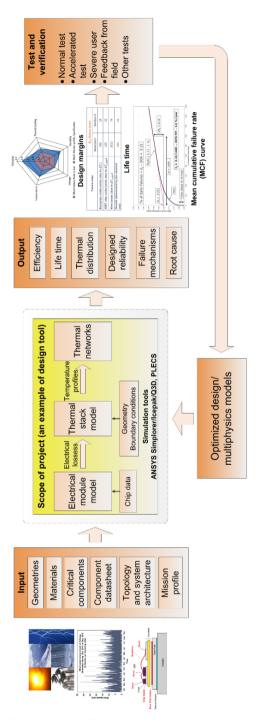

In order to optimize the system reliability of a power electronic circuit, first a comprehensive mathematical model must be established. This model can be a design tool, which includes thermal, electrical and mechanical models of the system. This tool could be based on component and circuit equations, on numerical simulations or both of them. Equation-based models can provide fast analysis of the system. These equation-based models are easy to use and time-efficient, but the accuracy of the final result is highly dependent on the accuracy of the component-level models, which is a great challenge. This is particularly true when using new power electronic devices, topologies or e.g. modulation techniques. Furthermore, simulation-based models are completely flexible, but may need strong computational efforts.

Fig. 1.4. A diagram illustrating a reliability-driven design process of a power electronic converter.

The behavior of the power electronic system could be predicted by applying the design tool. This tool can include junction temperature of components, thermomechanical stresses, and electrical parasitics in the circuit as well as the life-time of the power electronic circuit. In addition, this tool enables the reduction in time and cost of the system development, since the design tool can be implemented in software models instead of hardware. Besides, the failure mechanisms caused by component temperatures and mechanical stresses could be identified in the early design stage for various mission profiles such as overvoltage, overload, short-circuit, wind speed, solar irradiance, etc. without building complicated and expensive prototypes for the applications such as renewable energy systems, hybrid or electric vehicles.

Furthermore, using a design tool enables the design engineers to study the effect of parameter variations on the whole converter system. In this way, the variation could be held by multiple objectives, e.g. increase the efficiency together with power density in the state of keeping the costs as low as possible. Moreover, different converter topologies could be compared and the performance limitations of various topologies identified. The circuit models developed in the design tools have to be accurate and reliable for a wide range of operating conditions, such as temperature or load. In addition, the design models must be easy to be uses for design engineers to set up and to parameterize.

Power electronic devices and systems are affected by various stressors, such as temperature, overvoltage, overload, vibration, Electro-Magnetic Interference (EMI), humidity, etc. Therefore, the design process must include electrical, thermal, mechanical, fluid and control concerns within a multidisciplinary system. The design tool is a dynamic approach for the reliability problem and the design challenge. In this process, a simulation tool can be used, which incorporates multiple and integrated physics. The design tool will be developed by using electrical and thermal models based on a multiphysics simulation environment based on Finite Element Method (FEM).

One possible solution for multiphysics simulation at circuit level is ANSYS [20]. This software platform allows the analysis of all aspects of large-scale systems in a 6

single simulation design environment. Various controllable electrical, thermal, fluid and mechanical components are integrated into the simulation environment to develop power electronic system. This software ensures that the components in the system will operate like a real-world environment. Furthermore, for component models requiring the highest level of accuracy, ANSYS can enable power electronic designers to incorporate detailed physics-based models and to design complex systems by integration with other softwares such as ANSYS Icepack®, ANSYS Q3D Extractor®, ANSYS Simplorer®, ANSYS Mechanical®, etc. Moreover, professional programs such as MATLAB SIMULINK, PLECS, SolidWorks, etc. can be incorporated into ANSYS, where their benefits are used. This feature allows the designer to use customized codes and existing control or feedback methods without time consuming model translation.

#### 1.1.4 Design of high power modules

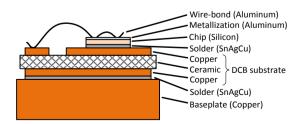

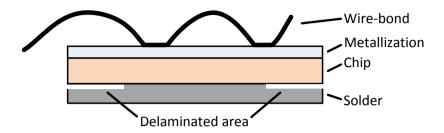

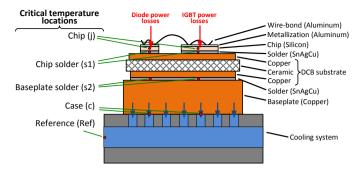

One of the most important issues that must be considered in the design process of power electronics is the characterization of devices including Insulated Gate Bipolar Transistor (IGBT) power modules. A power module is a physical package containing several power semiconductor devices that are typically soldered or sintered on a power electronic substrate. In the present work, the focus is placed on high power modules. Today, high power modules are widely used in wind turbines, motor drives, electric ships and trains [3]. For cost reduction reasons, manufacturers attempt to fabricate power modules with less silicon area, which leads to higher power density. Besides, the device manufacturers try to integrate power semiconductors in a common substrate with bond-wire connectors to increase the power density of circuit. These technologies introduce several stressors to the entire power module which may seriously affect the reliability of the device. For example, adverse thermal/power cycling may cause fatigues like bond-wire lift-off or solder cracking due to Coefficient of Thermal Expansion (CTE) mismatch [21]. So, an accurate prediction of the chip temperature in normal/abnormal operations and optimized cooling system are necessary in order to ensure a reliable and cost-effective converter design. Moreover, in practical applications, electrical parasitics cause many failures in the power module. The stray

inductances exist in the power module: from the IGBT chip collector and emitter to the busbars. The parasitic inductance accumulates energy, when the current flows through the commutation paths inside the power module. When the switch is turned off, this energy is released as a voltage spike, which may lead to device failure if no external snubber capacitor exists in the current path. The parasitics eventually affect the Electro-Magnetic Interference (EMI), and efficiency of the circuit [22]. Therefore, reduction of electrical parasitics is important in the power module layout design, especially in high frequency, high power applications of power electronics.

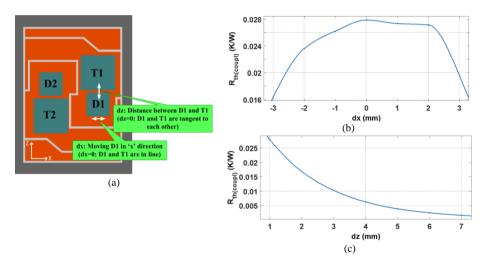

In the conventional design of power modules, it is intended to place multiple chips in a package to reduce the electrical parasitics in the conductors. However, by integration of the chips and making a compact layout design, thermal management of the power module becomes a critical issue since higher temperature is produced. In simple words in order to reduce the parasitic effects the connector lengths which semiconductor chips are placed on them should designed smaller and chips should be place closer to each other, but this will increase the heat generated in the power module due to thermal coupling effects among the chips [23].

Conventionally power module manufacturers follow a predefined layout design process based on the circuit topology, required electrical rating and geometrical constraints. The geometrical constraints include minimum chip size and conductor area/thickness and thus the minimum isolation layer required to mount the conductors [23]. When an initial layout is designed, the electrical parasitic parameters and the power module temperature can be extracted by simple mathematical models or Finite Element based tools. Finally, to obtain an optimized solution, an iterative process is done to find the layout with minimum electrical parasitics as well as minimum temperature. However, iterations demand for time-consuming calculations that may not be efficient for a fast analysis of the design. Therefore, simple modelling tool is required to iterate the electrical parasitics and thermal analyses of different layout designs towards an optimized solution.

#### 1.2 Hypothesis and objectives

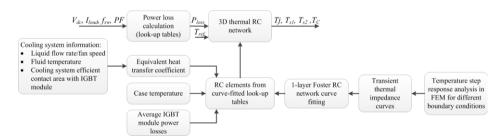

Thermal analysis and electrical parastics extraction are important in the design process for reliable performance. In the conventional design process, thermal analysis is performed by FEM tools such as ANSYS Icepak, SolidWorks, Pro/ENGINEER, etc. Electrical parasitic extraction, on the other hand, is performed by electromagnetic field FEM solvers such as ANSYS Q3D. The computation cost needed in the mentioned tools seriously affect the designing time. Especially in the cases when power modules are loaded in long-term thermal cycling or abnormal operations such as short-circuit which demands for very short time steps to capture short electrical/thermal stresses. On the other hand, circuit simulators are convenient tools which can model the power electronic circuit behaviors by using equivalent electrical elements. So, the objectives of the present work are:

- How to apply different circuit simulators in order to model various converter topologies and to investigate different control strategies in order to increase the efficiency of the power electronic system.

- How to employ multiphysics FEM tools in order to study the physical behavior of high power modules and to understand better the reliability of power modules in real operating conditions.

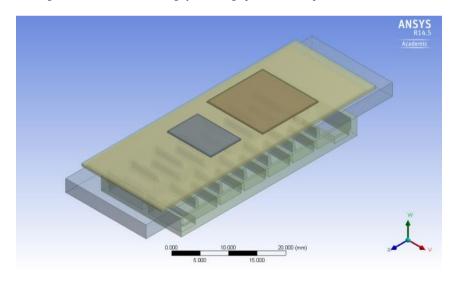

- How to simplify modelling of high power modules and cooling system inside the FEM environment in order to increase the efficiency of simulations and develop simple models to be used for reliability study.

- How to develop methods to extract electrical parasitics in the multi-chip power modules.

By applying the developed models in an optimization system design tool, shorter design cycle, cost reduction and improved power electronic system can be obtained.

#### 1.3 Thesis outline

Chapter 1 presents the introduction and motivation of the thesis, where the background, motivation and objectives of the thesis are addressed.

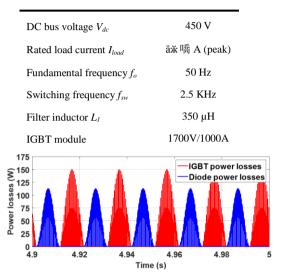

Chapter 2 studies several circuit topologies for high power applications to analyze different control strategies and circuit configurations in respect to the efficiency of the converters and loading of individual devices. It consists of two parts; first different topologies of multi-level inverters will be analyzed and efficiency of the inverters will be compared. In this part manufacturer datasheets will be used to calculate the power dissipation. In the second part, reduced switch converters will be studied and the efficiency of converters will be compared in different energy conversion conditions using generic power dissipation models.

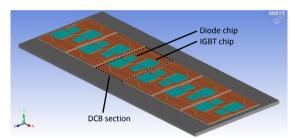

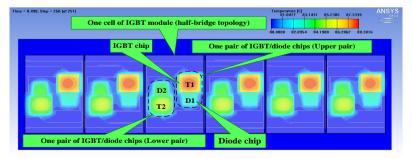

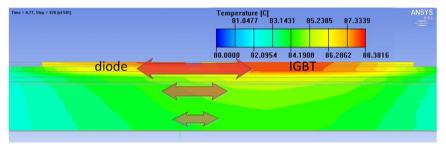

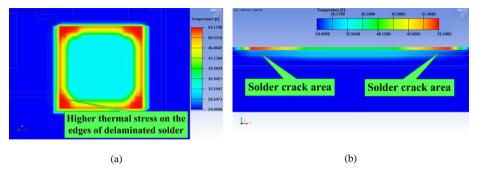

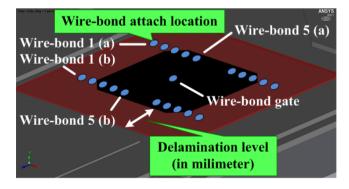

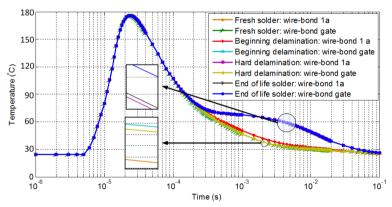

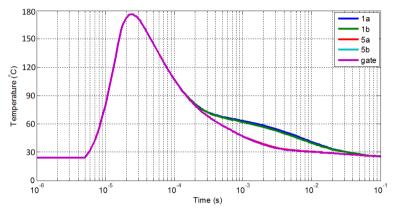

Chapter 3 explains the FEM modelling of power modules in both normal and abnormal operating conditions. The advantages and drawbacks of FEM simulations are first addressed. The concept of thermal coupling effect in power modules will be investigated and thermal design tools will be introduced for allocating power semiconductor chips. Finally, FEM simulations will be used to estimate the mechanical stress/strain in aged power module devices and short-circuit conditions

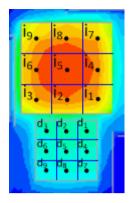

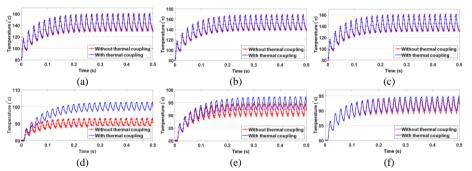

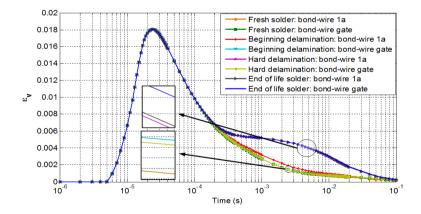

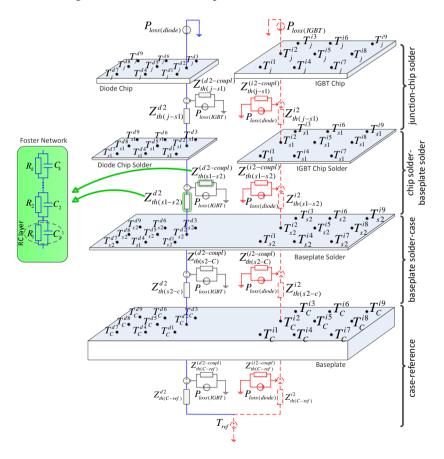

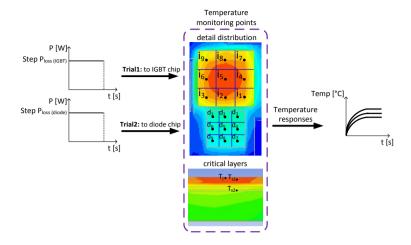

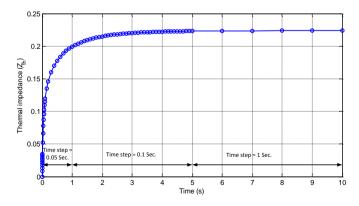

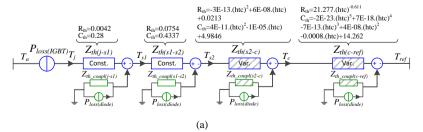

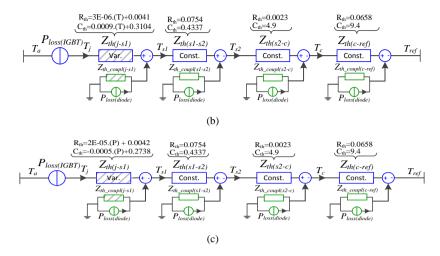

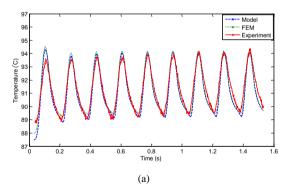

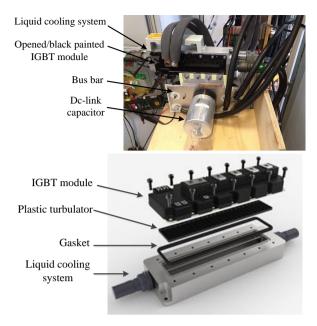

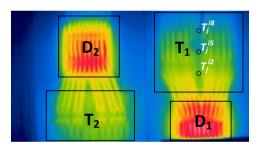

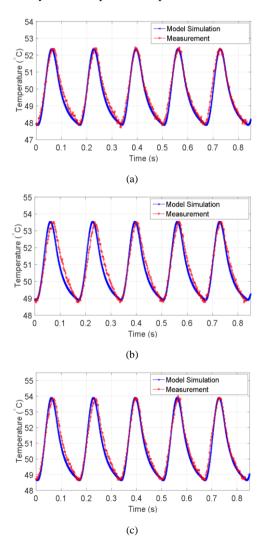

In chapter 4, an extensive study is devoted to develop simplified thermal model for high power modules. For this reason, 3D thermal network is constructed inside the power module in which critical temperature points are identified and assigned as nodes and lumped RC networks are constructed between the temperature points as branches. The main contribution of this 3D thermal network is identification of thermal coupling effects between chips and sublayers. In addition, the effect of boundary conditions on thermal modelling will be analyzed and modelled based on high power modules. Finally, the thermal model will be verified by FEM simulation and experimental testing.

In chapter 5, as another important factor in thermal management, cooling systems for power modules will be analyzed by means of FEM simulations. A design tool will be introduced to be applied for optimization of direct liquid cooling systems.

In chapter 6, the focus of the work is dedicated to electrical parasitics extraction of high power modules. The micro-strip transmission line method is employed to extract parasitic inductances in the multi-chip power modules. Also, a simplified index is presented to evaluate the parasitic inductances in different power module layouts. As a case study, parasitic parameters are extracted for a commercial SiC power module by means of mentioned method and the results are compared with FEM simulation results. Then by using parasitic reduction techniques, a reduced parastic power module is 10

designed and fabricated. The parasitic parameters of the optimized layout will be compared with parameters from a commercial power module.

In chapter 7, the conclusions and contributions of the thesis as well as potential suggestions for the future work will be given.

#### 1.4 List of publications

The list of publications extracted from the work presented in this thesis is in the following:

Journal papers:

- [P1] A.S. Bahman, K. Ma, P. Ghimire and F. Blaabjerg, "A Lumped Thermal Model Including Thermal Coupling and Thermal Boundary Conditions for High Power IGBT Modules," *IEEE Trans. Ind. Electron*, accepted with major revision.

- [P2] A.S. Bahman, K. Ma, P. Ghimire, F. Iannuzzo, and F. Blaabjerg, "A 3D Lumped Thermal Network Model for Long-term Load Profiles Analysis in High Power IGBT Modules," *IEEE J. Emerg. Sel. Topics. Power Electron*, to be published.

- [P3] K. Ma, A. S. Bahman, S. Beczkowski, and F. Blaabjerg, "Complete Loss and Thermal Model of Power Semiconductors Including Device Rating Information," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2556-2569, May 2015.

- [P4] Z. Qin, P. C. Loh, A. S. Bahman, and F. Blaabjerg, "Evaluation of current stresses in nine-switch energy conversion systems," *IET Power Electron.*, Vol. 7, No. 11, pp. 2877-2886, October 2014.

Conference proceedings:

- [P5] A. S. Bahman, F. Iannuzzo, C. Uhrenfeldt, F. Blaabjerg and S. Munk-Nielsen "Prediction of Short-Circuit-Related Thermo-Mechanical Stress in Aged IGBT Modules," submitted to ECCE 2016.

- [P6] A. S. Bahman and F. Blaabjerg, "Optimization Tool for Direct Liquid Cooling System of High Power Modules," submitted to *EPE 2016*.

- [P7] A.S. Bahman, K. Ma, and F. Blaabjerg, "General 3D Lumped Thermal Model with Various Boundary Conditions for High Power IGBT Modules," accepted, proc. of APEC 2016.

- [P8] A. S. Bahman, F. Blaabjerg, A. Dutta, and A. Mantooth, "Electrical Parasitics and Thermal Modeling for Optimized Layout Design of High Power SiC Modules," accepted, proc. of APEC 2016.

- [P9] A.S. Bahman, K. Ma, and F. Blaabjerg, "A Novel 3D Thermal Impedance Model for High Power Modules Considering Multi-layer Thermal Coupling and Different Heating/Cooling Conditions," in Proc. APEC 2015, pp. 1209-1215, 2015.

- [P10] A.S. Bahman, K. Ma, and F. Blaabjerg, "FEM Thermal Modelling and Improvement for High Power IGBT Modules Used in Wind Turbine Systems," *in Proc. WEGAT 2014*, pp. 1-7, 2014.

- [P11] K. Ma, A. S. Bahman, S. Beczkowski, and F. Blaabjerg, "Loss and thermal model for power semiconductors including device rating information," *in Proc. IPEC 2014 (ECCE-ASIA)*, pp. 2862-2869, 2014.

- [P12] A.S. Bahman, K. Ma, and F. Blaabjerg, "Thermal Impedance Model of High Power IGBT Modules Considering Heat Coupling Effects," in Proc. PEAC 2014, pp. 1382-1387, 2014.

- [P13] A. S. Bahman, Z. Qin, P. C. Loh, and F. Blaabjerg, "Loss comparison of different nine-switch and twelve-switch energy conversion systems," in Proc. APEC 2014, pp. 309-314, 2014.

- [P14] P. C. Loh, A. S. Bahman, Z. Qin, and F. Blaabjerg, "Evaluation of Switch Currents in Nine-Switch Energy Conversion Systems," in Proc. IECON 2013, pp. 755-760, 2013.

- [P15] A. S. Bahman, and F. Blaabjerg, "Comparison between 9-level hybrid asymmetric and conventional multi-level inverters for medium voltage application," *in Proc. ISIE 2013*, pp. 1-7, 2013.

#### References

- A. S. Bahman, "Comparison of Hybrid Asymmetric and Conventional Multi-level Inverters for Medium Voltage Drive Applications", Master Thesis, Chalmers University of Technology, March 2011.

- [2] J.M. Guerrero, F. Blaabjerg, T. Zhelev, K. Hemmes, E. Monmasson, S Jemei, M.P. Comech, R. Granadino, I. J. Frau, "Distributed Generation: Toward a New Energy Paradigm," *IEEE Ind. Electron. Mag.*, Vol. 4, Issue 1, pp. 52–64, 2010.

- [3] Y. Shaoyong, A. Bryant, P. Mawby, X. Dawei, R. Li, and P. Tavner, "An Industry-Based Survey of Reliability in Power Electronic Converters," *IEEE Trans. Ind. Appl.*, vol. 47, pp. 1441-1451, 2011.

- [4] H. Wang, M. Liserre and F. Blaabjerg, "Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities," *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp.17-26, Jun. 2013.

- [5] J. Biela, J. W. Kolar, A. Stupar, U. Drofenik, and A. Muesing, "Towards Virtual Prototyping and Comprehensive Multi-Objective Optimisation in Power Electronics," in Proc. of PCIM'2010, pp. 1-23, 2010.

- [6] S. V. Dhople, A. Davoudi, A. D. Dominguez-Garci, and P. L. Chapman, "A Unified Approach to Reliability Assessment of Multiphase DC-DC Converters in Photovoltaic Energy Conversion Systems," *IEEE Trans. Power Electron.*, vol. 27, pp. 739-751, 2012.

- [7] C. Rodriguez and G. A. J. Amaratunga, "Long-Lifetime Power Inverter for Photovoltaic AC Modules," *IEEE Trans. Ind. Electron.*, vol. 55, pp. 2593-2601, 2008.

- [8] US Department of Defense, "Reliability Prediction of Electronic Equipment," Washington DC, 1991.

- [9] ZVEL, Handbook for Robustness Validation of Automotive Electrical/Electronic Modules, Jun. 2008.

- [10] P. O'Connor, A. Kleyner, Practical Reliability Engineering, 5th Edition, John Wiley & Sons, 2012, ISBN: 978-0-470-97982-2.

- [11] S. Tarashioon, W. D. van Driel, and G. Q. Zhang, "System Approach for Reliability of Low-power Power Electronics; How to Break Down into Their Constructed Parts," in Proc. CIPS'2012, pp. 1-5, 2012.

- [12] I. Swan, A. Bryant, P. A. Mawby, T. Ueta, T. Nishijima, and K. Hamada, "A Fast Loss and Temperature Simulation Method for Power Converters, Part II: 3-D Thermal Model of Power Module," *IEEE Trans. Power Electron.*, vol. 27, pp. 258-268, 2012.

- [13] A. Schingale, D. Wolf, A. Schiessl, and M. Tarnovetchi, "New Methods Help Better Evaluate Risks Via Simulation," *in Proc. CIPS* '2012, pp. 1-5, 2012.

- [14] R. D. Lloyd, "Field Failure Analysis Using Root Cause Pattern Diagrams," in ASQ Webminar, 2012.

- [15] T. Huesgen, G. J. Riedel, and U. Drofenik, "Reliability driven virtual prototyping of power electronic equipment - a case study," in Proc. CIPS'2012, pp. 1-5, 2012.

- [16] V. Smet, F. Forest, J. Huselstein, F. Richardeau, Z. Khatir, S. Lefebvre, and M. Berkani, "Ageing and Failure Modes of IGBT Modules in High-Temperature Power Cycling," *IEEE Trans. Ind. Electron.*, vol. 58, pp. 4931-4941, 2011.

- [17] A. Testa, S. De Caro, and S. Russo, "A Reliability Model for Power MOSFETs Working in Avalanche Mode Based on an Experimental Temperature Distribution Analysis," *IEEE Trans. Power Electron.*, vol. 27, pp. 3093-3100, 2012.

- [18] M. Boettcher and F. W. Fuchs, "Power electronic converters in wind energy systems -Considerations of reliability and strategies for increasing availability," in Proc. EPE '2011, pp. 1-10, 2011.

- [19] K. Fischer, F. Besnard, and L. Bertling, "Reliability-Centered Maintenance for Wind Turbines Based on Statistical Analysis and Practical Experience," *IEEE Trans. Energy Convers.*, vol. 27, pp. 184-195, 2012.

- [20] ANSYS® Academic Research, Release 16.1.

- [21] N.Y.A. Shammas, "Present problems of power module packaging technology," *Microelectron. Rel.*, vol. 43, pp. 519-527, April 2003.

- [22] L. Shengnan, L. M. Tolbert, F. Wang, F. Z. Peng, "Stray Inductance Reduction of Commutation Loop in the P-cell and N-cell-Based IGBT Phase Leg Module," *IEEE Trans. Power Electron.*, vol.29, no.7, pp.3616-3624, July 2014.

- [23] Z. Gong, "Thermal and electrical parasitic modeling for multi-chip power module layout Synthesis," M.S. thesis, EE, Univ. of Arkansas, Fayetteville, AR, 2012.

# Power module applications in high power converters

As technology has evolved, industry has constantly been looking for methods to reduce the size and cost of power converters and also improving their reliability. This leads to the development of many new power converters and to invent new modulation methods, which so far, has focused on improving a few topological or performance features. This chapter deals with the application of alternative topologies and control strategies to increase the efficiency and reliability of power electronic converters. First alternative topologies and semiconductors will be used in multi-level inverters to increase the efficiency and then new topologies with reduced number of switches will be used to increase the efficiency in back to back converters.

#### 2.1 Application of power modules in multi-level inverters

There is an increasing demand for multi-level inverter systems capable of providing high output voltage, good spectral performance and easy control. Examples of such systems are medium voltage drives, FACTS devices, HVDC transmission, and active power filters [1], [2]. Currently, medium voltage drives cover a power range from 0.2 MW to 100 MW at voltage levels from 2.3 kV up to 13.8 kV [2].

Nevertheless, the design of medium voltage drives encounters a number of challenges related to the topologies and control of the grid side converter (e.g. power quality, resonance, and power factor) and motor side converter (e.g. dv/dt, torque ripples, motor derating caused by generated harmonics and traveling wave reflections), as well as power semiconductor devices (semiconductor losses) [1]. Essential requirements for medium voltage drives are high efficiency, high reliability, low cost, low volume, and in some applications, high dynamic performance and regeneration capability [1].

Due to limitations in semiconductor voltage and current rating, it is difficult to connect a single semiconductor device directly to a medium voltage network. To overcome this problem, a family of multi-level inverters hav been introduced for medium voltage levels [3].

Multi-level inverters consist of power semiconductor devices and capacitors which generate voltages with stepped waveforms in the output. The DC-link in the input of multi-level inverters comprises of a capacitor, or a bank of capacitors. The switching schemes of semiconductor switch devices allow the inverter to generate higher stepped voltages by using more capacitors in the DC-link. However, most semiconductor devices cannot withstand high level of voltages to several kVs.

The large number of semiconductors in multi-level inverters has negative impact on the reliability and overall efficiency. However, using inverters with a low number of semiconductors requires large and expensive LC-filters to limit insulation stress on the motor windings, or can only be used in applications with motors that can withstand this stress [4]. As a result, there is significant effort to develop multi-level inverters with the same performance and less power devices.

Best known multi-level topologies include: the cascaded H-bridge, diode clamped and flying-capacitor multi-level inverters [5]-[7]. These classical solutions are called symmetric multi-level inverters, because they have the same voltage on each of the intermediate-circuit capacitors, and all the power semiconductors have to be capable to block the same voltage in their 'off' state. An asymmetric multi-level inverter has exactly the same circuit topology as the symmetric multi-level inverter – it differs only in the capacitor voltages. However, the properties of asymmetric multi-level inverters are quite different. Specifically, the number of output-voltage levels can be dramatically increased [8], [9]. Since the different cells of asymmetric inverters work with different DC-link voltages and different switching frequencies, it is more efficient to select various semiconductor devices that are appropriate for the conditions of each cell and thereby optimize the performance of the converter. These inverters are called "hybrid multi-level inverters" [10].

In this section, hybrid asymmetric multi-level inverter will be compared with conventional symmetric multi-level inverters in terms of harmonic distortion, power 16

losses and efficiency for the same output voltage rating. This section is organized into the following sub-sections: First, the structure of the multi-level inverter topologies is briefly described. Then, the inverter specifications, modulation techniques and performance indexes are investigated. Finally, the investigated topologies are compared and simulation results are presented.

#### 2.1.1 Multi-level inverter topologies

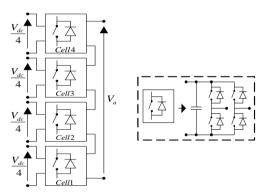

#### • Cascaded H-bridge multi-level inverter (CHB MI)

A single phase 9-level cascaded H-bridge multi-level (9-L CHB ML) inverter is shown in Fig. 2.1. In this topology, the power cells are in series and the number of phase voltage levels that can be obtained at the converter terminals is proportional to the number of cells. Simply, the number of phase voltage levels at the converter terminals is 2N+1, where N is the number of cells [3]. This topology has excellent input current and output voltage waveforms. The output voltage has smooth steps, so an output filter is usually not needed or in the case of need, it can be very small.

Fig. 2.1. 9-level Cascaded H-bridge multi-level inverter (9-L CHB MI) circuit.

#### • Diode Clamped Multi-Level Inverter (DC MI)

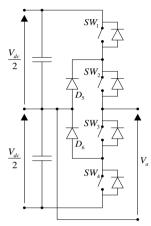

Fig. 2.2 shows a single phase of a 3-level diode-clamped multi-level inverter (3-L DC MI). In this topology, the semiconductor devices are connected in series and the dclink is divided by smaller capacitors and connects to the switches by clamping diodes [11]. The clamp diode connections are necessary to block the current and their numbers in each leg are selected in such a way to have the same blocking voltage like the

switches. This topology has a simple circuit topology, but generates high and steep voltage steps, which may impact the life time of the motor windings as the dv/dt can be high. An additional filtering stage is therefore needed to reduce the ripple in the inverter output voltage.

Fig. 2.2. 3-level Diode-clamped multi-level inverter (3-L DC MI) circuit.

#### • Hybrid Asymmetric Multi-Level Inverter (HA MI)

Fig. 2.3 shows the single phase circuit diagram of an asymmetric cascaded two-cell 9-level inverter (9-L HA MI), where the dc voltages for the H-bridge cells are not equal [12]. In the asymmetric topology, a High-Voltage (HV) cell, which has a higher voltage rating and operates at low switching frequency, is ideal for GTO/IGCT switches. GTO and IGCT are reliable devices providing a high blocking voltage [13], [14]. On the other hand, the Low-Voltage (LV) cell, which has a lower voltage rating and operates at high switching frequency, is ideal for IGBTs. IGBTs allow higher switching frequencies together with good performance at lower voltages [15]. By combining IGBT and GTO/IGCT in an asymmetric multi-level inverter, a hybrid inverter could be obtained by utilizing the benefits of two device technologies.

Fig. 2.3. 9-level Hybrid asymmetric multi-level inverter (9-L HA MI) circuit.

#### 2.1.2 Inverter specifications

In this section both the inverter rating and specifications are chosen close to that of what is commercially available for medium voltage applications [16], [17]. Some commercial medium voltage drives, their power and voltage ratings and converter topologies with the semiconductor switches applied to them are summarized in Table 2.1.

Table 2.1. Commercial available medium voltage drives

| Manufacturer     | Drive<br>Model     | Power (MVA) | Voltage<br>(kV)        | Topology                | Semi-<br>conductor |

|------------------|--------------------|-------------|------------------------|-------------------------|--------------------|

| Robicon          | Perfect Harmony    | 0.3 - 0.31  | 2.3 - 13.8             | CHB MI                  | LV IGBT            |

| Allen<br>Bradley | Power Flex 7000    | 0.15 – 6.7  | 2.3, 3.3,<br>4.16, 6.6 | CSI                     | IGCT               |

| Siemens          | Masterdrive MV     | 0.66 – 9.1  | 2.2, 3.3,<br>4.16, 6.6 | 3-L Diode<br>Clamped    | HV IGBT            |

| Siemens          | Masterdrive<br>ML2 | 0.66 – 9.1  | 3.3                    | 3-L Diode<br>Clamped    | IGCT               |

|                  | ACS 1000           | 0.3 – 5     | 2.3, 3.3, 4            | 3-L Diode<br>Clamped    | IGCT               |

| ABB              | ACS 5000           | 5.2 – 2.4   | 4.16, 6, 6.6,<br>6.9   | Cascaded H-<br>Bridge   | IGCT               |

|                  | ACS 6000           | 3 – 27      | 3, 3.3                 | 3-L Diode<br>Clamped    | IGCT               |

|                  | VDM 5000           | 1.4 - 7.2   | 2.3, 3.3, 4.2          | 2-L VSI                 | IGBT               |

| Alstom           | VDM 6000           | 0.3 – 8     | 2.3, 3.3, 4.2          | 3-L Flying<br>Capacitor | IGBT               |

|                  | VDM 7000           | 7 – 9.5     | 3.3                    | 3-L Diode<br>Clamped    | GTO                |

| General          | Dura-Bilt5 MV      | 0.3 – 2.4   | 4.16                   | 3-L Diode<br>Clamped    | IGBT               |

| Electric         | MV-GP Type H       | 0.45 – 7.5  | 3.3, 4.16              | Cascaded H-<br>Bridge   | IGBT               |

The drive system under study is designed to supply an induction motor with line-to-line voltage of 4.16 kV, Nominal power of 500 kVA, output frequency of 50 Hz and power factor of 0.85. Table 2.2 summarizes the basic inverter data for the design of the main power part components.

| Inverter line-to-line voltage (RMS) | 4.16 kV          |

|-------------------------------------|------------------|

| Phase current                       | 60 A             |

| Nominal inverter output power       | 500 kVA          |

| Power factor of motor               | 0.85             |

| Nominal dc-link voltage             | 6353 V           |

| Modulation technique                | Optimized PD-PWM |

| Switching frequency                 | 450 - 1050 Hz    |

| Maximum junction temperature        | 125°C            |

| (IGBT, IGCT, diode)                 | 123 C            |

Table 2.2. The basic specifications of inverter and induction motor for comparison

#### 2.1.2.1 Modulation technique

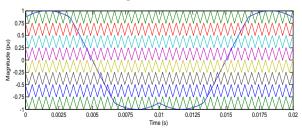

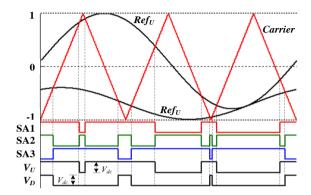

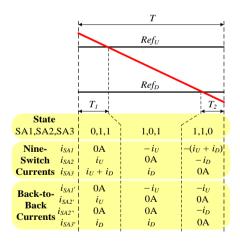

The modulation technique employed in this system is Phase Disposition PWM (PD-PWM). The PD-PWM method is one of the carrier-based PWM methods, and the implementation is based on a comparison of a reference waveform with vertically shifted carrier waveforms [18]-[21]. This method uses *N-1* carrier signals to generate the *N*-level inverter output voltage. The injection of a 3<sup>rd</sup> harmonic into the reference waveforms will achieve a 15% increase in modulation index compared to sinusoidal PWM before over-modulation nonlinearities occur. This is simply because of the reduced height of the three-phase reference envelope that is achieved by 3<sup>rd</sup> harmonic injection [22]. In this technique, the 3<sup>rd</sup> harmonic is cancelled out in a three-phase system. This modulation technique is called Switching Frequency Optimized PD-PWM (SFO-PD-PWM) and it is shown in Fig. 2.4.

Fig. 2.4. Switching Frequency Optimized PD-PWM (SFO-PD-PWM) technique, reference and carrier signals.

#### 2.1.2.2 DC-link voltage

The minimum dc-link voltage to achieve an output line-to-line voltage of 4.16 kV using SFO-PWM can be calculated by

$$V_{dc\,min} = \sqrt{2} \cdot V_{U\,rms} = \sqrt{2} \cdot 4.16 \, kV = 5883 \, V$$

(2.1)

where  $V_{dc,min}$  is the minimum dc-link voltage and  $V_{ll,1,rms}$  is the RMS value of the output line-to-line voltage. To determine the nominal dc-link voltage of the inverter, a voltage reserve of 8% is assumed (for the imperfections of the real system, control reserve, device voltage drops, etc.)

$$V_{dc,n} = 1,08 \cdot V_{dc,min} = 1,08 \cdot 5883 = 6353 V$$

(2.2)

where  $V_{dc,n}$  is the nominal dc-link voltage.

#### 2.1.2.3 Power semiconductors selection

Table 2.3 and Table 2.4 summarize the design of the power semiconductors for the 4.16 kV inverter, assuming a switching frequency of 600 Hz in all topologies. The voltage  $V_{com}$  describes the commutation voltage of the corresponding commutation cells.  $V_{com@100FIT}$  is an index for the maximum voltage that the semiconductor switch can withstand and is defined by the nominal voltage of the semiconductor for which it has a cosmic ray withstand capability of 100 FIT (one FIT is equivalent to one failure in  $10^9$  operation hours). The ratio of  $V_{com}/V_{com@100FIT}$  represents a measure of the device voltage utilization for different topologies [23].

Table 2.3. Inverter voltage and semiconductor specifications in the conventional multi-level topologies

| Topology                                   | 3L-DC MI                                  | 9L-CHB MI                                 |

|--------------------------------------------|-------------------------------------------|-------------------------------------------|

| Power devices                              | 6.5 kV / 200 A<br>FZ200R65KF2<br>INFINEON | 1.7 kV / 200 A<br>BSM200GB170DLC<br>EUPEC |

| Nominal dc-link voltage                    | 6353 V                                    | 794 V                                     |

| Rated device voltage                       | 6.5 kV IGBT                               | 1.7 kV IGBT                               |

| Commutation voltage                        | 3176 V                                    | 794 V                                     |

| $V_{com@100{ m FIT}}$                      | 3600 V                                    | 900 V                                     |

| V <sub>com</sub> / V <sub>com@100FIT</sub> | 0.88                                      | 0.88                                      |

|                                            | 9L-HA MI                                             |                                           |  |

|--------------------------------------------|------------------------------------------------------|-------------------------------------------|--|

| Topology                                   | Main Inverter (IGCT)                                 | Sub Inverter<br>(IGBT)                    |  |

| Power devices                              | 4.5 kV / 340 A<br>5SHX04D4502<br>/5SDF03D4502<br>ABB | 1.7 kV / 200 A<br>BSM200GB170DLC<br>EUPEC |  |

| Nominal dc-link<br>voltage                 | 2382 V                                               | 794 V                                     |  |

| Rated device voltage                       | 4.5 kV IGCT                                          | 1.7 kV IGCT                               |  |

| Commutation voltage                        | 2382 V                                               | 794 V                                     |  |

| $V_{com@100{ m FIT}}$                      | 2700 V                                               | 900 V                                     |  |

| V <sub>com</sub> / V <sub>com@100FIT</sub> | 0.88                                                 | 0.88                                      |  |

Table 2.4. Inverter voltage and semiconductor specifications in the hybrid asymmetric topology

#### 2.1.3 Performance indexes

The performance indexes used in the comparison are: Total Harmonic Distortion (THD), First-order Distortion Factor (DF1), semiconductor power losses (conduction and switching losses) and the efficiency.

#### a. THD

The THD of the inverter can be calculated as:

$$THD\% = \frac{100}{V_1} \sqrt{\sum_{h=2,3,\dots}^{\infty} V_h^2}$$

(2.3)

where  $V_1$  is the fundamental harmonic of the signal analyzed, h is the harmonic order, and  $V_h$  is the harmonic amount of order h.

#### 2.1.3.1 DF1

In AC motor drive applications, the first-order Distortion Factor (DF1) which is the Weighted Total Harmonic Distortion (WTHD) is another considerable index. DF1 is defined by:

$$DF1\% = \frac{100}{V_1} \sqrt{\sum_{h=2,3,\dots}^{\infty} (\frac{V_h}{h})^2}$$

(2.4)

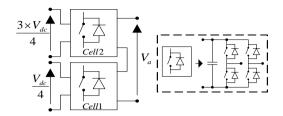

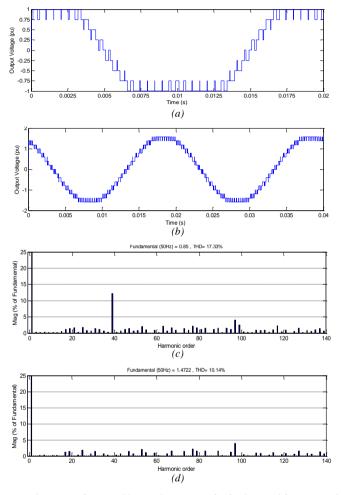

The output phase and line voltage waveforms and their harmonic spectrum for the 9-level hybrid asymmetric multi-level inverter are shown in Fig. 2.5. It can be seen that

the harmonic content, especially in the low level orders are decreased compared to twolevel inverters because of the increase in the number of output voltage levels.

Fig. 2.5. Output voltage waveforms and harmonic spectrum for fundamental frequency 50 Hz: a) Output phase voltage, b) Output line voltage, c) Harmonic spectrum of output phase voltage, d) Harmonic spectrum of output line voltage.

#### 2.1.3.2 Semiconductors power losses

The semiconductor power losses can be calculated from the curves  $(v_{sat} \times I_{load})$  and  $(E \times I_{load})$ , given in the datasheet of each device. In these curves the parameters are defined as:  $v_{sat}$ : The on-state saturation voltage  $(v_{ce})$  for the IGBT,  $v_T$  for the IGCT and  $v_F$  for the diode); E: The switching energy losses in one commutation  $(E_{on})$  for a turn-on

commutation,  $E_{off}$  for a turn-off commutation and  $E_{rec}$  for reverse recovery process);  $I_{load}$ : The load current. These curves are used in MATLAB to calculate the power losses. MATLAB uses the mathematical models that represent the functions  $v_{sat}(i_{load})$  and  $E(i_{load})$  for semiconductors. These models are obtained by extrapolation of curves extracted from datasheets and using the curve-fitting toolbox (cftool). Based on these mathematical models, the conduction and switching losses are calculated in each semiconductor device. The sum of switching and conduction power losses gives the total power losses.

#### Conduction losses

The conduction power losses are calculated by (2.5) in the main switch and by (2.6) in the diode:

$$P_{cond_{SW}} = \frac{1}{T_{SW}} \int_{0}^{T_{SW}} v_{sat}(t) . i_{load}(t) . v_{cmd_{SWx}}(t) . dt$$

(2.5)

$$P_{cond_D} = \frac{1}{T_{SW}} \int_{0}^{T_{SW}} v_F(t) \cdot i_{load}(t) \cdot v_{cmd_{SWx}}(t) \cdot dt$$

(2.6)

where  $T_{sw}$  is the switching cycle and  $v_{cmd}$  is the command signal of switch that can be 1 or 0. The total conduction power losses are calculated by (2.7):

$$P_{cond_{TOTAL}} = P_{cond_{IGBT/IGCT}} + P_{cond_{D}}$$

(2.7)

#### Switching losses

The turn on and the turn off power losses in the main switch are given by (2.8) and (2.9) and the reverse recovery power losses in the diode is calculated by (2.10) – for a given gate voltage:

$$P_{on} = \frac{1}{T} \sum E_{on} (i_{load}(t)) . f_{SW}$$

(2.8)

$$P_{off} = \frac{1}{T} \sum E_{off} (i_{load}(t)) . f_{SW}$$

(2.9)

$$P_{rec} = \frac{1}{T} \sum E_{rec} (i_{load}(t)) \cdot f_{SW}$$

(2.10)

The total switching power losses are calculated by (2.11):

$$P_{SW_{TOTAL}} = P_{on} + P_{off} + P_{rec} (2.11)$$

Finally, the total power losses are the sum of all conduction and switching power losses and computed by (2.12):

$$P_{loss} = P_{cond_{TOTAL}} + P_{SW_{TOTAL}} (2.12)$$

Based on these mathematical models, the conduction and switching losses are calculated in each semiconductor device. The sum of the switching and the conduction power losses gives the total power losses.

#### 2.1.4 Comparison of different multi-level inverter topologies

The comparison for the drive system explained in the previous section will be implemented in two ways: constant switching frequency and constant efficiency.

#### • Comparison in the state of constant switching frequency (600 Hz)

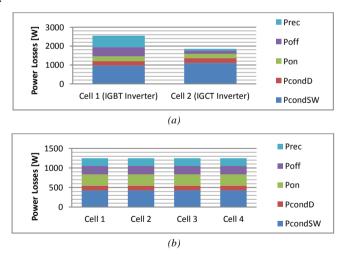

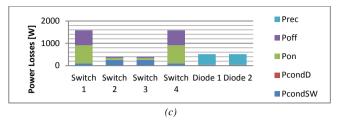

A switching frequency range of 450-1050 Hz is typical for available industrial medium voltage drives [17]. The switching frequency is assumed to be 600 Hz for the various topologies in this study. The performance indexes are listed in Table 2.5 and the power losses distributions for each topology are shown in Fig. 2.6.

According to Table 2.5, both the hybrid asymmetric and cascaded H-bridge inverters have the same THD for current and voltage, since they generate the same voltage levels. Compared with the other two topologies, the THD for the diode clamped inverter is about 3 times higher for the current and 3.8 times higher for the voltage. The THD of the voltage is higher than the current since the load is inductive and behaves as a filter. Similarly, the DF1 for the diode clamped is larger than the DF1 for the hybrid asymmetric and cascaded H-bridge inverters. This means that at a constant switching frequency, the harmonics of the output voltage appears at higher frequencies which are more damped by an inductive load. Moreover, power losses in the hybrid asymmetric topologies are lower, compared with both the cascaded H-bridge and the diode clamped inverters.

Considering the power rating of inverters, the hybrid asymmetric topology seems to show better performance in saving energy compared to other conventional topologies. As it can be seen in Fig. 2.6 (a), in the hybrid asymmetric inverter, the IGBT cell has the largest portion of power losses, as this cell operates at a higher switching frequency than IGCT cell, and therefore the switching losses increases. In

both of the cells the conduction power losses represent the most significant portion of the total losses. This is due to the fact that the switching frequency is low and all the switching devices commutate at a low switching frequency. Moreover, the RMS currents over the switches in the IGCT and IGBT inverters are 78 A and 72 A respectively – and consequently IGCT inverter has higher conduction losses than the other one.

Fig. 2.6 (b) shows the power losses distribution in cascaded H-bridge inverter. In this topology, all the cells operate with the same switching frequency and dc-link voltages. Therefore, all cells show approximately the same semiconductor power losses. In the diode clamped inverter, Fig. 2.6 (c), the power losses are concentrated in switch 1 and switch 4. This occurs because switch 2 in the positive and switch 3 in the negative half cycles do not commutate to generate the zero voltage level. So, the conduction losses are the major of power losses in these switches. In diodes, most of power losses are related to switching losses, since these diodes block the current in all the switches commutations as well as conducting functions.

Inverter Efficiency [%]

Fig. 2.6. Power loss distribution at constant frequency (600 Hz) with the test conditions given in Table 2.3 and Table 2.4 (a) Hybrid asymmetric 9-level inverter (b) Cascaded H-bridge 9-level inverter (c) Diode clamped 3-level inverter.

| Comparison                     | Constant Switching Frequency (600 Hz) |                                 |                                    |  |

|--------------------------------|---------------------------------------|---------------------------------|------------------------------------|--|

| Topologies                     | Hybrid<br>Asymmetric<br>9-Level       | Cascaded<br>H-bridge<br>9-Level | Diode-Clamped<br>3-Level           |  |

| Total number of devices/phase  | 4 IGBT Modules +<br>4 IGCT/Diodes     | 16 LV-IGBT<br>Modules           | 4 HV-IGBT<br>Modules +<br>2 Diodes |  |

| Number of phase-voltage levels | 9                                     | 9                               | 3                                  |  |

| Number of line-voltage levels  | 17                                    | 17                              | 5                                  |  |

| THD of phase-current [%]       | 5.09                                  | 5.21                            | 15.36                              |  |

| THD of line-voltage [%]        | 7.51                                  | 7.52                            | 31.6                               |  |

| DF1 of line-<br>voltage [%]    | 0.47                                  | 0.48                            | 10.21                              |  |

| Total power losses [W]         | 3552                                  | 3893                            | 4544                               |  |

99.29

99.22

99.09

Table 2.5. Comparison of Multi-Level Inverter Topologies at Constant switching Frequency

#### • Comparison in the state of constant efficiency (99%)

To evaluate the three designed topologies for different applications with a demanded efficiency, it is assumed that the inverter efficiencies for all of topologies are about 99% at a constant inverter power of 500 kVA. This efficiency is typical for state-of-the-art medium voltage drives [12]. Since the conduction losses of the switches are dependent to the average values of voltage and current of switches, by controlling the switching frequencies, the efficiency of 99% can be obtained. The performance indexes for this comparison are listed in Table 2.6 and the power losses distributions are shown in Fig. 2.7.

Compared to the constant frequency state, with an increase in the switching frequencies, the THD values of the current and voltage do not change significantly. This fact is due to the topologies and the output voltage levels are remaining unchanged. Instead, since the frequency of the first harmonic band directly affects the DF1, the first distortion factor is decreased. This can be seen especially in the hybrid asymmetric topology that by increasing the switching frequency to 5400 Hz, DF1 is reduced by 93%. In the cascaded H-bridge with the switching frequency of 800 Hz and diode-

clamped with the switching frequency of 1150 Hz, the reductions of DF1 are approximately 79% and 48%. These values of DF1 indicate that the output filter of the diode-clamped and cascaded H-bridge inverters will have greater volume, weight, and cost than the filter used in the hybrid asymmetric inverter to obtain the same line voltage distortion.

On the other hand, considering the power losses distribution in the hybrid asymmetric topology, the switching losses are the major part of the power losses in cell 1 (IGBT inverter). This increase of switching losses comparing to the previous case (switching frequency of 600 Hz) shows that in the hybrid asymmetric topology the switching frequency affects the IGBT inverter switching losses more than the IGCT inverter, since it works with higher switching frequency. In addition, in the state of operation at the same efficiency in the three topologies, the frequency of carrier signals in the hybrid asymmetric topology is about 6.2 times of cascaded H-bridge and 4.7 times of diode-clamped topology. It shows more relevance of this topology compared to the switching frequency that in practice limits the increase of switching frequency up to 1000 Hz.

**Inverter Efficiency [%]**

Fig. 2.7. Power loss distribution in equal efficiency (99%)) with the test conditions given in Table 2.3 and Table 2.4 (a) Hybrid asymmetric 9-level inverter (b) Cascaded H-bridge 9-level inverter (c) Diode clamped 3-level inverter.

| Comparison                     | Equal Efficiency (99%) |             |           |

|--------------------------------|------------------------|-------------|-----------|

|                                | Hybrid                 | Cascaded H- | Diode-    |

| Topologies                     | Asymmetric             | bridge      | Clamped   |

|                                | 9-Level                | 9-Level     | 3-Level   |

|                                | 4 IGBT                 | 16 LV-IGBT  | 4 HV-IGBT |

| Total number of devices/phase  | Modules +              | Modules     | Modules + |

|                                | 4 IGCT/Diodes          |             | 2 Diodes  |

| Number of phase-voltage levels | 9                      | 9           | 3         |

| Number of line-voltage levels  | 17                     | 17          | 5         |

| Switching frequency [Hz]       | 5400                   | 860         | 1150      |

| THD of phase-current [%]       | 1.73                   | 5.02        | 15.84     |

| THD of line-voltage [%]        | 6.6                    | 6.78        | 32.3      |

| DF1 of line-                   | 0.037                  | 0.102       | 5.338     |

| voltage [%]                    |                        |             |           |

| Total power losses [W]         | 4897                   | 4999        | 4982      |

Table 2.6. Comparison of Multi-Level Inverter Topologies at Equal Efficiency

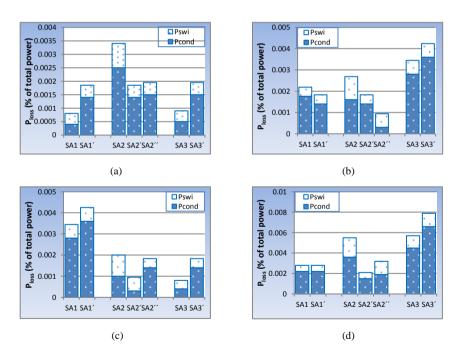

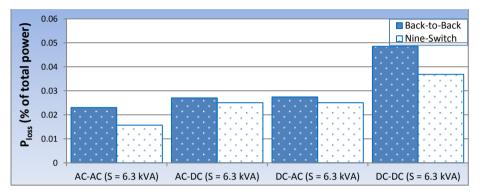

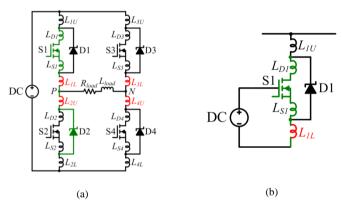

## 2.2 Application of power modules in reduced switch converters

99.01

99.01

99.01

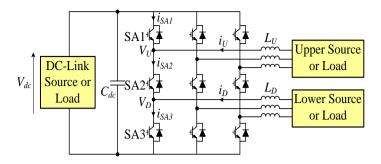

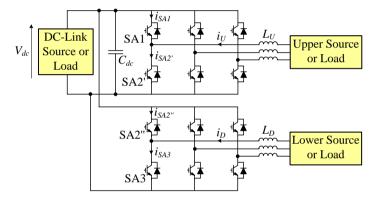

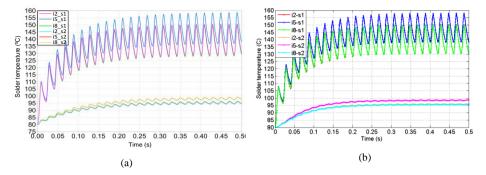

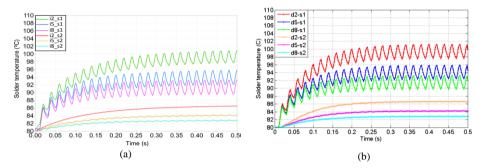

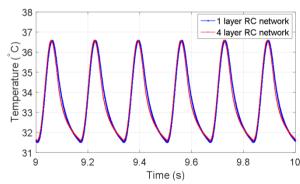

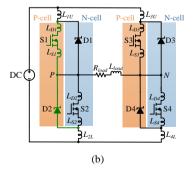

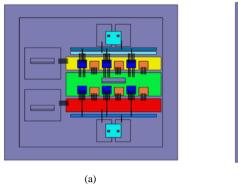

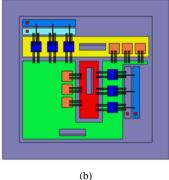

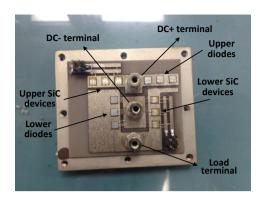

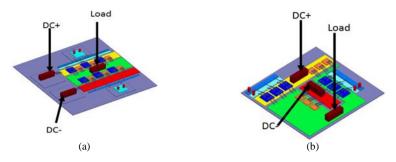

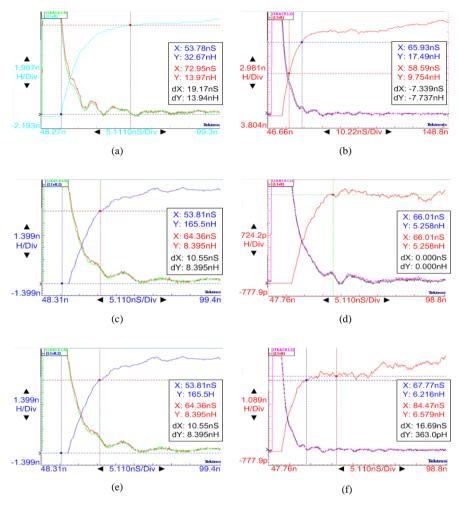

Besides to development of more efficient multi-level inverter topologies, one of the popularly pursued features is to reduce the number of components needed in the converters. For passive components, the commonly mentioned example will probably be the ac-ac matrix converters, where no bulky dc-link capacitors are needed [24]. Matrix converters are thus referred to as "all-semiconductor" even though a clamping capacitor is still needed in practice. The development in matrix converters has subsequently been progressed to the indirect type [25], where a fictitious dc-link has been introduced, but no large dc-link capacitor is used. This progress allows active switches to be reduced, leading to sparse matrix converters to be proposed in [26].