**Aalborg Universitet**

#### Lightweight Cryptography for Passive RFID Tags

David, Mathieu

Publication date: 2012

**Document Version** Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): David, M. (2012). Lightweight Cryptography for Passive RFID Tags.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Lightweight Cryptography for Passive RFID Tags

Ph.D Thesis by MATHIEU DAVID

December 2011

## **Supervisor**

Prof., Dr. Techn. Torben Larsen

## **Assessment Committee**

Prof. Gildas Avoine, Université Catholique de Louvain (UCL), Belgium

Postdoc Pedro Peris-Lopez, Delft University of Technology (TUD), The Netherlands

Assoc. Prof. Petar Popovski, Aalborg Universitet (AAU), Denmark

## **Moderator**

Assoc. Prof. Ole Kiel Jensen, Aalborg Universitet (AAU), Denmark

Copyright © December 2011

by Mathieu David

Aalborg University

Niels Jernes Vej 12

Aalborg Øst

Denmark

e-mail: md@es.aau.dk, mr.mathieu@gmail.com

All rights reserved by the author.

Printed in Aalborg, Denmark

I dedicate this Thesis

to my closest family relatives for their continuous support... (... even without understanding what I was doing).

achieved AES achieve able additional around author A2U2 authentication A2U2A2U2 also hlocitz annlication applications alsoh challenge area lassification attacks cipherblock chosen chapter ciphertext comparison constrained dete complexity computation mputational Chapter challenges Boolean described data counter mequations compared encryption clock electronics cryptanalysis cryptography capabl esigndifferent estimat full et CONSUMPTION designs nd Cryptography more a design gate evaluate functionsconsidered following cryptographic hardware example equation function service serv Figure devices high ever given, length linear information hash initialization kHz 1 level label Inter paper need limit knudsenzöi prinktyker metric Lightweight new of the second sec PRESENT output plaintext possible optimized obtaine performance non-linear random reader related PRINTclpher platforms period primitive propose ovidiv servery probability part presented requirements register published Section PUF proposed required resource resource result round response register resource result round 1m relativel rounds see protocol research process elicor provide recent size section shown requires simple second secure Since sequence state set secret results significant system systems Therefore selected solution suitable specific stream single thesis still time throughput two Table Sed use USH three technology values various version viriten viriten work Trivium without variables

# Abstract

I n 2011, we are entering a decade where Radio Frequency IDentification (RFID) systems will become ubiquitous, slowly but surely replacing its old ancestor: the barcode. With the RFID technology come many advantages such as faster retailing, continuous control along the supply chain, real-time monitoring and localization of items, etc. However, all these benefits come to the condition of secure systems, especially in sensitive application areas such as military, finance, pharmaceutics, etc. Additionally, the privacy aspect involved with this technology could become a major issue in the perspective of a global adoption. In the past few years, an increasing number of researchers concentrates their efforts into providing secure solutions for RFID systems.

After several attempts to integrate traditional cryptographic primitives into small, embedded, and extremely resource constrained devices, the results were mostly unsatisfactory. As a conclusion, a new branch of cryptography, commonly called *Lightweight Cryptography*, emerged to address the issues of these tiny ubiquitous devices.

This Thesis presents a comprehensive engineering to lightweight cryptography, proposes a classification and explores its various ramifications by giving key examples in each of them. We select two of these branches, ultralightweight cryptography and symmetric-key cryptography, and propose a cryptographic primitive in each of them. In the case of symmetric-key cryptography, we propose a stream cipher that has a footprint among the smallest in the published literature and aims at being implemented on printed electronics RFID tags.

Then, we compare different cryptographic primitives based on their key parameters: throughput, area, power consumption and level of security. Our main concern is the integrability of these selected primitives into real passive RFID tags. Therefore, in order to go beyond a comparison of the different parameters, we propose a metric that combines all their characteristics into one single value. This metric also has the advantage of being customizable, depending on the requirement of an integrator for a particular application.

Finally, we conclude that the research for finding robust cryptographic primitive in the branch of lightweight cryptography still has some nice days ahead, and that providing a secure cryptosystem for printed electronics RFID tags remains an open research topic.

**Keywords**: Lightweight Cryptography, RFID, Security, Printed Electronics, Stream Cipher, Comparison Metric.

# **Dansk Abstrakt**

I 2011 går vi ind i et årti, hvor RFID-systemer bliver allestedsnærværende og langsomt, men sikkert vil afløse dets gamle forgænger: stregkoden. Med RFID-teknologi er der mange fordele, såsom hurtigere detailhandel, kontinuerlig kontrol af logistikkæden, realtids monitorering og lokalisering af objekter osv. Men alle disse fordele kommer på betingelse af sikre systemer, specielt i følsomme applikations-miljøer såsom militæret, finansverdenen, medicinalindustrien osv. Desuden kan folks privatliv blive et problem med denne teknologi set i et globalt perspektiv. I de sidste år har et stigende antal forskere koncentreret deres indsats for at levere sikre løsninger til RFID systemer.

Efter adskillige forsøg på at integrere traditionel kryptografiske primitiver ind i små, indlejrede og ekstremt ressourcebegrænsede enheder var resultaterne meget utilfredsstillende. Som følge deraf startede en ny gren af kryptografi, kendt som *Letvægts-Kryptografi*, der henvender sig til disse små, allestedsnærværende enheder.

Denne afhandling præsenterer et omfattende teknisk perspektiv til letvægtskryptografi, foreslår en klassifikation og undersøger dens forskellige forgreninger ved at give eksempler på hver af dem. Vi vælger to af disse forgreninger: ultra-lightweight cryptography og symmetric-key cryptography og foreslår en kryptografisk primitiv for hver af dem. For symmetric-key cryptography foreslår vi et stream cipher med et areal, der hører til blandt de mindste i den udgivne litteratur og som sigter mod implementation i printede elektroniske RFID-mærker.

Derefter sammenligner vi forskellige kryptografiske primitiver baseret på deres nøgleparametre: produktion, areal, effektforbrug og sikkerhedsniveau. Vores hovedproblem er integrerbarheden af de valgte primitiver ind i eksisterende passive RFID-mærker. For at gå endnu længere end en sammenligning af forskellige parametre, foreslår vi derfor en måleenhed, der kombinerer alle disse karakteristika. Denne måleenhed har desuden fordelen af at være definerbar, afhængig af kravene til en integrator til en bestemt applikation.

Til sidst konkluderer vi, at forskning i at finde robuste kryptografiske primitiver inden for letvægts-kryptografi stadig har nogle gode dage foran sig og problemet med at levere et sikkert kryptografisk system til printede RFIDmærker forbliver et åbent forskningsområde.

**Nøgleord:** Letvægts-Kryptografi, RFID, Sikkerhed, Printet Elektronik, Stream Cipher, Sammenligningsmåleenhed.

Thanks to Karsten Fyhn for the translation and Eva Hansen for the proof-reading.

# Acknowledgements

My first thought goes to my current supervisor. While I was facing an NP-hard problem<sup>1</sup> for almost two years and started to lose hope, Torben Larsen gave me a hand to solve it, despite the fact that he was already overwhelmed with work. If I graduate today, this is mainly thanks to him, and I can never thank him enough for that. Torben, **THANK YOU!**

On the other side of the World – down under, as they say – stands another brilliant researcher who hosted me, inspired me, and guided me during the six months I spent with him. We had passionate discussions, he spent countless hours to help me, and he always pushed me to give the best ... and then a bit more. Damith Ranasinghe was my supervisor during the most productive period of my thesis and more than a mentor, he became a friend. Damith, **THANK YOU!**

I want to thank all the colleagues who helped me in different aspects of my thesis including Yannick Le Moullec, Mehmood-Ur-Rehman Awan, Jan Mikkelsen, Joachim Rodrigues (from Lund University), Olav Geil, and Hans Hüttel.

I want to thank all the colleagues who did not help at all with my thesis... but instead brought me so much more. Among the superheroes, you can find Jose Gutierrez, Michael Jensen, Tahir Riaz, Jens Myrup Pedersen, Carlo Galiotto, Bilge Kartal, Carrie Peterson, Alexandre Fleury, Patrick Lemmonier, Guillaume Monghal, Ruben Grigoryan, Pawel Pankiewicz, Karsten Fyhn and many more... but I promised my thesis will be shorter than 200 pages.

I do not forget to thanks Dorthe Sparre and Eva Hansen for their time, kindness and permanent support.

<sup>&</sup>lt;sup>1</sup>NP-hard stands for *Non Polynomial-hard* and refers to a problem one cannot solve in a lifetime.

I also take the occasion to thank all my international friends who were the elements of my surrogate family here in Aalborg and made time fly. A special thanks to my closest friends Karsten (Germany), Ubaldo (Mexico), Luca (Italy), Jette (Denmark), Hernan (Chile), Manuel (Portugal) and the two who convinced me to start a Ph.D: João Figueiras (Portugal) and Gian Paolo Perrucci (Italy).

Last but not least, a big thanks to my girlfriend Agnieszka for her permanent support, and to my family back in France who made this study abroad possible.

MATHIEU DAVID

10

## Preface

A large part of the content of this thesis has already been published (or submitted) in different papers. Following is the list of these publications, together with the contribution of the author to the respective papers, and how they have been reused in this thesis.

#### **Conference** papers

- **M. David** and N.R. Prasad. Providing strong security and high privacy in low-cost rfid networks. *Security and Privacy in Mobile Information and Communication Systems*, Turin, Italy, June 3-5, 2009, pages 172–179 [41].

- This paper is presented in Chapter 3. The author of this thesis is the main originator and contributor to the paper. He has conducted the major part of the analysis, has designed the security protocol, and has analyzed and concluded on the achieved results. In Chapter 3, Section 3.1.1 to Section 3.5 are directly copied from the paper. The remaining sections of that chapter are new in this thesis. Additionally, Table 3.1 has been updated in this thesis to match with the latest published literature.

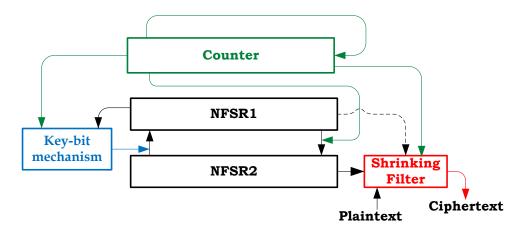

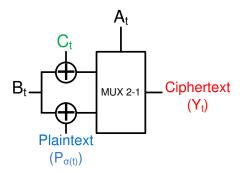

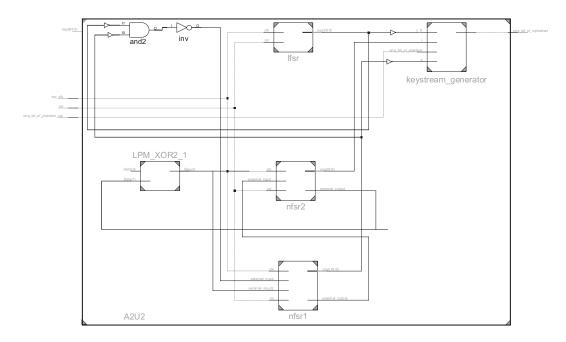

- M. David, D.C. Ranasinghe, and T. Larsen. A2U2: A stream cipher for printed electronics RFID tags. *RFID 2011, the fifth IEEE International Conference on RFID*, Orlando, Florida, USA, April 12-14, 2011, pages 176–183 [42].

- ♦ This paper is presented in Chapter 4. The author of this thesis is the main originator and contributor to the paper. He has conducted the major part of the analysis and the design of the cipher, and has

analyzed and concluded on the achieved results. He has written the original draft of the paper and has corrected it several times, based on the co-authors reviews. In Chapter 4, Section 4.1 to Section 4.5 are directly copied from the paper. Section 4.6 and Section 4.8 are new material in this thesis.

- M. A. Abdelraheem, J. Borghoff, E. Zenner and **M. David**. Cryptanalysis of the lightweight cipher A2U2. *Thirteen IMA International Conference on Cryptography and Coding*, Oxford, UK, accepted for publication in LNCS, 16 pages, December 12-15, 2011.

- This paper is included in Appendix A. The author of this thesis initiated the cooperation on the paper, and provided information on the background and details of the A2U2 cipher. He wrote the section on "Necessary changes and possible improvements" to the cipher based on the co-authors input, which identified the three main concerns. In Chapter 4, Section 4.7.2 is directly copied from the paper, while Section 4.7.1 is a summary of the main attacks presented in the paper.

#### Journal (submitted)

- D.C. Ranasinghe, **M. David** and Q. Z. Sheng. Lightweight Cryptography: Classification and Evaluation, *submitted in January 2011 to the Journal of Cryptology*, 50 pages.

- This paper is presented in Chapters 1, 2, 5, and 6. The author of this thesis wrote the first draft of the paper, based on a previous (unpublished) report written by Damith C. Ranasinghe, and updated the numbers in Section 2.5, based on the most recent published literature. He has conducted the power consumption analysis and written Section 5.1.4. He is the originator of the metric proposed in the paper and has written the Section 5.3.1. In Chapter 1, the Introduction and Problem Statement sections are copied from the paper. The remaining part of that chapter is new material in this thesis. In Chapter 2, the four sections are copied from the paper. In Section 2.5, some numbers have been updated since the submitted version of the paper, including some cryptanalysis results of KTANTAN[44]. The

section concerning PRINTcipher [96] is new material. In Chapter 5, the four section are copied from the paper, but have been updated accordingly to the inclusion of A2U2 [42] and PRINTcipher [96] in the several comparisons. Finally, in Chapter 6, some of the paragraphs are copied from the paper, while the remaining paragraphs are written for this thesis.

# Contents

### Contents

| 1 | Inti | roduct | ion                                                  | 19 |

|---|------|--------|------------------------------------------------------|----|

|   | 1.1  | Proble | em Statement                                         | 20 |

|   | 1.2  | Scient | tific Approach                                       | 21 |

|   | 1.3  | Scient | tific Challenge                                      | 23 |

|   | 1.4  | Contr  | ibutions                                             | 23 |

|   | 1.5  | Thesi  | s Organization                                       | 24 |

|   | 1.6  | Thesi  | s Delimitation                                       | 25 |

| 2 | Bac  | kgrou  | and and Challenges                                   | 27 |

|   | 2.1  | Intro  | luction                                              | 27 |

|   |      | 2.1.1  | RFID Technology                                      | 27 |

|   |      | 2.1.2  | Single Crystal Silicon Integrated Circuit based Tags | 29 |

|   |      | 2.1.3  | Printed Semiconductor Tags                           | 30 |

|   |      | 2.1.4  | Why is Providing Security a Challenge?               | 31 |

|   | 2.2  | Classi | ification                                            | 33 |

|   | 2.3  | Physi  | cal Primitives                                       | 36 |

|   |      | 2.3.1  | Physical One-Way Functions                           | 37 |

|   |      | 2.3.2  | Physical Layer Primitives                            | 42 |

|   | 2.4  | Ultra  | -Lightweight Protocols                               | 43 |

|   |      | 2.4.1  | One-Time Pads                                        | 43 |

|   |      | 2.4.2  | One-Time Pads: Pseudonyms                            | 44 |

|   |      | 2.4.3  | Re-encryption                                        | 45 |

|   |      | 2.4.4  | Passwords: Exploiting the KILL Password              | 45 |

|   | 2.5  | Comp   | utational Primitives                                 | 46 |

|   |      | 2.5.1  | Keyed Hash Functions (MAC)                           | 46 |

|   |      | 2.5.2  | Symmetric Key Primitives: Block Ciphers              | 50 |

14

|   |      | 2.5.3 Symmetric Key Primitives: Stream Ciphers       | 62 |

|---|------|------------------------------------------------------|----|

|   | 2.6  | Conclusion                                           | 66 |

| 3 | Ultı | a-Lightweight Primitive for passive RFID Tags        | 67 |

|   | 3.1  | Introduction                                         | 67 |

|   |      | 3.1.1 Components of networking security              | 68 |

|   |      | 3.1.2 Privacy threats                                | 68 |

|   | 3.2  | Related work                                         | 70 |

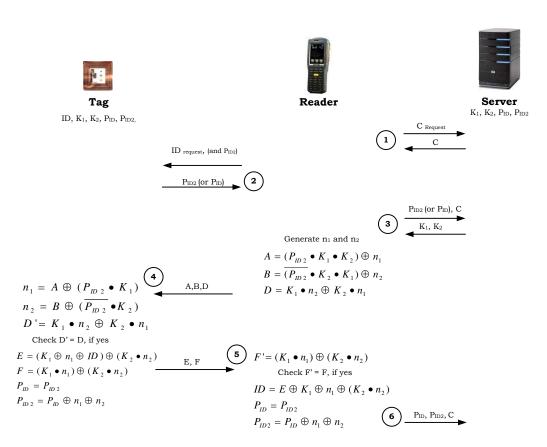

|   | 3.3  | Proposed Solution                                    | 71 |

|   |      | 3.3.1 A few assumptions                              | 71 |

|   | 3.4  | The Protocol                                         | 71 |

|   | 3.5  | Security and Privacy Evaluation                      | 73 |

|   | 3.6  | Cryptanalysis of the proposed protocol               | 75 |

|   | 3.7  | Discussion                                           | 76 |

|   | 3.8  | Conclusion                                           | 76 |

| 4 | A2U  | 2: A Stream Cipher for Printed Electronics RFID Tags | 77 |

|   | 4.1  | Introduction                                         | 77 |

|   | 4.2  |                                                      | 80 |

|   | 4.3  |                                                      | 81 |

|   |      |                                                      | 82 |

|   |      | -                                                    | 82 |

|   |      | 4.3.3 Exploit the Confusion and Diffusion Concepts 8 | 83 |

|   |      |                                                      | 84 |

|   |      |                                                      | 85 |

|   | 4.4  | -                                                    | 86 |

|   |      |                                                      | 86 |

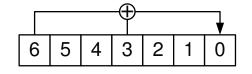

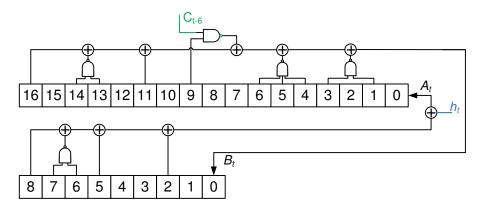

|   |      | 4.4.2 The Two Nonlinear Registers                    | 87 |

|   |      | 4.4.3 Nonlinear Boolean Function Design              | 88 |

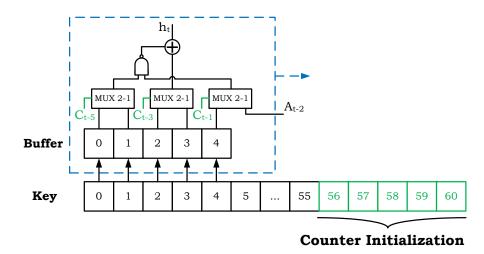

|   |      | 4.4.4 The Irregular Key-bit Mechanism                | 88 |

|   |      |                                                      | 89 |

|   | 4.5  |                                                      | 91 |

|   |      |                                                      | 91 |

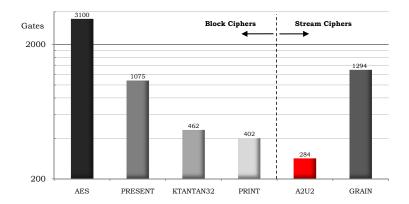

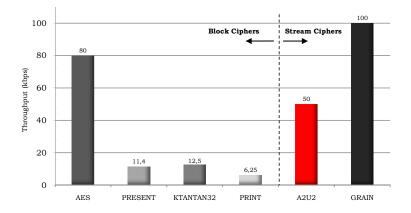

|   |      | 4.5.2 Throughput Evaluation                          | 93 |

|   |      |                                                      | 94 |

|   | 4.6  | -                                                    | 95 |

|   | 4.7  | -                                                    | 97 |

|   |      |                                                      | 97 |

|      |        | 4.7.2      | Necessary changes & Possible improvements                  | 98  |

|------|--------|------------|------------------------------------------------------------|-----|

|      | 4.8    | Concl      | usions                                                     | 100 |

| 5    | Con    | nparis     | on of Lightweight Cryptosystems                            | 101 |

|      | 5.1    | -<br>Primi | tives Comparisons                                          | 101 |

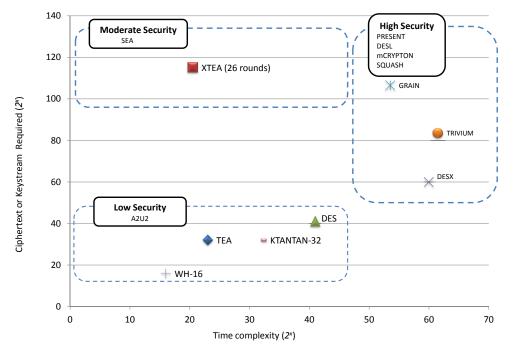

|      |        | 5.1.1      | Comparison Overview                                        |     |

|      |        | 5.1.2      | Security                                                   | 106 |

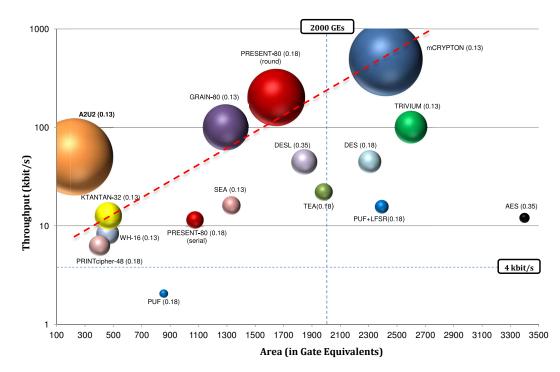

|      |        | 5.1.3      | Cost (Area) and Performance                                | 107 |

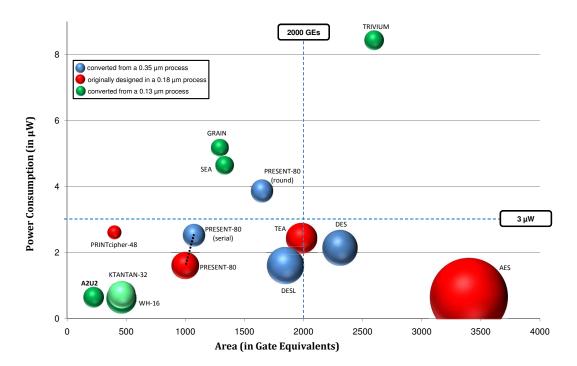

|      |        | 5.1.4      | Power Consumption                                          | 108 |

|      | 5.2    | Discu      | $\mathbf{ssions}$                                          | 111 |

|      |        | 5.2.1      | Single Crystal Silicon integrated Circuit based Tags       | 114 |

|      |        | 5.2.2      | Printed Semiconductor Tags                                 | 114 |

|      | 5.3    | Perfor     | mance Coupling Measure                                     | 115 |

|      |        | 5.3.1      | Weighted Normalized Cost Power and Throughput (WOOP        | Г)  |

|      |        |            | Metric                                                     |     |

|      |        | 5.3.2      | Primitive Selection for Single Crystal Silicon IC Tags: An |     |

|      |        |            | Example                                                    | 119 |

|      | 5.4    | Concl      | usion                                                      | 120 |

| •    | a      |            |                                                            | 101 |

| 6    | Con    | clusio     | ons                                                        | 121 |

| Bi   | ibliog | graphy     | <b>y</b>                                                   | 123 |

| Li   | st of  | Figur      | es                                                         | 133 |

| Li   | st of  | Table      | s                                                          | 134 |

| 1.11 | 50 01  | Iubic      | 5                                                          | 101 |

| In   | dex    |            |                                                            | 135 |

| Α    | Det    | ailed (    | Cryptanalysis of A2U2                                      | 137 |

|      | A.1    | A Cho      | osen Plaintext Attack                                      | 137 |

|      |        | A.1.1      | Disproving the Chai/Fan/Gong Attack                        | 137 |

|      |        | A.1.2      | A Leak in the Output Function                              | 138 |

|      |        | A.1.3      | The Attack                                                 | 139 |

|      | A.2    | Guess      | -and-Determine attack                                      | 140 |

|      | A.3    | Targe      | ting the low number of initialisation rounds               | 143 |

|      |        | A.3.1      | Recovering the 5-bit counter key                           | 144 |

|      |        | A.3.2      | Recovering the master key bits                             | 144 |

|      | A.4    | Explo      | iting the noisy keystream                                  | 145 |

#### CONTENTS

| A.5 Conclusion |

|----------------|

|----------------|

## Chapter 1

# Introduction

"Learning **seriously** affects your brain." – Aalborg University

key goal in the development of security mechanism for extremely low cost platforms, such as passive RFID tags, is the design of low cost security primitives that consume very little power (in the order of few micro Watts) and have adequate performance (throughputs of hundreds of kilobits per second). Their aim is to support various end-user applications such as product brand protection and authentication, disposable mass transit fare card ticketing, consumer retail product promotions, and embedded product intelligence [100]. For example, in a pharmaceutical supply chain, various parties may want to authenticate a vial of medicine or only allow authorized parties to access a bottle's globally unique identifier.

Most modern cryptographic mechanisms cannot be applied directly to low cost platforms, such as RFID technology, because their design goals do not meet the platform and regulation specific limitations offered by such innovative technologies [138, 137]. Moreover, encryption standards such as AES (Advanced Encryption Standard) [36], RSA (Rivest, Shamir and Adleman) [142], and Elliptic Curve Cryptography [124, 98] use larger and larger key sizes, supported by increasing computational capabilities of the target hardware platforms to achieve higher levels of security. However, modern pervasive technologies (e.g. low cost RFID) have limited memory and no processing capability. They are instead application specific integrated circuits (ASICs), whose operational aspects are further constrained by environmental factors, such as indeterministic power loss, and regulations, which limit period of tag engagement and available bandwidth [51, 83]. Consequently, an alternative approach is demanded by low cost platforms such as passive RFID technology. The resource constraints of the technology dictate the rules of security algorithm designs that must have an hardware implementation cost as low as possible, while ensuring adequate performance and security, in order to facilitate the use of mechanisms in real applications.

The attractiveness of applications enabled by low cost computing devices and the lack of secure and suitable solutions have initiated a global research effort to develop low cost cryptographic primitives and implementations. Its objective is to meet (i) the needs of extremely resource limited platforms, (ii) the security goals of those platforms, and (iii) the end-user requirements for adequate performance. Nevertheless, the growth of mobile device platforms over the past twenty years has pushed researchers to focus their efforts on cryptographic mechanisms capable of delivering fast, low cost and low power implementations in hardware (such as A5<sup>1</sup> in GSM mobile phones). However, approaches to optimize existing primitives for small hardware implementations have failed to deliver practicable solution for low cost devices [55, 54, 72]. This forced researchers to re-think the design of security primitives as opposed to optimizing existing designs [20, 44, 42, 96]. This view is clearly evident in recent European projects such as New European Schemes for Signatures, Integrity, and Encryption (NESSIE) [126], and ECRYPT Stream Cipher Project (eSTREAM) [52], as well as ECRYPT I and II (European Network of Excellence for Cryptology) [1], formulated to address the design vacuum.

#### **1.1 Problem Statement**

Given the critical importance of security for low cost pervasive technologies, an emerging array of security mechanisms often categorized under *lightweight cryptography* has sought to meet the challenge of developing fast and efficient security mechanisms for resource constrained environments. Many primitives and low cost implementations have been proposed recently [158, 66, 144, 105, 53]. Although the majority are presented as lightweight cryptographic primitives, they are based on various design goals and requirements that do not

$<sup>^{1}</sup>$ A5/1 (and A5/2) is a stream cipher used to encrypt data in the GSM cellular telephone standard.

necessarily satisfy those of extremely low cost platforms (e.g. DES [105], TRIV-IUM [53] and mCRYPTON [112] implementations are too large for passive RFID tags). Furthermore, the claim that a primitive is lightweight seems to be based entirely on a personal perspective rather than a quantitative analysis. Unfortunately, a clear view of what constitute a lightweight primitive or a coherent discourse in this area is lacking in the literature.

Moreover, reporting of developments in lightweight cryptography is tangled in a web of variables such as:

- levels of security,

- fabrication process parameters and technology used in the implementation (area),

- variations in power consumption measurements (power),

- clock rates at which the primitives are run (throughput).

Consequently, it is becoming increasingly difficult to compare their suitability for practical implementation in resource constrained platforms.

To the best of the authors knowledge, [50] is the only survey of lightweight cryptographic primitives that has attempted to compare various developments in this area. Unfortunately, a detailed comparison that is agnostic to numerous variations in the cipher design and implementation, as well as a careful consideration of a primitive's suitability for resource constrained devices is not presented. In addition, cryptography being heavily embedded in the discipline of pure mathematics, this survey has tended to exclude developments in other multidisciplinary areas capable of delivering security to extremely low cost devices. This is indeed the case with Physically Unclonable Functions [114, 62].

#### **1.2 Scientific Approach**

This thesis is written from an engineering perspective, where a strong emphasis is put on the integrability of a primitive into a real passive RFID tag. This approach is more practical rather than purely mathematical. It is a deliberate choice made by the author, accordingly to his educational background in telecommunication and networks. This thesis is articulated around a classical research method in three steps: analysis, proposition, and comparison, explained as follows:

- **Analysis** The mandatory first step into any new research topic is a thorough analysis of the State-of-the-Art (SoA) within the field. Lightweight cryptography has attracted a growing number of researchers for the past ten years due to the emergence of ubiquitous mobile devices and mobile networks that require embedded security. Here, the author focuses on lightweight cryptography applied to passive RFID tags (i.e. cryptographic primitives that can be implemented in less than 2000 gates). A classification of the primitives in different categories is introduced to evaluate where some contribution would have the most impact and/or fill a gap.

- **Proposition** Based on the analysis of the State-of-the-Art, the author identify two areas where a contribution would have some significance. First, with the design of an ultra-lightweight security primitive which, initially, appears to be the easiest entry to the world of cryptographic primitives design. Second, the author proceeds with a more elaborate security primitive by designing the smallest stream cipher possible to be implemented on an emerging and challenging technology: printed electronics RFID tags.

- **Comparison** A strong way of evaluating a research work is most likely to compare it with the existing published literature. This is the approach taken here with both of the proposed cryptographic primitives compared to similar works. The comparison methods are different for each proposed primitives. The ultra-lightweight primitive (Chapter 3) is compared in terms of (im)possible attacks, since not many proposals provide an implementation of their primitive. The second primitive, A2U2 (Chapter 4), is compared in terms of implementation performances, since the cryptanalysis of such ciphers usually can take up to several months or years. Additionally, the author go beyond the classical comparison scheme and propose a comparison metric to evaluate the different ciphers (see section 1.4). In order to design this metric, the ciphers are evaluated from a different perspective, from the side of an integrator who needs to implement a security protocol into a given RFID application.

#### **1.3 Scientific Challenge**

The main challenge raised in this thesis is to develop a realisticly secure cryptosystem for printed electronics RFID tags. By realisticly secure, the author means that the cryptosystem should be secure relatively to any given application of printed electronics RFID tags. From a mathematician point of view, a cryptosystem is not secure if it can be broken in a polynomial amount of time. From an engineering point of view, a cryptosystem is secure if it remains unbroken for the entire lifetime of a given application. For example, if a movie ticket carrying an RFID tag is secure for five years, this can be considered as sufficiently secure (given that revealing its secret information would only impact this sole ticket).

### **1.4 Contributions**

The key contributions of the author are summarized as the following:

- A definition and a classification of lightweight cryptographic primitives that incorporates recent developments in the area of cryptography for extremely resource limited platforms such as passive RFID technologies. The aim is to propose a common foundation for cryptographers working in the area of developing lightweight cryptographic primitives. The classification is comprehensive, meaning that it includes the multidisciplinary approaches taken by researchers to develop new solutions to the challenging problem of providing security to devices with limited resources. The classification is illustrated using existing cryptographic primitives published as being suitable for extremely resource limited devices such as passive RFID tags.

- The designof an ultra-lightweight primitive to improve on the work carried out previously by the research community. The aim of this protocol is to improve on the security issues (tracking, mutual authentication) of similar previously published works, while at the same time attempting to reduce the computational effort on the tag side.

- **The design of a tiny stream cipher** for implementation in printed electronics RFID tags, filling two open gaps in the literature: (i) a tiny stream cipher implementable on less than 1,000 gates, and (ii) a cipher small

enough to meet the heavy constraints of integration in printed electronics.

- The evaluation of the surveyed cryptographic primitives along four dimensions, (i) cost of implementation in hardware, (ii) performance in terms of throughput, (iii) performance in terms of power consumption and, (iv) the level of security each primitive is capable of providing.

- The development of the Weighted nOrmalised cOst Power and Throughput (WOOPT) metric for comparing and contrasting various lightweight cryptographic primitives identified through the preceding classification. The proposed metric incorporates multiple diverged characteristics of lightweight primitives, in particular their cost, power consumption and performance to evaluate their suitability for practical applications in resource constraint devices. The usefulness of the WOOPT metric is demonstrated to collectively assess the lightweight cryptographic primitives and help the selection of a primitive to meet application specific requirements.

#### **1.5 Thesis Organization**

The aim of this thesis is to assemble the work published (or submitted) during the entire period of the PhD studies into a monograph in order to avoid the abrupt topic switches of a collection of paper and to give an improved reading experience. In this way, Chapter 2 to Chapter 5 regroup the peer-reviewed material and is slightly adapted to match the general flow of the thesis. In the introduction of these chapters, the respective publication(s) is mentioned to the reader. Besides Chapter 1, which introduces the work achieved in the thesis, the remainder of the thesis is organized as follows:

**Chapter 2** briefly introduces the RFID technology and describes the platformspecific requirements for lightweight cryptographic primitives. It describes the development of the emerging area of lightweight cryptography for resource limited environments. It proposes a classification of lightweight cryptographic primitives. Finally, it expounds the research outcomes under the proposed classification reported as being capable of providing security services such as authentication, confidentiality and anonymity for resource limited platforms. **Paper used:** Lightweight Cryptography: Classification and Evaluation.

- **Chapter 3** presents an ultra-lightweight primitive design for passive RFID tags. A short introduction and background related to the specific area is given. The primitive is then compared to the existing related works. Additionally, some conclusions are drawn by taking into account the published cryptanalysis of the protocol. **Paper used:** *Providing strong security and high privacy in low-cost rfid networks*.

- Chapter 4 describes a stream cipher for printed electronics RFID tags. Here again, a comprehensive introduction and related works are presented in relation to the specific area. This is followed by the design criteria, the analysis of the cipher, and the results of a cryptanalysis of the cipher. The author propose some possible improvements to fix the cipher against the attacks described in the cryptanalysis. Paper used: A2U2: A stream cipher for printed electronics RFID tags and Cryptanalysis of the lightweight cipher A2U2.

- Chapter 5 compares cryptographic primitives and evaluates their merits, weaknesses and suitability for platforms such as low cost passive RFID tags. It extracts the primitives that can be categorized as being lightweight from those that we have evaluated based on the requirements framework presented in Chapter 2. Finally, it presents a metric for evaluating the goodness of a cryptographic primitive as a lightweight primitive based on coupling cost, throughput and power consumption. Paper used: Lightweight Cryptography: Classification and Evaluation.

- **Chapter 6** summarizes the work achieved in this thesis, provides concluding remarks and opens to further research perspectives. **Paper used:** *Lightweight Cryptography: Classification and Evaluation.*

#### **1.6 Thesis Delimitation**

As its title suggests, this thesis is almost exclusively focused on lightweight cryptographic primitives for passive RFID tags. It covers the various aspects and branches of lightweight cryptography, as presented in the proposed classification (see Section 2.2), and the keys requirements of integration in passive RFID tags (see Section 2.1.4).

However, this thesis does not go into much details regarding the operating process of the RFID technology itself, the RFID standards, nor the different types of active or passive attacks applied to RFID systems. The purpose is to focus principally on the contributions brought by the author to the scientific community, and avoid rewriting on topics widely covered in the literature, and where it would not add any relevant information. Furthermore, the author believes that the readers interested in this thesis already have a background in RFID, and therefore already know its main caracteristics. If necessary, it exists in the published literature a large amount of books and theses that describe all these different aspects of the technology. Among others, [57] presents a complete description of the RFID technology, [30] presents the issues and challenges of RFID cryptography, [128] presents the various type of attacks on RFID systems as well as the popular EPC standard. Additionally, [11] is an exhaustive repository of the existing published work on security and privacy for RFID systems.

## **Chapter 2**

# **Background and Challenges**

"Lots of people working in cryptography have no deep concern with real application issues. They are trying to discover things clever enough to write papers about." - Whitfield Diffie.

## Foreword

his chapter is a selected part of the journal paper Lightweight Cryptography: Classification and Evaluation, written in collaboration with Dr. D. Ranasinghe and Dr. Q. Sheng, and submitted in January 2011 to the Journal of Cryptology<sup>1</sup>.

## 2.1 Introduction

In this section we summarize the very low cost computing platforms, more specifically Radio Frequency Identification (RFID) technology, that are set to become ubiquitous over the coming years. Then we discuss the challenges of providing a layer of security to such platforms.

#### 2.1.1 **RFID** Technology

Radio frequency identification (RFID) regroups all the objects equipped with micro electronics that can process data automatically [33], but in this thesis, we consider exclusively passive low-cost RFID tags having the caracteristics presented in Table 2.1. A simple illustration of the concept of an RFID system

<sup>&</sup>lt;sup>1</sup>At the time of delivering this thesis, the paper is still under review.

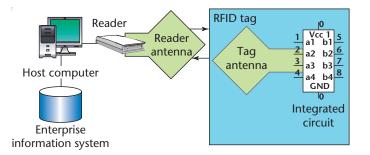

Figure 2.1: Illustration of an RFID system [133].

is provided in Figure 2.1. Here, a transmitter of interrogation signals, which is contained within an interrogator, communicates via electromagnetic waves with an electronically coded label to elicit from the label a reply signal containing useful data, characteristic of the object to which the label is attached. The reply signal is detected by a receiver in the interrogator, and made available to a control system.

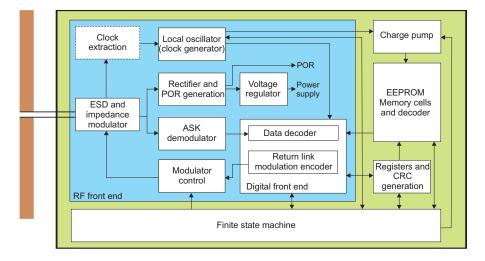

Figure 2.2: Block diagram of a passive UHF/HF RFID label [57].

One of the inhibitors to wide-scale adoption of RFID technology is the cost of a label [78]. The primary cost of an RFID label, which includes both an Integrated Circuit (IC) or the silicon chip and the antenna, is the cost of the silicon chip. Low cost RFID refers to an RFID system based on inexpensive RFID tags with the smallest possible implementation of the label IC. Low cost RFID labels are passive transponders since having an on-board battery would add significantly to the cost of the label. The most common operating principle of labels in the category of passive technology is that of RF backscatter or load modulation [30], in which a powering signal or communication carrier supplies power or command signals via an HF or UHF link. However, the circuits within the label operate at the carrier frequency or at a lower frequency. They reply via sidebands generated by modulation, within the label, of a portion of the powering carrier. This approach combines the benefits of relatively good propagation of signals at HF and UHF, and the low power operation of microcircuits at RF or lower. Powering at UHF is employed when a longer interrogation range (several meters) is required. HF powering is employed when electromagnetic fields, which exhibit good material penetration and sharp spatial field confinement, is required or sometimes when a very low cost RFID system implementation is desired [48, 76].

Figure 2.2 is an illustration of a typical low cost transponder [174]. The block diagram of an HF and a UHF chip varies little. In a UHF chip there is a dedicated low power oscillator, while in an HF chip the clock signal is derived from the received carrier by dividing down the carrier in steps. Low cost RFID chips generally have limited memory, typically around 512 bits or less and have no computing hardware except a simple finite state machine for logical functionality [57].

#### 2.1.2 Single Crystal Silicon Integrated Circuit based Tags

Until recently, RFID application specific integrated circuits have been fabricated on single crystal silicon. Although advanced technologies such as 0.13 micron, 0.15 micron or 0.16 micron have been used since 2008, 0.18 micron has been the popular process in widespread usage in low cost RFID manufacture since 2006 [57, 78]. The predominant reason for using older processes has been a strategy for constraining the cost of the RFID IC critical to supporting business cases for RFID enabled applications. Instead, older fabrication processes where the capital cost of the facilities have depreciated over at least 4 to 5 years – currently the 0.18 micron process – proves to be the most cost-effective choice for low cost RFID [78]. It is expected that this situation will eventually change and manufacturer will migrate to 0.15 micron and then eventually to 0.13 micron processes in years to come [40].

In 2005, it was estimated that no more than 2,000 gates were available for security in RFID tags [90]. Moore's Law meant that we are able to deliver more gates per unit area of silicon since then. However, continued end-user demands

for cheaper tags to support business cases of novel RFID applications, that will result in mass utilization of RFID tags, imply that the several thousand gates limit is still a reality. Furthermore, newer and smaller feature size fabrication processes are not used for low cost RFID devices [40].

#### 2.1.3 Printed Semiconductor Tags

In recent years, there has been a significant level of interest in printed electronics since it is believed to realize substantially lower cost electronic systems than those available from conventional single crystal integrated circuit (IC) chip based circuit fabrication [77]. Hence, printed electronics are often conceived as a feasible way to solve the high cost problem limiting widespread deployment of RFID tags through dropping the manufacturing cost per tag to the sub one cent level when processes and manufacturing plant is gradually up-scaled to high volume production [77]. Manufacturers of printed RFID are projecting early selling prices of only a few cents in the billions of RFID labels and some foresee sub one cent pricing in much higher volumes [86]. Currently two different approaches are used to develop printed semiconductor tags, namely Silicon Ink Printed Electronics and Organic Printed Electronics [31].

There are a few companies dedicating their R&D and commercialization resources to the application of organic printed RFID tags. One of the leading companies in this area is PolyIC (see *http://www.polyic.com*). In 2007, the company presented the first organic printed RFID tag working at the high frequency range of 13.56 MHz with a simple circuit and certainly low functionality [65]. It is only supposed to be used for brand protection and ticketing. Organic printed tags working in the LF band was obtained before the achievement of HF band tags. However, because the LF antenna element size is relatively larger than that of HF antenna, the LF band tags are not applied as widely as the HF band tags. Philips also reported that a 64-bit tag composed of 1940 transistors is obtained based on organic printed electronics. The tag's data rate is 150 bits per second [87]. This figure is much lower than that achievable with printed silicon ink CMOS technology, wherein a tag communication data rate of 106 kbps is believed to be achievable.

There are very few commercial players in the area of silicon ink printed semiconductor, currently exemplified by Kovio Inc. (see *http://www.kovio.com*). While silicon ink technologies have clear advantages over organic semiconductors, silicon ink technology shares with organic transistor technology the disadvantages of limited transistor numbers. Consequently, there is still an impact and limitation on the complexity of protocols. Somewhere around 2000 transistors are believed to be the comfortable upper boundary zone for printed semiconductor tag circuits today as demanded by yields from printing processes and physical feature sizes [31].

#### 2.1.4 Why is Providing Security a Challenge?

There are several reasons explaining why many of the currently available security primitives are unsuitable for integration into RFID tags:

- The cost of implementing algorithms on hardware is too high to be implemented on a cost constrained RFID Integrated Circuit (IC) where the price of tags, in large volumes, of around 8 US cents [30] is still considered too expensive for mass deployments.

- Relative power consumption by the cryptographic hardware modules is too high for RFID labels that are passive (not self-powered) and typically exceeds that required to operate the tag or read data from a tag's memory [57].

- RFID transponders have limited logic functionality (limited to one or a few state machines) and limited memory (limited to a few kilobits) with no microprocessor for complex operations [57].

- Large key sizes and the resulting ciphertext sizes are generally unsuitable for narrow band communication systems where transmission of significant amount of data directly affects the performance of the system [48].

- The security protocol must be robust against sudden power loss, for example due to the mobility of tagged objects or multipath effects [48].

- Regulatory limitations imply that times in the order of milliseconds are available to complete a secure transaction with a low cost RFID tags [51].

In this thesis, our focus is on mechanisms for addressing the problem of providing secure primitives to extremely resource constrained environments such

|               |                                                                                                                                                                         | -                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|               | Conventional Silicon passive RFID tags                                                                                                                                  | Printed ink passive RFID tags [77]               |

| Gates         | 2000 available for a security primitive [90]                                                                                                                            | Less than 200 available for a security primitive |

| Available     | Most likely an EPC (Electronic Product Code) of 96 – 256 (see                                                                                                           | Enough bits (96-256) to store a                  |

| memory        | EPCglobal's tag data specification standard [51]) and several                                                                                                           | unique identifier. Additional bits               |

|               | hundred bits of user memory. Read-Write memory. Although                                                                                                                | may need to be implemented as                    |

|               | further steps to reduce costs imply that we are likely to only see                                                                                                      | ROM.                                             |

|               | Read-Only memory.                                                                                                                                                       |                                                  |

| Power         | 10s of microwatts, and should not exceed that required for                                                                                                              | Few microwatts.                                  |

| consumption   | EEPROM read operation, so the tag read range requirements can                                                                                                           |                                                  |

|               | be maintained. Currently EEPROM read operations require                                                                                                                 |                                                  |

|               | around 20-30 µW [108].                                                                                                                                                  |                                                  |

| Performance   | In North America it is conceivable to allow a tag to expend around                                                                                                      | Around 100 kbit/s will not be able               |

|               | 400,000 clock cycles (based on a 1 MHz internal clock) during a 400                                                                                                     | to support complex anti-collision                |

|               | millisecond period (time constraint imposed by FCC regulations for                                                                                                      | techniques and thus may only                     |

|               | UHF frequencies) for communications. In Europe under revised EN                                                                                                         | support the reading of few labels a              |

|               | 302 208 regulations it is conceivable to allow a tag a maximum of 4                                                                                                     | second.                                          |

|               | seconds for communications. Then performance appears to be                                                                                                              |                                                  |

|               | mainly limited by user requirements and air interface protocols. Bit                                                                                                    |                                                  |

|               | rates: 40 kbps to 640 kbps (EPCglobal C1G2 protocol) Tag read                                                                                                           |                                                  |

|               | rates of $200 - 1500$ (demanded by end users).                                                                                                                          |                                                  |

| Read range    | $3\ m-10\ m$ for UHF and $200-500\ mm$ for HF operation under FCC                                                                                                       | Much reduced read ranges.                        |

|               | regulations [57, 48].                                                                                                                                                   | Currently UHF tags are not                       |

|               |                                                                                                                                                                         | possible.                                        |

| Communication | The most prevalent standard for UHF tags is the CIG2 protocol                                                                                                           | No standardized protocols suitable               |

| Protocols     | [51]. The multi-part ISO 18000 air interface standard defines                                                                                                           | for printed ink tags. New protocols              |

| used          | protocols for a number of different frequencies; LF, HF and UHF.                                                                                                        | based on the keeping their                       |

|               | ISO 18000 Part 3 Mode 1 is possibly the most prevalent standard as                                                                                                      | implementation to around 1200                    |

|               | of yet. The most commonly used HF standard, other than the $\ensuremath{\mathrm{ISO}}$                                                                                  | transistors leaving around 800                   |

|               | 18000, is ISO 14443 (types A and B).                                                                                                                                    | transistors or 200 gates for                     |

|               |                                                                                                                                                                         | security are needed.                             |

| Tag IC        | Currently 18,000 – 30,000 gates for a Class I Generation 2 air                                                                                                          | Around 2000 transistors (500                     |

| footprint     | interface protocol (C1G2) implementation [51]. However these are                                                                                                        | gates)                                           |

|               | expected to be simplified in the future to reduce the cost of tag ICs.                                                                                                  |                                                  |

| Available     | $32\ \mathrm{bit}\ \mathrm{random}\ \mathrm{number}\ \mathrm{generator}\ (\mathrm{as}\ \mathrm{required}\ \mathrm{by}\ \mathrm{the}\ \mathrm{C1G2}\ \mathrm{protocol})$ | None.                                            |

| Resources     |                                                                                                                                                                         |                                                  |

Table 2.1: Security related system characteristics comparison.

as passive RFID tags. These technologies provide extremely resource scarce platforms (as outlined in Table 2.1) on which to implement security primitives. In the case of low-cost RFID tags, the challenges presented are threefold:

- The cost (area of silicon used or the gate count) has to be minimal in order to ensure that the security solution will be used in low cost tags. A low cost tag demand a very limited silicon area footprint from conventional tags (typically around 2000 gates) and a more severe limitation from printed ink RFID tags (typically around 200- 300 gates is considered as threshold).

- Power consumption of the security implementation has to be reduced to its minimum since passive devices do not have an on-board battery and rely on an external electromagnetic field to supply them the required energy [57, 48].

- Performance (throughput) should be reasonable to support application and end-user requirements (read rates of over 200 tags per second) to as well as to allow their use in real protocol such as EPCglobal Class 1 Generation 2 or ISO 18000- 6C [51].

One of the goals of this thesis is to develop a classification scheme and a definition for lightweight cryptography. It is done in such a way that it is inclusive of various schools of thought pursued by researchers, in order to achieve solutions to meet the challenges of providing security to the extremely resource constrained devices.

#### 2.2 Classification

Early candidates for resource constrained devices are based on a simplification or hardware optimization (for minimum area) of well-known block ciphers: Feldhofer proposed an optimized version of AES [55] while Leander did a similar work with the DES [105]. XTEA [125] and SEA [158] are two other block ciphers suitable for embedded devices. However, none of these ciphers were designed with RFID applications as a precise target and turned out to be either slow (AES, SEA, TEA) or have a high cost (AES, DESL, TEA) as presented in Table 5.1. The first block cipher intentionally designed for resource constrained devices, PRESENT [20], is the result of the work carried out in an EU Project called UbiSec&Sens [163]. PRESENT is based on key ideas articulated by both Shannon and Rueppel, and widely used in the design of modern stream ciphers. Inspired by the techniques used in DES and AES, PRESENT's design was derived in two different flavors: a low cost implementation (1000 gates) and a high throughput implementation (200 Kbps) [144]. A later block cipher, KATAN [44], has reached an extra step with a design tailor-made for low-cost RFID tags. A rigorous analysis of power consumption (< 1 $\mu$ W), area minimization (down to 480 gates) and throughput optimization (12.5 kbps) has been achieved in its design.

However, the number of mechanisms that are suitable for extremely resource limited devices is unfortunately much fewer. For instance, none of the stream ciphers resulting from the EU project NESSIE ([126]) met the requirements of passive RFID systems, leading to a new EU project called eSTREAM ([52]), to address this gap. Among the selected candidates of eSTREAM, there are only two of particular interest for low cost RFID applications; GRAIN and TRIV-IUM [53, 66].

Other designers have tried to exploit characteristics that are unique to these resource limited platforms to develop less orthodox security mechanism. For example, the physical variation of signaling [161, 63] or the difference in the strength of the bi-directional link between the tag and the reader [74]. Finally, an interesting alternative to block and stream ciphers was proposed by Yüksel with a scalable universal hash function for RFID tags called WH-16 [174], at a very low cost (460 gates).

Nevertheless, the term *Lightweight Cryptography* is widely used to describe many optimizations of existing primitives as well as new designs. These often fail to meet the requirements of the target platforms described in Section 2.1, albeit a few (as demonstrated further in this thesis). Moreover, new developments in lightweight cryptography cannot be adequately and appropriately reflected in the broad field of cryptography, exemplified by recent developments such as physical one-way functions [161, 63] or distance implies distrust [58]. Furthermore, the term lightweight cryptography lacks an adequate articulation of its meaning in the literature.

From previous work such as [50], lightweight cryptography can be considered as a fusion of separate disciplines in cryptography, information technology, radio frequency engineering, and microelectronics. It can be considered as a novel direction in cryptography that aims to develop fast and efficient security mechanisms for extremely resource constrained environments such as passive RFID tags. In building primitives suitable for limited resource environments such as low cost RFID the designers not only have to consider the security strength of its algorithm, but also its computational complexity, its power consumption and its hardware integration size.

Lightweight Cryptography is the collection of cryptographic primitives, techniques and ciphers that can be implemented in highly resource-constrained mobile devices such as passive RFID tags. Such devices harvest energy for all their functions, communicates over band limited channels and every gate used for security is considered an additional cost that must be carefully utilized. In the lightweight context, a designer has to analyze the computational complexity of the algorithm, with respect to the demands on the hardware and other limitations of the device. There are both a direction and a constraining challenge in these limitations that guide the development of cryptography.

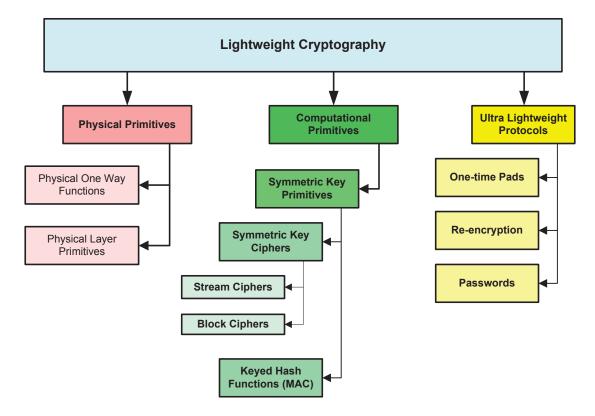

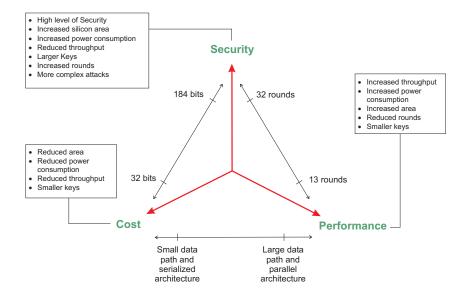

In a scheme that is built on traditional cryptography, lightweight cryptography can be classified as shown in Figure 2.3.

A distinct omission from the classification scheme is asymmetric key primitives because public key ciphers, based on the factorization of the dicrete log problems, are unsuitable for implementation in resource constrained devices because their implementation cost is too high [50]. The only public key cipher that could be considered suitable for RFID tags is NTRU [81], based on the closest vector problem [160]. It requires moderate resources and is considered to be a much faster algorithm compared to other public key ciphers such as RSA [142]. The most recent low cost implementation of NTRU presented in [9] uses 2,884 gates for encryption on a 0.13  $\mu$ m process with an architecture that consumes 1.78  $\mu$ W of power when clocked at 500 kHz. Although the cipher is considered to be faster than other public key ciphers, the implementation presented in [9] still requires 28,223 clock cycles to generate 1,169 ciphertext bits for a 256 bit plaintext message. Consequently, researchers have not focused on lightweight primitives based on asymmetric key ciphers.

The following sections illustrate the proposed classification using primitives published in the literature (briefly mentioned in this section) as being suit-

Figure 2.3: Classification of Lightweight Cryptography.

able for resource constrained devices. Furthermore, we present a brief analysis along the dimensions of (i) cost of implementation in hardware, (ii) performance in terms of throughput, (iii) power consumption and, (iv) the level of security each primitive is capable of providing, where such information is publicly available.

# 2.3 Physical Primitives

The general idea of physical primitives mainly lies in the use of biometrics for authentication. However, in RFID a physical primitive is a function that is inseparably integrated to the hardware platform and the physical layer of the device. Therefore, a physical primitive can measure an analogue phenomenon or variations in physical characteristics, which is inherent to physical systems but prohibitively difficult to duplicate, and convert it to a digital value for the purpose of precise quantification.

Such a function was first published in [64]. The Physical One-Way Functions

(POWF) described in [64] are based on accurately measuring scattering patterns of visible laser radiation, resulting from the 3D microstructures of a transparent optical medium, which is incorporated into the physical system. The output is dependent on the frequency, the angle of the laser beam entering the optical medium, and the optical characteristics of the medium.

POWF provide a means to assign a unique, tamper-resistant, and unclonable identifier to everyday objects at a relatively very low implementation cost. However, the cost of embedding optical structures onto electronic transponders and the added cost of scatter pattern measuring instruments on RFID readers implies that POWF are not a suitable low cost solution for RFID.

In addition to optical systems, there are several other physical systems on which POWF can be based. The main types are coating POWF [64], acoustic POWF [64] and silicon POWF. The primitives derived in silicon are the most relevant to the author's investigation.

#### 2.3.1 Physical One-Way Functions

The ability to construct a POWF on silicon was outlined in [64, 114, 62]. These POWFs, referred to as Integrable Physically Unclonable Functions (IPUF), map a set of challenge inputs to a set of responses, utilizing some physical characteristic of integrated circuits on silicon. There are also various IPUF, most often referred to simply as PUF (Physical Unclonable Function), such as:

- architectures termed Arbiter PUFs [161],

- XOR Arbiter PUFs [161],

- Lightweight Secure PUFs [118],

- Feed Forward Arbiter PUFs [63],

- Ring Oscillator PUFs [161].

The main concept behind PUF designs is to use process variations in wires and transistors on an IC to obtain a characteristic response from each IC, when given a certain input. Manufacturers always attempt to control process variations to a great degree. However, these variations are largely beyond their control and hence it is not possible for an adversary to fabricate identical PUF circuits. The PUF circuit is able to uniquely characterize each IC due to manufacturing variations. Thus, it may be possible to identify and authenticate each IC reliably by observing the PUF response.

The particular advantage in this technique is that secret keys no longer need to be securely stored in memory. Therefore, physical attacks such as microprobing, laser cutting and reverse engineering techniques [167], which are used to reconstruct the layout of circuits to enable adversaries to extract digital keys stored in the memory of integrated circuits are no longer effective. While various tamper-proofing methods – such as the tamper sensing technology in [101] – have been developed over the years to counter such physical attacks, they are a costly solution, especially for low cost RFID applications. Therefore, PUFs provide a powerful primitive upon which to build security mechanisms.

#### 2.3.1.1 Physically Unclonable Function Implementations

There exist a number of structures for building a PUF [82, 116, 117]. The most notable ones are the latch based structures and the ring oscillator based structures. This thesis focuses on the latch based structures because they offer architectures with the lowest power consumption as well as the lowest silicon area.

The PUF based structures are sensitive to noise, especially thermal noise, as wire latencies and gate delays depend on the operating temperature of the device [64]. This leads to reliability issues when trying to obtain consistent responses for a given input. Unreliability due to such environmental variations have been addressed in a PUF configuration given in [114], wherein a challenge response pair is created using an PUF circuit based on a differential topology. It is such a differential configuration that is considered in this thesis.

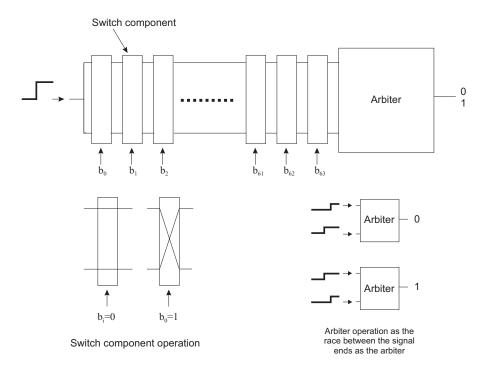

Figure 2.4 depicts the structure of a PUF circuit, which is based on the arbiterbased PUF in [114, 139]. The circuit accepts a n bit challenge  $b_0, b_1, b_2, \ldots, b_n$  to form two delay paths in  $2^n$  different configurations. In order to generate a response bit, two delay paths are excited simultaneously to allow the transitions to race against each other. The arbiter block, at the end of the delay paths, determines which rising edge arrives first and sets its output to 0 or 1. The actual implementation of arbiter-based PUFs in [114, 139] uses 64 bit challenges.

Figure 2.4: Arbiter-based PUF circuit implementation [139].

The switch component is implemented using a pair of two-to-one multiplexers. Depending on the select bit  $C_i$ , the switch either allows the signal to travel straight through or swap the delay paths. The arbiter is constructed using a simple transparent latch with an active-low enable input.

It was estimated in [114] that there is a strong enough variation between two chips fabricated from the same silicon wafer for a sufficient number of random challenges to identify billions of chips. The probability that the first measured response bits to a given challenge (set of bits) on a chip is different from the measured response for the same set of bits (challenge) on a different chip is estimated to be 23% to 40% depending on the PUF circuit architecture [114]. It has been estimated that about 800 challenge response pairs are sufficient to distinguish  $10^9$  chips with an error probability  $p_e < 10^{-10}$  [114].

Measurements of noise in PUF circuits have shown a bit error rate comprised between 8% and 25% as a result of challenges not producing predictable response in repeated measurements. This effect is due to various environmental factors such as fluctuation in operating voltage and temperature [172]. There are two possible approaches to overcome the issues related to unreliability in the context of RFID:

- 1. Using a threshold level for matching bits. For instance if 75 bits of a 100 bit response are validated, the tag is evaluated to be authentic.

- 2. Using helper bits to correct the errors in the PUF responses.

Although correcting PUF responses can be employed at the RFID reader, correcting responses is unnecessary for a simple authentication mechanism. Such a strategy will require the storage of error correcting information (for instance with the ability to correct 25 bits out of 100 bits), called a syndrome, based on coding schemes such as BCH (Bose-Chaudhuri-Hochquenghem) or index-based syndrome (IBS) coding [172]. Instead, it can be shown that, by selecting an appropriate threshold level, associated false negative can be minimized. It has been reported that using 128 challenges of 64 bits each to generate a response of 128 bits is adequate to achieve a false-positive or a false-negative probability of a few parts per billion [46].

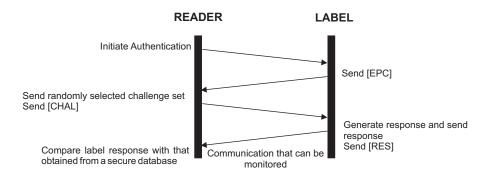

#### 2.3.1.2 Authentication: Direct Use of PUF

Simplest authentication mechanisms use PUFs responses directly in a challengeresponse protocol based authentication mechanism (as illustrated in Figure 2.5) instead of using a PUF as a mechanism to obtain a secret key. In such a scheme, a trusted party such as a product manufacturer securely stores a set of challenge response pars (CRPs) from an RFID tagged object when the object is certain to be authentic. It is these responses that are compared with those obtained from an RFID tag to establish its authenticity at a later time. To defend against man-in-the-middle attacks, CRPs are never reused.

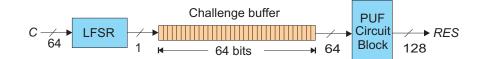

## 2.3.1.3 Authentication: PUF and Linear Feedback Shift Register (LFSR) Combination Design

The primary performance obstacle in the tag authentication protocol presented above is the excessive overhead of transmitting a large number of challenges. Based on using a 64 stage PUF circuit, each challenge consists of 64 bits. Thus to obtain a PUF response of 128 bits the reader must transmit 8,192 bits using a narrow-band communication channel.

An alternative method published in [139] is to transmit only one challenge C, where the challenge is used to initialize a linear feedback shift register. Then

Figure 2.5: Message exchange between a reader and an RFID label during an authentication process [139].

the following challenges can be generated on-tag to extract a response from the PUF circuit. This arrangement is illustrated in Figure 2.6. The additional hardware of an LFSR allows the challenge response protocol to be executed with greater efficiency.

Figure 2.6: PUF-based authentication engine design to reduce overhead [139].

#### 2.3.1.4 Evaluation

The performance of the two security schemes outlined above are presented in Table 2.2. The need to transmit a large number of challenges from the reader to the tag remains the primary obstacle with using PUFs directly, especially given that the maximum possible transmission speed from a reader to a tag in the EPC Class 1 Generation 2 (C1G2) specification is about 126 kbps given equiprobable ones and zeros [51]. As a consequence of this overhead, on average, only 15 tags can be authenticated per second.

Table 2.2: Evaluation of PUF implementations [139].

|                             | PUF (using 128 | PUF (using a LFSR to generate |

|-----------------------------|----------------|-------------------------------|

|                             | CRPs)          | 128 CRPs)                     |

| PUF area (gates)            | 856            | 1720                          |

| Effective Throughput (kbps) | 2.048          | 15.49                         |

The schemes using a LFSR (see Figure 2.6) overcomes the overhead of trans-

mitting large sets of challenges. Unlike the authentication schemes outlined previously, where a large number of challenges need to be sent to the tag, the current transmission requirement is that of a single challenge C, from which other challenges are derived. Using a smaller challenge set as well as the incorporation of an LFSR has allowed the lightweight primitive to be implemented in a low cost RFID tag while improving its performance.

The following are challenges and security issues related to PUF that need to be considered despite the attractiveness of the physical cryptographic technique:

- The arbiter favors the path to output zero since it is preset to zero and requires a setup time constraint to switch to a logic one. Fixing a small number of most significant challenge bits can compensate for this skew by effectively lengthening one delay path. The circuit layout must be designed carefully to ensure that both paths are symmetrical and arbiter responses are not biased to 0 or 1.

- Recently, model building attacks performed on software-based implementations of PUF instances have shown the use of machine learning techniques to generate accurate-enough delay-based models of PUF circuits [147]. The models developed can, with accuracies of over 95%, predict the response of PUF circuits. More significantly, the complexity of these attacks is linear or log-linear with respect to the parameters such as the number of stages in the PUF circuit [147]. However, the attack methods have not yet been verified using actual hardware implementations of PUF circuits.

It should be noted that addressing modeling attacks may require the use of more stages in the PUF circuits and/or using more challenges. Both approaches increase the cost of implementation and further reduce performance of the approach.

#### 2.3.2 Physical Layer Primitives

The Distance Implies Distrust scheme [58] is a prime example of developing a simple lightweight cryptographic primitive based on the physical layer of RFID systems. The mechanism is based on the assumption that an unauthorized reader attempting to read a tag is generally more physically distant from the tags than a legitimate reader. The latter assumption is based on the realization that a closer and more visible reader draws greater investigation by tag owners or tag bearers. Thus, the measurement of distance of a reader to a tag based on link layer measurements is proposed as a measure of trust [74]. This is a simple implementation that should be considered for applications based on proximity cards where the reading distances are indeed small to prevent malicious scanning attacks on tags or mafia fraud type attacks.

# 2.4 Ultra-Lightweight Protocols