Aalborg Universitet

### **Reliability-Oriented Design and Optimization of Photovoltaic Microinverters**

Shen, Yanfeng

DOI (link to publication from Publisher): 10.5278/vbn.phd.eng.00058

Publication date: 2018

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Shen, Y. (2018). *Reliability-Oriented Design and Optimization of Photovoltaic Microinverters*. Aalborg Universitetsforlag. https://doi.org/10.5278/vbn.phd.eng.00058

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## RELIABILITY-ORIENTED DESIGN AND OPTIMIZATION OF PHOTOVOLTAIC MICROINVERTERS

BY YANFENG SHEN

**DISSERTATION SUBMITTED 2018**

AALBORG UNIVERSITY

# Reliability-Oriented Design and Optimization of Photovoltaic Microinverters

Ph.D. Dissertation Yanfeng Shen

Dissertation submitted August 27, 2018

| Dissertation submitted:   | August 27, 2018                                                  |  |

|---------------------------|------------------------------------------------------------------|--|

| PhD supervisor:           | Prof. Frede Blaabjerg<br>Aalborg University                      |  |

| Assistant PhD supervisor: | Assoc. Prof. Huai Wang<br>Aalborg University                     |  |

| PhD committee:            | Professor MSO Stig Munk-Nielsen (chairman)<br>Aalborg University |  |

|                           | Professor Johan Drisen<br>ELECTA, K.U.                           |  |

|                           | Associate professor Robert S. Balog<br>University at Qatar       |  |

| PhD Series:               | Faculty of Engineering and Science, Aalborg University           |  |

| Department:               | Department of Energy Technology                                  |  |

| ISSN (online): 2446-1636  |                                                                  |  |

ISBN (online): 978-87-7210-252-8

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Yanfeng Shen

Printed in Denmark by Rosendahls, 2018

# Abstract

Photovoltaic (PV) energy has become increasingly popular worldwide. As an indispensable part in PV power systems, inverters play a crucial role in reducing volume, enhancing system reliability, and lowering the levelized cost of energy (LCOE). PV inverters can be classified into central, string, and micro- inverters. Notably, the market share of microinverters in residential PV systems has been increasing due to their abilities to achieve the modulelevel maximum power point tracking (MPPT), and module-level monitoring and troubleshooting. Nevertheless, there are still challenges which should be properly addressed in order to improve the essential performances of PV microinverter systems.

Firstly, the power conversion efficiency of a PV microinverter is still relatively low compared with transformerless string inverters. Particularly, it is challenging for a microinverter to maintain high efficiencies over a wide PV operating range. Therefore, new topologies and control methods are required to improve the efficiency performance of microinverter such that the advantages of PV microinverter systems in energy yields can be strengthened.

Secondly, there is a trend that a PV microinverter will be integrated into a PV module, which implies that the future microinverter should be more compact and of low physical profile. In addition, it is reported that the price per unit of electricity of a PV microinverter is higher than those of string and central inverters. Hence, the volume and cost metrics of PV microinverters need to be upgraded.

Thirdly, the panel-embedded microinverter may be inevitably heated up by the PV panel, accelerating the degradation of components. Also, due to the higher number of components used in the microinverter-based PV power systems, the reliability performance may be deteriorated. Consequently, the reliability evaluation and reliability-oriented design of PV microinverters become paramount.

To tackle those issues and thus enable a compact, low-cost-of-energy and reliable PV microinverter system, this PhD project discusses the corresponding solutions.

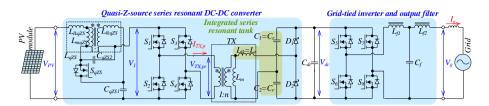

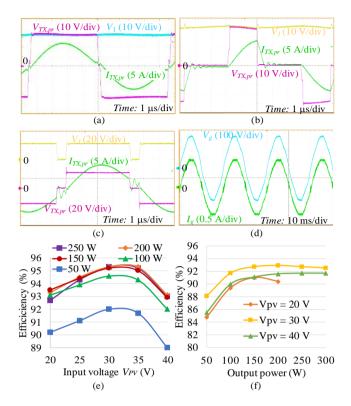

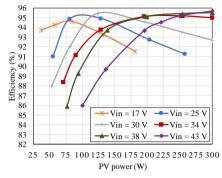

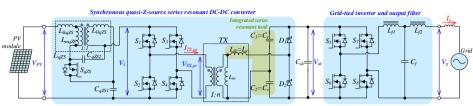

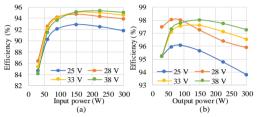

Increasing the power conversion efficiency and reducing the power losses

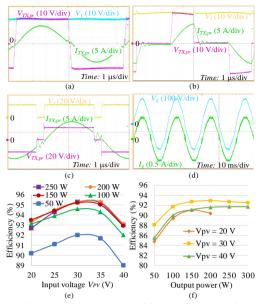

can significantly enhance the energy yield and reliability of a PV microinverter. For a two-stage single-phase PV microinverter, the DC-AC stage implemented with the classic full-bridge inverter topology can achieve a high efficiency, whereas it is challenging for the front-end DC-DC stage to maintain high efficiencies over wide PV voltage and power ranges. Therefore, this PhD thesis proposes a new isolated series resonant DC-DC converter which can cope with a wide input voltage range along with a variable DC-link voltage control. The operation principle and key characteristics of the proposed converter are analyzed. A 1-MHz 250-W PV microinverter prototype has been built and tested to verify the theoretical analysis and the feasibility of the proposed converter. Additionally, a structure-reconfigurable SRC is also discussed for the grid-connected PV microinverter systems with a wide-input voltage range and different grid voltage levels, i.e., 110/120 V and 220/230/240 V.

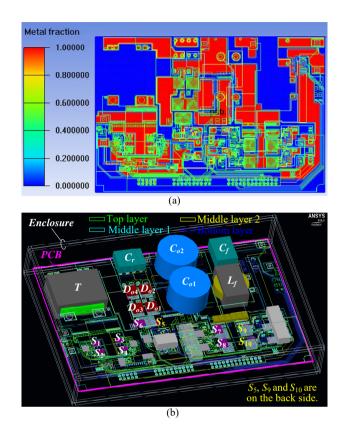

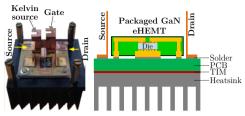

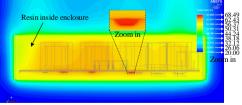

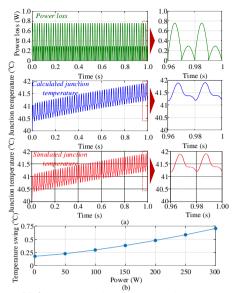

PV microinverters are typically enclosed in a compound-filled case which prevents the erosion of critical components from humidity. Thus, the temperature cycling is reported as the most significant stressor that affects the reliability of microinverter products. Electro-thermal modeling is crucial to the junction/hotspot temperature prediction and reliability evaluation of devices and systems. In this regard, critical parameters and power loss characteristics are modeled for a series of 650-V GaN enhancement-mode highelectron-mobility transistors (eHEMTs). As another important part in highpower-density power electronic converter, printed circuit board (PCB) vias and pads are also analytically modeled concerning their thermal resistance. An optimal design trajectory and an algorithm are proposed for PCB vias and pads, respectively. Finite element method (FEM) simulations and experimental tests are further conducted to verify the built thermal models.

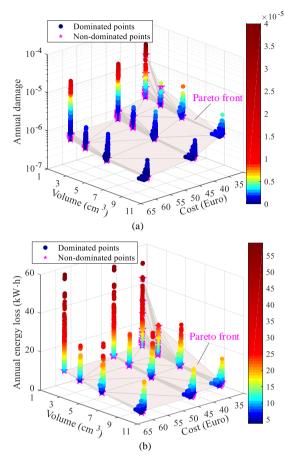

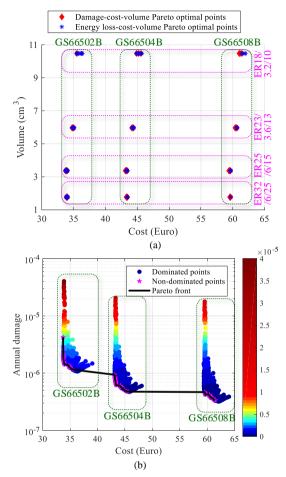

The three performance metrics of a PV microinver, i.e., cost, volume and reliability, all are concerned by the industry. In this regard, a cost-volume-reliability Pareto optimization method is proposed for a PV microinverter. The modeling process of power loss, thermal impedance, lifetime, cost, and volume of components are conducted. Then the cost-volume-reliability Pareto optimization method is executed, yielding a Pareto front which enables a design trade-off among the three performance metrics.

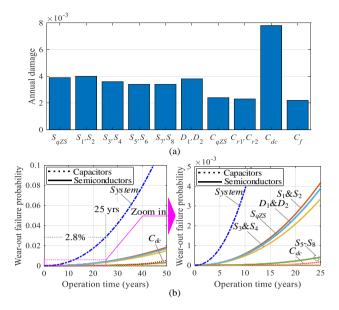

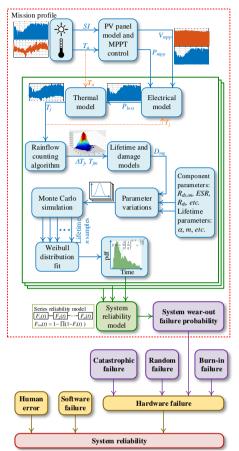

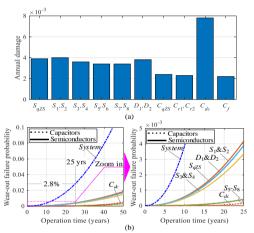

Furthermore, this PhD thesis exemplifies the procedure and function of a reliability-oriented design method. As a case study, the electro-thermal and lifetime modeling of components is carried out for an impedance-source PV microinverter product. Then, the wear-out performance of the PV microinverter product is analyzed to identify the weakest link which, as a result, is the DC-link capacitor. Accordingly, the previous DC-link capacitor is replaced with a better one, and a variable DC-link voltage control is introduced to the PV microinverter. It turns out that the adopted measures can significantly improve the system reliability.

# Dansk Resumé

Solcelle (PV) energi er blevet mere og mere populær over hele verden. Som en uundværlig del af PV-systemer spiller vekselrettere en afgørende rolle i at reducere størrelse, forbedre systemets pålidelighed og sænke Levelized Cost of Energy (LCOE). PV-vekselrettere, også kaldet PV-invertere, kan klassificeres i central-, streng- og mikroinvertere. Markedsandelen af mikroinvertere i residentielle PV-systemer er især stigende på grund af deres evne til at opnå maksimal powerpoint tracking (MPPT), overvågning og fejlfinding på modulniveau. Ikke desto mindre er der stadig udfordringer, som bør adresseres for at forbedre PV-mikroinverter-systemer på en række essentielle områder.

For det første er effektiviteten af en PV-mikroinverter stadig relativt lav sammenlignet med transformerløse strengomformere. Det er især udfordrende for en mikroinverter at opretholde høj effektivitet over et bredt PVdriftsområde. Derfor er der brug for nye topologier og kontrol for at forbedre mikroinverterens effektivitet, således at PV-mikroinverter-systemers fordel med hensyn til energiudbytte kan styrkes.

For det andet er der en tendens til at en PV-mikroinverter integreres i et PV-modul, hvilket indebærer, at den fremtidige mikroinverter skal være mere kompakt og med lille fysisk profil. Derudover er det rapporteret at prisen pr. enhed produceret energi for er højere for en PV-mikroinverter end for streng- og centrale vekselrettere. Derfor skal volumen og omkostningerne for PV-mikroinvertere sænkes.

For det tredje vil den panelindlejrede mikroinverter uundgåeligt opvarmes af PV-panelet og fremskynde nedbrydningen af elektriske komponenter. På grund af det højere antal elektroniske komponenter der anvendes i de mikroinverterbaserede PV-strømsystemer kan pålideligheden forringes. På baggrund af dette bliver pålidelighedsevaluering og pålidelighedsorienteret design af PV-mikroinvertere afgørende.

For at løse disse problemer og dermed muliggøre et kompakt, billigt og pålideligt PV-mikroinvertersystem, diskuterer dette ph.d.-projekt de tilsvarende løsninger.

Forøgelse af effektiviteten og reduktion af effekttabet kan betydeligt øge energiproduktionen og pålideligheden af en PV-mikroinverter. For en totrins en-faset PV-mikroinverter kan DC-AC-trinet, implementeret med den klassiske fuldbro-inverter-topologi, opnå en høj effektivitet, mens det er udfordrende for DC-DC-trinet foran at opretholde høj effektivitet over bred vifte af PV spændinger og effektområder. Derfor foreslår denne ph.d.-afhandling en ny isoleret serie-resonans DC-DC-konverter, som kan klare et bredt indgangsspændingsområde sammen med en variabel DC-link spændingskontrol. Operationsprincippet og nøglekarakteristika for den foreslåede konverter analyseres. En 1-MHz 250-W PV mikroinverter prototype er blevet bygget og testet for at verificere den teoretiske analyse og gennemførligheden af den foreslåede konverter. Derudover diskuteres en strukturkonfigurérbar SRC også for de netforbundne PV-mikroinverter-systemer med et bredt indgangsspændingsområde og forskellige netniveauer, dvs. 110/120 V og 220/230/240 V.

PV mikroinvertere er typisk pakket i en beskyttende indstøbning, der forhindrer korrosion af kritiske komponenter på grund af luftfugtighed. Således rapporteres temperatursvingninger som den mest signifikante stressor, der påvirker pålideligheden af mikroinvertere. Nøjagtige elektro-termiske modeller er afgørende for at forudsige junction/hotspot temperatur og pålideligheden af enheder og systemer. I denne henseende modelleres vigtige parametre og effekttabskarakteristik for en serie af 650 V GaN-enhancementmode høj-elektron-mobilitetstransistorer (eHEMT'er). Som en anden vigtig del i højeffektdensitets-konvertere er printkort (PCB), viaer og pads også analytisk modelleret med hensyn til deres termiske modstand. En optimal designprocedure og en algoritme foreslås for henholdsvis PCB vias og pads. Finite element method (FEM) simuleringer og eksperimentelle tests udføres for at verificere de opbyggede termiske modeller.

De tre præstationskriterier for en PV-mikroinverter, dvs. omkostning, volumen og pålidelighed, er alle vigtige for industrien. I denne henseende foreslås en Pareto-optimeringsmetode for en pris-volumen-pålidelighedsoptimering af en PV-mikroinverter. Modelleringen af effekttab, termisk impedans, levetid, omkostninger og volumen af komponenter udføres. Derefter udføres Pareto-optimeringsmetoden, som giver en pris-volumen-pålidelighed. Dette giver en Pareto-front, der muliggør en afvejning af design blandt de tre præstationskriterier.

Desuden præsenterer denne ph.d.-afhandling et eksempel for proceduren og funktionen af en pålidelighedsorienteret designmetode. Som en caseundersøgelse udføres elektro-termisk- og levetidsmodellering af komponenter for en Impedance-Source PV-mikroinverter. Derefter analyseres wear-out analyse af PV-mikroinverterproduktet for at identificere det svageste led, som vises heraf at være DC-link kondensatoren. På baggrund af dette foreslås en ny variabel DC-spændingskontrol til anvendelse på PV-mikroinverteren, og den tidligere DC-link kondensator erstattes med et nyt design. Det vises at dette kan forbedre systemets pålidelighed betydeligt.

| Abstract iii   |                                                                  |   |  |

|----------------|------------------------------------------------------------------|---|--|

| Dansk Resumé v |                                                                  |   |  |

| Thesis         | Thesis Details xi                                                |   |  |

| Preface        | Preface xiii                                                     |   |  |

|                |                                                                  |   |  |

| I Re           | eport                                                            | 1 |  |

| 1 Inti         | roduction                                                        | 3 |  |

| 1.1            |                                                                  | 3 |  |

| 1.2            |                                                                  | 5 |  |

|                | 1.2.1 Architectures                                              | 5 |  |

|                | 1.2.2 DC-DC Converter Topologies for PV Microinverters           | 7 |  |

| 1.3            | Electro-Thermal Modeling of PCBs and GaN eHEMTs 1                | 1 |  |

|                | 1.3.1 Thermal Modeling of PCBs                                   | 1 |  |

|                | 1.3.2 Characterization and Electro-Thermal Modeling of GaN       |   |  |

|                | 0                                                                | 2 |  |

| 1.4            | Reliability-Oriented Design and Multiobjective Optimization      |   |  |

|                |                                                                  | 4 |  |

|                | 1.4.1 Reliability Evaluation and Reliability-Oriented Design . 1 | 5 |  |

|                | 1.4.2 Multiobjective Optimization                                | 6 |  |

| 1.5            | Research Questions and Objectives                                | 6 |  |

|                | 1.5.1 Research Questions                                         | 6 |  |

|                | 1.5.2 Research Objectives                                        | 7 |  |

| 1.6            | Thesis Outline                                                   | 8 |  |

| 1.7            | List of Publications                                             | 9 |  |

| 2 | A 1-  | 1-MHz Series Resonant DC-DC Converter With a Dual-Mode Rec-    |    |

|---|-------|----------------------------------------------------------------|----|

|   | tifie | r for PV Microinverters                                        | 23 |

|   | 2.1   | Abstract                                                       | 23 |

|   | 2.2   | Operation Principle of the Proposed Converter                  | 24 |

|   |       | 2.2.1 Topology Description                                     | 24 |

|   |       | 2.2.2 Operation Principle                                      | 26 |

|   | 2.3   | Characteristics of the Proposed Converter                      | 28 |

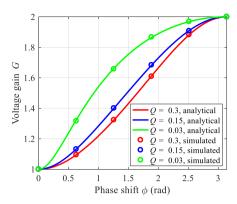

|   |       | 2.3.1 Voltage Gain                                             | 28 |

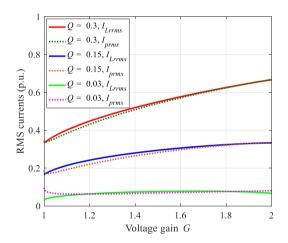

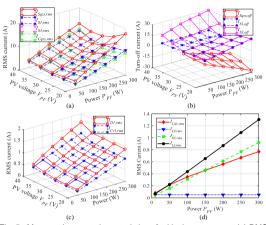

|   |       | 2.3.2 RMS Currents                                             | 29 |

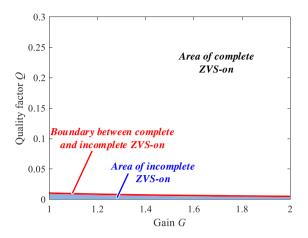

|   |       | 2.3.3 Soft-Switching                                           | 29 |

|   | 2.4   | Experimental Verifications                                     | 32 |

|   | 2.5   | Topology Extension–a Structure-Reconfigurable SRC              | 39 |

|   | 2.6   | Summary                                                        | 39 |

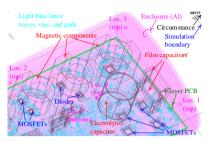

| 3 | The   | rmal Modeling of PCB for High-Power-Density Converter Ap-      |    |

|   | plica | ations                                                         | 41 |

|   | 3.1   | Abstract                                                       | 41 |

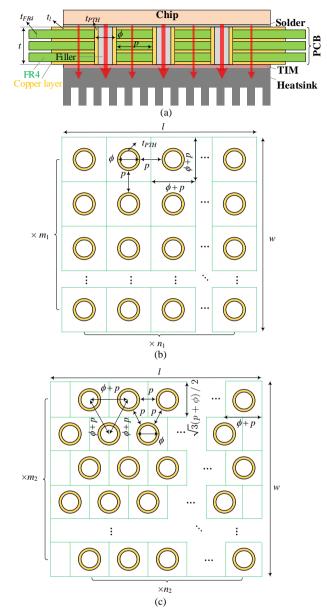

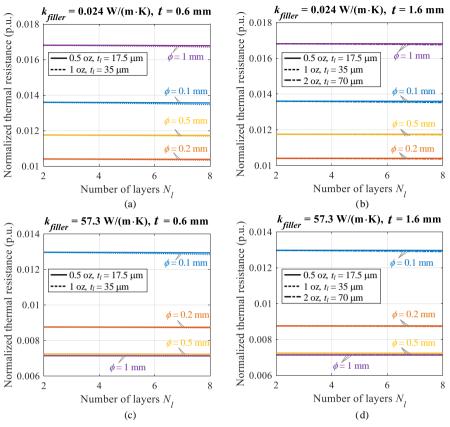

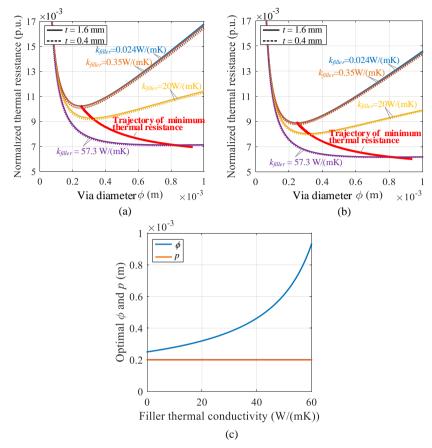

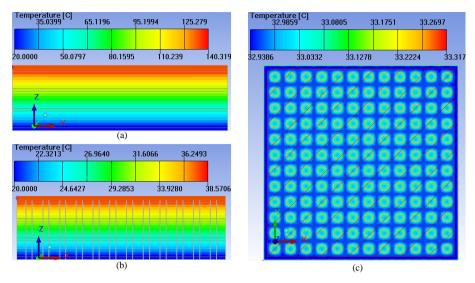

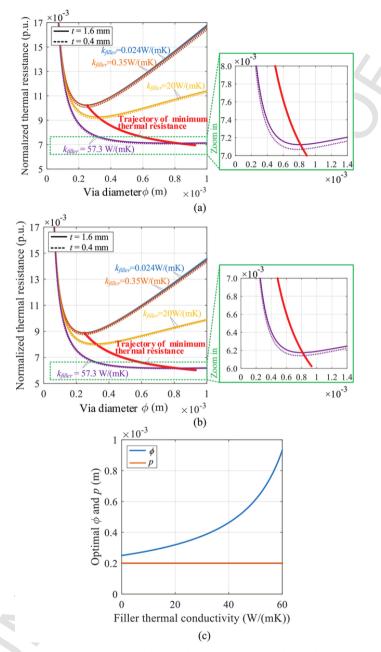

|   | 3.2   | Thermal Modeling and Design Optimization of PCB Vias           | 41 |

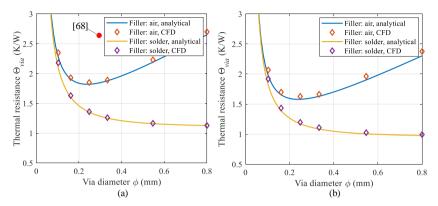

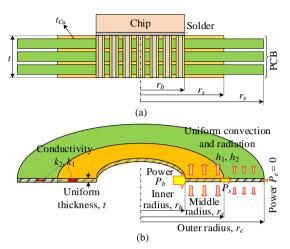

|   |       | 3.2.1 Thermal Modeling of PCB Vias                             | 42 |

|   |       | 3.2.2 Design Optimization of PCB Vias                          | 45 |

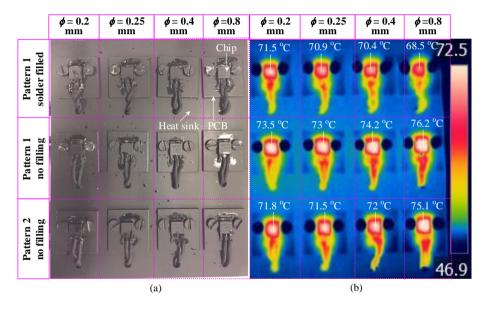

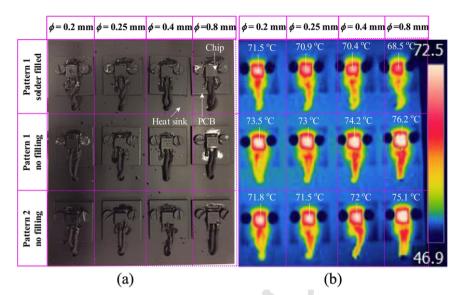

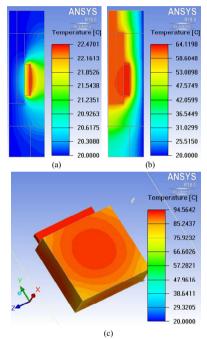

|   |       | 3.2.3 CFD and Experimental Results                             | 46 |

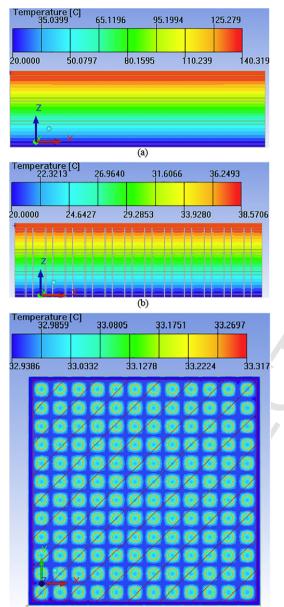

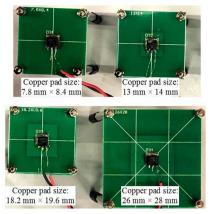

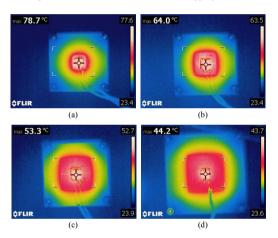

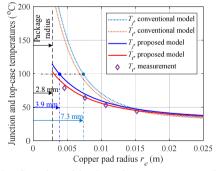

|   | 3.3   | Thermal Modeling and Sizing of PCB Copper Pads                 | 48 |

|   |       | 3.3.1 Heat Transfer in a Circular PCB                          | 48 |

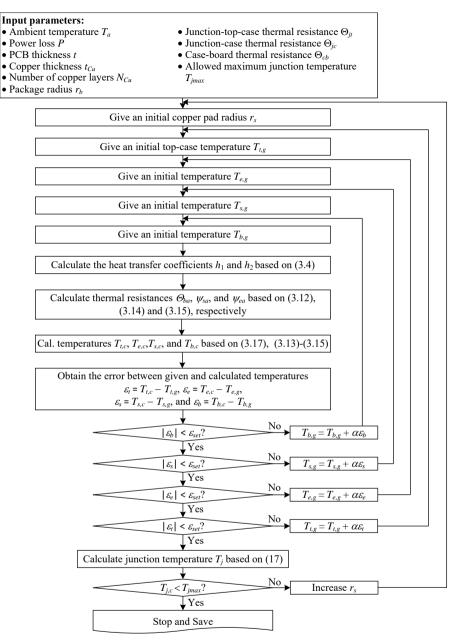

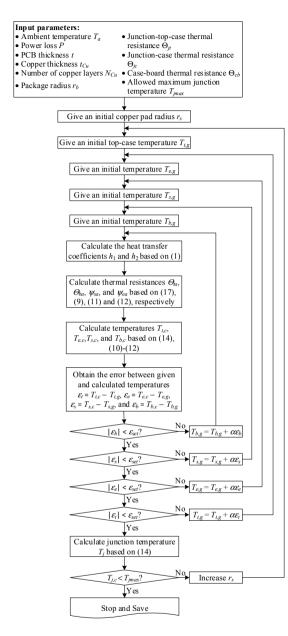

|   |       | 3.3.2 Algorithm for Copper Pad Sizing                          | 51 |

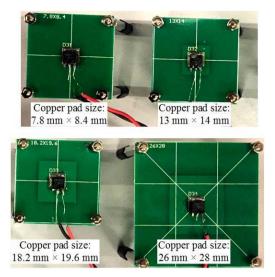

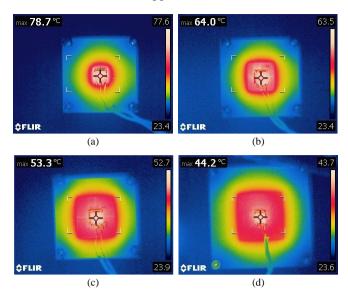

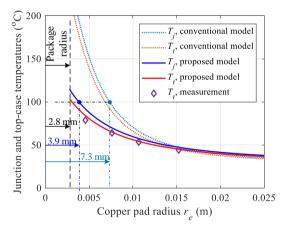

|   |       | 3.3.3 Experimental Results                                     | 53 |

|   | 3.4   | Summary                                                        | 55 |

| 4 | Cha   | racterization and Electro-Thermal Modeling of GaN eHEMTs       | 57 |

|   | 4.1   | Abstract                                                       | 57 |

|   | 4.2   | Parameter Characterization of GaN eHEMTs                       | 57 |

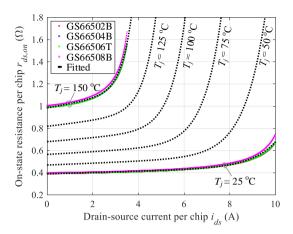

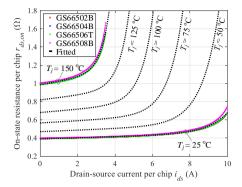

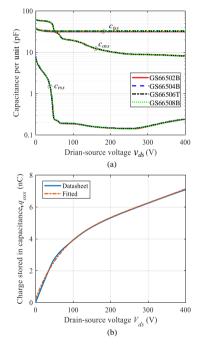

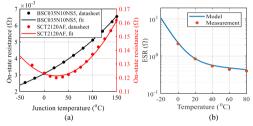

|   |       | 4.2.1 Normalized Drain-Source On-State Resistance              | 57 |

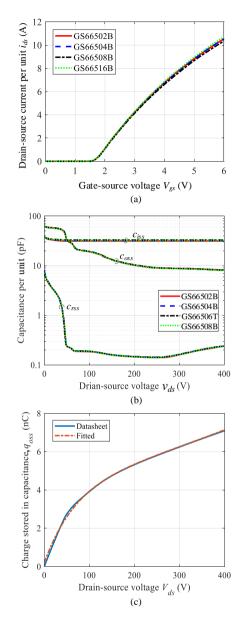

|   |       | 4.2.2 Normalized Transconductance and Parasitic Capacitance    | 59 |

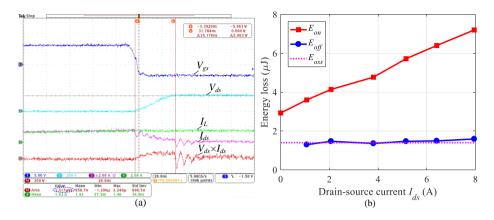

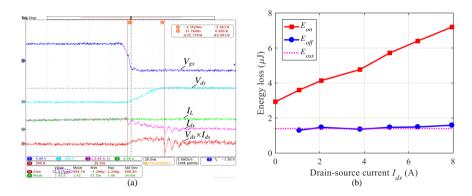

|   | 4.3   | Turn-off Power Loss of GaN eHEMTs                              | 61 |

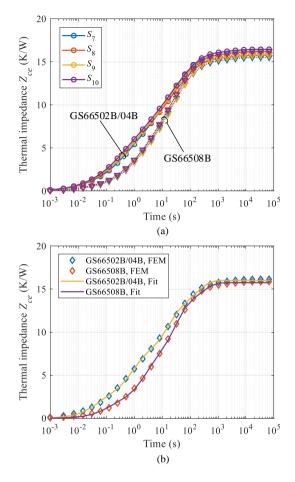

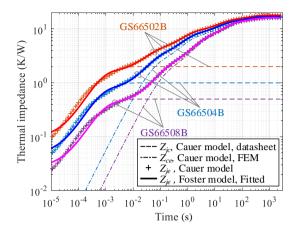

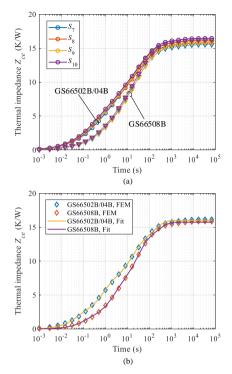

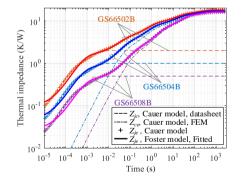

|   | 4.4   | Junction-Case Thermal Impedance of GaN eHEMTs                  | 62 |

|   | 4.5   | Summary                                                        | 64 |

| 5 |       | t-Volume-Reliability Pareto Optimization of a PV Microinverter |    |

|   | 5.1   | Abstract                                                       | 65 |

|   | 5.2   | Operation Principle and Characteristics of the Proposed PV     |    |

|   |       | Microinverter                                                  | 65 |

|   |       | 5.2.1 Topology Description                                     | 65 |

|   |       | 5.2.2 Boundary-Conduction-Mode Operation                       | 66 |

|   | 5.3   | Electro-Thermal Modeling                                       | 68 |

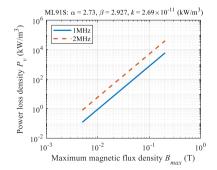

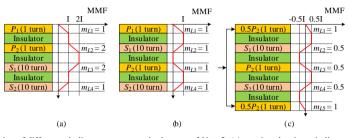

|   |      | 5.3.1           | Power Loss Modeling                                                                                       | 68  |

|---|------|-----------------|-----------------------------------------------------------------------------------------------------------|-----|

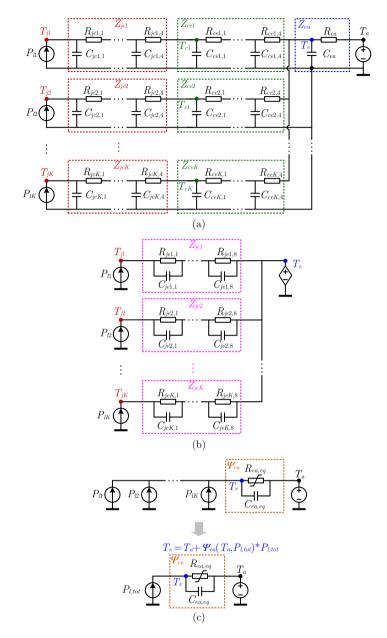

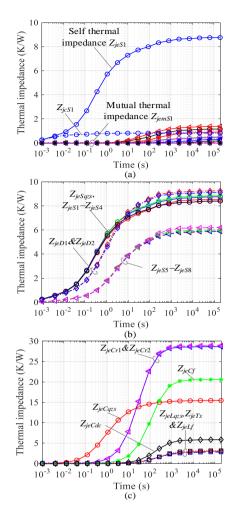

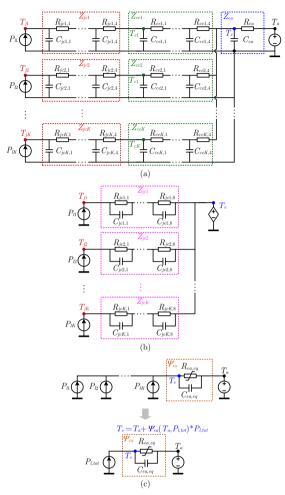

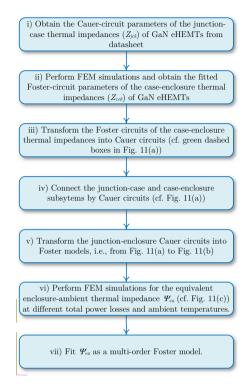

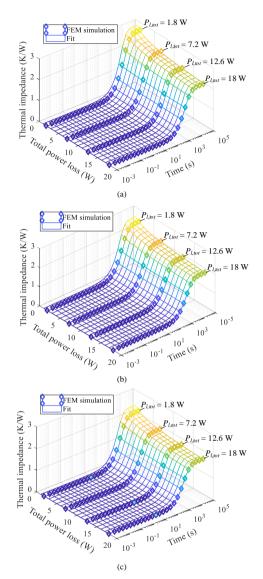

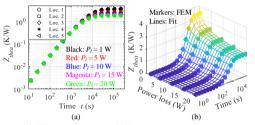

|   | - 4  | 5.3.2           | Thermal Modeling                                                                                          | 70  |

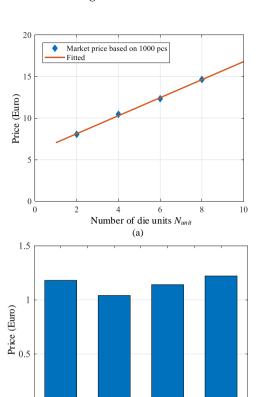

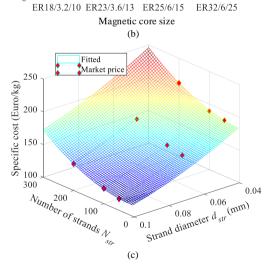

|   | 5.4  |                 | ling of Lifetime, Cost and Volume                                                                         | 75  |

|   |      | 5.4.1           | Lifetime Modeling of GaN eHEMT                                                                            | 75  |

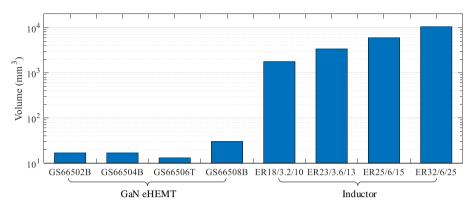

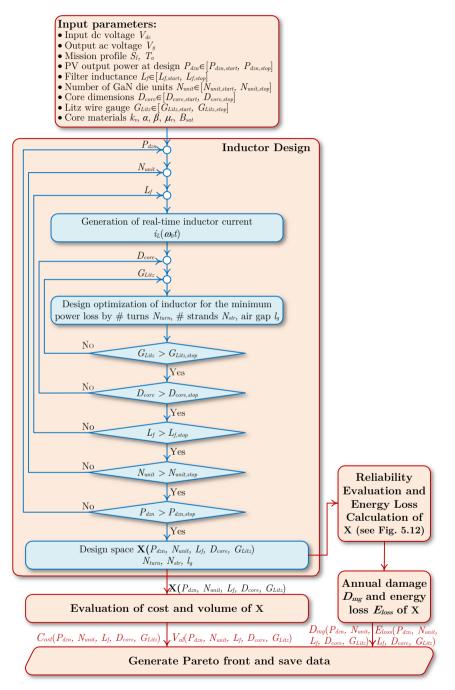

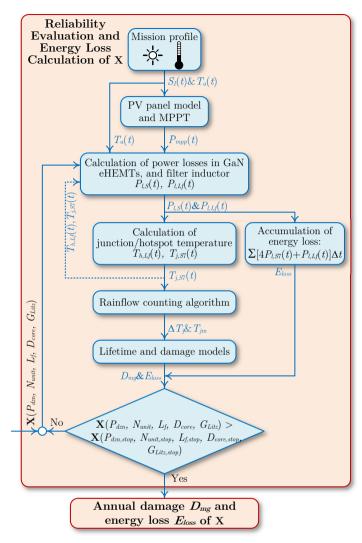

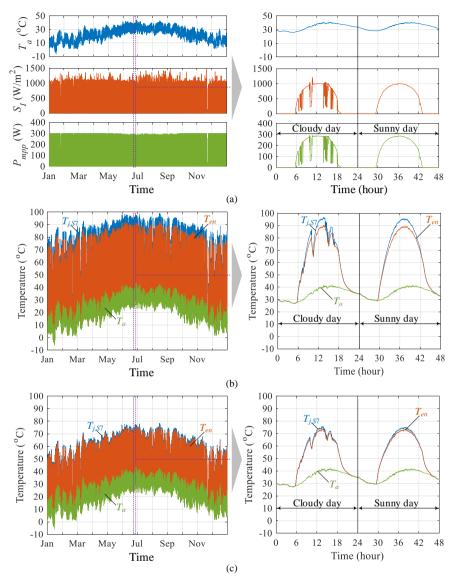

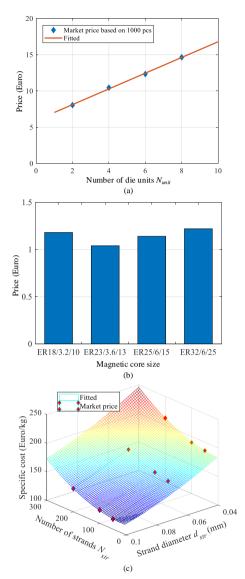

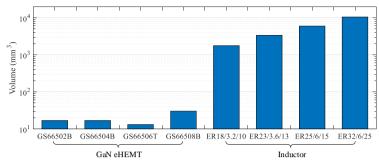

|   | 5.5  | 5.4.2<br>Cost-V | Cost and Volume Modeling of GaN eHEMT and Inductor Volume-Reliability Pareto Optimization of the Proposed | 76  |

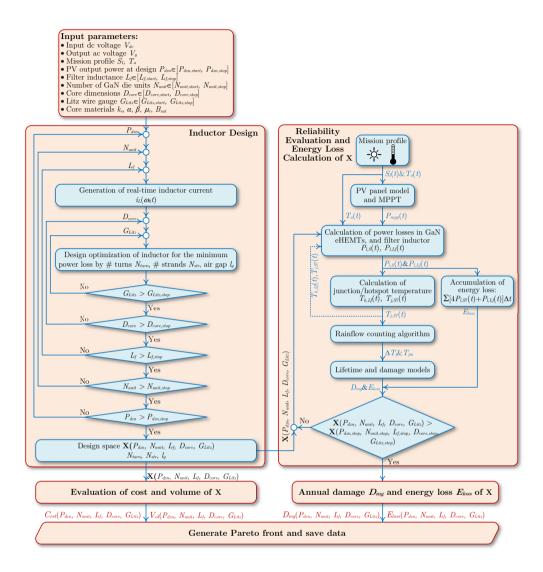

|   |      |                 | inverter                                                                                                  | 79  |

|   |      | 5.5.1           | Design Process                                                                                            | 79  |

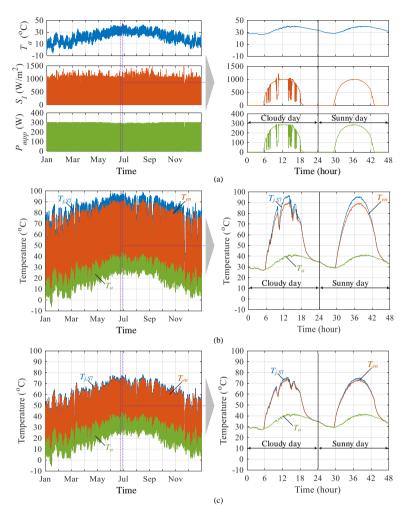

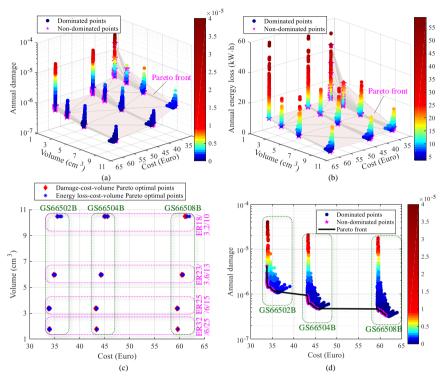

|   |      | 5.5.2           | Cost-Volume-Reliability Pareto Optimization                                                               | 82  |

|   | 5.6  | Summ            | nary                                                                                                      | 86  |

| 6 | Reli | ability         | Analysis and Improvement of a PV Microinverter Prod-                                                      |     |

|   | uct  |                 |                                                                                                           | 87  |

|   | 6.1  | Abstra          |                                                                                                           | 87  |

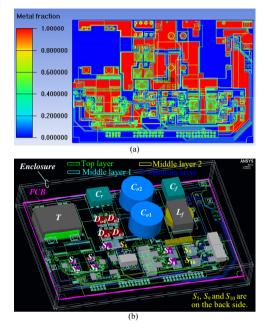

|   | 6.2  | 5               | n Description and Reliability Evaluation Process                                                          | 87  |

|   |      | 6.2.1           | System Description                                                                                        | 88  |

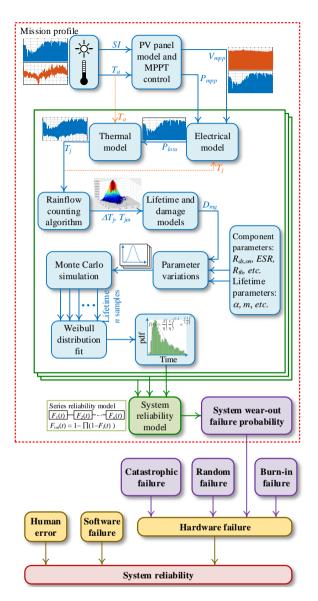

|   |      | 6.2.2           | Reliability Evaluation Process                                                                            | 88  |

|   | 6.3  |                 | o-Thermal and Lifetime Modeling                                                                           | 89  |

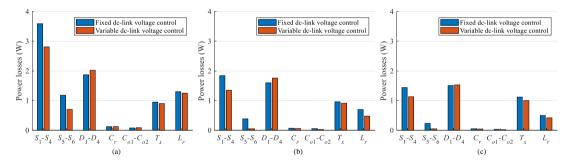

|   |      | 6.3.1           | Power Loss Modeling                                                                                       | 89  |

|   |      | 6.3.2           | Thermal Modeling                                                                                          | 90  |

|   |      | 6.3.3           | Lifetime Modeling                                                                                         | 95  |

|   | 6.4  |                 | Out Failure Analysis of the PV Microinverter                                                              | 96  |

|   |      | 6.4.1           | Static Annual Damage of Components                                                                        | 96  |

|   |      | 6.4.2           | Monte Carlo Simulation                                                                                    | 98  |

|   |      | 6.4.3           | System Failure Probability due to Wear Out                                                                | 98  |

|   | 6.5  |                 | ility Improvement of the PV Microinverter                                                                 | 99  |

|   |      | 6.5.1           | 1                                                                                                         | 100 |

|   |      | 6.5.2           | New DC-Link Electrolytic Capacitor with Longer Nom-                                                       |     |

|   |      |                 |                                                                                                           | 101 |

|   |      | 6.5.3           | 5                                                                                                         | 101 |

|   | 6.6  | Summ            | nary                                                                                                      | 101 |

| 7 |      | clusior         |                                                                                                           | 103 |

|   | 7.1  |                 |                                                                                                           | 103 |

|   | 7.2  |                 |                                                                                                           | 105 |

|   | 7.3  |                 | 1                                                                                                         | 106 |

|   | Refe | erences         | · · · · · · · · · · · · · · · · · · ·                                                                     | 107 |

|   |      |                 |                                                                                                           |     |

### **II** Papers

121

A A 1-MHz Series Resonant DC-DC Converter With a Dual-Mode Rectifier for PV Microinverters 123

| B                                                           | A Series Resonant DC-DC Converter With Wide-Input and Configur<br>Output Voltages | rable-<br>161 |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------|

| С                                                           | Thermal Resistance Modelling and Design Optimization of PCE                       | 3             |

|                                                             | Vias                                                                              | 175           |

| D                                                           | Thermal Modeling and Sizing of PCB Copper Pads                                    | 183           |

| Ε                                                           | Cost-Volume-Reliability Pareto Optimization of a Photovoltaic Mi                  | -             |

|                                                             | croinverter                                                                       | 193           |

| F Wear-out Failure Analysis of an Impedance-Source PV Micro |                                                                                   | r             |

|                                                             | Based on System-Level Electro-Thermal Modeling                                    | 231           |

# **Thesis Details**

| Thesis Title: | Reliability-Oriented Design and Optimization of Photo- |

|---------------|--------------------------------------------------------|

|               | voltaic Microinverters                                 |

| PhD Student:  | Yanfeng Shen                                           |

| Supervisors:  | Prof. Frede Blaabjerg, Aalborg University              |

|               | Assoc. Prof. Huai Wang, Aalborg University             |

|               |                                                        |

The main body of this thesis consists of the following papers:

#### **Publications in Refereed Journals**

- **J1.** Y. Shen, H. Wang, Z. Shen, Y. Yang, and F. Blaabjerg, "A 1-MHz Series Resonant DC-DC Converter With Dual-Mode Rectifier for PV Microinverters," *IEEE Trans. Power Electron.*, 2018, Status: Under Review.

- J2. Y. Shen, H. Wang, A. Al-Durra, Z. Qin, and F. Blaabjerg, "A Series Resonant DC-DC Converter With Wide-Input and Configurable-Output Voltages," *IEEE Trans. Ind. Appl.*, 2018, Status: Under Review.

- **J3.** Y. Shen, H. Wang, and F. Blaabjerg, "Thermal Resistance Modelling and Design Optimization of PCB Vias," *Microelectron. Rel.*, vol. PP, no. 99, pp. 1-6, 2018, Accepted.

- J4. Y. Shen, S. Song, H. Wang, and F. Blaabjerg, "Cost-Volume-Reliability Pareto Optimization of a Photovoltaic Microinverter," *IEEE Trans. Power Electron.*, 2018, Status: to be Submitted.

- J5. Y. Shen, A. Chub, H. Wang, D. Vinnikov, E. Liivik, and F. Blaabjerg, "Wear-out Failure Analysis of an Impedance-Source PV Microinverter Based on System-Level Electro-Thermal Modeling," *IEEE Trans. Ind. Electron.*, vol. PP, no. 99, pp. 1-14, 2018, Early Access.

#### **Publications in Refereed Conferences**

**C1. Y. Shen**, H. Wang, and F. Blaabjerg, "Thermal Modeling and Sizing of PCB Copper Pads," in *Proc. ECCE 2018*, Portland, 2018, pp. 1-7.

#### Thesis Details

This thesis has been submitted for assessment in partial fulfillment of the PhD degree. The thesis is based on the submitted or published scientific papers which are listed above. Parts of the papers are used directly or indirectly in the extended summary of the thesis. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science, Aalborg University.

# Preface

The work presented in this PhD thesis is a summary of the outcome from the PhD project *Reliability-Oriented Design and Optimization of Photovoltaic Microinverters*, which was carried out at the Department of Energy Technology, Aalborg University, Denmark. This PhD project is supported by China Scholarship Council, Department of Energy Technology, Aalborg University, Otto Mønsteds Fond, Tallinn University of Technology, Ubik Solutions LLC, Hitachi Metals Ltd., and Innovation Fund Denmark through the Advanced Power Electronic Technology and Tools (APETT) project. The author would like to give an acknowledgment to the above-mentioned institutions.

First of all, I would like to sincerely thank my supervisor Prof. Frede Blaabjerg for his patient guidance, continued encouragement, and valuable advice throughout this PhD project. He is such a great mentor, and he has offered plenty of helpful guidance in my PhD research. The thesis could not be finalized without his support. I would also like to deeply thank my cosupervisor Assoc. Prof. Huai Wang who has been supporting me in many aspects of my PhD research, including research planning, paper writing, and experimental testing. It is a wonderful experience to work under his supervision.

I am deeply grateful to Prof. Dmitri Vinnikov, Dr. Andrii Chub, and Dr. Elizaveta Liivik for their kind and strong support for this PhD research. I would also like to thank Prof. Ahmed Al Durra for offering me the opportunity to visit the Petroleum Institute, UAE.

Special thanks go to Assoc. Professor Yongheng Yang, Assist. Prof. Zian Qin, Mr. Sungyoung Song, and Mr. Ole Damm Kristensen for their valuable suggestions and kind help. I am also grateful to all my colleagues at the Department of Energy Technology, Aalborg University, for their kind support and fruitful discussions.

Finally, I would like to express my gratitude to my family and my girlfriend Tik Muk for their endless love and continued support to me. You are the source of my happiness.

> Yanfeng Shen Aalborg University, August 27, 2018

Preface

# Part I

# Report

# Chapter 1

# Introduction

### 1.1 Background

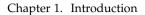

The deployment of photovoltaic (PV) is becoming increasingly popular worldwide. The growth in solar PV capacity in 2016 was larger than any other form of generation; since 2010, the costs of new solar PV systems have decreased by 70% [1]. For instance, the past few years have witnessed the rapid growth of the cumulative PV installation capacity in the US, as shown in Fig. 1.1 [2]. Particularly, since 2015, the residential PV system has exceeded the commercial PV systems in the total installation capacity.

Typically, a PV power system consists of modules, inverters, and other balance-of-system (BOS) components (structural and electrical components, e.g., wiring, switches, mounting systems) [2]. As an indispensable part in a PV power system, the PV inverter plays a crucial role in reducing volume, enhancing system reliability and lowering the levelized cost of energy (LCOE) [3]; therefore, the performance optimization of inverters has gained more and more attention from both academia and industry. For instance, the *Little Box Challenge* launched by Google and the institute of electrical and electronics engineers (IEEE) attracted over 2000 teams from the whole world to register for the competition [4].

Generally, PV inverters can be classified into three categories: central inverters, string inverters, and microinverters. For the microinverter-based PV power systems, each module is connected to a microinverter, which allows the module-level maximum power point tracking (MPPT), improved energy yield from module mismatch reduction, and module-level monitoring and troubleshooting [2, 5–7]. Moreover, compared with the cental and string inverters, the microinverter-based power system is the safest solution as there is no high DC voltage [2]. These features make microinverters popular in residential PV power system. Consequently, the market share of microinverters

Fig. 1.1: U.S. PV market growth from 2004 to 2016 [2].

in residential systems has been increasing, e.g., from 12% in 2010 to 53% in 2016 California, US [2].

Nevertheless, there are still several issues with PV microinverters:

- PV microinverters are more expensive than string and central inverters [2, 3, 7]. According to the technical report [2], the prices of miroinverters, string inverters and central inverters in the US in 2017 were 0.4 \$/Wac, 0.15 \$/Wac, and 0.08 \$/Wac, respectively. It is a requirement that the cost-of-energy performance of PV microinverters should be lowered.

- The power conversion efficiency of microinverters is still relatively low compared with transformerless string inverters (e.g., a peak efficiency of 99.2% is reported in [8]). Thus, the efficiency performance of microinverters needs to be improved by new topologies and/or control schemes.

- There is a trend that a PV microinverer will be integrated into a PV module [9, 10], which implies that the microinverter should be more compact in the future.

- The panel-embedded microinverter may be inevitably heated up by the PV panel, accelerating the degradation of components [11, 12]. Furthermore, due to the greater number of components used in the micro-inverter-based PV power systems, the reliability performance may be deteriorated [2]. On the other hand, increasing the microinverter reliability results in a longer lifetime, which helps to lower the LCOE of a PV microinverter system. Therefore, the reliability evaluation and reliability-oriented design of PV microinverters become paramount.

#### 1.2. Architectures and Topologies of PV Microinverters

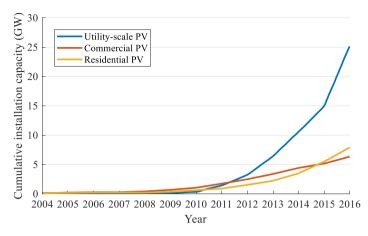

Fig. 1.2: Structures of grid-connected PV microinverter systems [6, 7, 13]: (a) HF-link (single-stage) microinverter, (b) pseudo-DC-link microinverter, (c) DC-link (two-stage) microinverter.

Motivated by the above issues, this PhD project focuses on the topology, electro-thermal modeling, reliability-oriented design, and cost-volumereliability Pareto optimization of PV microinverters.

### 1.2 Architectures and Topologies of PV Microinverters

#### 1.2.1 Architectures

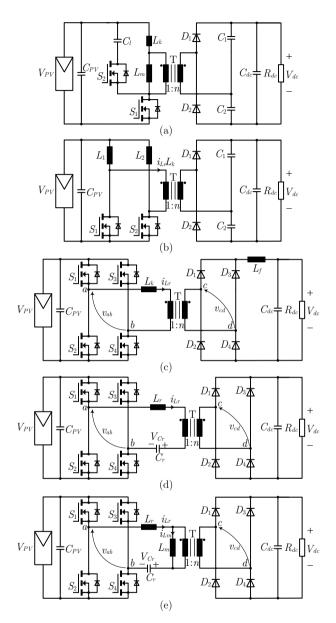

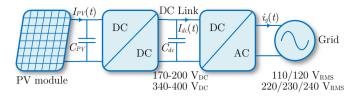

In the literature, various microinverter topologies can be found. Based on the structure, these topologies can be categorized into three types [6, 7, 13], i.e.,

high-frequency (HF) link (single-stage) microinverter [14], pseudo-DC-link microinverter [15], and DC-link (two-stage) microinverter [16], as shown in Fig. 1.2.

- **HF-link microinverter** (cf. Fig. 1.2(a)): The output DC current of a PV panel is converted into an HF AC current by a DC-AC converter. Then, the connected AC-AC stage transforms this HF AC current into a low-frequency (LF) sinusoidal grid current  $i_g(t)$ .

- **Pseudo-DC-link microinverter** (cf. Fig. 1.2(b)): With an HF DC-DC stage, the PV current is modulated to a rectified sinusoidal current at the pseudo-DC-link where the voltage is pulsating as well. The following DC-AC stage operates as an unfolder at line frequency, and inverts the LF pseudo-DC-link current into an LF sinusoidal current  $i_g(t)$ .

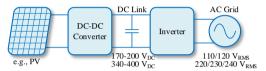

- **DC-link microinverter** (cf. Fig. 1.2(c)): An intermediate DC-link exists between the DC-DC stage and the DC-AC stage. The DC-link voltage is regulated to a constant average value with double line frequency ripples. Both stages are operating at high frequencies.

The output power from a PV module is constant, i.e., DC power, whereas the delivered power to the grid is pulsating at double line frequency. The instantaneous power mismatch between the input and output ports must be decoupled by passive and/or active energy buffers [17].

In the HF-link and pseudo-dc-link microinverters, the energy buffer is normally placed on the low-voltage PV side. Due to the MPPT requirement, the PV voltage ripple should essentially be kept constant, leading to the need for bulky electrolytic capacitors [7, 10]. Thus, the system volume, cost, and reliability may be compromised. By contrast, the DC-link (two-stage) microinverter decouple the power mismatch at the high-voltage DC-link. A significant ripple voltage is tolerable on this capacitor because the DC-AC stage can tolerate an input voltage fluctuation and still can deliver sinusoidal power to the utility [10]. Therefore, low-capacitance high-reliability non-electrolytic capacitors may be used [10]. Moreover, the DC-link solution enables an easier performance optimization for each stage and various grid-support functionalities, e.g., Volt/VAR support [10]. Hence, this solution has been widely adopted [10, 16, 18, 19]. This research project also focuses on the DC-link solution.

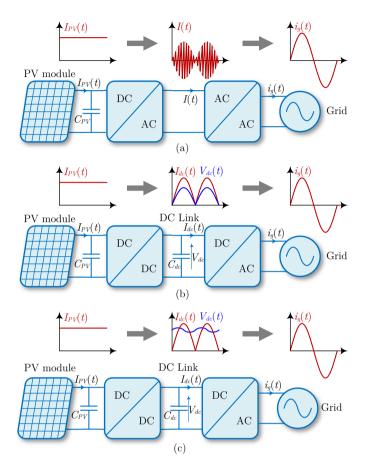

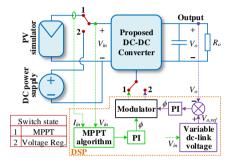

Fig. 1.3 shows a typical control scheme for DC-link (two-stage) gridconnected PV microinverters. The front-end DC-DC stage is employed to achieve the MPPT of the PV panel, whereas the DC-AC inverter stage is controlled to regulate the DC-link voltage as well as to feed power to the grid.

In the literature, various single-phase inverter topologies have been proposed, e.g., basic full-bridge inverter [22], H5 inverter [23], HERIC inverter

#### 1.2. Architectures and Topologies of PV Microinverters

Fig. 1.3: A typical control diagram of DC-link (two-stage) grid-connected PV microinverters [20, 21].

[24], REFU inverter [25], neutral point clamped (NPC) half-bridge inverter [26], T-type half-bridge inverter [16], and other multilevel inverters [27]. Multilevel inverters have advantages of reducing electromagnetic interference (EMI) filter size with improved total harmonic distortion (THD), but also result in increased component count and control complexity [28]. By contrast, the basic full-bridge inverter has the simplest topology structure, and it is able to achieve high power density with low cost and complexity. Moreover, various modulation schemes (e.g., the unipolar modulation, bipolar modulation and hybrid modulation), and flexible control strategies can be applied to the full-bridge inverter to achieve multiple functionalities, e.g., the DC-link voltage regulation, soft-switching of switches, Volt/VAR support to grid and selected harmonics elimination. Therefore, it is the most popular topology among the Google Little Box Challenge teams [29]. As for the PV microinverter applications, the reported peak efficiencies of full-bridge inverters have been as high as 98.6% [30] and 98.8% [16]. Therefore, the basic full-bridge inverter topology is selected as the DC-AC stage of the PV microinverters in this PhD research.

#### 1.2.2 DC-DC Converter Topologies for PV Microinverters

Typically, the front-end DC-DC converter is controlled to achieve the MPPT of a PV module. Depending on the module characteristics and the operating conditions, the output voltages of a PV module at the maximum power points vary over a wide range (e.g., 20-40 V). Therefore, the DC-DC converter is expected to be capable of handling a wide input voltage range while maintaining high efficiencies. It is also required that the dc-dc converter should boost the low-voltage (< 50 V [10]) PV module output to a desired high voltage (at the DC link) in order to feed a grid-connected or standalone inverter [40]. Preferably, a high-frequency transformer is inserted into the

**Fig. 1.4:** Popular DC-DC converter topologies for two-stage PV microinverter products, evaluation boards and prototypes. (a) Active-clamped Flyback DC-DC converter employed in [31–35], (b) isolated Boost DC-DC converter used in [36], (c) phase-shift full-bridge DC-DC converter adopted in [37], (d) series resonant DC-DC converter used in [13, 38], and (e) *LLC* resonant DC-DC converter employed in [16, 39].

front-end DC-DC stage to achieve galvanic isolation, leakage current elimina-

tion, and a high voltage-boost ratio [13]. Furthermore, in order to reduce the system profile, it is necessary to increase the switching frequency and/or to adopt low-profile passive components (e.g., planar magnetics and low-profile decoupling capacitors).

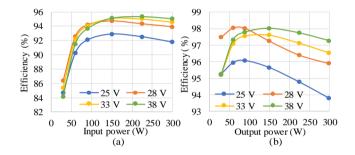

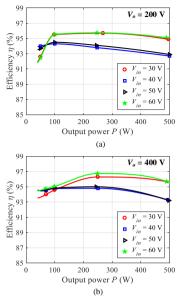

In contrast to the high power conversion efficiencies achieved in the DC-AC stage, it is challenging for the isolated high-step DC-DC stage to achieve high efficiencies over wide ranges of PV voltage and power [7]. Hence, one of the goals of this PhD research is to develop isolated DC-DC converters which can maintain high efficiencies over a wide operating range. In addition, it has been stated in [7, 18] that improving the power conversion efficiency and reducing power losses can be an effective way to enhance the energy yield and reliability of PV microinverters.

Many popular isolated DC-DC converter topologies can be identified from PV microinverter products, evaluation boards/prototypes and scientific papers [13, 16, 31–39], as shown in Fig. 1.4.

- The Flyback DC-DC converter and its derivatives (e.g., interleaved Flyback converter and active-clamped Flyback converter) are the most popular topologies for PV microinverters because of their simpler structures, fewer components counts and lower costs than other topologies. However, the primary-side switches suffer from high voltage stresses, and the low-voltage low-resistance MOSFETs cannot be used [41]. Furthermore, the Flyback transformer loss is still problematic even using a nanocrystalline core material [7]. Consequently, the efficiency performance of Flyback converters is not satisfactory in PV microinverters.

- Compared with the Flyback converters, the DC-offset current of the transformer can be eliminated in the isolated Boost converter. Thus, its efficiency could be enhanced by the reduced transformer losses. However, the primary switches still operate in the hard-switching conditions, and the voltage stress of switches are high. Therefore, the switching and conduction losses of the primary switches may be problematic.

- The phase-shift full-bridge (PSFB) DC-DC converter has a better efficiency performance due to the soft-switching of switches and zero DC-offset current in the transformer. However, it is challenging for a PSFB converter to operate over a wide load range due to the issues like the hard-switching of the lagging-leg MOSFETs at light loads, large circulating current, high voltage stress over the rectifier diodes, and duty-cycle loss. [15, 42].

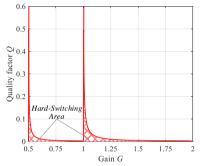

- A high power conversion efficiency is easier to achieve for the series resonant converter (SRC) because of the direct power transfer mechanism [40]. However, the main issue with this topology is that the light-load gain range is very narrow even within a wide frequency range [43].

#### Chapter 1. Introduction

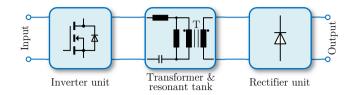

Fig. 1.5: Basic structure of LLC resonant converters [46] and their derivatives [40, 47–57].

As a result, this topology cannot effectively accommodate the wide PV voltage and power ranges.

• The last two decades have witnessed an increasing popularity of the *LLC* resonant converters. A high efficiency of 97.6% has been reported even at 1-MHz switching frequency [44]. Compared with the series resonant converter, the *LLC* resonant converter has a wider voltage gain range; and thus, high efficiencies can be achieved over a wider PV voltage range. Nevertheless, its voltage gain range is still not wide enough to cover the PV operating range, especially at high PV power outputs [18, 39, 45]. Therefore, hybrid control schemes (e.g., burstmode control + variable frequency control, pulse-frequency modulation (PFM) + phase-shift pulse-width modulation (PS-PWM)) have to be applied, leading to increased implementation complexity for PV microinverters.

In order to address the issue of narrow voltage gain range, various modified *LLC* resonant converters have been proposed [40, 47–57]. Fig. 1.5 shows the basic structure of *LLC* resonant converters [46] and their derivatives [40, 47–57]. The topological modifications can be made to the primary-side inverter unit [47, 48, 50, 51, 58], the secondary-side rectifier unit [52–54] and the transformer & resonant tank [55–57].

Instead of the conventional half-bridge or full-bridge structure, a variable frequency multiplier is applied to the *LLC* resonant tank to extend the voltage gain range while maintaining high efficiencies [48]. In [58], the primary-side full-bridge inverter is replaced by a dual-bridge inverter; thus a multi-level AC voltage can be applied to the resonant tank, and a twofold voltage gain range can be achieved; however, the primary-side switches have high turn-off currents, and may suffer from high off-switching losses when operating in high step-up applications (e.g., PV microinverters). By combining a Boost converter with an *LLC* resonant converter, two current-fed LLC resonant converters are proposed in [50, 51]. Nevertheless, the primary-side switches share uneven current stresses, which may lead to high conduction losses as well as high off-switching losses.

To avoid the high off-switching losses on the high-current primary-side

#### 1.3. Electro-Thermal Modeling of PCBs and GaN eHEMTs

switches, references [52–54] propose secondary-rectifier-modified *LLC* resonant converter topologies. Specifically, in [52] and [53], two diodes in the full-bridge rectifier are replaced with two active switches, yielding a controllable rectifier. In [54], two active switches are adopted to obtain a reconfigurable voltage multiplier rectifier, leading to a squeezed switching frequency range and improved efficiencies over a wide input voltage range; notably, the rectifier components count is high (8 diodes + 2 active switches + 6 capacitors), and thus this topology may not be cost-effective for PV microinverter applications.

Furthermore, references [55–57] modify the transformer and resonant tank to extend the voltage gain range of the *LLC* resonant converter. In [55], an auxiliary transformer, a bidirectional switch (implemented with two MOS-FETs in an anti-series connection), and an extra full-bridge rectifier are added to the conventional *LLC* resonant converter. Thus, the equivalent transformer turns ratio and magnetizing inductance can be adaptively changed in order to achieve a wide voltage gain range; however, the components count is high and the transformers utilization ratio is relatively low. To address the issues [55] as well as to maintain high efficiencies over a wide input voltage range, Sun *et al* [57] propose a new *LLC* resonant converter with two split resonant branches; in this way, two operation modes, i.e., the low- and mediumgain modes, are enabled, and the gain range for mode transition is 1.5 times, leading to a smoother efficiency curve over the gain range. In reference [56], a new transformer plus rectifier structure with fractional and reconfigurable effective turns ratios is proposed for a widely varying voltage gain.

# 1.3 Electro-Thermal Modeling of PCBs and GaN eHEMTs

#### **1.3.1** Thermal Modeling of PCBs

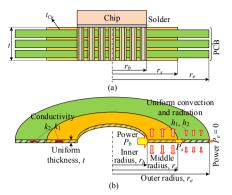

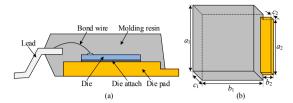

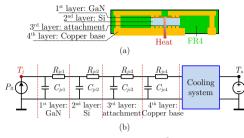

Modern power semiconductor devices are shrinking in size in order to achieve better performance in terms of parasitic inductance, power density, and power losses [59]. Good thermal management must be achieved to ensure the heat generated inside the device is effectively dissipated to the ambient. Otherwise, the high temperature may lead to reliability issues with the semiconductor, solder joint and thermal grease [60–63]. In addition, suitable heat dissipation measures should be considered as early as in the design and development phase, because subsequent modifications are generally more costly and involve increased engineering effort [64].

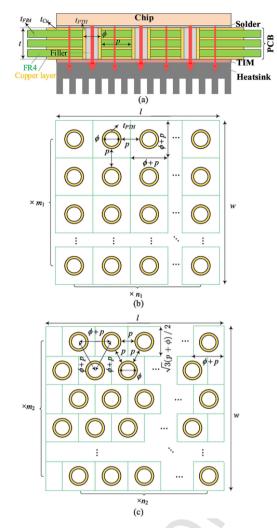

In medium power applications, a surface-mounted device (SMD) is typically cooled by a heatsink attached to the PCB. In this case, the PCB vias offer an efficient thermal propagation path [65, 66]. In low power scenarios, a PCB copper pad is used for heat spreading, and thus, a SMD can be cooled by natural convection [67]. Semiconductor device manufacturers have provided many thermal design guidelines [67–71]. However, those reference design schemes are for specific cases only and are not optimized. There is even some discrepancy between the design guidelines, e.g., [69] and [70] give the opposite recommendations for the thermal via diameter. Moreover, the computational fluid dynamics (CFD) simulations are costly and time-consuming despite higher accuracy. Hence, the development of an analytical thermal model, which supports a quick design optimization of PCB vias and pads, is of significance.

References [72–74] employ either experiment or CFD simulation to obtain the thermal resistance of PCB vias. In [65, 75–78], analytical thermal models are built for PCB vias. However, the main issue is that not all parameters are analyzed or considered, and thus, the derived via design is not optimal.

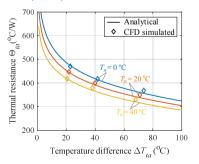

For the heat transfer characteristics of a PCB pad, the heat conduction, convection and radiation all exist, which makes the thermal analysis complicated. Texas Instruments develops an online PCB thermal calculation tool based on CFD thermal resistance data of different package sizes and pad dimensions [79]. However, some important factors (e.g., PCB thickness, number of copper layers, and copper thickness) are not taken into account, and the online tool does not support design optimization. In addition to the CFD simulations, many other numerical calculation methods are developed [80, 81]. The study in [81] deals with a substrate for a ball grid array package, where a belt of densely populated vias and two continuous copper layers are placed; however, the built model is complicated and no CFD or experimental verifications are provided. For electrical engineers, it is more desired to have an analytical thermal model such that the temperature of devices with different designs and cooling methods can be fast predicted [82, 83]. In [67], an analytical thermal resistance model is developed for PCB thermal pads; however, the heat transfer boundary and the convective heat transfer coefficient variation over temperature difference are not included, and as a result, there might be a remarkable error between calculations and measurements.

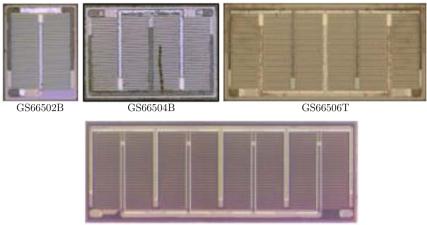

# 1.3.2 Characterization and Electro-Thermal Modeling of GaN eHEMTs

GaN power transistors, e.g., enhancement-mode high-electron-mobility transistors (eHEMTs), feature higher power density, higher switching frequency, and lower loss than their silicon counterparts [28, 84]. Accordingly, GaN eHEMTs are becoming increasingly popular in power electronic converters. With the same voltage rating and drain-source on-state resistance, the parasitics of a GaN eHEMT, including the parasitic inductance and capacitance, are significantly smaller than silicon power switches. Thus, fast switching

#### 1.3. Electro-Thermal Modeling of PCBs and GaN eHEMTs

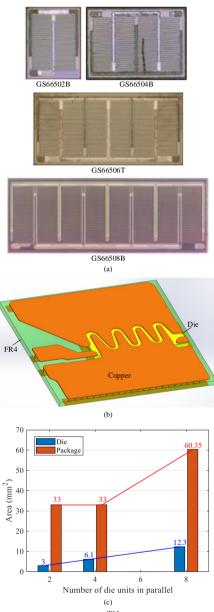

GS66508B

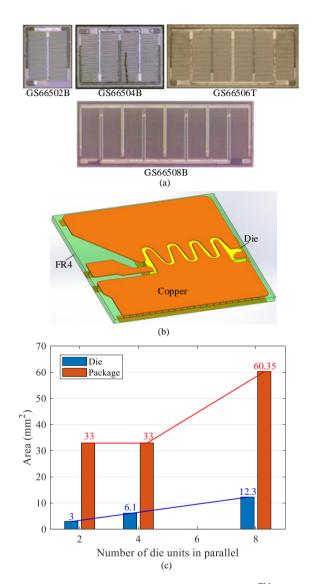

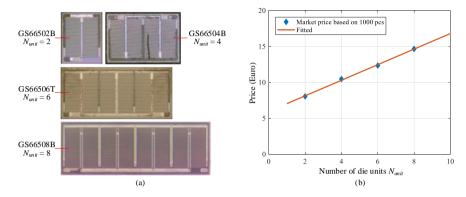

**Fig. 1.6:** Scanning acoustic microscopy (SAM) images of the 650-V GaN eHEMT dies of GaN Systems<sup>TM</sup>; The numbers of die units inside GS66502B, GS66504B, GS66506T and GS66508B are 2, 4, 6, and 8, respectively. The total die area of GS66508P (12.3 mm<sup>2</sup> [85]) is almost twice of that of GS66504B (6.1 mm<sup>2</sup> [86]).

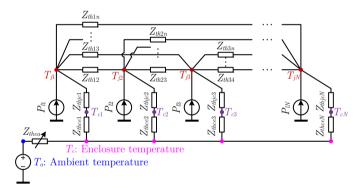

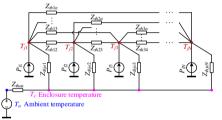

Fig. 1.7: Thermal impedance network of an enclosed converter system, including the self and mutual junction-enclosure thermal impedances. Source: [J5].

and low switching loss are possible for GaN eHEMTs. When the switching frequency is pushing up to megahertz, the side effect of parasitics and the switching loss can still be pronounced. In this PhD project, the employed GaN eHEMTs can achieve the zero-voltage switching (ZVS) turn-on, and the turn-on loss can be negligible. Consequently, only the conduction loss, turn-off loss and soft-switching characteristics of GaN eHEMTs are focused on.

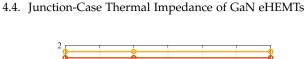

For a series of 650-V GaN eHEMTs from GaN Systems<sup>TM</sup>, the current rating and on-state drain-source resistance of a transistor are achieved by employing different standard die units in parallel, as shown in Fig. 1.6. The

numbers of die units inside GS66502B, GS66504B, GS66506T, and GS66508B are 2, 4, 6, and 8, respectively.

Detailed information concerning the drain-source resistance, parasitic capacitance, and junction-case thermal impedance of a GaN eHEMT can be found from the datasheet. However, there is still a lack of generic analytical parameter models which can be used for the design optimization of PV microinverters.

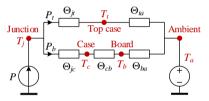

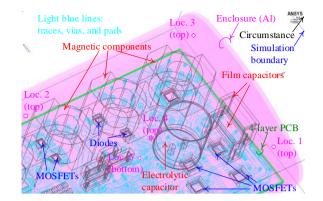

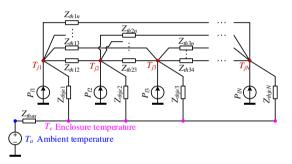

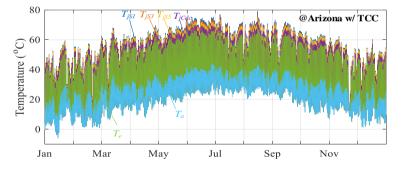

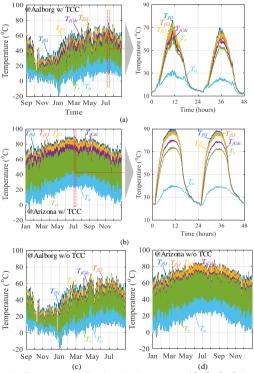

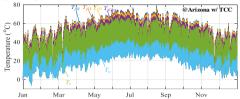

For the thermal performance of a GaN eHEMT, it is also determined by the cooling system which may vary significantly with different designs. Most of the PV microinverter products on the market are filled up with high-thermal-conductivity compound [18] in order to improve the cooling performance and protect the converters from humidity erosion. However, the compound reinforces the thermal cross-coupling among the components inside the microinverter enclosure, as illustrated in Fig. 1.7. The heat propagation from the components to the ambient can be divided into three parts, i.e., from the junction/hotspot to the case, from the case to the enclosure, and from the enclosure to the ambient. For the first two heat transfer paths, the heat conduction dominates, whereas the third heat transfer path, i.e., from the converter enclosure to the environment, involves all the three heat transfer approaches, heat conduction, convection, and radiation. The heat transfer rate of convection is determined by the temperature difference between the enclosure surface and the environment, whereas the radiation intensity relates to the absolute temperatures [87]. The participation of convection and radiation makes the whole thermal system strongly nonlinear [18]. Particularly, it is challenging to accurately and quickly calculate the long-term (e.g., 1 year) junction/hotspot temperatures of main components for a complete PV microinverter system operating in the real field.

### 1.4 Reliability-Oriented Design and Multiobjective Optimization of PV Microinverters

The essential performance metrics of a PV microinverter include efficiency, energy caption, grid integration, cost, volume, reliability, etc. Most early studies and current work focus on the efficiency [7, 14, 16, 18, 32, 35, 39, 40, 43], energy caption [88, 89], grid support function [10, 19], power decoupling [17, 31, 90, 91], and LCOE of PV microinverters [2, 92–94].

Specifically, the most attention has been paid to the power conversion efficiency, which could not only reduce the cost of energy but also improve system reliability [18]. The efficiency improvement of a PV microinverter can be achieved by the innovations on converter topology [35, 40, 43], modulation scheme [14, 16], control strategy [18, 32, 39], and system design (including component selection, PCB design, cooling design, etc.) [7]. The en-

#### 1.4. Reliability-Oriented Design and Multiobjective Optimization of PV Microinverters

ergy caption enhancement of a PV microinverter system can be realized by adopting a shade-tolerant (global) MPPT algorithm [88] or using a differential power processing architecture [89]. To enable the grid-support functions, e.g., Volt/VAR support and harmonics mitigation, advanced controls are applied to the two-stage microinverters in [10, 19]. A growing number of works have recently focused on both the passive and active power decoupling techniques of PV microinverters to obtain higher reliability or smaller physical size [17, 31, 90, 91]. Furthermore, one of the most popular benchmarking criteria for different PV microinverter techniques is the LCOE, which is widely adopted in industry, academia, and government [2, 92, 93]. The LCOE of a PV microinverter system can be lowered by reducing the system cost and increasing the efficiency and reliability [94].

#### 1.4.1 Reliability Evaluation and Reliability-Oriented Design

The lifetime/warranty of PV modules is about 25 years, but inverters often have to be replaced every 5 to 10 years [95], implying that the reliability of a microinverter needs improvement in order to get along with a PV module. Therefore, the reliability-oriented design of photovoltaic microinverters under a harsh environment becomes more and more important [12, 61].

A failure mode and effects analysis (FMEA) survey for PV module-level power electronics (MLPE) products [96] shows that the loose connection of dc input and ac output connectors, wear-out of dc-link electrolytic capacitors, varistor failure-short from the surge, and degradation of MOSFETs and diodes are the top four failure modes [J5]. Due to the compound filled inside microinverter enclosures, the erosion of critical components from humidity is prevented; thus, the temperature cycling is stated as the most significant stressor determining the reliability performance of microinverter products [96].

Recently, increasing effort has been made to the reliability of discrete power electronics components or modules (e.g., IGBT [97], MOSFET [98], and capacitor [99]) [J5]. In the literature, only a few works concerning the microinverter reliability can be found, and most of them use the MIL-HDBK-217 handbook [100] to determine the failure rates of microinverters [101, 102]. Unfortunately, the constant failure rates only describe the large-population statistics of random failures, and the wear-out failure is not considered [J5]. There are also a few works [103, 104] focusing on the system-level reliability. Moreover, the main issue with previous and current works on the reliability assessment is that the local ambient temperature and the thermal cross-coupling effect among components are not considered; thus, the wear-out performance is usually overestimated [J5].

On the other hand, the independent reliability testing and long-term usage data are still missing since the MLPE market is nascent [J5]. Nevertheless, *Flicker* et al [11] perform long-term accelerated tests for multiple PV microinverter products. As a result, the relative degradation performances of those PV microinverter products in the real-world operation can be predicted. However, the accelerated testing of microinverter products may be time-consuming, e.g., one year as spent in [11].

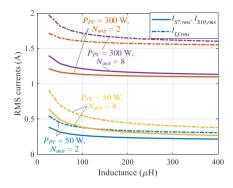

### 1.4.2 Multiobjective Optimization

The multiobjective optimization of power electronics enables designers to make the trade-off among multiple performance metrics. During the last decade, the efficiency plus power density Pareto optimizations of a power factor correction (PFC) rectifier, *LC* output filters, inductive power transfer coils, switched capacitor converters have been presented in [105–108], respectively. Recently, another important goal, cost, is also taken into account in the multiobjective Pareto optimization of dual active bridge (DAB) converters [109]. However, a crucial performance criterion, i.e., reliability, is still neglected in the existing multiobjective optimization literature.

On the other hand, only a few papers can be found for the multiobjective optimization of PV microinverters. In [110], a comparative study on different microinverter architectures is conducted to make a trade-off between efficiency and Volt/VAR support capability. Dong *et al* [10] presents a detailed procedure considering multiple performance metrics (e.g., efficiency, cost, and reliability) and compliances (e.g., EMC and safety compliance, and agency compliance); however, only part of the design possibilities are explored, and therefore, the design may not be Pareto optimal.

### 1.5 Research Questions and Objectives

### 1.5.1 Research Questions

The final goal of this PhD project is to develop a reliability-oriented design and optimization method for PV microinverters.

The power conversion efficiency does not only determine the energy yield of a PV microinverter, but also affects its reliability due to the power losses [18]. Thus, it is needed to propose new microinverter topologies which are able to maintain high efficiencies over wide PV voltage and power ranges. Since the temperature cycling is the primary cause of the wear-out failure of PV microinverters [96], the electro-thermal modeling of components is of necessity for fast and accurate reliability evaluation. Furthermore, cost and volume are also essential performance metrics determining the competitiveness of a PV microinverter product on the market, and therefore, it is necessary to include the two metrics in the reliability-oriented design. 1.5. Research Questions and Objectives

Based on the above justification, the following research questions are considered:

- Is it possible to develop a new microinverter topology which enables wide ranges of voltage gain and power, while maintaining high efficiencies?

- How to quantify and optimize the thermal resistance and/or power losses of critical components in PV microinverters, e.g., PCB vias, PCB pads, and GaN eHEMTs?

- Is it possible to simultaneously take into account the four performance metrics, i.e., cost, volume, reliability, and energy yield, for the design optimization of a PV microinverter?

- How to evaluate and improve the reliability of a PV microinverter product in the design phase?

### 1.5.2 Research Objectives

Motivated by those research questions, this PhD project aims to achieve the following objectives:

- High-efficiency DC-DC converter topologies suitable for PV microinverters: as mentioned previously, increasing the power conversion efficiency and reducing the power losses can significantly enhance the energy yield and reliability of a PV microinverter. Given that the DC-AC stage implemented with the full-bridge inverter has already achieved high power conversion efficiencies, one of the goals of this PhD project is to propose new wide-voltage-gain DC-DC converters for the twostage PV microinverters. The operation principle and essential characteristics will be analyzed. Converter prototypes will be built, and the testing results are expected to verify the advantages of the proposed converters in terms of maintaining high efficiencies over wide inputvoltage and power ranges.

- Electro-thermal modeling of components and PV microinverter systems: accurate electro-thermal models, including the power loss model and the thermal model, are crucial for the junction/hotspot temperature prediction of a device. Notably, for the naturally cooled PV microinverters, the heat conduction, convection and radiation all are involved, which complicates the long-term temperature prediction and online design optimization. Hence, this PhD research attempts to develop analytical power loss models and thermal models for two types of components, GaN eHEMT and PCB. PCB prototypes and a doublepulse test setup will be built to validate the developed models.

- **Cost-volume-reliability Pareto optimization of a PV microinverter:** the three performance metrics, cost, volume and reliability, all are concerned by the industry. However, there is still a lack of design method which can accommodate all the three requirements. In this regard, the PhD project will propose a cost-volume-reliability Pareto optimization method for PV microinverters. A cost-volume-reliability Pareto front is expected to be generated, and thus, a trade-off design/decision can be made among the three performance metrics.

- Reliability evaluation and improvement of a PV microinverter product: the last objective of this PhD study is to exemplify the procedure and function of a reliability-oriented design method. As a case study, the wear-out performance of a commercial PV microinverter product will be analyzed to find out the weakest link in terms of reliability. Then, proper measures concerning design and control will be adopted to improve the reliability of the PV microinverter product.

### 1.6 Thesis Outline

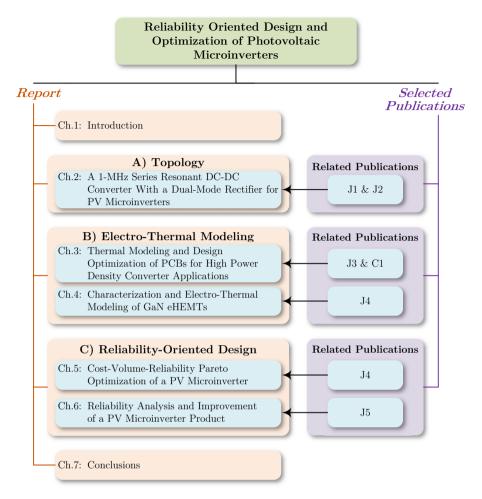

The obtained results of this project are documented in the PhD thesis based on the collection of papers published/submitted during the PhD period. The document consists of the *Report* and the *Selected Publications*, as illustrated in Fig. 1.8. The *Report* presents a brief summary of the research outcomes related to the PhD project, whereas the *Selected Publications* present the papers derived during the PhD period.

The Report begins with the introduction of this PhD project, where the background, critical issues, challenges, state-of-the-art, and research objectives are discussed. *Chapter 2* mainly focuses on a new wide-voltage-gain DC-DC converter topology for PV microinverters; specifically, the operation principle, characteristics and experimental verifications of the proposed converter are presented in brief. Then the following two chapters (i.e., *Chapters 3 and 4*) deal with the electro-thermal modeling and optimization of GaN eHEMTs and PCBs. The main focus of *Chapters 5 and 6* is on the reliability-oriented analysis and design of PV microinverters. In addition to reliability, the other two performance metrics, cost and volume, are also taken into account in *Chapter 5* for the Pareto optimization of a PV microinverter. In *Chapter 6*, the wear-out performance of a PV microinverter product is analyzed before a new design is implemented to improve the reliability of the product. Finally, Chapter 7 concludes the thesis, summarizes the main contributions of this research, and outlines the future research perspectives.

#### 1.7. List of Publications

Fig. 1.8: Thesis structure and relationship between the *Report* and the *Selected Publications*.

# 1.7 List of Publications

The research outcomes during the Ph.D. study have been disseminated in several forms of publications: journal papers, conference publications, book chapters, as listed in the following. Parts of them are used in the Ph.D. thesis as previously listed.

#### **Publications in Refereed Journals**

**J1.** Y. Shen, H. Wang, Z. Shen, Y. Yang, and F. Blaabjerg, "A 1-MHz Series Resonant DC-DC Converter With Dual-Mode Rectifier for PV Microinverters," *IEEE Trans. Power Electron.*, 2018, Status: Under Review.

- J2. Y. Shen, H. Wang, A. Al-Durra, Z. Qin, and F. Blaabjerg, "A Series Resonant DC-DC Converter With Wide-Input and Configurable-Output Voltages," *IEEE Trans. Ind. Appl.*, 2018, Status: Under Review.

- **J3.** Y. Shen, H. Wang, and F. Blaabjerg, "Thermal Resistance Modelling and Design Optimization of PCB Vias," *Microelectron. Rel.*, vol. PP, no. 99, pp. 1-6, 2018. Accepted.

- J4. Y. Shen, S. Song, H. Wang, and F. Blaabjerg, "Cost-Volume-Reliability Pareto Optimization of a Photovoltaic Microinverter," *IEEE Trans. Power Electron.*, 2018, Status: to be Submitted.

- J5. Y. Shen, A. Chub, H. Wang, D. Vinnikov, E. Liivik, and F. Blaabjerg, "Wear-out Failure Analysis of an Impedance-Source PV Microinverter Based on System-Level Electro-Thermal Modeling," *IEEE Trans. Ind. Electron.*, vol. PP, no. 99, pp. 1-14, 2018, Early Access.

- Y. Shen, H. Wang, A. Al-Durra, Z. Qin, and F. Blaabjerg, "A Bidirectional Resonant DC–DC Converter Suitable for Wide Voltage Gain Range," *IEEE Trans. Power Electron.*, vol. 33, no. 4, pp. 2957-2975, Apr. 2018.

- M. Forouzesh, Y. Shen, Y. P. Siwakoti, K. Yari., and F. Blaabjerg, "High-Efficiency High Step-Up DC-DC Converter with Dual Coupled Inductors for Grid-Connected Photovoltaic Systems," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5967-5982, Jul. 2018.

- Z. Qin, Y. Shen, P. C. Loh, H. Wang, and F. Blaabjerg, "A Dual Active Bridge Converter with an Extended High-Efficiency Range by DC Blocking Capacitor Voltage Control," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5949-5966, Jul. 2018.

- X. Sun, X. Wu, Y. Shen, X. Li, and Z. Lu, "A Current-Fed Isolated Bidirectional DC–DC Converter," *IEEE Trans. Power Electron.*, vol. 32, no. 9, pp. 6882-6895, Sep. 2017.

- X. Sun, X. Li, Y. Shen, B. Wang, and X. Guo, "Dual-Bridge LLC Resonant Converter With Fixed-Frequency PWM Control for Wide Input Applications," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 69-80, Jan. 2017.

#### **Publications in Refereed Conferences**

**C1. Y. Shen**, H. Wang, and F. Blaabjerg, "Thermal Modeling and Sizing of PCB Copper Pads," in *Proc. 2018 IEEE Energy Conversion Congress and Exposition (ECCE)*, Portland, 2018, pp. 1-7.

- Y. Shen, H. Wang, Z. Shen, F. Blaabjerg, and Z. Qin, "An Analytical Turn-on Power Loss Model for 650-V GaN eHEMTs," in *Proc. 2018 IEEE Applied Power Electronics Conference and Exposition (APEC)*, San Antonio, TX, 2018, pp. 913-918.

- Y. Shen, H. Wang, and F. Blaabjerg, "Reliability Oriented Design of a Grid-Connected Photovoltaic Microinverter," in *Proc. 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC* 2017 - ECCE Asia), Kaohsiung, 2017, pp. 81-86.

- Y. Shen, H. Wang, F. Blaabjerg, X. Sun, and X. Li, "Analytical Model for LLC Resonant Converter With Variable Duty-Cycle Control," in *Proc. 2016 IEEE Energy Conversion Congress and Exposition (ECCE)*, Milwaukee, WI, 2016, pp. 1-7.

- Y. Shen, H. Wang, Y. Yang, P. D. Reigosa, and F. Blaabjerg, "Mission Profile Based Sizing of IGBT Chip Area for PV Inverter Applications," in *Proc. 2016 IEEE 7th International Symposium on Power Electronics for Distributed Generation Systems (PEDG)*, Vancouver, BC, 2016, pp. 1-8.

- K. Li, Y. Shen, Y. Yang, Z. Qin, and F. Blaabjerg, "A transformerless single-phase symmetrical z-source HERIC inverter with reduced leakage currents for PV systems," in *Proc. 2018 IEEE Applied Power Electronics Conference and Exposition (APEC)*, San Antonio, TX, 2018, pp. 356-361.

- Z. Shen, H. Wang, Y. Shen, Z. Qin, and F. Blaabjerg, "Winding design of series AC inductor for dual active bridge converters," in *Proc. 2018 IEEE Applied Power Electronics Conference and Exposition (APEC)*, San Antonio, TX, 2018, pp. 565-570.

## **Book Chapter**

• Y. Shen, Z. Qin, and H. Wang, "Modeling and Control of DC-DC Converters," in Control of Power Electronic Converters and Systems, 1st ed., Frede Blaabjerg, Ed.: Elsevier, 2018, ch.3.

Chapter 1. Introduction

# Chapter 2

# A 1-MHz Series Resonant DC-DC Converter With a Dual-Mode Rectifier for PV Microinverters

# 2.1 Abstract

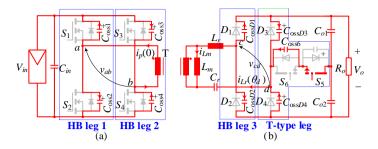

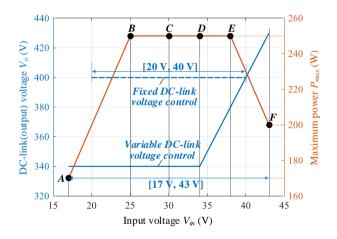

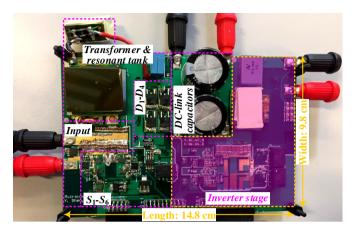

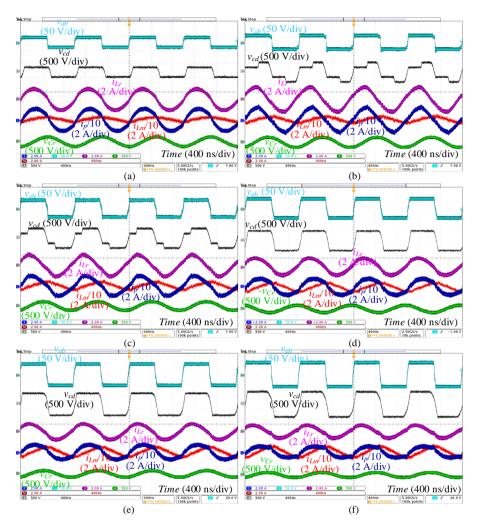

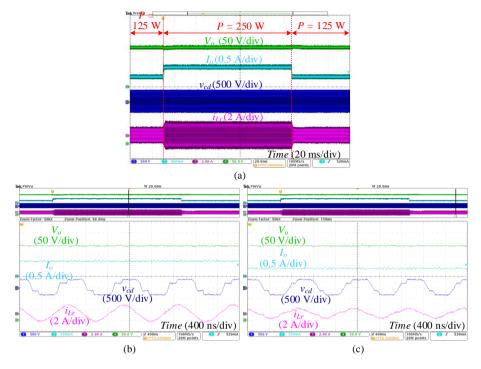

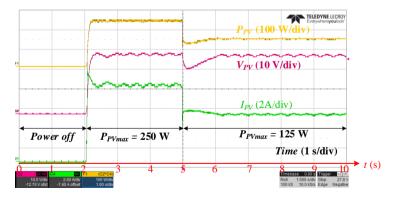

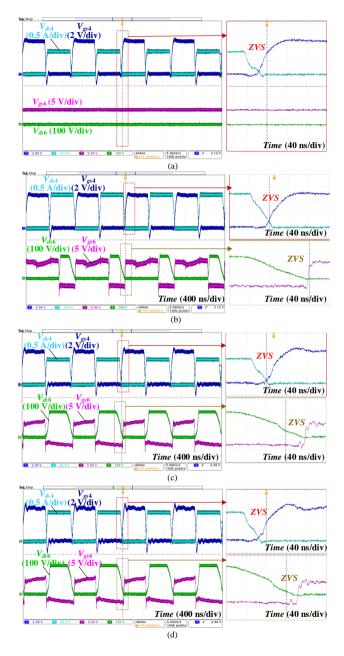

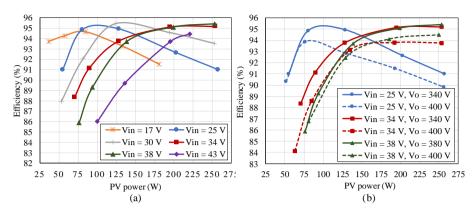

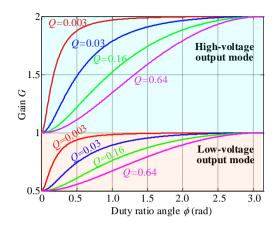

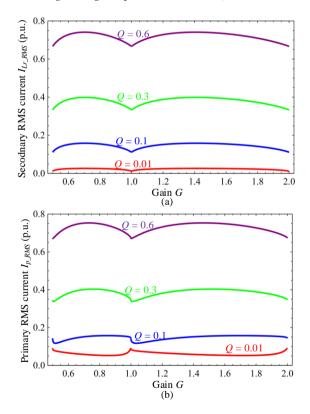

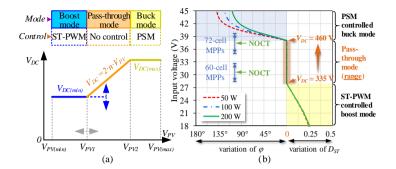

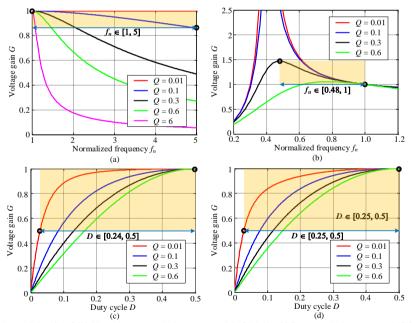

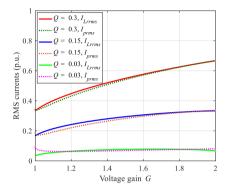

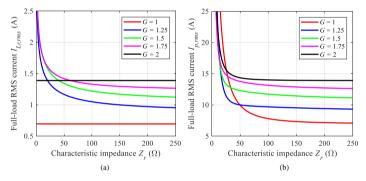

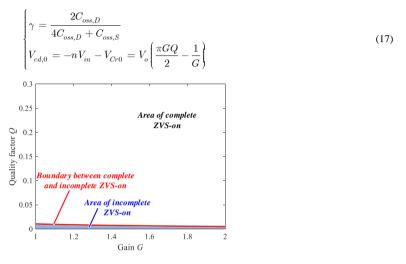

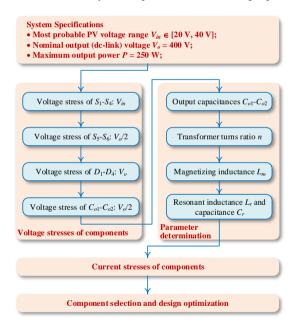

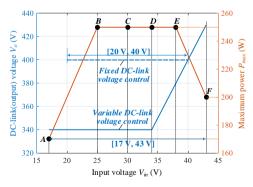

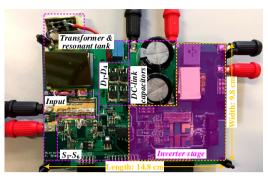

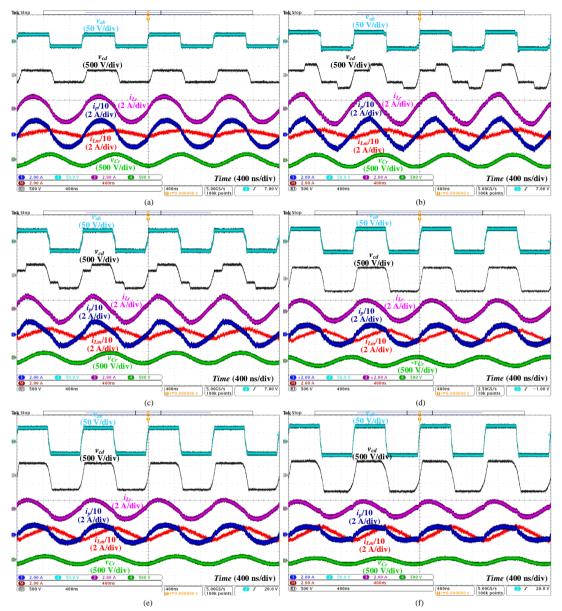

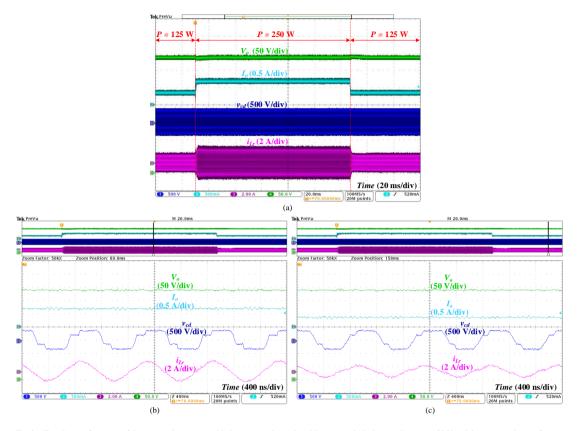

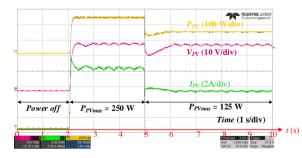

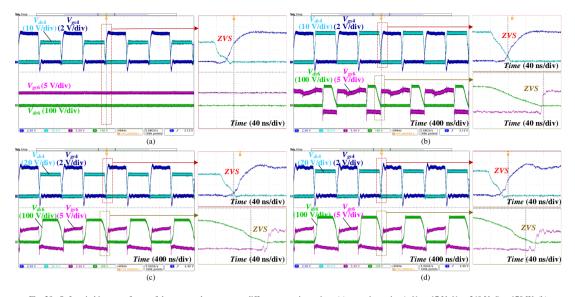

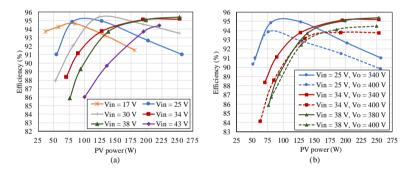

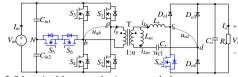

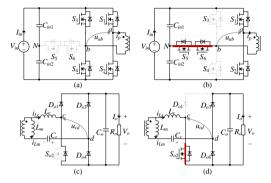

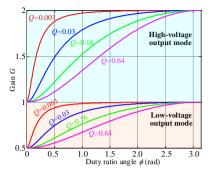

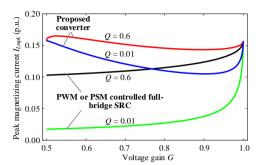

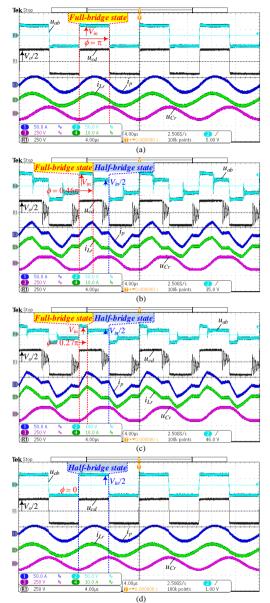

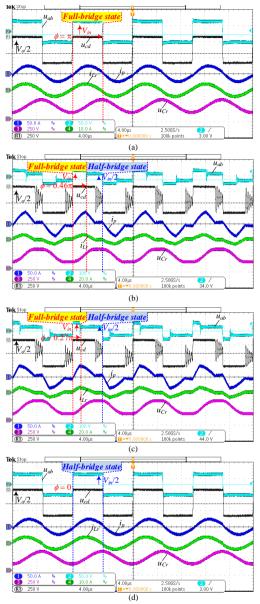

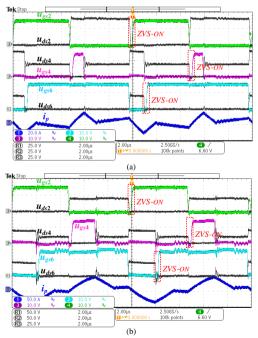

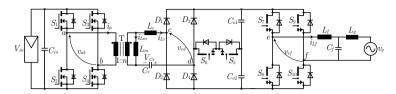

The DC-DC stage of a two-stage PV microinverter is required to handle a wide input voltage range while maintaining high efficiencies. This chapter proposes a new isolated series resonant DC-DC converter topology suitable for PV microinverter systems. Compared with the conventional series resonant converter (SRC), a dual-mode rectifier is formed on the secondary side, which enables a twofold voltage gain range for the proposed converters with a fixed-frequency phase-shift modulation scheme. The zero-voltage switching (ZVS) turn-on and zero-current switching (ZCS) turn-off can be achieved for active switches and diodes, respectively, thereby reducing the switching losses. A variable dc-link voltage control scheme is introduced to the studied converter, yielding a remarkable efficiency improvement and inputvoltage range extension. The operation principle of the proposed converter is first detailed and then the essential characteristics, i.e., the voltage gain, softswitching, and root-mean-square (RMS) current, are analyzed. After that, the power loss modeling and design optimization of components are conducted. A 1-MHz 250-W converter prototype with 17 V – 43 V input has been built and tested to verify the theoretical analysis and the feasibility of the proposed converter. Additionally, a structure-reconfigurable SRC is also discussed for

Chapter 2. A 1-MHz Series Resonant DC-DC Converter With a Dual-Mode Rectifier for PV Microinverters

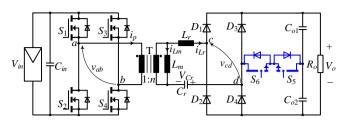

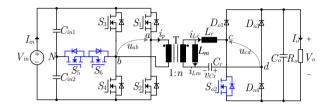

Fig. 2.1: Schematic of the proposed DMR-SRC. Source: [J1].

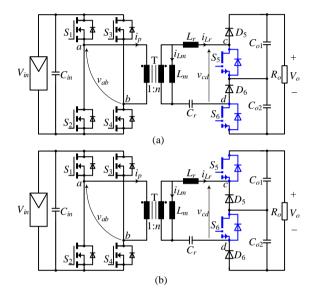

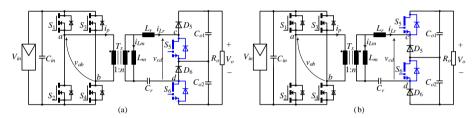

**Fig. 2.2:** Schematics of the extended DMR-SRC topologies for high-voltage output applications: (a) extended topology *A* and (b) extended topology *B*. Source: **[J1**].

the grid-connected PV microinverter systems with a wide-input voltage range and different grid voltage levels, i.e., 110/120 V and 220/230/240 V.

# 2.2 **Operation Principle of the Proposed Converter**

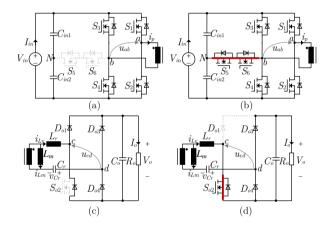

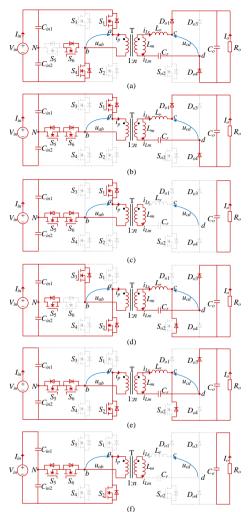

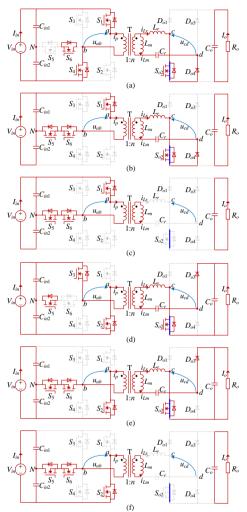

### 2.2.1 Topology Description

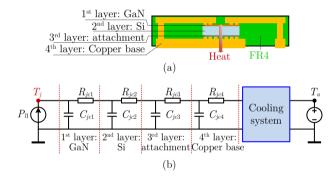

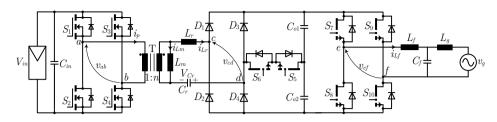

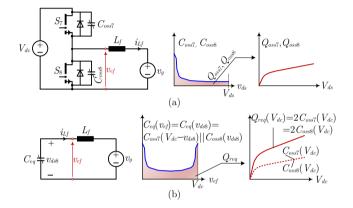

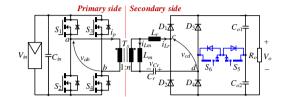

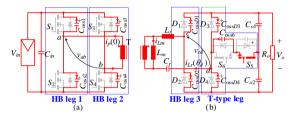

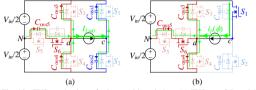

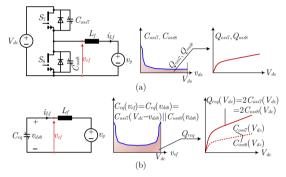

The proposed dual-mode rectifier based series resonant converter (DMR-SRC) is shown in Fig. 2.1 [J1], [111]. It is realized by adding a pair of antiseries transistors  $(S_5 - S_6)$  between the midpoints of the diode leg  $(D_3 - D_4)$ and the output capacitor leg  $(C_{o1}$  and  $C_{o2}$ ) [J1], [111]. Thus, a dual-mode rectifier (DMR) can be formed by controlling the anti-series transistors  $S_5 - S_6$ [J1], [111].

2.2. Operation Principle of the Proposed Converter

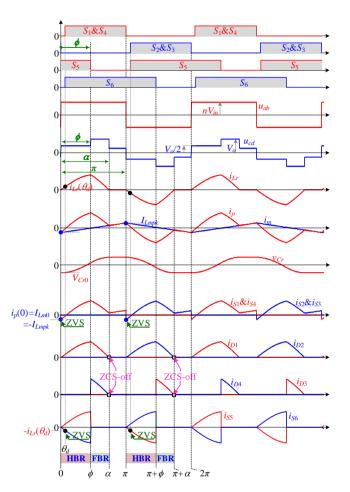

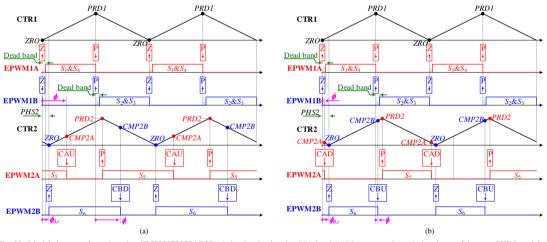

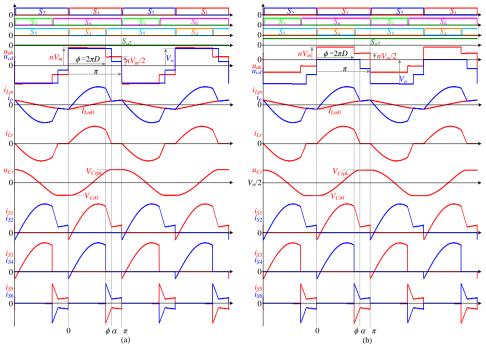

Fig. 2.3: Fixed-frequency phase-shift modulation for the proposed converter shown in Fig. 2.1 and the key operating waveforms. Source: [J1].

- Half-Bridge Rectifier (HBR) mode: when the anti-series transistors S<sub>5</sub> S<sub>6</sub> are triggered on, a half-bridge rectifier (voltage doubler) composed of D<sub>1</sub>, D<sub>2</sub>, S<sub>5</sub>, S<sub>6</sub>, C<sub>01</sub> and C<sub>02</sub> presents on the secondary side [J1], [111];

- Full-Bridge Rectifier (FBR) mode: when  $S_5 S_6$  are disabled, there is a full-bridge rectifier consisting of  $D_1 D_4$  on the secondary side [J1], [111].

Inspired by the dual-mode rectification concept, two extended DMR-SRCs are proposed for high-voltage output applications, as shown in Fig. 2.2. All the secondary diodes and transistors only need to withstand half of the output voltage  $V_0$ . By controlling the secondary-side active switches  $S_5$  and  $S_6$ ,

a dual-mode rectifier can be formed on the secondary side, and as a result, a wide voltage gain can be achieved. Nevertheless, only the basic topology shown in Fig. 2.1 is investigated.

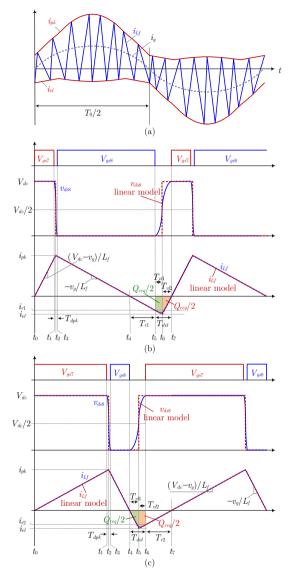

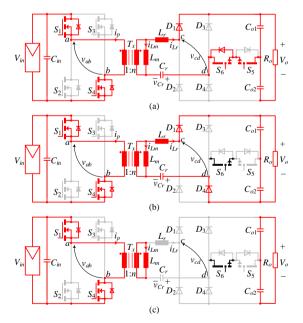

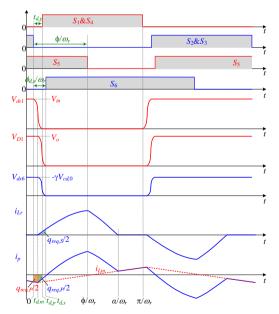

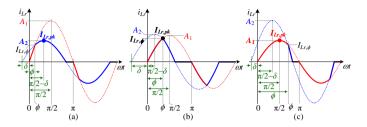

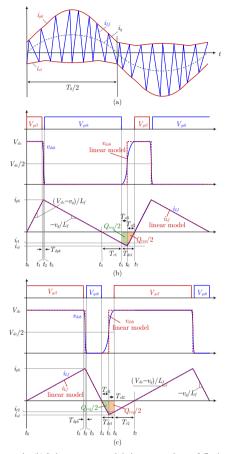

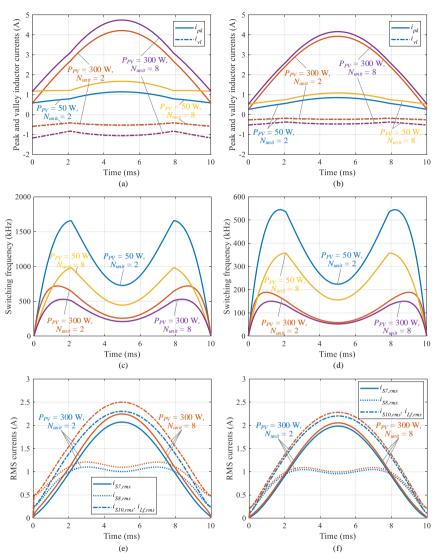

## 2.2.2 Operation Principle

A fixed-frequency phase-shift modulation is applied to the proposed DMR-SRC, as illustrated in Fig. 2.3. The primary-side diagonal switches are driven synchronously, and the upper and lower switches of each leg are phase-shifted by  $\pi$ . On the secondary side, the turn-on instant of  $S_5$  is synchronized with that of  $S_2$  and  $S_3$ , but the turn-off of  $S_5$  is lagged by a phase of with respect to that of  $S_2$  and  $S_3$ . The gate signal of  $S_6$  is shifted by a phase of with that of  $S_5$ . It is noted that the fixed-frequency phase-shift modulation scheme also holds for the two extended topologies shown in Fig. 2.2(a) and (b).

With this modulation scheme, the voltage across the midpoints of the two primary-side switch legs, i.e.,  $v_{ab}$ , is an AC square wave (with an amplitude of  $V_{in}$ ) which applies to the transformer. In addition, the switching frequency  $f_s$  is equal to the series resonant frequency of the resonant inductor  $L_r$  and capacitor  $C_r$ , i.e.,  $f_s = f_r = 1/(2\pi\sqrt{L_rC_r})$ .

The primary-side transformer current  $i_p$  is the sum of the magnetizing current  $i_{Lm}$  and the resonant current  $i_{Lr}$  referred to the primary side, i.e.,  $i_p = n(i_{Lm} + i_{Lr})$ , where *n* represents the transformer turns ratio.

The waveform of capacitor voltage  $v_{Cr}$  has half-wave symmetry, i.e.,  $v_{Cr}(t) = -v_{Cr}(t + T_s/2)$ . Thus, the charge variation of the resonant capacitor over half a switching cycle [0,  $T_s/2$ ] can be obtained as

$$q_{hs} = [v_{Cr}(T_s/2) - v_{Cr}(0)]C_r = -2V_{Cr0}C_r$$

=  $\int_0^{T_s/2} i_{Lr}(t)dt = \int_0^{T_s/2} \frac{i_p(t)}{n}dt - \int_0^{T_s/2} i_{Lm}(t)dt$

=  $\int_0^{T_s/2} \frac{i_p(t)}{n}dt = \frac{T_s}{2nV_{in}} \frac{2}{T_s} \int_0^{T_s/2} [V_{in}i_p(t)]dt = \frac{P}{2nf_rV_{in}}$  (2.1)

where  $V_{Cr0}$  denotes the initial resonant capacitor voltage at t = 0 (see Fig. 2.3), and *P* is the transferred power.

The voltage gain of the converter and the inductors ratio of  $L_m$  to  $L_r$  are defined as  $G = V_0/(nV_{in})$ , and  $m = L_m/L_r$ , respectively. The quality factor is denoted as  $Q = Z_r/R_0 = P/(V_0^2/Z_r)$ , in which the characteristic impedance  $Z_r = \sqrt{L_r/C_r}$ . Thus the quality factor Q is also termed as the normalized power. The initial capacitor voltage  $V_{Cr0}$  can be obtained from (2.1) as

$$V_{Cr0} = \frac{P}{4nf_r C_r V_{in}} = -\frac{\pi G Q V_o}{2}$$

(2.2)

The magnetizing current  $i_{Lm}$  can be expressed as

$$i_{Lm}(\theta) = I_{Lm0} + \frac{nV_{in}}{m\omega_r L_r} \theta = I_{Lm0} + \frac{nV_{in}}{mZ_r} \theta$$

(2.3)

#### 2.2. Operation Principle of the Proposed Converter

where  $\theta = \omega_r t$  with  $\omega_r = 2\pi f_r$  being the resonant angular frequency, and  $I_{Lm0}$  represents the initial magnetizing current at  $\theta = 0$ . The peak magnetizing current  $I_{Lmpk}$  is reached at  $\theta = \pi$  i.e.,  $I_{Lmpk} = i_{Lm}(\pi)$ . Due to the half-wave symmetry of the magnetizing current  $i_{Lm}$ , we have  $I_{Lm0} = i_{Lm}(0) = -i_{Lm}(\pi) = -I_{Lmpk}$ . Then, the peak and initial magnetizing currents can be obtained as

$$I_{Lmpk} = -I_{Lm0} = \frac{\pi n V_{in}}{2mZ_r} = \frac{\pi V_o}{2mZ_r G}$$

(2.4)

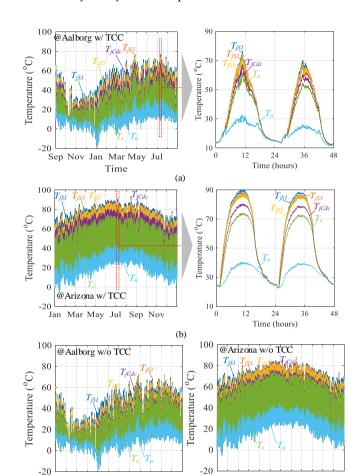

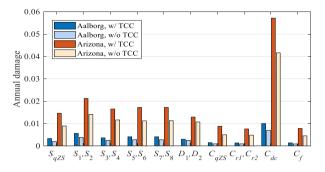

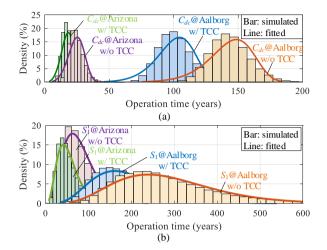

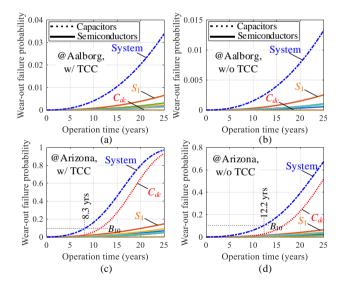

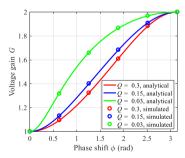

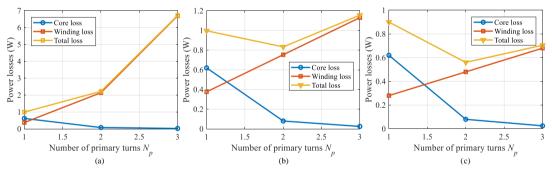

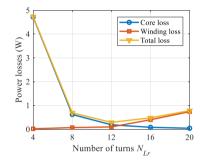

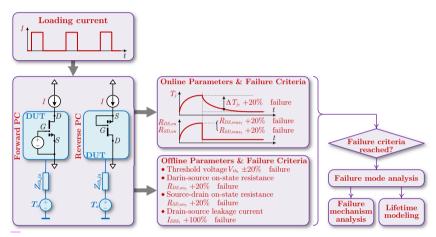

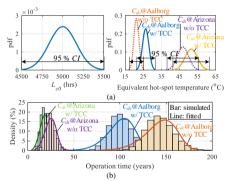

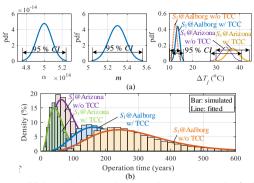

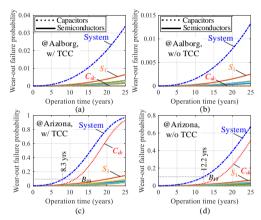

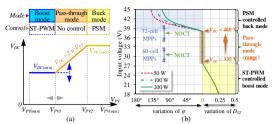

Fig. 2.3 shows the operating waveforms of the proposed converter. Neglecting the deadtime, six stages can be identified over one switching cycle [J1], [111]. Due to the symmetry of operation, only stages I-III over the first half switching cycle  $[0, \pi]$  are described [J1], [111].