Aalborg Universitet

### Interharmonics Analysis and Mitigation in Adjustable Speed Drives

Soltani, Hamid

DOI (link to publication from Publisher): 10.5278/vbn.phd.engsci.00078

Publication date: 2016

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Soltani, H. (2016). Interharmonics Analysis and Mitigation in Adjustable Speed Drives. Aalborg Universitetsforlag. https://doi.org/10.5278/vbn.phd.engsci.00078

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

### INTERHARMONICS ANALYSIS AND MITIGATION IN ADJUSTABLE SPEED DRIVES

BY HAMID SOLTANI

**DISSERTATION SUBMITTED 2016**

AALBORG UNIVERSITY DENMARK

### Interharmonics Analysis and Mitigation in Adjustable Speed Drives

by

Hamid Soltani

A Dissertation Submitted to the Faculty of Engineering and Science at Aalborg University in Partial Fulfillment for the Degree of Doctor of Philosophy in Electrical Engineering

April 2016 Aalborg, Denmark

| Dissertation submitted: | February 28, 2016                                                        |

|-------------------------|--------------------------------------------------------------------------|

| PhD supervisor:         | Professor Frede Blaabjerg<br>Aalborg University                          |

| PhD committee:          | Associate Professor Kaiyuan Lu (chairman)<br>Aalborg University, Denmark |

|                         | Professor JJ Liu<br>Xi'an Jiaotong University, China                     |

|                         | Professor Enrique Romero-Cadaval<br>University of Extremadura, Spain     |

| PhD Series:             | Faculty of Engineering and Science, Aalborg University                   |

ISSN (online): 2246-1248 ISBN (online): 978-87-7112-521-4

Published by: Aalborg University Press Skjernvej 4A, 2nd floor DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Hamid Soltani

Printed in Denmark by Rosendahls, 2016

### MATLAB®

is a trademark of The MathWorks, Inc.. dSPACE® and Control Desk ® are trademarks of dSPACE GmbH. Simulations included in this dissertation are done using the MATLAB® software. For experimental tests in this dissertation, the control system was implemented on the dSPACE® DS1103/1006 PCC Controller Board with the graphic user interface (Control Desk ®). The power converter used for experimental verifications is Danfoss ® VLT FC302. This Ph.D. thesis has been typeset in LATEX2ɛ.

### PUBLIC DEFENCE OF PHD DISSERTATION

### Thesis Title:

Interharmonics Analysis and Mitigation in Adjustable Speed Drives

### Ph.D. Defendant:

Hamid Soltani

### Supervisor: Prof. Frede Blaabjerg

#### **Co-supervisors:**

Dr. Firuz Zare Prof. Poh Chiang Loh

### Assessment Committee:

Assoc. Prof. Kaiyuan Lu (Chairman) Department of Energy Technology Aalborg University Pontoppidanstraede 111 9220 Aalborg, Denmark

Prof. Jinjun Liu School of Electrical Engineering Xi'an Jiaotong University 710049 Xi'an, China

Prof. Enrique Romero-Cadaval

School of Industrial Engineering University of Extremadura Badajoz, Spain

### **Defence Date and Place:**

Thursday, April 28, 2016 Pontoppidanstraede 111, auditorium, Aalborg University

### COPYRIGHT STATEMENTS

This thesis has been submitted to the Faculty of Engineering and Science at Aalborg University for assessment in partial fulfilment for the Degree of Doctor of Philosophy (Ph.D.) in Electrical Engineering. The documented thesis is based on the submitted or published academic papers, which are listed in § 1. Parts of the papers are used directly or indirectly in the extended summary of this thesis. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science. The thesis is **NOT** in its present form acceptable for open publication but only in limited and closed circulation as the copyright may **NOT** be ensured.

Dedicated to my parents for their encouragement and exceptional love.

## Preface

This thesis is written according to the project entitled "Interharmonics Analysis and Mitigation in Adjustable Speed Drives". The Ph.D. project is supported mainly by Iran Ministry of Science, Research and Technology (MSRT) and partially by the Department of Energy Technology, Aalborg University, Denmark.

This research project was done under the supervision of Prof. Frede Blaabjerg and Prof. Poh Chiang Loh from the Department of Energy Technology, Aalborg University, and Dr. Firuz Zare from the Global Research and Development Centre, Danfoss Drives A/S, Denmark. First and foremost, I would like to express my deepest gratefulness to my supervisor, Prof. Frede Blaabjerg, for his constructive discussions, patient guidance and continuous supports in the Ph.D. project period. His extreme inspiration and professional behaviors learned me how I should get through the difficulties during the Ph.D. project. I do believe that the precious lessons I earned under his supervision will deeply influence both my career and personal life. I would also like to give my sincere thanks to my co-supervisor Prof. Poh Chiang Loh for the time he spent to discuss the detail issues with me, and for his valuable guidance at the Ph.D project. Besides, I would like to express my deepest respect to my lovely cosupervisor Dr. Firuz Zare for his inspirational proposals, technical discussions and tremendous encouragements. He was my supervisor at the B.Sc. and M.Sc period, and also my co-supervisor at the Ph.D period. I should say I owe all my knowledge to his brightness and kindness. It was my pleasure to work with him such long time.

My gratitude also goes to Dr. Pooya Davari from the Department of Energy Technology for his useful discussions and great encouragement in the last year of my Ph.D. It was a short period but very constructive.

I would also like to take this opportunity to thank all my colleagues from the Department of Energy Technology for providing a warm environment and full of enthusiasm. My best wishes to my lovely friends - Dr. Qobad Shafiee, Dr. Reza Ahmadi, Dr. Amir Sajjad Bahman, Dr. Alireza Rezaniakolaei, Dr. Bakhtyar Hoseinzadeh, Dr. Seyed-Mostafa Farashbashi-Astaneh, Mohammadkazem Bakhshizadeh and Esmaeil Ebrahimzadeh. Moreover, my special appreciations are extended to John K. Pedersen, Tina Larsen, Corina Busk Gregersen, Mette Skov Jensen, Eva Janik and Casper Jørgensen for their valuable assistance in different ways. Hamid Soltani

February, 2016 Aalborg Øst, Denmark

### Abstract

With the growing use of power electronics technology in different applications, many efforts have simultaneously been devoted to improve the grid quality issues. In this respect, harmonic and interharmonic distortions are among the most important criteria, which are needed to meet the required standards. Meanwhile, issues related to interharmonics have recently gained more attention besides classical harmonics, due to their specific negative effects as well as those common with harmonics. Interharmonic distortions can seriously hamper the normal operation of the power system by means of side effects such as excitation of undesirable electrical and/or mechanical resonances, misoperation of control devices, and so forth. Adjustable Speed Drive (ASD) based on double-stage AC-DC-AC converter is considered as one of the main sources of interharmonics in the grid. Literature survey shows that most of the works focus on analyzing and reducing the harmonics in power system and motor drives, while less attempts are devoted to interharmonic-related issues. In this respect, this Ph.D. project has investigated and evaluated the adjustable speed drive input current interharmonics caused by different sources, and proposed some appropriate solutions to enhance the grid quality. The main scopes of this research work can be introduced as: 1) General study of interharmonic sources and identification in Voltage-Source Inverter (VSI-) fed ASD, 2) Input current interharmonic characterization in a double-stage VSI-fed ASD, and 3) Mitigation of ASD's input current interharmonics due to motor current imbalance.

Chapters 2 and 3 present a general study on the harmonic and interharmonic sources and detections in the ASD. The study is particularly performed with respect to a VSI-fed ASD with very low switching frequency and a naturally sampled Sinusoidal Pulse Width Modulation (SPWM) strategy in Chapter 2. Then, some practical challenges associated with interharmonics detection are followed in Chapter 3. A thorough discussion introduces the existing desynchronized interharmonics detection method, which in this thesis is applied as highly accurate measurement strategy.

Thereafter, the ASD input current interharmonics are evaluated in Chapters 4 and 5 with respect to the inverter's modulation strategy, and to the ASD's passive filter effects. In Chapter 4, the symmetrical regularly sampled SPWM, Space Vector Modulation (SVM), and Discontinuous Pulse Width Modula-

tion (DPWM2), and also the asymmetrical regularly sampled SVM modulation techniques are chosen as the most popular modulation strategies applied in the motor drive applications. A frequency mapping characterizes the ASD's input current interharmonic locations. Then, it recommends the suitable strategy associated with the fixed-frequency switching methods (e.g., SPWM, SVM, and DPWM2) in order to reduce the drive input current interharmonic components. Chapter 5 investigates the effects of the ASD's passive filters (AC choke, DC choke, and DC-link capacitor) on the input current interharmonics caused by motor current imbalance. This investigation has been carried out in both cases of the balanced and the unbalanced load conditions.

In Chapter 6, some active compensation methods are proposed in order to mitigate the ASD's input current interharmonics generated by the motor current imbalance. In the case of partially-controlled ASD, where an inverter is connected to the front-end diode rectifier back-to-back sharing a common DC link, the AC- and/or DC- side active compensators are proposed for input current interharmonics reduction. Moreover, in the case of a fully-controlled ASD (a back-to-back converter), the drive input current interharmonics are mitigated by proposing an appropriate control strategy.

The contribution of this research work is a better understanding of the drive input current interharmonics with respect to different modulation techniques. It investigates the interharmonics issue both in cases of balanced and unbalanced load conditions. Appropriate solutions are proposed in order to reduce the drive input current interharmonics. It is expected that the outcome of this work would be helpful for people investigating the origin of interharmonics, and looking for new potential strategies for their reduction.

## Dansk Abstrakt

Med den stigende brug af effektelektronik i forskellige applikationer har der været gjort bestræbelser på at forbedre spændings-kvaliteten af elnettet, eksempelvis styret i form af nye standarder. I denne forbindelse er harmoniske og interharmoniske forvrængninger blandt de mest vigtige kriterier, som er nødvendige for at opfylde standarder, der er gældende for effektelektronisk apparater. I den sidste tid har spørgsmål vedrørende interharmoniske fået en større opmærksomhed ud over de klassiske harmoniske forstyrrelser på grund af deres specifikke negative påvirkninger, såvel som dem der er fælles med de harmoniske problemer. Interharmoniske kan forstyrre den normale drift via bivirkninger som excitation af uønskede elektrisk og/eller mekaniske resonanser, eller forstyrrelser i selve reguleringen og kommunikationen. Motorstyringer baseret på et to-trins AC-DC-AC konverter betragtes som en af de vigtigste kilder til interharmoniske i el-nettet. Undersøgelser viser, at den primære litteratur fokuserer på at analysere og reducere harmoniske i el-systemet og motor drev, mens langt færre forsøger at afdække de interharmoniske problemer. Derfor har dette Ph.D. projekt undersøgt og evalueret motorstyringers nuværende interharmoniske på el-nettet forårsaget af forskellige kilder, og har foreslået nogle passende løsninger til at forbedre el-nettets kvalitet. De vigtigste anvendelsesområder for dette forskningsarbejde kan introduceres som: 1) Generel undersøgelse af interharmoniske kilder og deres identifikation i frekvensomformer-styret motorer, 2) Interharmonisk karakterisering i en motorstyring, og 3) Reduktion af motorstyringens interharmoniske på grund af ubalance i motorstrømmen.

Kapitel 2 og 3 foretager en generel undersøgelse af de harmoniske og interharmoniske kilder i motorstyringer. Studierne er især udført i forhold til at en Voltage Source Inverter fødet motor med en relativ lav skifte frekvens er anvendt og som samtidig anvender en naturligt samplet Sinus-formet Pulse Width Modulations (SPWM) strategi. Derefter er der nogle praktiske udfordringer forbundet med interharmonisk detektion, som er beskrevet i detaljer i kapitel 3. Efter diskussionen introduceres eksisterende asynkrone interharmonisk detektions metoder, som i denne afhandling er anvendt som en meget nøjagtig måle-strategi.

Derefter bliver de interharmoniske strømme på net-siden evalueret i kapitel 4 og 5 i forhold til motorstyringens modulations strategi, og i forhold til de

passive filter-effekter i mellemkredsen. I kapitel 4 undersøges den symmetrisk naturligt samplet SPWM, Space Vector Modulation (SVM), og Diskontinuerlig Pulse Width Modulation (DPWM2), og også den asymmetriske naturlig samplet SVM modulation teknikker som er valgt da de er de mest populære modulations strategier i motordrev applikationer. En detaljeret kortlægning af de nuværende interharmoniske strømme på net-siden er foretaget. Dernæst anbefales en passende kompenseringsstrategi med fast skifte frekvens (fx SPWM, SVM, og DPWM2) for at reducere motorstyringens net-side interharmoniske komponenter. I kapitel 5 undersøges virkningerne af motorstyringens passive filtre (AC spole, DC spole, og DC-link kondensator) på net-siden, når de interharmoniske er forårsaget af motorstrøms ubalance.

I kapitel 6 er der foreslået nogle aktive kompensations-metoder til at kunne afbøde net-sidens interharmoniske, som igen er skabt af motorens ubalance. I tilfælde af at en delvis kontrolleret motorstyring anvendes, hvor en inverter er forbundet med en diode ensretter tilsluttet el-nettet, er en aktiv AC- og DC- side kompensationsmetode foreslået for at kunne reducere net-sidens interharmoniske. Endvidere i tilfælde af en fuldt kontrolleret motorstyring (en back-to-back konverter) er anvendt, vil de skabte interharmoniske kunne afbødes ved en ny foreslået kontrolstrategi.

Bidragene i denne PhD afhandling er en bedre forståelse af de interharmoniske på net-siden som stammer fra motor-styringen via forskellige modulations metoder. Afhandlingen undersøger også de interharmoniske både i tilfælde af balanceret og ubalanceret belastningsforhold på motor-siden. Passende løsninger foreslås til at kunne reducere de interharmoniske fra motorstyringen. Det forventes, at resultatet af dette arbejde ville være nyttigt for folk, der undersøger oprindelsen af interharmoniske, og undersøger nye potentielle strategier til at kunne reducere dem.

## Contents

| Pref            | face         |                                                                                         | vii            |

|-----------------|--------------|-----------------------------------------------------------------------------------------|----------------|

| Abs             | tract        |                                                                                         | ix             |

| Dan             | sk Abstrak   | t                                                                                       | xi             |

| $\mathbf{List}$ | of Figures   |                                                                                         | xvii           |

| $\mathbf{List}$ | of Tables    | 2                                                                                       | cxiii          |

| Par             | t I Repor    | ·t                                                                                      | 1              |

| 1               | Introducti   |                                                                                         | 3              |

|                 | 1.1          | Background and motivation1.1.1Harmonic distortions1.1.2Interharmonic distortions        | $3 \\ 3 \\ 4$  |

|                 | $1.2 \\ 1.3$ | Project motivation                                                                      | 5 7            |

|                 | 1.4          | Thesis outline                                                                          | 7              |

|                 | 1.5          | List of publications                                                                    | 9              |

| <b>2</b>        | Harmonics    | and Interharmonics in VSI-fed ASD                                                       | 11             |

|                 | 2.1          | Introduction                                                                            | 11             |

|                 | 2.2          | Harmonic analysis                                                                       | 12<br>12<br>14 |

|                 | 2.3          | Interharmonic analysis                                                                  | 17             |

|                 | 2.4          | Summary                                                                                 | 20             |

| 3               | Interharm    | onic Identification                                                                     | <b>21</b>      |

|                 | 3.1          | Introduction                                                                            | 21             |

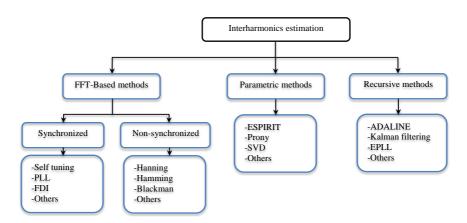

|                 | 3.2          | Interharmonic estimation methods                                                        | 22             |

|                 |              | 3.2.1 FFT-based methods                                                                 | 22             |

|                 |              | 3.2.2 Parametric methods                                                                | 23             |

|                 |              | $3.2.3 \qquad \text{Recursive methods} \dots \dots \dots \dots \dots \dots \dots \dots$ | 24             |

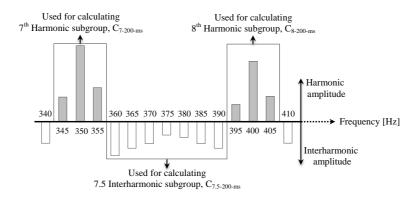

|                 | 3.3          | Harmonics and interharmonics in standard framework                                      | 24             |

|                 | 3.4          | Desynchronized processing technique                                                     | 30             |

|                 | 3.5          | Summary                                                                                 | 34             |

| 4 | Interharm  | nonic Cł | naracterization in ASD                                       |

|---|------------|----------|--------------------------------------------------------------|

|   | 4.1        | Introdu  | letion                                                       |

|   | 4.2        | Harmon   | nics transfer at inverter level                              |

|   |            | 4.2.1    | Symmetrical regularly sampled strategy                       |

|   |            | 4.2.2    | Asymmetrical regularly sampled strategy                      |

|   | 4.3        | Harmon   | nics transfer at the rectifier level                         |

|   | 4.4        | Hardwa   | are setup and practical implementation                       |

|   |            | 4.4.1    | Hardware setup                                               |

|   |            | 4.4.2    | Measurement                                                  |

|   | 4.5        | Simulat  | tion and laboratory test results                             |

|   |            | 4.5.1    | Symmetrical regularly sampled SPWM mod-<br>ulation technique |

|   |            | 4.5.2    | Symmetrical regularly sampled SVM modu-                      |

|   |            | 1.0.2    | lation technique                                             |

|   |            | 4.5.3    | Symmetrical regularly sampled DPWM2 mod-                     |

|   |            | 1.0.0    | ulation technique                                            |

|   |            | 4.5.4    | Asymmetrical regularly sampled SVM modu-                     |

|   |            | 1.0.1    | lation technique                                             |

|   | 4.6        | Conclus  |                                                              |

|   | -          |          |                                                              |

| ) |            |          | omponents Effects on Input Current In-                       |

|   | terharmo   |          |                                                              |

|   | 5.1        | Introdu  |                                                              |

|   | 5.2        |          | nced load conditions                                         |

|   |            | 5.2.1    | Interharmonics initiated by load current im-                 |

|   |            |          | balance                                                      |

|   | <b>F</b> 0 | 5.2.2    | Effect of passive components                                 |

|   | 5.3        |          | ed load conditions                                           |

|   | 5.4        | Conclus  | sion                                                         |

|   | Interharn  | nonic Mi | itigation in Partially- and Fully-Controlled                 |

|   | ASDs       |          | 0 0                                                          |

|   | 6.1        | Introdu  | letion                                                       |

|   | 6.2        | Partiall | y-controlled ASD                                             |

|   |            | 6.2.1    | Shunt active power filter (SAPF)                             |

|   |            | 6.2.2    | DC-link active capacitor                                     |

|   | 6.3        | Fully-co | ontrolled ASD                                                |

|   | 0.0        | 6.3.1    | Sources 1 and 2 related to DC voltage ripple                 |

|   |            | 6.3.2    | Source 3 related to DC current ripple                        |

|   |            | 6.3.3    | Mitigation of sources 1 and 2 related to DC                  |

|   |            | 0.0.0    | voltage ripple                                               |

|   |            | 6.3.4    | Mitigation of source 3 related to DC current                 |

|   |            | 0.3.4    | ripple                                                       |

|   |            | 6.3.5    |                                                              |

|   | 6.4        |          | Proposed methodology                                         |

|   | 0.4        | Conclus  | 51011                                                        |

| 7              | Conclusion  | 1                                                      | 91  |

|----------------|-------------|--------------------------------------------------------|-----|

|                | 7.1         | Summary                                                | 91  |

|                | 7.2         | Contributions in the thesis                            | 92  |

|                | 7.3         | ${\rm Future \ work}\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$ | 93  |

| Bił            | oliography  |                                                        | 95  |

| Pa             | rt II Publi | cations                                                | 101 |

| Journal Papers |             |                                                        | 103 |

| Co             | nference Co | ntributions                                            | 105 |

Contents

# List of Figures

| $1.1 \\ 1.2 \\ 1.3$ | Typical structure of a voltage sourced adjustable speed drive<br>A typical ASD's equivalent DC-link resonance amplification<br>Thesis structure with a report and publication part                                  | 5<br>6<br>8 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.1                 | Block diagram of a double-stage voltage sourced ASD with the associated harmonics and interharmonics interaction.                                                                                                   | 12          |

| 2.2                 | Typical structure of a six-pulse diode rectifier connected to a stiff grid                                                                                                                                          | 13          |

| 2.3                 | Diode rectifier voltages and currents waveforms. (a) Three-phase<br>input voltages. (b) DC-link voltage. (c) DC-link current with infi-<br>nite size inductor. (d) DC-link current with finite size inductor. (e)   |             |

|                     | Input current with infinite size inductor.                                                                                                                                                                          | 13          |

| 2.4                 | PWM inverter feeding three-phase Induction Motor (IM).                                                                                                                                                              | 15          |

| 2.5                 | Synchronous sinusoidal PWM: (a) $C_{UO}$ is the sinusoidal modulation signal for the phase U, and, $\Delta$ is the carrier signal, (b) $v_{UO}$ is the                                                              |             |

|                     | output voltage pulse train with reference to Figure 2.4                                                                                                                                                             | 15          |

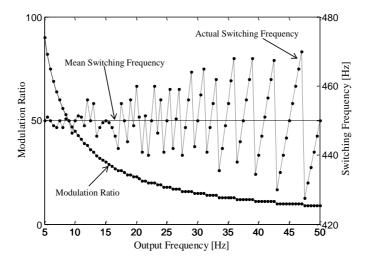

| 2.6                 | The inverter modulation ratio $m_f$ and the switching frequency $f_{sw}$ when implementing the synchronous SPWM.                                                                                                    | 19          |

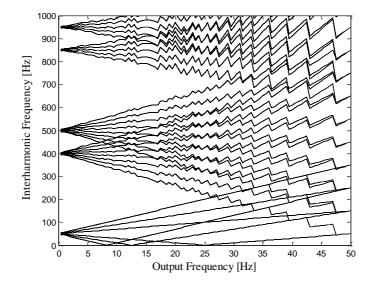

| 2.7                 | The drive input current interharmonic frequency versus output fre-<br>quency, obtained using equation (2.15), with $m = 1$ , modulation<br>ratio $m_f$ as given in Figure 2.6, and $(p,r) = \{(0,2), (0,4), (0,6),$ |             |

|                     | $(1,1), (1,3), (1,5), (1,7), (2,0), (2,2), (2,4)$ }                                                                                                                                                                 | 20          |

| 3.1                 | Classification of the interharmonic estimation methods.                                                                                                                                                             | 22          |

| 3.2                 | Harmonics and interharmonics grouping based on IEC 61 000-4-30.                                                                                                                                                     | 24          |

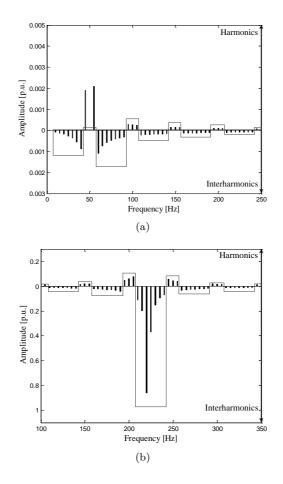

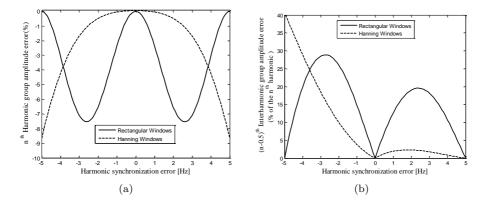

| 3.3                 | Frequency spectrum and grouping bars of the signal when applying<br>a 200 ms rectangular window width, (a) The signal is a sinusoidal<br>tone with amplitude of 1 p.u. and frequency of 50.01 Hz. (b) The           |             |

|                     | signal is an interharmonic with amplitude of 1 p.u. and frequency                                                                                                                                                   |             |

| ~ .                 | of 221.5 Hz.                                                                                                                                                                                                        | 26          |

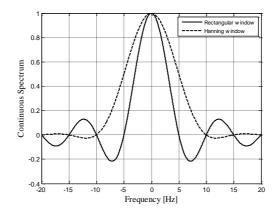

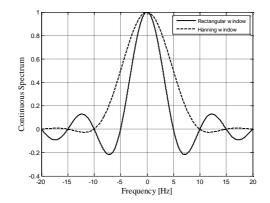

| 3.4                 | Continuous spectrum of Rectangular Window (RW) and Hanning Window (HW)                                                                                                                                              | 27          |

|                     |                                                                                                                                                                                                                     |             |

| 3.5 | Frequency spectrum and grouping bars of the signal with applying<br>a 200 ms width Hanning window, (a) The signal is a sinusoidal tone<br>with amplitude of 1 p.u. and frequency of 50.01 Hz. (b) The signal<br>is an interharmonic with amplitude of 1 p.u. and frequency of 221.5                                             |          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | Hz                                                                                                                                                                                                                                                                                                                              | 28       |

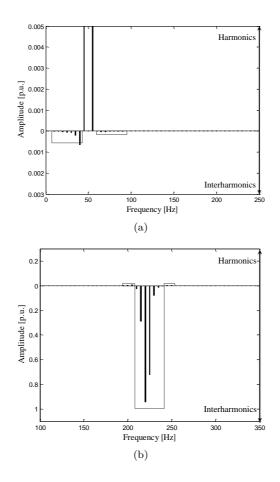

| 3.6 | Sensitivity analysis of the group amplitude error when applying dif-<br>ferent windowing techniques. (a) $n^{th}$ HG amplitude error with re-<br>spect to harmonic synchronization error. (b) $(n - 0.5)^{th}$ IG ampli-                                                                                                        |          |

| 3.7 | tude error with respect to harmonic synchronization error A typical power system signal waveform, which is composed of the                                                                                                                                                                                                      | 29       |

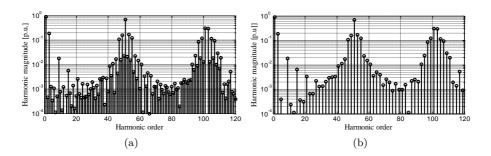

| 3.8 | harmonic and interharmonic tones listed in Table 3.1 Spectral components of the signal given in Table 3.1, by applying (a)                                                                                                                                                                                                      | 31       |

| 3.9 | RW complying IEC procedure. (b) HW complying IEC procedure.<br>Spectral components of the signal given in Table 3.1, by applying (a)<br>Desynchronized RW complying IEC procedure. (b) Desynchronized                                                                                                                           | 32       |

|     | HW complying IEC procedure.                                                                                                                                                                                                                                                                                                     | 33       |

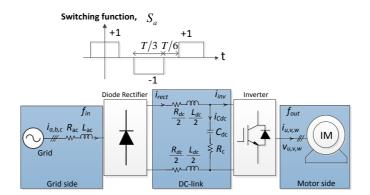

| 4.1 | Equivalent circuit diagram of an adjustable-speed drive for system analysis with an Induction Motor (IM).                                                                                                                                                                                                                       | 36       |

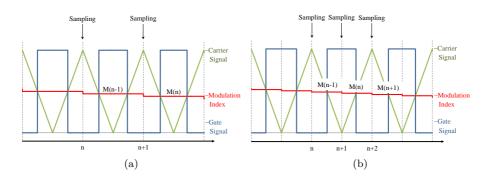

| 4.2 | Modulation schemes. (a) Model of the symmetrical regularly sam-<br>pled modulation strategy with the corresponding gate signal. (b)<br>Model of the asymmetrical regularly sampled modulation strategy                                                                                                                          |          |

| 4.3 | with the corresponding gate signal                                                                                                                                                                                                                                                                                              | 38<br>39 |

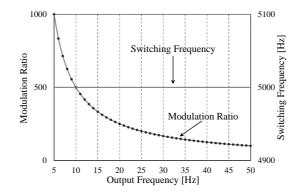

| 4.4 | The inverter switching frequency and the corresponding modulation ratio at different output frequency $f_o$ variation ranges.                                                                                                                                                                                                   | 43       |

| 4.5 | ASD input current $i_a$ interharmonics frequency location with re-<br>spect to output frequency $f_o$ variations, (a) By applying the sym-<br>metrical modulation method using (4.22). (b) By applying the<br>asymmetrical modulation method using (4.23).                                                                      | 44       |

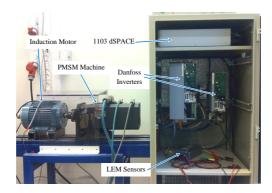

| 4.6 | Laboratory setup for experimental verification.                                                                                                                                                                                                                                                                                 | 45       |

| 4.7 | Continuous spectrum of Rectangular Window (RW) and Hanning Window (HW)                                                                                                                                                                                                                                                          | 46       |

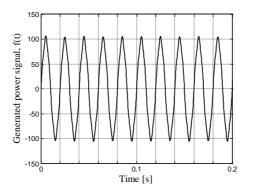

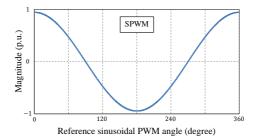

| 4.8 | Phase- $u$ reference waveform for SPWM scheme with modulation index $M=0.945$ .                                                                                                                                                                                                                                                 | 47       |

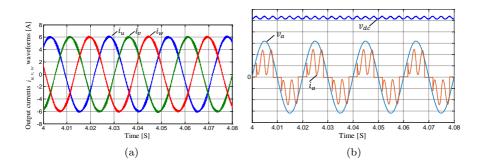

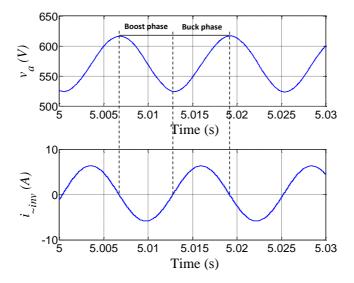

| 4.9 | (a) The simulated three-phase motor currents $i_{u,v,w}$ waveforms, (b) The simulated input current $i_a$ (2.5 A/div), input phase voltage $v_a$ (100 V/div), and DC-link voltage $v_{dc}$ (100 V/div) waveforms, when the induction motor is operating at the output frequency $f_o = 40$ Hz and a load torque value of 12 Nm. | 47       |

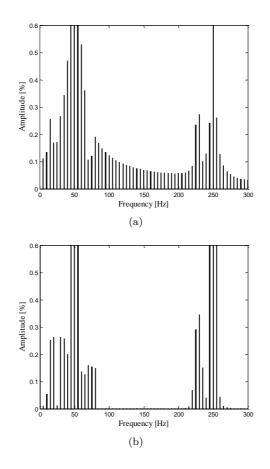

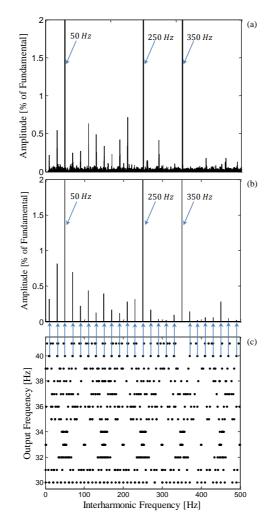

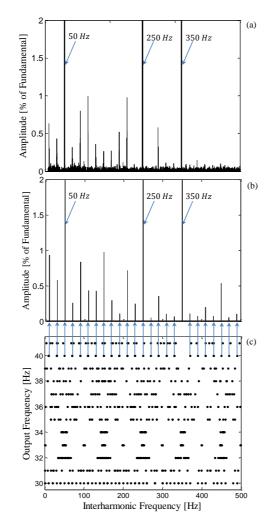

| 4.10  | Drive input current $i_a$ interharmonics at the output frequency $f_o =$                                                                                                                                                                                                                   |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | 40 Hz and load torque of 12 Nm by applying SPWM technique:                                                                                                                                                                                                                                 |    |

|       | (a) Experimental results, (b) Simulation results, and (c) Output                                                                                                                                                                                                                           | 48 |

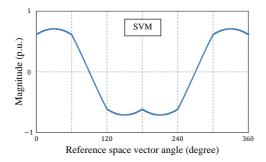

| 1 1 1 | frequency versus interharmonic frequencies. $\dots$ Phase- $u$ reference waveform for SVM scheme with modulation index                                                                                                                                                                     | 40 |

| 4.11  | M=0.818.                                                                                                                                                                                                                                                                                   | 49 |

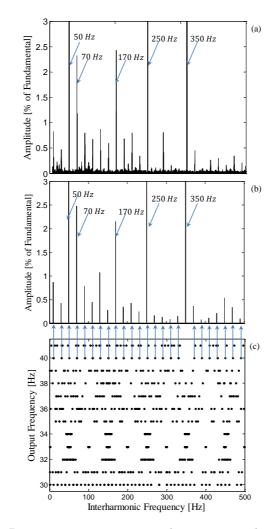

| 4 1 9 | Drive input current $i_a$ interharmonics at the output frequency $f_o =$                                                                                                                                                                                                                   | 49 |

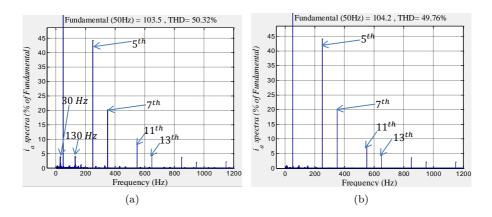

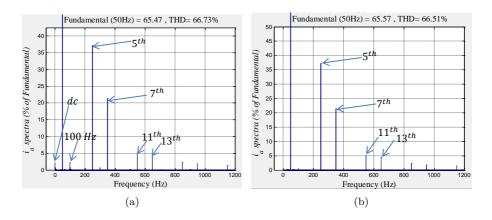

| 4.12  | 40 Hz and load torque of 12 Nm by applying SVM technique: (a) Experimental results, (b) Simulation results, and (c) Output frequency versus interharmonic frequencies                                                                                                                      | 50 |

| 4.13  | Phase- $u$ reference waveform for DPWM2 scheme with modulation index $M=0.818$ .                                                                                                                                                                                                           | 51 |

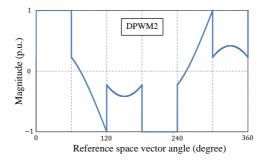

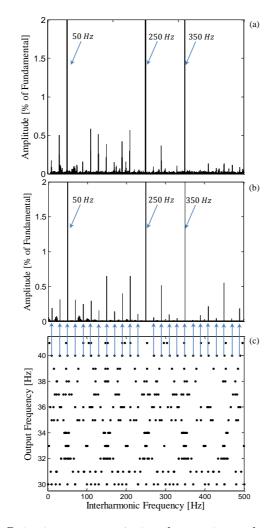

| 4.14  | Drive input current $i_a$ interharmonics at the output frequency $f_o = 40$ Hz and load torque of 12 Nm by applying DPWM2 technique:                                                                                                                                                       | 01 |

|       | (a) Experimental results, (b) Simulation results, and (c) Output frequency versus interharmonic frequencies.                                                                                                                                                                               | 52 |

| 4.15  | Drive input current $i_a$ interharmonics at the output frequency $f_o = 40$ Hz and load torque of 12 Nm by applying an asymmetrical regularly sampled SVM modulation technique: (a) Experimental result, (b) Simulation result, and (c) Output frequency versus interhar-                  |    |

|       | monic frequencies.                                                                                                                                                                                                                                                                         | 53 |

| 5.1   | Equivalent circuit of an adjustable-speed drive for system analysis with an induction motor (IM).                                                                                                                                                                                          | 56 |

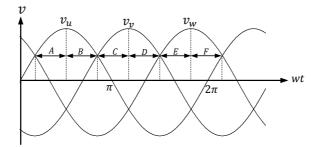

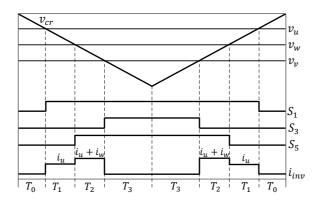

| 5.2   | Three-phase output reference signals divided into six intervals (A $\rightarrow$ F)                                                                                                                                                                                                        | 57 |

| 5.3   | PWM and DC-link inverter-side current waveforms in interval A                                                                                                                                                                                                                              | 58 |

| 5.4   | DC-link equivalent circuit for motor drive                                                                                                                                                                                                                                                 | 59 |

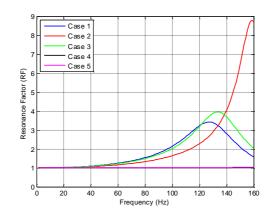

| 5.5   | DC-link RFs associated with Cases 1–5.                                                                                                                                                                                                                                                     | 60 |

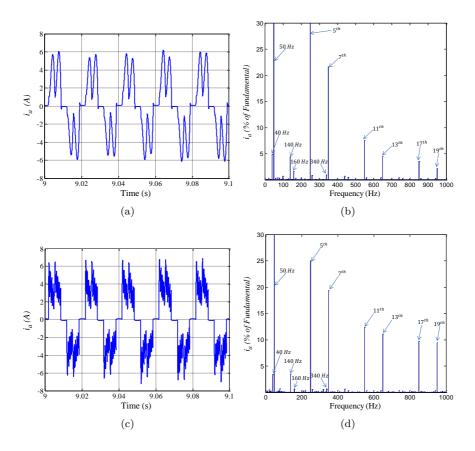

| 5.6   | Drive input current $i_a$ waveforms and frequency spectrum at load<br>torque $T_L$ value of 12 Nm, and an output frequency $f_{out}$ of 45 Hz<br>with cases from Table I. (a) Input current waveform in Case 1. (b)<br>Input current spectra in Case 1. (c) Input current waveform in Case |    |

|       | 5. (d) Input current spectra in Case 5                                                                                                                                                                                                                                                     | 61 |

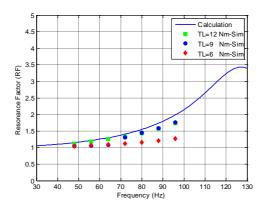

| 5.7   | Simulated and calculated DC-link resonance factor associated with                                                                                                                                                                                                                          | 00 |

| -     | Case 1 at different output frequencies and load torque values                                                                                                                                                                                                                              | 62 |

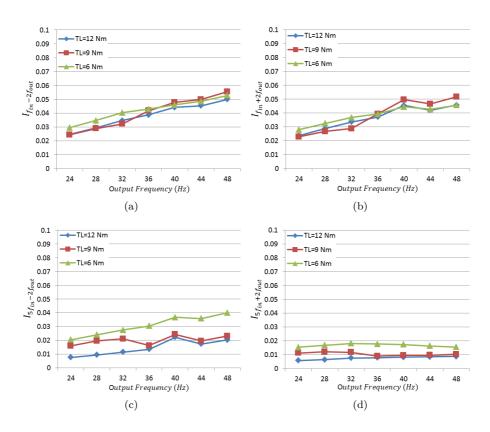

| 5.8   | Simulated normalized input current interharmonic components in                                                                                                                                                                                                                             |    |

|       | Case 1 (see Table 5.1) versus output frequencies of the ASD at different load torque $T_L$ values. (a) Interharmonics coupled with                                                                                                                                                         |    |

|       | and below the fundamental frequency $I_{f_{in}-2f_{out}}$ . (b) Interharmonics                                                                                                                                                                                                             |    |

|       | coupled with and above the fundamental frequency $I_{f_{in}+2f_{out}}$ . (c)                                                                                                                                                                                                               |    |

|       | Interharmonics coupled with and below the fifth-order frequency $I_{5f_{in}-2f_{out}}$ . (d) Interharmonics coupled with and above the fifth-                                                                                                                                              |    |

|       | order frequency $I_{5f_{in}+2f_{out}}$ .                                                                                                                                                                                                                                                   | 63 |

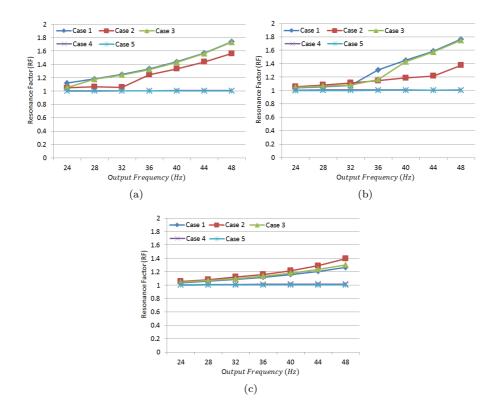

| 5.9                                       | Simulated DC-link resonance factors associated with Cases 1–5 versus different output frequencies of the ASD. (a) load torque equal to 12 Nm. (b) load torque equal to 9 Nm. (c) load torque equal to 6 Nm.                                                                                                                                                                                                                   | 64       |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

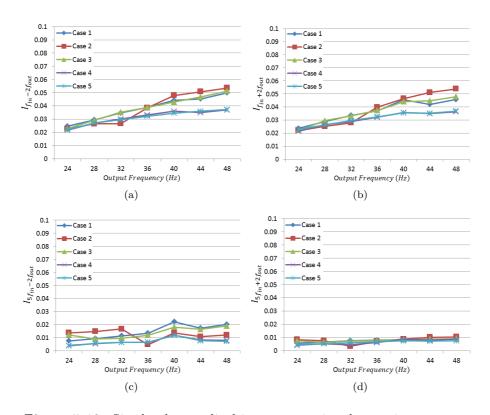

| 5.10                                      | Simulated normalized input current interharmonic components in Cases 1–5 versus output frequencies of the ASD at the load torque $T_L$ equal to 12 Nm. (a) Interharmonics coupled with and below the fundamental frequency $I_{fin-2fout}$ . (b) Interharmonics coupled with and above the fundamental frequency $I_{fin+2fout}$ . (c) Interharmonics coupled with and below the fifth-order frequency $I_{5fin-2fout}$ . (d) | 04       |

| 5.11                                      | Interharmonics coupled with and above the fifth-order frequency $I_{5f_{in}+2f_{out}}$                                                                                                                                                                                                                                                                                                                                        | 65       |

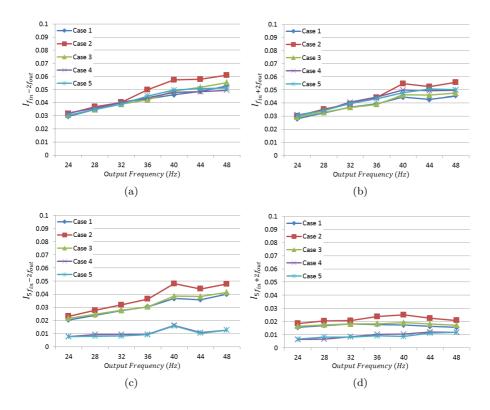

| 5.12                                      | $I_{5f_{in}+2f_{out}}$                                                                                                                                                                                                                                                                                                                                                                                                        | 66       |

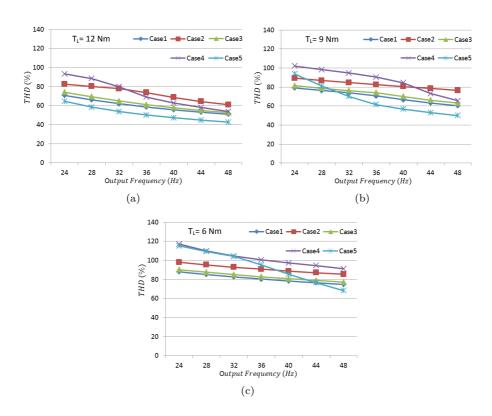

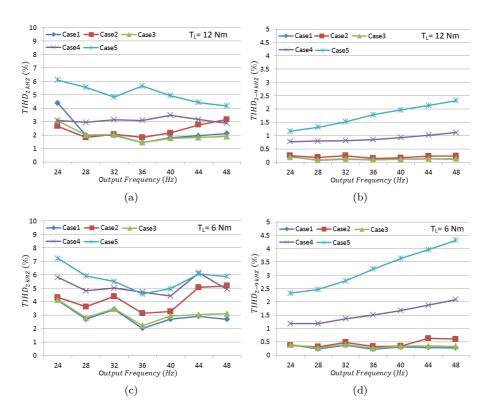

| 5.13                                      | torque equal to 9 Nm. (c) load torque equal to 6 Nm Simulated input current total interharmonic distortions in Cases 1–<br>5 versus output frequencies of the ASD. (a) $\text{TIHD}_{2kHz}$ at the load<br>torque of 12 Nm. (b) $\text{TIHD}_{2-9kHz}$ at the load torque of 12 Nm.<br>(c) $\text{TIHD}_{2kHz}$ at the load torque of 6 Nm. (d) $\text{TIHD}_{2-9kHz}$ at the<br>load torque of 6 Nm                          | 68<br>69 |

| 6.1                                       | Equivalent circuit of an adjustable-speed drive for system analysis                                                                                                                                                                                                                                                                                                                                                           |          |

| 6.2                                       | with an induction motor (IM)                                                                                                                                                                                                                                                                                                                                                                                                  | 72       |

| 6.3                                       | current $i_a$ spectra                                                                                                                                                                                                                                                                                                                                                                                                         | 73       |

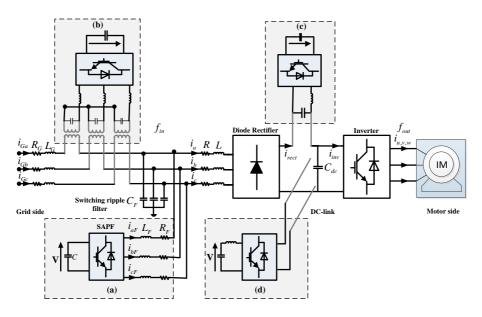

|                                           | series active compensator, d) DC-link shunt active compensator.                                                                                                                                                                                                                                                                                                                                                               | 75       |

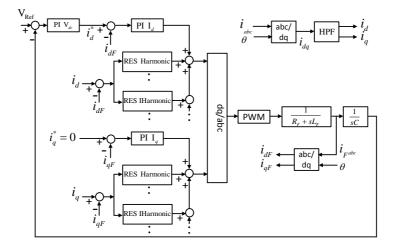

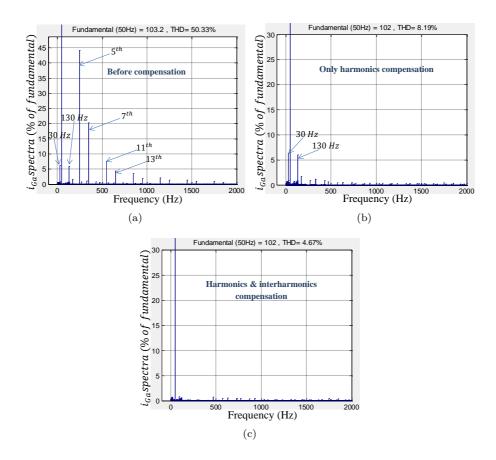

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Control block diagram for the shunt APF shown in Figure 6.3(a)<br>Grid current spectra at a load torque, $T_L$ , equal to 460 Nm, $f_{out}=40$ Hz and with a 5% motor current imbalance. (a) Before compensation, (b) After harmonics compensation and (c) After harmonics                                                                                                                                                    | 76       |

|                                           | and interharmonics compensation.                                                                                                                                                                                                                                                                                                                                                                                              | 77       |

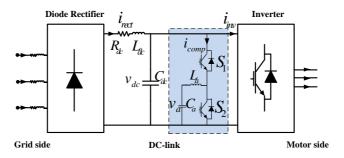

| 6.6  | Schematic diagram of an adjustable speed drive with an active DC-       |     |

|------|-------------------------------------------------------------------------|-----|

|      | link interharmonic compensator.                                         | 78  |

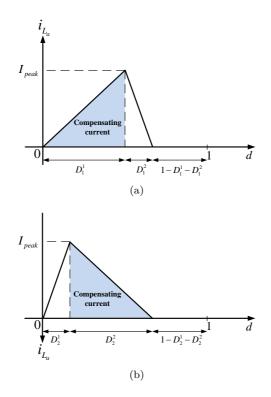

| 6.7  | Compensation scheme. (a) Duty-cycle related to the switch $S_1$ and     |     |

|      | the corresponding charging and discharging state of the inductor $L_a$  |     |

|      | when the ripple current is positive. (b) Duty-cycle related to the      |     |

|      | switch $S_2$ and the corresponding charging and discharging state of    |     |

|      | the inductor $L_a$ when the ripple current is negative                  | 79  |

| 6.8  | Simulation waveforms with the active DC-link interharmonic com-         |     |

|      | pensator.                                                               | 81  |

| 6.9  | Input current $i_a$ spectra when the motor input voltage frequency is   |     |

|      | equal to 40 Hz. (a) Before applying the DC-link compensator. (b)        |     |

|      | After applying the DC-link compensator.                                 | 82  |

| 6.10 | Input current $i_a$ spectra when the motor input voltage frequency is   |     |

|      | equal to 25 Hz. (a) Before applying the DC-link compensator. (b)        |     |

|      | After applying the DC-link compensator.                                 | 83  |

| 6.11 | Equivalent circuit of an adjustable speed drive for system analysis     |     |

|      | and control system for interharmonic compensation                       | 84  |

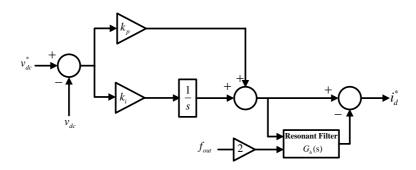

| 6.12 | Block diagram showing resonant filter after the outer PI controller     |     |

|      | for use in a back to back converter                                     | 87  |

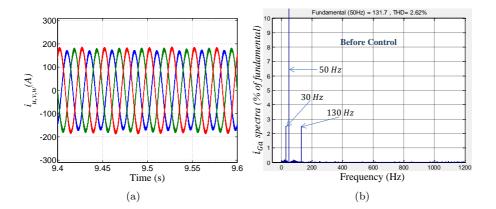

| 6.13 | Simulation results at load torque $T_L$ equal to 460 Nm, $f_{out} = 40$ |     |

|      | Hz and with a motor current imbalance of 5% before applying the         |     |

|      | proposed control strategy. (a) Motor currents. (b) Grid current         |     |

|      | spectra in common coupling point.                                       | 88  |

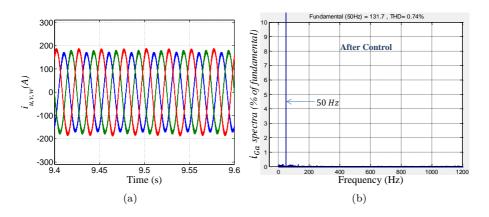

| 6.14 | Simulation results at load torque $T_L$ equal to 460 Nm, $f_{out} = 40$ |     |

|      | Hz and with a motor current imbalance of 5% after applying the          |     |

|      | proposed control strategy. (a) Motor currents. (b) Grid current         | ~~~ |

|      | spectra in common coupling point.                                       | 89  |

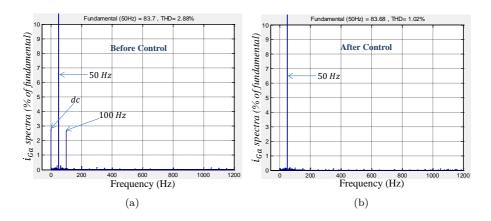

| 6.15 | Input current $i_{Ga}$ spectra when the motor input voltage frequency   |     |

|      | is equal to 25 Hz. (a) Before applying the proposed control strategy.   | 00  |

|      | (b) After applying the proposed control strategy                        | 89  |

List of Figures

# List of Tables

| 2.1          | Parameters $p$ and $k$ regarding <i>even</i> and <i>odd</i> $m_f$ in terms of harmonic analysis using synchronous SPWM | 17 |

|--------------|------------------------------------------------------------------------------------------------------------------------|----|

| 2.2          | Parameters $p$ and $r$ regarding <i>even</i> and <i>odd</i> $m_f$ in terms of harmonic analysis using synchronous SPWM | 18 |

| 3.1          | The generated harmonic and interharmonic tones for the $i^{th}$ analysis.                                              | 31 |

| 3.2          | Comparative results of Interharmonic subgroups IGs with imple-<br>menting different techniques.                        | 33 |

| 4.1          | Simulation and Experimental Parameter Values                                                                           | 45 |

| 5.1          | Parameter values for simulation study of interharmonics in ASD                                                         | 59 |

| 6.1          | Parameters for simulation study of interharmonics in ASD                                                               | 72 |

| $6.2 \\ 6.3$ | Simulation parameter values for SAPF                                                                                   | 76 |

|              | tation.                                                                                                                | 84 |

List of Tables

# Part I Report

### Chapter 1

### Introduction

This chapter firstly presents the background and motivation of this research project. It includes a short description about harmonic and interharmonic distortions and their impact on the grid, followed by the objectives and limitations of the project. Then, the thesis structure is presented to give a better understanding about the flow of the research work.

### 1.1 Background and motivation

In modern electrical energy systems, voltages and especially currents may become very irregular due to large numbers of non-linear loads and generators in the grid. In this regard, power electronic based systems such as adjustable speed drives, power supplies for IT-equipment and high efficiency lighting and inverters in systems generating electricity from distributed renewable energy sources are important sources to create disturbances [1–5]. Distortions encountered are, for example, harmonics, interharmonics, rapid amplitude variations (flicker) and transients, which are all elements of 'power quality' problems.

A voltage waveform in a conventional power system is expected to be pure sinusoidal with a fundamental frequency and a rated amplitude. When non-linear loads are connected to an electric power system they tend to draw non-linear currents, and consequently, to distort the grid voltage due to the impedance on the network [6]. Mathematically, the distorted voltage and/or current signal can be represented as a combination of the grid fundamental frequency components and its multiples named as harmonic frequency components. In the case that systems operating at different frequencies are tied to each other via non-linear devices, the frequency interaction may result in interharmonic distortions.

#### 1.1.1 Harmonic distortions

Harmonics are defined as sinusoidal voltages or currents whose frequencies are multiple integers of the fundamental frequency [6]. Proliferation of non-linear loads in power systems has increased harmonic pollution and has deteriorated the power quality. It is worth to mention that the rapid variations in distortion levels are basically considered in the category of transients rather than harmonics [7]. In this respect, as the speed of the variations decreases, at some point the distortion is more clearly described as being a set of harmonics of varying magnitude rather than a transient phenomena.

IEC 61000-4-3 [8] has set a window of 3 seconds as the shortest window over which harmonics should be measured, and IEC 61000-3-2 [9] allows a 50 % increase in distortion level for this period, for certain types of equipment. The fundamental principles which led to the harmonic standards can be noted as:

- a) Avoid system and load damage and disruption due to high harmonic levels.

- b) Limit harmonic losses to an acceptable level.

- c) When mitigation is necessary, find an economical and equitable solution.

Regarding the harmonic identity, it should be noted that harmonics are typically assumed to be periodical and time-invariant. This is while harmonic components are steadily changing with time [10]. It is then always appreciated to look at the harmonics based on time-variant identities and evaluate the harmonic distortions in this perspective.

Harmonic distortions, which are tied to either voltage magnitudes and current flow amplitudes may result in severe effects on the connected power system. It may cause erratic behavior in microcontrollers, breakers, and relays. In addition, these distortions may lead to increased temperature and consequently to increased losses, transformer derating, possible equipment failure over time, and interaction between the controllers.

#### 1.1.2 Interharmonic distortions

According to IEC 61000-4-7 [11], interharmonic frequencies are defined as any frequencies, which are not integer multiples of the fundamental frequency. Generally, two basic mechanisms lead to the interharmonics generation. The nonlinear interaction between two systems operating at different frequencies can give rise to interharmonics. These interactions are usually a consequence of the switching characteristics of power electronic devices [12] or rapid changes of current in the equipment and installation. Due to the non-linear interaction, the fundamental frequency component and its harmonics from one source modulate with the propagated waveforms coming from the other frequency source. Consequently, the interharmonic components settle in the sidebands of the fundamental and harmonic frequencies. The second mechanism is associated with the asynchronous switching of power converters, where, the output frequency of the power converter is not synchronized with the fundamental frequency of the power system. In this condition, interharmonic components

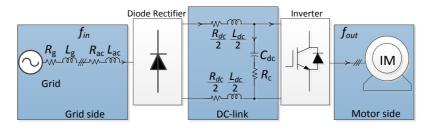

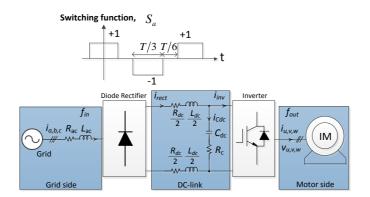

Figure 1.1: Typical structure of a voltage sourced adjustable speed drive.

may appear at different frequencies with respect to the power supply voltage harmonics. Practical applications which cause interharmonic distortions are adjustable speed drives [13–15], arcing loads [16–18], static converters [19], and ripple controls [19, 20].

In respect to interharmonic distortions, much research works are devoted to the identification of interharmonic sources, their adverse effects, and measurement strategies [12,17,21–25]. However, the ever increasing usage of power electronic devices made this issue even more important and there is an ongoing global discussion to set a regulation in the standards for interharmonic distortions.

### 1.2 **Project motivation**

As mentioned earlier, the presence of harmonic distortions in the power system may induce problems like overloading of neutrals, nuisance tripping of circuit breakers, over-stressing of power factor correction capacitors and zero-crossing noise. In addition, these distortions cause overheating and losses in transformers [26], and interference with communication lines [27].

With respect to interharmonic distortions, they can induce the same effects on the power system as those associated with the harmonic distortions [28,29]. Basically, the common negative effects have less significance in the interharmonic distortions because of their typically smaller magnitudes compared with the harmonic one. Interharmonic components, although smaller in magnitudes, may cause their own unique problems. The problems have mainly roots on the interharmonic characteristics, where they can spread to a wide range in the frequency spectrum. Light flicker [30–32], sideband torques on the motor/generator shaft [33–35], interference with control and protection signals [19,36,37], dormant resonance excitation [15,38,39] are some of the most significant negative effects caused by interharmonic distortions.

Adjustable Speed Drives (ASDs) are considered as one of the main sources of interharmonics in the power system, where the load (induction machine, permanent magnet motor) is usually required to operate at different frequency conditions. Meanwhile, the ASD's input/output frequency interactions can lead to the input/output interharmonic components. Considering the ASD struc-

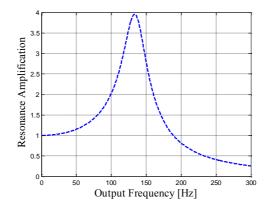

Figure 1.2: A typical ASD's equivalent DC-link resonance amplification.

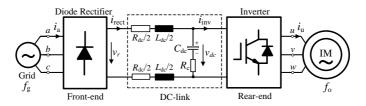

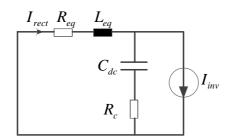

ture shown in Figure 1.1, the DC-link filter (DC-link inductor  $L_{dc}$  and capacitor  $C_{dc}$ ) and the AC-side inductor  $L_{ac}$  have significant effects on the drive interharmonics emission to the grid. The drive output harmonics when transferred to the grid side via the DC link, have to deal with an equivalent DC-link resonance amplification, as shown in Figure 1.2 (by using  $L_{ac}=4.5 \text{ mH}$ ,  $R_{ac}=0.2 \Omega$ ,  $L_{dc}=2$ mH,  $R_{dc}=0.09 \Omega$ ,  $C_{dc}=125 \mu$ F, and  $R_{c}=0.5 \Omega$ ). Those DC-link oscillations accommodated around the resonance frequency will be magnified, and then give rise to a higher amplitude interharmonics in the grid side. Moreover, it can be seen in Figure 1.2 that the DC-link high order oscillations will be decreased while the filter's effect on the low frequency oscillations are negligible. Hence, an appropriate design procedure and well selection of drive passive filters can play an important role in the interharmonic emissions. Although, the authors in [13] discussed the relative effects of DC-link inductance and source inductance on interharmonic propagation, there is still a special need to consider the direct effects of the filter components on the input current interharmonics at different working points of the ASD.

The ASD's inverter modulation strategy may also play an important role in the interharmonics emission. The interharmonics generation process of the double-stage ASD has been studied in [14], where a naturally sampled Sinusoidal Pulse Width Modulation (SPWM) technique has been chosen for the inverter at a relatively low switching frequency. The theoretical analysis was realized to provide a good understanding of the harmonics interaction, and consequently to assess the interharmonics. However, more attention is needed to precisely analyze the ASD interharmonic frequencies in practical applications. In respect to the most common modulation techniques in drive applications (e.g., SPWM, Space Vector Modulation (SVM), and Discontinuous Pulse Width Modulation (DPWM2) techniques), it is worth to investigate their effects on the drive interharmonic components.

Besides many investigations dedicated to the interharmonic sources in ASDs,

mitigation of interharmonics is another scope, which has not been studied thoroughly. In [40], an investigation has been initiated with the intention of mitigating interharmonics by applying harmonic dithering. Although sound in concept, the dithering approach discussed in [40] is more for spreading the intensities of interharmonics over a frequency range, rather than eliminating them. In [41], an investigation has been initiated regarding interharmonics minimization by applying a DC-link active compensator. However, it has been implemented only in current source AC-drive and suffers also from applying a full-bridge inverter as an active compensator which definitely increases the costs.

The above considerations initiated this research project and the main motivation of this project is to examine the ASD input current interharmonics to find more optimal strategies, which can give rise to the less interharmonic components.

### **1.3** Project objectives

With the rapid growth of power electronics applications, the deteriorate effects of interharmonics are becoming more and more evident. Consequently, interharmonics power quality issues have gained more attention in the recent years. In order to address the identified shortfalls, the objectives of this project are,

- How the effect of the fixed frequency modulation techniques like SPWM, SVM and DPWM2 can be evaluated on the input current interharmonic components of the double-stage Voltage Source Inverter (VSI)-fed ASDs?

- What is the effect of ASDs filter (AC choke, DC choke, and DC-link capacitor) on the drive input current interharmonics distortion?

- How can the ASDs input current interharmonic components be reduced? Is it possible to mitigate distortions properly?

The goal of this dissertation is to scrutinize the interharmonic generation process in the double-stage VSI-fed ASD, where the most common fixed frequency modulation strategies (e.g., SPWM, SVM and DPWM2) in drive application are implemented. The obtained results will provide a good insight into the modulation technique effects on the interharmonics issues. Thereafter, the effect of the drive filter components on the input current interharmonics will be investigated in the cases of balanced and unbalanced output current. Moreover, for those interharmonics generated by the drive output current imbalance, some active compensators are applied to reduce the related interharmonics.

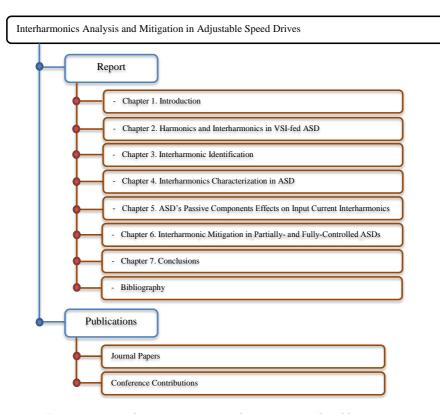

### 1.4 Thesis outline

The obtained results of this project are documented in the form of Ph.D. thesis, which consists of the **Report** and the **Publications**. In the **Report**, a summary of this research work is presented, whilst in the **Publications**, the papers

Figure 1.3: Thesis structure with a report and publication part.

derived in Ph.D. period are presented. A general framework of the project is shown in Figure 1.3 and is organized as follows:

A brief background of this research work is introduced in Chapter 1. It investigates the importance of the harmonic and interharmonic distortions in the grid. The motivation and objectives of the project are then addressed followed by the thesis outline.

Chapter 2 generally investigates the ASD's interharmonic components when a naturally sampled sinusoidal pulse width modulation technique is applied for the inverter switching. It shows how the drive output harmonic components may pass through the DC link and lead to input voltage and/or current interharmonic distortion.

Chapter 3 introduces some practical challenges with respect to interharmonics identification. The harmonics and interharmonics evaluation methods proposed by the IEC standard are also shortly presented. Then, a thorough discussion introduces existing desynchronized interharmonics detection methods, which are applied in this research work as highly accurate measurement strategies. In Chapter 4, the double-stage VSI-fed ASD input current interharmonics are evaluated with respect to the adopted modulation techniques. The symmetrical regularly sampled SPWM, SVM, and DPWM2 techniques are selected as well as the asymmetrical regularly sampled SVM modulation technique, due to being the most popular modulation techniques applied in motor drive applications. Finally, the suitable strategy associated with the fixed frequency switching methods (i.e., SPWM, SVM, and DPWM2) is proposed in order to reduce the drive input current interharmonic components.

Chapter 5 investigates the effects of adjustable speed drive passive components on the input current interharmonics. The evaluation has been done both for the unbalanced and balanced motor current cases.

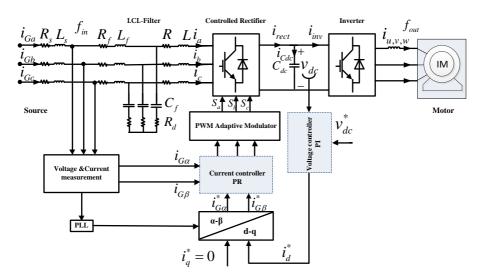

Chapter 6 suggests implementing some active compensation methods in order to reduce the drive input current interharmonics generated by the motor current imbalance. In the case of a partially-controlled ASD, an AC-side or DC-side parallel active compensators are proposed to decrease the drive interharmonic components. Also for the fully-controlled ASD (with applying a back-to-back converter), a control strategy is proposed to reduce the drive input current interharmonics.

Chapter 7 concludes the thesis, summarizes the main contributions of this research, and gives some proposals for future work.

### 1.5 List of publications

A list of the papers derived from this project, which are published till now or have been submitted, is given as follows:

Journal Papers

- J1. H. Soltani, F. Blaabjerg, F. Zare, and P. C. Loh, "Effects of passive components on the input current interharmonics of adjustable-speed drives," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 1, pp. 152–161, Mar. 2016.

- J2. H. Soltani, P. Davari, F. Zare, P. C. Loh, and F. Blaabjerg, "Characterization of input current interharmonics in adjustable speed drives," *IEEE Trans. Power Del.*, Under second review.

Conference Contributions

- C1. H. Soltani, P. C. Loh, F. Blaabjerg, and F. Zare, "Sources and mitigation of interharmonics in back-to-back controllable drives," in *Proc. IEEE-EPE*, 2014, pp. P.1– P.9.

- C2. H. Soltani, P. C. Loh, F. Blaabjerg, and F. Zare "Interharmonic analysis and mitigation in adjustable speed drives," in *Proc. IEEE-IECON Conf.*, 2014, pp. 1556–1561.

- C3. H. Soltani, P. Loh, F. Blaabjerg, and F. Zare, "Interharmonic mitigation of adjustable speed drives using an active DC-link capacitor," in *Proc. ICPE-ECCE Asia*, 2015, pp. 2018–2024.

- C4. H. Soltani, P. Davari, F. Zare, P. C. Loh, and F. Blaabjerg, "Input current low-frequency interharmonics in adjustable speed drives caused by different

modulation techniques," in Proc. IEEE-APEC, 2016, Accepted/In press.

# Chapter 2

# Harmonics and Interharmonics in VSI-fed ASD

This chapter focuses on the harmonics and interharmonics generation process in a double-stage VSI-fed ASD, where a three-phase diode rectifier is connected to an inverter sharing a common DC link. The inverter output harmonic components are first analzed when using the SPWM modulation technique. Then, the interaction between the inverter output-side harmonics and the diode rectifier input-side harmonics, which can lead to the drive input-side interharmonics, are discussed.

# 2.1 Introduction

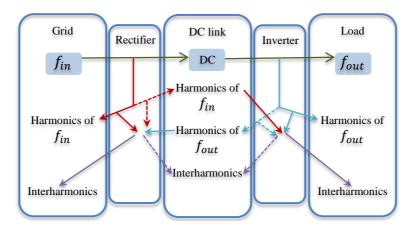

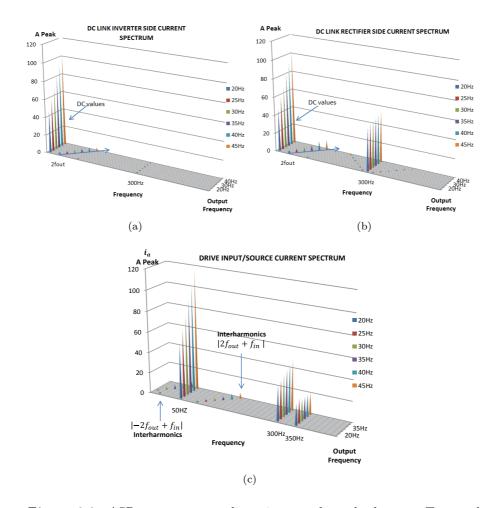

Double-stage voltage sourced AC-DC-AC ASDs are witnessed as a major source of interharmonics in the power system. A block diagram of adjustable speed drives with the associated harmonics and interharmonics interactions are shown in Figure 2.1. In this respect, fundamental frequency,  $f_{in}$ , of the grid is first rectified via a three-phase diode rectifier. Then, at the DC link, when using passive filters (inductor and capacitor), a smoother DC voltage is obtained to feed the rear-end PWM inverter. Finally, the three-phase inverter supplies the output loads at the required power and frequency levels. Since the diode rectifier and the PWM inverter convert the fundamental frequency by switching operations, they produce harmonics associated with the fundamental frequency varies in a wide range, the system's input frequency,  $f_{in}$ , is different with the output frequency,  $f_{out}$ . The harmonic components at both sides, when propagated through the DC link, will interact with the other side harmonic components, which in turn will give rise to the interharmonics at both sides of the ASD.

Figure 2.1: Block diagram of a double-stage voltage sourced ASD with the associated harmonics and interharmonics interaction.

Harmonic and interharmonic frequencies in ASD are characterized by the configuration of the devices. The ASD structure and the associated modulation technique determine the interharmonic locations. Although some other issues such as the load torque variations and motor shaft eccentricity may also cause interharmonic components in ASD, they are not included in the scope of this dissertation. In this chapter, harmonic and interharmonic components associated with the double-stage VSI-fed ASD are analyzed, when the naturally sampled SPWM modulation technique is implemented.

### 2.2 Harmonic analysis

#### 2.2.1 Three-phase diode rectifier

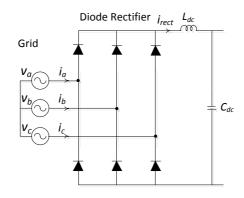

A three-phase diode rectifier is the most popular structure for rectifying the three-phase grid voltage in adjustable speed drive specially in the medium to higher power applications. As long as the regulated DC-link voltage meets the limitations at different loading conditions, this structure is an appropriate choice, otherwise, the diodes have to be replaced by switching devices such as thyristors and silicon-controlled rectifiers. Figure 2.2 shows the typical structure of a six-pulse diode rectifier. A proper design of the DC-link inductor  $L_{dc}$  and capacitor  $C_{dc}$  results in a smoother DC-link current and voltage variations, respectively.

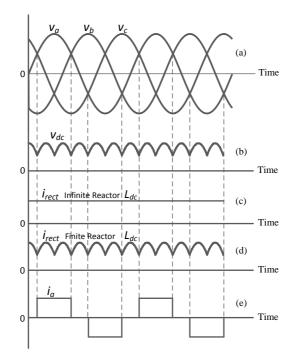

Assuming the rectifier is supplied by an infinite bus, the DC-link voltage is formed of six hump-shape ripples at one fundamental period of the power supply, as shown in Figure 2.3. Considering a ripple-free DC-link current  $i_{rect}$ , the input current  $i_a$  is composed of periodic rectangular pulses with the frequency of the grid fundamental component. Hence, the diode rectifier's input current can be mathematically represented by the well-known Fourier expansion and

Figure 2.2: Typical structure of a six-pulse diode rectifier connected to a stiff grid.

Figure 2.3: Diode rectifier voltages and currents waveforms. (a) Three-phase input voltages. (b) DC-link voltage. (c) DC-link current with infinite size inductor. (d) DC-link current with finite size inductor. (e) Input current with infinite size inductor.

it is given as below,

$$i_{a} = \frac{2\sqrt{3}}{\pi} i_{rect} \left[ \cos 2\pi f_{in}t - \frac{1}{5} \cos 2\pi (5f_{in})t + \frac{1}{7} \cos 2\pi (7f_{in})t - \ldots \right] = \frac{2\sqrt{3}}{\pi} i_{rect} \left[ \cos 2\pi f_{in}t \pm \sum_{k'=1}^{\infty} \frac{1}{6k'\pm 1} \cos[(6k'\pm 1)(2\pi f_{in})t] \right]$$

(2.1)

where, the DC-link current and the grid fundamental frequency are notated as  $i_{rect}$  and  $f_{in}$  respectively. In the calculation of (2.1), the DC-link current  $i_{rect}$  is considered as constant value due to applying a large DC-link inductor  $L_{dc}$ . In a practical condition, the DC-link current see the oscillation with the same frequencies as those of the DC-link voltage. Thus, it contains the 6th order multiples of the grid fundamental frequency, and its frequency components  $f_{dc}^h$  can be represented as,

$$f_{dc}^{h} = 6 \cdot m \cdot f_{in} \qquad m = 1, 2, 3, \dots$$

(2.2)

From (2.1), it can be noted that the input currents have the frequency orders of  $(6k' \pm 1)$  with respect to the fundamental frequency. The harmonic frequency of  $(6k' \pm 1)f_{in}$  can then be modulated with the 6th order oscillations of DC-link current  $i_{rect}$ , by implementing the trigonometric identity given in (2.3),

$$\sin a \cdot \sin b = \frac{1}{2} [\cos (a - b) - \cos (a + b)]$$

(2.3)

By substituting (2.2) into (2.1), and, using the trigonometric identity of (2.3), the input current harmonic frequencies  $f_{in}^h$  can be described as

$$\begin{aligned}

f_{in}^{h} &= [6 \cdot (k'+m) \pm 1] \cdot f_{in} \\

&= (6k \pm 1) \cdot f_{in} \\

k &= 1, 2, 3, \dots

\end{aligned}$$

(2.4)

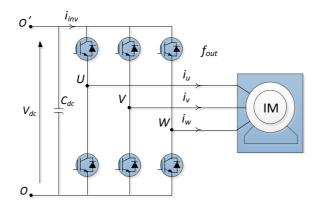

#### 2.2.2 Pulse width modulated inverter

Voltage source inverter fed ASDs are widely used in industry [42] from low to medium-high power applications, where they convert up to a few MVA power ratings. SPWM modulation technique is considered as one of the major modulation methods implemented on ASDs inverter, mainly because of its simple structure and linear controllability. In this chapter, the harmonic and interharmonic analyses are performed based on the synchronous naturally sampled SPWM, where the carrier frequency  $f_c$  is a multiple integer of the drive's output fundamental frequency  $f_{out}$ . It is worth to mention that implementing a non-synchronous PWM may cause undesired harmonics in the inverter output, and consequently, can give rise to unknown input current interharmonics.

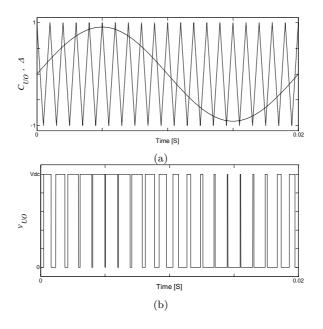

Figure 2.4 shows the general structure of a three-phase IGBT inverter, which supplies the Induction Machine (IM) as a load. As a result of the switching, the DC-link voltage will be converted to a pulse train, whose fundamental frequency is equal to the desired output frequency. Figure 2.5 illustrates the modulation process leading to the inverter output switched pulse train. By

Figure 2.4: PWM inverter feeding three-phase Induction Motor (IM).

**Figure 2.5:** Synchronous sinusoidal PWM: (a)  $C_{UO}$  is the sinusoidal modulation signal for the phase U, and,  $\Delta$  is the carrier signal, (b)  $v_{UO}$  is the output voltage pulse train with reference to Figure 2.4.

comparing the carrier signal  $\Delta$  with the modulation signal  $C_{UO}$ , the output voltage pulse train  $v_{UO}$  is generated. The output voltages  $v_{VO}$  and  $v_{WO}$  can also be obtained by comparing  $\Delta$  with other two modulation signals  $C_{VO}$  and  $C_{WO}$ , which are phase shifted by 120° and 240° with respect to  $C_{UO}$ . The generated pole voltages contains a DC value  $V^0$ , the fundamental component  $v_{XO}^1$  and harmonics  $\tilde{v}_{XO}$  (mainly located around the switching frequency and its multiples), and consequently can generally be presented as follows,

$$v_{XO} = V^0 + v_{XO}^1 + \tilde{v}_{XO} \tag{2.5}$$

where X denotes the nodes U, V and W shown in Figure 2.4. The harmonic components  $\tilde{v}_{XO}$  can be considered as follows,

$$\tilde{v}_{XO} = \sum_{n=2}^{\infty} A_n \sin(2\pi n f_{out} t + n\varphi_X)$$

(2.6)