Aalborg Universitet

### Electro-thermal Modeling of Modern Power Devices for Studying Abnormal Operating Conditions

Wu, Rui

Publication date: 2015

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Wu, R. (2015). Electro-thermal Modeling of Modern Power Devices for Studying Abnormal Operating Conditions. Department of Energy Technology, Aalborg University.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

### Electro-thermal Modeling of Modern Power Devices for Studying Abnormal Operating Conditions

by

### Rui Wu

A Dissertation Submitted to the Faculty of Engineering and Science at Aalborg University in Partial Fulfillment for the Degree of Doctor of Philosophy in Electrical Engineering

December 2015 Aalborg, Denmark AALBORG UNIVERSITY Department of Energy Technology Pontoppidanstraede 101 Aalborg East, DK-9220 Denmark Phone: +45 29 63 20 67 Fax: +45 98 15 14 11 http://www.et.aau.dk

Copyright © Rui Wu, 2015

Printed in Denmark by Uniprint First Edition (October 2015) Second Edition (December 2015)

MATLAB<sup>®</sup> is a trademark of The MathWorks, Inc., PSpice<sup>®</sup> is a trademark of Cadence, Inc., and ANSYS<sup>®</sup> is a trademark of ANSYS, Inc. Simulations included in this dissertation are done using the MATLAB<sup>®</sup>, PSpice<sup>®</sup> and ANSYS<sup>®</sup> software. This Ph.D. thesis has been typeset in L<sup>A</sup>T<sub>E</sub>X  $2\varepsilon$ .

### PUBLIC DEFENCE OF PHD DISSERTATION

### Thesis Title:

Electro-thermal Modeling of Modern Power Devices for Studying Abnormal Operating Conditions

### Ph.D. Defendant:

Rui Wu

Supervisor: Prof. Frede Blaabjerg

### **Co-Supervisor:**

Prof. Francesco Iannuzzo

### Assessment Committee:

Prof. Chen Zhe (Chairman) Department of Energy Technology Aalborg University Pontoppidanstraede 101 9220 Aalborg, Denmark

### Prof. Alberto Castellazziä

Nottingham University 17, Clumber Court, Clumber Crescent South NG7 1EE Nottingham, UK

Dr. Muhammad Nawaz ABB

Forskargränd 7 721 78 Västerås, Sweden

### **Defence Date and Place:**

Monday, December 14, 2015 Pontoppidanstraede 101, Room 23, Aalborg University

### Copyright Statements

This present report combined with the above listed scientific papers has been submitted for assessment in partial fulfilment of the PhD degree. The scientific papers are not included in this version due to copyright issues. Detailed publication information is provided above and the interested reader is referred to the original published papers. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science, Aalborg University.

## Preface

This thesis is a summary of the PhD project "Multi-Physics Based Modeling of Power Electronic Components and Circuits". The PhD project is supported by the Center of Reliable Power Electronics (CORPE), and Department of Energy Technology at Aalborg University. Acknowledgements are given to the above mentioned institutions, as well as Otto Mønsteds Fond, which provides financially support for the conference participation and the study abroad.

This project was supervised by Professor Frede Blaabjerg, Professor Francesco Iannuzzo, and Associate Professor Huai Wang from Department of Energy Technology in Aalborg University. I would like to express my deepest gratitude to my supervisor, Professor Frede Blaabjerg, for his inspired proposals, constructive discussions, patient guidance and consistent encouragements. Furthermore, I would like to sincerely acknowledge Professor Francesco Iannuzzo for his inspired suggestions and invaluable help to both of my research and career. I would also appreciate Associate Professor Huai Wang for his continuous support and help during the whole PhD study.

This project was done with a close collaboration with the companies, such as Vestas, Danfoss, Grundfos, and KK wind solutions. I would like to send my special thanks for their support and suggestions.

I would like to express my gratitude to the honoured preliminary examiners of this doctoral dissertation, Professor Chen Zhe from Aalborg University, Professor Alberto Castellazzi from Nottingham University and Dr. Muhammad Nawaz from ABB, for their time and effort in evaluating my work.

I appreciate the fruitful collaborations with Miss Paula Diaz Reigosa, Mr. Pramod Ghimire, Dr. Kristian Bonderup Pedersen, Dr. Liudmila Smirnova as well as all the group members in CORPE. I also want to thank my colleagues from the Department of Energy Technology for the friendly environment and enthusiastic help. I would like to send my best wishes to my friends – Dao Zhou, Yongheng Yang, Xiongfei Wang, Ke Ma, Fan Zhou, Zi'an Qin, Dan Wu,Wenli Yao, Casper Jørgensen and Anna Miltersen. Moreover, my special appreciations are extended to John K. Pedersen, Tina Larsen, Mette Skov Jensen, Corina Busk Gregersen, Ann Louise Henriksen, Walter Neumayr, Mads Lund and Jan Krogh Christiansen for their assistance in many different ways. Special thanks to my parents for their continuous encouragement and support throughout my life.

Finally, I would like to thank my wife Qian Shi for her love and support. Without your support this thesis would not have been possible.

Rui Wu

October, 2015 Aalborg Øst, Denmark

## Abstract

In modern power electronic systems, there are increasing demands for improvement of the whole system endurance and safety level while reducing manufacturing and maintenance costs. Insulated Gate Bipolar Transistor (IGBT) power modules are the most widely used as well as most critical power devices in industrial power electronic systems in the power range above 10 kW. The failure of IGBTs can be classified as catastrophic failures and wear out failures. A wear out failure is mainly induced by accumulated degradation with time, while a catastrophic failure is triggered by a single-event abnormal condition, for example overvoltage, overcurrent, overheating, and cosmic rays. The degradation and wear out failure of IGBTs can be monitored by Prognostics and Health Management methods; however, it is more difficult to predict the catastrophic failure, for instance the short circuit conditions. The objective of this project has been to model and predict the electro-thermal behavior of IGBT power modules under abnormal conditions, especially short circuits.

A thorough investigation on catastrophic failure modes and failure mechanisms of modern power semiconductor devices, including IGBTs and power diodes, has been given in Chapter 2. The failure mechanisms investigation suggests that the abnormal junction temperature or hot spots normally happen with the occurrence of failure. The practical challenges in predicting junction temperature during short circuit operations are also identified: a) electro-thermal coupling effects become significant in high current and high temperature variation conditions; b) uneven current distribution and thermal loading inside the IGBT chip as well as among the different chips in an IGBT module during high dynamics of short circuit; c) there is still a lack of methods to measure the IGBT junction temperature precisely in a time duration of several or tens of  $\mu$ s in order to protect the devices.

According to the aforementioned investigations, a PSpice-Icepak co-simulation method is proposed to be used for studies in this thesis, which is introduced and discussed in Chapter 3. It combines a physics-based, device-level, distributed PSpice model with a thermal Finite-Element Method (FEM) simulation, gaining the possibility to take into account the electro-thermal coupling effects and uneven electro-thermal stresses among the chips. Case studies on the new and degraded modules, as well as geometrical parameters variations, further prove the effectiveness of the proposed approach in Chapter 4. Then, a 1.1 kV/ 6 kA non-destructive testing facility is built up at the Center of Reliable Power Electronics (CORPE), Aalborg University, to experimentally verify the simulation results of IGBT power modules as described in Chapter 5. The setup provides also the capability to study the wide-band-gap devices short circuit behavior in the future.

It is found that catastrophic failure is the shortfall of the reliability of modern power devices, while its behavior is difficult to be predicted. The proposed PSpice-Icepak electro-thermal co-simulation method demonstrates the capability of predicting IGBT power modules electro-thermal stresses during short circuits, which can be used for further optimizing the performance of modules.

## Danske Resume

I moderne effektelektroniske systemer, er der stigende krav til at forbedre hele systemets udholdenhed og sikkerhedsniveau, mens produktions- og vedligeholdelsesomkostninger reduceres. Insulated Gate Bipolar Transistor (IGBT) effektmoduler er de mest udbredte samt mest kritiske effektenheder i industrielle effektelektroniske systemer i området over 10 kW. IGBT fejl kan generelt klassificeres som katastrofale fejl og udmattelses fejl (fatigue failure) or nedslidnings fejl (wear out failure). En nedslidningsfejl er hovedsageligt induceret af akkumuleret nedbrydning med tiden, mens en katastrofal fejl udløses af en enkelt begivenhed unormal tilstand, for eksempel overspænding, overstrøm, overophedning og kosmiske stråler. Nedbrydnings og nedslidnings fejl af IGBTs kan overvåges ved prognosticerings og sundhedsledelses metoder. Det er imidlertid vanskeligere at forudsige katastrofale fejl, f.eks kortslutningsforhold. Formålet med dette projekt har været at modellere og forudsige den elektro-termiske opførsel af IGBT effektmoduler under unormale forhold, især kortslutninger.

En grundig undersøgelse af katastrofale fejltilstande og mekanismer i moderne effekthalvlederkomponenter, herunder IGBT'er og effekt dioder, der er givet i kapitel 2. Brudmekanismens undersøgelse tyder på, at abnorm knudepunktstemperatur eller hot spots normalt sker med forekomsten af fejl. De praktiske udfordringer i at forudsige knudepunktstemperaturen under kortslutningsdrift er også identificeret: a) elektrotermiske koblingseffekter bliver betydelige i høje strøm og høje temperatuerudsvings forhold; b) ujævn strømfordeling og termisk belastning inde i IGBT-chippen samt mellem de forskellige chips i en IGBT-modul under høje dynamikker ved kortslutning; c) der er stadig mangel på metoder til måling af IGBT'ens knudepunktstemperatur præcist i en tidsvarighed af få mikrosekunder med henblik på at beskytte enhederne.

Ifølge de nævnte undersøgelser, foreslås en PSpice-Icepak co-simulering metode, der skal bruges til studierne i denne afhandling, som introduceres og diskuteres i kapitel 3. Den kombinerer en fysik baseret, enhedsniveau, distribueret PSpice model med en termisk Finite-Element Method (FEM) simulering, der giver mulighed for at tage hensyn til de elektrotermiske koblede effekter og ujævne elektrotermiske belastninger blandt chips. Casestudier om de nye og slidte moduler samt geometriske parametre variationer, yderligere beviser effektiviteten af den foreslåede tilgang i kapitel 4. Derefter, en 1,1 kV / 6 kA ikke-destruktiv test facilitet er bygget op på Center of Reliable Power Electronics (CORPE), Aalborg Universitet, for eksperimentelt at kontrollerede simulerede resultater af IGBT effekt moduler som beskrevet i kapitel 5. Opsætningen giver også mulighed for at studere bredt båndgabs enheders kortslutning adfærd i fremtiden.

Det konstateres, at katastrofal fejl er den største begrænsning af pålideligheden af moderne effektenheder, men er samtidig svær at forudse. Den foreslåede PSpice-Icepak elektro-termisk co-simulering metode demonstrerer evnen til at forudse IGBT effektmodulers elektriske og termiske belastninger under kortslutninger, som kan anvendes til yderligere optimering af modulets ydeevne.

## Contents

| Pref            | face       |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{v}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{Abs}$  | tract      | t                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Dan             | ske .      | Abstra                                                   | kt                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\mathbf{List}$ | of F       | igures                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\mathbf{List}$ | of T       | ables                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1               | Intr       | oducti                                                   | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 | 1.1<br>1.2 | $ \begin{array}{c} 1.1.1 \\ 1.1.2 \\ 1.1.3 \end{array} $ | round and Motivation       Reliability of Modern Power Devices         Reliability of Modern Power Devices       Summary of the Package-related Failure Mechanisms         Summary of the Package-related Failure Mechanisms       Secondary         Project Motivation       Secondary         of the Thesis       Secondary         Scientific Questions       Secondary         Objectives       Secondary         Research Scopes and Limitations       Secondary | $     \begin{array}{c}       1 \\       4 \\       8 \\       9 \\       9 \\       9 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\      $ |

|                 | 1.3        | Outlin                                                   | e of the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 1.4        | List of                                                  | Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>2</b>        | Cat        | astrop                                                   | hic Failures of Modern Power Semiconductor Devices                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2.1        | Power                                                    | Semiconductor Devices Failures Classification                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2.2        | Power<br>2.2.1<br>2.2.2                                  | Diode Catastrophic Failure Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17<br>17<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 2.3        | IGBT<br>2.3.1<br>2.3.2                                   | Catastrophic Failure Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                       | $20 \\ 21 \\ 23$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 2.4        | IGBT<br>2.4.1                                            | Short Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $27 \\ 27$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | 2.4.2            | Challenges Induced by Short Circuits                              | 28              |

|----------|------|------------------|-------------------------------------------------------------------|-----------------|

|          | 2.5  | Summ             | ary                                                               | 30              |

| 3        |      |                  | -based Electro-thermal Modeling Method of IGBT Mod-               |                 |

|          | ules | unde             | r Abnormal Conditions                                             | <b>31</b>       |

|          | 3.1  |                  | ples of Electro-thermal Analysis                                  | 31              |

|          |      | 3.1.1            | Fundamentals of Heat Transfer and Thermal Analysis                | 32              |

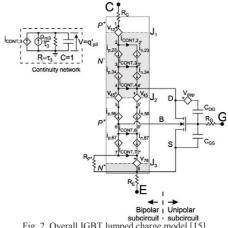

|          |      | $3.1.2 \\ 3.1.3$ | IGBT Electrical Model                                             | $\frac{35}{36}$ |

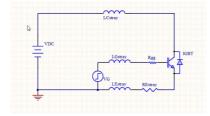

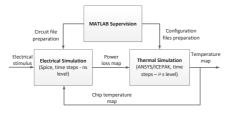

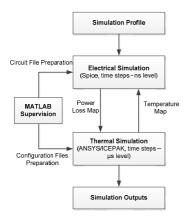

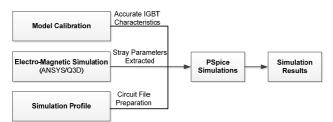

|          | 3.2  | $\mathbf{PSpic}$ | e-Icepak Co-simulation Description                                | 37              |

|          |      | 3.2.1            | Basic Principle                                                   | 37              |

|          |      | 3.2.2            | PSpice File Format                                                | $\frac{38}{39}$ |

|          | 0.0  | 3.2.3            | ANSYS/Icepak Program                                              |                 |

|          | 3.3  | Case 3           | Studies of One IGBT Section                                       | $40 \\ 41$      |

|          |      | 3.3.1            | Case Study II: Short Circuit in case of Bond Wire Lift-off        | 44              |

|          |      | 3.3.3            | Case Study III: Short circuit in case of Threshold Voltage Degra- |                 |

|          |      |                  | dation                                                            | 46              |

|          | 3.4  | Summ             | ary                                                               | 48              |

| 4        | Elec | ctro-th          | ermal Modeling of the Commercial IGBT Power Modules               | <b>49</b>       |

|          | 4.1  | Inform           | nation of the Studied 1.7 kV/ 1 kA IGBT Power Modules $\ldots$ .  | 49              |

|          |      | 4.1.1            | Outline and Specifications of the Power Modules                   | 49              |

|          |      | 4.1.2            | Stray Parameters inside the Power Module                          | 51              |

|          | 4.2  |                  | Study I: Short circuit Behavior with Imbalanced Stray Parameters  |                 |

|          |      | -                | g Parallel Chips                                                  | 54              |

|          |      | $4.2.1 \\ 4.2.2$ | Extraction of the Stray Parameters                                | $55 \\ 57$      |

|          |      | 4.2.2            | Electro-thermal Co-simulation Results of Short Circuit Behavior   | 58              |

|          | 4.3  |                  | Study II: Short Circuit Behavior under Uneven Initial Tempera-    | 00              |

|          | 1.0  |                  | among Parallel Chips                                              | 59              |

|          |      | 4.3.1            | Co-simulation Profile Definitions                                 | 59              |

|          |      | 4.3.2            | Co-simulation Results                                             | 61              |

|          | 4.4  | Summ             | ary                                                               | 62              |

| <b>5</b> |      |                  | ermal Model Validation by means of Non-destructive                |                 |

|          | IGE  | BT Tes           |                                                                   | 63              |

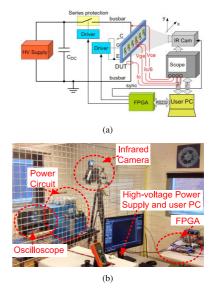

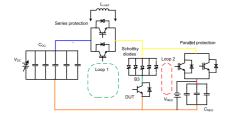

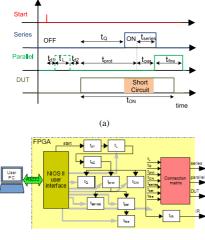

|          | 5.1  |                  | ption of 1.1 kV/6 kA Non-destructive Tester                       | 63              |

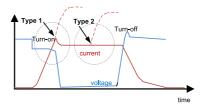

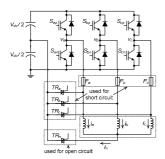

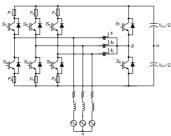

|          |      | 5.1.1            | Structure and Operating Principle                                 | 63              |

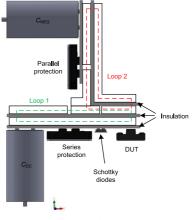

|          |      | 5.1.2            | Low Inductance Busbar                                             | 67              |

|      |        | 5.1.3 FPGA-based Supervising Unit                                                                                                     | 68                   |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|      | 5.2    | <ul> <li>Short Circuit Electrical Behavior Validation</li></ul>                                                                       | 69<br>69<br>70<br>73 |

|      | 5.3    | Temperature Evaluation during Short Circuit                                                                                           | 75<br>75<br>76       |

|      | 5.4    | Summary                                                                                                                               | 78                   |

| 6    | Con    | clusions and Future Work                                                                                                              | 79                   |

|      | 6.1    | Conclusions                                                                                                                           | 79                   |

|      | 6.2    | Research Highlights                                                                                                                   | 80                   |

|      | 6.3    | Proposals for Future Research Topics                                                                                                  | 81                   |

| Bib  | liogra | aphy                                                                                                                                  | 83                   |

| 7    | App    | pendix                                                                                                                                | 91                   |

| Jou  | rnal   | Papers                                                                                                                                | 99                   |

|      | 1      | Overview of Catastrophic Failures of Freewheeling Diodes in Power<br>Electronic Circuits                                              | 101                  |

|      | 2      | Study on Oscillations during Short Circuit of MW-Scale IGBT Power Modules by Means of a $6-kA/1.1-kV$ Nondestructive Testing System . | 109                  |

|      | 3      | Robustness of MW-Level IGBT Modules against Gate Oscillations under Short Circuit Events                                              | 121                  |

| Sele | ected  | Conference Papers                                                                                                                     | 129                  |

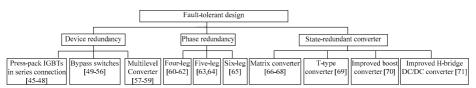

|      | 4      | Catastrophic Failure and Fault-Tolerant Design of IGBT Power Elec-<br>tronic Converters - An Overview                                 | 131                  |

|      | 5      | Fast and Accurate Icepak-PSpice Co-Simulation of IGBTs under Short-<br>Circuit with an Advanced PSpice Model                          | 141                  |

|      | 6      | Electro-thermal Modeling of High Power IGBT Module Short-circuits with Experimental Validation                                        | 149                  |

|      | 7      | A Comprehensive Investigation on the Short Circuit Performance of<br>MW-level IGBT Power Modules                                      | 159                  |

# List of Figures

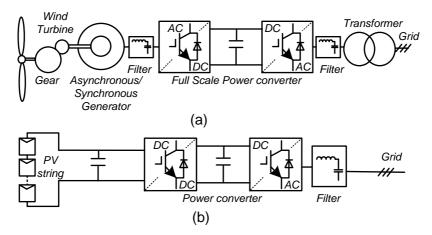

| 1.1 | Applications with modern power electronic systems: (a) wind turbine sys-                                |    |

|-----|---------------------------------------------------------------------------------------------------------|----|

|     | tem with full-scale power converter; (b) transformer-less single-phase grid-                            |    |

|     | connected PV system.                                                                                    | 2  |

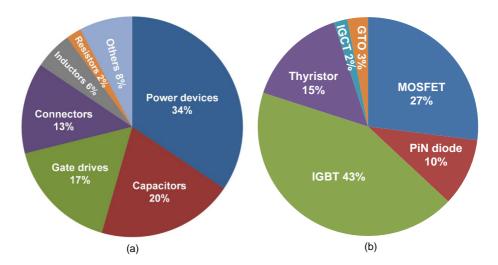

| 1.2 | An industry survey on power electronic systems: (a) percentage of the re-                               |    |

|     | sponse to the most frangible components; (b) percentage of the response to                              |    |

|     | the most used power devices question (% may vary for different applications                             |    |

|     | and designs). $\ldots$ | 2  |

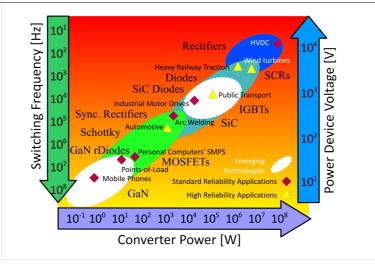

| 1.3 | Modern semiconductor devices and their typical applications                                             | 3  |

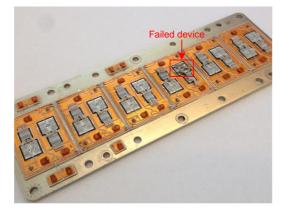

| 1.4 | The photo of a failed IGBT power module due to short circuit                                            | 4  |

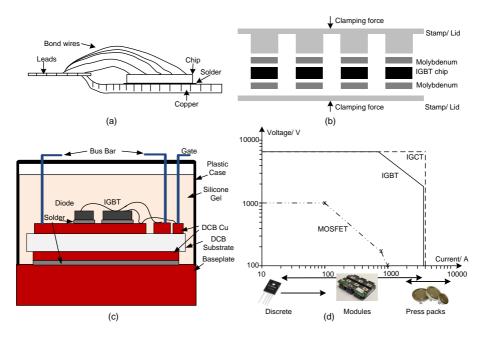

| 1.5 | Different power devices packaging technology: (a) internal structure of dis-                            |    |

|     | crete IGBT device; (b) cross section of IGBT press-packs; (c) cross section                             |    |

|     | of IGBT power modules; (d) power range of modern semiconductor devices                                  |    |

|     | together with the predominant package type                                                              | 5  |

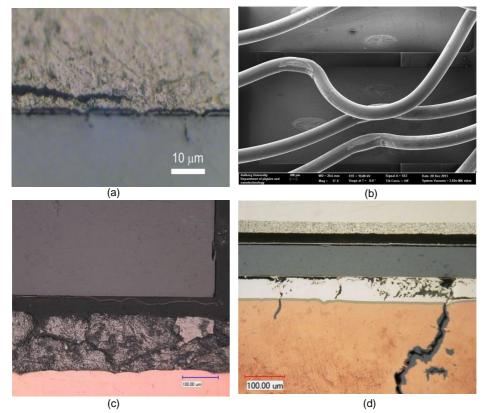

| 1.6 | Selected failures of semiconductor power devices: (a) bond wire heel crack-                             |    |

|     | ing, (b) bond wire lift-off, (c) solder degradation, (d) vertical cracks in the                         |    |

|     | substrate metal.                                                                                        | 7  |

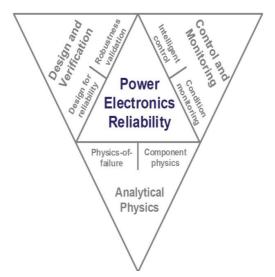

| 1.7 | The scope of reliability of power electronics.                                                          | 9  |

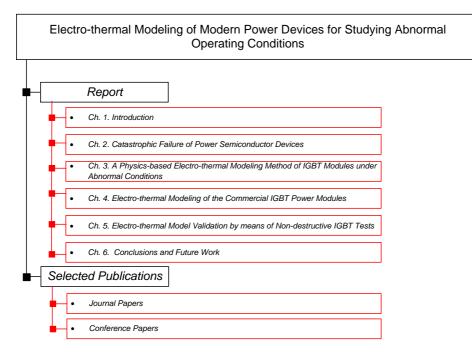

| 1.8 | Thesis structure and the studied topics.                                                                | 11 |

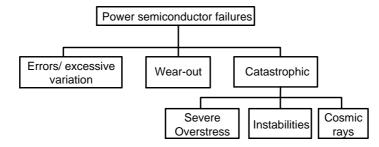

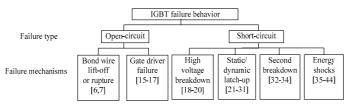

| 2.1 | Classification of power semiconductor devices failures.                                                 | 16 |

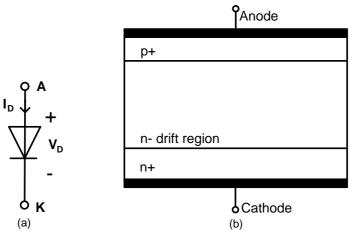

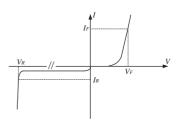

| 2.2 | Power diode symbol and structure: (a) circuit symbol with terminals: Anode                              |    |

|     | (A), Cathode (K); (b) cross section of most widely used power diode structure.                          | 16 |

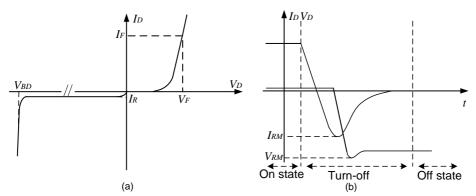

| 2.3 | Characteristics of power diodes: (a) I-V characteristics with parameters def-                           |    |

|     | initions; (b) normal turn-off waveforms.                                                                | 17 |

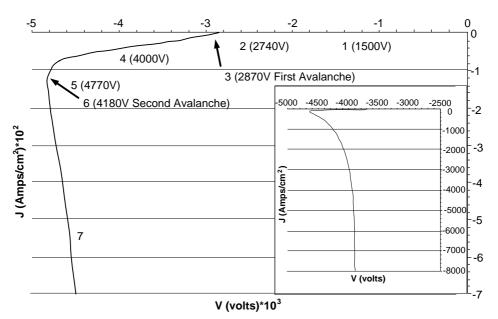

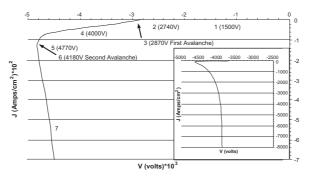

| 2.4 | First and second static avalanche breakdown of a 1700V rated power diode.                               | 20 |

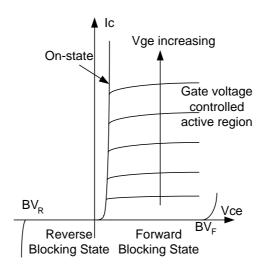

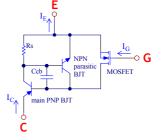

| 2.5 | IGBT component: (a) circuit symbol with terminals: Gate (G), Collector                                  |    |

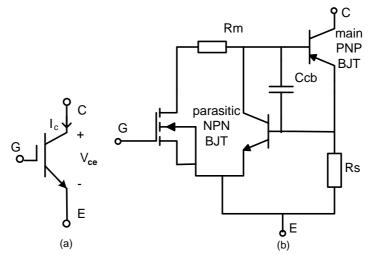

|     | (C), Emitter (E); (b) equivalent circuit. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$     | 21 |

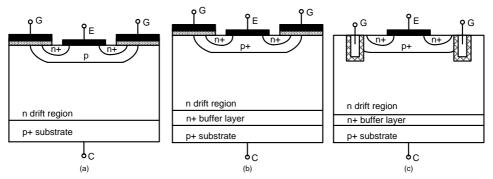

| 2.6 | Cross section of most widely used IGBT structures: (a) Non-Punch-Through                                |    |

|     | (NPT) IGBT; (b) Punch-Through (PT) IGBT with n+ buffer layer; (c)                                       |    |

|     | Trench-gate with soft/light PT or field stop layer IGBT                                                 | 22 |

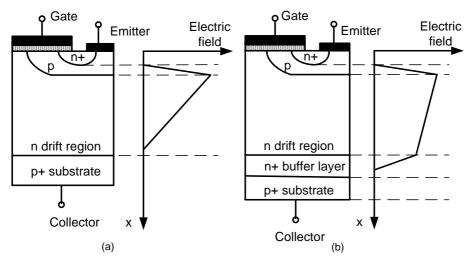

| 2.7          | The planer gate NPT and PT IGBT structures and corresponding electric fields: (a) planer gate NPT IGBT and electric field; (b) planer gate PT IGBT                                                                                                                                                                |          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0.0          |                                                                                                                                                                                                                                                                                                                   | 23       |

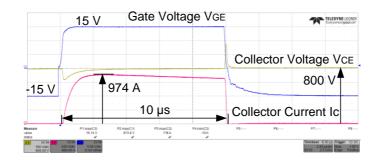

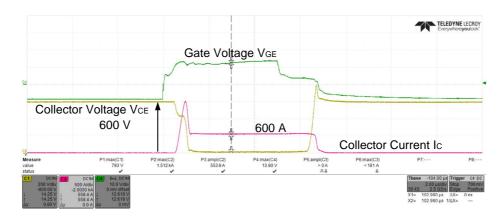

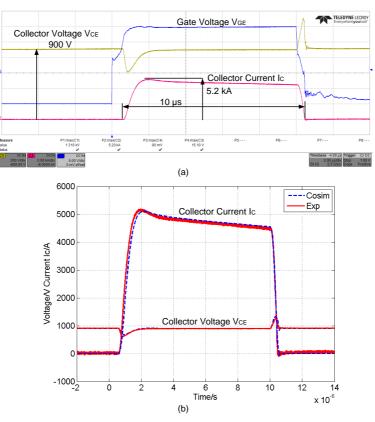

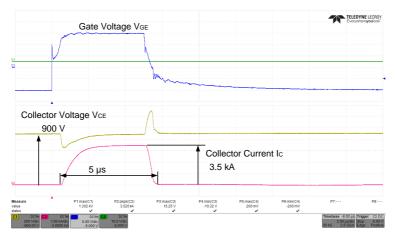

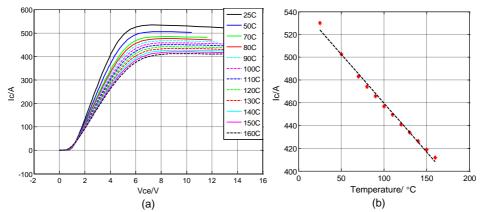

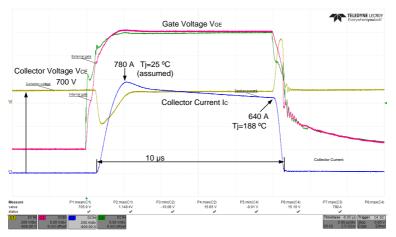

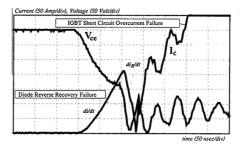

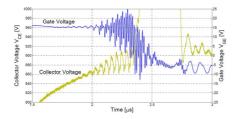

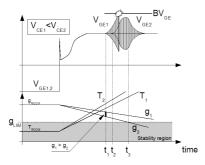

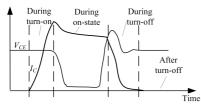

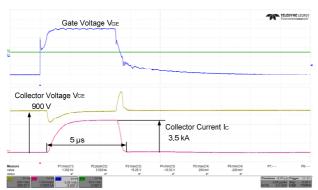

| 2.8<br>2.9   | Experimental waveforms of short circuit Type I test of a 1.7 kV / 150 A IGBT power module performed at 800 V of collector voltage. Time scale: 2 $\mu$ s/div; gate voltage: 5 V/div; collector voltage: 200 V/div; collector current:                                                                             | 24<br>27 |

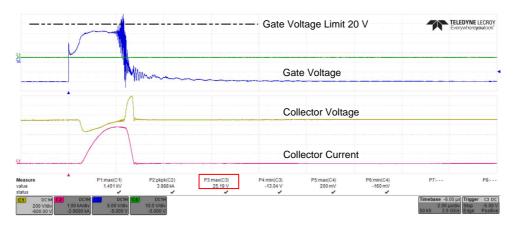

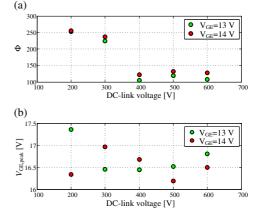

| 2.10         | Evidence of oscillations occurring during a short circuit test of a 1.7 kV / 1 kA IGBT power module performed at 900 V of collector voltage. Time scale: 2 $\mu$ s/div; gate voltage: 5 V/div; collector voltage: 200 V/div; collector current: 1 kA/div. The gate peak voltage was 25.19 V, whereas the absolute | 21       |

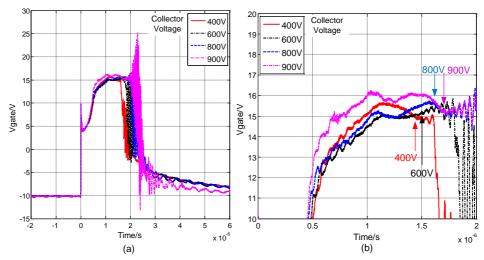

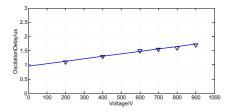

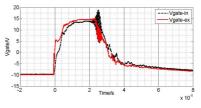

| 2.11         | emitter voltages: (a) gate voltage waveforms obtained at increasing collector voltages from 400 V to 900 V, (b) details of the same waveforms before the                                                                                                                                                          | 29       |

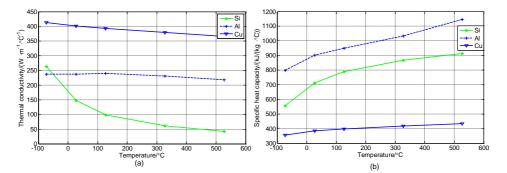

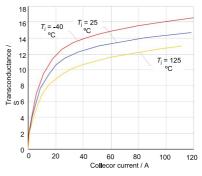

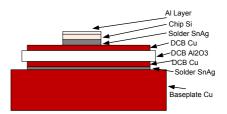

| $3.1 \\ 3.2$ | Temperature effects on the thermal properties of Si, Al, and Cu: (a) thermal                                                                                                                                                                                                                                      | 33<br>34 |

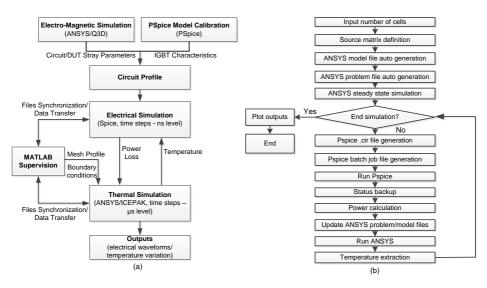

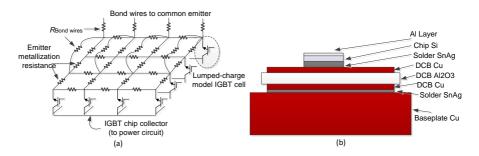

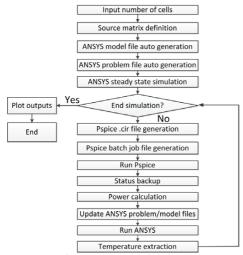

| 3.3<br>3.4   | Principle of the proposed electro-thermal modeling method: (a) the struc-<br>ture; (b) MATLAB script flow chat                                                                                                                                                                                                    | 37       |

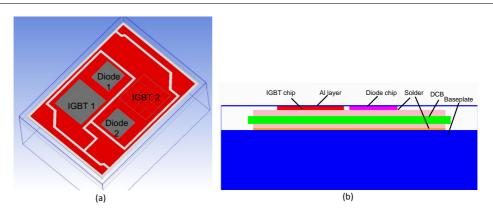

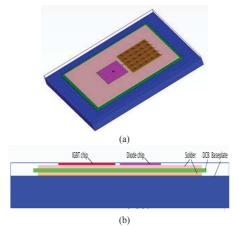

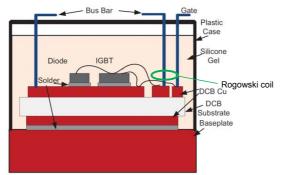

| 3.5          | Thermal model of one section of IGBT power module constructed in Icepak:<br>(a) 3D view of the geometry, (b) details of the cross section on the vertical                                                                                                                                                         | 39<br>40 |

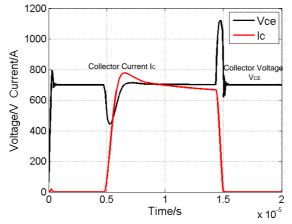

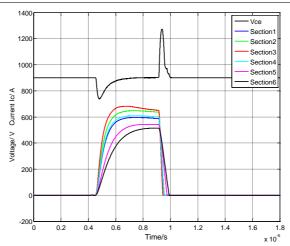

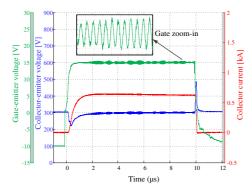

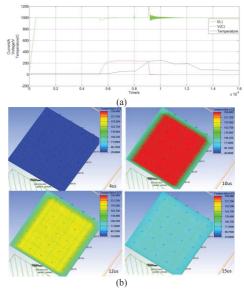

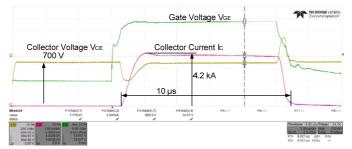

| 3.6          | Simulated collector current/voltage waveforms of the IGBT chip under 700                                                                                                                                                                                                                                          | 42       |

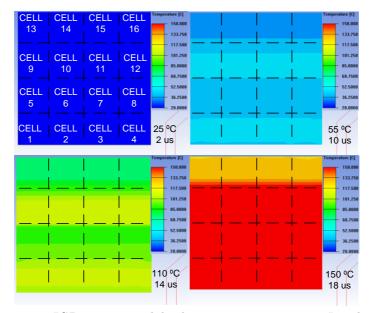

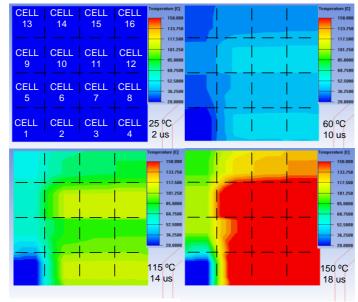

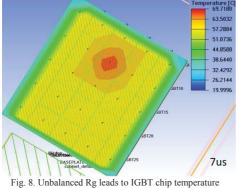

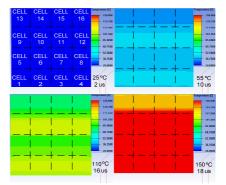

| 3.7          | IGBT power module chip temperature maps in Icepak during short-circuit at $2/10/14/18 \ \mu$ s (times and highest temperature at bottom right of each                                                                                                                                                             | 43       |

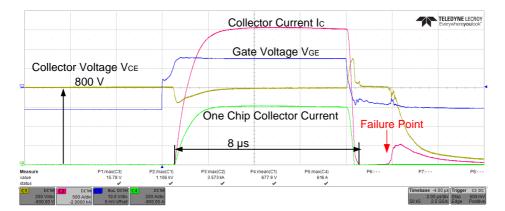

| 3.8          | Experimental waveforms of the "delay failure" for the 1.7 kV/1 kA IGBT module during a 800 V/10 $\mu$ s short circuit: time scale 2 $\mu$ s/div, collector voltage 200 V/div, collector current 500 kA/div, gate voltage 5 V/div, one                                                                             | 43       |

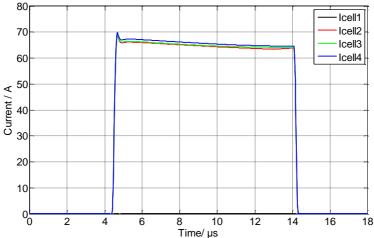

| 3.9          | Simulated current distribution among the IGBT cells 1-4 during short circuit                                                                                                                                                                                                                                      | 44       |

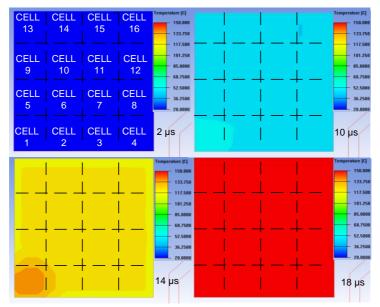

| 3.10         | IGBT power module chip temperature maps in Icepak during short circuit at $2/10/14/18 \ \mu$ s in case of one bond wire lift-off (temperature color bar – max 150 °C, min 20 °C).                                         | 45         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

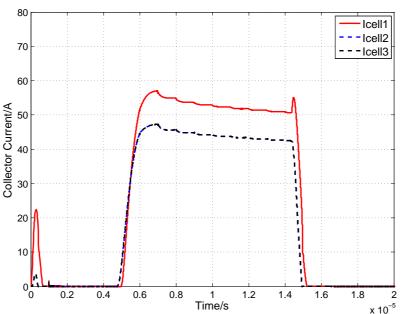

|              | Simulated current distribution among the IGBT cells 1-3 during short circuit in case that cell 1 has a $V_{th}$ degradation.                                                                                              | 46         |

| 3.12         | IGBT power module chip temperature maps in Icepak during short-circuit at $2/10/14/18 \ \mu$ s in case of $V_{th}$ degradation in cell 1 (temperature color bar – max 150 °C, min 20 °C).                                 | 47         |

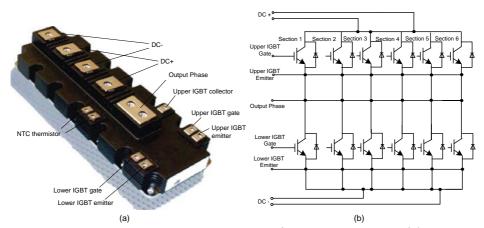

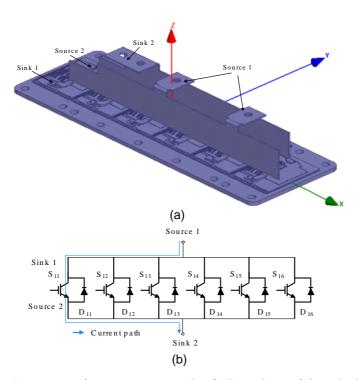

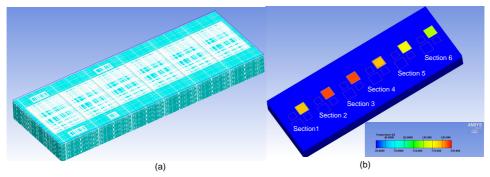

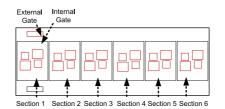

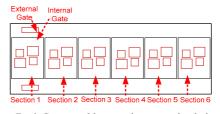

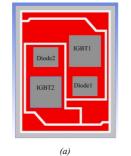

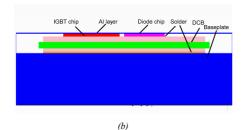

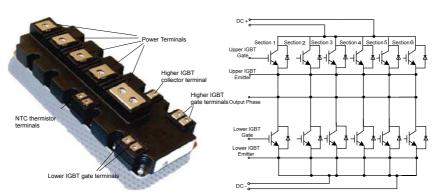

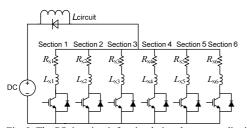

| 4.1          | Information of the studied $1.7 \text{ kV}/1 \text{ kA}$ power module: (a) a packaging outline picture; (b) internal structure of the power module with sections definition.                                              | 50         |

| 4.2          | Double pulse testing waveforms for 1.7 kV/1 kA module at 600 V DC voltage.<br>time scale: 2 $\mu$ s/div; collector voltage (C1): 200 V/div; collector current (C2): 500 A/div; gate voltage (C4): 10 V/div.               | 51         |

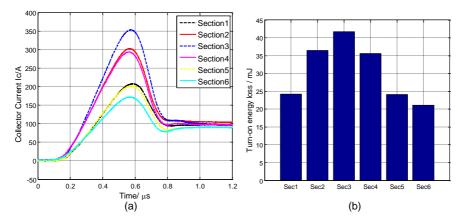

| 4.3          | Tests of $1.7 \text{ kV}/1 \text{ kA}$ module A at 600 V DC voltage: (a) measured current distribution among six sections during turn-on transient; (b) measured turn-on energy loss distribution among the six sections. | 52         |

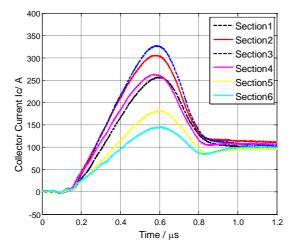

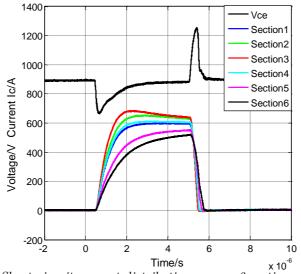

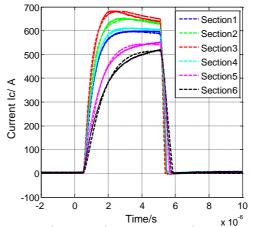

| 4.4          | Measured current distribution among six sections of the 1.7 kV/1 kA module $-$                                                                                                                                            |            |

| 4.5          | B at 600 V DC voltage                                                                                                                                                                                                     | 53         |

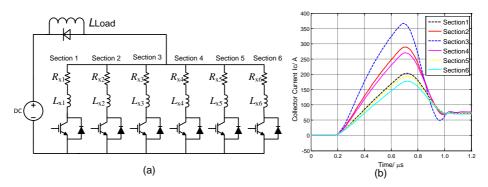

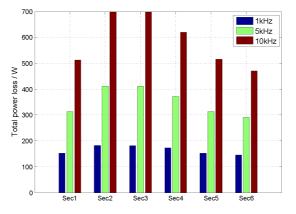

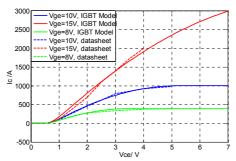

| 4.6          | analysis, where the current path through the section 1 is given Simulations of the stray parameters effects inside the $1.7 \text{ kV/1 kA}$ module:                                                                      | 54<br>56   |

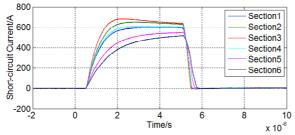

| 4.7          | (a) PSpice circuit. (b) simulated current distribution among six sections Collector current waveforms among the parallel sections during the $900 \text{ V}/10$                                                           | 56         |

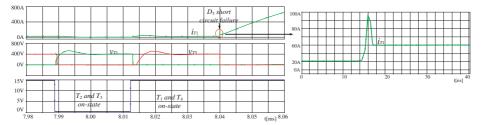

| $4.8 \\ 4.9$ | $\mu$ s short circuits in a pure PSpice simulation                                                                                                                                                                        | $57 \\ 57$ |

|              | module                                                                                                                                                                                                                    | 58         |

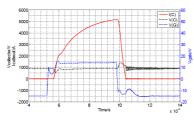

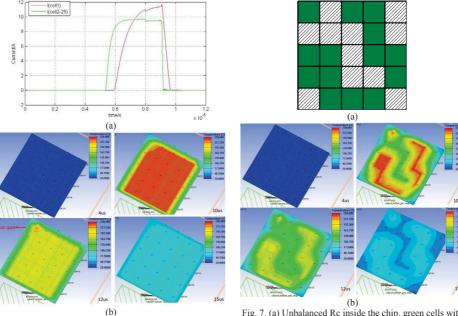

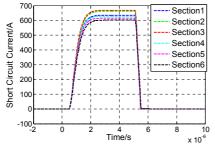

|              | Simulated current distribution waveforms among six sections of the 1.7 kV/1 kA module under the 900 V/5 $\mu$ s short circuit.                                                                                            | 59         |

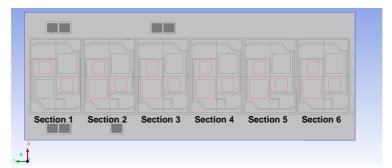

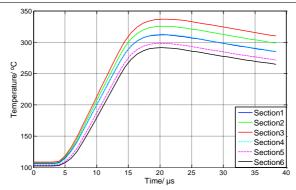

| 4.11         | Simulations of IGBT module under short circuit: (a) the mesh profile; (b) simulated temperature profile at the end of the short circuit pulse(temperature                                                                 | <u> </u>   |

| 4.12         | color bar – max 220 °C, min 20 °C)                                                                                                                                                                                        | 60         |

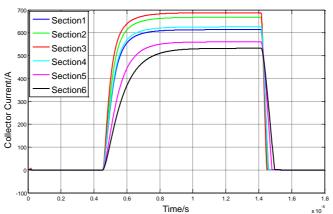

| 4.13         | sections at different switching frequencies                                                                                                                                                                               | 60         |

|              | uneven initial temperatures                                                                                                                                                                                               | 61         |

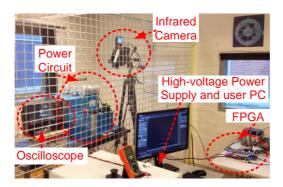

| 5.1          | Picture of the high current Non-Destructive Tester (NDT).                                                                                                                                                                 | 64         |

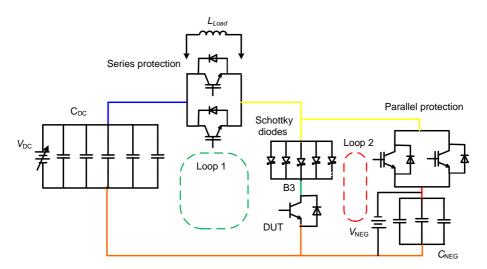

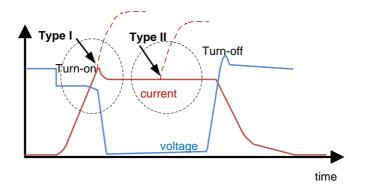

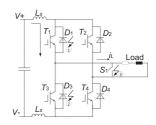

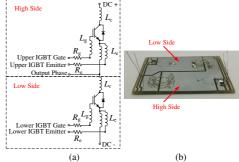

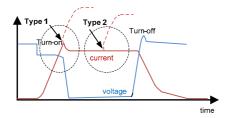

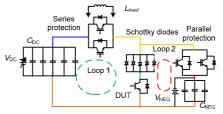

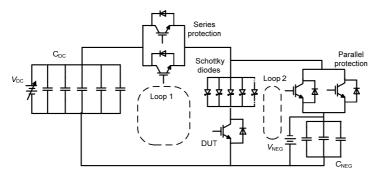

| $5.2 \\ 5.3$ | Detailed schematic of the Non-destructive Tester circuit                                                                                                                                                                                                                                                                          | 66 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

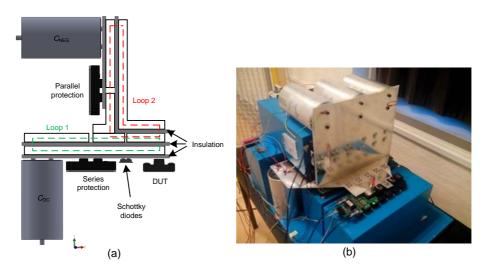

| 5.4          | turn-on, whereas the Type II short circuit occurs during the conduction state.<br>Busbar design of the nondestructive testing circuit. (a) principle cross section                                                                                                                                                                | 67 |

|              | of the busbar layers - Loop 1 is the horizontal one, Loop 2 is the vertical one.<br>(b) picture of the final physical prototype                                                                                                                                                                                                   | 67 |

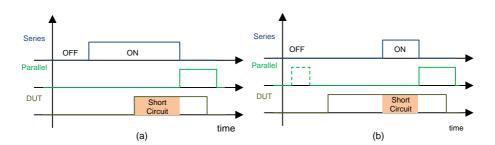

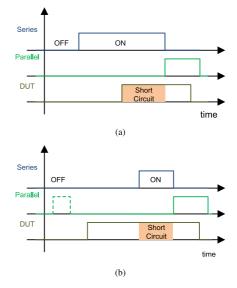

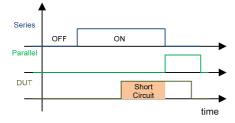

| 5.5          | Timing settings for two types of short circuits. (a) timing diagram for Type                                                                                                                                                                                                                                                      | 07 |

| 0.0          | I short circuit. (b) timing diagram for Type II short circuit                                                                                                                                                                                                                                                                     | 68 |

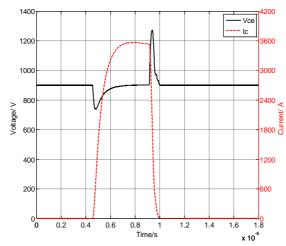

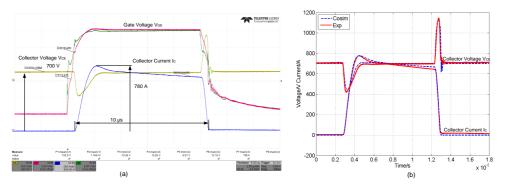

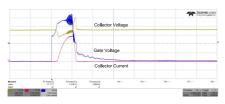

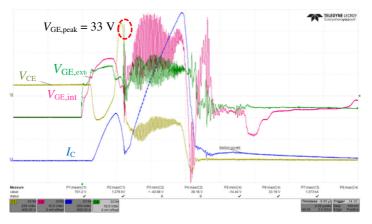

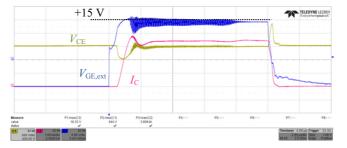

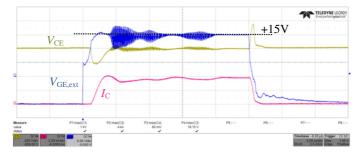

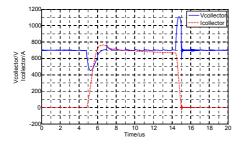

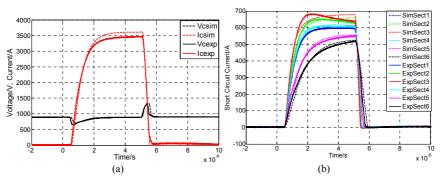

| 5.6          | Short circuit of one section inside the IGBT module: (a) experimental wave-<br>forms during a 700 V/10 $\mu$ s short circuit at room temperature 25 °C: time<br>scale 2 $\mu$ s/div, collector voltage 200 V/div, collector current 200 A/div, gate<br>voltage 5 V/div, (b) comparison between the electro-thermal simulation and |    |

|              | the experimental waveforms under the same condition                                                                                                                                                                                                                                                                               | 69 |

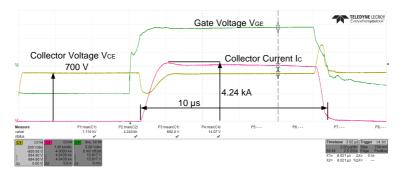

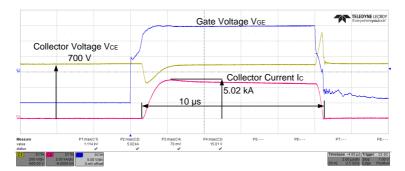

| 5.7          | Electrical behavior of the 1.7 kV/1 kA IGBT module during a 700 V/10 $\mu$ s                                                                                                                                                                                                                                                      |    |

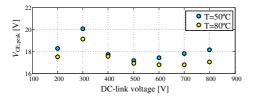

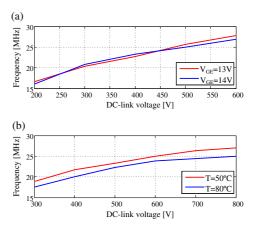

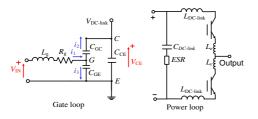

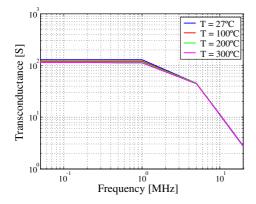

|              | short circuit: time 2 $\mu$ s/div, collector voltage 200 V/div, collector current 1 kA/div, gate voltage 5 V/div                                                                                                                                                                                                                  | 70 |