#### **Aalborg Universitet**

#### **Active Stabilization Techniques for Cascaded Systems in DC Microgrids**

Lorzadeh, Omid

DOI (link to publication from Publisher): 10.54337/aau455012597

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Lorzadeh, Ó. (2021). Active Stabilization Techniques for Cascaded Systems in DC Microgrids. Aalborg Universitetsforlag.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# ACTIVE STABILIZATION TECHNIQUES FOR CASCADED SYSTEMS IN DC MICROGRIDS

# BY OMID LORZADEH

**DISSERTATION SUBMITTED 2021**

# Active Stabilization Techniques for Cascaded Systems in DC Microgrids

Ph.D. Dissertation

#### Omid Lorzadeh

Aalborg University

Department of Energy Technology

Thesis submitted to the Doctoral School of Engineering and Science,

Aalborg University, Denmark, for the degree of Doctor of Philosophy

August 2021

Dissertation submitted: 08 August 2021

PhD supervisor: Associate Prof. Mohsen N. Soltani

Aalborg University

Assistant PhD supervisor: Associate Prof. Amin Hajizadeh

Aalborg University

PhD committee: Associate Professor Sanjay Chaudhary (chairman)

Aalborg University

Professor Martin Ordonez

The University of British Columbia

Associate Professor Maryam Saeedifard

Georgia Institute of Technology

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: Department of Energy Technology

ISSN (online): 2446-1636

ISBN (online): 978-87-7210-979-4

Published by:

Aalborg University Press

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk

forlag.aau.dk

© Copyright: Omid Lorzadeh

Printed in Denmark by Rosendahls, 2021

### **Curriculum Vitae**

Omid Lorzadeh received the B.Sc. degree in electrical engineering and M.Sc. degree in control engineering from the Shiraz University, Shiraz, Iran, in 2006 and 2011, respectively. He is currently working toward the Ph.D. degree in electrical engineering with the Department of Energy Technology, Aalborg University, Aalborg, Denmark. He was a Visiting Researcher with the Center for Combined Smart Energy Systems, Technical University of Munich (TUM), Germany, Iran in 2020. His research interests include modeling, advanced control concepts, power quality, and stability issues of power electronics-based power systems and microgrids.

#### **Professional Experience:**

**Jun-Dec 2019-** Electrical and Control (E&C) Engineer, ATKINS A/S (SNC-Lavalin Group, Denmark)-Student Assistant Position.

2012-2018 Lead/Senior E&C Engineer, Maroon Sazeh Shiraz Co, Tehran, Iran.

2010-2012 E&C Engineer, Maroon Sazeh Shiraz Co, Tehran, Iran.

2006-2009 Electrical Engineer, Fars Scout Industrial Co, Shiraz, Iran.

#### Curriculum Vitae

#### **Preface:**

This Ph.D. dissertation entitled "Active Stabilization Techniques for Cascaded Systems in DC Microgrids" has been submitted to the Doctoral School of Aalborg University, in partial fulfillment of the requirement for the Ph.D. degree.

All researches are carried out at the Department of Energy Technology, Aalborg University from July 2018 to June 2021 under supervision of Associate Prof. Mohsen Soltani and co-supervision of Associate Prof. Amin Hajizadeh.

This dissertation has been submitted in the partial fulfillment for the Ph.D. degree. The thesis is based on the published and submitted papers, and parts of the papers are used directly or indirectly in the thesis. The present form of the thesis cannot be openly published, only limited and closed circulation as copyright may not be ensured.

Omid Lorzadeh

#### Preface

#### **English Summary**

In recent years, multi-converter DC power distribution networks or DC Microgrids (MGs) have been extensively used in applications such as more electric aircraft, more electric ships, hybrid vehicles, and data centers. This is owing to high power transfer capacity, no frequency and reactive power control requirements, and avoidance of numerous power conversions provided by these systems. Hence, this has led to the superiority of these types of systems over their AC MGs counterparts in terms of achieving simple control structures and higher productivity. DC/DC conversion cascaded systems (shortened cascaded systems) are known as the prevailing subsystems in DC MG relying on their modularity and high efficiency. Despite the potential instability resulting from interactions between the individually designed feedback-controlled converters in these predominant interconnections, supplying loads in a tightly-controlled form (active loads) such as constant power loads (CPLs) inject a destabilizing effect into the network. CPLs tend to destabilize the system owing to their negative resistance characteristics that cause reduced system damping, limited cycle oscillation and voltage collapse on the DC bus, degraded stability margins, and in the worst case, the shutdown of the whole system.

Consequently, addressing active load's instability effect is one of the most vital issues in obtaining a stable cascaded system, which has lately become an attractive and challenging topic. Although several stabilization techniques have been proposed in this area, most of them suffer from shortcomings and limitations that include the use of complex corrective control structures with various levels of conservatism in the design and satisfaction of stability criteria. Besides, their effectiveness and applicability against unforeseen changes in the network, such as changes in input voltage level and load set, as

well as step changes in the output voltage reference, have not been comprehensively evaluated.

Prompted by the mentioned challenges, this work proposes novel active damping (AD)-based stabilization techniques for suppressing CPL instability of cascaded systems in DC MGs without affecting the dynamic performance of the load-side converter. These proposed design-oriented active stabilization approaches take advantage of simple control structures with straightforward adjustment of a control parameter. The presented AD stabilization methods are tested by Matlab/Simulink in the discrete-time domain and also experimental implementation by dSPACE for three cascaded systems comprising basic DC/DC converters, i.e. Buck, Boost, and Buck-Boost converters loaded with CPLs and resistive load. The results are provided as proof of concept, thus validating the theoretical findings and demonstrating the advantages of the proposed approaches during different operational cases such as input voltage changes, plug and play (PnP) operational of CPLs, and step changes in output voltage references. The outcome of this work proves the effectiveness and operational feasibility of the AD-based stabilization techniques on the cascaded systems feeding multiple CPLs in DC MGs.

#### Dansk Resume

I de senere år har multi-converter DC strømforsyningsnetværk eller DC Microgrids (MG'er) været meget udbredt i applikationer såsom mere elektriske fly, mere elektriske skibe, hybridbiler og datacentre. Dette skyldes høj effekt overførselskapacitet, ingen krav til frekvens og reaktiv effektstyring og undgåelse af adskillige effektkonverteringer leveret af disse systemer. Derfor har dette ført til overlegenhed af disse typer systemer i forhold til deres AC MG'er-kolleger med hensyn til at opnå enkle kontrolstrukturer og højere produktivitet. DC/DC-kaskade konverterings systemer (kortere kaskade systemer) er kendt som de fremherskende undersystemer i DC MG, der er afhængige af deres modularitet og høj effektivitet. På trods af den potentielle ustabilitet som følge af interaktioner mellem de individuelt design konvertere i disse dominerende sammenkoblinger, levering af belastninger i stramt kontrolleret form (aktive belastninger) såsom konstant effektbelastning (CPL'er) injicerer en destabiliserende effekt i systemet. CPL'er har tendens til at destabilisere systemet på grund af deres negative modstandskarakteristika, der forårsager reduceret system dæmpning, begrænset cyklusoscillation og spændingskollaps på jævnstrømsbussen, forringede stabilitetsmargener og i værste fald nedlukning af hele systemet.

Derfor er adressering af aktiv belastnings stabilitet effekt et af de mest vitale problemer i at opnå et stabilt kaskadet system, som for nylig er blevet et attraktivt og udfordrende emne. Selv om flere stabiliseringsteknikker er blevet foreslået på dette område, lider de fleste af dem med mangler og begrænsninger, der inkluderer brugen af komplekse korrigerende kontrolstrukturer med forskellige niveauer af konservatisme i udformningen og opfyldelsen af stabilitetskriterier. Derudover er deres effektivitet og anvendelighed mod uforudsete ændringer i netværket, såsom variationer i

indgangsspænding belastningssæt, trinændringer og samt udgangsspændingsreferencen ikke blevet vurderet grundigt. Tilskyndet til de nævnte udfordringer foreslår dette arbejde nye aktive dæmpnings baserede (AD)-baserede stabiliseringsteknikker til undertrykkelse af CPL-ustabilitet af kaskadede systemer i DC MG'er uden at påvirke den dynamiske vdeevne for belastningsside konverteren. Disse foreslåede designorienterede aktive stabiliseringsmidler drager fordel af enkle kontrolstrukturer med ligetil justering af en kontrolparameter. De præsenterede AD-stabiliseringsmetoder testes af Matlab / Simulink i det diskrete tidsdomæne og også eksperimentel implementering af dSPACE til tre kaskadede systemer, der omfatter grundlæggende DC/DC konvertere, dvs., Buck, Boost og Buck-Boostomformere indlæst med CPL'er og resistiv belastning. Resultaterne tilvejebringes som bevis på konceptet og validerer således de teoretiske fund og demonstrerer fordelene ved de foreslåede tilgange under forskellige operationelle tilfælde såsom indgangs spændings ændringer, tilslut og brug operation af CPL'er og trinændringer i udgangsspændingsreferencer. Resultatet af dette arbejde beviser effektiviteten, og den operationelle gennemførlighed af AD-baserede stabiliseringsteknikker på de kaskadede systemer, der fodrer flere CPL'er i DC MG'er.

#### Acknowledgment

At First, I would like to express my great gratitude to my supervisor, Associate Professor Mohsen Soltani for all trust and helps given to me to pursue a Ph.D. He always inspired and encourage me with new ideas during this journey. He has not been only an advisor also as a friend making the work environment more pleasant for me. Also, I am highly indebted to my cosupervisor, Associate Professor Amin Hajizadeh, for help, supports, and valuable comments to ensure the success of my researches on this Ph.D. study.

I sincerely thank my friends and colleagues, Meisam Sadi, Mehdi Nikbakht Fini, Mojtaba Yousefi, Navid Bayati, and Zahra Nourbakhsh Soltani for making enlivening, and interesting times on my Ph.D. journey.

I also like to thank Prof. Hamacher and Dr. Vedran Perić and their team, CoSES, at Technical University of Munich (TUM) in Germany for hosting me during study abroad. Thanks for the hospitality of the CoSES team and for making a successful scientific research for me.

At the end, I would like to say a huge thanks to my family from the bottom of my heart. Thanks, Mehrnaz, my lovely wife, for encouraging me with her patience and kindness as well as my honey girl, Rose, through this way. Thanks, my mother, Farideh, and my father, Ghasem, for trusting me on my ideas and guiding me during tough moments. Also thanks my brothers, Mohammad Ali, and Iman for helping me with my entire life.

I would like to thank God for giving me the strength, and knowledge to undertake this research study and to persevere and complete it satisfactorily. Without his blessings, this achievement would not have been possible.

# Contents

| Curriculum VitaeIII                                                |

|--------------------------------------------------------------------|

| PrefaceV                                                           |

| English SummaryVII                                                 |

| Dansk ResumeIX                                                     |

| AcknowledgmentXI                                                   |

| CHAPTER 1: Introduction 1                                          |

| 1.1. Background and Motivation                                     |

| 1.2. Project Objectives                                            |

| 1.3. Outline of the thesis                                         |

| 1.4. List of publications                                          |

| 1.5.Scientific Contributions                                       |

| CHAPTER 2: Stabilization of DC Microgrids11                        |

| 2.1. Dynamic Characteristics of DC Microgrids                      |

| 2.2. Challenges of stability in DC Microgrids                      |

| 2.2.1. Problem Definition                                          |

| 2.3. Active Stabilization of a cascaded system with CPL            |

| 2.3.1 Literature Review                                            |

| CHAPTER 3: Source-Side Virtual RC Damper-Based Active              |

| Stabilization Strategy17                                           |

| 3.1. Methodology                                                   |

| 3.1.1 Advantages and Main Contributions                            |

| 3.2. Proposed Virtual RC Damper-Based Active Stabilizer Method for |

| Cascaded Systems in DC MGs                                         |

| 3.2.1 DC/DC Buck Converter feeding Resistive Load and CPLs 20      |

| 3.2.1.1 Modeling and Stability Analysis                            |

| 3.2.1.2 Control Realization                                       | 23   |

|-------------------------------------------------------------------|------|

| a. Circuit Physical Meaning                                       | 24   |

| b. Choosing an Effective AD Term ( $K_{AD}$ )                     | 26   |

| 3.2.1.3 Simulation and Experimental Results                       | 32   |

| 3.2.1.4 Comparative study with the PI+Designed D Control          |      |

| scheme                                                            | 39   |

| 3.2.1.5 Comparative study with the Virtual Series <i>RL</i> Dampe | er-  |

| Based Stabilization Technique Proposed by [31]                    | 40   |

| 3.2.2 DC/DC Boost and Buck-Boost Converters feeding Resistive     |      |

| Load and CPLs                                                     | 41   |

| 3.2.2.1 Modeling and Stability Analysis                           | 42   |

| 3.2.2.2 Control Realization                                       | 44   |

| a) Circuit Physical Meaning                                       | 44   |

| b) Choosing an Effective $K_{AD}$                                 | 46   |

| 3.2.2.3 Simulation and Experimental Results                       | 48   |

| CHAPTER 4: Source-Side Adaptive Parallel-Virtual Resistance (AP   | VR)  |

| Control Strategy -Based Stabilization Scheme                      | 53   |

| 4.1. Methodology                                                  | 53   |

| 4.2. Unified Average Modeling of the DC/DC Converter Systems Loa  | ded  |

| by Resistive Load and CPLS                                        | 55   |

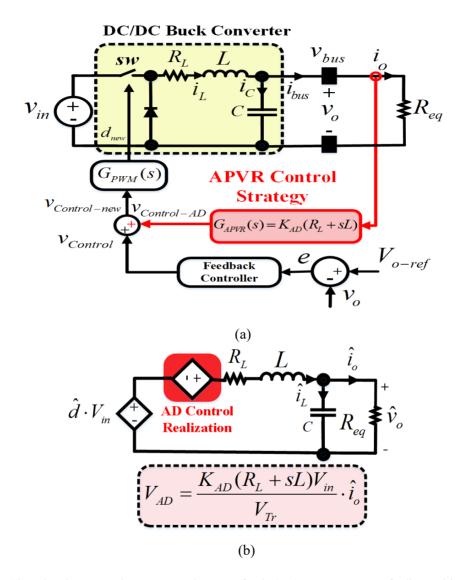

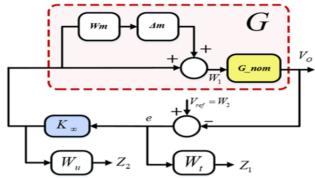

| 4.3. Proposed APVR Control Strategy for Cascaded Systems in DC MC | Gs56 |

| 4.3.1 DC/DC Buck Converter feeding Resistive Load and CPLs        | 56   |

| 4.3.1.1 Control Realization of the APVR Control Strategy          | 56   |

| a) Circuit Physical Meaning                                       | 56   |

| b) Designing of Effective AD Control Coefficient                  | 61   |

| c) Intrinsic Load Adaptive feature                                | 64   |

| 1312 Simulation and Experimental Results                          | 65   |

| 4.3.2 DC/DC Boost and Buck-Boost Converters feeding Resistive Lo                                                           | oad  |

|----------------------------------------------------------------------------------------------------------------------------|------|

| and CPLs                                                                                                                   | . 70 |

| 4.3.2.1 Control Realization of the APVR Control Strategy                                                                   | . 70 |

| a) Circuit Physical Meaning                                                                                                | . 70 |

| b)Designing of Effective AD Control Coefficients                                                                           | . 75 |

| 4.3.3 Simulation and Experimental Results                                                                                  | . 78 |

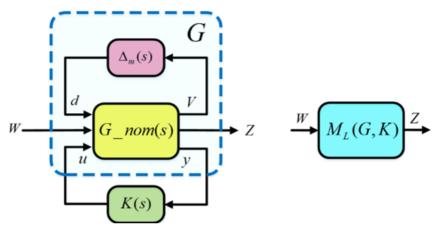

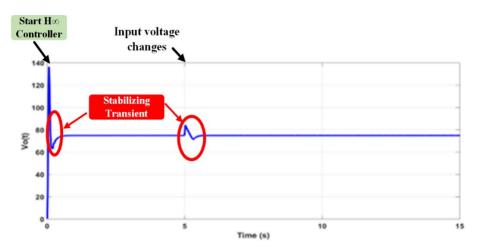

| 4.4. Comparison with H∞-control method                                                                                     | .82  |

| 4.4.1 Methodology                                                                                                          | .82  |

| 4.4.2 Simulation Results and Comparison Study                                                                              | .85  |

| CHAPTER 6: Conclusion and Future Work                                                                                      | . 87 |

| 5.1. Conclusion                                                                                                            | . 87 |

| 5.2. Future Work                                                                                                           | . 90 |

| 5.3. References                                                                                                            | . 91 |

| Papers                                                                                                                     | .97  |

| A Source-Side Virtual RC Damper-Based Stabilization Technique<br>Cascaded Systems in DC Microgrids                         | for  |

| B Active Load Stabilization of Cascaded Systems in DC Microgr<br>Using Adaptive Parallel-Virtual-Resistance Control Scheme | ids  |

| C H∞-Based Robust Controller for Step-Down Non-Isolated DC/Converter Loaded by Constant Power Load in DC Microgrids        | DC   |

feeding constant power load

$\label{eq:converter} \textbf{A novel active stabilizer method for DC/DC power converter systems}$

#### Contents

# Chapter 1

#### Introduction

This chapter gives an introduction, background, motivation, and aims of this thesis.

#### 1.1. Background and Motivation

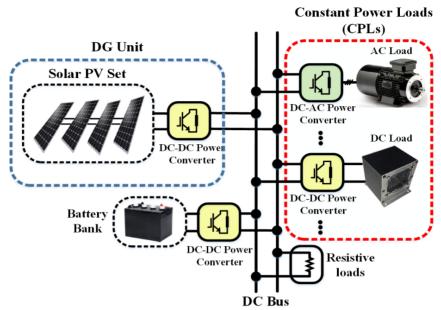

With the increasing trend of developments in power electronics, modern control technologies, worldwide demand for more and more use of renewable energy sources, and energy storage systems, DC distribution is treated as one of the preferred architectures for power distribution grids [1]-[6]. These systems have the potential for higher efficiency and reliability (by preventing multiple conversion stages), better power transfer capacity of lines, and rapid response compared to their AC counterparts [1]-[6]. In addition to these features, DC distribution systems also offer benefits in terms of the nonexistence of reactive power flow and power quality issues as well as the elimination of synchronization problems (due to lack of frequency and phase), leading to non-complexity in control structures and robust performance in comparison with AC-linked systems [1]-[6]. These superiorities have led modern societies to move more and more towards the use of DC distribution with different voltage and power levels in many practical applications [1]-[3],[7] and [8]. Nowadays, modern transportation systems (air, land, and sea), residential and commercial facilities, all new appliances, data centers, telecom systems as well as renewable energy resources increasingly rely on DC power distribution technology [2]. Accordingly, the use of DC at low voltage levels has dramatically increased in these applications, where all of them can be classified under a similar label, i.e., DC Microgrid (MG) [1]. In general, DC MGs can operate on an island or grid-connected modes [1],[2]. The schematic diagram of generic DC MGs is illustrated in Fig.1.1. As seen, in DC MGs,

Fig. 1.1 A typical structure of DC MGs.

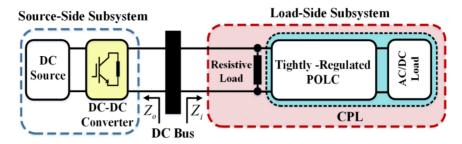

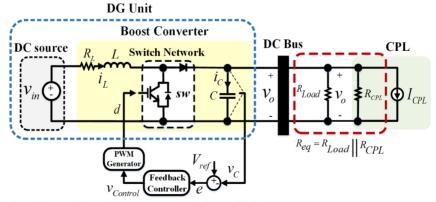

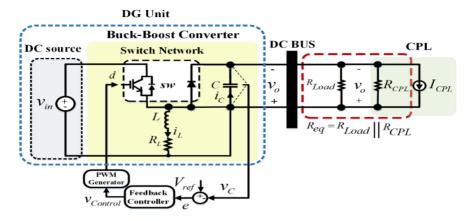

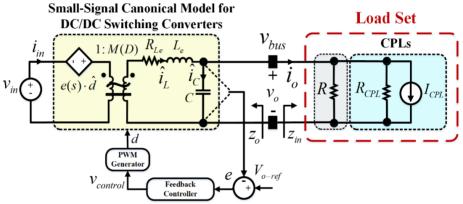

from the source-side, the distributed generation (DG) units (power sources plus their respective controllable power electronics converters) power is injected into the intermediate DC bus to generate a regulated voltage on it [9]. In terms of loading, besides passive (resistive) loads, active loads are mainly connected to the DC bus through tightly regulated point-of-load converters (POLCs) [9]. Therefore, the cascaded interconnection of source- and load-side subsystems is a prominent configuration in such networks, where switching power converters are usually designed and tested individually with only resistive loads [9]-[13] and [15]. A generic model of such configuration in DC MGs is depicted in Fig. 1.2. In these structures, even if each converter is individually well-designed, it can lead to poor dynamic performance, impedance interactions between the source and load side circuits, and ultimately inject an unstable state into the system [9],[10]. In this regard, POLCs in a multi- converter DC distribution system having a cascaded

Fig. 1.2 a generic cascaded system.

structure with a rapid that behaves as constant power loads (CPLs) can be considered a clear example of these issues [8]-[10]. CPLs receive constant power from their feeder, regardless of its terminal voltage when the bandwidth and control loop gain of the load converter is adequately grater than that of the source converter [9], [11]. From the point of view of the upstream circuit, the CPL characteristic behaves as a negative resistance [9]. Though the inherent incremental negative resistance feature of the CPL guarantees the fast-dynamic performance of the converter of the load-side, it will jeopardize the stability of cascaded systems [9]-[12],[15]. This instability effect on cascaded systems can cause reduced system damping, limited cycle oscillation and voltage collapse on the DC bus, degraded stability margins, and in the worst case, blackout of the whole microgrid. Therefore, the stability issues and active stabilization solutions for DC MGs under such loads can be an attractive and challenging topic.

#### 1.2. Project Objectives

Motivated by the mentioned issues and challenges in the previous section, overcoming CPL instability in the architecture indicated in Fig. 1.2 is one of the key points in obtaining a stable low voltage direct current (LVDC) network or DC MGs. Although several techniques have been presented for active stabilization of the CPL's destabilizing effects in DC MG applications based

on different stability criteria, many of them suffer from shortcomings and limitations. Weaknesses of existing techniques can be included as follows, but not limited to:

- Complex control structures with different control parameters and the use of a high number of measurement sensors.

- High levels of conservatism in designing and satisfying stability criteria.

- Affecting the desirable and fast dynamic performance of the load-side converter.

- Incompatibility, inflexibility, and impracticality for all cascaded systems comprising the basic DC/DC converters (Buck, Boost, Buck-Boost) feeding CPLs (Lack of benefit from a similar control structure).

- Absence of a comprehensive evaluation regarding their effectiveness and dynamic performance under unforeseen changes in the system, i.e., load level (PnP operation), input voltage amplitude, and step changes in the output voltage reference, simultaneously.

Therefore, research to achieve active stabilization approaches for suppressing CPL's instability in DC MGs that well address the limitations and shortcomings of past works remains a critical research gap in this area. Hence, the research hypotheses are as follows:

• It is possible to robustly stabilize with fast dynamic response for the DC-DC cascaded systems with multiple CPLs in DC MGs under anticipated changes in the input voltage, load level, and output reference voltage while maintaining desirable dynamic load performance.

Accordingly, the aims of this project are classified as follows, step by step;

- ➤ Investigating the dynamic characteristics of DC MGs and analyzing instability issues.

- Modelling DC/DC conversion cascaded systems with resistive load and CPL in DC MG applications and evaluating dynamic and transient performance under different operational cases.

- ➤ Small-signal stability analysis for three DC/DC conversion cascaded systems (Buck, Boost, Buck-Boost converters) with resistive and multiple CPLs, separately and identification of stability conditions for these dominant structures.

- Proposing new active stabilization methods to compensate for the CPL instability effects with the aim of covering the limitations and shortcomings of existing works.

- > Experimental implementation of proposed stabilization schemes to confirm their feasibility in real life and to validate theoretical findings.

#### 1.3. Outline of the thesis

The outcome of this Ph.D. thesis is expected to be a collection of related published/submitted articles during the performed project period. In addition, the structure of this thesis is as follows:

**Chapter 1.** This chapter briefly introduces stability issues and their challenges for DC MGs, motivation, research objectives, list of published journals and conference papers.

**Chapter 2.** First, this section begins by describing the dynamic characteristics of DC MGs and defining the problem for the stability of these systems. Then, a literature review on the active stabilization solutions, the techniques functional comparison, and existing works for suppressing DC MG's destabilizing effects induced by CPLs are carried out.

Chapter 3. presents a new source-side AD-based stabilization method for cascaded systems in DC MGs. This stabilizer approach is realized by a virtual series *RC* damper in parallel with the source converter's capacitor for suppressing CPL destabilizing effect without compromising the dynamic performance of the load converter. Using this design-oriented AD control scheme that takes advantage of an easy control structure with a simple adjustment of the control parameter, the system stability is ensured. The superiority and effectiveness of the proposed stabilizer technique in terms of the transient and dynamic performances, reference voltage tracking, and robust stability compared to other methods that are close to ours, are tested and validated by simulations and experimentation implementations. The content of this chapter has been presented in the first journal paper that is published in IEEE Transaction of Energy Conversion.

Chapter 4. introduces a novel active stabilization method for cascaded systems in DC MGs using an adaptive parallel-virtual-resistance (APVR) control scheme. The presented load adaptive-based source-side AD stabilizer approach is achieved by positive proportional-derivative feedback of the equivalent load current with an intrinsic self-tuning control parameter without affecting the dynamic performance of the load set. The design-oriented APVR control strategy ensures stability and dynamic performance of the system through actively compensating the CPLs (active loads) destabilizing effect by utilizing a simple control structure and easy control parameter adjustment. Moreover, the high robustness and effectiveness of the offered active stabilization idea against unforeseen variations in input voltage level and plugand-play (PnP) of CPLs (load changes) without knowledge of their value are verified. Simulation and experimental results have been validated the applicability and flexibility of the proposed stabilizer technique by applying and testing on the three cascaded systems containing basic DC/DC converters

(Buck, Boost, and Buck-Boost) supplying CPLs in DC MG. The content of this chapter has been reported in the second journal paper that is under review in IEEE Journal of Emerging and Selected Topics in Power Electronics.

#### 1.4. List of publications

The following is a list of papers published/ submitted during the Ph.D. study.

#### Journal Papers

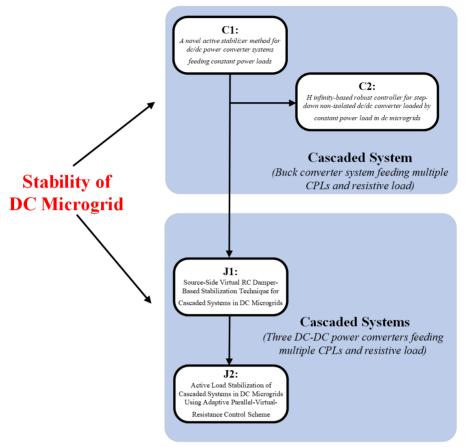

- **J1.** O. Lorzadeh, I. Lorzadeh, M. Soltani and A. Hajizadeh, "Source-Side Virtual RC Damper-Based Stabilization Technique for Cascaded Systems in DC Microgrids," in IEEE Transactions on Energy Conversion, doi: 10.1109/TEC.2021.3055897. (Published)

- **J2.** O. Lorzadeh, I. Lorzadeh, M. Soltani, A. Hajizadeh, and K. Jessen "Active Load Stabilization of Cascaded Systems in DC Microgrids Using Adaptive Parallel-Virtual-Resistance Control Scheme," IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021. (under review).

#### Conference

- C1. O. Lorzadeh, I. Lorzadeh, M. N. Soltani, and A. Hajizadeh, "A novel active stabilizer method for dc/dc power converter systems feeding constant power loads," in 2019 IEEE 28th International Symposium on Industrial Electronics (ISIE), pp. 2497–2502. IEEE, 2019.

- **C2.** O. Lorzadeh, I. Lorzadeh, M. N. Soltani, and A. Hajizadeh, "H infinity-based robust controller for step-down non-isolated dc/dc converter loaded by constant power load in dc microgrids," in 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), pp. 1–6. IEEE, 2020.

The chronology of the papers follows Fig.1.3.

Fig. 1.3 Chronology of papers

#### 1.5. Scientific contributions

- The transient and dynamic behaviors, as well as the stability of three basic DC/DC converter systems feeding resistive load and multiple CPLs (cascaded systems) in DC MGs, are separately tested and analyzed under four performance scenarios as follows:

- I. Without and with applying proposed stabilization methods.

- II. Sudden variations in the input voltage amplitude.

- III. Unforeseen changes in load level (CPL power rating).

- IV. Step changes in voltage level of the output reference.

- Using a similar control structure with only various analytical concepts for the stability of these systems, which confirms the high compatibility and flexibility of the proposed stabilization methods.

- Three separate experimental setups have been built and used to show the feasibility of the proposed active stabilization approaches for these predominant structures in DC MGs.

- The effectiveness, robustness, and acceptable dynamic performance of the offered active stabilization schemes are validated under the above scenarios by simulation and experimental results.

- The superiorities of the proposed stabilization ideas compared with other stabilization methods, which are close to our work, are proven by a comprehensive performance comparison.

#### Chapter 1

# Chapter 2

# Stabilization of DC Microgrids

#### 2.1. Dynamic Characteristics of DC Microgrids

Commonly, using dynamics corresponding to time constants ranging in different time scales can identify stability issues in DC MGs. At longer scales, which sometimes vary from seconds to hours, the need to match the powers produced and consumed is a worrying factor in stability in these ranges [1],[2]. This means that from a static point of view, the power generated must match the energy consumed in the loads and sources, while dynamically, the response ramps of the power sources must be able to track load changes [1],[2]. In static and dynamic terms, these stability issues related to the matching of production and demand are still essentially similar to the stability concerns noticed in AC power systems and MGs. The usual method to solve these stability issues is to add energy storage [1],[13], which can behave as temporary sources by discharging and charging dependent on power demands.

As discussed, stability concerns related to mismatching of the power generation and consumption are accounted as common issues in AC and DC MGs [1],[9], and [11]. However, shorter time scale-based stability issues more commonly occur in DC MGs compared to AC power systems because these concerns arise in the presence of loads linked to the tightly-regulated power converters (Point-of-Load converters) acting as CPLs [1]-[3],[11]-[15]. Therefore, the framework of this work has been focused on the discussion of DC MGs stability in the presence of CPLs and introducing appropriate approaches to suppress the effect of instability injected into the system by these load types.

#### 2.2. Challenges of stability in DC Microgrids

The purpose of this section is to describe in detail the instability issue originated by CPLs for the cascaded configuration shown in Fig. 1.2, which introduces severe challenges to the DC MG [1]-[6],[9]-[13].

#### 2.2.1 Problem Definition

The essential challenge in the stability issue of multi-converter LVDC networks emerges when individually well-designed switching converters are tested on the grid. This is because connecting them to other circuits will no longer maintain the stability conditions of closed-loop converters designed as a freestanding device and may impose unforeseeable dynamic responses on the system [9],[12], and [15]. Also, these predominant structures in DC MG applications are commonly loaded with large active loads such as motor drives or electronic loads, which all these loads tend to be energized by POL converters [3],[16]. These loads act as instantaneous CPLs when tightlycontrolled by their respective converters, which have a rapid dynamic response with minimal output voltage ripple [9]-[12],[17], and [18]. In this case, when the bandwidth and control loop gain of the load side converter is adequately greater than that of the converter at the source side [9],[11], CPLs draw constant power from their upstream circuit, regardless of its terminal voltage [14]-[16]. CPLs introduce incremental negative resistance characteristic for their upstream circuit. It is worth noting that in the design of switching converter, the important aim of the designer is to obtain a high-efficiency system, i.e.,

$$P_o = P_{in} = V_{in}I_{in} \tag{2-1}$$

Where  $V_{in}$ ,  $I_{in}$ ,  $P_{in}$ , and  $P_{o}$  are the input voltage, input current, input power,

and output power of load converter, respectively. After adding the disturbances in (2-1) and considering the behavior of the load converter as CPL [16],[19],

$$P_{o} + \hat{p}_{o} = (V_{in} + \hat{v}_{in}) \cdot (I_{in} + \hat{i}_{in}) = Cons$$

(2-2)

Replacing (2-1) to (2-2) and neglecting the second-degree disturbance term,

$$\hat{Z}_{in} \triangleq \frac{\hat{V}_{in}}{\hat{i}_{in}} = -\frac{V_{in}^2}{P_o}.$$

(2-3)

According to (2-3), though the inherent negative resistance property of CPL ensures the fast-dynamic performance of the load converter, it will negatively affect the stability of the cascaded systems [2],[9],[19], and [20]. Hence, if the network is not supported with a suitable stabilization scheme over during the transient and any unwanted disturbance in the system, the voltage will go zero as the current goes to infinity, and vice versa [16],[17]. Finally, the system state variables will no longer return to equilibrium and the system will become unstable. Therefore, the major effects of CPL instability on cascaded systems in DC MGs can cause reduced system damping, limited cycle oscillation and voltage collapse on the bus voltage, degraded stability margins, and in the worst case, the whole system will shut down [1]-[4],[9]-[11]. Consequently, suppressing CPL instability in the structure illustrated in Fig. 1.2 is one of the vital concerns in obtaining a stable LVDC network. In addition, the accepted control approach must be robust enough to ensure the stability of the system against anticipated variations while simultaneously maintaining fast dynamic performance [9]-[16].

#### 2.3. Active Stabilization of a cascaded system with CPL

#### 2.3.1 Literature Review

In this part, a review of the literature presents on compensation for the destabilizing effects caused by CPLs in cascaded systems in DC MGs. In this way, several methods have been accomplished to mitigate CPL instability in cascading systems in accordance with the different stability criteria, [4]-[19], and [32]. The main concept behind these approaches is the effective improvement of the system damping rate by some modifications that can be commonly categorized into three zones of system-level compensation, namely source-level, load-level or the use of additional circuits at the intermediate level [9], [11], [24]-[26], and [31]-[42]. To fulfill this purpose, various solutions have been performed, which are based on passive (hardware) [33]-[35], and active (software) damping methods [9],[11],[16],[19],[24]-[26],[31]-[32], and [36]-[42]. Passive damping methods are easily realized by passive components to the network. However, system performance and efficiency under these approaches inevitably deteriorates due to the increased size, cost, weight, power dissipation, and decreasing the system bandwidth [2],[9],[16]. In contrast, active damping (AD) techniques with having a high flexibility and efficiency present adequate damping rate for the system control strategy through dynamic modifications [9],[16]. The control concept for these methods is based on satisfying the stability criteria for cascaded systems with emphasis on the modification of  $Z_{in}$  (input impedance of the load-side circuit) or/and  $Z_o$  (output impedance of the source-side circuit). It should be noted that when the upstream circuit of the CPL is uncontrollable, the AD control solutions at the load-side and intermediate levels are considered as executable options. In load-side compensators, to mitigate CPL effects,  $Z_{in}$  is modified by injecting a current or power stabilizing signal into the load converter control loops [16]. However, the CPL control loop will be adversely affected by the dynamics of the AD stabilization strategy and as a result, it cannot maintain its

desirable and fast performance [2],[9]. In intermediate-side AD compensators implemented by an additional active damper between the source and load subsystems, stabilization is realized through effective shaping of  $Z_{in}$  or/and  $Z_o$  [9],[16]. Although these approaches maintain the network modularity feature, they can impose negative effects on the system, such as increased costs, system complexity, and energy loss [2],[9],[21]. The source-side AD methods dynamically modify  $Z_o$  either by adding an ancillary effective damping loop to the source converter [9],[11], [19],[31],[32],[36], and [38] or by increasing the control loop bandwidth of it [24]. Therefore, in these approaches, since overcoming CPL destabilization effect in the cascaded systems is achieved by modifying the control structure of the converter of source-side, the favorable dynamic performance of the load converter will not be jeopardized [2],[9], and [36]. Accordingly, the source-side-based active stabilizers are usually more preferred by researchers and designers over the AD stabilization approaches at the load side [9],[11]. In [31], a source-side AD control scheme is proposed for cascaded systems with CPL in DC MGs, where the system stability condition is satisfied by enhancing damping rate via the virtual insertion of a resistance in series with the inductor corresponding to the source converter [31]. However, due to the inherent shortcomings of the presented idea in [31], including the limited stable band to increase the damping rate and the restriction in the value of the virtual maximum resistance [9], dynamic and transient performance under different performance conditions cannot be appropriately guaranteed. In general, many of the impedance-based active stabilization strategies that have been proposed to date have complex control structures with different levels of conservatism in the design and realization of the stability criteria [9],[16]. In addition, their

effectiveness and dynamic performance against unforeseen changes in the cascaded system has not been evaluated holistically [9],[11], and [31].

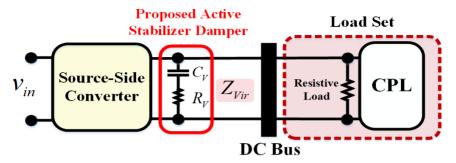

Motivated by these issues, this work proposes novel design-oriented source-side active stabilization schemes for stabilizing cascaded systems with CPLs in DC MGs without negative impact on the favorable performance of the load converter. These AD control strategy-based stabilizer techniques utilize simple control structures with straightforward control parameter tuning to achieve a reliable and robust stable level. The flexibility, and applicability, of these control schemes will be well-demonstrated by applying to three cascade systems consisting of basic DC/DC converters (Buck, Boost, and Buck-Boost) supplying multiple CPLs and resistive loads. Effectiveness and robustness of the active stabilizer approaches will be confirmed by simulation and experimental results.

# Chapter 3

# Source-Side Virtual *RC* Damper-Based Active Stabilization Strategy

Based on JP1, this chapter proposes new source-side active stabilization scheme for DC cascaded systems in DC MGs

This chapter presents a new stabilization approach based on source-side AD control scheme to overcome the CPL instability effects for DC cascaded systems in DC MGs, which has been published in [9].

#### 3.1. Methodology

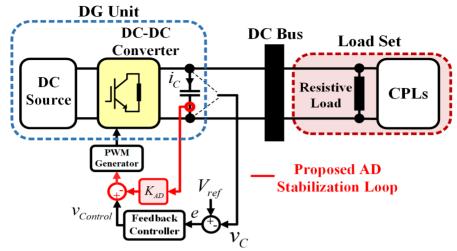

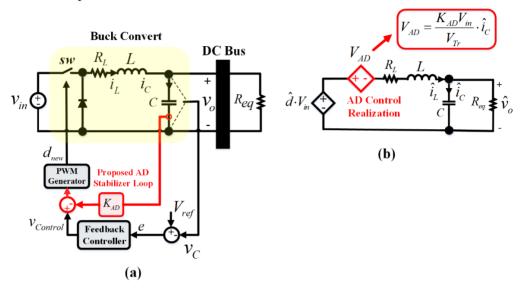

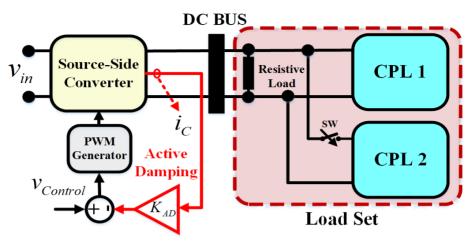

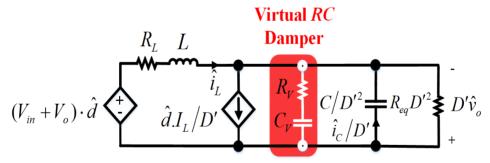

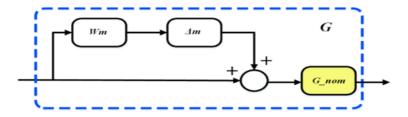

As discussed in the previous chapter, compensating the active load instabilities (CPLs) in the configuration illustrated in Fig. 1.2 is one of the key subjects in obtaining a stable DC MG and also a desired voltage on the DC bus. Therefore, this chapter presents a novel virtual series *RC* damper that is placed in the output of the source-side subsystem without affecting the favorable performance of the load converter. The presented active stabilization strategy is achieved by feeding back the capacitor current source converter via a precise and well-designed proportional term [9]. Using this design-oriented AD technique that uses a easy control mechanism with simple control parameter setting (see Fig. 3.1), stability and dynamic performance of the system are ensured in a rigorous deterministic way [9]. In the following, the main advantages and new contributions of the proposed active stabilization method are presented, which completely covers the deficiencies of the existing techniques and shows outstanding performance in comparison with them.

Fig. 3.1. The proposed control strategy based on virtual *RC* damper applied to the cascaded systems with multiple CPLs and resistive load in DC MG.

### 3.1.1 Advantages and Main Contributions

1) Easy control mechanism with simplicity in control parameter adjustment [9]

Using these competencies, it is easy to explore the possibility of generalizing this control approach for more complicated DC MGs at source level.

### 2) Operational ability with high flexibility and compatibility [9]

This privileged feature is since the proposed active stabilization technique with a same control scheme and only with different analytical concepts is well-applicable in the three main cascaded systems with multiple CPLs in the DC MGs [9].

3) Without any adverse effects on the desirable dynamic performance of the load-side converter [9]

Verification of the effectiveness of a control technique in overcoming exclusively unfavorable effects without adversely affecting other optimal system conditions is an important and vital factor. Since the proposed stabilizer

control strategy is created by modifying the source converter's voltage control signal, the CPL destabilizing effects are omitted without adverse effect on the dynamic performance of the load converter [9].

4) High robustness versus unanticipated changes in the system (changes in input Voltage level, load changes (power rating in CPLs), and step change in reference voltage) [9]

The presented AD control approach without the need for new information from the network shows high robustness with admissible transient and fast dynamic responses to possible unforeseeable changes in the system [9].

# 3.2. Proposed Virtual *RC* Damper-Based Active Stabilizer Method for Cascaded Systems in DC MGs

In this part, given the system dynamics, the stability issue of the cascaded systems comprising the DC/DC converters supplying multiple CPLs and resistive loads is individually analyzed [9]. Besides, the principles of control idea and its operation as well as the circuit physical concept created by the suggested stabilizer scheme for these systems in DC MGs, have been theoretically analyzed. Effectiveness, and robustness of this technique are validated by simulation and experimental results [9]. It is worth mentioning that all DC/DC converters supplying CPLs that are operating in continuous conjunction mode (CCM) have unstable performance under both voltage mode control (VMC) and current mode control (CMC) [2],[9]. Therefore, owing to the simplicity in design and execution as well as the assessment of the presented active stabilizer strategy in the worst operating conditions from the point of view of stability, the performance of the source side converters is considered in CCM and under VMC [9]. However, the proposed method can also be well-accomplished for these systems in CMC.

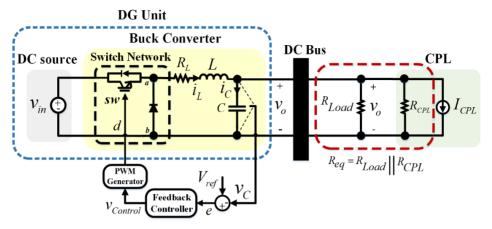

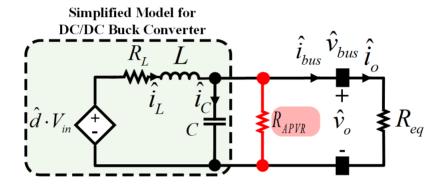

Fig. 3.2. A DC/DC buck converter feeding CPL and resistive load in cascaded form [9].

### 3.2.1 DC/DC Buck Converter feeding Resistive Load and CPLs

### 3.2.1.1 Modeling and Stability Analysis

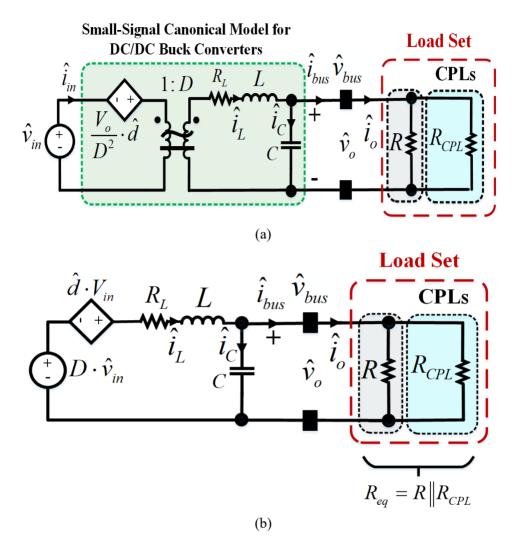

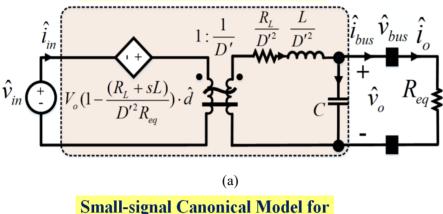

Fig. 3.2 illustrates a DC/DC buck converter system loaded by CPLs and resistive load. In this configuration, CPL has been modeled by its small-signal circuit consisting of a negative resistance ( $R_{CPL}$ =- $V^2/P$ ) in parallel with an independent current source ( $I_{CPL}$ =2P/V), where V and P are terminal voltage and power of the CPL for a certain operating point, respectively [9]. Though  $I_{CPL}$  does not impact on the system stability,  $R_{CPL}$  reduces system damping and tries to impose instability on the system [9]. L and C are the inductor and capacitor of the source-side converter,  $R_L$  is the inductor's inherent resistance,  $V_{in}$  is the input voltage,  $R_{eq}$  is the small-signal equivalent load resistance. To extract the linearized circuit averaged model of the cascaded system shown in Fig. 3.2, the averaged switch modeling technique is applied into the system with subintervals during each switching period [9]. The process of

implementing the averaged switch modeling method is summarized in the following steps.

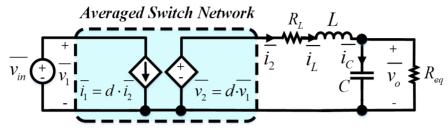

Fig. 3.3. The averaged time-invariant network of Fig. 3.2 (Step 1) [9].

Fig. 3.4 Simplified averaged model of. 3.2 (Step 2) [9].

**Step 1.** The switch network shown in Fig. 3.2 can be modeled a as two-port network with four variables, called,  $v_1$ ,  $i_1$ ,  $v_2$ , and  $i_2$  [9],[43]. Two of these variables can be random candidate as independent inputs  $(v_1, i_2)$  and the remaining two quantities are then considered as dependent outputs  $(i_1, v_2)$

[43],[9]. The only action necessary at this stage is to calculate the average values of the dependent sources, where they are represented by  $\overline{x}$ .

Step 2. First, in this section, suppose that the parameters of the averaged system model are equal to the corresponding dc values, X, plus small ac variations,  $\tilde{x}$ . As specified in Fig. 3.4, by replacing these perturbed signals in the model demonstrated in Fig. 3.3, and disregarding the second-order terms derived from the multiplication of ac values, the small-signal averaged model is achieved [9].

Consequently, the small-signal control-to-output transfer function and its related poles can be readily derived as (1) and (2), respectively.

$$\frac{\hat{v}_o}{\hat{d}} = \frac{V_{in}}{LC \cdot s^2 + (R_L C + \frac{L}{R_{eq}}) \cdot s + (1 + \frac{R_L}{R_{eq}})}$$

(3-1)

$$P_{1}, P_{2} = \frac{-\left(\frac{L}{R_{eq}} + R_{L}C\right) \pm \sqrt{\left(\frac{L}{R_{eq}} + R_{L}C\right)^{2} - 4LC\left(1 + \frac{R_{L}}{R_{eq}}\right)}}{2LC}.$$

(3-2)

Since  $R_{eq}\langle 0 \text{ and } | R_{eq} | \rangle R_L$  (real condition), due to the presence of a complex conjugate pole pair in the right half-plane (RHP), the system operation will be in an unstable position [9]. Hence, by applying Routh's stability criterion for (1), the stability condition for the system is satisfied through the realization of the following inequality [9].

Fig. 3.5. control realization of the presented AD control scheme [9].

$$R_L C \rangle \frac{L}{\left|R_{eq}\right|}$$

(3-3)

Evidently,  $R_{eq}$  cannot be changed flexibly for specific CPL and restrictions on the  $R_{Load}$  control [9]. Therefore, it can be concluded that to satisfy (3), one of the LC filter parameters should be adjusted properly, that is, either increasing  $R_L$  or C, and or decreasing L. Generally, L is usually chosen to meet other design requirements, like CCM, and the favorable inductive current ripple magnitude [43]. Hence, as is clear from (3), this case does not match the stability condition mentioned for the inductor value. Also, actively increasing  $R_L$  cannot be a proper solution to overcome CPL instability effects under different loading cases [9],[31]. As a result, in this case, the only parameter that can be freely adjusted is C. However, increasing C alone guarantees the stability performance of the system in exchange for slowing down the dynamic response. Consequently, as shown in Fig. 3.5, to ensure stability of the system, improved dynamic performance and enhanced damping, the virtual insertion of a series RC damper into the source's converter output would be a great choice [9].

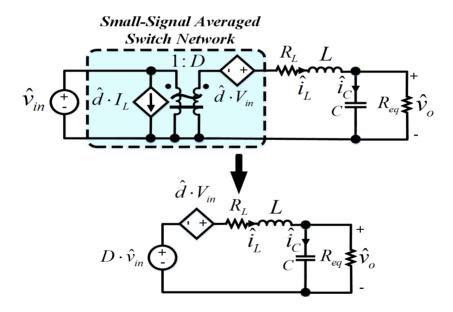

#### 3.2.1.2 Control Realization

### a) Circuit Physical Meaning

This section describes in detail how to influence and design the suggested AD-based stabilizer scheme for stabilizing buck converter system supplying multiple CPLs in DC MGs.

Fig. 3.6. The proposed AD control strategy for the buck converter feeding CPLs and resistive load. (a) Circuit model. (b) Modified small-signal averaged circuit [9].

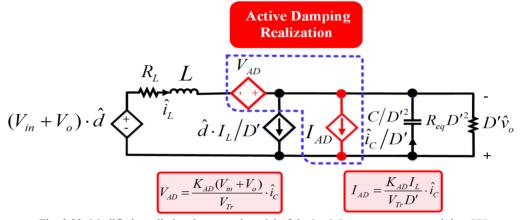

In this regard, Fig. 3.5(a) illustrates the circuit schematic of the cascaded system shown in Fig. 3.2 considering the suggested AD control strategy. As seen, this active stabilizer approach is realized by the proportional feedback of the source converter capacitor current and subtracting it from the voltage control signal [9]. Thus, by substituting  $\hat{d}_{new} = \hat{d} - (\frac{K_{AD} \cdot \hat{i}_C}{V_{Tr}})$  in lieu of  $\hat{d}$  in

Fig. 3.4, the simplified small-signal average model is modified by neglecting the ac term of input voltage source (see Fig. 3.5(b)). It is well understood that the presented AD technique behaves as a dependent voltage source for suppressing CPL's instability effect by dynamically modifying the converter

Fig. 3.7. Another analytical commentary of Fig. 3.5(b).

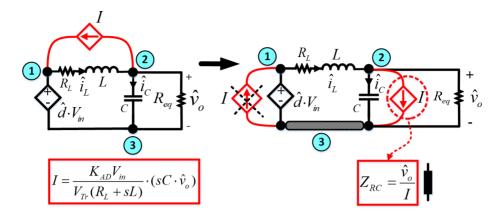

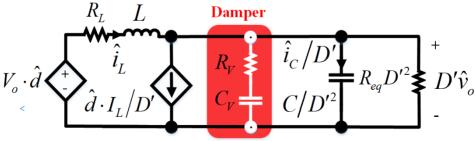

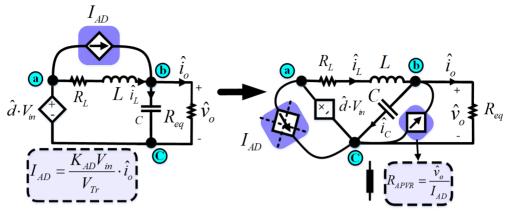

CPL's instability effect by dynamically modifying the converter output voltage. As can be seen from Fig. 3.5 (b), the proposed AD control scheme presents an interesting concept of a physical circuit, the result of which is shown graphically in Fig. 3.6. This outcome is achieved based on the circuit analysis, the process which is summarized step-by-step as bellow [9]:

- 1) Conversion of the Thevenin circuit including the voltage source  $V_{AD}$  and the impedance  $R_L L$  to the related Norton equivalent circuit.

- 2) Deleting the dependent current source, I, between nodes 1 and 2 and transferring it from node 2 toward node 3 and finally to node 1.

At this point, the dependent current source parallel to the voltage source can be neglected [9].

- 3) Conversion of the dependent current source to an impedance.

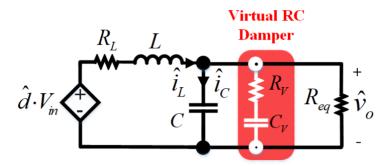

According to one of the efficient rules used in circuit analysis, which states: "Each dependent current source that depends on its voltage can be modeled as an impedance", the proposed active stabilization technique injects a virtual series RC damper in parallel to the converter output (see Fig. 3.7) [9].

Fig. 3.8. The circuit physical meaning of the suggested AD control strategy for to the buck converter feeding multiple CPLs and resistive load.

In this way,  $R_V$  and  $C_V$  can be readily achieved as [9]

$$\frac{\hat{v}_o}{I} = \frac{LV_{Tr}}{K_{AD}CV_{in}} + \frac{1}{s} \left( \frac{R_L V_{Tr}}{K_{AD}CV_{in}} \right) = R_V + \frac{1}{sC_V}$$

(3-4)

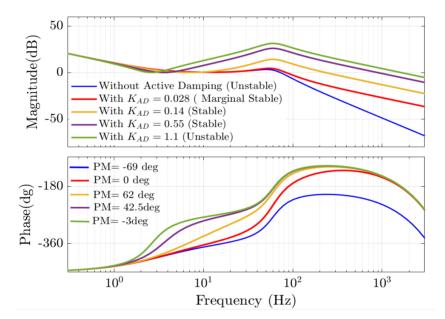

### b) Choosing an Effective AD Term ( $K_{AD}$ )

As obvious from (4), since the effect of resistance term ( $R_V$ ) is more negligible than capacitance term ( $C_V$ ) at around DC frequency, the system's equivalent capacitance can be regarded with an acceptable approximation as  $C + C_V$  [9]. In this regard, as discussed in the previous section, by increasing the equivalent capacitor of source-side output, i.e., (Increasing  $C_V$ ), the damping rate can be significantly improved to stabilize the system. It is important to note that in order to avoid slowing down the response of the system owing to increased capacitance alone, the existence of the term resistance in the damper branch is vital. Considering (3) and the stability analysis discussed, the minimum required capacitor to compensate instability effects induced by CPL is obtained as [9]

$$C_{\min} = \frac{L}{R_L \left| R_{eq} \right|}.$$

(3-5)

Therefore, the damping gain (  $K_{AD}$  ) must be chosen effectively so that  $C_V$  is much larger than  $C_{V, \min}$ , i.e. [9];

$$C_{V \text{ off}} \gg C_{V \text{ min}} = (C_{\text{min}} - C) \tag{3-6}$$

Whereby, given the importance of choosing a suitable and optimal  $K_{AD}$  for offsetting the CPL instability, the design process algorithm is outlined below;

**Step 1)** Computing the  $C_{min}$  [9].

Given the value of  $|R_{eq}|$  at the desired output voltage, the  $C_{\min}$  required to meet the system stabilization conditions is calculated by (3-5) [9].

### **Step 2)** Computing the $C_{V,\min}$ .

In this step, minimum value of admissible virtual capacitor,  $C_{V, \min}$  , is achieved by  $C_{\min} - C$  .

**Step 3)** Computing the  $K_{AD, min}$ .

With obtaining of  $K_{AD, \min}$  by (3-7), a virtual series RC damper ( $C_{V, \min}$  and  $R_{V, \max}$ ) can be realized [9].

$$K_{AD,\min} = \frac{C_{V,\min} R_L V_{Tr}}{CV_{in}}.$$

(3-7)

**Step 4)** Choosing an effective  $K_{AD}(K_{AD,eff})$ .

To reach a robust level of the system with an acceptable damping rate and desirable dynamic performance along with a safe phase margin, an effective choice for the AD controller gain must be accomplished by the designer. This represents high flexibility in choosing  $K_{AD}$  an allowable stable band complies with design requirements [9].

It must be acknowledged that since  $K_{AD}$  has a reverse dependence on  $V_{in}$  and  $\left|R_{eq}\right|$ , it shall be set much larger than  $K_{AD, \min}$  to attain high robustness against descending changes of those agents. This indicates that only in the initial  $K_{AD}$  adjustment requires to know  $V_{in}$  and the equivalent load set. As a result, with unforeseen changes in these factors, stability can be well guaranteed only by designing the  $K_{AD,eff}$  without knowing their new values[9].

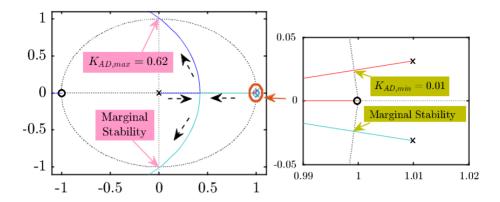

It should be noted that the digital implementation of the proposed active stabilizer loop is an important subject that must be considered. Indeed, in practice, the factors influencing digitally-controlled systems include pulse width modulation (PWM) and computational delays [9],[16],[44]. Given that the synchronous sampling approach is commonly applied to the digitally-controlled systems, one sampling period  $T_s$  for computation delay effect and half of the sampling period for PWM delay caused by the zero-order-hold (*ZOH*) effect are considered. These delays are accomplished in the control loop of the digitally-controlled converter at the output related to the difference between the presented AD loop and the digital PI controller's output via the cascaded connection of  $Z^{-1}$  and *ZOH* blocks [9]. This phase lag effect owing to delay factors yield a decrease in the phase margin in the high-frequency range. Therefore, in the low-frequency range and the small value of  $T_s$ , the

virtual RC damper-based control scheme will not be affected by the delays effect, and can only limit the upper band of  $K_{AD}$ .

Table 3.1. The Parameters of the Cascaded Systems with CPL and resistive load [9].

| Source-Side Converter | L                 | C                   | $R_L$                | $R_{Load}$   | $P_{CPL}$ | $V_{in}$ | $V_o$ | D    |

|-----------------------|-------------------|---------------------|----------------------|--------------|-----------|----------|-------|------|

| Buck                  | 20 mH             | $350~\mu\mathrm{F}$ | $45~\text{m}\Omega$  | $470~\Omega$ | 2250 W    | 200 V    | 150 V | 0.75 |

| Boost                 | $2.4~\mathrm{mH}$ | $750~\mu\mathrm{F}$ | $5~\text{m}\Omega$   | 200 $\Omega$ | 2250 W    | 100 V    | 150 V | 0.33 |

| Buck-Boost            | 2.4 mH            | $750~\mu\mathrm{F}$ | $5~\mathrm{m}\Omega$ | 200 $\Omega$ | 1800 W    | 120 V    | 150 V | 0.55 |

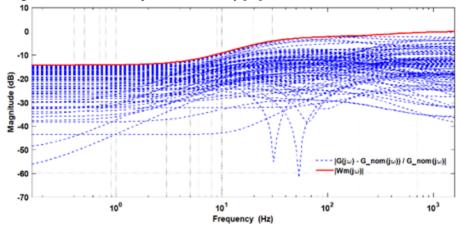

Fig. 3.9. Bode analysis of the open-loop gain of  $\hat{v}_o/\hat{d}$  related to the buck converter supplying CPL. Red line:  $C_{V, \min} = 43.2 mF$ ,  $R_{V, \max} = 10.2 \Omega$ ; Yellow line:  $C_V = 5 C_{V, \min}$ ,  $R_V = 0.2 R_{V, \max}$  Purple line:  $C_V = 20 C_{V, \min}$ ,  $R_V = 0.05 R_{V, \max}$  [9].

Bode analysis of the open-loop gain corresponding to the control-to output of Fig. 3.6(a) is plotted in Fig. 3.8 given the relevant delays and the parameters given in Table I. As seen from Fig.3.8,

$$\measuredangle \left[ e^{-jT_{Sw}}G(s) \right] = -\pi \tag{3-8}$$

$$\left| e^{-jT_{Sw}}G(s) \right| = 1 \tag{3-9}$$

where

$$\bullet G(s) = \frac{\hat{v}_o}{\hat{d}}(s) \Big| open - loop = e^{-jT_{sw}} \cdot \big[ Eq.(1) \big] \cdot \big( G_{AD}(s) + G_{PI}(s) \big),$$

$$\bullet G_{AD}(s) = s \cdot K_{AD, \max} \cdot C : (AD \text{ Controller})$$

•

$$G_{PI}(s) = K_P + \frac{K_I}{s}$$

: (PI Controller)

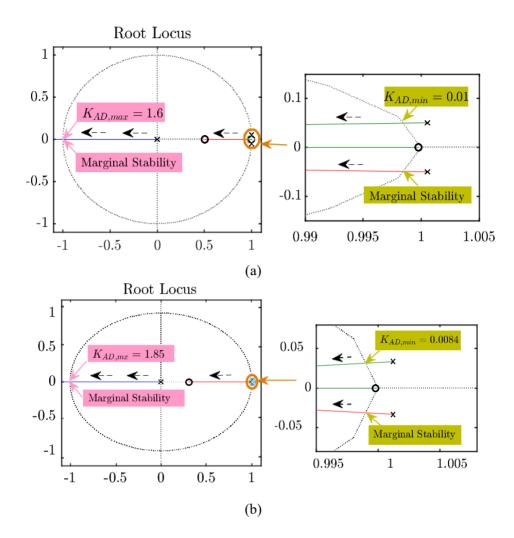

the system reaches marginal stability status for the minimum amount of AD gain (  $K_{\rm AD,min}$  ) [9]. As the  $K_{\rm AD}$  increases, the damping rate enhances, which indicates an improvement in the system phase margin. Thereby, the stability of the closed-loop control system is also guaranteed. However, due to the effect of considered delays in the digital control system, increasing the  $K_{\scriptscriptstyle AD}$ from a certain value leads to gradually decreasing the phase margin, and ultimately, the system approaches instability. Therefore, the allowable stable band can be defined for  $K_{AD}$  as  $\left[K_{AD, \min}, K_{AD, \max}\right]$ . The value of the lower band was obtained by (7) and upper band that defined as the maximum amount of the allowable damping gain can be easily derived by solving (8) and (9). Then,  $K_{\rm AD,max} \cong 0.98$  is attained through substituting the parameters of Table. 3.1 in the expressed equations and fulfilling them simultaneously. Consequently, the permissible stable band is specified as [0.028,0.98], which well confirmed the results achieved from Fig. 3.8. In general, it should be mentioned that the aim of an efficient design is to reach a robust system with effective damping rate and desirable dynamic performance, as well as a safe phase margin. Therefore, in this regard, effective selection of  $K_{AD}$  in

order to meet the targets of an efficient design will be very important. This in turn indicates the high flexibility of the proposed stabilization scheme in selecting an admissible damping gain rate that can vary from the designer's point of view depending on the design requirement [9]. However, by choosing efficient  $K_{\rm AD}$  (  $K_{\rm AD,eff}$  ) that is certainly much higher than  $K_{\rm AD,min}$  , in addition to desired dynamic and transient performance, the robust stability of the system against abrupt changes in voltage input and load level will also be wellguaranteed [9]. It should be noted that considering the relationship between capacitor voltage and current, it seems that the AD control feedback of the proposed stabilization approach can also be realized using the output voltagederived feedback with the adjusted gain  $\mathit{CK}_{\mathit{AD}}$ . With this frame of mind, first, we will encounter a PID controller with a design-oriented derivative part, not a standard PID controller. Second, the capacitor current feedback-based control scheme, which utilizes information about the load current and dynamics related to the source converter inductor current, has a different dynamic and functional nature than the output voltage of the source converter derivative term. Third, the derivative term related to output voltage for the PID controller introduces a considerable noise into the closed-loop system of power converters compared with other AD approaches that use information of the capacitor current. This adverse impact is mainly arising from the parasitic resistance and inductance of the source converter's output capacitor, which are determined as the equivalent series resistance (ESR) and equivalent series inductance (ESL), respectively [9],[43], and [45]. Moreover, it can have harmful effects on the network by generating impulse responses along with large overshoots/undershoots, and discrete jumps at switching transitions during small and large signal transients or even at steady-state [9],[45], and [46]. These adverse reactions significantly reduce phase margin and ultimately

Fig. 3.10. DC MG topology intended for simulation and laboratory tests [9].

compromise the system stability [9], [47], and [48]. Although by decreasing the cut-off frequency of the low-pass filter corresponding to the derivative term, noise and phase margin can be enhanced, it causes jeopardizing of the closed-loop control bandwidth performance and also slowing down the system's dynamic responses. Accordingly, under this approach, there will always be a trade-off between the filter bandwidth and the damping performance of a closed-loop system [9]. Given these interpretations, it can be seen that by further reduction of the filter bandwidth, the stable band of  $K_{AD}$  is severely limited and as a consequence, the advantages of the derivative part cannot be fully utilized. Eventually, it can be concluded that for robust stabilization of cascaded systems loaded by multiple CPLs, the presented capacitor current-based AD control scheme has a reliable and acceptable performance in various operating conditions with minimal recovery time and slight output voltage deviation for different transient times compared with PI + designed D control approach [9].

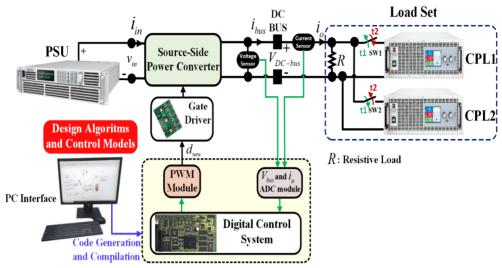

### 3.2.1.3 Simulation and Experimental Results

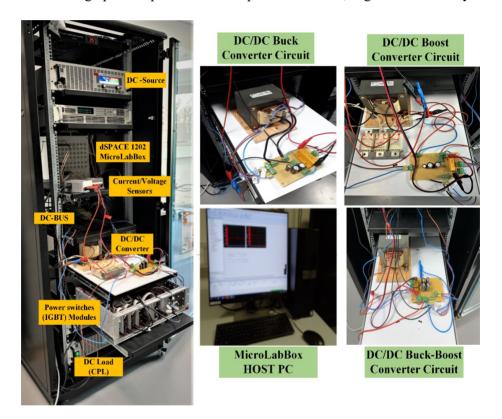

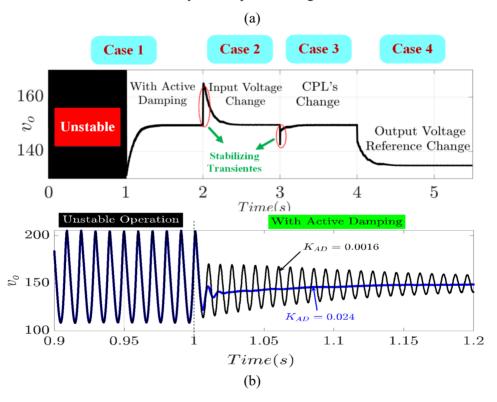

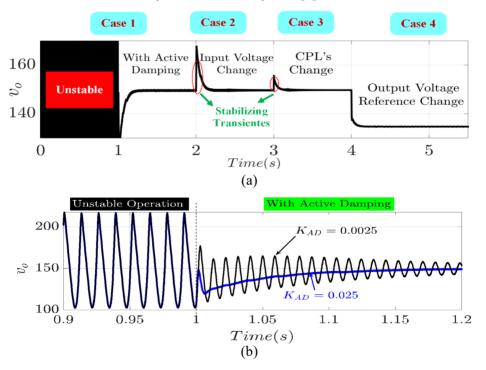

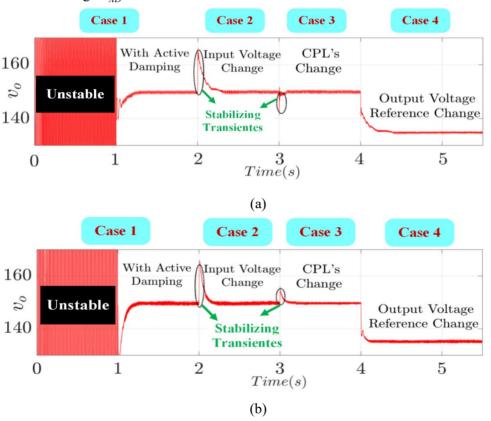

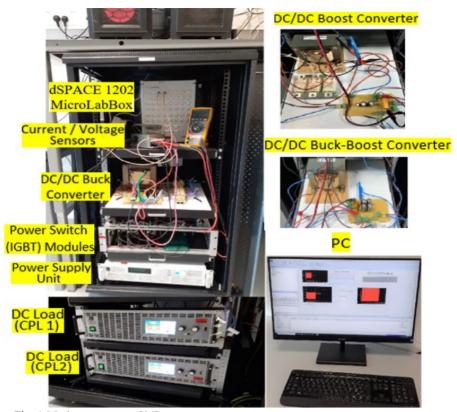

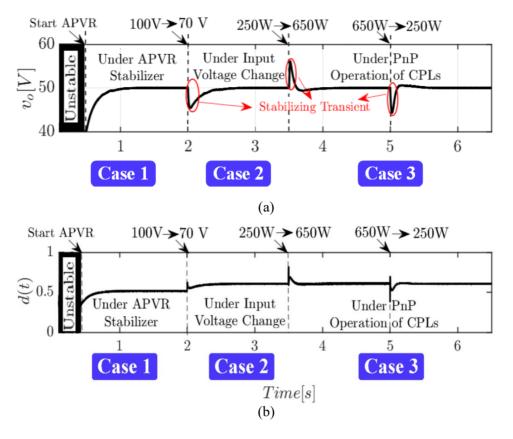

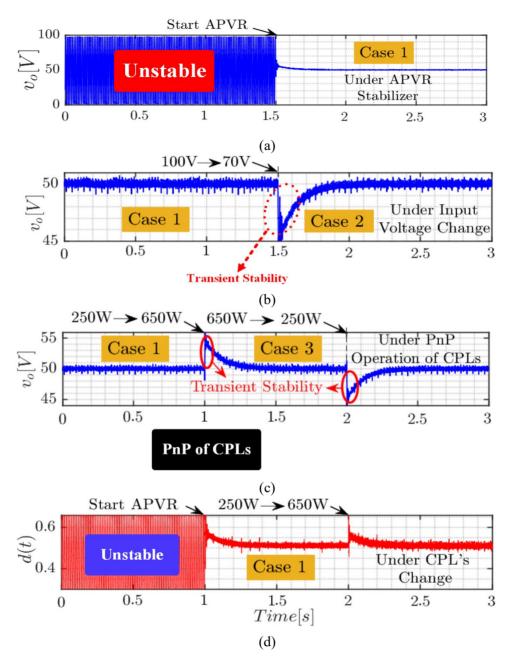

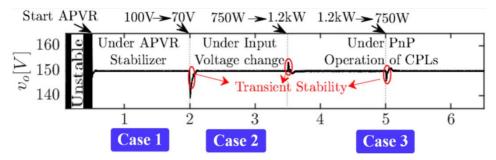

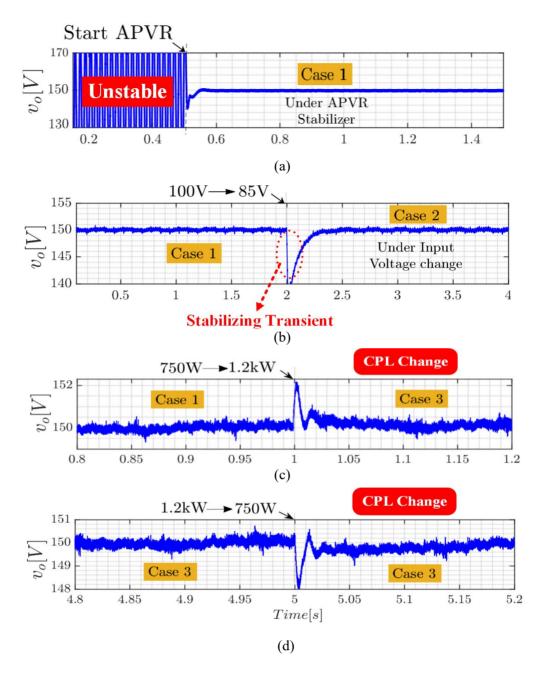

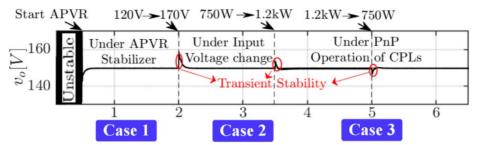

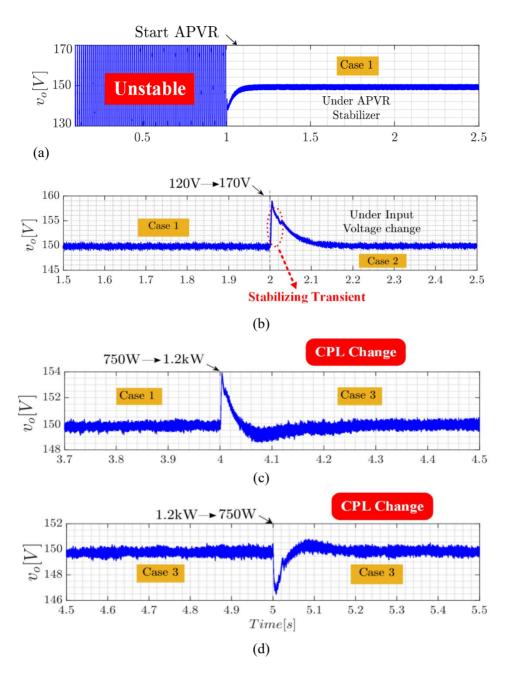

To verify the validity and effectiveness of the presented control strategy, a simulation was accomplished on a generic DC MG demonstrated in Fig. 3.9 using MATLAB/Simulink in the discrete-time domain with the parameters mentioned in Table I [9]. Meantime, in order to be more in line with the real conditions and to show the feasibility of the proposed AD stabilization method, digital control system delays consisting of the PWM and computational delays are also considered in the simulated model [9]. Besides, as shown in Fig. 3.11, to corroborate the applicability of the presented stabilization method in practice, the hardware configurations of the cascaded systems comprising the three DC/DC converters feeding CPLs (see Fig. 3.10) have also been separately fabricated and tested. In this laboratory setup, the control part is implemented by real hardware controller-SPACE 1202, whose sampling rate is 10 kHz. The switching frequency has been selected equal to the sampling rate of the control part [9]. Also, a low-pass filter with a cut-off frequency of about 50 kHz between the analog-to-digital converter and the current sensor has been implemented to compensate for the distortion effect caused by switching noises in capacitor's current sampling [9], [49]. It is worth noting that this cut-off frequency would be proper given that the switching noise frequency is usually higher than 1 MHz [9],[50]. The system parameters for the experimental test were intended similarly to the simulation implementation. The following three operational cases have been studied under both simulation and experimental tests.

*Case 1:* Evaluating the system performance without and with the offered AD stabilizer technique.

Case 2: Evaluating transient stability and dynamic performance of the system under variations in input voltage amplitude.

Case 3: Evaluating transient stability and dynamic performance of the system under CPL changes (power rating).

Before analyzing the achieved results, how to effectively choose  $K_{AD}$  based on the design process presented in the previous section, is given numerically.

Fig. 3.11. The laboratory platform.

Negative equivalent load resistance of the cascaded system based on a certain desired output voltage of the source converter is obtained as [9]:

$$R_{eq} = R_{CPL} \left\| R_{Load} = -\frac{150^2}{2250} \right\| 470 = -10.2\Omega \cdot$$

(3-10)

Then, for satisfying the system stability, minimum required virtual capacitor is derived as [9]

$$C_{V,\text{min}} = \frac{L}{R_L |R_{eq}|} - C = 43.2 mF.$$

(3-11)

Therefore, in accordance with (3-7), the  $K_{AD, min}$  can be easily obtained as [9]

$$K_{AD,\min} = \frac{C_{V,\min} R_L V_{Tr}}{C V_{in}} = 28 \times 10^{-3} \Omega.$$

(3-12)

As previously described in detail, for having an efficient damping rate with admissible phase margin (see Fig.3.9) and high robustness versus unexpected variations in load level and input voltage, as well as preventing slowing down the system's dynamic response,  $K_{AD,eff}=0.55$  ( $R_V=519.5m\Omega$ ,  $C_V=855.5mF$ ) that is almost 20 times larger than  $K_{AD,min}$  has been selected [9]. Therefore, in accordance with (7), the  $K_{AD,min}$  can be easily achieved as

$$K_{AD,\min} = \frac{C_{V,\min} R_L V_{Tr}}{C V_{in}} = 28 \times 10^{-3} \Omega.$$

(3-13)

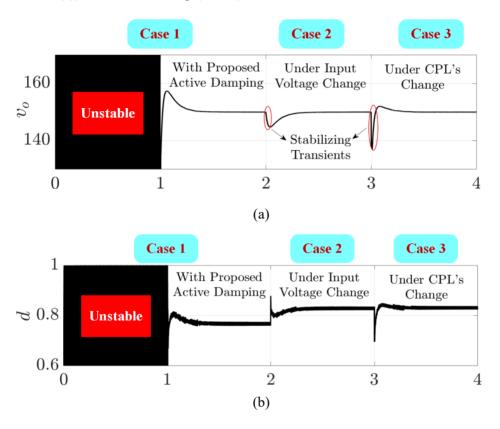

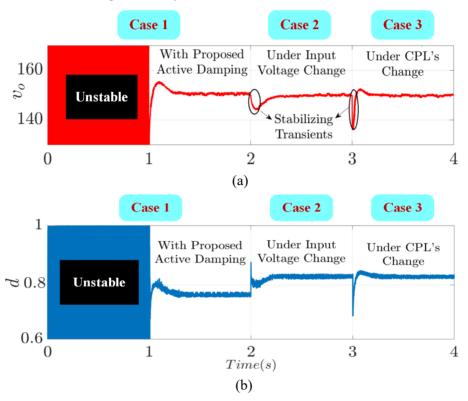

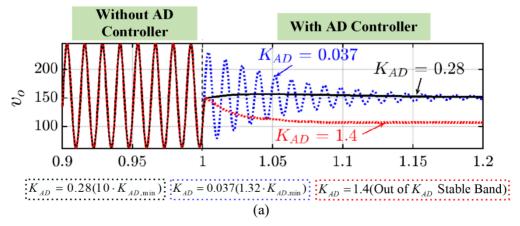

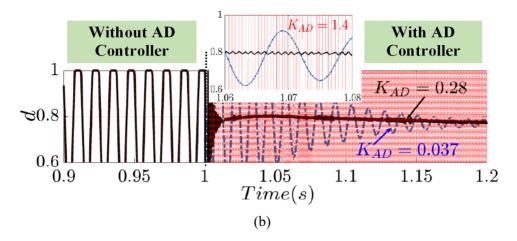

In Case 1, as can be seen from Figs. 3.12(a) and 3.13(a), when the proposed active stabilizer strategy is turned off  $(0 \le t \le 1s)$ , severe unstable fluctuations arise on the DC bus voltage of the cascaded system owing to the CPLs [9]. Once the AD controller is turned on, unstable oscillations in DC bus voltage are quickly damped, and the system becomes stable. Due to the desired duty cycle depicted in Figs. 3.12(b) and 3.13(b), stability and effective damping performance of the system by employing the presented control scheme can also be well-authenticated [9]. Hence, in first step, 12.5%

reduction in the amplitude of the input voltage is applied in case 2 (see Fig. 3.12(a)). In the second step (case 3), CPL 750W has been connected to the

Fig. 3.12. Simulation results of the buck converter systems supplying CPLs under three operation cases. (a) Output voltage. (b) Switch duty cycle [9].

system in parallel with the existing CPL 2250W at t=3s. As can be understood from the results, after these sudden changes, without making unstable fluctuations, the DC bus voltage with stable transitions and fast dynamic responses reaches the desired value (output voltage reference) [9]. According to the three operational cases, acceptable results have also been obtained for the switch duty cycle (see Figs. 3.12(b) and 3.13(b)) [9]. Evidently, the results

demonstrate the robustness of the proposed active stabilizer strategy against unforeseen changes in the system.

Fig. 3.13. Experimental results of the buck converter feeding CPLs (three operation cases). (a) Output voltage. (b) Switch duty cycle [9].

Fig. 3.14. Buck converter systems loaded with CPLs and resistive loads. (a) The dynamic performance for different  $K_{AD}$ . (b) Switch duty cycle variations for different  $K_{AD}$  [9].

As seen in Fig. 3.14(a), by increasing  $K_{AD}$  in the permissible stable band  $(K_{AD}=10\cdot K_{AD,\rm min}=0.28)$ , unstable fluctuations in DC bus voltage are rapidly damped compared to  $K_{AD}=0.037$   $(1.32\cdot K_{AD,\rm min})$  [9]. However, with a further increase in  $K_{AD}$  and over its allowable stable range, e.g.,  $K_{AD}=1.4$ , the performance of the presented stabilization approach will no longer appropriately follow the output voltage reference and lead to system instability, of which these results are also well confirmed. in Fig.3.9. These outcomes can also be approved by Fig.3.14(b) which shows the switch duty cycle variations under the different  $K_{AD}$  [9]. Eventually, it can be concluded that the CPL instability effect can be effectively compensated using the proposed active stabilizer scheme, provided that  $K_{AD}$  meets the stability condition by virtually introducing an appropriate series RC damper that is placed in parallel with the capacitor of the source converter [9].

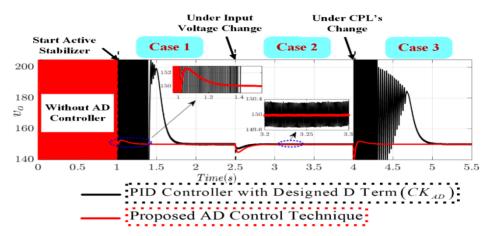

### 3.2.1.4 Comparative Study with the PI + Designed D Control

Fig. 3.15. Comparative experimental results between the proposed method and the PI + designed D (CKAD) controller with a similar damping gain rate (KAD = 0:55) for the buck converter powering CPLs [9].

As illustrated in Fig.3.15, to exhibit and accredit the superiority of the proposed active stabilization method over the PI + designed D control approach, their dynamic performance and transient stability has been experimentally compared for a similar damping gain for three operational cases [9]. In Table 3.2, the comparative results on the performance of both control strategies are also outlined. Reference voltage tracking, transient recovery time, and dynamic performance for the buck converter systems loaded with CPLs under changes in input voltage and load level (CPL power rating) have been comprehensively evaluated. The rate of change at the system level for this comparison is similar to the conditions analyzed in the previous section [9]. As is well understood in Figure 3.15 and Table 3.2, using the AD control strategy presented at t = 1s, the sharp unstable fluctuations of the bus voltage are rapidly damped. In addition, under this stabilization method, the achievement of an optimal dynamic response with a minimum transient recovery time is also achieved. On the other hand, the stabilization approach

Table 3.2. A Performance Comparison Between the Proposed Active Stabilizer Scheme and PI+Designed D Control Technique Under the Same Damping  $(K_{4D} = 0.55)$  for the Buck Converter Feeding CPLs [9].

| Proposed AD Control Strategy  Evaluation of Transient and Dynamic Performance |              |           |           |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|--------------|-----------|-----------|--|--|--|--|--|--|--|

|                                                                               |              |           |           |  |  |  |  |  |  |  |

| Dynamic Response Time                                                         | Very Fast    | Very Fast | Very Fast |  |  |  |  |  |  |  |

| Maximum Overshoot or Undershoot                                               | 2.8%         | 3.2%      | 2.6%      |  |  |  |  |  |  |  |

| Settling Time (Transient Recovery Time)                                       | 185 ms       | 220 ms    | 208 ms    |  |  |  |  |  |  |  |

| PI + Design                                                                   | ed D Control | Strategy  |           |  |  |  |  |  |  |  |

| Evaluation of Transient and Dynamic Performance                               |              |           |           |  |  |  |  |  |  |  |

| Response Characteristics                                                      | Case 1       | Case 2    | Case 3    |  |  |  |  |  |  |  |

| Dynamic Response Time                                                         | Very Slow    | Very Fast | Very Slow |  |  |  |  |  |  |  |

| Maximum Overshoot or Undershoot                                               | 230%         | 2.1%      | 285%      |  |  |  |  |  |  |  |

| Settling Time (Transient Recovery Time)                                       | 785 ms       | 205 ms    | 1.05 s    |  |  |  |  |  |  |  |

based on PI + designed D controller demonstrates a weak and slow dynamic response with remarkable oscillations in transient performance [9]. The advantages of the proposed stabilizer scheme are also absolutely obvious when applying a sudden changes in load level (CPL power rating). Moreover, it is clear that in the PI + designed D control strategy, both proper transient recovery time and insignificant output voltage deviations cannot be realized simultaneously [9]. Accordingly, by evaluating and the results obtained, it can be concluded that in the stabilization of cascaded systems consisting of DC/DC power converters supplying CPLs, the suggested method is more efficient, robust, and more reliable than the PI+designed D control method [9].

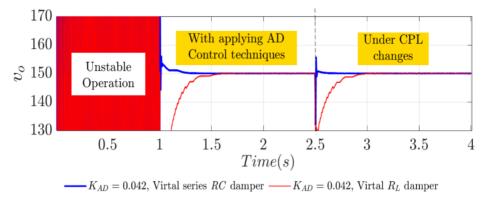

# 3.2.1.5 Comparative Study with the Virtual Series *RL* Damper-Based Stabilization Technique Proposed by [31]

Since the stabilization method presented in [15] is close to our control idea, a comparative study has been conducted to show the superiority of our contributions over it. The active stabilization approach used in [31] has

introduced a virtual series resistance to improve the damping rate and overcome the CPL instability effect for DC cascaded system. This realization of control was obtained by feedback the proportional coefficient of the inductor current of the source converter and subtracting it from the voltage control signal. However, this technique cannot be an adequate control idea in various performance states owing to intrinsic shortcomings and limitations. The first constraint is the restriction in stable band  $K_{\scriptscriptstyle AD}$  for this stabilization strategy so that it shows inflexibility in the proposed AD controller. In this regard, for instance, by applying the AD control approach offered by [15] to the cascaded system depicted in Fig. 3.2 with the parameters determined in Table 3.1, the allowable stable range for  $K_{AD}$  is restricted to (0.027, 0.051). It is evident that in this condition, the maximum damping rate is only 1.5 times its minimum amount. In contrast, as described in detail, for attaining a safe phase margin and admissible damping effect,  $K_{\rm AD,max}$  achieved by our proposed active stabilizer strategy is 20 times  $K_{{\scriptscriptstyle AD.min}}$  . Second, considering that the permissible virtual  $R_{L,\mathrm{max}}$  is limited to  $\left|R_{eq}\right|$  , under an intensive descending change in the load level (CPL power rating), the stability of system may not be preserved. Therefore, the proposed active stabilization technique in [31] cannot provide reliable and robust performance against sudden changes in load set. Third, as seen in Fig. 3.16, the proposed AD control scheme applied to the system illustrated in Fig.3.2 presents a fast-dynamic response with a decrease of about 75% in settling time and also significant improvement in rise time.

# 3.2.2 DC/DC Boost and Buck-Boost Converters feeding Resistive Load and CPLs

Fig. 3.16. Comparison of dynamic and transient performance of the AD technique offered by [31] with the proposed active stabilizer scheme [9].

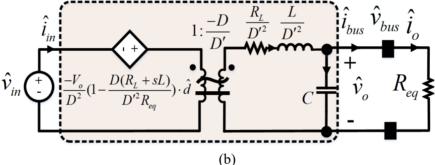

### 3.2.2.1 Modeling and Stability Analysis

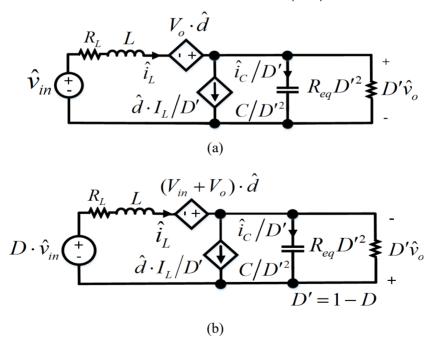

Figs. 3.17 and 3.18 show the boost and buck-boost converter systems feeding multiple CPLs and resistive loads, respectively [9]. A similar implementation process related to the averaged switch modeling method, such as steps 1 and 2, explained in detail in Section 3.2.1, is accomplished to obtain their simplified small signal-averaged equivalent models (see Figs. 3.19(a) and (b)). Then, the control-to-output transfer functions are derived (14) and (15), respectively, and also the poles are obtained by (16) [9]. According to the location of the poles and by considering  $R_L \langle R_{eq} | \cdot D'^2$  and  $R_{eq} \langle 0$ ; the

Fig. 3.17. A DC/DC boost converter supplying multiple CPLs.

Fig. 3.18. A DC/DC buck-boost converter with multiple CPLs.

stability conditions of these cascaded systems, like the configuration demonstrated in Fig.3.2, can be satisfied by  $R_L C \rangle \frac{L}{|R_{eq}|}$ .

Fig. 3.19. Simplified small-signal averaged equivalent circuit. (a) Boost converter. (b) Buckboost converter [9].

#### 3.2.2.2 Control Realization

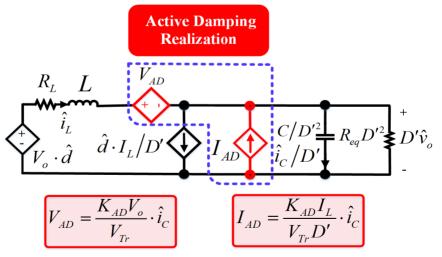

### a) Circuit Physical Meaning

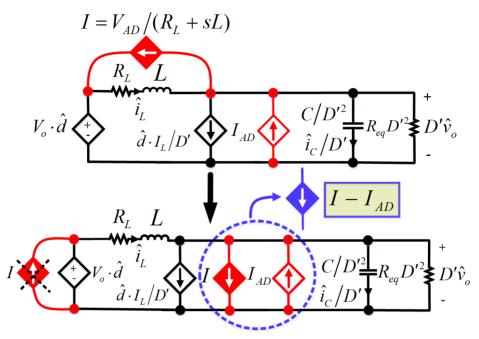

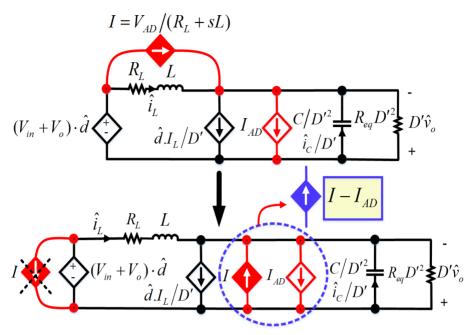

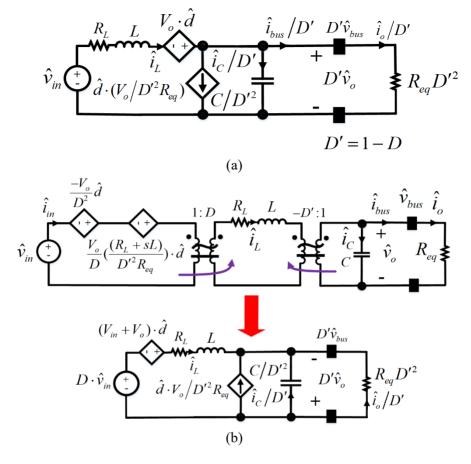

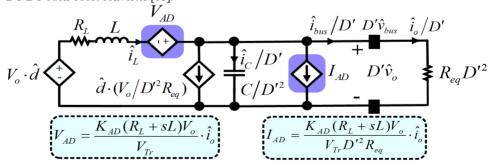

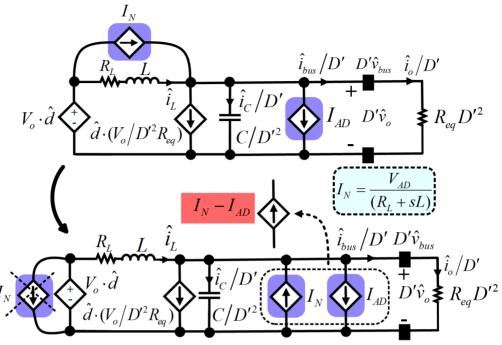

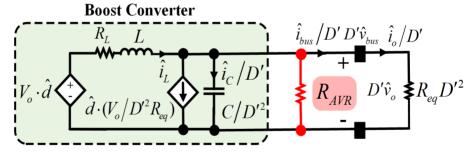

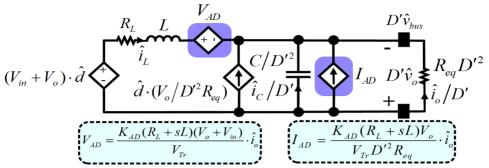

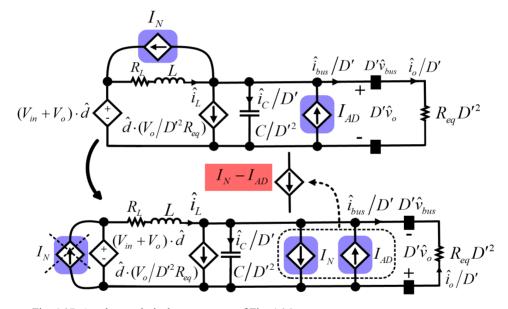

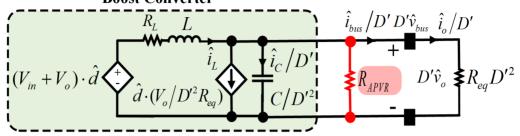

By employing the proposed AD control technique, Fig. 3.19(a) is dynamically modified as Fig. 3.20 through substitution of  $\hat{d} - \left(K_{AD} \cdot \hat{i}_C / V_{Tr}\right)$  instead of  $\hat{d}$  [9]. As observed in Fig.3.20, the control realization of this stabilizer strategy leads to the addition of the dependent voltage and current sources, namely  $I_{AD}$  and  $V_{AD}$ , into the simplified small-signal averaged model shown in Fig.3.19(a) [9]. As a result, using an efficient circuit analysis, the presented control approach introduces an interesting circuit physical meaning as demonstrated in Fig. 3.21. Given the DC relations and also considering the actual conditions,  $R_L \ll \left|R_{eq}\right| \cdot D'^2$ ,  $I - I_{AD}$  can be obtained as