Aalborg Universitet

## High power medium voltage DC/DC converter technology for DC wind turbines

Dincan, Catalin Gabriel

DOI (link to publication from Publisher): 10.5278/vbn.phd.eng.00072

Publication date: 2018

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Dincan, C. G. (2018). *High power medium voltage DC/DC converter technology for DC wind turbines*. Aalborg Universitetsforlag. https://doi.org/10.5278/vbn.phd.eng.00072

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# HIGH POWER MEDIUM VOLTAGE DC/DC CONVERTER TECHNOLOGY FOR DC WIND TURBINES

BY CATALIN DINCAN

DISSERTATION SUBMITTED 2018

AALBORG UNIVERSITY DENMARK

# High power medium voltage DC/DC converter technology for DC wind turbines

Ph.D. Dissertation Catalin Dincan

Dissertation submitted month 07, 2018

To Lara-Maria, Luca and Andreea.

| Dissertation submitted:   | July 2018                                                                          |

|---------------------------|------------------------------------------------------------------------------------|

| PhD supervisor:           | Prof. Philip Kjær<br>Aalborg University                                            |

| Assistant PhD supervisor: | Prof. Stig-Munk Nielsen<br>Aalborg University                                      |

|                           | Prof. Claus Leth Bak<br>Aalborg University                                         |

| PhD committee:            | Associate professor Michael Møller Bech (chairman)<br>Aalborg University           |

|                           | Professor Drazen Dujic<br>Ecole Polytechnique Fédérale de Lausanne – EPFL          |

|                           | Managing Director, Dr Kazuhiro Imaie<br>Hitachi Hi-Rel Power Electronics Pvt. Ltd. |

| PhD Series:               | Faculty of Engineering and Science, Aalborg University                             |

| Department:               | Department of Energy Technology                                                    |

| ISSN (online): 2446-1636  |                                                                                    |

ISSN (online): 2446-1636 ISBN (online): 978-87-7210-227-6

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Catalin Dincan

Printed in Denmark by Rosendahls, 2018

# Abstract

High voltage direct current (HVDC) connected wind farms promise reduced electrical losses, lower bill-of material cost and undiminished functionality with the condition the wind plant medium voltage (MV) collection network becomes DC, rather than MVAC. One dearly missed building block that would enable the transition to a DC voltage collection, is the DC/DC converter for high power & high voltage.

The main hypothesis of this thesis is that transition of MVAC connected wind turbines to MVDC (medium voltage direct current) output is conceivable with present and commercial technologies. Therefore, the main objective was investigation and development of proof of concept demonstrator for a high efficient, medium voltage (MV) converter topology, across relevant power (5 to 15 MW) and voltage range ( $\pm$ 35 kV to  $\pm$ 50 kV).

Research and concept demonstrators in DC/DC converters for high powers and voltages have emerged over the last decade, but none have become products yet, due to high cost, complexity or market volume.

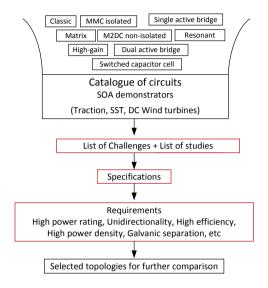

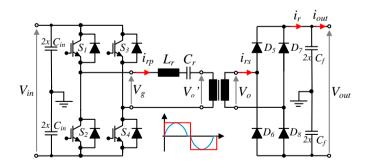

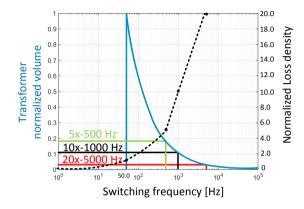

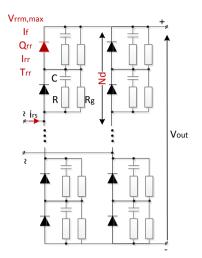

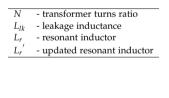

With priority on availability, losses and power density, an analysis of a large catalogue led to favor a variant of the series resonant converter ( entitled SRC#). As the DC turbine application does not require bidirectional power flow, forced commuted semiconductors on the  $\pm 50$  kVdc side are not required. A monolithic rectifier and transformer configuration was favoured for further robustness. With amorphous steel the transformer excitation frequency of 1 kHz was deemed achievable. Even more, at this frequency, line-frequency rectifier diodes are still feasible to use in series connected design, respecting their individual characteristics in recovery charge and recombination time, to balance losses and ratings.

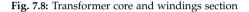

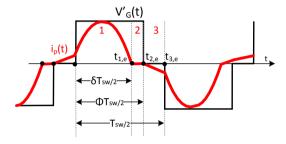

During analysis, it was discovered that the transformer core size and losses could be significantly reduced by shifting the resonant inductor and capacitor to the transformer secondary, and operate the inverter (on the primary) with a modified pulse-pattern, entitled pulse removal technique. The new modulation scheme permits regulation of power from nominal level to zero, in presence of variable input and output DC voltage levels. Combination of variable switching frequency and phase-shift modulation, below the resonant point of the LC tank, allows soft-switching commutation on all semiconductors and design of the medium frequency transformer for highest operating frequency.

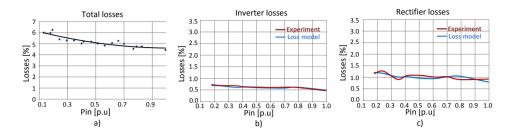

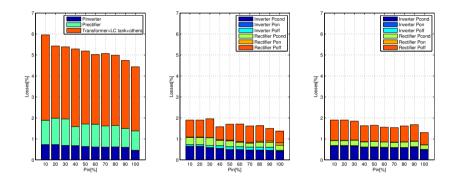

Further on, substantial effort was invested to develop the analysis and design guide line tool, including a 10 kW, 5 kV laboratory test circuit. From this scaled power circuit - and simulation & design tools, the full-scale circuit performance was estimated to yield impressive 1-1.5% losses and transformer weight of less than 4 tonnes. This should be comparable to the present solution of some 2-2.5% losses and weight of 20 tones.

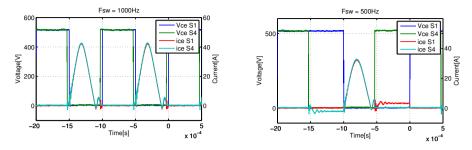

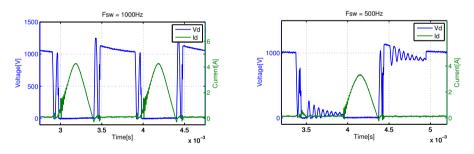

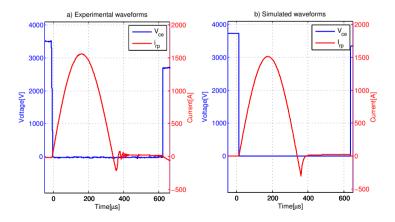

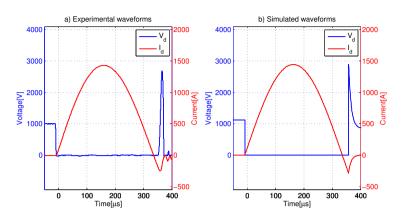

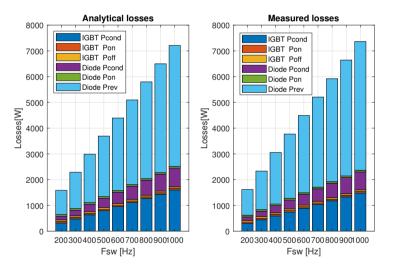

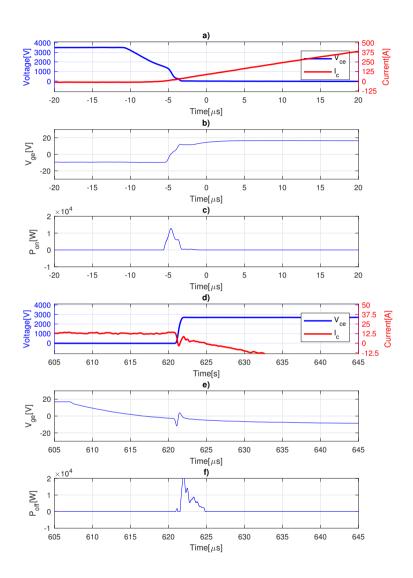

On a different medium voltage experimental setup, target 6.5 kV igbts and press-pack diodes have been exposed to similar voltage and current waveforms as in the target converter. The proposed soft-switching characterization setup allows generation of kilovolt and kiloamps pulses for a short time, without the need of bulky and expencive dc sources and loads. The semiconductor loss model was further validated and calibrated, while further works needs to address the validation of the monolithic transformer loss model.

# Resumé

HVDC-tilsluttede vindmølleparker lover reducerede elektriske tab, lavere materielomkostninger og ufortyndet funktionalitet med den betingelse, at vindmølle spændingsnetværket bliver DC, snarere end MVAC. En meget savnet byggesten, der ville muliggøre overgangen til en DC-spændingsopsamling, er DC/DC-konverteren til høj effekt og højspænding.

Hovedopgaven af denne afhandling er, at overgangen af MVAC-tilsluttede vindmøller til MVDC-strøm (mellemspændingsstrøm) er tænkelig med nutidige og kommercielle teknologier. Derfor var hovedformålet at undersøge og udvikle bevis for konceptdemonstrator til en høj effektiv, mellemspænding (MV) konverter topologi på tværs af relevant effekt (5 til 15 MW) og spændingsområde ( $\pm 35$  kV til  $\pm 50$  kV).

Forsknings- og konceptdemonstratorer i DC/DC-omformere til høj spændinger og spændinger er opstået i løbet af det sidste årti, men ingen er blevet til produkter endnu på grund af høje omkostninger, kompleksitet eller markedsvolumen.

Med en prioritet om tilgængelighed, tab og strømtæthed førte en analyse af et stort katalog til fordel for en variant af serieresonantomformeren (med navnet SRC #). Da DC-turbineapplikationen ikke kræver tovejstrømstrøm, kræves der ingen tvungen, kommuerede halvledere på  $\pm 50$  kVdcsiden. En monolitisk ensretter og transformatorkonfiguration blev favoriseret for yderligere robusthed. Med amorft stål blev transformatorens eksitationsfrekvens på 1 kHz anset for opnåelig. Endnu mere, ved denne frekvens er line-frekvens ensretterdioder stadig mulige at anvende i serieforbundet design, idet de respekterer deres individuelle egenskaber ved genopretningsafgift og rekombinationstid for at balancere tab og ratings.

Under analysen blev det opdaget, at transformatorens kernestørrelse og tab kunne reduceres signifikant ved at skifte resonansspole og kondensator til transformatoren sekundært, og betjene inverteren (primært) med et modificeret pulsmønster, der har ret pulsfjernelsesteknik. Den nye modulationsplan gør det muligt at regulere strøm fra nominelt niveau til nul, i nærværelse af variable indgangs- og udgangsspændingsniveauer. Kombination af variabel koblingsfrekvens og faseforskydningsmodulering, under resonanspunktet for LC-tanken, tillader soft-switching commutation på alle halvledere og design af mediumfrekvenstransformeren til højeste driftsfrekvens.

Endvidere blev der investeret betydelige anstrengelser for at udvikle analysen- og designstyringsværktøjet, herunder et 10 kW, 5 kV laboratorietestkredsløb. Fra dette målte kredsløbskredsløb - og simulerings- og designværktøjerne estimeres fuldskalaenhedens ydelse til imponerende 1-1.5% tab og transformatorvægt på mindre end 4 tons. Dette skal være sammenligneligt med den nuværende løsning på ca. 2-2.5% tab og vægt på 20 toner.

På en anden mellemspændings eksperimentelle opsætning er mål 6,5 kV igbts og press-pack diodes blevet udsat for tilsvarende spændings- og strømbølgeformer som i målkonverteren. Den foreslåede soft switching karakterisering opsætning giver mulighed for generering af kilovolt og kiloamps pulser i en kort tid, uden behov for omfangsrige og expencive DC kilder og belastninger. Halvleder tabet model blev yderligere valideret og kalibreret, mens yderligere værker skal adressere valideringen af den monolitiske transformator tabmodel.

# Contents

| Ał                                   | ostrac     | et de la constant de | v   |  |  |  |

|--------------------------------------|------------|----------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Re                                   | Resumé vii |                                                                                                                |     |  |  |  |

| Pr                                   | eface      |                                                                                                                | xi  |  |  |  |

| 1                                    | Intr       | oduction                                                                                                       | 1   |  |  |  |

|                                      | 1.1        | Background and motivation                                                                                      | 2   |  |  |  |

|                                      | 1.2        | Principle hypotheses, objectives and limitations                                                               | 7   |  |  |  |

|                                      | 1.3        | Thesis outline                                                                                                 | 8   |  |  |  |

|                                      | 1.4        | List of publications                                                                                           | 10  |  |  |  |

| 2                                    | Inve       | estigation of current state of the art                                                                         | 13  |  |  |  |

|                                      | 2.1        | An overview of DC wind farms configurations                                                                    | 14  |  |  |  |

|                                      | 2.2        | An overview of DC wind turbine concepts                                                                        | 16  |  |  |  |

|                                      | 2.3        | A survey of DC/DC converter topologies                                                                         | 19  |  |  |  |

|                                      | 2.4        | A survey of DC/DC converter demonstrators and technologies                                                     | 30  |  |  |  |

|                                      | 2.5        | Conclusions                                                                                                    | 46  |  |  |  |

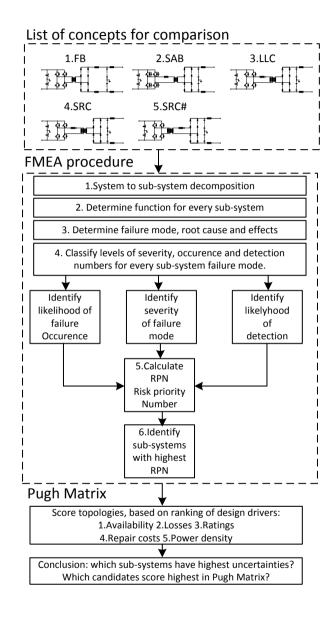

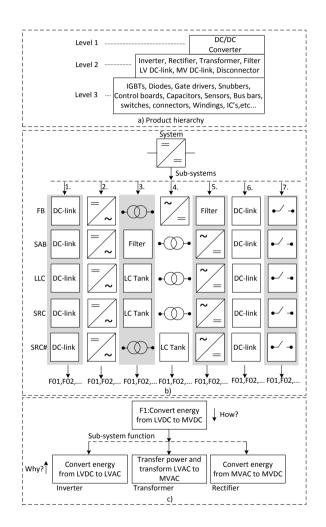

| 3 DC/DC converter topology selection |            | DC converter topology selection                                                                                | 47  |  |  |  |

|                                      | 3.1        | Methodology to select circuits for comparison                                                                  | 48  |  |  |  |

|                                      | 3.2        | Methodology to select suitable DC/DC converter                                                                 | 55  |  |  |  |

|                                      | 3.3        | Selection results                                                                                              | 63  |  |  |  |

|                                      | 3.4        | Conclusions                                                                                                    | 69  |  |  |  |

| 4                                    | Seri       | es resonant converter - SRC#                                                                                   | 71  |  |  |  |

|                                      | 4.1        | Introduction                                                                                                   | 72  |  |  |  |

|                                      | 4.2        | Review of classic series resonant converter                                                                    | 76  |  |  |  |

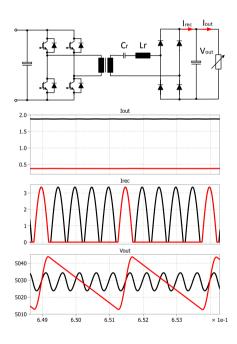

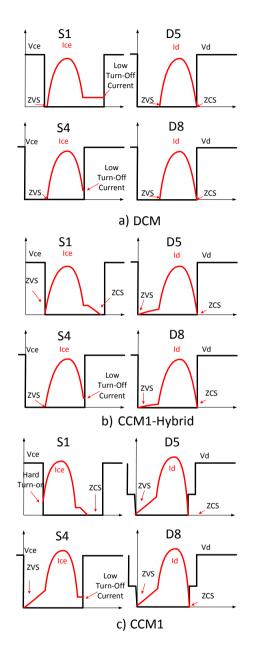

|                                      | 4.3        | Operation principle of the SRC#                                                                                | 82  |  |  |  |

|                                      | 4.4        |                                                                                                                | 101 |  |  |  |

|                                      | 4.5        | Conclusions                                                                                                    | 105 |  |  |  |

| 5       | Controller structure for SRC# 1                                                                           |                                          | 107                                                                                                                                                                                                           |

|---------|-----------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 5.1                                                                                                       | Principle of control                     | 108                                                                                                                                                                                                           |

|         | 5.2                                                                                                       | Proposed controller structure            | 108                                                                                                                                                                                                           |

|         | 5.3                                                                                                       | Controller performance                   | 113                                                                                                                                                                                                           |

|         | 5.4                                                                                                       | Conclusions                              | 116                                                                                                                                                                                                           |

| 6       | 5 Sensitivity studies of SRC#                                                                             |                                          | 117                                                                                                                                                                                                           |

|         | 6.1                                                                                                       | Peak resonant current and voltage stress |                                                                                                                                                                                                               |

|         | 6.2                                                                                                       | LC tank sensitivity to specifications    |                                                                                                                                                                                                               |

|         | 6.3                                                                                                       | Transformer                              |                                                                                                                                                                                                               |

|         | 6.4                                                                                                       | Rectifier                                |                                                                                                                                                                                                               |

|         | 6.5                                                                                                       | Waveforms sensitivity to non-idealities  | 134                                                                                                                                                                                                           |

|         | 6.6                                                                                                       | Conclusions                              | 140                                                                                                                                                                                                           |

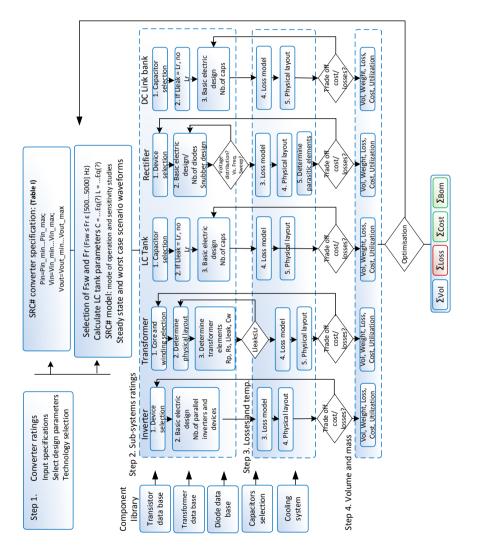

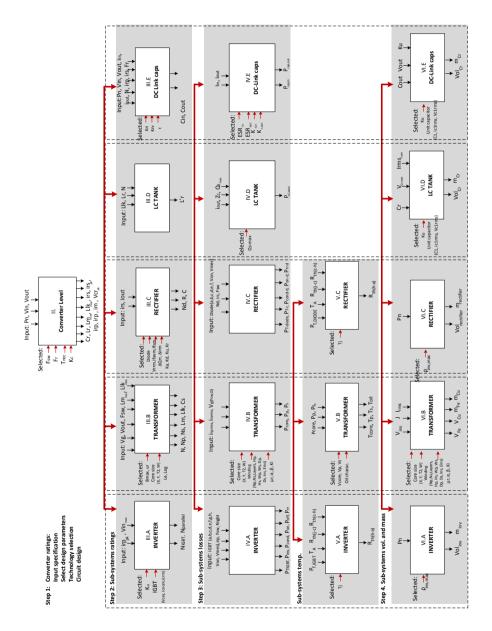

| 7       | Des                                                                                                       | ign guide line for SRC#                  | 141                                                                                                                                                                                                           |

|         | 7.1                                                                                                       | Methodology                              |                                                                                                                                                                                                               |

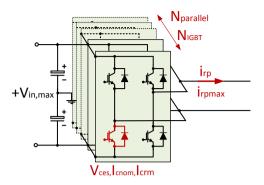

|         | 7.2                                                                                                       | Converter ratings                        | 146                                                                                                                                                                                                           |

|         | 7.3                                                                                                       | Sub-system ratings                       | 152                                                                                                                                                                                                           |

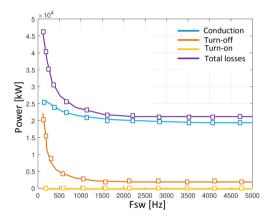

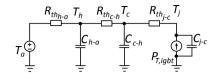

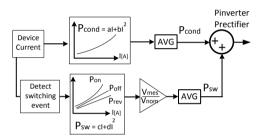

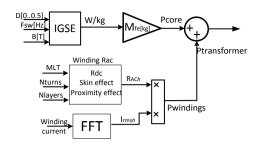

|         | 7.4                                                                                                       | Sub-systems losses and temperature       | 160                                                                                                                                                                                                           |

|         | 7.5                                                                                                       | Sub-systems volume and mass              |                                                                                                                                                                                                               |

|         | 7.6                                                                                                       | 10MW Design example                      |                                                                                                                                                                                                               |

|         | 7.7                                                                                                       | Conclusions                              | 183                                                                                                                                                                                                           |

|         |                                                                                                           |                                          |                                                                                                                                                                                                               |

| 8       | Exp                                                                                                       | erimental work                           | 185                                                                                                                                                                                                           |

| 8       | <b>Exp</b><br>8.1                                                                                         | Proof of concept: 10 kW SRC#             | <b>185</b><br>186                                                                                                                                                                                             |

| 8       | 8.1<br>8.2                                                                                                | Proof of concept: 10 kW SRC#             | <b>185</b><br>186<br>193                                                                                                                                                                                      |

| 8       | 8.1                                                                                                       | Proof of concept: 10 kW SRC#             | <b>185</b><br>186<br>193                                                                                                                                                                                      |

| 8<br>9  | 8.1<br>8.2<br>8.3                                                                                         | Proof of concept: 10 kW SRC#             | <ul><li>185</li><li>186</li><li>193</li><li>202</li><li>203</li></ul>                                                                                                                                         |

|         | 8.1<br>8.2<br>8.3                                                                                         | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> </ul>                                                                                                                      |

|         | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2                                                             | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> </ul>                                                                                                         |

|         | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3                                                      | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> </ul>                                                                                            |

|         | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4                                               | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> </ul>                                                                               |

|         | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3                                                      | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> </ul>                                                                               |

| 9       | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5                                        | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> </ul>                                                                               |

| 9<br>Bi | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5                                        | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> <li>208</li> </ul>                                                                  |

| 9<br>Bi | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br><b>bliog</b>                        | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> <li>208</li> <li>209</li> </ul>                                                     |

| 9<br>Bi | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br><b>bliog</b>                        | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> <li>208</li> <li>209</li> <li>223</li> <li>223</li> </ul>                           |

| 9<br>Bi | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br><b>bliog</b><br><b>ppend</b><br>A.1 | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> <li>208</li> <li>209</li> <li>223</li> <li>224</li> </ul>                           |

| 9<br>Bi | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br><b>bliog</b><br>A.1<br>A.2          | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> <li>208</li> <li>209</li> <li>223</li> <li>224</li> <li>226</li> </ul>              |

| 9<br>Bi | 8.1<br>8.2<br>8.3<br><b>Con</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br><b>bliog</b><br>A.1<br>A.2<br>A.3   | Proof of concept: 10 kW SRC#             | <ul> <li>185</li> <li>186</li> <li>193</li> <li>202</li> <li>203</li> <li>204</li> <li>205</li> <li>206</li> <li>207</li> <li>208</li> <li>209</li> <li>223</li> <li>224</li> <li>226</li> <li>228</li> </ul> |

# Preface

Foremost, I would like to thank my main supervisor, Prof. Philip Carne Kjær for giving me the opportunity to do research in the field of high power dc/dc converters, for his guidance, patience, professionalism and excellent feedback. I would also like to thank Prof. Stig Munk Nielsen and Prof. Claus Leth Bak for their feedback and help during my PhD studies. Also, my acknowledgements go to Prof. Drazen Dujic, Dr. Kazuhiro Imaie and Assoc. Prof. Michael Møller Bech for their effort, for being part of the examination committee and for the important contributions to the thesis. The financial support during my PhD study offered by the Department of Energy Technology is deeply appreciated.

During the two years we have been working together, my thanks go to Dr. Yu-hsing Chen for the interesting collaboration we had. Further on, during the times of practical challenges, a lot of help was given by Szymon Beczkowsky, Emanuel Petre Eni and Lorand Bede. A special thanks go also to Enrique Rodrigues Diaz for putting further effort in evaluation of SRC# and all the interesting discussions. I am also grateful to Cristian Sintamarean who has encouraged me to embark on the PhD journey and motivated me along the studies.

A special thanks go to Alberto Tonellotto and Eduard Sarra Macia. The collaboration with you has made the last months of my PhD interesting and motivating. Thank you for being team mates and for all the great conversations we have had during the spanish/italian coffee time.

During my stay at the university, I met many people who have made the work environment an interesting place to share ideas. These people are Yahya Naderi, Denis Zaikin, Carlos Munoz, Radhika Sarda. Thank you for the support and change of ideas.

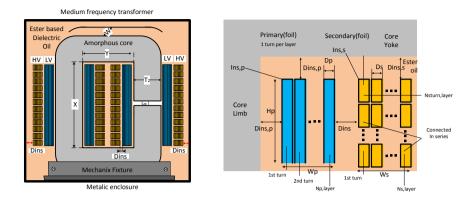

To Dr. Vaisambhayana Brihadeeswara Sriram and the team from NTU Singapore, I must thank them for all their support, help and work related to the design of medium frequency transformers.

The effort of Mads Lund and Walter Neumayr during the practical implementation of the medium voltage setups, is kindly appreciated. Let's hope, we will change that ground protection scheme in the future.

#### Preface

Many thanks go to my friends from Koinonia who have supported and encouraged me during the studies. Lee Hanson, continue the good work that you are doing there.

Finally, I would like to acknowledge my family for all their support. The biggest thanks go to my darling wife Andreea, my boy Luca and my little princess Lara-Maria. You have kept me motivated, focused and loved all these years and also made sure I was not working from home.

Catalin Dincan Aalborg University, July 4, 2018

# Nomenclature

- $\Delta V$  Voltage difference between  $V'_g$  and  $V_o$

- $\delta$  Inverter legs phase displacement

- $\gamma$  Normalized switching frequency

- $\omega_r$  Resonant angular frequency

- $\omega_{sw}$  Switching angular frequency

- $\Phi$  Inverter legs phase displacement in CCM mode

- $C_r$  Resonant (tank) capacitor

- CCM Continuous conduction mode

- DCM Discontinuous conduction mode

- $F_r$  Resonant frequency

- *F<sub>sw</sub>* Switching frequency

- HVDC High voltage direct current

- *i<sub>m</sub>* Transformer magnetizing current

- *i*<sub>out</sub> Output current of the converter

- *i*<sub>rp</sub> Primary resonant current

- *i*<sub>rs</sub> Secondary resonant current

- *i<sub>r</sub>* Rectified current

- K Constant

- *L<sub>m</sub>* Transformer magnetizing inductance

- $L_r$  Resonant (tank) inductor

## Preface

| LVDC Low voltage direct current    |                                         |  |  |

|------------------------------------|-----------------------------------------|--|--|

| М                                  | Voltage gain                            |  |  |

| MVDC Medium voltage direct current |                                         |  |  |

| Ν                                  | Transformer turns ratio                 |  |  |

| $P_{in}$                           | Input power                             |  |  |

| Pout                               | Output power                            |  |  |

| Q                                  | Converter quality factor                |  |  |

| $q_s$                              | Resonant capacitor stored charge        |  |  |

| SRC                                | Series resonant converter               |  |  |

| SRC#                               | Series resonant converter sharp         |  |  |

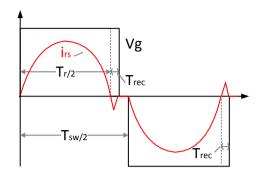

| $T_r$                              | Resonant current pulse period           |  |  |

| T <sub>rec</sub>                   | Rectifier diode reverse recovery time   |  |  |

| $T_{sw}$                           | Switching period                        |  |  |

| $V_{Cr}$                           | Resonant capacitor voltage              |  |  |

| $V_g$                              | Inverter output voltage                 |  |  |

| $V'_g$                             | Inverter reflected voltage on secondary |  |  |

| $V_{in}$                           | Input voltage                           |  |  |

| Vout                               | Output voltage                          |  |  |

| $V_o$                              | Rectifier voltage                       |  |  |

| $V_o'$                             | Rectifier voltage reflected on primary  |  |  |

| $V_t$                              | Resonant tank voltage                   |  |  |

| $Z_c$                              | Resonant tank characteristic impedance  |  |  |

|                                    |                                         |  |  |

# Chapter 1

# Introduction

# 1.1 Background and motivation

#### 1.1.1 A case for DC power collection

One of the main reason why DC power collection was not initially adopted as standard for electric power transmission and distribution was its inability to change voltage levels, meaning step-up at point of power generation for transport and step down again in the vicinity of the load. The equivalent of an ac transformer was missing and DC interrupters are inherently more difficult then AC. In the pioneering days of electro-technical development, DC power stations were able to supply customers within only a few km away from the plant, limited by the high power losses in the cables. On the other hand, the development of AC transformers, generators and polyphase induction motors facilitated the transmission of gigawatt power around the globe, powering factories and households with no storage required. This facilitated the interconnection of electric networks like Europe, China and US with more then 500 million consumers in synchronism. In the 20th century, AC has dominated the power industry for the right reasons at the time, becoming the status quo for electric power.

Moving fast forward to the 21<sup>st</sup> century, the electric scenery is dramatically changed and it's no longer possible to depended on a century old and aging AC infrastructure. Power electronics technologies have started a new era, due to focus on continued improvements and higher efficiencies [1]. Classic AC energy sources (such as coal and gas power plants) will no longer dominate the energy mix, mainly due to the advent and increased shares of renewable energy. DC consumer devices (as data and computer centres, LED lighting, variable frequency drivers), high power energy storage, electric vehicles are all rapidly expanding.

In the last decade, *R*&*D* studies for high voltage direct current (HVDC) grids and micro DC grids have been under progress in all the major corporate research centers, universities and industries. HVDC is considered today as the optimal choice for bulk power transmission at high voltage level and over virtually unlimited distance for cables, which are limited for AC transmission systems due to reactive power loading. HVDC is the suitable solution for easy interface of asynchronous AC systems and are suited for weak AC network connection.

In the same manner, LVDC micro grid demonstrators have been built to prove their benefits and feasibility compared to AC solution. Higher efficiency, synchronization of distributed generators is not necessarily, loads are not affected by voltage disturbances and power quality is not impacted by inrush currents and single phase loads or generators.

If DC seems to be preferred at HVDC transmission and LVDC consumption, it's only logical that medium voltage direct current (MVDC) grids should

#### 1.1. Background and motivation

be investigated. There are a few strong arguments for this: the need of smart grid development and high penetration of distributed energy resources and energy storage favours DC connection point. Increased flexibility and reliability at a lower cost by sharing resources is offered. Synchronization between DC grids is no longer necessarily, while active and reactive power can be controlled through rapidly and independently between AC/DC or DC/DC converters and the AC grid. There is provision of reactive power support and enhanced fault ride through capability [2]. In theory, MVDC grids are the best technical solution for integration of renewable energy resources in distribution networks, as they have the benefits of higher efficiency and reliability, increase power transfer capability, while offering lower size, weight and bill of materials cost.

On the practical side, Europe's first MVDC link was recently commissioned, linking the Isle of Anglesey to North Wales AC collection grid, employing MV-VSC converters. The Angle-DC project aims to demonstrate a novel network reinforcement technique by converting an existing 33-kilovolt (kV) AC circuit to DC operation [3]. The reason of implementation was that uncontrolled power flows where putting the system at risk by exceeding thermal limits of the cables and overhead lines, while the MVDC link is expected to enable improved power flow and voltage control. Similar, commercial concepts from [4] have been introduced to the market, while offering efficient power transfer in the range of 30 MW to 150 MW.

#### **1.1.2 HVDC wind farm with MVDC power collection**

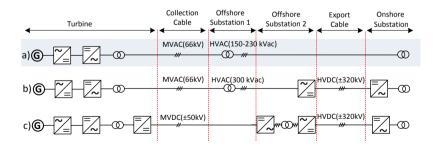

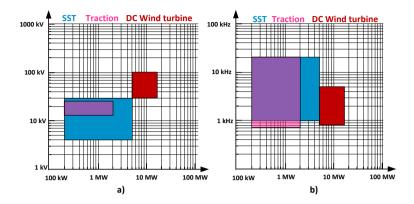

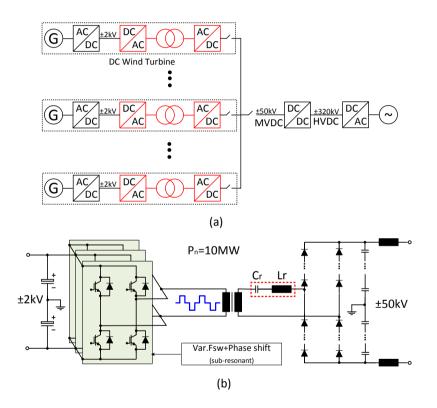

**Fig. 1.1:** Layouts of different configurations of electrical systems for offshore wind farms: a) MVAC collection and HVAC transport; b) MVAC collection and HVDC transmission; c) MVDC collection and HVDC transmission

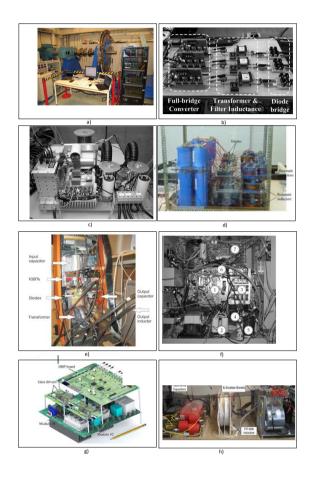

A near term application of MVDC technology exists in the collector networks of large offshore wind farms with HVDC links to onshore AC grids. The solution can offer savings on system level, only if new electrical solutions are introduced, meaning key components like the DC/DC converter: a mega-watt, high voltage, high frequency power electronic "transformer". Fig. 1.1 presents layouts of different types of electrical systems for offshore wind farms, which are: AC collection/AC transmission (1.1a), AC collection/DC transmission (1.1b) and the hypothetical DC collection/ DC transmission (1.1c).

All present onshore and offshore wind farms use an AC collection network, typically of 33kV or 66kV. Most of offshore wind farms use HVAC collection grids to transmit the energy collected from wind turbines to onshore (Fig. 1.1a). Other solutions use HVAC up to a large VSC rectifier station and then to the mainland, through high voltage DC (HVDC) transmission cables (Fig. 1.1b). But, as mentioned earlier this technique could be improved, by replacing the AC offshore collection grid with a medium voltage DC (MVDC) grid, as shown in Fig. 1.1c. It has been demonstrated in [5],[6] that wind farms could operate with higher efficiency when connected to MVDC collection grid. The motivation lays in the fact that the levelized cost of energy (LCOE) could be reduced by as much as 3%, by improving the efficiency with 2% and reducing the bill of materials (BoM) costs by at least 1%.

In a conventional offshore wind turbine, the generator output is connected through an AC/DC/AC converter, giving a constant frequency & voltage, which is elevated to 33kVac or 66kVac (medium voltage) for the collection network and secondly to 150-230 kVac (high voltage) for transmission. The MV/HV transformer is usually built on a separate platform from the offshore substation converter. Compared with AC and AC/DC layout configurations, in DC systems the line frequency transformers are replaced with high power dc/dc converters with medium frequency transformers, which could lead to significant reduction in the overall system size, weight, as well as the construction and installation cost of the wind turbines and substation platform (Fig. 1.1c). Up to this date, few active steps on realizing the paradigm shift have been implemented and there is no MVDC system commissioned for wind farms. There are no standards or design guidelines mentioning recommended MVDC levels where the system should operate and especially there are no high power DC/DC converters [1], [2]. The ambition of this work is therefore to update the state of the art and fill the gap regarding the DC/DC converter technologies.

A possible path-to-product route is illustrated in Fig. 1.2 and it proposes a series of intermediate stages within a controlled laboratory environment. An initial prof of principle needs to be selected from a myriad of DC/DC topologies and should fulfill all basic requirements regarding efficiency, power density and obtain initial characterization waveforms. To increase certainty in the design, a proof of concept at elevated voltage and power level should be

#### 1.1. Background and motivation

obtained increasing technology readiness level to TRL 6. At this level, the demonstrator experiments must provide results and confirm the design analysis and simulation, so confidence in the design guide line is built. Component losses and temperature rise would be characterized in a demonstrator with lower output voltage, while a 2nd demonstrator with higher voltage gain could evaluate static and dynamic voltage sharing on the rectifer side. Certainly, in both demonstrators, philosophies regarding power circulation should be discussed. The collected results will be further used to implement a third state of demonstrators, where a *thermal proof of concept* is implemented. Here the semiconductor components tested must be identical to those intended in the fully-rated product, while magnetics and capacitors are scaled down.

#### 1.1.3 The high power DC/DC converter

The DC/DC converter for high power & high voltage (basically the equivalent of the ac transformer) is a missing building block for many applications spanning renewable energy, DC transmission & distribution, railway supply and traction. Its absence and low technology readiness level are the principle reasons of why MVDC collection networks have not been integrated on a large scale in wind farms. There are many arguments in favour of converting the wind turbine to DC output. For instance, in a wind turbine, the line frequency transformer and the DC/AC converter are replaced with a high power DC/DC converter, using a medium frequency transformer (Fig. 1.1c). This will lead to significant reduction in the overall turbine size and weight. But the area of applications for such a converter is larger: a cost efficient solution for medium voltage drives and traction, power supply to offshore oil/gas extraction platforms, grid connection of large PV plants or the replacement of large traditional power transformers with the so-called *solid state transformers*.

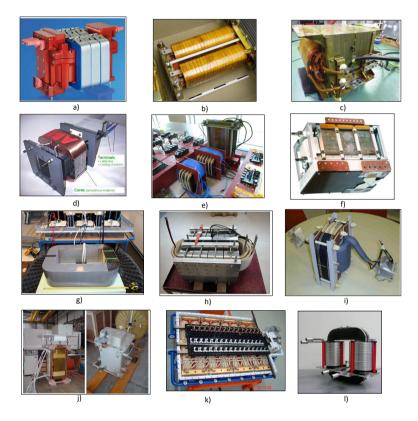

In the last decade, DC/DC converter research and concept demonstrators for smart grid and traction application at relevant power and voltage level have emerged, but no so many to collector networks for wind farms, which impose tougher specifications. Nevertheless, the design competence has grown, where circuit ratings, control, transformer electrical, magnetic and thermal performance have increased. It is mandatory therefore, to create a pool of knowledge that allows the design of demonstrators and should be extended to calculate the true cost and performance of the turbine DC/DC converter. Previous work has formulated many concepts for high power DC/DC converters related to DC wind turbines, but none have become products or even relevant demonstrators.

This thesis aims at increasing the technology readiness level (Fig. 1.2) for the wind turbine high power DC/DC converter, while employing existing

Fig. 1.2: Technology readiness level a) and path to technology b).

power electronics and transformer technology. The technologies of interest are resonant and soft-switching topologies that employ commercial silicon semiconductors and medium frequency transformers. Most of the circuit components are catalogue item-proven technology, but which where never integrated and engineered into the application of interest here. Off the shelf monolithic transformers are not available, but low loss core materials do exist as there are suppliers able to provide cores up to 2-3 MVA for line frequency distribution. Therefore a demonstration project that shows the feasibility and benefits of the comercial technology is a must to stimulate further R&D investments across the supply chain (cables, converters, transformers, control, OEMs) as many wind farm and wind turbine developers avoid the technology due to lack of low technology readiness level and field experience. The thesis suggests to bridge a proof of principle to a scaled laboratory prototype and build a foundation for future demonstrators at full ratings.

# 1.1.4 Terminology

The turbine DC/DC converter can be understood as a DC transformer that adapts voltages between LVDC and MVDC levels, while the substation DC/DC converter adapts voltage levels between MVDC and HVDC.

# **1.2** Principle hypotheses, objectives and limitations

# 1.2.1 Main hypotheses

The following hypotheses are formulated and their demonstration is confirmed ( or infirmed) in the following chapters:

- The transition of SOA (state of the art) wind turbines to MVDC output is conceivable with present and commercial technologies, while having equal or greater efficiency and power density as compared to SOA MVAC connected wind turbines

- Low loss commutation of semiconductors at high power, medium voltage and medium frequency is achievable with soft-switching or resonant topologies

- High power density is conceivable as long as the transformer permits design for medium frequency operation (i.e losses are kep below Currie temp. point) and the semiconductors are highly utilized

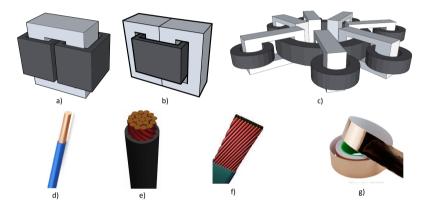

- A medium frequency transformer with low core losses, suitable windings and insulation system can be designed for powers up to 15 MVA, by investigation of different core materials and structures

- Handling of medium voltage can be achieved through passive devices series connection rather than series connection of active devices or modular architecture that employs a large number of components

# 1.2.2 Main objectives

The main objective of this Phd thesis is to investigate and develop a proof of concept *demonstrator* for a high efficient, medium voltage (MV) converter topology, across relevant power (5 to 15 MW) and voltage range ( $\pm 35kV$  to  $\pm 50kV$ ). Expected outcome of the thesis will be:

- Survey of DC/DC converters for wind turbine and applications akin.

- Down selection of semiconductors and medium frequency transformer among multiple choices.

- Selection of suitable and later also optimal DC/DC topology.

- Analysis of selected converter topology, by means of simulation and preliminary loss investigation

- Design guide line and analysis tool for DC/DC converter.

- Build-up and testing of the prototype to validate the proposed design guide line.

# 1.2.3 Project Limitations

- Topologies that have ease of connection to the state of the art generators + active rectifiers will have the highest priority.

- The research on the circuits and their operation will focus only on commercially available Si-based semiconductors

- High detail design aspects of medium frequency transformer are not the main focus of the work and the outcome of the research is limited to core and windings material and layout selection, with preliminary study of losses

- Due to high costs, manufacturing time, logistics, number of researchers, complicated testing due to safety procedures, the initial demonstrator is limited to 5 kV and 100 kW, as this value allows sufficient value to extrapolate to  $\pm 50kV$ , 10MW or similar

Following areas will not be covered in the thesis and they are suggested for future work: protection schemes and strategies; isolation coordination; EMI (electromagnetic interference) impact and design of auxiliary supply.

# 1.3 Thesis outline

The thesis is presented as a monograph and is divided in nine chapters.

## Chapter 1 - Introduction

Gives the background and motivation of this research. The main application of HVDC wind farms with MVDC power collection is introduced and it promises consistent advantages, with the key component being the DC/DC converter located in the turbines. The main objectives of the work are presented together with project limitations and a summary of the main contributions is given.

## Chapter 2 - Investigation of current state of the art

Gives a review of DC wind farms, DC wind turbine concepts and DC/DC high power converters. A catalogue of circuits is organized to get a general picture of previous proposed topologies and a list of industrial and academic demonstrators is presented. The main goal is to guide towards the optimal topology.

## Chapter 3 - DC/DC converter topology selection

This chapter presents the list of major challenges, list of studies to generate the nominal specifications and a methodology that helps to downsize the catalogue of circuits to only a few candidates, based on different design drivers and list of functionalities.

## Chapter 4 - Series resonant converter - SRC#

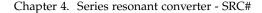

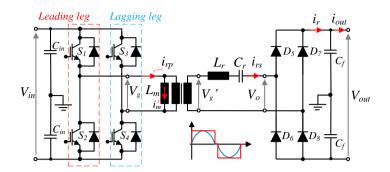

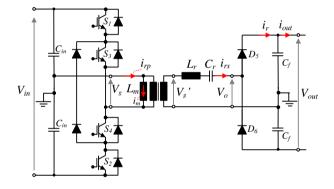

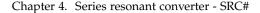

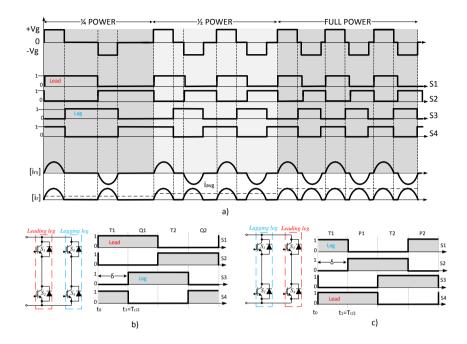

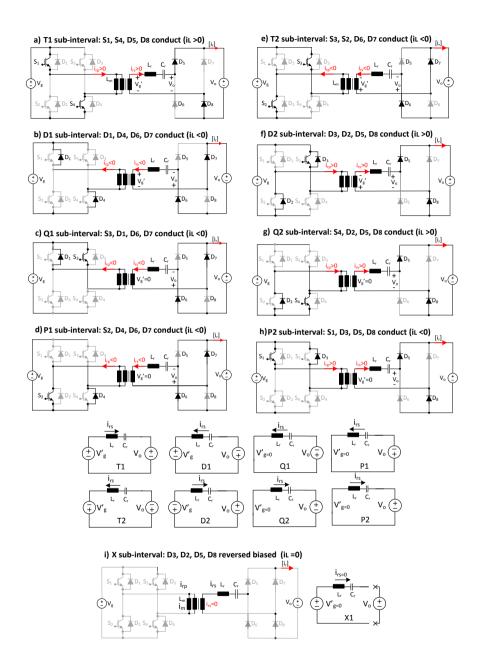

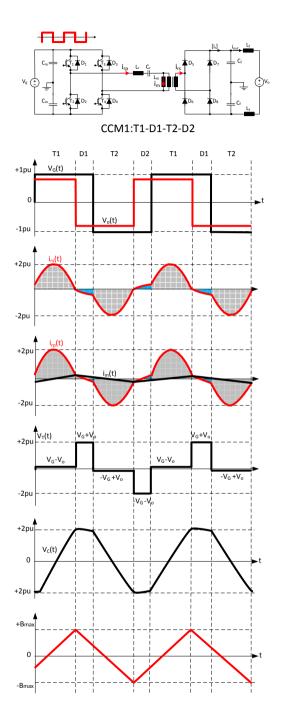

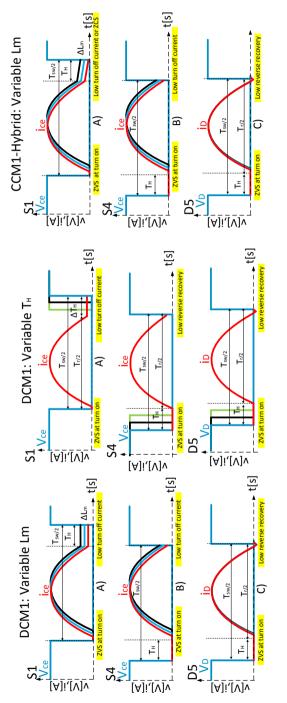

Major focus is put on the applicability of the series resonant converter for DC wind turbines. General modes of operation and control methods are discussed, while a novel operating mode is introduced for a series resonant converter (entitled SRC#) with LV tank located on rectifier side.

## Chapter 5 - Controller structure for SRC#

In this chapter the general structure of SRC# controller is evaluated and characteristic waveforms are presented for steady state, dynamic, fault ride through and short circuit operation.

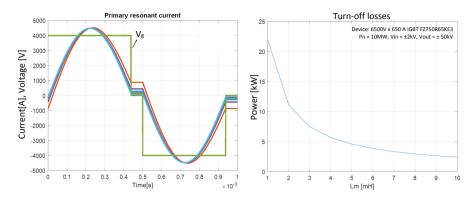

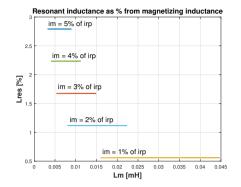

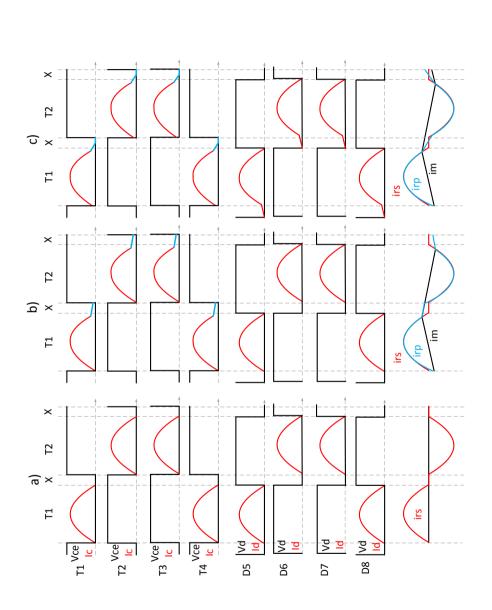

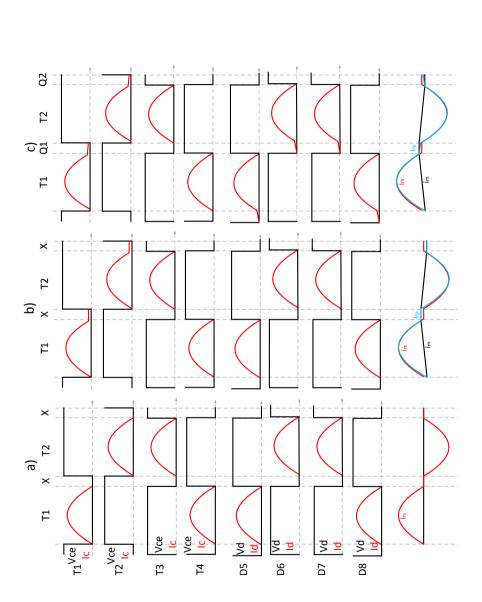

## Chapter 6 - Sensitivity studies of SRC#

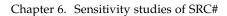

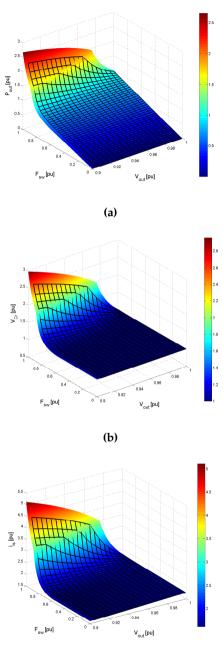

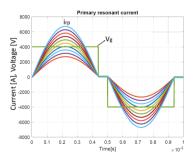

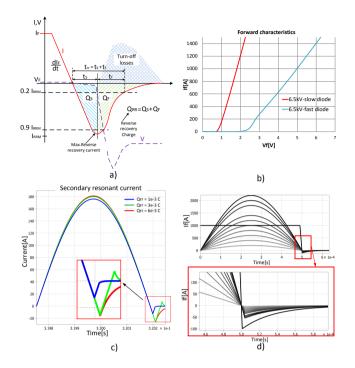

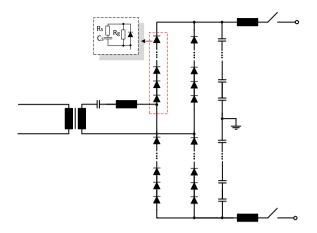

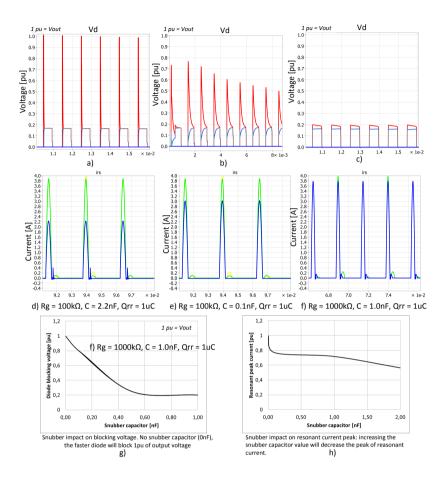

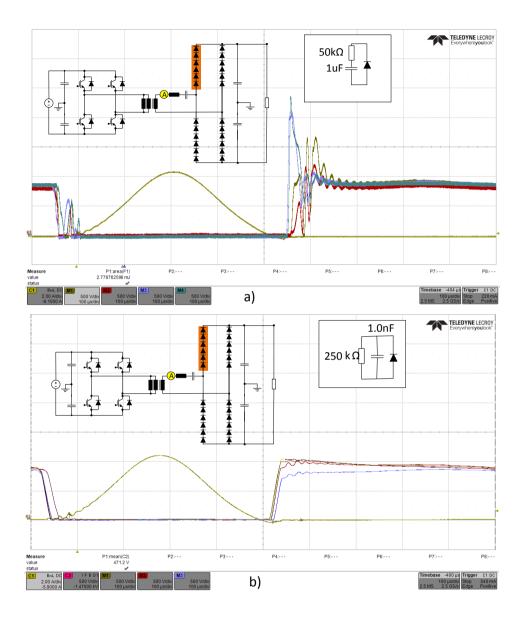

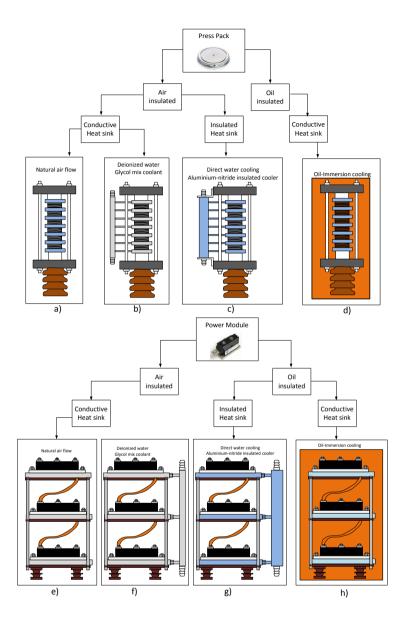

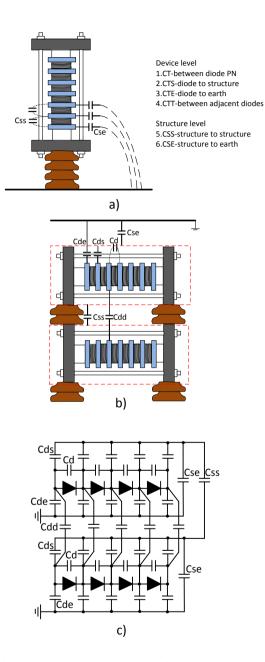

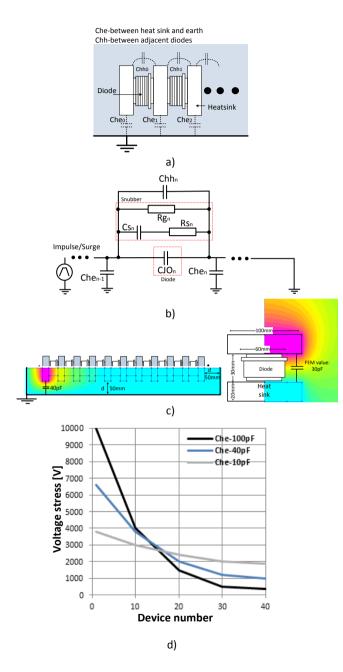

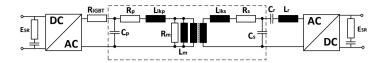

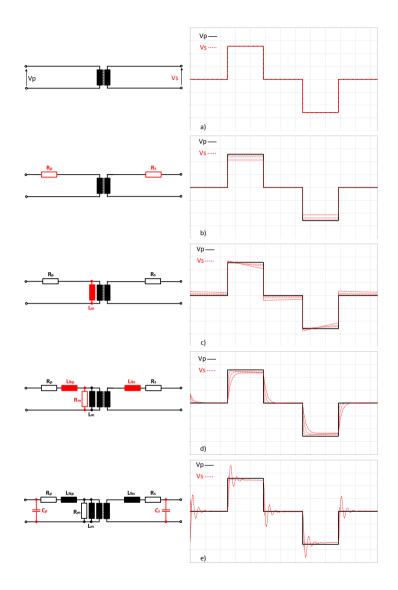

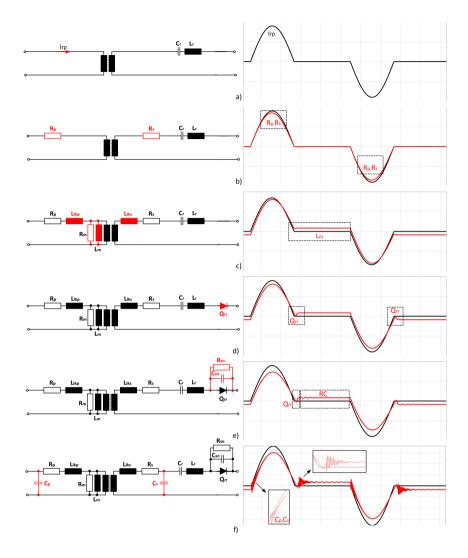

LC tank, transformer and rectifier sensitivity studies are discussed. The selection of LC tank parameters has the strongest impact on delivered nominal power, peak current and voltage values, which impact the circuit ratings. Transformer magnetizing inductance has to be carefully selected and it is shown what impact it has on transformer size, semiconductor losses and primary resonant current waveforms. Discussions about rectifier voltage balancing across the series connected diodes are shown, while the impact of snubber/parallel RC circuit and valve stray parameters are presented.

## Chapter 7 - Design guide line for SRC#

This chapter is showing a design guide line for the SRC# suitable for megawatt, kilovolt and kilohertz range. A general step by step methodology is illustrated and design example for a 10 MW specification is presented.

#### Chapter 8 - Experimental work

Shows two different experimental setups built during this research and a description and test method of each circuit is presented.

#### Chapter 9 - Conclusions and future work

This final chapter summarizes the performed work during this thesis and shows final conclusions and discusses future work.

# **1.4** List of publications

Certain parts of this PhD Thesis have been published or will be published in international scientific journals, conference proceedings, tutorials or are contained in patent applications. The list of publications is shown below:

## Journal papers

- C. Dincan, P. C. Kjaer, Y. Chen, S.M. Nielsen, C. L. Bak, "Analysis of a high power, resonant DC-DC converter for DC wind turbines", IEEE Trans. Power Electron. and Appl, Nov. 2017 (early access). DOI: 10.1109/TPEL.2017.2770322.

- C. Dincan, P. C. Kjaer, Y. Chen, S.M. Nielsen, C. L. Bak, "High power, medium voltage, series resonant converter for DC wind turbines", IEEE Trans. Power Electron. and Appl, Nov. 2017 (early access). DOI: 10.1109/TPEL.2017.2770220.

- C. Dincan, P. C. Kjaer, Y. Chen, S.M. Nielsen, C. L. Bak, E. Sarra, V. Sriram,"Design of a high power, resonant converter for DC wind turbines", IEEE Trans. Power Electron. and Appl, under review.

- A. Tonellotto, E. Maccia, C. Dincan, P. Kjaer, S.M. Nielsen, C.L. Bak, "Control aspects for a high power, resonant converter for wind turbines", IEEE Trans. Power Electron. and Appl, under review.

#### **Conference papers**

- C. Dincan, P. Kjaer, S.M. Nielsen, C.L. Bak, "Soft-switching characterization of medium-voltage IGBT power modules and press-pack diodes in a 1 kHz mega-watt dc/dc resonant converter", Proc. IEEE Eur. Conf. Pow. Electron. and Appl. (EPE2018), under review

- C. Dincan, P. C. Kjaer, Y. Chen, S.M. Nielsen, C. L. Bak, "Analysis and design of a series resonant converter with wide operating range and

minimized transformer ratings", Proc. IEEE Eur. Conf. Pow. Electron. and Appl. (EPE2017), Sept. 2017. DOI: 10.23919/EPE17 ECCEEurope.2017.8099407

- C. Dincan, P. C. Kjaer, Y. Chen, S.M. Nielsen, C. L. Bak, "Selection of DC/DC converter for offshore wind farm with MVDC power collection", Proc. IEEE Eur. Conf. Pow. Electron. and Appl. (EPE2017), Sept. 2017. DOI: 10.23919/EPE17ECCEEurope.2017.8099408

- C. Dincan, P. C. Kjaer, Y. Chen, S.M. Nielsen, C. L. Bak, "Establishment of functional requirements to DC-connected wind turbine and their use in concept selection", Proc. IEEE Int. Conf. on DC Micro. (ICDCM), Jun. 2017. DOI: 10.1109/ICDCM.2017.8001021

- C. Dincan, P. C. Kjaer,"Characterization of diode valve in medium voltage dc/dc converter for wind turbines", Proc. IEEE Eur. Conf. Pow. Electron. and Appl. (EPE2016), Sept. 2016. DOI: 10.1109/EPE.2016.7695404.

- C. Dincan, P. C. Kjaer,"Control and modulation for loss minimization for dc/dc converter for wind turbines", Proc. PCIM, May. 2016.

#### Patent application

• C. Dincan, P. C. Kjaer, "DC-DC Converter and DC-DC conversion method". European Pat. Appli., no. 70059, Filed March. 2017.

Chapter 1. Introduction

# Chapter 2

# Investigation of current state of the art

# Summary

This chapter presents an overview of DC wind farms configurations and DC wind turbine concepts. Afterwards, a catalogue of DC/DC converter topologies is built, categorizing the topologies from switching and isolation type. A survey of university and industrial demonstrators is presented and it illustrates the challenges, specifications and functionalities that the dc/dc converter located in the wind turbine will experience. The end goal of the chapter is to guide toward the optimal topology.

# 2.1 An overview of DC wind farms configurations

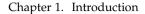

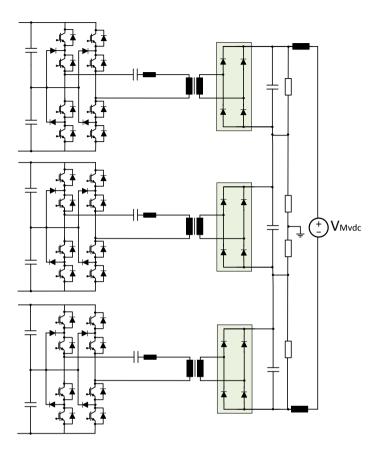

An overview of DC wind farms configurations is illustrated in Fig. 2.1. As discussed in [7] and [5], DC collector grids offer advantages regarding efficiency and investment costs. The DC collector grid layout can be realized through a two conversion stage (Fig. 2.1a) or a single conversion stage concept (Fig. 2.1b). In the two stage concept, the output of the turbine's active rectifier (responsible with the control of generator's power) is increased to medium voltage level, with the help of the dc/dc converter. Outside the turbine, power is collected and stepped up a second time through an offshore substation converter to HVDC level. The single stage concept assumes there is no LVDC/MVDC turbine dc/dc converter, and power is collected at a considerably lower medium voltage level (determined directly by the generator's nominal voltage level) and further stepped-up by substation converter to transmission level. The main disadvantages are increased collection network losses, due to higher currents and increased cables' diameter. The third farm layout (Fig. 2.1c) proposes turbine located dc/dc converters that step up voltage to medium voltage level close to transmission level  $(\pm 100kV_{dc})$ and direct to on shore connection. The solution has the advantage of not requiring an offshore substation converter, but according to [8], the layout will have higher losses compared to the previous two for larger wind farms. The solution would be optimal for small size offshore wind farms and located close to the shore. The forth wind farm layout, discussed in [9]-[11] proposes a radical solution, where in order to reach high voltage transmission levels, without the need of an offshore substation and even no medium voltage turbine converter, it proposes series connection of the wind turbine output converter poles. The concept has been proposed in the early 2000's but presents technical challenges and risks. From technical point, efficiency and easiness of advancing the state of the art, the two stage concept is chosen as the main frame work of this research work.

2.1. An overview of DC wind farms configurations

**Fig. 2.1:** Overview of dc wind farms configurations: a) Turbine with dc/dc converter, MVDC collection and HVDC transmission - two conversion stage concept; b) Turbine with no dc/dc converter, lower MVDC offshore substation and HVDC transmission - one stage concept; c) direct to shore MVDC transmission; d) Series connected wind turbines with HVDC transmission.

## 2.2 An overview of DC wind turbine concepts

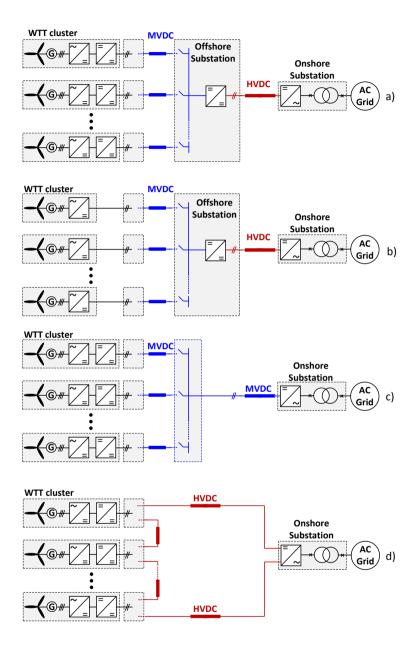

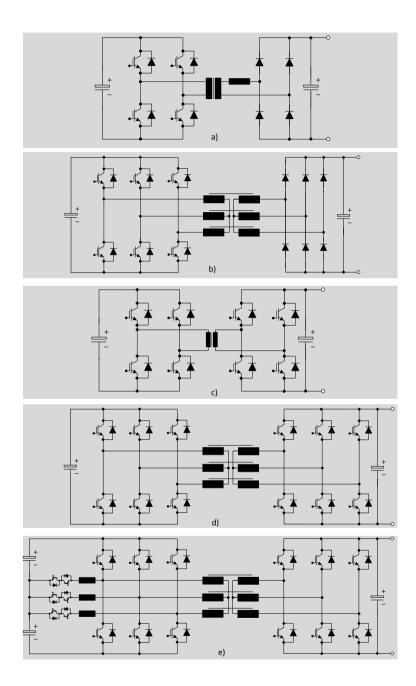

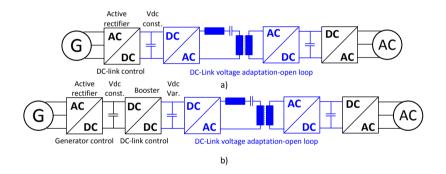

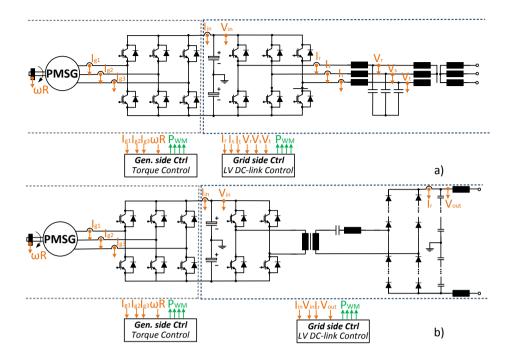

Assuming that state of the art generators are employed, a number of dc wind turbines concepts classified by the number of power electronic stages was identified and shown in Fig. 2.14. This categorization is not considering modular generators [12] and series connected converters as in [13], even if the proposed solutions have some interesting advantages. The first concept (Fig. 2.14a), employing only 1 stage, that of an active rectifer was presented in [14] and has the advantage of low number of components and simplicity. The problem is that maximum output voltage is limited to the generator's nominal voltage level and it has no galvanic separation. Therefore, concept from Fig. 2.14b (presented in [15]) could alleviate this issue, by simply adding non-isolated dc/dc converter, to step up to medium voltage level. Another 2 stage concept ((Fig. 2.14c and presented in [16] suggests a low frequency transformer followed by a passive rectifier. Simplicity and low number of components are advantages, but fixed speed operation and transformer saturation risks are main disadvantages. Another interesting concept, composed of 3 stages ((Fig. 2.14d) was proposed by [9], [17] and employs a matrix converter (AC/AC). Another 3 stage concept (Fig. 2.14e), aims at limiting the disadvantages of (Fig. 2.14c), by incorporating a series connected front to front converter. Further on, a 4 stage concept (Fig.2.14f) that reuses the AC turbine's generator and active rectifie, followed by an isolated high power dc/dc converter. This approach would imply that the main research focus should be on the dc/dc converter, while the rest of components are off the shelf and present low technology risk. It also presents the lowest impact on AC turbine design to turn it into DC turbine. For these reasons it will be the main frame work of this research. A final turbine concept, with 5 converter stages (Fig. 2.14g) incorporates a boost converter between the active rectifier and the isolated dc/dc converter. The topology was suggested in [18], and it assumes that the boost converter is actively controlling the LV side DC link, while the DC/DC converter is operated in open loop in the manner of a DC/DC transformer.

#### 2.2. An overview of DC wind turbine concepts

**Fig. 2.2:** Catalogue of dc wind turbine concepts: a) 1 stage concept with only active rectifier, no galvanic separation; b) 2 stage concept witch active rectifier and non-isolated dc/dc converter; c) 2 stage concept with transformer and passive rectifier; d) 3 stage concept with matrix converter, MF transformer and passive rectifier; e) 3 stage concept with V/Hz controller, medium frequency transformer and passive rectifier; f) 4 stage concept with active rectifier and galvanic isolated dc/dc converter; g) 5 stage concept employing a boost converter between the active rectifier and galvanic isolated dc/dc converter;

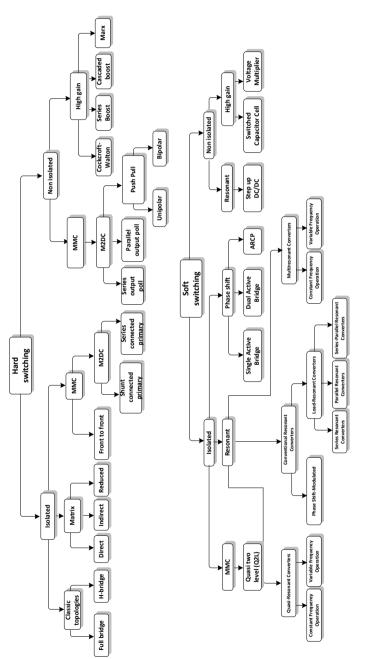

Fig. 2.3: Family tree of hard and soft-switching DC/DC converter topologies

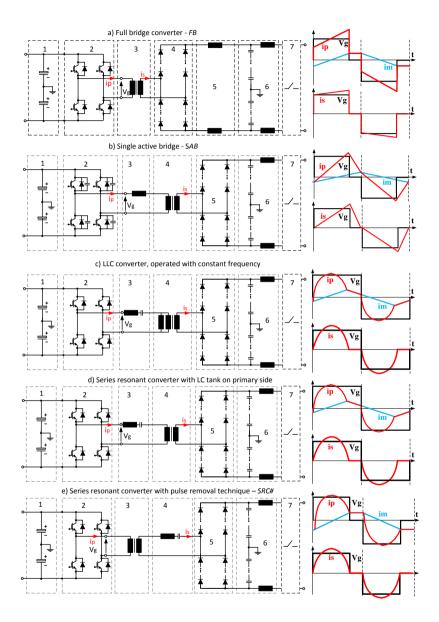

# 2.3 A survey of DC/DC converter topologies

A multitude of DC/DC converter topologies exists, the vast majority being applied for low voltage and low power applications. Up to this point, there are no commercial high power, high voltage DC/DC converters. Nonetheless, corporate research centers, industry and universities have put effort in the last decade in research and demonstration of high power dc/dc converters and a few concepts have been proposed. A simple family tree illustrating the surveyed topologies and organized from switching point of view (hard vs. soft) and galvanic separation (isolated vs. non-isolated) is shown in Fig. 2.3.

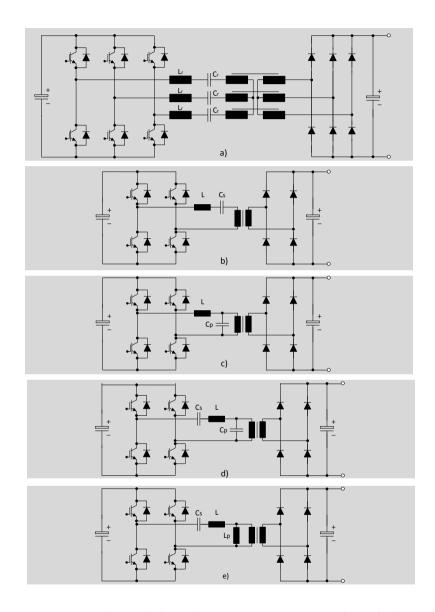

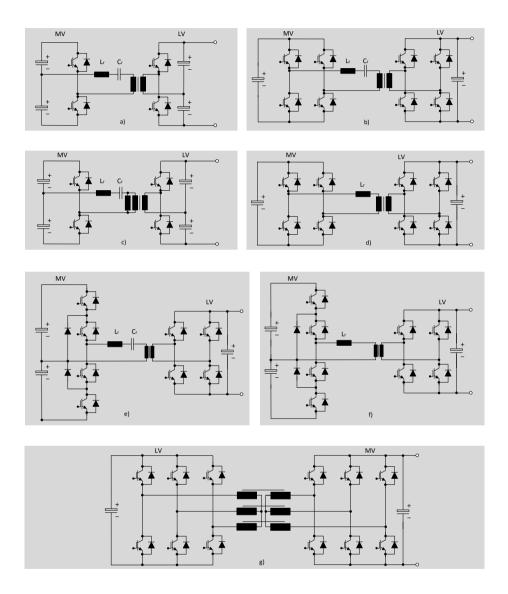

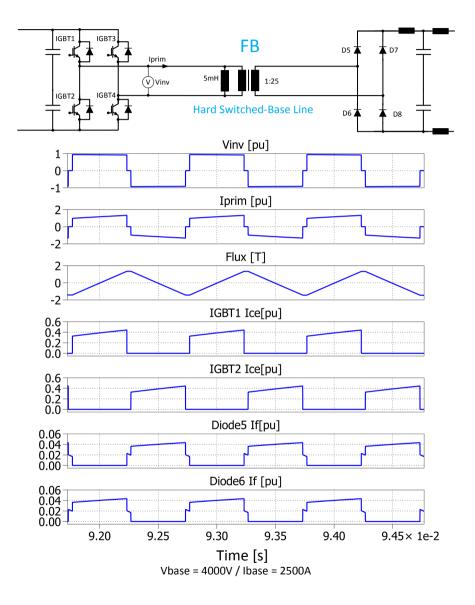

# 2.3.1 Hard-switching topologies

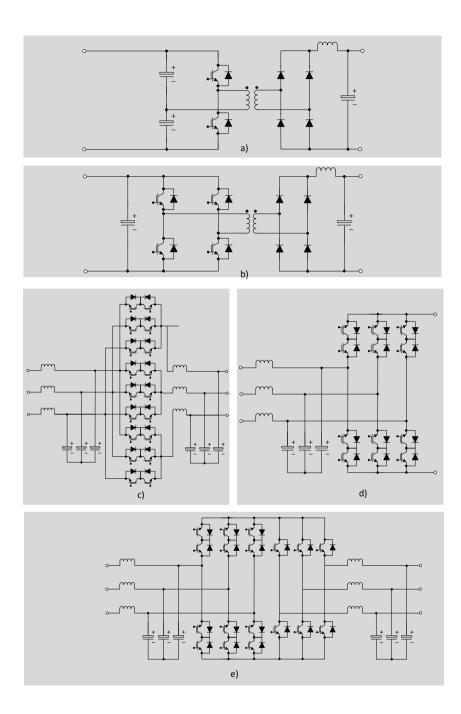

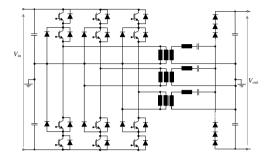

# Isolated: Half bridge and full bridge converter

The classic half and full bridge VSC-converter (2-level or 3-level) (Fig. 2.4) would be the most simple circuitry to be implemented: compared to the AC solution, they require the addition of a passive rectifier and MV-DC link stage. The topologies were investigated in a DC collection grid study in [6] and operation at constant frequency and variable duty cycle was employed. Compared to soft-switching topologies, they require no addition of inverter snubber components, with the penalty of hard-switching losses, turn-off voltage overshoot and high transformer dv/dt. Switching frequency and transformer design are limited, as stray parameters increase linearly with frequency, leading to oversized number of semiconductors only to accomodate voltage overshoots.

# Isolated: Matrix converter

In order to remove the LV side DC-link capacitors, thus decreasing the number of stages, different AC/AC matrix topologies have been investigated in [9], [11], [19], [17] and [20] with the advantages of decreased cost, weight and volume compared to classic back-to-back topologies. In general, matrix topologies have been studied in applications that require small size and high reliability, such as motor drives, aircrafts, marine propulsion and lately offshore wind farms [9]. In [20], a multi-objective design of a modular power converter for DC wind turbines was performed. The direct matrix converter (Fig. 2.4c) is a direct three phase AC-AC converter that does not incorporate DC link capacitors. The indirect matrix converter (Fig. 2.4d) has a DC-link stage, but no capacitors. In both cases, a clamp circuit is required due to the lack of a natural freewheeling path like in the case of classic back-to-back topology. Bidirectional switches are employed in both converter types. Unlike these conventional matrix topologies, the reduced matrix converter was analysed in [9] and the proposed topology is able to convert three-phase AC into a single phase AC. Also in this case, bidirectional switches with two reverse blocking IGBTs and without additional diodes are required.

The main advantages of incorporating a matrix topology are one less conversion stage, low switching losses and presumably a smaller transformer due to higher frequency.

According to the study from [17], compared to the conventional AC/DC/AC converter, it was found that for the range of transformer frequencies from 1 kHz to 20 kHz, the reduced matrix topology has the highest efficiency and the highest power density. On the other, the topology requires additional components for protection against overvoltages that might be destructive for semiconductors.

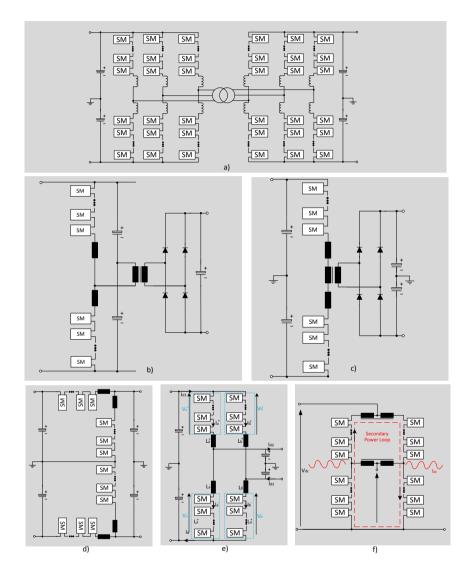

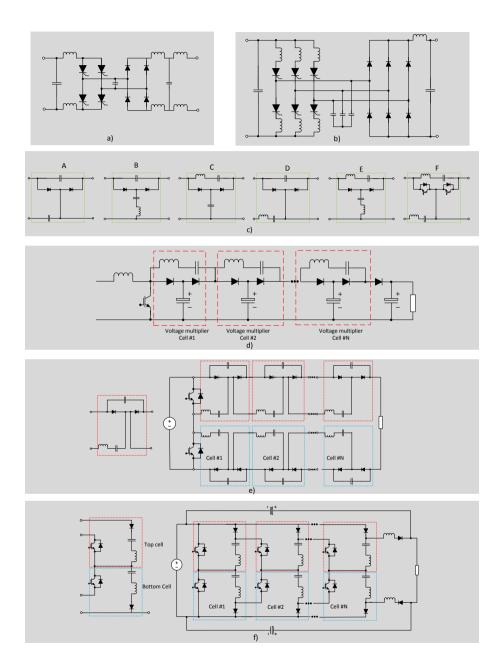

#### Isolated: Front to front modular multilevel converter

The modular multilevel converter (MMC) is commercially productified for HVC transmission converters and MV stations, being interfaced with the AC grid, where two MMC are connected at their DC transmission lines. Galvanic isolation and voltage step-up and step-down is performed through a power frequency (50 Hz/60 Hz) transformer. The conventional Modular Multilevel Converter (MMC, also known as M2C or M2LC) was proposed in a DC/DC configuration in [21]–[24], while incorporating a transformer designed for higher frequency and with the ability of handling short-circuit at the input and output without the need of additional DC or AC circuit breakers for protection. A three-phase solution is suggested in Fig. 2.5a.

A general conclusion of [21] was that the efficiency of the modulation method cannot be drawn because it depends on converter configuration, and depending on the nominal submodule voltage, different switches have to be chosen and this influences the loss calculation. Efficiencies higher than 98% (at 1 kHz) are achievable. On the other hand, the capacitors will occupy large fraction of the volume, motivating the use of the modular converter system for high voltage, high power specifications, such as the offshore substation converter. The large number of submodules will lead to an increase in power circuit and control complexity.

#### Isolated: M2DC - Shunt and series connected primary

Two other isolated-unidirectional variants of M2DC are shown in Fig. 2.5b and c, namely the Isolated Shunt connected primary and Isolated Series connected primary, both investigated in [25]. The topologies were introduced for HVDC interconnection links such as taps (defined as the interface between HVDC transmission line and local MVAC network) to inject/extract relatively small amounts of power. With the inclusion of a transformer and

**Fig. 2.4:** Hard switching DC/DC converter topologies: a) Half bridge ; b) Full bridge; c) Direct matrix; d) Reduced matrix; e) Indirect matrix

square wave operation, taps with high voltage transformation ratios (such as 500 kV to 50 kV)are achievable. The circuit from Fig. 2.5b consists of a single phase leg with the transformer's primary connected between its midpoint and the midpoint of the split DC link capacitors. The Architecture from Fig. 2.5c is a variation of the shunt connected primary, where the transformer primary is connected between two arms and left floating. Other advantages worthy to mention are fault limitation due to galvanic separation, and AC frequency can be optimized to achieve a trade off between transformer size and switching losses.

# Non-isolated: M2DC - Series Output pole and Parallel output pole

Two direct architectures of modular DC/DC converters for HVDC use were studied in [24] and are identified in Fig. 2.5d and e as the series output pole and the parallel output pole. The first topology consists of two phase legs connected in series with each other, while the midpoint of each phase leg connects to a lower DC voltage terminal. The parallel output pole architecture is seen as a DC version of the MMC, where each terminal of the lower DC voltage side is connected to the midpoint of a phase leg consisting of two arms. Because the cell arm has to provide the full DC step, the circuits suffer from an energy drift and require an internal AC rebalancing current to be circulated. The circuits have a poor capacity factor and are suitable for voltage gains up to 2:1, meaning they are more suitable for connecting HVDC links of adjacent voltage level.

# Non-isolated: M2DC - Non-isolated Unipolar Push Pull

The M2DC - A non-isolated unipolar push pull topology was first introduced in [26], [27] and it is illustrated in Fig. 2.5f. The converter consists of four converter arms and two coupled inductors. The circuit was investigated in [28] for MVDC to HVDC connections and it was concluded that it requires a large number of semiconductors. Also, it was considered not to be suitable for high voltage ratios, as the circulating current in the converter becomes high, results in a poor efficiency of 95%. On the other hand, if primary and secondary voltages differ only by a few percent and no galvanic isolation is required, the maximum efficiency exceeds 99%.

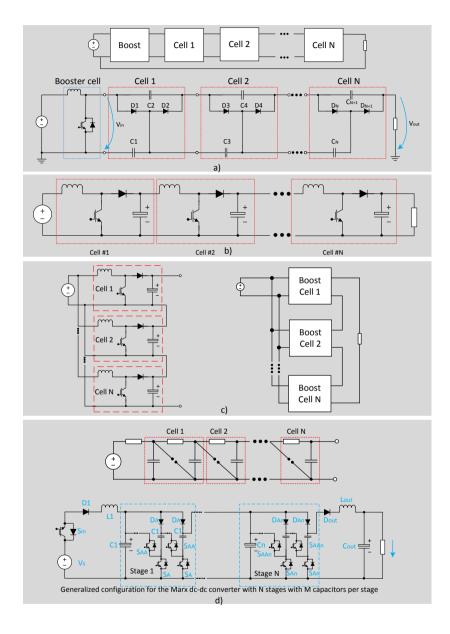

# Non-isolated: Cockcroft Walton

The Cockcroft Walton circuit from Fig. 2.6a is another topology suitable to achieve high voltage DC gains, while offering low weight and volume [29]. It has a simple control, simple structure, it can employ only diodes and it can offer ripple cancellation with symmetrical and double ladder. The topology

**Fig. 2.5:** MMC topologies: a) Isolated Front to front; b) M2SC Isolated Shunt connected primary; c) M2DC Isolated Series connected primary; d) M2DC Non-isolated Series output pole; e) M2DC Non-isolated Parallel output pole; f) M2DC Non-isolated Unipolar Push Pull

is suitable for high voltage and low power applications and has the disadvantages of poor voltage regulation and no galvanic separation.

# Non-isolated: Cascaded and series boost converter

A multiple module high-gain and high-voltage DC-DC topology was proposed in [30] for offshore wind energy systems under the form of cascaded and series boost converter (Fig. 2.6b and c). Results for a low voltageexperimental prototype showed gains of up to 29 p.u. The cascaded configuration connects the output of the first boost converter to the input of the second one, while each converter is rated for the full input power. There are indeed potential for large gains due to the multiplicative effect, but the efficiency losses compound quickly for the same reason. Among other practical issues, the cascaded converter's components suffer from intermediate voltage stress and large current stresses. Control becomes difficult due to the interaction between the converters. The series boost converter configuration connects the input of the converter in parallel and the outputs in series. Both types were investigated for a theoretical 1 MW wind turbine with 1kV and boosted to 132 kV for HVDC transmission. The main issues are that due to the large switch duty ratio, required to achieve high voltage gain, and due to low switching frequency, conductions losses are high and size of passives is not decreased compared to low frequency magnetics. As every cell must be rated for entire output voltage and a fraction of input current, selection of semiconductor devices is not a straight-forward process.

# Non-isolated: Marx converter

A variation of the Marx converter (Fig. 2.6d) was presented in [31], for a highpower application. The topology used IGBTs and diodes and was compared to the conventional boost converter. The main principle is based on charging capacitors in parallel followed by reconnection in series to create higher voltage. Output voltage regulation, high voltage stress and large number of semiconductors and passives are some of disadvantages that don't favour this choice of circuit.

# 2.3.2 Soft-switching topologies

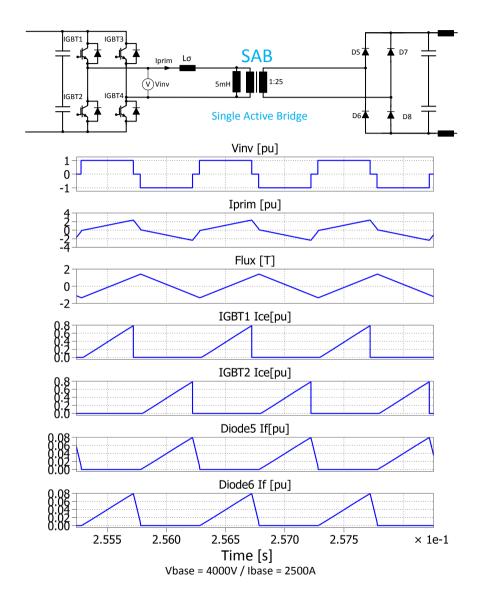

# Isolated: Phase-shift single active bridge

The single active bridge (single and three phase 2 level variant) are depicted in Fig. 2.7a and b. The three phase variant has been initially discussed in [5] and the small signal analysis was performed in [32]. The three phase variant has a simple mode of operation, meaning constant frequency operation, and 120 deg phase shift between each phase leg. The transformer windings will

Fig. 2.6: Hard switching high gain topologies; a) Cockcroft Walton; b) Cascaded boost; c) Series boost; d) Marx converter

experience a square wave excitation and due to the presence of stray inductance or an individual series connected inductance, a phase shift between the primary and secondary windings will occur. A single phase interleaved variant was proposed in [33], [34], leading to lower current and voltage ripple on input and output side dc-link capacitors. According to [5] one disadvantage of the topology, is that it requires a very small stray inductance to transfer a large amount of power, leading to technical constraints on the transformer design. F.ex., to deliver a power level of 20 MVA, the total stray inductance should be below 0.1% of magnetizing inductance, which is hard to achieve in practice for a high power transformer. The topology exhibits a limited zero voltage switching (ZVS) range for the IGBT transistors and high turn-off currents for the rectifier diodes, leading to high losses due to reverse recovery.

#### Isolated: Phase-shift dual active bridge

To improve the drawbacks of the single active bridge, the dual active bridge is further discussed in [5], [35] and illustrated in Fig. 2.7c and d. The topology was initially introduced by [36] for aerospace application. Since then, the concept has gained wide acceptance, especially for high power applications, related to traction, solid-state transformer and commercial EV battery chargers. It consists of two full bridge converters and a medium frequency transformer with a turns ratio of 1:1. As explained in [7], both bridges are modulated in six-step voltage at the transformer terminals. The phase shift  $\alpha$ between the input and output bridge voltages results in a voltage difference across the leakage inductance of the transformer. As the topology is able to achieve soft-switching at turn-on for the active semiconductors for a certain operating range (which can be increased by adding snubbers), it promises increased efficiency and the possibility of employing a three phase medium frequency transformer. To extend the soft-switching boundaries, the auxiliary resonant-commutated poles (ARCP) can be applied, as seen in Fig. 2.7. The auxiliary devices are rated for a fraction of the nominal power and are operated during hard-switching operational points, at low power ratings or unegual dc voltages [7].

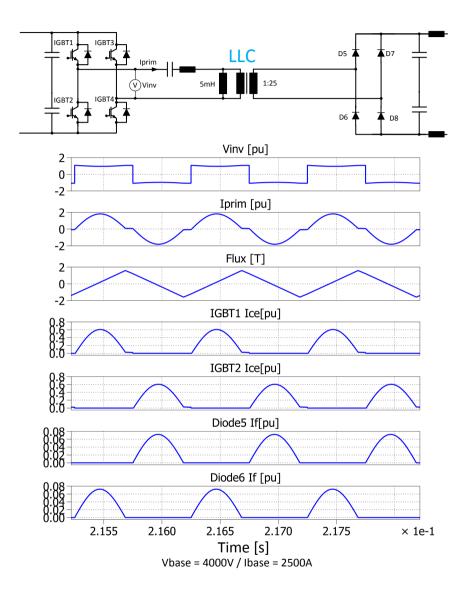

#### **Isolated: Resonant topologies**

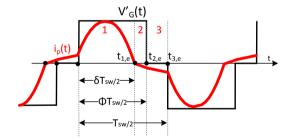

Resonant topologies get their name from the LC tank or variations of it, which is positioned on the inverter or rectifer side, depending on the application. Among the first to discuss resonant converters was [37] and it proposed an improved method of resonant current pulse modulation for power converters. Due to small size and high efficiency requirements for aerospace application, the interest in the philosophy of resonant topologies gained a lot of attention especially in the 80's. Nowadays, resonant converters find applications in a

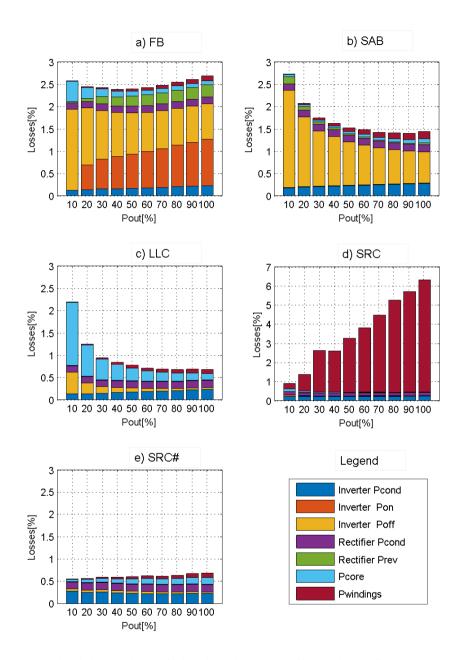

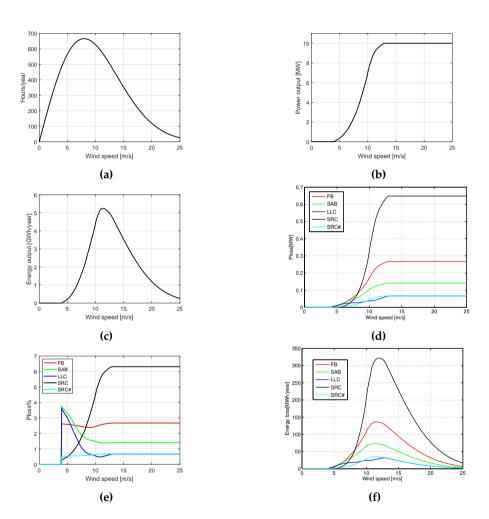

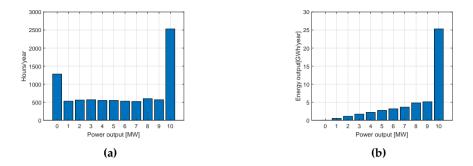

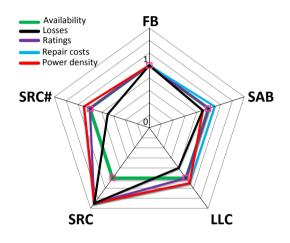

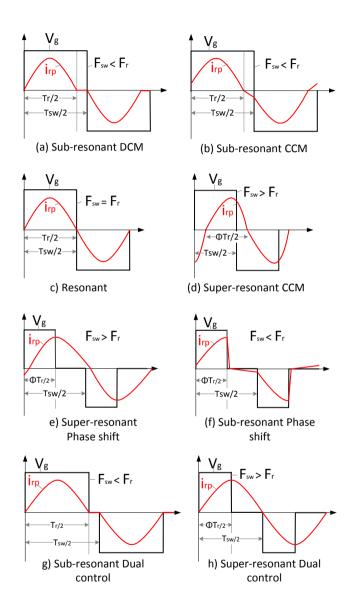

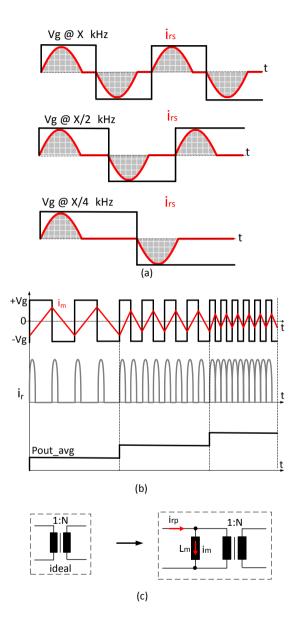

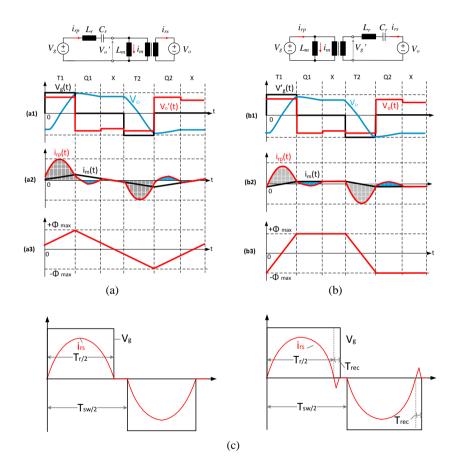

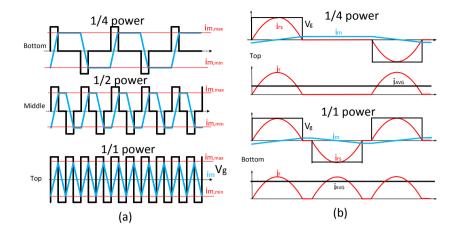

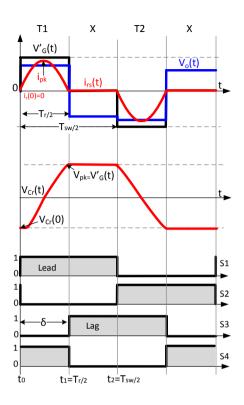

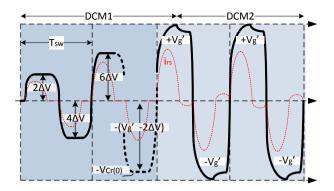

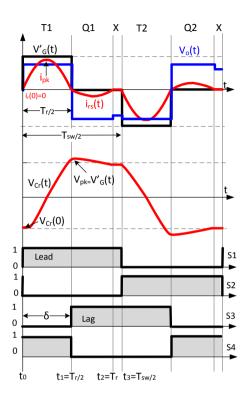

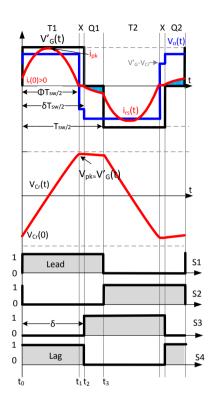

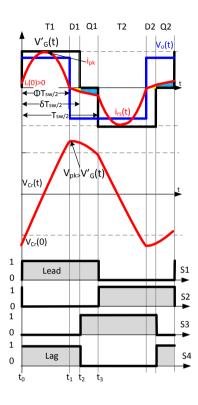

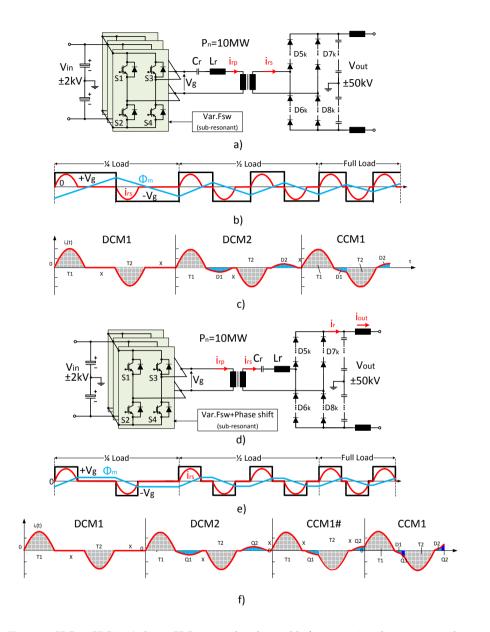

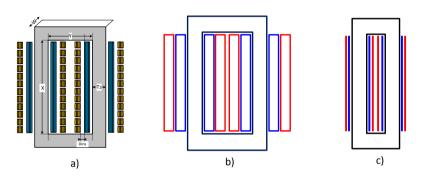

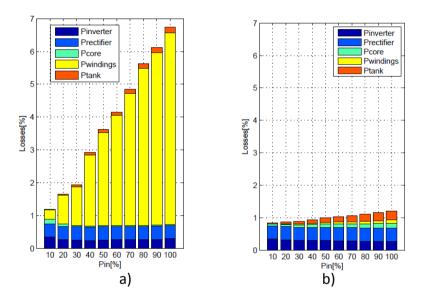

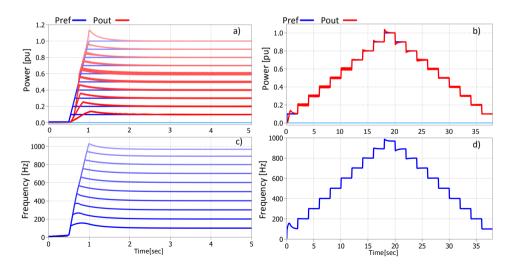

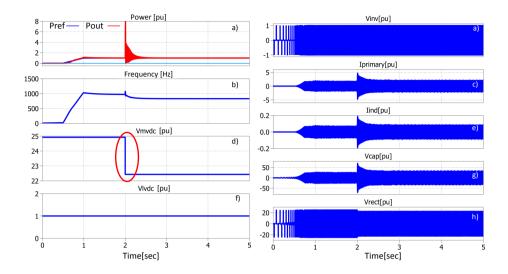

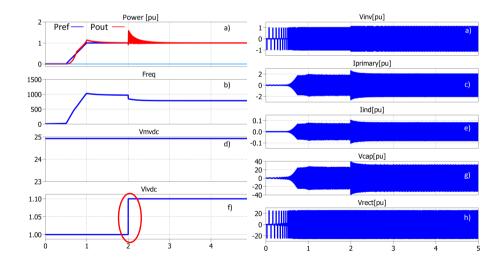

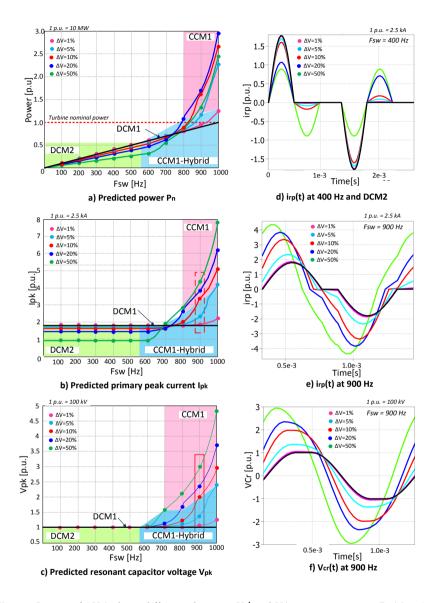

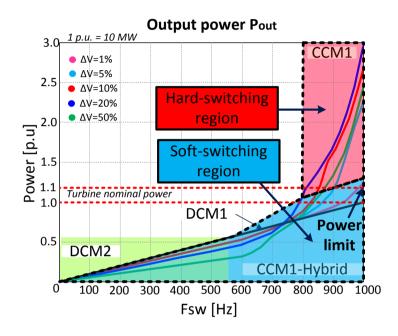

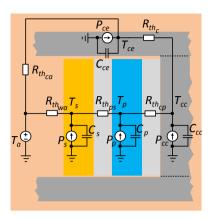

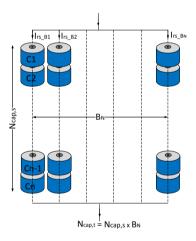

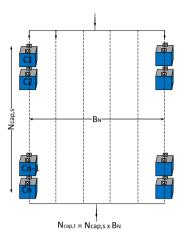

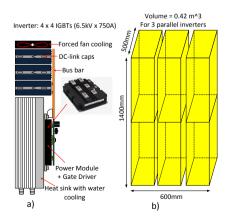

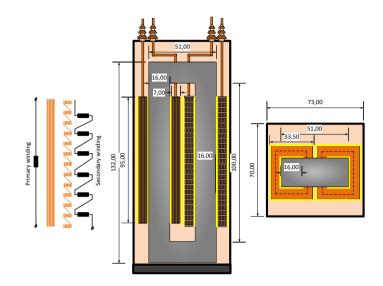

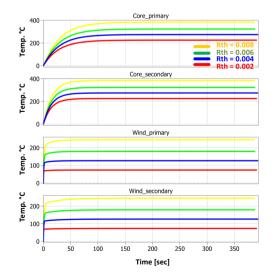

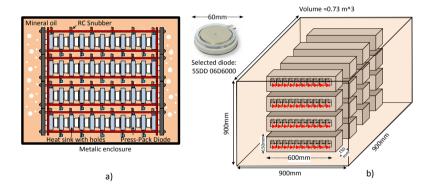

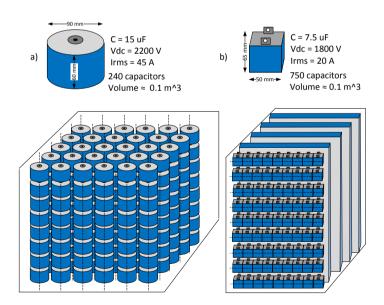

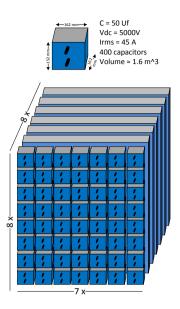

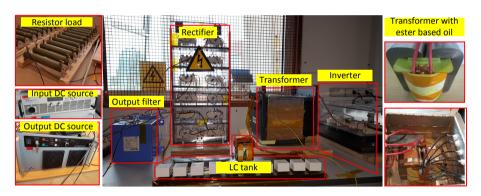

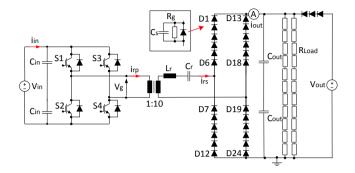

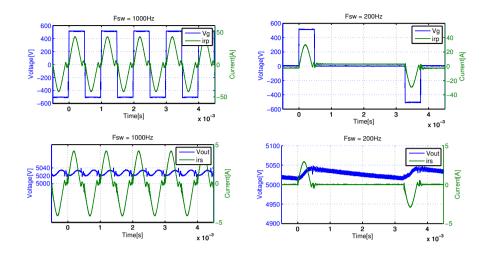

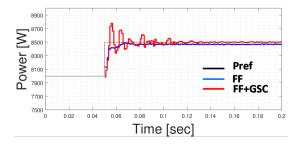

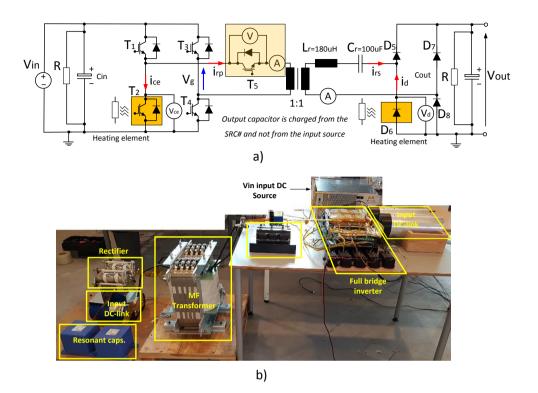

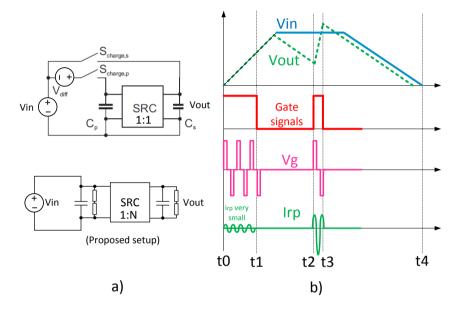

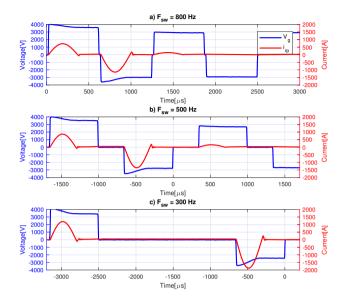

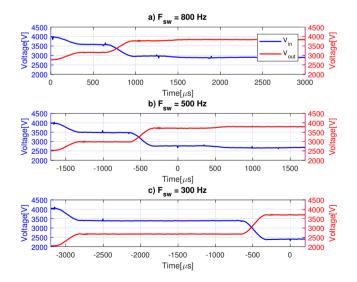

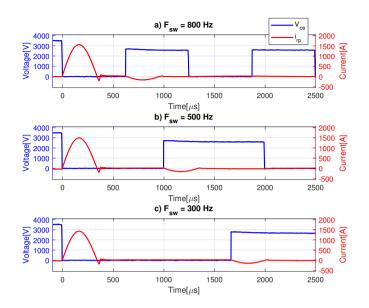

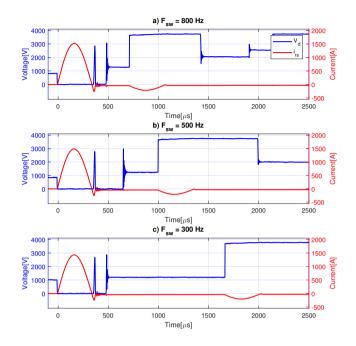

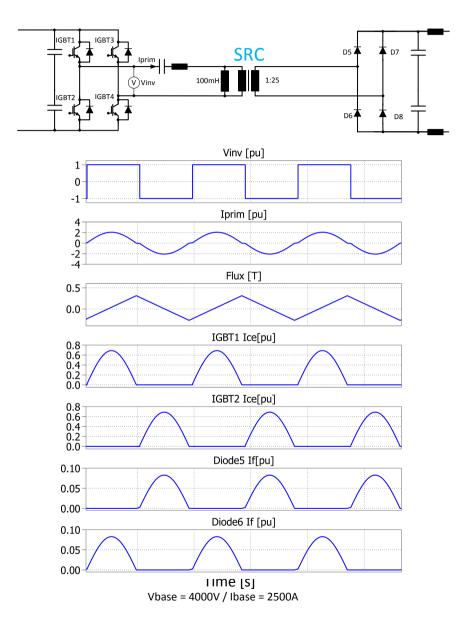

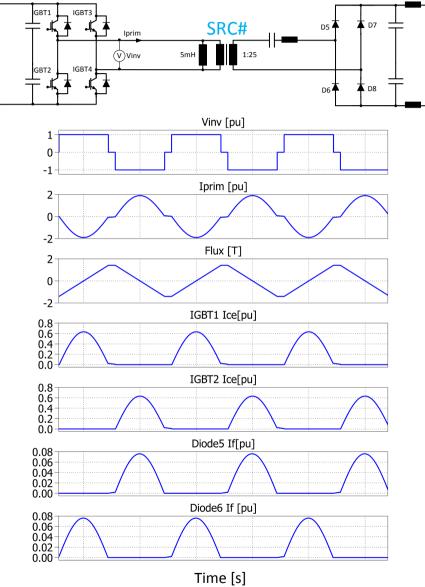

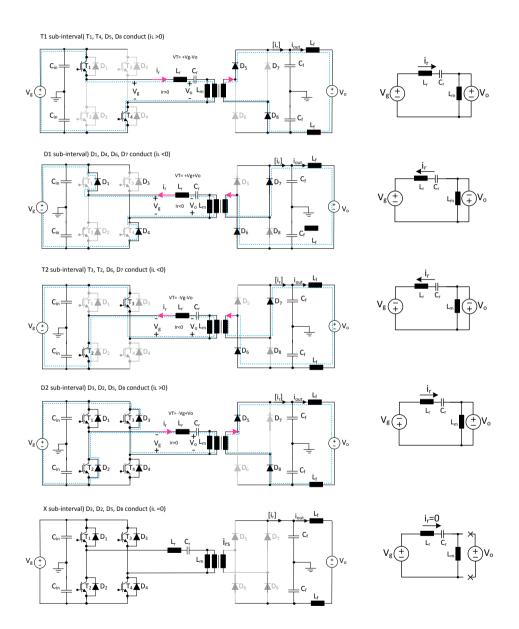

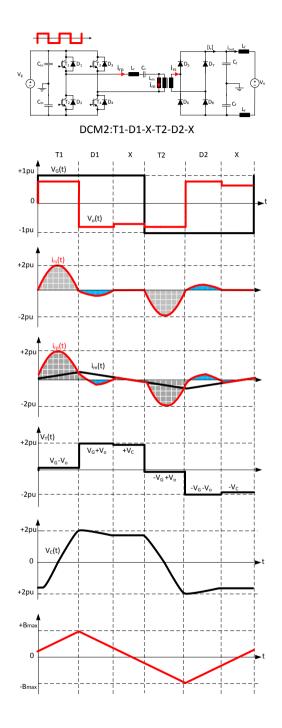

**Fig. 2.7:** Soft switching topologies: a) Phase shift single active bridge; b) Phase shift three phase active bridge; c) Single phase dual active bridge; d) Three phase dual active bridge; e) ARCP dual active bridge