Aalborg Universitet

# An Electrical Method for Junction Temperature Measurement of Power Semiconductor Switches

Baker, Nick

DOI (link to publication from Publisher): 10.5278/vbn.phd.engsci.00098

Publication date: 2016

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Baker, N. (2016). An Electrical Method for Junction Temperature Measurement of Power Semiconductor Switches. Aalborg Universitetsforlag. https://doi.org/10.5278/vbn.phd.engsci.00098

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# AN ELECTRICAL METHOD FOR JUNCTION TEMPERATURE MEASUREMENT OF POWER SEMICONDUCTOR SWITCHES

BY NICK BAKER

**DISSERTATION SUBMITTED 2016**

AALBORG UNIVERSITY DENMARK

# An Electrical Method for Junction Temperature Measurement of Power Semiconductor Switches

by

**Nick Baker**

Supervisors: Prof. Stig Munk-Nielsen and Prof. Francesco Iannuzzo

AALBORG UNIVERSITY DENMARK

| Dissertation submitted: | April 6 <sup>th</sup> 2016                                |

|-------------------------|-----------------------------------------------------------|

| PhD supervisor:         | Prof. Stig Munk-Nielsen<br>Aalborg University, Denmark    |

| PhD committee:          | Professor Josep Guerrero (chairman)<br>Aalborg University |

|                         | Dr. Gernot J. Riedel<br>ABB Cooperate Research            |

|                         | Professor Philip Andrew Mawby<br>University of Warwick    |

| PhD Series:             | Faculty of Engineering and Science, Aalborg University    |

ISSN (online): 2246-1248 ISBN (online): 978-87-7112-548-1

Published by: Aalborg University Press Skjernvej 4A, 2nd floor DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Nick Baker

Printed in Denmark by Rosendahls, 2016

# **Copyright Statement**

This thesis has been submitted for assessment in partial fulfillment of the PhD degree. The thesis is based on the submitted or published scientific papers which are listed below. Parts of the papers are used directly or indirectly in the extended summary of the thesis. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty.

**Thesis Title:** An Electrical Method for Junction Temperature Measurement in Power Semiconductor Switches

Name of PhD Student: Nick Baker

Name of Supervisors: Professor Stig Munk-Nielsen and Professor Francesco Iannuzzo

### List of Publications:

- N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Junction temperature measurements via thermo-sensitive electrical parameters and their application to condition monitoring and active thermal control of power converters," in 39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), pp. 942-948, 10-13 Nov. 2013.

- N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods," in IEEE Industrial Electronics Magazine, vol.8, no.3, pp. 17-27, Sept. 2014.

- N. Baker, L. Dupont, Y. Avenas, F. Iannuzzo, S. Munk-Nielsen, "Experimental Evaluation of IGBT Junction Temperature Measurement via a Modified VCE Method with Series Resistance Removal," in 9<sup>th</sup> International Conference on Integrated Power Systems (CIPS 2016), to be published, March 2016.

- N. Baker, S. Munk-Nielsen, M. Liserre, F. Iannuzzo, "Online junction temperature measurement via internal gate resistance during turn-on," in 2014 16th European Conference on Power Electronics and Applications (EPE'14-ECCE Europe), pp. 1-10, 26-28 Aug. 2014.

- N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "Online junction temperature measurement using peak gate current," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1270-1275, 15-19 March 2015.

- N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "IGBT Junction Temperature Measurement via Peak Gate Current," in IEEE Transactions on Power Electronics, vol.31, no.5, pp. 3784-3793, May 2016.

- N. Baker, L. Dupont, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "Experimental evaluation of IGBT junction temperature measurement via peak gate current," in 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), pp. 1-11, 8-10 Sept. 2015.

- 8. N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current," in review for IEEE Transactions on Power Electronics.

# Acknowledgements

Firstly, I am eternally grateful to Professor Stig Munk-Nielsen for giving me the chance to work at Aalborg University. Thank you to Professor Marco Liserre for allowing me the opportunity to work on this PhD in Power Semiconductor Devices, and to Professor Stig Munk-Nielsen and Professor Francesco Iannuzzo for agreeing to continue supervision of the project.

I must also extend my sincerest gratitude to Dr. Laurent Dupont and Associate Professor Yvan Avenas for their incredibly helpful advice throughout the PhD period. In particular, their knowledge in the topic of junction temperature measurements was invaluable in the beginning stages of this research.

Furthermore, I would like to make a special thank you to Dr. Laurent Dupont for inviting me for a 6 month research visit at the SATIE Laboratory in Versailles, France. His meticulous approach and detailed planning ensures that experimental quality under his supervision is second to none.

I would also like to thank Iain Russell and Alan James for the many great debates in The Wharf. Finally, I thank my family and my girlfriend for their support during this period.

I wish all my colleagues and friends from the CORPE and IEPE projects at Aalborg University all the best for the future.

# Abstract

Power semiconductor switches are critical components in power electronic converters and operate in thermally stressful environments. The junction temperature of a power semiconductor directly influences its power loss and is intrinsically linked to numerous failure mechanisms. Knowledge of this temperature is therefore important for optimal operation and for reliability reasons. If the junction temperature is known during the operation of a converter, real-time condition monitoring and active thermal control systems could be developed to improve system reliability.

Performing direct measurements of junction temperature is difficult since the power semiconductor is generally encapsulated inside an array of packaging materials. Alternatively, the electrical behaviour of a semiconductor largely depends on temperature. If this relationship is known, the electrical parameters of the device can be monitored and used to estimate the junction temperature. These are known as Temperature Sensitive Electrical Parameters (TSEPs) and are one way to carry out non-invasive, real-time junction temperature measurements on fully packaged devices.

Nevertheless, successful implementation of these techniques during the normal operation of a power semiconductor is thus far limited. Often holding back their use is the need to compensate for inherent fluctuations caused by a constantly changing electrical environment (or alternatively requiring interruption to normal operation to force fixed electrical conditions), and significant uncertainty over accuracy. As a result, this PhD aims to develop new methods, or improvements to existing methods, for junction temperature measurement via TSEPs during the operation of power semiconductor switches.

In Chapter 1, the state-of-the-art in the topic of junction temperature measurement is introduced. A literature review of TSEPs investigated for use in operating power semiconductor switches is then provided. From this, several implementation issues are identified and used to formulate technical objectives for the PhD thesis.

Chapter 2 introduces the first original contribution of the thesis. Two TSEP-based methods for junction temperature measurement, unpublished in scientific literature before the commencement of the PhD, are presented. The measurement principles are explained, and experimental validation is provided on Insulated-Gate-Bipolar-Transistors (IGBTs). The foremost advantages in the presented TSEPs are that they are measured without interruption to normal IGBT operation, and do not require compensation for varying load current conditions. The primary method presented is referred to as the Peak Gate Current (I<sub>GPeak</sub>) method, which is selected for further examination in Chapter 3.

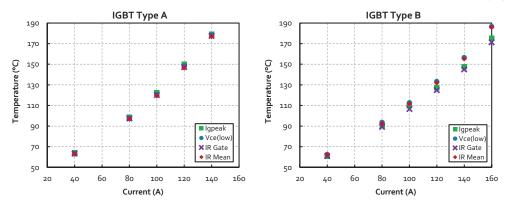

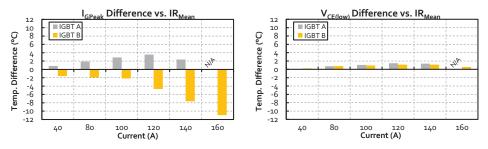

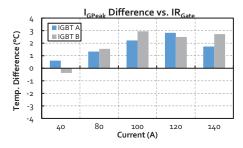

In Chapter 3, the second scientific contribution of the thesis is provided. Here, the accuracy of the  $I_{GPeak}$  method on IGBTs is extensively examined using direct measurements of junction temperature from an Infra-Red camera. The validation is performed on IGBT dies with differing geometry, as well as IGBTs in both healthy and degraded conditions. Finally, IGBTs in a paralleled configuration are investigated. These results in terms of accuracy are compared with a traditional TSEP method commonly found in prior art.

Finally, Chapter 4 provides a summary of the work, along with the main scientific contributions and limitations of the PhD.

# **Thesis Structure**

This thesis is presented as a collection of papers, however an extended summary is provided comprising of 4 chapters. The relevant papers for each chapter are listed as follows, and are included in Appendix C of the extended summary.

# Chapter 1:

- A. N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Junction temperature measurements via thermo-sensitive electrical parameters and their application to condition monitoring and active thermal control of power converters," in 39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), pp. 942-948, 10-13 Nov. 2013.

- B. N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods," in IEEE Industrial Electronics Magazine, vol.8, no.3, pp. 17-27, Sept. 2014.

- C. N. Baker, L. Dupont, Y. Avenas, F. Iannuzzo, S. Munk-Nielsen, "Experimental Evaluation of IGBT Junction Temperature Measurement via a Modified VCE Method with Series Resistance Removal," in 9<sup>th</sup> International Conference on Integrated Power Systems (CIPS 2016), to be published, March 2016.

# Chapter 2:

- D. N. Baker, S. Munk-Nielsen, M. Liserre, F. Iannuzzo, "Online junction temperature measurement via internal gate resistance during turn-on," in 2014 16th European Conference on Power Electronics and Applications (EPE'14-ECCE Europe), pp. 1-10, 26-28 Aug. 2014.

- E. N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "Online junction temperature measurement using peak gate current," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1270-1275, 15-19 March 2015.

- F. N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "IGBT Junction Temperature Measurement via Peak Gate Current," in IEEE Transactions on Power Electronics, vol.31, no.5, pp. 3784-3793, May 2016.

# Chapter 3:

G. N. Baker, L. Dupont, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "Experimental evaluation of IGBT junction temperature measurement via peak gate current," in 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), pp. 1-11, 8-10 Sept. 2015. H. **N. Baker**, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current," in review for IEEE Transactions on Power Electronics.

Chapter 4:

N/A

# Contents

| I. Introduc | tion                                                                       | 1  |

|-------------|----------------------------------------------------------------------------|----|

| 1.1. Rel    | iability Challenges in Power Electronics                                   | 1  |

| 1.1.1.      | Power Converter Failures                                                   | 1  |

| 1.1.2.      | Failures in Power Semiconductor Devices                                    | 1  |

| 1.1.3.      | Benefits of Accurate T <sub>j</sub> Knowledge for Power Module Reliability | 3  |

| 1.1.4.      | Junction Temperature Estimation in Power Electronic Converter Design       | 4  |

| 1.1.5.      | Thesis Scope                                                               | 5  |

| 1.2. Mai    | in methods of real time junction temperature measurement                   | 5  |

| 1.2.1.      | Direct Temperature Measurement Methods                                     | 7  |

| 1.2.2.      | Temperature Sensitive Electrical Parameters (TSEPs)                        | 9  |

| 1.3. Lite   | erature Review of Online TSEP Proposals                                    | 11 |

| 1.3.1.      | Classical TSEPs                                                            | 11 |

| 1.3.2.      | Static Characteristic                                                      | 13 |

| 1.3.3.      | Dynamic Characteristics                                                    | 15 |

| 1.4. Add    | ditional TSEP Implementation Issues                                        | 15 |

| 1.4.1.      | Calibration Requirements                                                   | 16 |

| 1.4.2.      | Accuracy of TSEP Measurements                                              | 17 |

| 1.5. PhI    | O Objectives                                                               | 18 |

| 1.5.1.      | Research Questions                                                         | 18 |

| 1.5.2.      | Technical Objectives                                                       | 19 |

| II. Propose | d TSEP Measurement Methods                                                 | 20 |

| 2.1. Inte   | ernal Gate Resistance - R <sub>Gint</sub>                                  | 20 |

| 2.2. Pea    | k Gate Current (I <sub>GPeak</sub> ) Measurement Principle                 | 22 |

| 2.2.1.      | I <sub>GPeak</sub> Measurement – Peak Detector Circuit                     | 24 |

| 2.2.2.      | Gate Driver Performance Compensation                                       | 26 |

| 2.2.3.      | High Power Verification of Measurement Concept                             | 27 |

| 2.2.4.      | Sensitivity Variation between Modules                                      | 29 |

| 2.2.5.      | Gate Driver Requirements for Implementation                                | 31 |

| 2.3. Ten    | nperature Measurement using Gate Voltage Integration                       | 34 |

| 2.3.1.      | Gate Charging Constant                                                     | 34 |

| 2.3.2.      | Reasons for discontinuing research                                         | 35 |

| 2.4. Cha    | apter Summary                                                              | 36 |

| III.  | Exp   | erimental Validation of I <sub>GPeak</sub>                            |

|-------|-------|-----------------------------------------------------------------------|

| 3.1.  | Μ     | otivation for Temperature Measurement Validation                      |

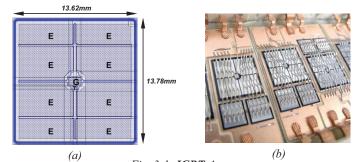

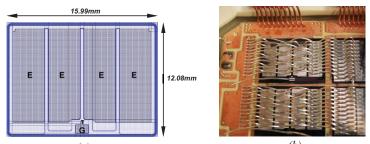

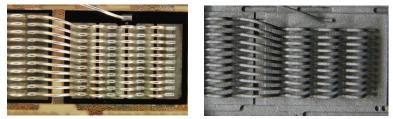

| 3.2.  | IC    | BTs under test                                                        |

| 3.3.  | In    | fra-Red Thermal Measurements                                          |

| 3.4.  | Т     | est Bench Operation                                                   |

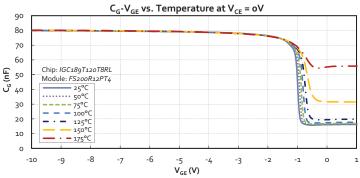

| 3.5.  | G     | ate Capacitance Stability at $V_{CE} = 0V$                            |

| 3.6.  | R     | esults                                                                |

| 3     | .6.1. | Definition of 'Junction Temperature'                                  |

| 3     | .6.2. | Location of R <sub>Gint</sub>                                         |

| 3     | .6.3. | Calibration                                                           |

| 3.    | .6.4. | Dissipation Results: Single IGBTs45                                   |

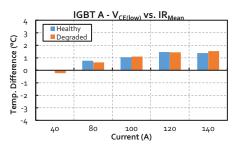

| 3.    | .6.5. | Dissipation Results: Degraded IGBTs – Partial Bondwire Removal        |

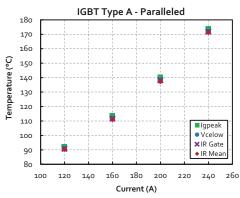

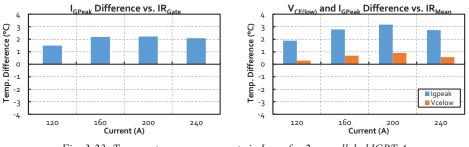

| 3.    | .6.6. | Dissipation Results: Paralleled IGBTs50                               |

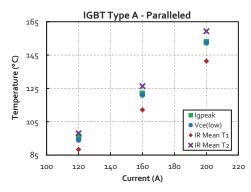

| 3.    | .6.7. | Dissipation Results: Paralleled IGBTs with Temperature Disequilibrium |

| 3.7.  | С     | hapter Summary                                                        |

| IV.   | Con   | clusion                                                               |

| 4.1.  | С     | ontributions                                                          |

| 4.2.  | Li    | mitations                                                             |

| 4.3.  | Fı    | ıture Work                                                            |

| V. B  | iblio | graphy                                                                |

| VI.   | App   | endix A – IGBT Die Datasheets                                         |

| VII.  | App   | endix B – Dissipation Results Table72                                 |

| VIII. | Арр   | endix C – Attached Collection of Papers73                             |

# I. Introduction

This section will outline the background and motivation for junction temperature measurements in power semiconductors. A literature review of the state-of-the-art for junction temperature measurements will be provided. In particular, problems and challenges associated with using Temperature Sensitive Electrical Parameters will be identified and described. From this, objectives for the PhD Thesis are formulated.

# 1.1. Reliability Challenges in Power Electronics

# 1.1.1. Power Converter Failures

Power electronic converters are used to provide high efficiency power conversion in a variety of industries and can be found in many renewable, automotive, aerospace and railroad systems. These applications are often safety critical and place stringent demands on reliability. For example, unexpected failures may lead to severe accidents in automotive or aerospace applications, while unscheduled maintenance or downtime can induce high economic costs for renewable power plants. In numerous cases, power electronic converters are also required to operate in thermally stressful environments, such as in electric vehicles where ambient operating temperatures may exceed 150°C.

The anticipation of failures in power electronic converters is difficult, but is of great interest so that the operation of a system can be halted before a breakdown occurs and prompt maintenance scheduled. Taking the case of a photovoltaic (PV) power plant, the system can be simplified into two distinct units: the solar panels/modules, and the power inverter. A complete breakdown in either of these units can cause significant downtime in the system. Nevertheless, multiple solar module failures can often be tolerated and not lead to a breakdown of the entire array, whereas a component failure in the inverter can lead to downtime in the entire system.

The relevance of inverter reliability is further heightened with solar panel/module manufacturers frequently offering warranties of up to 20-years (perhaps covering the life of the power plant), while warranties for solar inverters rarely reach the 10-year mark [1]. Although the market competition between PV inverter manufacturers has traditionally focused on the efficiency of their product, a failure that induces a downtime of just a few days can easily negate the yield attained through a 1% efficiency improvement. Oversizing the inverter, or introducing redundancy into the inverter system is one option to improve reliability, however this is often not economical.

# 1.1.2. Failures in Power Semiconductor Devices

Power semiconductors are a key element in converter systems. In a 2011 industry-based survey [2], 93% of respondents placed reliability as a primary issue in the field of power electronic converters. Power semiconductors were ranked as one of the most fragile components, with 31% of respondents considering them as the weakest link. This was followed by capacitors and gate drivers at under 20% and 15% respectively.

The junction temperature  $(T_j)$  and temperature cycling conditions form a considerable influence on power semiconductor reliability and performance. Failure mechanisms are generally separated into two categories: semiconductor-related failure mechanisms and package-related failure mechanisms. Wu *et al.* [3] define semiconductor-related failure mechanisms with two further groupings: short-circuit and open-circuit failures. Many of these failures are due to abnormal conditions rather than longer term wear-out fatigue induced by temperature cycling. Nevertheless, some semiconductor failure mechanisms such as latch-up (loss of control of an IGBT/MOSFET from the gate), leading to a short circuit, can be provoked through the accumulation of thermal fatigue [4].

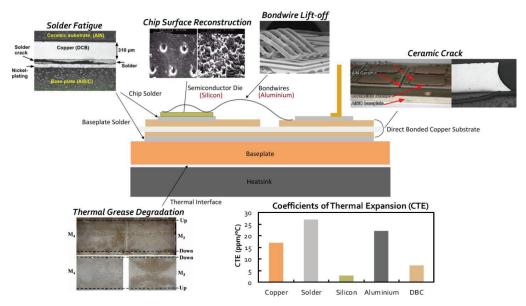

The silicon semiconductor die is usually housed in a structure to form what is known as a power module. It is in these packaging materials that failures are most frequently observed. Figure 1-1 displays a typical structure of a traditional wire-bonded power module along with some of the common failure locations. These failures are primarily attributed to the differences in the coefficients of thermal expansion (CTE) of the various materials of the semiconductor die and package construction, combined with the temperature swings they experience [5].

Fig. 1-1: Cross-section and common degradation locations of a traditional wire-bonded power module [6][7][8][9]

One of the largest mismatches in CTE is between the semiconductor die (silicon), and the bondwires and surface metallisation (aluminium) [5]. This mismatch is exacerbated due to the bondwire being bonded directly onto the surface of the die. Therefore, the power dissipation in the semiconductor, along with the ohmic self-heating of the bondwire, induce large temperature swings in the materials. Repeated thermal cycling then leads to stress that results in degradation of the bondwires and eventual lift-off from the semiconductor die itself.

The failure of a single or small number of bondwires can alter the current distribution in the module and increase ohmic resistances. If operation of the device is not halted before a suitable threshold, catastrophic failure can occur that can manifest itself in a number of ways. This could include melting of the remaining bondwires, thermal runaway in paralleled semiconductors, or triggering of parasitic events that lead to device destruction.

Outside of these categories, some system level degradations can also have a large impact on power semiconductor health. For example, Perpina *et al.* show how thermal grease displacement occurs during thermal cycling tests – leading to a deteriorated thermal conductivity between the heatsink and the power module [9]. Intermittent misfiring of the gate driver can also lead to catastrophic failures or repeated short periods of overstress [10].

# 1.1.3. Benefits of Accurate T<sub>j</sub> Knowledge for Power Module Reliability

An active area of research in power module reliability is the development of condition monitoring systems. Much research has focused on monitoring electrical parameters that indicate degradation. In particular, the collector-emitter voltage ( $V_{CE}$ ) at high current in IGBTs [11][12][13], and the evolution a module's thermal resistance ( $R_{th}$ ) [8][14][15][16] have been studied since the 1990s.

While these parameters readily observe degradation in laboratory conditions, they are ultimately influenced by numerous failure mechanisms. As such, they are difficult to use as a standalone parameter to monitor device degradation. This is especially the case for the  $V_{CE}$  at high current, which can be effected by junction temperature, gate oxide integrity, bond-wire fatigue, quality of electrical connections, and surface metallisation reconstruction. This manifests in aging trends for  $V_{CE}$  that are not consistent: increases of 5%, 7% and 20% before module failure have been reported in literature [11][13][17], while decreases of up to 25% were present in other studies [18][19].

As a result, interpreting parameters of this nature requires a thorough understanding of the relationship between the parameter, health condition, and operational profile. As a first principle, accurate real-time junction temperature knowledge can help identify which failure mechanism is dominant in the device, or more precisely determine when a degradation parameter signals a critical level of degradation.

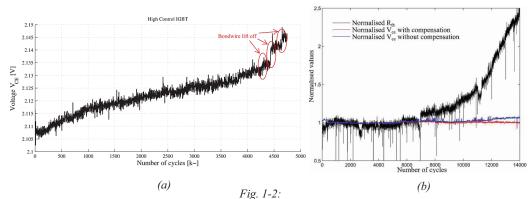

Illustrating this point, Fig. 1-2a displays a commonly reported trend in the  $V_{CE}$  as an IGBT is subject to an accelerated aging test. The gradual increase of  $V_{CE}$  could be due to aluminium reconstruction increasing the ohmic sheet resistance, or degradation in the thermal path contributing to a gradual increase in T<sub>j</sub>. On the other hand, sharp step increases in the V<sub>CE</sub> can often be seen when a bond wire lifts off from the IGBT. Therefore, knowledge of T<sub>j</sub> is necessary to reliably assess which failure mechanism is causing the increase in V<sub>CE</sub>. In fact, some aging studies that monitor the V<sub>CE</sub> attempt to compensate for T<sub>j</sub> using electrothermal models (shown in Fig. 1-2b) [20], while others include a temperature sensitive parameter for T<sub>j</sub> measurement in laboratory accelerated aging test benches [16][17][21][12].

Outside of the traditional  $V_{CE}$ , several alternative approaches have been proposed for damage evaluation in power modules. Principally, these indicators involve switching transients or

parasitic ringing variations in the device [4][23][24][25][26]. Nevertheless, these parameters are also intrinsically linked to junction temperature.

(a) Increase of  $V_{CE}$  during accelerated aging test: step change indicates bondwire lift-off [22] (b)  $V_{CE}$  increase during aging test with junction temperature compensation (red) and without (blue) [20]

Finally, precise knowledge of the amplitude and frequency of junction temperature swings could lead to better utilisation of model based prognostic systems that predict the remaining life of a power module [27]. This information could also be used to develop thermal control algorithms that regulate power losses to reduce thermal stress, and prolong module lifetime, when operating in a degraded condition [28].

#### 1.1.4. Junction Temperature Estimation in Power Electronic Converter Design

The junction temperature is therefore a necessary consideration in the design of a converter system to ensure optimal reliability and operation. At a minimum, it must be guaranteed that  $T_j$  does not exceed the specified maximum limits under all operating conditions. Traditionally,  $T_j$  estimation has been performed using analytical calculations; in fact, some semiconductor manufacturers provide software tools for this purpose [29]. These calculations are usually based on datasheet values for both the electrical and thermal characteristics of the power module.

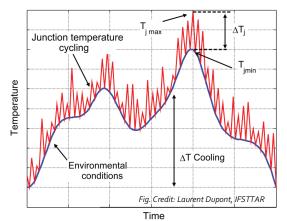

The junction temperature variation of a power semiconductor is generally a result of the power losses resulting from the application mission profile, in addition to changes in environmental conditions. Fig. 1-3 demonstrates an idealised evolution of  $T_j$  in a power module over time. The smaller and faster  $T_j$  cycles may be caused by the demands of the application, while the larger and slower cycles are a result of the environmental conditions.

An average junction temperature could be determined using one-dimensional stationary thermal models and neglecting thermal capacitances. If non-stationary phenomena are accounted for, it is possible to estimate the junction temperature swing,  $\Delta T_j$ , and then the maximum junction temperature,  $T_{j(max)}$ , which must be respected for safe operation. Otherwise, a safety margin for the maximum junction temperature ripple must be included in the design of the cooling system. As a result, there is interest in developing more complex models for real-time  $T_j$  estimation [30].

Although these modelling techniques are widely used, there are several questions regarding their accuracy. Bruckner and Bernet [31] attempt to experimentally verify the accuracy of these estimations on IGBTs in a three-level voltage source inverter. They find that the estimated  $T_j$  is typically higher than the measured temperature via an infra-red camera – with realistic errors in the region of ±11%. This uncertainty can lead to an oversizing of cooling systems to ensure a proper level of reliability, at the expense of increased volume, weight and cost. Furthermore, the thermal and electrical characteristics of a power module alter over the lifetime of a converter [9] [32]; consequently, these calculations are not valid during the entire lifecycle of the module.

Fig. 1-3: Typical idealised evolution of junction temperature in a power module over time

#### 1.1.5. Thesis Scope

Since model based junction temperature estimation is prone to error, an accurate method for real-time junction temperature measurement would be beneficial. Nevertheless, direct measurements of junction temperature in power semiconductors are problematic: access to the semiconductor die is blocked by the packaging materials.

Consequently, this thesis focuses on a group of indirect measurements known as Temperature Sensitive Electrical Parameters (TSEPs). Here, the temperature dependent electrical behaviour of the semiconductor is used as the temperature sensor. The measurements are therefore non-invasive. This work focuses on developing TSEP-based methods for power semiconductor switches, which encompasses both IGBTs and MOSFETs.

#### 1.2. Main methods of real time junction temperature measurement

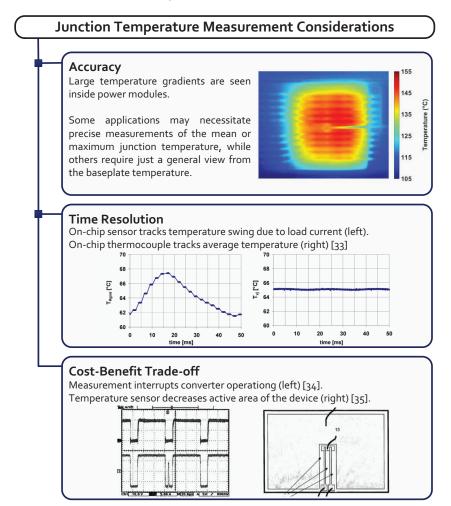

Sensing junction temperature during converter operation is difficult, and the selection of a measurement method should be made with respect to the application. The main dilemmas in the selection or design of a temperature measurement system are displayed in Fig. 1-4 and entail:

- Accuracy:

- $\rightarrow$  The desired accuracy vs. actual T<sub>j</sub>: a measurement of baseplate temperature may be sufficient to indicate a fault in the heatsink or cooling

system, while measurements of actual die or bondwire temperatures may be required for thermal control algorithms.

- Time resolution:

- Some measurement methods are unable to track short temperature cycles induced by load current and can only provide an averaged value over a number of seconds.

- Cost-benefit trade-off

- → Aside from the initial implementation cost, methods of junction temperature measurement may disrupt power module operation in a number of ways.

Fig. 1-4: Considerations for designing or selecting a junction temperature measurement method

# 1.2.1. Direct Temperature Measurement Methods

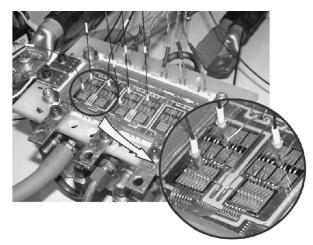

In laboratory settings, a variety of  $T_j$  measurement methods are available. If direct access to the semiconductor die is possible, optical and physical contact methods such as infra-red (IR) cameras or optical fibres can be used to map temperature inside the power module. Fig. 1-5 displays an open IGBT module with optical fibre thermal sensors in direct contact to several of the dies, allowing temperature measurements at high voltage during IGBT operation [36]. Nevertheless, this solution is limited by the response time of the sensor (25ms). Multiple optical fibres can also be used on the same die to map the temperature distribution across the die surface [37].

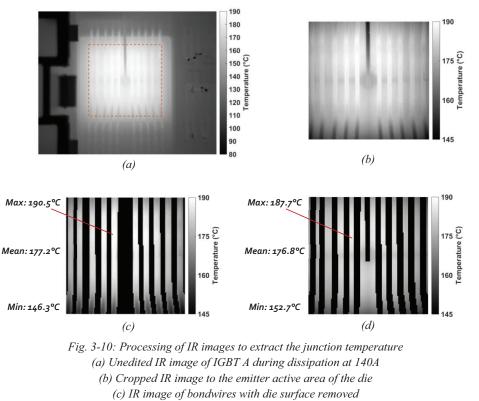

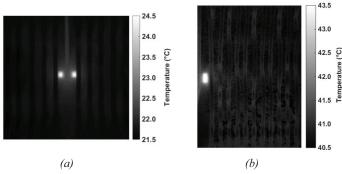

For IR camera measurements, the removal of the dielectric insulating gel is required. Additionally, both the die and bondwires must be painted to create a uniform emissivity across the surface [38]. If care is not taken, an excessively thick layer of paint can have an impact on the thermal operating environment, and high voltage operation may be unsafe due to the absence of dielectric gel.

Fig. 1-5: Power module with integrated optical fibre thermal sensors [36]

Since direct access to the semiconductor is usually prevented by the module packaging, electrical methods are often preferred for temperature measurements in power modules. Two families are outlined in scientific literature: firstly, the use of supplementary electrical sensors located on the chip surface; and secondly, the use of the semiconductor's electrical behaviour.

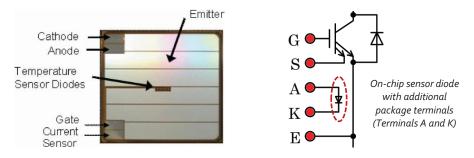

In the category of supplementary sensors, a common approach is to use a diode, or string of diodes, fabricated on the chip surface. Because the forward voltage drop of a diode has a linear relationship with temperature, it is possible to use it as a temperature indicator. An example of this is displayed in Fig. 1-6; in fact, commercial examples already exist [39][40]. These sensors provide accurate measurements and fast response times, but the increased complexity of the power module is a drawback: a temperature sensing diode decreases the active area of the die, and requires additional contact pads and packaging terminals.

Fig. 1-6: On-chip supplementary temperature sensors [39][40]

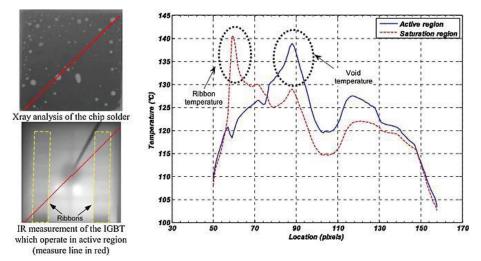

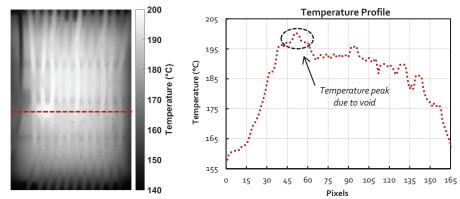

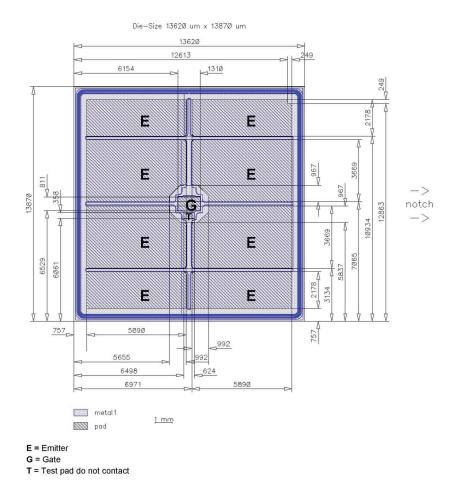

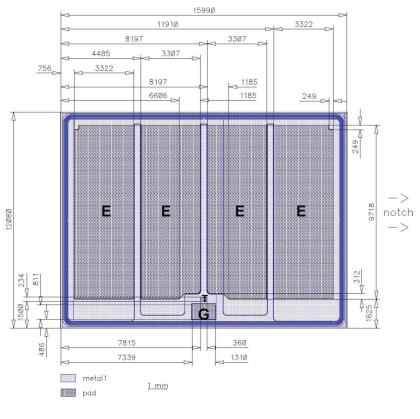

These sensors also provide local temperature measurements, which can present some issues. For instance, Fig. 1-7 displays a map of the temperature distribution in two IGBTs, in which the peak temperature results from a solder void located in the backside of the chip. Unless a sensor is situated in the immediate vicinity, a local measurement is unable to detect the presence of peaks such as this. In fact, if the sensor is not optimally placed, the measured temperature could be more than 20°C below the maximum.

In order to have a good representation of the global surface temperature, Thollin *et al.* [41] present a functional power semiconductor die containing an array of 13 temperature and voltage sensors. They are made with a deposition of a thin thermo-sensitive polysilicon layer and located inside the top metallisation. In this case, multiple external wires are needed to obtain the temperature value given by each sensor; therefore, the setup becomes increasingly complex.

Another sensor solution requiring power module modification is outlined by Brekel *et al.* [33]. A modified IGBT substrate layout, including a gate connection with dual contact pads, is used to provide room for sensing equipment that facilitates the measurement of the internal gate resistance. The temperature dependence of this resistance is then used to evaluate the semiconductor temperature.

*Fig. 1-7a: Temperature distribution in an IGBT chip with peak temperature caused by a solder void* [42]

Fig. 1-7b: Temperature distribution in an IGBT chip with peak temperature caused by a solder void

#### 1.2.2. Temperature Sensitive Electrical Parameters (TSEPs)

The observation of junction temperature without modification to the die or packaging can be achieved through the use of temperature-sensitive electrical parameters (TSEPs). These approaches directly use the electrical behaviour of the semiconductor as the temperature sensor, which theoretically allows for instantaneous junction temperature measurements. The electrical parameter that is selected for use is usually calibrated with respect to temperature by setting the power module to a series of known temperatures and recording the electrical parameter to create a look-up table. Typically, just one representative temperature can be extracted and is assumed to be influence by the entire active area of the die – multiple measurements cannot be extracted to create a temperature distribution profile.

TSEPs have been used to perform thermal characterisation of semiconductors for a number of years. Reviews of the variety of TSEPs are provided by Blackburn [43] in 1988, and more recently in 2012 by Avenas, Dupont and Khatir [44].

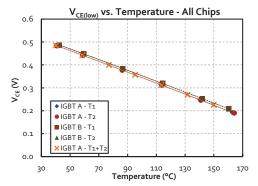

The most commonly used TSEP is the voltage drop under a low current injection ( $V_{CE(low)}$ ). This TSEP has been used for thermal measurements in bipolar transistors for many decades [43][45][46], and takes advantage of the temperature dependence of the voltage drop across a PN junction.

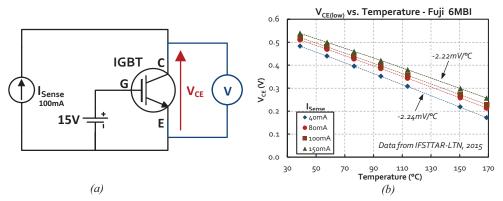

The measurement process is very simple and demonstrated in Fig. 1-8 for an IGBT: a constant sensing current generally in the range of 1mA - 100mA (or approximately 1/1000th of the device current rating) is fed into the power device and the subsequent voltage drop is measured. In silicon devices, this parameter generally exhibits a negative temperature dependence of approximately  $-2\text{mV}/^{\circ}\text{C}$ . The V<sub>CE(low)</sub> vs. temperature on a Fuji 1200V/100A IGBT module for a variety of sensing currents is shown in Fig. 1-8, where a temperature sensitivity of between  $-2.22\text{mV}/^{\circ}\text{C}$  and  $-2.24\text{mV}/^{\circ}\text{C}$  is apparent. The V<sub>CE(low)</sub> can also be seen to depend highly on the value of the sensing current. Therefore, the sensing current must be strictly controlled and a measurement of V<sub>CE(low)</sub> is not possible during normal load current commutation.

Typically, the  $V_{CE(low)}$  has been used for offline characterisation or in current cycling setups [12], where the sensing current is injected into the device after a short delay (perhaps a few hundred  $\mu$ s) once the load current has been removed. The  $V_{CE(low)}$  can then be recorded as the device is cooling, and a linear regression vs. the square root of time can be used to estimate the temperature value at the moment the load current is switched off [43][46].

Fig. 1-8: (a) Electrical circuit for measurement of the most common TSEP,  $V_{CE(low)}$  (b)  $V_{CE(low)}$  on a Fuji 6MBI100VA-120-50 IGBT measured with a variety of sensing currents

The  $V_{CE(low)}$  is widely used since most power semiconductors contain a PN junction in their structure (e.g. diodes, IGBTs, base-emitter in bipolar transistors). For MOSFET devices, the  $V_{CE(low)}$  can also be used by applying the method to the intrinsic body-diode; however, the threshold voltage ( $V_{TH}$ ) has been traditionally used with more accurate results [47].

Nevertheless, temperature measurements using TSEPs in power semiconductors during normal operation are not well developed. Issues surrounding their use range from the need to separate of the effects of temperature from inherent electrical variations, to significant errors in accuracy of the measurements.

In the past three years, a significant amount of research has been disseminated on this topic. Table I displays a synthesis of publications where a TSEP has been investigated for use in online junction temperature measurement (i.e. during normal semiconductor operation). Some of the key concepts will be outlined in the following subsections. In order to ease this process, the TSEPs have been divided into three main categories:

- Classical TSEPs: This includes the use of traditional TSEPs such as V<sub>CE(low)</sub>, V<sub>TH</sub> and the saturation current (I<sub>sat</sub>)

- Static characteristic: Principally, this involves the on-state voltage drop at high current

- **Dynamic characteristics:** These measurements generally consist of using the transient switching parameters of the device

The main implementation issues and barriers to using TSEPs in operating power semiconductors will be summarised. From this, technical objectives for the PhD are formulated.

### 1.3. Literature Review of Online TSEP Proposals

# 1.3.1. Classical TSEPs

Classically used TSEPs are attractive since significant knowledge on these measurement techniques is already available and the methods are well characterised. For example, the  $V_{CE(low)}$  has been repeatedly demonstrated to provide accurate results close the mean junction temperature of the chip [48][49]. This is also true for  $V_{TH}$  [44][47].

The main drawback in the use of classical TSEPs is that they typically have to be performed in specific electrical conditions, and thus many attempts to incorporate the measurements in converter setups have required significant modification to the converter or control strategy. This can include the addition of supplementary components, momentary disconnection of power devices from the power circuit, and interruption to normal load current control.

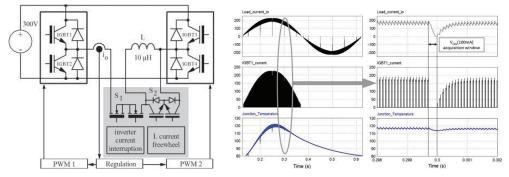

Regarding the most common TSEP,  $V_{CE(low)}$ , temperature measurement can be conducted in inverters when the output current crosses close to zero [21][50]. An accompanying delay is consequently necessary in order to have enough time to complete the measurement [21]. Alternatively, some authors propose to include supplementary switches in order to momentarily interrupt the load current and isolate the characterised devices while the temperature measurement takes place [51][52]. This is displayed in Fig. 1-9, where Forest *et al.* place additional MOSFETs and IGBTs in the load line of an H-bridge inverter, allowing the load current to be diverted in under 1µs. A 100mA sensing current can then be injected into the desired IGBT and a measurement of  $V_{CE(low)}$  performed. The total delay for this procedure amounts to a few hundred microseconds.

Fig. 1-9: V<sub>CE(low)</sub> measurement during inverter operation using supplementary switches [52]

The  $V_{CE(low)}$  has also been proposed for online measurements in MOSFET devices by applying the method to the body-diode [53]. Likewise, this application required momentary disconnection of the MOSFET from the power circuit.

For  $V_{TH}$ , measurement in both IGBTs and MOSFETs has been proposed in several publications. In the case of MOSFETs, measurement circuits included an additional gate resistor of several k $\Omega$  which could be used to slow down the turn-on transition when a measurement is desired [54]. A disconnection of the MOSFET from the main power circuit was also required in order to force the drain current to a fixed, low value of several mA.

|                          |                             | Comments                                              |                             |                                                                                                                                                                                  |                                                                                    |                             |                                                                                             |                                             |  |

|--------------------------|-----------------------------|-------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------|--|

| Method                   |                             | Device Dependents                                     |                             | Additional Comments                                                                                                                                                              | Potential<br>Measurement<br>Frequency                                              | Linearity                   | Required<br>Sensing<br>Resolution                                                           | Reference                                   |  |

|                          | Short<br>Circuit<br>Current | IGBT                                                  | Τ, V                        | Induces a Hard<br>Switching Fault to<br>create short circuit.                                                                                                                    | Very Low                                                                           | Good<br>Linearity           | Depends on<br>device (0.15%<br>of max I <sub>short</sub><br>per °C)                         | [59]                                        |  |

| Classical TSEPs          | Saturation<br>Current       | MOS<br>Transistors                                    | Τ, V                        | Partially turns on the<br>device with a low<br>gate voltage during<br>the off-state                                                                                              | Unknown                                                                            | Non-Linear<br>(Exponential) | Varies<br>depending on<br>temperature<br>range                                              | [34]                                        |  |

|                          | V <sub>CE(low)</sub>        | Transistors<br>and Diodes<br>MOSFET<br>Body-<br>diode | Т                           | Requires specific<br>current low current<br>level.<br>Requires interruption<br>to normal load<br>current.                                                                        | Low (when<br>load current<br>comes close to<br>0A or<br>interrupting<br>operation) | Good<br>Linearity           | 2mV/°C in silicon devices                                                                   | [21] [50]<br>[51] [52]<br>[53]              |  |

|                          | V <sub>TH</sub>             | IGBTs,<br>MOSFETs                                     | Т                           | Possible<br>disconnection of the<br>device from power<br>circuit<br>May require<br>increased gate<br>resistor<br>Dependence on load<br>current according to<br>extraction method | Dependent on<br>measurement<br>circuit                                             | Good<br>Linearity           | 4 - 10mV°/C<br>May require<br>measurement<br>synchronisatio<br>n accuracy in<br>nanoseconds | [54] [55]<br>[56] [57]                      |  |

| Static<br>characteristic | $V_{CE(high)}$              | IGBTs,<br>Diodes,<br>MOSFETs                          | T, I, V <sub>GE</sub>       | Requires very<br>accurate current<br>sensors<br>Generally inaccurate<br>temperature<br>measurements                                                                              | High (each on-<br>state)                                                           | Good<br>Linearity           | ±2-3mV/°C<br>Sensitivity<br>depends on<br>current level<br>and device<br>type               | [62] [63]<br>[64] [65]<br>[66] [67]<br>[68] |  |

| eristics                 | IGBT<br>Turn-Off            | IGBT                                                  | T, I, V,<br>V <sub>GE</sub> | Dependent on a high<br>number of inherent<br>electrical variations                                                                                                               | High (Each<br>Switching<br>Cycle)                                                  | Good<br>Linearity           | ns/ps per °C                                                                                | [72] [73]<br>[74] [69]<br>[75] [76]<br>[78] |  |

| Dynamic characteristics  | Turn-On<br>Delay            | MOS<br>Transistors                                    | T, V, V <sub>GE</sub>       | Closely related to $V_{TH}$                                                                                                                                                      | High (Each<br>Switching<br>Cycle)                                                  | Good<br>Linearity           | ns/ps per °C                                                                                | [69] [70]<br>[71]                           |  |

|                          | Rise-Time                   | MOS<br>Transistors                                    | T, I, V,<br>V <sub>GE</sub> | Dependent on a high<br>number of inherent<br>electrical variations                                                                                                               | High (Each<br>Switching<br>Cycle)                                                  | Good<br>Linearity           | ns/ps per °C                                                                                | [69] [71]                                   |  |

#### ${\tt TABLE \ I.} \qquad {\tt Literature \ Review \ of \ TSEPs \ investigated \ for \ online \ use}$

For  $V_{TH}$  in IGBTs, several authors use the induced voltages over the parasitic inductances of the packaging to trigger a measurement of the gate voltage as the IGBT turns on [55][56][57]. This gate voltage value is then assumed to be  $V_{TH}$ . Since the IGBT is not disconnected from the power circuit (and in particular the collector current is not controlled), this  $V_{TH}$  extraction may be influenced by collector current variation [56][58]. Furthermore, unless the external gate

resistance is significantly larger than the internal gate resistance, the sensitivity of the method is impaired. Low values of gate resistor can also mean that measurement synchronisation jitter in the region of 10ns can induce significant errors [55].

Another known TSEP for power-MOS devices is the saturation current ( $I_{sat}$ ) under a given gateemitter (gate-source) and a given collector-emitter (drain-source) voltages. Bergogne *et al.* [34] use this technique when the semiconductor is in off-state by partially turning on the device for 2µs with a gate voltage of around 6V. As with the  $V_{CE(low)}$ , interruption to normal converter operation is a primary drawback (shown in Fig. 1-4). In addition,  $I_{sat}$  has an exponential relationship with temperature which could present difficult calibration procedures [34][49].

A similar method is presented by Xu *et al.* [59], who study the short circuit current as a TSEP in a 2-level inverter. Here, a hard switching fault is induced during inverter operation with the use of supplementary switches, and the peak short circuit current measured. The foremost problem here is a very high thermal dissipation during the short circuit which can cause fast thermal runaway. Logically, the measurement frequency is very limited since repetitive short circuits could cumulatively degrade the device. Another facet of this method is ensuring that negligible self-heating is present before a measurement of the peak short circuit current can performed. Consequently, a very low stray inductance in the current loop is a likely requirement.

As a conclusion, it appears that temperature measurements are possible during the operation of a converter using classical TSEPs. However, the modification to the structure of the converter and/or its operation can be seen as a serious drawback. It is therefore important to find TSEPs that are electrically suited to online temperature measurements: static and dynamic characteristics are both potential solutions.

# 1.3.2. Static Characteristic

Because the IV characteristic of all power devices depends on the temperature, an obvious way to estimate the junction temperature of a device would be to simultaneously measure its forward voltage and current ( $V_{CE(high)}$ ). This is an attractive option since opportunity to measure this TSEP occurs naturally in every switching cycle. Moreover, current sensors are generally already included in converter setups, and several measurement circuits have recently been presented that allow measurement of the forward voltage in real operating conditions [60][61]. This method has been used by several different authors in recent years [62][63][64][65][66][67].

Issues with the  $V_{CE(high)}$  approach stem from the fact that power modules do not permit electrical measurements on solely the semiconductor die – individual dies are connected to the 'outside' (and thus any measurement system) through a series of interconnections, bond-wires and packaging materials. The ohmic voltage drop of these materials becomes significant at higher current and significantly impacts the measurement. Therefore, the layout of the module has a large influence on the method. Typically, the interconnection and packaging materials will be at different temperatures to the die during operation and introduce large errors in the temperature measurement. These errors have been documented in a number of publications and can exceed  $\pm 30^{\circ}$ C [62][67]. The inaccuracy also exists in MOSFET devices when similarly using R<sub>DS(on)</sub> as a TSEP [47].

To counteract this problem, Choi [65] and Ghimire [66] propose the use of a correction factor. Although providing accurate results, this correction factor is generated directly from measuring the module resistance, coupled with measurements made via an IR camera or through FEM simulations. A thorough knowledge of the exact layout inside the module, or indeed an open module to perform measurements on, is consequently required to formulate the corrections. Additionally, due to the natural variation of  $V_{CE}$  through bondwire lift-off or aluminium surface reconstruction, this correction factor needs constant recalibration as the device ages.

An alternative correction method is proposed by Dupont and Avenas [67], which mathematically reduces the resistance contribution to zero. Here, the  $V_{CE}$  is measured at two different gate voltages (15V and 13V), and the difference between the two measurements is used as the TSEP. This method is reported to reduce measurement errors to usually within -5°C, as well as being reasonably unaffected by bond-wire lift-off. Nevertheless, an advanced gate driver providing fast transition between two different stable turn-on voltages, along with a high degree of post-processing of measurement data, would be required to perform the measurement.

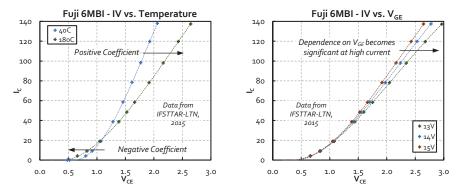

This leads to another fundamental issue with  $V_{CE(high)}$ : the dependence on gate voltage ( $V_{GE}$ ) as well as load current. If the gate driver turn-on voltage is not stable with performance demands or ambient temperature, a method to compensate for these fluctuations may be necessary. Finally, the sensitivity of the TSEP is particularly dependent on the current level, and can range from a negative dependency at low current, to a positive dependency at high current. A crossover point is also present where the temperature dependence of  $V_{CE(high)}$  is negligible. Both of these issues are displayed in Fig. 1-10 on a Fuji 6MBI100VA-120-50 IGBT module.

Fig. 1-10: IV Characteristic ( $V_{CE(hieh)}$ ) vs. Temperature and  $V_{GE}$  for a Fuji1200V/100A IGBT Module

Lastly, the accuracy of the current sensors can present an issue. Table II shows the results of temperature measurement using  $V_{CE(high)}$  on an Infineon SIGC100T60R3 IGBT while lightly varying the current measurement. It can be seen that a current variation of only 0.5% introduces a temperature measurement discrepancy of close to 4°C. Therefore, the current sensor requires excellent accuracy and synchronisation with voltage measurement in order obtain reliable temperature values.

| TABLE II. | EFFECT OF THE CURRENT LEVEL ON $V_{CE(\text{HIGH})}TSEP$ |  |

|-----------|----------------------------------------------------------|--|

|-----------|----------------------------------------------------------|--|

|                            | Current close to 80A Current close to 100A |      |       | ose to 100A |  |

|----------------------------|--------------------------------------------|------|-------|-------------|--|

| Current (A)                | 79.8                                       | 80.2 | 99.8  | 100.2       |  |

| Estimated temperature (°C) | 111.2                                      | 116  | 150.5 | 154         |  |

| Data from IFSTTAR, LTN     |                                            |      |       |             |  |

#### 1.3.3. Dynamic Characteristics

The dynamic (or switching) characteristics of a power module are another attractive group of TSEPs since a measurement opportunity presents itself in each switching cycle. In the case of IGBTs and MOSFETs, several different TSEPs are available: the turn-on delay [69][70][71], the turn-off delay [69][72][73][74][75][76][78], and the current slope during turn-on [69][71].

These measurements are constrained by the need for very fast sensors as the sensitivity of the TSEPs can be in the range of several ns/°C or even ps/°C in smaller devices. A particularly developed TSEP in this category appears to be the use of the length of the miller plateau during turn-off in an IGBT. A similar approach is presented in two publications [75][78]. In both cases, authors show the possibility to generate two automatic pulses that signify the start and the end of the miller plateau; these two pulses could then be used to trigger a time-to-digital converter. The sensitivity here appears to be in the region of 1-5ns/°C for medium-high power devices.

Dynamic characteristics however are particularly susceptible to inherent electrical variations induced by the operating conditions. For example, the turn-off time in the TSEP described above may be influenced by: temperature, DC voltage, load current, control strategy, and fluctuations in gate driver performance. A high number of dependents would seemingly suggest increased complexity in both the calibration process, as well as in actual use in a converter setup.

Anyhow, Sundaramoorthy *et al.* [76] demonstrate a technique to simultaneously measure both temperature and current by using the voltage over the parasitic emitter inductance during turn-off. The peak value of this voltage is dictated by the current slope (which is temperature dependent), while the integral of the voltage is determined by the total current being switched.

Validation of the accuracy of TSEPs based on switching times appears to be scarce in scientific literature. Sundaramoorthy *et al.* [77] provide a validation of the previously mentioned junction temperature measurement via the miller plateau length, but the validation does not include comparisons with infra-red measurements and is performed on a closed module. Therefore, temperature measurements made using these methods should be made with caution, especially given the influence of numerous electrical parameters.

#### 1.4. Additional TSEP Implementation Issues

In addition to those highlighted above, some other general implementation issues also surround the use of TSEPs during normal operation of power semiconductors. These general issues are briefly outlined in the following paragraphs and principally include: calibration requirements, and the accuracy of TSEP measurements.

#### 1.4.1. Calibration Requirements

Before using a TSEP, it is necessary to obtain its relationship with temperature. This procedure can be more or less complex depending on the properties of the TSEP in question.

First of all, the linearity of the TSEP and number of electrical dependents can be a good indicator of the time and post processing requirements. The amount of time consumed in the calibration process depends upon the number of calibration points desired, and the time required to heat the power module to the desired series of temperatures. If the TSEP is linear with no electrical dependents, only a few calibration points are needed. In this category, the  $V_{CE(low)}$  appears to be the most ideal TSEP, since it has a linear dependency on temperature and calibration is only required at one low current level (around  $1/1000^{th}$  of the rated current).

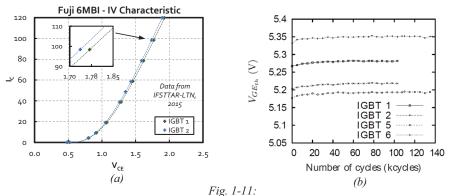

For a large number of devices of the same batch and part number, the variability of the TSEP between each device is of great interest. Ideally, all devices would have an identical calibration curve, so that one set of data could be used across the entire batch. If the temperature sensitivity does not vary from device to device, then a single calibration point may be adequate in order to adjust for the variance of the absolute value of the TSEP parameter. Again, the  $V_{CE(low)}$  demonstrates the most ideal properties in this category, for which most silicon devices will display a temperature sensitivity of around  $-2mV/^{\circ}C$ . Most TSEPs however generally display some variation between devices. In particular,  $V_{TH}$  demonstrates a non-negligible variation between chips of the same type [21][47][49]; while TSEPs that are influenced by module layout, such as  $V_{CE(high)}$ , will also require individual calibration. This is displayed in Fig. 1-11a, where the  $V_{CE(high)}$  for two IGBTs from inside the same module are shown, and a clear offset can be seen.

(a) IV characteristic for two IGBTs inside a Fuji 6MBI100VA-120-50 module – an offset in the TSEP can be seen between the two IGBTs

(b) V<sub>TH</sub> during power cycling on four IGBTs from the same module [21]

Another pressing issue for calibration is the stability of TSEPs as the power module ages. Fig. 1-11b shows the  $V_{TH}$  for four IGBTs inside a power module throughout a power cycling test. A clear offset between the  $V_{TH}$  of each IGBT can be seen, as well as a variation as the power cycling test progresses. If the TSEP changes significantly during a power module's lifetime, periodic TSEP recalibration may therefore be required.

Finally, it is usually assumed that the entirety of the power module, including the die and packaging materials, is at a uniform temperature set by the oven or hot-plate used in the calibration procedure. However, this is not valid for TSEPs that require calibration at high current levels, since non-negligible self-heating is induced in the device. As a result, calibration has to be performed with short current pulses (from 10 to 100 microseconds) in order to keep self-heating to a minimum.

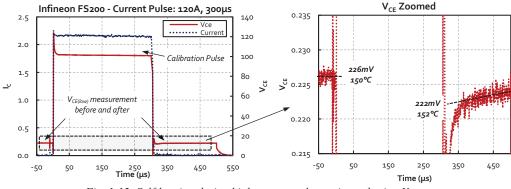

Alternatively, Dupont and Avenas present a compensation technique that uses the  $V_{CE(low)}$  to adjust for the self-heating during the high current calibration pulses of  $V_{CE(high)}$  [67]. This technique involves measuring the junction temperature of an IGBT via  $V_{CE(low)}$  directly before, and after, the high current calibration pulse. To estimate self-heating,  $V_{CE(low)}$  is recorded after the calibration pulse for a period of a few hundred microseconds and extrapolated back to the point at which the calibration current is removed. The measurement is then compared to the junction temperature via  $V_{CE(low)}$  from directly before the calibration. Using this technique, an estimation of the self-heating in an Infineon FS200R12PT4 IGBT module is shown in Fig. 1-12. It can be seen that, for a high starting temperature of 150°C and a 120A calibration pulse lasting 300µs (IGBT is rated for 200A), the self-heating induced can close to 2°C.

Fig. 1-12: Self-heating during high current pulse, estimated using  $V_{CE(low)}$

#### 1.4.2. Accuracy of TSEP Measurements

The term 'junction temperature' is ambiguous, since the temperature of a power semiconductor cannot be described using a single temperature value. Instead, the junction is made up of a distribution of temperatures. A clear demonstration of this is in Fig. 1-7, where the surface temperature of the IGBT dies can span up to 30°C when measured via an IR camera. In some conditions, a non-negligible temperature gradient may also be apparent with respect to depth [79]; nevertheless, direct measurements of the die surface (such as via IR camera) are usually taken as representative of the junction. As a result of this ambiguity, the 'accuracy' of a TSEP measurement depends on the desired temperature to be measured: whether this is the mean, maximum, or some other pertinent temperature of the device.

Inconsistencies between TSEP measurements have in fact been found as far back as 1966, where researchers placed the maximum temperature of the junction with most importance [45]. Since then, there is ample research to back up the assertion that TSEPs deliver different temperature

measurements on the same device. These discrepancies may also change depending on the device and dissipation conditions [42][47][49]. An example of this is shown in Table III, which displays the results of a study where three different TSEPs are used on a variety of power MOSFETs. It can be seen that on MOSFETs 3 and 5, the temperature measurements via TSEPs can diverge over 10°C. On the other hand, the TSEPs used on MOSFETs 2 and 4 show a divergence of only 3°C.

|             | Measured Temperature (°C) |          |                                   |                     |  |

|-------------|---------------------------|----------|-----------------------------------|---------------------|--|

| MOSFET Type | IR Radiometer (Max)       | $V_{TH}$ | V <sub>CE(low)</sub> (body-diode) | R <sub>DS(on)</sub> |  |

| 1           | 33.5                      | 31.0     | 28.8                              | 25.7                |  |

| 2           | 38.0                      | 35.0     | 36.5                              | 33.4                |  |

| 3           | 80.0                      | 80.3     | 70.7                              | 69.2                |  |

| 4           | 37.0                      | 36.8     | 36.1                              | 33.0                |  |

| 5           | 73.0                      | 69.0     | 62.0                              | 56.0                |  |

TABLE III. TEMPERATURE MEUSUREMENTS ON POWER MOSFETS USING DIFFERENT TSEPS [47]

As a result, any new TSEP proposal should undergo experimental validation and comparison with a direct measurement method, in order to specify what temperature of the device is being measured. Additionally, since TSEP concepts are generally substantiated on new power modules, it is not clear whether all TSEPs provide repeatable measurements throughout the entire module lifetime. The accuracy should therefore also be assessed on power modules that are in a degraded condition.

A particular source of inaccuracy can come when using TSEPs on modules with paralleled semiconductors dies. For example, both  $V_{TH}$  and  $I_{sat}$  have been demonstrated to give inconsistent errors depending on which particular die is most thermally stressed in the case of two IGBTs in parallel [49].

A further limitation encountered with several paralleled dies is that a TSEP typically only provides a single temperature, but large temperature distributions may be seen inside power modules with multiple dies. To map the temperatures of each chip, some authors have proposed methods which involve taking several TSEP measurements in different electrical conditions, and then using numerical techniques to extract individual temperatures [80].

# 1.5. PhD Objectives

# 1.5.1. Research Questions

From the literature review of TSEP studies, several research questions emerge:

- Can a TSEP be implemented in a converter without undue disruption to power module operation?

- Is there a simple way to separate the effects of temperature from inherent electrical fluctuations? Alternatively, is a TSEP available that is solely dependent on temperature?

- What is the level of accuracy of the TSEP?

- What would be the level of complexity of the TSEP calibration procedure?

• Can a TSEP be robust and reliable throughout the lifespan of the device and withstand the effects of power module degradation?

# 1.5.2. Technical Objectives

As a result, the PhD has several technical objectives. In short, the PhD should develop a new TSEP, or an improvement to an existing TSEP, that has the following features:

- Measured in the normal operating cycle of a power semiconductor switch (MOSFET or IGBT) without disruption to operation or control strategy

- Does not require a calibration procedure with complex post-processing

- Is independent from inherent electrical variations outside of temperature, or allows easy separation of the effects of temperature

In addition, the PhD should also:

- Validate the temperature measurement provided by the new TSEP via direct measurements such as optical fibres or an IR camera.

- Perform this validation on multiple types of semiconductor (MOSFET or IGBT), and on paralleled semiconductor dies

- Assess the effect that common power module degradation mechanisms have on the accuracy of the TSEP

# **II.** Proposed TSEP Measurement Methods

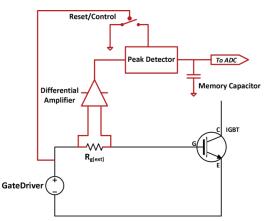

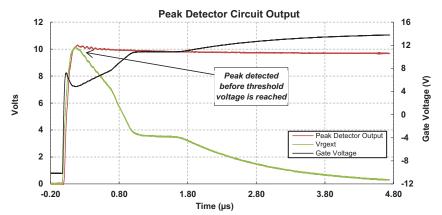

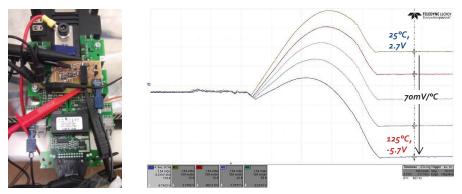

In this chapter, electrical methods for junction temperature measurement in IGBTs and MOSFETs are presented. Predominantly, a measurement method called the 'Peak Gate Current' is focused on, which involves detecting the peak voltage over the external gate resistor during the turn-on delay. This voltage is then used to calculate the internal gate resistance, which is a temperature dependent electrical parameter. The theoretical background for the temperature measurement is explained, along with experimental verification provided on IGBTs. Primary advantages of the method include an immunity to load current variation, a good linear relationship with temperature, and an autonomous measurement circuit that can be integrated into a gate driver without disruption to operation. Both the advantages and disadvantages of the method will be discussed.

An additional electrical method considered during the PhD period will also be briefly outlined. However, this was not extensively studied. Both envisioned methods do not require compensation for load current, as this was seen to be a major contributor to some of the implementation issues outlined in Chapter 1.

# 2.1. Internal Gate Resistance - R<sub>Gint</sub>

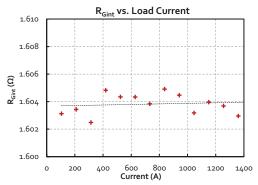

To achieve the technical objectives stipulated in section 1.5.2, developing a TSEP that would be uninfluenced by load current variation was a key focus. Such a TSEP would hold multiple advantages. Firstly, the calibration procedure would comprise of few measurement points; secondly, accurate and synchronised load current measurements would not be required.

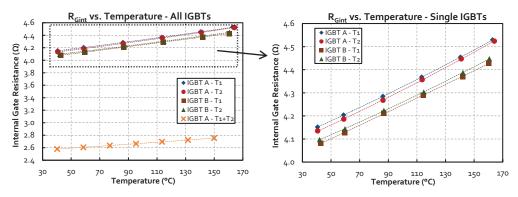

The internal gate resistance ( $R_{Gint}$ ) of an IGBT or MOSFET is one electrical parameter that is not influenced by load current. The  $R_{Gint}$  of an IGBT or MOSFET has conventionally been a distributed resistance of the gate that influences the propagation delay of the gate signal across the die [81]. In power modules that include paralleled power MOS transistors, manufacturers often increase the size of  $R_{Gint}$ , or include additional integrated resistors in the die, in order to prevent high frequency oscillations and to improve current sharing [82][83]. The temperature dependence of  $R_{Gint}$  is a consequence of the temperature coefficient of resistivity for polysilicon, which is often the material of manufacture.

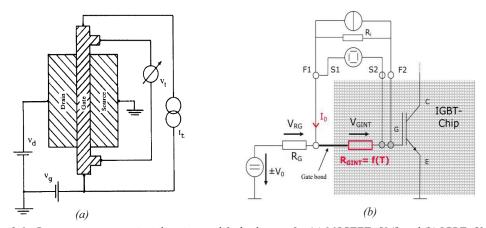

Using  $R_{Gint}$  as a TSEP is particularly appealing since a review of academic literature reveals previous investigations using  $R_{Gint}$  for temperature measurement in both MOSFETs and IGBTs [33][84]. Nevertheless, both of these investigations required a modified substrate layout to facilitate the measurement. By modifying the substrate to include a gate connection with dual contact pads, a four-point probing technique could be used to measure the ohmic resistance of the gate. This measurement principle is depicted in Fig. 2-1. Taking Fig. 2-1b on an IGBT, a constant sense current of 500mA is applied at the connections F1 and F2, which creates a voltage drop over  $R_{Gint}$ . This voltage is then measured through connections S1 and S2. Because the resistance depends on temperature, the measured voltage drop varies and is used as the temperature indicator.

*Fig. 2-1:*  $R_{Gint}$  measurement principle using modified substrate for (a) MOSFETs [84] and (b) IGBTs [33] The modification of the substrate layout and the need for additional measurement equipment inside the power module can be seen as a drawback to this approach. Consequently, the following subsections will identify measurement principles that allow the temperature variation of R<sub>Gint</sub> to be viewed on any standard power MOSFET or IGBT module – without modification to the device substrate or packaging.

#### 2.1.1. R<sub>Gint</sub> Measurement on Standard Power Modules

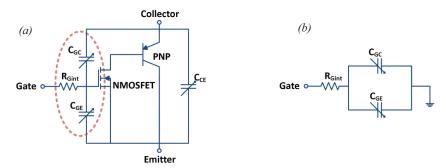

For the purpose of temperature measurement in standard power modules,  $R_{Gint}$  is considered to be the equivalent series resistance (ESR) of both the gate-emitter and gate-collector capacitance (gate-source and gate-drain capacitance in MOSFETs), as shown in Fig. 2-2.

Fig. 2-2: (a) IGBT Parasitic Capacitances:  $R_{Gint}$  and input capacitances circled (b) Equivalent circuit with  $R_{Gint}$  as the ESR of the paralleled  $C_{GC}$  and  $C_{GE}$  capacitances.

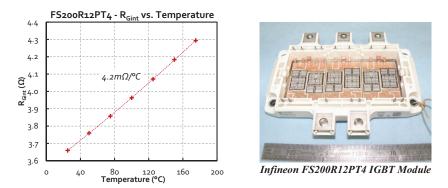

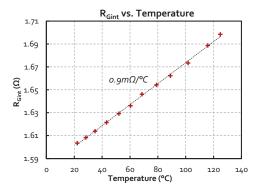

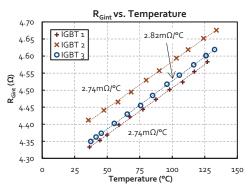

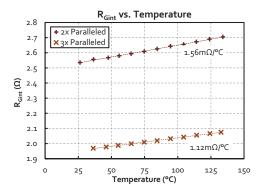

For a standalone measurement, the ESR (or  $R_{Gint}$ ) of a MOSFET or IGBT can be measured using an LCR meter. This involves shorting the collector and emitter, applying a high frequency sinusoidal voltage to the gate, and measuring the resultant magnitude and phase. The frequency of the sinusoidal voltage must be high enough to ensure that the reactance of the gate capacitance is negligible, and is therefore typically in the region of 1MHz or more. Fig. 2-3 displays  $R_{Gint}$  vs. temperature for one IGBT inside an Infineon FS200R12PT4 module, measured using a Keysight E4990A impedance analyser. A temperature sensitivity of +4.2m $\Omega$ /°C can be observed, with a nominal  $R_{Gint}$  at 25°C of approximately 3.65 $\Omega$ .

*Fig. 2-3: R<sub>Gint</sub> vs. Temperature for an IGBT from an Infineon FS200R12PT4 module. Measured using a Keysight E4990A impedance analyser*

Some high-end LCR meters are able to perform measurements in around 20ms, which is too long for direct application during the operation of most converters where switching frequencies usually exceed 1 kHz.

Nevertheless, this sinusoidal voltage method has very recently been proposed for use in operating IGBTs through the use of a specialised gate driver [85][86]. Here, a high frequency sinusoidal signal, at the resonant frequency of the gate capacitance, is superimposed on the gate voltage during the off-state. In this approach, the drawbacks appear to be that the gate driver requires substantial modification, along with additional external control to safely feed in the high frequency sinusoidal voltage. The resonant frequency of each device may also vary and thus the measurement circuit could require tailoring to each individual device. In some cases, an additional inductance may be added to the sinusoidal voltage feed-in path in order to lower the resonant frequency of the gate [85].

The following section will present the first original contribution of the thesis: a method to measure  $R_{Gint}$  that does not require any modification to the gate driver, or additional external control. To achieve this, the peak gate current during turn-on and the voltage swing of the gate driver are used to calculate the internal gate resistance. A description of the measurement principle, followed by experimental verification on IGBTs is provided. However, the measurement principle should be applicable to all MOSFETs and IGBTs containing an internal gate resistance. Advantages and disadvantages of the method are also discussed, along with some implementation considerations.

#### 2.2. Peak Gate Current (I<sub>GPeak</sub>) Measurement Principle

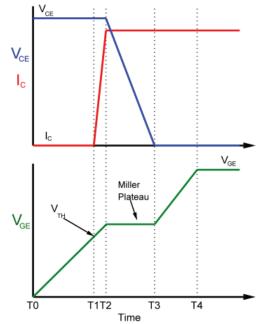

The peak gate current ( $I_{GPeak}$ ) method for junction temperature measurement uses the normal charging cycles of the gate terminal during a hard switching turn-on. Simplified waveforms of an IGBT turn-on process are shown in Fig. 2-4. The turn-on process of an IGBT is well documented [87][88]; therefore, only the beginning of the process (between T0 and T1) will be discussed here, since this is where the peak gate current occurs.

The turn-on process begins at T0 when the gate driver output voltage swings from 0V, to a positive value above the threshold voltage of the transistor. At this point, the gate current begins

charging the capacitances  $C_{GE}$  ( $C_{GS}$  in MOSFETs) and  $C_{GC}$  ( $C_{GD}$  in MOSFETs), while the device remains in an off-state. This period is known as the turn-on delay and continues until T1, when the charge on  $C_{GE}$  reaches the threshold voltage and the transistor turns on. The length of this period can range from just a few nanoseconds for small discrete transistors, to up to a microsecond for large IGBT modules.

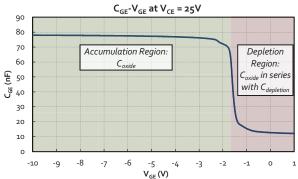

During T0-T1, both  $C_{GE}$  and  $C_{GC}$  remain stable for the following reasons. Firstly, the  $V_{CE}$  remains at a high and constant value (perhaps at the DC-link for that particular application). In these conditions,  $C_{GC}$  remains small and independent of  $V_{GE}$  [89][90].  $C_{GE}$  also remains stable with a high  $V_{CE}$ , and is independent of  $V_{GE}$  while the charge remains below  $V_{TH}$  [89].

Fig. 2-4: Simplified gate voltage, collector current, and collector-emitter voltage waveforms during IGBT turn-on process

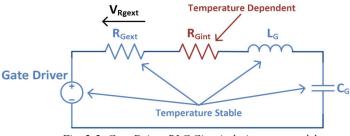

Fig. 2-5: Gate Driver RLC Circuit during turn-on delay

Subsequently, the gate current during the turn-on delay can be viewed as a step response of a second order RLC circuit [91]. This supposition is displayed in Fig. 2-5 and includes: the gate driver as a step voltage source, the parasitic gate inductance, the gate resistance (both internal

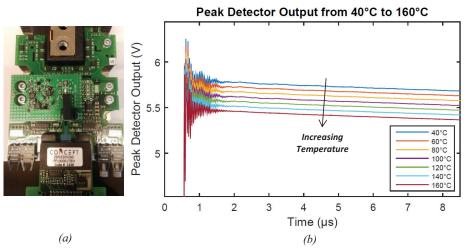

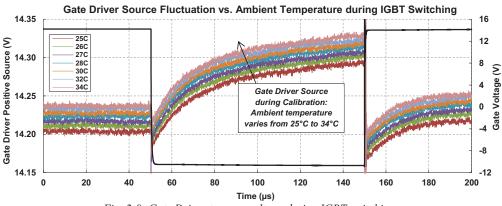

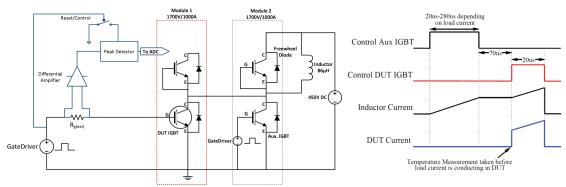

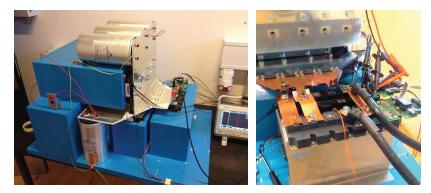

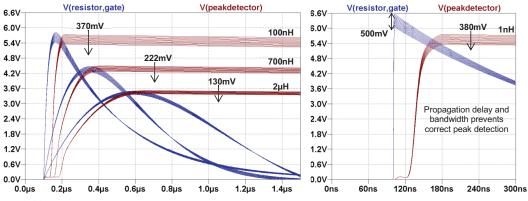

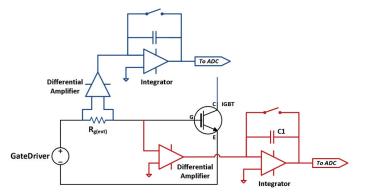

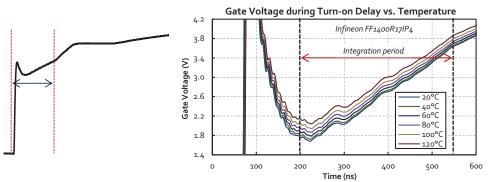

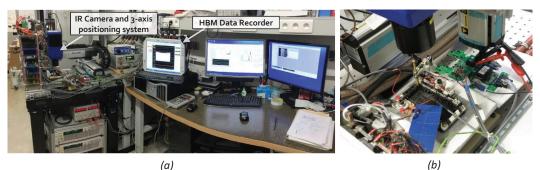

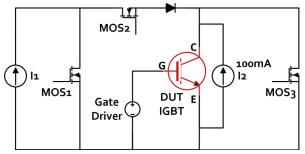

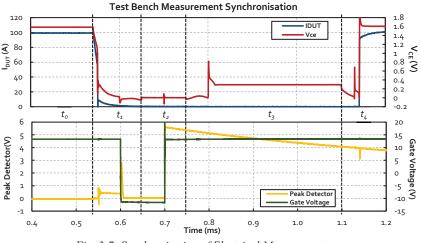

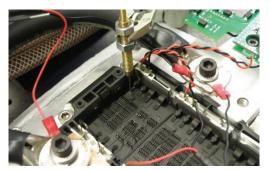

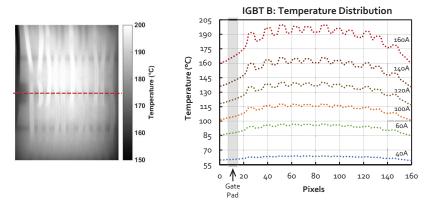

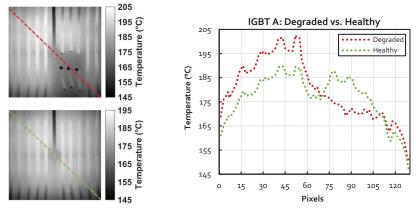

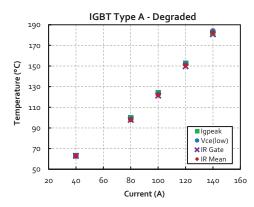

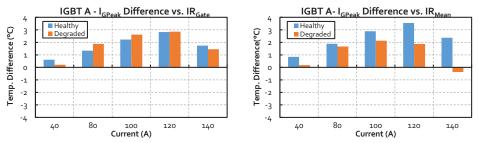

and external), and the gate capacitance (the combined paralleled capacitances  $C_{GC}$  and  $C_{GE}$ ). Essentially, the gate is seen to be a fixed capacitor being charged through a resistor by a step voltage source.