# **Aalborg Universitet**

# A Novel Harmonic Elimination Approach in Three-Phase Multi-Motor Drives

Davari, Pooya; Yang, Yongheng; Zare, Firuz; Blaabjerg, Frede

Published in:

Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE)

DOI (link to publication from Publisher): 10.1109/ECCE.2015.7310640

Publication date: 2015

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Davari, P., Yang, Y., Zare, F., & Blaabjerg, F. (2015). A Novel Harmonic Elimination Approach in Three-Phase Multi-Motor Drives. In *Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE)* (pp. 7001-7008). IEEE Press. https://doi.org/10.1109/ECCE.2015.7310640

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

# Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: August 23, 2025

# A Novel Harmonic Elimination Approach in Three-Phase Multi-Motor Drives

Pooya Davari<sup>†</sup>, Yongheng Yang<sup>†</sup>, Firuz Zare<sup>‡</sup>, Frede Blaabjerg<sup>†</sup>

<sup>†</sup>Department of Energy Technology Aalborg University, 9220 Aalborg, Denmark pda@et.aau.dk, yoy@et.aau.dk, fbl@et.aau.dk <sup>‡</sup>Danfoss Power Electronics A/S 6300 Gråsten, Denmark fza@danfoss.com

Abstract— Power electronics technology has been widely used for decades in the modern motor drive systems. Beyond the control flexibility, the power electronics devices (e.g., diode rectifiers) are also the main harmonic source to the grid due to their nonlinearity, which deteriorate the power grid quality and may cause unnecessary losses in power system transformers. Both degradations are apt to occur in motor drive applications. As a consequence, it calls for advanced and intelligent control strategies for the power electronics based drive systems like adjustable speed drives in industry. At present, many industrial drives are still equipped with three-phase diode rectifiers. Thus, it is difficult to implement the prior-art harmonic control strategies for active front-ends. Moreover, the total cost and complexity has become an obstacle for these harmonic elimination approaches in multiple drive systems. Therefore, in this paper, a new cost-effective harmonic mitigation approach has been proposed for multiple drives. The proposed approach can control the generated current harmonics by benefiting of the nonlinearity of the drive units and through a novel current modulation scheme. Simulation and experimental results have validated the effectiveness of the proposed approach in terms of harmonic elimination in three-phase multi-drive systems.

Keywords—adjustable speed drives; harmonic elimination; multiple drives; three-phase rectifiers;

#### I. INTRODUCTION

Electrical motor drive systems consume a considerable amount of global electrical energy. As the electricity demand is growing faster worldwide, industry has been pushed towards an era of developing more energy-efficient drives. Employing intelligent control techniques for the power electronics based drive systems can improve the efficiency to some extent [1]. However, generated harmonics as a consequence of employing power electronics devices deteriorates the power grid quality [2]-[4]. The high level imposed harmonic input currents may cause unnecessary losses and heat in power system transformers and nuisance tripping of circuit breakers and overstressing of power factor correction capacitors. This highlights the necessity for the drive systems to comply with international standards such as IEC61000 standard [5], and it calls for more smart harmonic elimination strategies for the drive systems.

Typically, a standard motor drive system comprises of three main sections: the front-end power converter that converts AC power from the mains to DC power, an energy storage unit called the DC-link, and finally an inverter as the rear-end

power converter which converts the DC back to AC at the voltage and frequency demanded by the motor. A three-phase diode bridge rectifier is usually employed at the front-end stage, thus being the main harmonic source. A vast array of methods have been introduced to improve the input current quality by shaping it as close as possible to a sinusoidal waveform [3], [4], [6]-[8] as well as using active damping methods [9]-[14]. However, the complexity and cost are significantly increased. Therefore, diode rectifiers (uncontrolled) or thyristor-based rectifiers (phase-controlled) of less complexity and cost are still widely used in Adjustable Speed Drives (ASD).

In addition, the undesirable nonlinearity of the conventional AC-DC conversion stage may become significant, when a large number of industrial converters and ASDs are connected to the Point of Common Coupling (PCC). It has been found that a proper arrangement of these nonlinear loads can contribute to an effective harmonic mitigation, where some of the harmonics from one unit (e.g., diode rectifier) can be cancelled out by the other/s units [15]. The feasibility of this solution is attained only when suitable and accessible communication among the nonlinear units can be performed. For instance, it can be observed in some practical applications, where many ASD based industrial pumps, fans or compressors are operated all together. In fact, improving the input current quality by combining the nonlinear loads was first introduced in multipulse rectifiers [16]. In this method, by employing phaseshifting transformers, the harmonics of each unit can be phasedisplaced with respect to each other, and thus they can cancel out each other. Depending on the number of connected units a range of harmonics can be eliminated. Taking a 24-pulse rectifier [16] as an example, the current Total Harmonic Distortion (THD<sub>i</sub>) can significantly be improved (< 5 %) by using this method. Despite the effectiveness in harmonic mitigation, the volume, associated losses, and also the cost of the phase-shifted transformer are the main concerns.

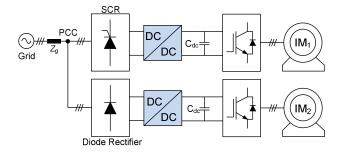

In this paper, a novel harmonic elimination approach is proposed to tackle the aforementioned challenges. The proposed method does not require any phase-shifting transformers like what have been used in multi-pulse rectifiers. Instead, as depicted in Fig. 1, it combines a three-phase diode rectifier with a three-phase Silicon Controlled Rectifier (SCR) unit to cancel out the harmonics. Additionally, in order to improve the performance and flexibility of the system, each

Fig. 1. Typical configuration for a multi-drive application with the proposed harmonic mitigation method.

unit is equipped with a novel current modulation technique, which can individually mitigate a certain number of current harmonics. Obtained simulation and experimental results have verified the effectiveness of the proposed method.

The rest of this paper is organized as follows. Section II presents the detailed analysis of the proposed harmonic elimination method along with the optimum harmonic solutions. In Section III, implementation details and hardware setup are pointed out. The performance of the proposed method is validated through simulation and experimentation in Section IV. Finally, concluding remarks are given in Section V.

#### II. PROPOSED HARMONIC ELIMINATION METHOD

# A. Nonlinear Loads Comibinaton for Harmonic Cancellation

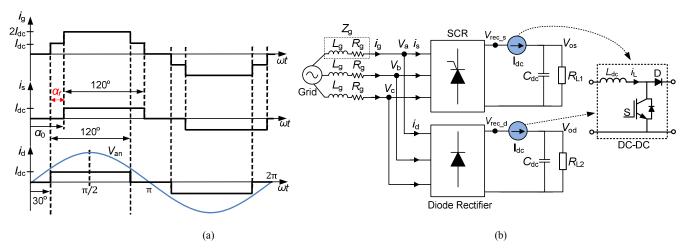

In order to demonstrate and evaluate the proposed method a multi-drive system of two three-phase rectifier units is built up as shown in Fig. 1. The details of system operation are illustrated in Fig. 2, where it is assumed that the current source at the DC-link side of the rectifier draws a constant current (i.e.,  $I_{dc}$ ). In practice, the current source can be implemented in a DC-DC converter (e.g., a boost converter), which can emulate an ideal inductor behavior [17]-[20]. Therefore, for

both rectifiers as shown in Fig. 2, the input currents (i.e.,  $i_s$  and  $i_d$ ) will be a square-wave with the conduction angle of 120°, since at each instant of time interval only two phases conduct and circulate the DC-link current through the grid.

For the rectifier system shown in Fig. 2, Fourier series analysis has been adopted to identify the harmonic content of the input currents. According to Fig. 2(a), in a controlled rectifier (SCR), the harmonics (i.e.,  $i_s(n)$ ) of the square-wave input current with the 120° conduction angle and an adjustable phase angle of  $\alpha_0$  ( $\alpha_0 = \alpha_f + 30^\circ$ ) can be identified as:

$$i_{s}(n) = \sqrt{\left(a_{n}\right)^{2} + \left(b_{n}\right)^{2}}$$

with

$$\begin{cases}

a_{n} = \frac{2I_{dc}}{n\pi} \left[ -\sin\left(n\alpha_{0}\right) + \sin\left(n\alpha_{0} + \frac{2\pi n}{3}\right) \right] \\

b_{n} = \frac{2I_{dc}}{n\pi} \left[ \cos\left(n\alpha_{0}\right) - \cos\left(n\alpha_{0} + \frac{2\pi n}{3}\right) \right]

\end{cases} \tag{1}$$

in which n is the harmonic order. As for the three-phase diode rectifier, it can be taken as a special case of the SCR with a fixed phase angle of  $\alpha_0 = 30^{\circ}$  ( $\alpha_f = 0^{\circ}$ ). In that case,  $a_n = 0$  according to (1), and thus the harmonics of the input current induced by the diode rectifier can be calculated as:

$$i_{d}(n) = \frac{4I_{dc}}{n\pi} \cos\left(\frac{n\pi}{6}\right) \tag{2}$$

According to Fig. 2, the harmonics appearing in the line current  $(i_g = i_s + i_d)$  can be expressed as,

$$i_{g}(n) = \sqrt{(a_{n})^{2} + (i_{d}(n) + b_{n})^{2}}$$

(3)

Fig. 2. Current distribution at the PCC of a multi-drive system with one diode rectifier and one SCR unit: (a) ideal currents and (b) system schematic.

Fig. 3. Illustration of the proposed current modulation waveform with selected harmonic cancellation for a single rectifier unit ( $\alpha_f = 0$  in the case of a diode rectifier).

In order to cancel out any *n*-th harmonics and maintain the desired fundamental content of the grid current as the modulation index, the transcendental equations given in (4) should be solved.

$$\begin{cases} i_g(1) = M_a \\ a_n = 0 \\ b_n + i_d(n) = 0 \end{cases}$$

$$(4)$$

where  $M_a$  is the desired modulation index.

## B. Novel Current Modulation Technique

Although an appropriate adjustment of the phase angle of the SCR unit can contribute to an improvement of the current quality, a new current modulation technique is further applied to each DC-DC converter in order to improve the current quality. In the new current modulation approach, certain low frequency harmonics in the three-phase input line currents can be eliminated by adding (or subtracting) phase-displaced current levels, thus leading to a better overall grid power quality. This technique is based on a pre-programmed switching pattern for the DC-link current to obtain input currents with zero content at those specific harmonics [7].

The basic idea of the proposed current modulation method for only one rectifier unit (SCR) is demonstrated in Fig. 3. For simplicity, the waveforms have been centralized in respect to the grid voltage to analyze the harmonic characteristics. In order to mitigate the triple harmonics, new added current levels should be repeated every 1/6 of the fundamental period. For instance, in the two sectors of 1 and 2 shown in Fig. 3, where in each sector  $i_{sa}$  is circulated through one of the other phase currents, if the new current level is added into sector 1, it should be exactly repeated in sector 2. This means that the frequency of the added pulses at the DC-link should be six times of the fundamental frequency. As it is shown in Fig. 3, the proposed current waveform consists of three square-wave signals with different magnitudes and angles. The first current waveform has the magnitude of  $I_{dcl}$  with the conduction phase angle of  $\alpha_0$  ( $\alpha_0 = \alpha_f + 30^\circ$ ). Notably, for a three-phase diode rectifier this conduction phase angle is constant,  $\alpha_0 = 30^{\circ}$ . The

second current waveform has the magnitude of  $I_{dc2}$  with the conduction phase angle of  $\alpha_I$ . The third current waveform has the magnitude of  $I_{dc2}$  but with a conduction phase angle of  $\alpha_2$ . According to (1) the input current harmonics can be calculated.

with

$$i_{s}(n) = \sqrt{(a_{n} + a'_{n})^{2} + (b_{n} + b'_{n})^{2}}$$

with

$$\begin{cases}

a'_{n} = \sum_{j=1}^{2} \frac{2I_{dc2}(-1)^{j+1}}{n\pi} \left[ -\sin(n\alpha_{j}) + \sin\left(2n\alpha_{0} - n\alpha_{j} + \frac{2\pi n}{3}\right) \right] \\

b'_{n} = \sum_{j=1}^{2} \frac{2I_{dc2}(-1)^{j+1}}{n\pi} \left[ \cos(n\alpha_{j}) - \cos\left(2n\alpha_{0} - n\alpha_{j} + \frac{2\pi n}{3}\right) \right]

\end{cases}$$

(5)

where  $i_a$  is the phase A current of the grid,  $a'_n$  and  $b'_n$  are the Fourier coefficients of the new added current levels that conduct at  $\alpha_1$  and  $\alpha_2$ , and  $\alpha_0 < \alpha_1 < \alpha_2 < \alpha_0 + 60^\circ$ . Hence, in order to individually cancel out up to two low order harmonics, e.g.,  $i_a(m)$  and  $i_a(k)$ , the following condition holds,

$$2\beta + \theta = 60$$

or  $2(\alpha_1 - \alpha_0) + (\alpha_2 - \alpha_1) = 60$  (6)

As for the three-phase diode rectifier  $\alpha_0 = 30^{\circ}$  ( $\alpha_f = 0^{\circ}$ ) and in that case  $a_n = a'_n = 0$ . Therefore, the harmonics of the input current represented in (5) can be simplified as:

$$i_{d}(n) = \frac{4}{n\pi} \left[ I_{dc1} \cos\left(\frac{n\pi}{6}\right) + I_{dc2} \cos\left(n\alpha_{1}\right) - I_{dc2} \cos\left(\frac{2\pi n}{3} - \alpha_{1}\right) \right]$$

(7)

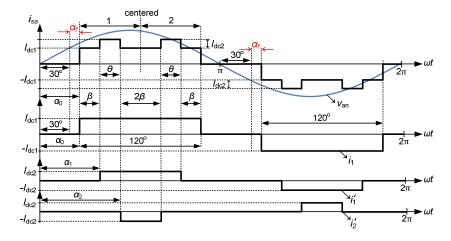

Hence, applying the proposed current modulation technique to both of the rectifier units can significantly improve the input current quality. Notably, the harmonics appearing in the supply line (i.e., *i<sub>g</sub>*) can be calculated as,

$$i_{g}(n) = \sqrt{(a_{n} + a'_{n})^{2} + (i_{d}(n) + b_{n} + b'_{n})^{2}}$$

(8)

# C. Optimum Harmonic Solution

The above illustrates the impact on the harmonics by selecting proper modulation parameters (amplitudes and switching angles) for the proposed current modulation scheme. However, an optimization for these parameters may result in a more suitable solution and also higher flexibility to eliminate the harmonics of interest. The following demonstrates the harmonic optimization solution considering the maximum allowable harmonic level defined by the application or the grid code. In other words, instead of fully nullifying the distortions, the harmonics could be reduced to acceptable levels by adding suitable constraints  $(L_n)$ . Then, an optimization problem  $(Obj_n)$  that searches a set of  $\alpha_n$  and  $I_{dc}$  values over the allowable intervals can be defined as,

$$\begin{cases} Obj_{1} = M_{a} - \left| i_{g}(1) \right| \leq L_{1} \\ Obj_{n} = \frac{\left| i_{g}(n) \right|}{\left| i_{g}(1) \right|} \leq L_{n} \end{cases}$$

$$(9)$$

Based on (9) an objective function  $F_{obj}$  has to be formed to minimize the error. The objective function plays an important role in leading the optimization algorithm to the suitable solution set. Here,  $F_{obj}$  is formed based on a squared error with more flexibility by adding constant weight values  $(w_n)$  to each squared error function [21]:

$$F_{obj} = \sum w_{n} \cdot \left(Obj_{n} - L_{n}\right)^{2} \tag{10}$$

Moreover, the  $THD_i$  restriction could also be the objective function or included in (10) and prioritized with a suitable weight value. In addition to the optimization constraint  $L_n$ , the following condition needs to be included as well:

$$\alpha_{\scriptscriptstyle 0} < \alpha_{\scriptscriptstyle 1} < \alpha_{\scriptscriptstyle 2} < \dots < \alpha_{\scriptscriptstyle m} < \alpha_{\scriptscriptstyle 0} + \frac{\pi}{3} \tag{11}$$

### III. SINGLE SWITCH THREE-PHASE BOOST RECTIFIER SYSTEM

In order to control the DC-link current shape and magnitude following the waveforms shown in Fig. 2, a boost converter topology based on the electronic inductor [17]-[20] concept is employed. Using the conventional boost topology has the advantage of boosting the output DC voltage to a suitable level when it is fed to an inverter. Moreover, as the DC-link current is controlled based on the load power, it has the advantage of keeping the  $THD_{\rm i}$  independent of the load profile.

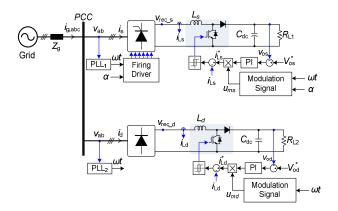

Fig. 4 depicts the block diagram of the overall control structure for the multi-rectifier units, where a hysteresis controller is adopted as the current controllers for the boost converters. The reference tracking performance of the current controller has an important role in the harmonic mitigation, thus fast current control methods such as hysteresis or deadbeat control should be employed. In order to synchronize the current controllers with the grid, for each rectifier unit a Second-Order Generalized Integrator (SOGI) based Phase

Fig. 4. Block diagram of the overall control structure implemented for the multi-rectifier system.

Locked Loop (PLL) system is adopted [22]. For simplicity, assuming a balanced system, only one line-to-line voltage is fed to the PLL. Therefore, the result will have a phase shift of 30° in respect to the phase voltage, which should be corrected within the reference current generator algorithm. In order to obtain a discretization for the PLL and the Proportional Integrator (PI) controller, a trapezoidal method is used. Moreover, as it can be seen from the system schematics shown in Fig. 4, the firing angle of the thyristor based rectifier (SCR) should be applied according to the phase detected by the PLL.

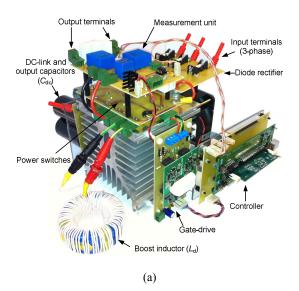

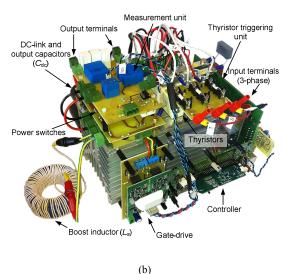

Fig. 5 shows the developed prototypes for the three-phase rectifier systems, where Fig. 5(a) depicts a photograph of the three-phase diode rectifier unit and Fig. 5(b) shows the three-phase SCR unit including the boost converter for each unit. Table I summarizes the employed modules in the implemented prototypes.

# IV. RESULTS

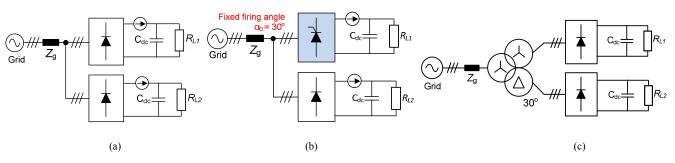

Simulations have firstly been done to verify the effectiveness of the proposed method. A comparison with other systems (see Fig. 6) in terms of harmonic mitigation has been carried out. For the first two systems shown in Fig. 6, a constant current source (implemented by a boost converter) at the DC-link side has been considered. Actually, the SCR without any current modulation in the second system has a fixed 30° phase-shift in respect to the other unit. The grid impedance  $L_g$  and  $R_g$  ( $Z_g$ ) as shown in Figs. 2 and 4 are set to 0.1 mH and  $0.01 \Omega$ , respectively. For the 12-pulse phaseshifting transformer impedance components are selected to be 160  $\mu$ H and 5 m $\Omega$ . The grid phase voltage is 220  $V_{RMS}$  and the grid frequency is 50 Hz. The output voltage of the boost converter is maintained at 700 V<sub>DC</sub> by employing a proportional integrator controller and a hysteresis controller is adopted as the current controller. A MATLAB function -"fmincon" has been used for optimization. The results are shown in Figs. 7 and 8.

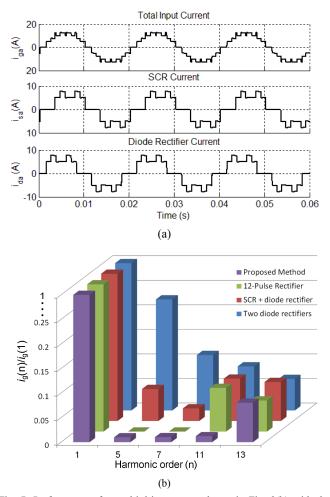

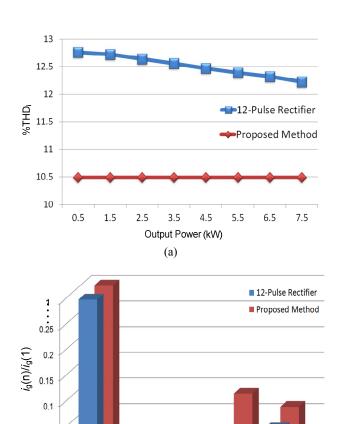

Since only the low-order harmonics are of much interest, the proposed method has been optimized according to (9)-(11) in order to attenuate the  $5^{th}$ ,  $7^{th}$  and  $11^{th}$  harmonics to be less than 1 % of the fundamental component (i.e., selected optimization constraints). In addition, THD<sub>i</sub> is also included in the objective function (THD<sub>i</sub> < 12.5 %). Fig. 7 (a) presents the

Fig. 5. Photograph of implemented single switch three-phase boost rectifier for (a) diode rectifier and (b) SCR system.

results of the multi-drive system shown in Fig. 2 (b) with the proposed modulation strategy, which confirms that a multi-level input current is achieved by the phase-shift based modulation scheme, contributing to a lower THD<sub>i</sub>. This benefit is further verified by the comparison with other configurations

TABLE I

EMPLOYED MODULES IN THE IMPLEMENTED PROTOTYPE (Fig. 5)

| Module                      | Part-Number                                   | Qty |

|-----------------------------|-----------------------------------------------|-----|

| Three-phase diode rectifier | SKD30                                         | 1   |

| Three-phase SCR             | SKKT 106/16                                   | 3   |

| IGBT-diode                  | SK60GAL125                                    | 2   |

| IGBT gate drive             | Skyper 32-pro                                 | 2   |

| SCR triggering circuit      | RT380T                                        | 1   |

| Current measurement         | HX-15                                         | 2   |

| Voltage measurement         | LV25-P                                        | 2   |

| SCR snubber branch          | $R_{snub} = 100 \Omega, C_{snub} = 0.1 \mu F$ | 6   |

| Controller                  | TMS320F28335                                  | 2   |

(see Fig. 6), where the low-order harmonics (5<sup>th</sup>, 7<sup>th</sup>, and 11<sup>th</sup>) have been controlled (optimized) to a relatively low level by the proposed method, as it is shown in Fig. 7(b). However, the 7<sup>th</sup> and the 11<sup>th</sup> harmonics are slightly higher than the optimization target (less than 1 %) due to the effect of the grid impedance.

In addition, the flexibility of the proposed method is demonstrated in another case study, where the  $THD_i$  is selected as the optimization objective function. It can be observed in Fig. 8(a) that a  $THD_i$  of 10.5 % is attained in the multi-drive system with the proposed method regardless of output power levels (load profiles) in contrast to the 12-pulse based drive system. Although some individual harmonics are higher when compared to the 12-pulse rectifier as shown in Fig. 8(b), the  $THD_i$  is minimized in contrast to that in Fig. 6(b). Table II summarizes the detailed harmonic content of the rectifier systems at a constant output power level of 5.5 kW.

It should be noted that the optimization was performed based on an assumption that each rectifier unit draws equal amount of current from the grid; otherwise, the rectified voltages  $V_{rec\_s}$  and  $V_{rec\_d}$  (see Fig. 4) are different due to the phase-shift and thus leading to different boost conversion gain ratio and may complicate the harmonic distributions.

In addition to the effect of the phase-shift, in real-world applications the two rectifier units do not necessarily operate at the same power level. Since the system is not dependent on the load profile, the power level itself is not the concern, and the ratio between output-power levels of the rectifier units are of importance. Therefore, as long as the following equation holds true, the rectifiers draw equal amount of current from the grid; otherwise it should be reflected in the optimization process in one of the objective functions.

Fig. 6. Different rectifier units: (a) two diode rectifiers, (b) one diode rectifier and one SCR with a fixed phase shift of 30° and (c) 12-pulse rectifier.

Fig. 7. Performance of a multi-drive system shown in Fig. 2(b) with the proposed method: (a) current waveforms and (b) comparison of the low-order harmonics with other configurations (see Fig. 4) at the total output power level of 5.5 kW.

$$\frac{P_{o_{-}d}}{P_{o_{-}s}} \times \cos(\alpha_f) = 1 \tag{12}$$

where  $P_{\text{o\_d}}$  and  $P_{\text{o\_s}}$  are the output power of the diode rectifier and SCR unit, respectively. Notably, to save computation complexity different pre-calculated current modulation parameters with their corresponding power ratios should be included as a look-up table in the controller. Therefore, by including a communication between each rectifier units suitable combination of the input currents at the PCC can be made under varied situation.

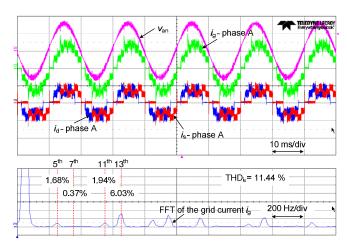

In order to verify the effectiveness of the proposed method, experimental tests have been carried out on a 5.5-kW multi-rectifier system (Fig. 5). Firstly, the control objective is to lower the THD<sub>i</sub> and also to reduce the  $5^{th}$ ,  $7^{th}$ , and  $11^{th}$  harmonics. It can be seen in Fig. 9 that the  $5^{th}$ ,  $7^{th}$ , and  $11^{th}$  – order harmonics are almost completely eliminated, since they are considered in the optimization function as shown in (10). In addition, a THD<sub>i</sub> of 11.5 % of the grid current is also obtained,

Fig. 8. Performance of the multi-drive system with the proposed method and the 12-pulse rectifier based system: (a) total input current THDi at varied power levels and (b) input current spectrums of the two systems at the total output power level of 5.5 kW.

7

Harmonic order (n) (b) 11

13

0.05

0

1

TABLE II. HARMONIC DISTRIBUTION OF DIFFERENT SIMULATED RECTIFIER SYSTEMS AT A TOTAL OUTPUT POWER LEVEL OF  $5.5\,\mathrm{kW}$ .

| AT A TOTAL COTTOT TO WER ELEVEL OF 3.3 KW. |                                                |                     |                      |                      |      |

|--------------------------------------------|------------------------------------------------|---------------------|----------------------|----------------------|------|

| System                                     | Harmonic Distribution and THD <sub>i</sub> (%) |                     |                      |                      |      |

| Configuration                              | $i_{g(5)}/i_{g(1)}$                            | $i_{g(7)}/i_{g(1)}$ | $i_{g(11)}/i_{g(1)}$ | $i_{g(13)}/i_{g(1)}$ | THDi |

| Two Diode<br>Rectifiers<br>(Fig. 6(a))     | 22.6                                           | 11.3                | 9                    | 6.4                  | 29.4 |

| SCR + Diode<br>Rectifier<br>(Fig. 6(b))    | 6.5                                            | 2.6                 | 8.6                  | 8                    | 15.6 |

| 12-Pulse<br>Rectifier<br>(Fig. 6(c))       | 0                                              | 0                   | 8.9                  | 6.3                  | 12.4 |

| <sup>1</sup> Proposed<br>Method            | 1                                              | 1                   | 1.2                  | 8                    | 12.3 |

| <sup>2</sup> Proposed<br>Method            | 2.6                                            | 0.95                | 1.7                  | 4.9                  | 10.5 |

Optimization objective is to minimize the low order harmonics including the THD<sub>i</sub> (see Fig. 7)

<sup>2.</sup> Optimization objective is to achieve a lower THD<sub>i</sub> (see Fig. 8(b))

Fig. 9. Experimental results (phase A) of the multi-drive system with the novel current modulation scheme at  $P_o \approx 5.5$  kW,  $V_o = 700$  V<sub>DC</sub>, targeting at reducing the low order harmonics and also a lower THD<sub>i</sub>: grid current  $i_g$  [10 A/div], grid phase voltage  $v_{an}$  [200 V/div], diode rectifier input current  $i_d$  [10 A/div], SCR unit input current  $i_s$  [10 A/div], and Fast Fourier Transform (FFT) analysis of the grid current [500 mA/div].

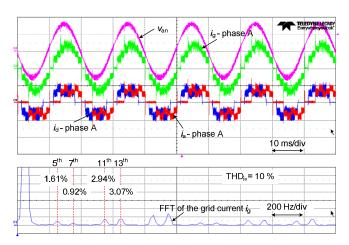

Fig. 10. Experimental results (phase A) of the multi-drive system with the novel current modulation scheme at  $P_o \approx 5.5$  kW,  $V_o = 700$  V<sub>DC</sub>, targeting at a minimized THD<sub>i</sub>: grid current  $i_g$  [10 A/div], grid phase voltage  $v_{\rm an}$  [200 V/div], diode rectifier input current  $i_d$  [10 A/div], SCR unit input current  $i_s$  [10 A/div], and Fast Fourier Transform (FFT) analysis of the grid current [500 mA/div].

when applying the novel modulation scheme to both rectifier units. The occurrence of the current spikes in the SCR current (e.g.  $i_s$ ) at the point of commutation is due to presence of the snubber branches in the SCR unit. In practice, to avoid SCR unit failures and to reduce the overvoltage to a reasonable limit an RC snubber branch is connected across each thyristor. In order to damp the current spikes, small AC-side inductors can be placed in series prior to the SCR unit.

To further validate the performance of the proposed method minimizing the  $THD_i$  was only considered as the optimization target. Fig. 10 presents the performance of the multi-rectifier system where a  $THD_i$  of around 10 % is achieved. At the same time, the low order harmonics are at relatively low levels. The results are quite in agreement with the simulations. Table III

TABLE III.

HARMONIC DISTRIBUTION OF DIFFERENT EXPERIMENTAL CASES FOR RECTIFIER SYSTEMS AT A TOTAL OUTPUT POWER LEVEL OF 5.5 kW.

| Optimization                    | Harmonic Distribution and THD <sub>i</sub> (%) |                     |                      |                      |      |

|---------------------------------|------------------------------------------------|---------------------|----------------------|----------------------|------|

| Objective                       | $i_{g(5)}/i_{g(1)}$                            | $i_{g(7)}/i_{g(1)}$ | $i_{g(11)}/i_{g(1)}$ | $i_{g(13)}/i_{g(1)}$ | THDi |

| <sup>1</sup> Proposed<br>method | 1.7                                            | 0.4                 | 1.9                  | 6                    | 11.4 |

| <sup>2</sup> Proposed method    | 1.6                                            | 0.9                 | 2.9                  | 3                    | 10   |

- Optimization objective is to minimize the low order harmonics including the THD<sub>i</sub> (see Fig. 9)

- 2. Optimization objective is to achieve a lower THD<sub>i</sub> (see Fig. 10)

TABLE IV. OPTIMIZED CALCUALTED MODULATION PARAMETERS (WITH  $M_a=1$ ).

| Optimization Objective       | Normalized Parameters |           |            |       |

|------------------------------|-----------------------|-----------|------------|-------|

|                              | $I_{dc1}$             | $I_{dc2}$ | $\alpha_1$ | $a_f$ |

| <sup>1</sup> Proposed method | 0.4                   | 0.22      | 50°        | 36°   |

| <sup>2</sup> Proposed method | 0.4                   | 0.2       | 50°        | 38.7° |

- Optimization objective is to minimize the low order harmonics including the THD<sub>i</sub> (see Fig. 9)

- 2. Optimization objective is to achieve a lower THD<sub>i</sub> (see Fig. 10)

summarizes the harmonic distribution of the conducted experimental cases.

As stated before, the pre-calculated switching parameters for the modulation strategy under different situations should be included as a look-up table in the controller. Table IV illustrates the estimated current modulation parameters for the two optimized cases with normalized amplitudes. Notably, the same parameters are applied to both rectifier units with a phase-shift of  $\alpha_{\rm f}$ .

To sum up, both the experimental tests and the simulations have demonstrated the effectiveness of current harmonic mitigations in multi-rectifier systems by means of: a) phase-shifting the currents drawn by SCR unit and b) a novel current modulation scheme at the boost inductor. Those can significantly contribute to a good power quality in both the single-drive and the multi-drive systems.

#### V. CONCLUSIONS

In this paper, a new harmonic elimination approach by combining different non-linear loads has been proposed for three-phase multi-drive systems, where also a Silicon Controlled Rectifier (SCR) is adopted. The proposed method can enable the selected harmonic cancellation by adjusting the phase angle of the SCR, and thus it can contribute to an improved power quality of the main grid. Moreover, in order to further reduce the harmonics, a novel modulation scheme has been applied to the DC-DC converter in the drive systems. The modulation scheme is able to eliminate the harmonics of interest by adding or subtracting specific current levels with respect to the conventional modulation approach. As a consequence, the combination of multiple non-linear loads with the new modulation scheme offers much flexibility as well as

cost-effectiveness for the multi-drive systems in terms of harmonic elimination. A main advantage of the proposed method is that the harmonic distribution remains the same regardless of load profile variations. Simulation and experimental results have verified the effectiveness of the proposed harmonic elimination approach.

#### REFERENCES

- [1] B.K. Bose, B.K., "Power electronics and motor drives recent progress and perspective," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 581-588, 2009.

- [2] J.W. Gray and F. J. Haydock, "Industrial power quality considerations when installing adjustable speed drive systems," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 646-652, May/Jun 1996.

- [3] D. Kumar and F. Zare, "Analysis of harmonic mitigations using hybrid passive filters," in *Proc. of PEMC*, 2014, pp. 945-951, 21-24 Sept. 2014.

- [4] F. Zare, "Harmonics issues of three-phase diode rectifiers with a small DC link capacitor," in *Proc. of PEMC*, 2014, pp. 912-917, 21-24 Sept. 2014.

- [5] G.K. Andersen and F. Blaabjerg, "Current programmed control of a single-phase two-switch buck-boost power factor correction circuit," *IEEE Trans. Ind. Electron.*, vol. 53, no. 1, pp. 263-271, Feb. 2006

- [6] J. W. Kolar and T. Friedli, "The Essence of Three-Phase PFC Rectifier Systems - Part I," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 176-198, Jan. 2013.

- [7] F. Zare, "A novel harmonic elimination method for a three-phase diode rectifier with controlled DC link current," in *Proc. of PEMC*, 2014, pp. 985-989, 2014.

- [8] C. Klumpner, F. Blaabjerg, and P. Thogersen, "Converter topologies with low passive components usage for the next generation of integrated motor drives," in *Proc. of PESC*, vol. 2, pp. 568-573, 2003.

- [9] H. Akagi and K. Isozaki, "A hybrid active filter for a three-phase 12-pulse diode rectifier used as the front end of a medium-voltage motor drive," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 69-77, Jan. 2012

- [10] M. Liserre, A. Dell'Aquila, and F. Blaabjerg, "An overview of three-phase voltage source active rectifiers interfacing the utility," in *Proc. of Power Tech Conf.*, pp. 1-8, vol. 3, 2003.

- [11] M. Liserre, F. Blaabjerg, and S. Hansen, "Design and control of an LCL-filter-based three-phase active rectifier," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1281-1291, 2005.

- [12] H. Akagi, "Modern active filters and traditional passive filter," Bulletin of the polish academy of sciences technical sciences, vol. 54, 2006.

- [13] J. W. Kolar and H. Ertl, "Status of the techniques of three-phase rectifier systems with low effects on the mains," in *Proc. of Telecommunication Energy Conf.*, pp. 1-16, 1999.

- [14] S. Hansen, P. N. Enjeti, H. Jae Hong, and F. Blaabjerg, "An integrated single-switch approach to improve harmonic performance of standard PWM adjustable speed drives," in *Proc. of IAS Annual Meeting*, vol. 2, pp. 789-795, 1999.

- [15] S. Hansen, P. Nielsen, and F. Blaabjerg, "Harmonic cancellation by mixing nonlinear single-phase and three-phase loads," *IEEE Trans. Ind. Appl.*, vol. 36, no. 1, pp. 152-159, Jan/Feb 2000.

- [16] S. Choi, B.S. Lee, and P.N. Enjeti, "New 24-pulse diode rectifier systems for utility interface of high-power AC motor drives," *IEEE Trans. Ind. Appl.* vol. 33, no. 2, pp. 531-541, Mar./Apr. 1997.

- [17] K. Mino, M. L. Heldwein, and J. W. Kolar, "Ultra compact three-phase rectifier with electronic smoothing inductor," in *Proc. of APEC*, 2005, pp. 522-528, 2005.

- [18] J. Salmon and D. Koval, "Improving the operation of 3-phase diode rectifiers using an asymmetrical half-bridge DC-link active filter," in *Proc. of IAS Annual Meeting*, vol. 4, pp. 2115-2122, 2000.

- [19] P. J. Grbovic, P. Delarue, and P. Le Moigne, "A Novel Three-Phase Diode Boost Rectifier Using Hybrid Half-DC-Bus-Voltage Rated Boost Converter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1316-1329, 2011.

- [20] C. Galea and L. Asiminoaei, "New topology of electronic smoothing inductor used in three phase electric drives," in *Proc. of EPQU*, pp. 1-6, 2011.

- [21] L. G. Franquelo, J. Napoles, R. C. P. Guisado, J. I. Leon, and M. A. Aguirre, "A Flexible Selective Harmonic Mitigation Technique to Meet Grid Codes in Three-Level PWM Converters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 3022-3029, 2007.

- [22] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A New Single-Phase PLL Structure Based on Second Order Generalized Integrator," in *Proc.* of PESC, 2006, pp. 1-6, 18-22 June 2006.