Aalborg Universitet

# Small Signal Modeling and Design Analysis for Boost Converter with Valley V2 Control

Leng, Minrui; Zhou, Guohua; Tian, Qingxin; Xu, Guodong; Blaabjerg, Frede

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2020.2990305

Publication date: 2020

**Document Version** Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Leng, M., Zhou, G., Tian, Q., Xu, G., & Blaabjerg, F. (2020). Small Signal Modeling and Design Analysis for Boost Converter with Valley V2 Control. *I E E E Transactions on Power Electronics*, *35*(12), 13475-13487. Article 9079211. Advance online publication. https://doi.org/10.1109/TPEL.2020.2990305

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

IEEE POWER ELECTRONICS REGULAR PAPER

# Small Signal Modeling and Design Analysis for Boost Converter with Valley V<sup>2</sup> Control

Minrui Leng, Student Member, IEEE, Guohua Zhou, Senior Member, IEEE, Qingxin Tian, Student Member, IEEE, Guodong Xu, and Frede Blaabjerg, Fellow, IEEE

Abstract - Recently, it has been reported that valley  $V^2$  control can be applied to the boost converter. However, the actual transient performance and design methodology are not clear due to insufficient knowledge about its small signal model. In this paper, a small signal model of valley  $V^2$  controlled boost converter is proposed, by combining average method and sampled-data method, possessing simplicity and it is accurate to half the switching frequency. Then, design guidance focused on dynamical performance and stability are provided. Moreover, compensator for the valley  $V^2$  controlled boost converter is discussed. The proposed small signal model and design guidelines are verified with experimental results. Results firstly indicate that for the valley  $V^2$  controlled boost converter, the inductor current information is contained in the control loop because of the discontinuous output voltage ripple, which is totally different with that in  $V^2$  controlled buck converter. And the equivalent series resistance as well as the duty ratio will affect the transient performance to some extent. Moreover, just by using the simple proportional integral compensator, the valley  $V^2$  controlled boost converter can be compensated, and it possesses fast transient performance. As for the stability issues, the ramp compensation is useful to eliminate the instability, improving the stability margin.

*Index Terms*: small signal model, valley  $V^2$  control, boost converter, design guidance, stability, compensator

# NOMENCLATURE

|                | NOMENCLATORE                        |

|----------------|-------------------------------------|

| ESR            | Equivalent series resistance.       |

| L              | Inductor.                           |

| С              | Output capacitor.                   |

| $i_{ m L}$     | Inductor current.                   |

| vo             | Output voltage.                     |

| i <sub>o</sub> | Load current.                       |

| $v_{\rm r}$    | Compensation ramp.                  |

| $v_{\rm c}$    | Control signal.                     |

| $V_{\rm ref}$  | Reference voltage.                  |

| R              | Load resistance.                    |

| $v_{\rm C}$    | Capacitor voltage.                  |

| $m_1$          | Increase slope of inductor current. |

Manuscript received October 6, 2019; revised February 04, 2020 and March 9, 2020; accepted April 20, 2020. This work was supported in part by the National Natural Science Foundation of China under Grant 61771405, the Sichuan Science and Technology Program under Grant 2019JDTDD0003, the Fundamental Research Funds for the Central Universities under Grant 2682019YQ02, the Doctoral Innovation Fund Program of Southwest Jiaotong University under Grant D-CX201918, and the State Scholarship Fund of China Scholarship Council (CSC). (*Corresponding author: Guohua Zhou*)

| $m_2$          | Decrease slope of inductor current.                   |

|----------------|-------------------------------------------------------|

| $m_{\rm v}$    | Decrease slope of output voltage during switch on.    |

| $m_{\rm v2}$   | Decrease slope of output voltage during switch off.   |

| d              | Duty ratio.                                           |

| $T_{\rm s}$    | Switching period.                                     |

| $m_{\rm s}$    | Slope of the compensation ramp.                       |

| $F_{\rm m}$    | Modulator gain.                                       |

| $F_{ m L}$     | Inductor current gain.                                |

| $F_{g}$        | Input feedforward gain.                               |

| $F_{\rm v}$    | Output feedback gain.                                 |

| $G_{ m vg}$    | Input voltage-to-output voltage transfer function.    |

| $G_{ m vd}$    | Duty ratio-to-output voltage transfer function.       |

| $G_{ m ig}$    | Input voltage-to-inductor current transfer function.  |

| $G_{\rm id}$   | Duty ratio-to-inductor current transfer function.     |

| $G_{ m vc}$    | Control-to-output voltage transfer function.          |

| $H_{c}$        | Sensing gain of inductor current.                     |

| $H_{\rm v}$    | Sensing gain of output voltage.                       |

| $H_{\rm vs}$   | Sample-and-hold gain of new output voltage $v'_{o}$ . |

| $H_{cs}$       | Sample-and-hold gain of inductor current.             |

| T(s)           | Loop gain.                                            |

| $f_{\rm RHPZ}$ | Frequency of right-half plane (RHP) zero.             |

|                |                                                       |

## I INTRODUCTION

The boost converter, known as the step-up converter, is the basic dc-dc converter with an output voltage higher than its input voltage [1]. A reliable boost converter has been widely used in industrial applications, such as uninterruptible power supplies, power systems, dc motor drives, telecommunication equipment, renewable energy system, etc. With the growing requirement for these power supplies, many efforts have been done to generate a higher regulated voltage [2], [3] and achieve good performance [4], [5].

Design and analysis of a boost converter are challenging because boost converter exhibits non-minimum phase behavior due to the existence of a right-half plane (RHP) zero when it operates in continuous conduction mode (CCM), which would limit the stability and transient response [6]. Recently, there have been many researches on nonlinear control techniques [7]-[10] and designing controllers [11]-[15] to remedy the effect of non-minimum phase behavior. Nonlinear control techniques possess fast response time. However, among these control techniques, sliding-mode control may suffer chattering characteristics, causing large output voltage ripple [7]; fuzzy control needs experience to design suitable parameters which is lacking of theoretical guidance [8]; robust control and predictive control perform well but have complicated calculations [9]. Moreover, there are state-plane based fast transient controls, such as natural switching surfaces, centric control, and so on. Ref. [12] proposed a boundary control scheme for boost converters

M. Leng, G. Zhou, Q. Tian, and G. Xu are with School of Electrical Engineering, Southwest Jiaotong University, Chengdu 611756, China (e-mail: mrleng\_pece@163.com; ghzhou-swjtu@163.com; qingxintianabc @163.com; xgd\_pece@163.com.

F. Blaabjerg is with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: fbl@et.aau.dk).

with enhanced performance using the natural switching surface. Ref. [13] proposed a novel pulse-width modulation (PWM) based geometric control scheme to obtain a reliable and consistent transient response, with an enhanced dynamic regulation. And the transient performance can be evaluated by the benchmarking tool mentioned in [14]. As for controllers, auto tuning methods for controllers are introduced to obtain a better performance and bring more design flexibility, but they seem to be more complicated than the traditional proportional integral (PI) or proportional integral differential (PID) compensator design procedure [15]. Ref. [16] describes a technique to modify the nonminimum phase boost converter to a minimum phase for a constant further implementing the input-output power load, linearization technique to stabilize the system. Aiming at stabilization of converter loaded with a constant power load, the concept of feedback linearization also provides a good idea for controlling boost converter. It would be helpful if the simple linear control applied to the boost converter could achieve good performance.

As generally acknowledged, the voltage mode controlled CCM boost converter is difficult to compensate because of the RHP zero, and the closed-loop bandwidth is restricted, which degrades the transient response [17]. For current-mode control, it makes loop compensation a little simpler [18] and improves the transient performance slightly, but fails to satisfy high demanding applications.  $V^2$  control, features simple implementation and ultrafast transient response, and it is popular for buck converters [19]-[21]. Compared with the current mode control,  $V^2$  control has the following three features [21]: 1) no current sensing network is required; 2) fast load transient characteristics with direct output voltage feedback; and 3) the outer-loop compensator is much simpler, usually a simple integrator is adequate. So  $V^2$  control is a popular control scheme in point-of-load converters and voltage regulators for microprocessor [19]. However, the traditional  $V^2$  control (peak  $V^2$  control) cannot be applied to boost converters due to the discontinuous ripple of output voltage. Ref. [22] has pointed out that valley  $V^2$  control is the duality of conventional  $V^2$  control, where the valley value of the output voltage is controlled to turn on the power switch. Then, it is indicated that the valley  $V^2$  controlled boost converter can be realized by analyzing the output voltage ripple carefully [23]. However, up to now, the analysis of transient response and design guidance for valley  $V^2$ controlled boost converter are not clear due to insufficient knowledge about the small signal model.

As for the modeling of  $V^2$  control, there are several published papers. Originating from the modified average model of peak current mode control [24], small signal of  $V^2$ controlled buck converter is discussed [25], [26], which is only accurate in the low frequency range. It is due to the reason that the modified average model of the peak current mode control only considers the current-sampling function while it does not consider the effect of the capacitor voltage, which is vital for  $V^2$  control. Moreover, models derived from discrete time method and Floquet theory are accurate which are based on the numerical analysis, but lack of physical meaning [27]. Ref. [28] uses sampled-data method to get the stability criterion of  $V^2$  control while provide a little design guideline of the controller. Krylov-Bogoliubov-Mitropolsky technique is accurate but its complexity is a hamper for practical use [29]. Considering the effect of the capacitor voltage, the small signal model is investigated based on the describing function method, and the optimal design strategy is given [30]. Then, internal and external ramp compensation are explored to provide stabilization and design flexibility [31], [32]. Nevertheless, these models are all for  $V^2$  controlled buck converter, which cannot be applied to model valley  $V^2$ controlled boost converter directly, because the output voltage ripples of boost converter and buck converter are totally different. Modelling and designing of valley  $V^2$ controlled boost converter have not been investigated clearly so far. And the discontinuous voltage ripple of the boost converter adds additional difficulties on the modeling.

The contribution of the paper is given as follows.

- (1) By analyzing the discontinuous output voltage ripple, small signal model of valley  $V^2$  controlled boost converter is firstly proposed by combining average method and sampled-data method, which is simple and accurate to half the switching frequency.

- (2) Based on the proposed model, it also firstly reveals that the inductor current information is contained in the control loop because of the discontinuous output voltage ripple. And the weight of the inductor current information related to ESR and duty ratio has effect on the transient performance, which is different from the  $V^2$  controlled converter with continuous output voltage ripple, like  $V^2$  controlled buck converter.

- (3) Moreover, stability as well as compensator are analyzed, providing design guidelines for practical applications.

The remaining of this paper is organized as follows. The output voltage ripple and operation principle of valley  $V^2$  controlled boost converter are expressed in section II. Small signal model of valley  $V^2$  controlled boost converter is presented in section III. Design considerations, including transient performance, stability and closed-up loop compensator, are stated in section IV. Simulation and experimental results are shown in section V. Section VI concludes the paper.

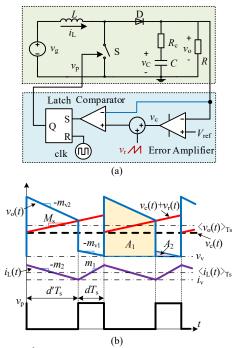

# II VALLEY $V^2$ CONTROLLED BOOST CONVERTER

It is investigated in [23] that the valley  $V^2$  control can be applied to the boost converter. The control diagram and operation waveforms of the valley  $V^2$  controlled boost converter are shown in Fig. 1, where an external compensation ramp  $v_r$  with the slope of  $M_s$  is introduced, providing stabilization and design flexibility. There are two discontinuities in the output voltage of the boost converter within each switching cycle due to the existing of ESR, resulting in discontinuous output voltage ripple. The valley  $V^2$ controller consists of an error amplifier, a comparator, a latch and a clock clk, which has two loops, to make it specifically, the inner voltage loop and the outer voltage loop. The output voltage is sensed as the feedback variable  $v_s$ , and the control signal  $v_c$  is obtained by compensating the error signal between the reference voltage  $V_{ref}$  and output voltage  $v_o$ . It should be noted that the valley voltage occurs actually at the switch ON instant. The discontinuity of the output voltage is caused by the  $R_c$ , and it is hard to control the exact point. So, the continuous part of the output voltage ripple is used to implement the control. It does not necessary to control the minimum value of  $v_0$  due to the effect of the  $R_c$ .

At the beginning of each switching cycle, clk resets the latch and the switch S is turned off by the driving signal  $v_{\rm p}$ , making  $i_1$  as well as  $v_0$  decrease linearly from the initial value. Under the assumption that the load resistance R is much larger than the ESR of the output capacitor, almost all of the inductor current ripple will flow through the output capacitor during the off time of switch S. Furthermore, as the switching frequency is usually much higher than the natural frequency of the output low-pass filter, the ripple voltage across the output capacitor is very small and can be ignored. Under these conditions, the output ripple voltage is simply the linear ripple voltage across the ESR, which is equal to the inductor ripple current times  $R_c$  [29]. When  $v_o$  decreases to  $v_c+v_r$ , S is turned on, resulting in an increase of  $i_{\rm L}$  while  $v_0$  decreases until the end of the present switching cycle. The increase and decrease slopes of inductor are  $m_1$  and  $m_2$ , while decrease slopes of the output voltage during on state and off state of switch S are  $m_{v1}$  and  $m_{v2}$  respectively, which can be denoted as:

$$m_1 = \frac{v_g}{L}, \quad m_2 = \frac{v_o - v_g}{L}$$

(1)

$$m_{\rm v1} = \frac{v_{\rm o}}{RC}, \ m_{\rm v2} = \frac{v_{\rm o} - v_{\rm g}}{L} R_{\rm c}$$

(2)

Fig. 1. Valley  $V^2$  controlled boost converter and its operation waveforms. (a) Valley  $V^2$  controlled boost converter. (b) Operation waveforms.

# III SMALL SIGNAL MODELING OF VALLEY V<sup>2</sup> CONTROLLED BOOST CONVERTER

# A Average Small Signal Model of Control Loop

As can be seen from Fig. 1(b), the average of the output voltage during one switching cycle can be expressed as:

$$\left\langle v_{o}\left(t\right)\right\rangle_{T_{s}} = v_{v} + \frac{A_{1} + A_{2}}{T_{s}}$$

$$\tag{3}$$

where  $T_s$  is the switching period,  $A_1$  and  $A_2$  denote areas shown in Fig. 1(b) and  $v_v$  is the minimum value of the output voltage during one switching period, which can be derived as:

$$v_{\rm v} = v_{\rm c} + M_{\rm s} d' T_{\rm s} - i_{\rm v} R_{\rm c} - m_{\rm vl} dT_{\rm s}$$

(4)

$$A_{1} = \frac{1}{2} \Big[ 2m_{v1}dT_{s} + 2i_{v}R_{c} + m_{v2}d'T_{s} \Big] d'T_{s}$$

(5)

$$A_2 = \frac{1}{2} m_{\rm vl} d^2 T_s^2 \tag{6}$$

In (4) ~ (6),  $i_v$  is the valley value of inductor current;  $i_v R_c$  describes the discontinuity of output voltage at the turn-on instant of switch S.

Adding small disturbance into (3), and making linearly approximation, the small signal expression of the duty ratio can be gotten as

$$\hat{d}(t) = F_{\rm m} \Big[ F_{\rm c} \hat{v}_{\rm c}(t) - F_{\rm L} \hat{i}_{\rm L}(t) - F_{\rm g} \hat{v}_{\rm g}(t) - F_{\rm v} \hat{v}_{\rm o}(t) \Big]$$

(7)

where  $F_{\rm m}$ ,  $F_{\rm L}$ ,  $F_{\rm g}$ ,  $F_{\rm v}$  denote the modulator gain, inductor current gain, input feedforward gain and output feedback gain respectively, which can be further expressed:

$$\begin{split} F_{\rm c} &= 1 \,, \ F_{\rm L} = DR_{\rm c} \,, \ F_{\rm g} = -\frac{(1-D)R_{\rm c}T_{\rm s}}{2L} \,, \\ F_{\rm m} &= \frac{1}{\left(M_{\rm s}T_{\rm s} - \frac{M_{\rm v2}T_{\rm s}}{2} + \frac{v_{\rm o}(1-D)T_{\rm s}}{RC} + I_{\rm L}R_{\rm c}\right)} \,, \\ F_{\rm v} &= \left(1 + \frac{(1-D)R_{\rm c}T_{\rm s}}{2L} + \frac{(2-3D)DT_{\rm s}}{2RC}\right) \,, \end{split}$$

where  $I_{\rm L}$  is the average of inductor current, D is the steady state duty ratio,  $M_{\rm y2}$  and  $M_{\rm s}$  are the steady state of  $m_{\rm y2}$  and  $m_{\rm s}$ .

It can be seen from (7) that in the valley  $V^2$  controlled boost converter, inductor current information is introduced, and  $F_L = DR_c$  can be regarded as its weight, which is different from the average small signal of  $V^2$  controlled buck converter.

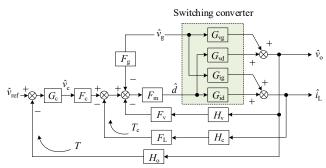

Based on the analysis, the small signal block diagram of valley  $V^2$  controlled boost converter can be obtained, as shown in Fig. 2. It includes the small signal model of the control loop as well as power stage transfer functions, where  $G_{\rm vg}$  is the input voltage-to-output voltage transfer function,  $G_{\rm ig}$  is the duty ratio-to-output voltage transfer function and  $G_{\rm id}$  is the duty ratio-to-inductor current transfer function. Since it is an average model, the condition "switching frequency" should be much higher than the *LC* resonant frequency" should be satisfied.

0885-8993 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on May 01,2020 at 06:31:39 UTC from IEEE Xplore. Restrictions apply. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2020.2990305, IEEE Transactions on Power Electronics

Fig. 2. Small signal block diagram of valley  $V^2$  controlled boost converter.

Based on the small signal diagram of valley  $V^2$  controlled boost converter, the control-to-output voltage transfer function  $G_{vc}$  can be expressed as:

$$G_{\rm vc} = \frac{F_{\rm c}F_{\rm m}G_{\rm vd}}{1 + F_{\rm m}G_{\rm vd}F_{\rm v}H_{\rm v} + F_{\rm L}F_{\rm m}G_{\rm id}H_{\rm c}}$$

(8)

where  $H_c$  and  $H_v$  are the sensing gain of inductor current and output voltage respectively.

# **B** Introduction of Sample-and-Hold Gains

Average small signal model represented in (8) may be accurate in the low frequency range while it fails to predict the performance in high frequency, because it is derived based on the concept of averaging. Sample-and-hold gain derived from the modified average model of peak current mode control in [24] is inapplicable, because it is based on the ripple of inductor current and does not consider the influence of the capacitor voltage feedback. So it is important to find out the sample-and-hold effect on the valley  $V^2$ controlled boost converter.

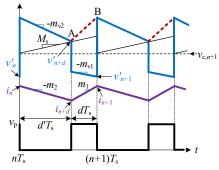

The output voltage ripple of valley  $V^2$  controlled boost converter has two discontinuities at the turn-on and turn-off instant of switch S, resulting in complexity as well as confusion of choosing exact discrete points for analyzing. Then, virtual slope is introduced by connecting point A and point B in Fig. 3. The new output voltage  $v'_0$  is continuous and can be used to get the sample-and-hold gain of the output voltage, which is reasonable because the control point A is contained.

Fig. 3. Operation waveforms of valley  $V^2$  controlled boost converter introducing virtual slope.

Denoting  $i_L$ ,  $v_C$  and  $v'_o$  at the beginning of the *n*th switching cycle are  $i_n$ ,  $v_n$  and  $v'_n$ . When the switch S is exactly turned on, the inductor current  $i_{n+d}$ , capacitor voltage  $v_{n+d}$  and output voltage  $v'_{n+d}$  can be expressed as:

$$i_{n+d} = i_n - m_2 d' T_s$$

$$v_{n+d} = v_n + \frac{i_n - i_o}{C} d' T_s - \frac{m_2}{2C} d'^2 T_s^2 \qquad (9)$$

$$v'_{n+d} = v_{n+d} + (i_{n+d} - i_o) R_s$$

At the end of the *n*th switching cycle, inductor current  $i_{n+1}$ , capacitor voltage  $v_{n+1}$  and output voltage  $v'_{n+1}$  can be deduced:

$$i_{n+1} = i_{n+d} + m_1 dT_s$$

$$v_{n+1} = v_n + \frac{i_n - i_o}{C} d'T_s - \frac{m_2}{2C} d'^2 T_s^2 - \frac{i_o}{C} dT_s \quad (10)$$

$$v_{n+1}' = v_{n+1} + (i_{n+1} - i_o) R_c$$

According to the operation waveforms, shown in Fig. 3, the control constraint can be expressed as:

$$(i_{n+d} - i_{o})R_{c} + v_{n+d} = v_{c,n+1} + v_{r}$$

(11)

It should be noted that the control signal  $v_{c,n+1}+v_r$  is regarded to be constant because it is a slower variable compared to  $v_o$  and  $v'_o$ . Then by introducing small disturbance into (9) ~ (11), the sampled-data voltage-feedback relationships can be described:

$$\hat{v}'_{n+1} = (1 - k_1 + k_2)\hat{v}'_n + k_1\hat{v}_{c,n+1}$$

(12)

where

$$k_{1} = \frac{2RCR_{c}(m_{2} + m_{1})(1 - D) + 4DV_{o} - 2V_{o} + m_{2}R(1 - D)^{2}T_{s}}{2RC(m_{2}R_{c} + M_{s})(1 - D) + m_{2}R(1 - D)^{2}T_{s}} ,$$

$$k_{2} = \frac{(1 - k_{1})(1 - D)T_{s}}{CR_{c}} .$$

Furthermore, the z-transform of (12) can be obtained and the control-to-output voltage transfer function  $G_{vc}(z)$  is derived as:

$$G_{\rm vc}(z) = \frac{k_1}{1 - (1 - k_1 + k_2)z^{-1}}$$

(13)

The continuous time representation of (13) can be obtained by taking the substitution  $z = e^{sT_s}$  and multiplying  $(1-e^{-sT_s})/(sT_s)[21]$ .

$$G_{\rm vc}(s) = \frac{k_1}{1 - (1 - k_1 + k_2)e^{-sT_{\rm s}}} \frac{1 - e^{-sT_{\rm s}}}{sT_{\rm s}}$$

(14)

As for the continuous  $v'_{o}$ , the representation of sample-hold effect  $H_v = H_{vs}$  can be derived by making  $H_c = 0$  based on Fig. 2 and (14).

$$H_{\rm vs} = \frac{F_{\rm m}G_{\rm vd} \left[1 - \left(1 - k_1 + k_2\right)e^{-sT_{\rm s}}\right]sT_{\rm s} - k_1 \left(1 - e^{-sT_{\rm s}}\right)}{k_1 \left(1 - e^{-sT_{\rm s}}\right)F_{\rm v}F_{\rm m}G_{\rm vd}}$$

(15)

It is indicated that the inductor current information is included in (7), which is introduced by the discontinuous output voltage ripple. So the sample-and-hold gain of inductor current should also be introduced, and  $F_{\rm L}$  can be regarded as its weight. According to (9) ~ (14), the continuous time control-to-inductor current transfer function  $G_{\rm lc}(s)$  can be described:

$$G_{\rm Lc}(s) = \frac{(1-\alpha)(1-e^{-sT_s})}{(1-\alpha e^{-sT_s})sT_s}$$

(16)

where

$$\alpha = \frac{M_{\rm s} - m_1}{M_{\rm s} + m_2}$$

0885-8993 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on May 01,2020 at 06:31:39 UTC from IEEE Xplore. Restrictions apply. Then, the expression of sample-hold effect  $H_c = H_{cs}$  for inductor current can be deduced by making  $H_v = 1$  based on Fig. 2 and (16).

$$H_{\rm cs} = \frac{F_{\rm m}G_{\rm id} \left(1 - \alpha e^{-sT_{\rm s}}\right) sT_{\rm s} - (1 - \alpha) \left(1 - e^{-sT_{\rm s}}\right) \left(1 + F_{\rm m}G_{\rm vd}F_{\rm v}\right)}{(1 - \alpha) \left(1 - e^{-sT_{\rm s}}\right) F_{\rm m}G_{\rm id}}$$

(17)

Therefore, for the valley  $V^2$  controlled boost converter, sample-hold effects including the virtual continuous  $v'_0$  and inductor current should be considered to obtain the proposed small signal model. The difference between the proposed model and the average model lies on the modeling of the inner loop. Therefore, they share the same design procedure for the outer voltage loop.

# IV DESIGN CONSIDERATION FOR VALLEY $V^2$ CONTROLLED BOOST CONVERTER

# A Analysis of Transient Performance and Stability

In order to make a comparison, the small signal model of the valley current-mode controlled boost converter is introduced which can be obtained by adopting the similar modeling process with peak current-mode control [24], expressed as:

$$\hat{d}(t) = F_{\rm ml} \Big[ \hat{i}_{\rm L}(t) - \hat{v}_{\rm c}(t) - F_{\rm gl} \hat{v}_{\rm g}(t) - F_{\rm vl} \hat{v}_{\rm o}(t) \Big]$$

(20)

where  $F_{m1} = \frac{1}{(M_1 - M_s)T_s}$ ,  $F_{g1} = \frac{T_s}{2L}$ ,  $F_{v1} = \frac{-(1 - D)^2 T_s}{2L}$ .

Moreover, the sample-hold effect of the valley current-mode controlled boost converter can be expressed as [24]:

$$H_{\rm cs} = \frac{sT_{\rm s}}{e^{sT_{\rm s}} - 1} \tag{21}$$

As a result, the control-to-output transfer function  $G_{vc}$  of the valley current-mode controlled boost converter can be obtained based on (8) by fixing  $F_c = -1$  and  $F_L = -1$ .

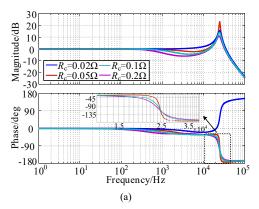

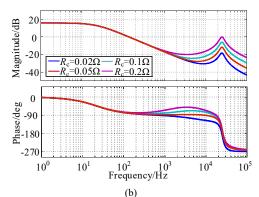

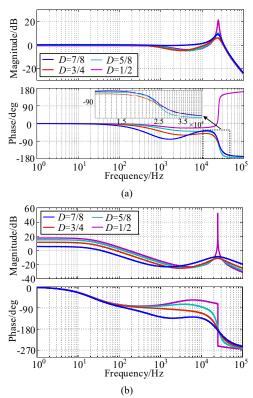

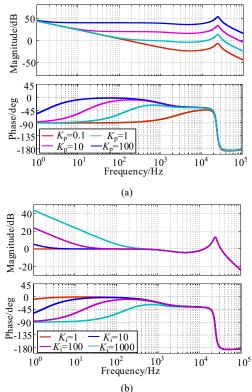

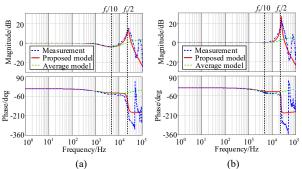

For both the valley current-mode controlled and valley  $V^2$ controlled boost converters, there are two loops: an inner loop and an outer voltage loop. The inner loop along with the converter power stage is the plant for the outer voltage loop of the converter. Therefore, the control-to-output transfer function of the converter is needed to design the compensator in the outer voltage loop. The differences of the valley current-mode control and valley  $V^2$  control are caused by the inner loop. As a result, bode plots of the control-to-output transfer function under two control methods are analyzed and compared. Bode plots of  $G_{vc}$  for the boost converter under two control methods with different  $R_c$  as well as different duty ratios (related to input voltages) are depicted in Fig. 4 and Fig. 5, respectively. In Fig 4, duty ratio D = 7/12. The switching frequency  $f_s = 50$  kHz, inductor  $L = 100 \mu$ H, the output capacitor  $C = 470 \ \mu\text{F}$ , the load  $R = 30 \ \Omega$ , output voltage  $v_0 = 24$  V.

The control-to-output voltage transfer function reflects the feedback of the inner loop. And the introduction of the inner loop will reduce the duty ratio-to-output voltage transfer function gain of the power stage. The more the reduction is, the more obvious the effect is. Compared the low-frequency gains of these two controls in Fig. 4, the magnitude of  $G_{vc}$  for valley  $V^2$  controlled boost converter is lower than the valley current-mode controlled boost converter, which indicates that the former one has stronger control for the output voltage than the later one. It is observed from Fig. 4 that the instability will occur in the valley  $V^2$  controlled boost converter when the small ESR is used, while the stability of valley current-mode controlled boost converter is not affected by the ESR. The bandwidth of valley  $V^2$  controlled boost converter is about 30kHz while the bandwidth of valley current-mode controlled boost converter is about 150Hz. The system bandwidth of valley  $V^2$  controlled boost converter is always wider than that of valley current-mode controlled boost converter, indicating a better transient performance. In Fig. 4(a), a pole will be introduced with the increase of ESR, which is different with the impact of ESR on the  $V^2$ controlled buck converter [30], because the information of the inductor current is included in the control loop of valley  $V^2$ controlled boost converter, whose weight is  $DR_c$ . Moreover, the phase margins of valley current-mode controlled boost converter with different  $R_c$  are the same with each other: 100°, which indicates that the ESR will not affect the stability. For the valley  $V^2$  controlled boost converter, when  $R_c = 0.05\Omega$ , the phase margin is close to  $0^{\circ}$ , when  $R_{\rm c} = 0.1\Omega$ , the phase margin is about 9°, when  $R_c = 0.2\Omega$ , the phase margin is about 15°. Phase margins of the valley  $V^2$  controlled boost converter with different  $R_c$  are slightly different but the bandwidths are almost the same with each other, which results in small differences in transient performance.

The valley  $V^2$  control is a ripple-based control, which uses the output voltage ripple to implement the control. So a relatively large equivalent series resistance (ESR) of the output capacitor should be used to ensure stable operation. As for the voltage ripple, although larger ESR will indicate larger voltage ripple, the voltage ripple may be increased with smaller ESR because the converter is unstable. There are three typical capacitors: OSCON, SP and Ceramic capacitors. The OSCON capacitor has relatively large ESR. The Ceramic and SP capacitors have relatively small ESR. Theoretically, the larger capacitor results in better filter effect. It should be noted that the selection of filter capacitor is a compromise of stability, voltage ripple, losses, compact, filtering effect. Designer should keep that in mind and can choose proper parameters to meet their requirements in different applications by the proposed model.

0885-8993 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on May 01,2020 at 06:31:39 UTC from IEEE Xplore. Restrictions apply.

Fig. 4. Bode plots of  $G_{vc}$  for the boost converter under two control methods with different  $R_c$  when D = 7/12 ( $v_g = 10$  V). (a) Valley  $V^2$  control. (b) Valley current-mode control.

Fig. 5. Bode plots of  $G_{vc}$  for the boost converter under two control methods with different duty ratios when  $R_c = 0.1 \Omega$ . (a) Valley  $V^2$  control. (b) Valley current-mode control.

In Fig. 5, it can be seen that with the large  $v_g$  (small *D*), the boost converter with valley  $V^2$  control or valley current mode control may operate in an unstable state. The location of the low-frequency pole in valley  $V^2$  controlled boost converter is relevant to the duty ratio *D*, shown in Fig. 5(a). The bandwidths of the valley  $V^2$  controlled boost converter with different *D* are almost identical, while the differences in phase margins indicate different transient performance. Moreover, the peak of valley current-mode controlled boost converter on the gain plot is very high and the phase drops very fast at half of the switching frequency when D = 0.5 ( $v_g = 12$  V), which means that the converter is operating in critical stable state. And the instability will occur when *D* is smaller than 0.5 ( $v_g > 12$  V). The peak of the valley  $V^2$  controlled boost converter on the gain plot is not so sharp compared with that of valley current-mode controlled boost converter. The phase character of valley  $V^2$  controlled boost converter indicates there is a RHP pole, so the instability may happen before *D* decreases to 0.5. In order to make it clearly, Fig. 6 is carried out when  $v_g = 11.5$  V (D = 7/12) which makes *D* close to 0.5.

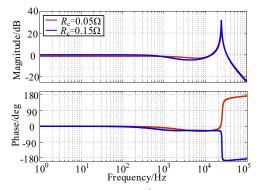

In Fig. 6, it can be seen that the instability may happen even with D > 0.5 ( $v_g < 12V$ ), but if the ESR is large enough, the valley  $V^2$  controlled boost converter can operate stably.

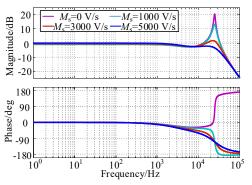

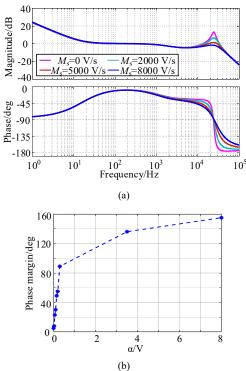

Moreover, except for using relatively large ESR, ramp compensation is also a good candidate for improving the stability. The Bode plots of  $G_{vc}$  under ramp compensation with different slopes  $M_s$ , can be obtained, as shown in Fig. 7.

It can be concluded from Fig. 7 that the valley  $V^2$  controlled boost converter is unstable without ramp compensation when  $v_g = 11.5$  V (D = 7/12),  $R_c = 0.05 \Omega$ . However, with the increase slope of ramp compensation, the converter is stabilized and the stability margin is extended, while the transient performance would be slowed down due to the increase of the phase margin or decrease of the bandwidth.

Fig. 6. Bode plots of  $G_{vc}$  for the valley  $V^2$  controlled boost converter under different  $R_c$  when D = 25/48 ( $v_g = 11.5$  V).

Fig. 7. Bode plots of  $G_{vc}$  for the valley  $V^2$  controlled boost converter under different compensation ramps when D = 25/48 ( $v_g = 11.5$  V),  $R_c = 0.05\Omega$ .

The model of valley  $V^2$  controlled boost converter is proposed by combining average method and the sampled-data method. The averaging method is used to reveal the low-frequency characteristic which is simple but fails to predict the subharmonic oscillation due to the neglection of the sampled output voltage and the control information. The sample-and-hold effect of the output voltage is introduced by transferring sampled-data model into the continuous domain. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2020.2990305, IEEE Transactions on Power Electronics

The instability can be predicted by introducing the sample-and-hold gains according to the sampled-data method. So, it is essential and simple to directly estimate the stability by investigating the discrete system expressed in (9) ~ (11), which is equivalent to investigate it in the Laplace domain. To investigate the relationship of  $R_c$ , the duty ratio D and the slope of ramp compensation  $M_s$  further, the stability analysis is carried out. According to (9) - (11) as mentioned before, the Jacobian matrix can be obtained as:

$$\mathbf{J} = \begin{bmatrix} J_{11} & J_{12} \\ J_{21} & J_{22} \end{bmatrix}$$

(22)

where  $J_{11} = \partial i_{n+1} / \partial i_n$ ,  $J_{12} = \partial i_{n+1} / \partial v_n$ ,  $J_{21} = \partial v_{n+1} / \partial i_n$ ,  $J_{22} = \partial v_{n+1} / \partial v_n$ .

The eigenvalues of the Jacobian matrix located inside the unit cycle indicate that the valley  $V^2$  controlled boost converter operates in stable state. Otherwise, it operates in unstable state.  $\lambda_1$  and  $\lambda_2$  are eigenvalues of the Jacobian matrix, which should be  $|\lambda_1| < 1$  and  $|\lambda_2| < 1$ . Then, the following critical condition should be satisfied to ensure a stable operation of the converter.

$$\frac{(4D-2)v_{o}}{(1-D)R} + m_{1}(1-D)T_{s} - 4M_{s}C - 2(m_{2}-m_{1})R_{c}C < 0 \quad (23)$$

It can be seen from (23) that the time constant of the capacitor is very important for stability. It indicates that, to ensure stability, the ESR can be reduced if a relatively large capacitance is used. But the increase of the capacitance will increase the volume of the system.  $R_c$  and C have similar tendency on the effect of the stability. And  $R_c$  is taken as example for investigating the effects on stability.

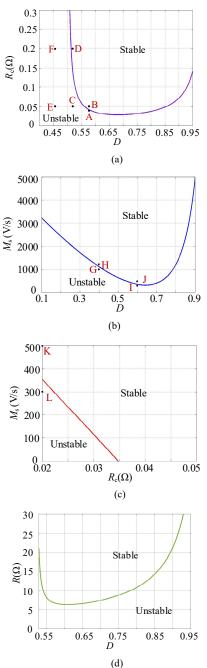

Stability regions between D and  $R_c$  under different ramp compensation can be carried out based on (23). By fixing  $M_s$ = 0 in Fig. 8(a), fixing  $R_c = 0.02\Omega$  in Fig. 9(b), fixing D = 0.6( $v_g = 9.6V$ ) in Fig. 8(c).

According to Fig. 8(a), it can be seen that without the ramp compensation, the valley  $V^2$  controlled boost converter may be unstable before *D* decreasing to 0.5, like points B, C, E and F. But when a large  $R_c$  is used, the converter can operate stably with D > 0.5 ( $v_g > 12$  V), like points A and D. Taking points G ~ L as example, in Fig. 8(b) and Fig. 8(c), it indicates that the ramp compensation can extend the stability region and make the valley  $V^2$  controlled boost converter operate stably with D < 0.5 or small  $R_c$ . Fig. 4 ~ Fig. 6 agree well with Fig. 8(a) and Fig. 7 agree well with Fig. 8(b), providing information for controller design and stability analysis. Points A ~ L will be further verified in the experimental part.

In (23), the load resistance *R* will also affect the stability, which reflects the influence of output voltage/output power on the stability. Fixing  $R_c = 0.1\Omega$ ,  $v_g = 10$  V, stability regions between the duty ratio and the load resistance is carried out, as shown in Fig. 8(d). Fig. 8(d) indicates that the converter is more likely to operate in stable state with relatively large load resistance.

We can improve the stability of the valley  $V^2$  controlled boost converter by choosing proper parameters according to the stability analysis. And a tradeoff between the stability margin, voltage ripple, losses and system volume should be considered according to actual requirement and practical design.

Fig. 8. Stability regions. (a)  $D-R_c$ ; (b)  $D-M_s$ ; (c)  $R_c-M_s$ ; (d) R-D.

## B Design of Compensator

As for the control of boost converter, voltage-mode and the current-mode controls are popular. For voltage-mode control, there are two conjugate poles and one RHP zero in the duty-cycle to the output voltage transfer function. A simple PI compensator is not enough for good performance and a complicated Type III compensation network is needed. With current-mode control, the RHP zero stays unchanged but the conjugate poles are spilt into a low-frequency pole and a high-frequency pole, making loop compensation simpler. Compared to the current-mode control,  $V^2$  control has fast

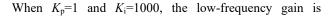

load transient characteristics with direct output voltage feedback. And the outer-loop compensator is much simpler, usually a simple integrator is adequate [21]. A number of previous studies have mentioned that the existence of the RHP zero in the boost converter limits the system bandwidth, degrading the transient performance greatly. However, for valley  $V^2$  controlled boost converter, the inner voltage loop possesses a relatively high bandwidth. Therefore, a simple PI compensator is considered for the outer-loop compensation. The transfer function  $G_{c}(s)$  of PI compensator can be expressed as  $(K_p + K_i / s)$ , with one zero and one optional pole, which can reduce the steady state error in output voltage. The outer voltage loop gain T(s) of valley  $V^2$  controlled boost converter can be represented as  $G_{c}(s)G_{vc}(s)H_{o}$ , where  $H_{o}$  is the sensing coefficient of output voltage. It can be known from above analysis that the low-frequency gain of  $G_{vc}(s)$  is 0 dB, which should be improved. Moreover, the phases in the low-frequency and medium-frequency are far away from 180°, but there is a phase lag in the half of the switching frequency caused by a pair of poles. Choosing the same parameters with that used in Fig. 4, and  $v_g = 10V$ ,  $R_c = 0.1\Omega$ ,  $v_0 = 24V, D = 7/12$ , the characteristics of loop gain T(s) with different PI parameters are investigated, as shown in Fig. 9.

It can be observed from Fig. 9 that  $K_p$  influences the bandwidth while  $K_i$  influences the low-frequency gain of valley  $V^2$  controlled boost converter. The compensator only affects the characteristics of T(s) in low-frequency and medium-frequency range. Based on the analysis,  $K_p$  and  $K_i$  can be chosen according to the practical requirements.

Fig. 9. Loop gain T(s) with different PI parameters. (a)  $K_i = 1000$ . (b)  $K_p = 1$ .

increased compared to the  $G_{vc}$ , which is benefit to the reduce of the steady state error. Moreover, with  $K_p=1$  and  $K_i=1000$ , the transient performance of the converter is better than that with  $K_p=0.1$  and  $K_i=1000$ ; the stability of the converter is better than that with  $K_p=10$ ,  $K_i=1000$ . Here,  $K_p=1$ ,  $K_i=1000$ are chosen for the following analysis. Designers can also choose PI parameters according to their specific requirements on the steady state error, the stability margin and transient performance. For a boost converter, the RHP zero always exits, created by lack of continuous current flowing to the output. In order to investigate the influence of RHP zero on the performance of the valley  $V^2$  controlled boost converter, the frequency of RHP zero [4] is calculated:

$$f_{\rm RHPZ} = \frac{R^2 v_{\rm g}^2}{2\pi L (R + R_{\rm c}) v_{\rm g}^2}$$

(24)

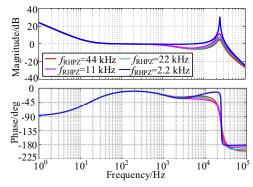

It can be seen in (24) that with a larger  $v_g$  and R or with a smaller L and  $v_o$ , the  $f_{RHPZ}$  is larger. The effect of RHP zero on the loop gain T(s) is investigated by describing T(s) with different  $f_{RHPZ}$ , as shown in Fig. 10.

As it can be seen from Fig. 10 that the low-frequency and medium-frequency characteristics of T(s) are almost invariant with the change of  $f_{RHPZ}$ . The RHP zero has only slightly effect on the bandwidth of the valley  $V^2$  controlled boost converter. However, the stability will be degraded with the decrease of  $f_{\rm RHPZ}$ . According to the above analysis, the increase of  $R_c$  or the introduction of the ramp compensation can improve the stability. Taking ramp compensation as an example, loop gain T(s) with different ramp compensation is shown in Fig. 11. It indicates that the ramp compensation can provide sufficient phase margin. However, adding too much compensation ramp will limit the outer loop bandwidth and degrade the transient performance. In order to investigate the relationship of compensation ramp, phase margin and bandwidth, the normalized ramp  $\alpha$  is defined as  $M_s/f_c$ , where  $f_{\rm c}$  is the cutoff frequency. According to the bode diagrams, the normalized curve can be obtained, as shown in Fig. 11(b). It can be concluded that the larger normalized ramp  $\alpha$ indicates larger phase margin, but the smaller transient response. The normalized curve can provide more intuitive design guides.

Fig. 10. Loop gain T(s) with different  $f_{RHPZ}$ .

In conclusion, the valley  $V^2$  controlled boost converter with PI compensator has wide bandwidth even though there is an RHP zero. The phase margin can be extended by increasing the  $R_c$  or ramp compensation while slightly degrade the

transient response. This part provides the design guidance for practical applications. Based on the above analysis, designers can choose proper circuit parameters to achieve different design objectives.

Fig. 11. Loop gain T(s) with different  $M_s$  and the corresponding normalized curve. (a) Loop gain T(s) with different  $M_s$ . (b) the normalized curve.

## V SIMULATION AND EXPERIMENTAL RESULTS

The experimental hardware prototype is set up. The diode is implemented with MBR20100 and the switch S is implemented with MOSFET IRF540N, where their GS pins are driven by IR2110. For the control circuit, LT1357 is used to implement the error amplifier to generate  $v_c$ . The logical control circuit comprises comparators LM319 and RS triggers CD4043. It is used to compare  $v_c$  with  $v_o$  to generate signals for the switch S. Moreover, the ramp compensation is introduced by the signal generator ATF20B. The parameters of the experimental prototype are chosen as the same with that in simulation: input voltage  $v_g$  varies from 10V ~13V; the output voltage  $v_o = 24V$ ; the power is about 20W; the switching frequency  $f_s = 50$  kHz.

To investigate the performance of the valley  $V^2$  controlled boost converter and to verify the theoretical analysis, the frequency characteristics, the stability and the transient performance are carried out.

#### A Verification of Frequency Characteristics

An experiment on the control-to-output voltage transfer function is measured by the Frequency Response Analyzer PSM1700, and the simulation results obtained based on the average model (8) and the proposed model, are depicted in Fig. 12, using the same circuit parameters with that in Fig. 4: inductor  $L = 100 \mu$ H, the input voltage  $v_g = 10V$ , output voltage  $v_o = 24V$ , the duty ratio D = 7/12.

Fig. 12. Control-to-output voltage transfer function based on experiment and small signal model with different parameters. (a)  $R_c = 0.1 \ \Omega$ . (b)  $R_c = 0.04 \ \Omega$ .

As it can be seen, (8) indicates a low-frequency model for the system, which is accurate to 1/10 switching frequency. Model (8) is essentially an average model if the sample-and-hold effects are not considered, which means that the average information of control variable is used to establish the model and the information of control instant is missed. The proposed model, considering the sample-and-hold effects of inductor current and output voltage, is accurate to 1/2 switching frequency, which can predict the subharmonic oscillation accurately. It can be seen that the proposed model accurately shows the high peak of the gain plot, predicting the character caused by the small ESR. There are the differences under high frequency ranges because the small signal model proposed in this paper is an improvement of the average small signal model, which is essentially derived based on the averaging concept. The high frequency dynamics in the power stage and the control part are ignored. The proposed model is still useful for the design of the valley  $V^2$  controlled boost converter and it is just a little more complicated than the average model.

# B Stability

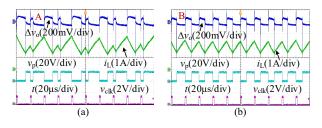

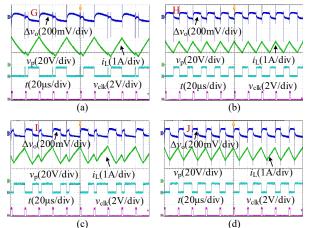

Fig. 13 shows the steady state waveforms of the valley  $V^2$  controlled boost converter under different  $R_c$  and different  $v_g$  when  $M_s = 0$ . It is concluded in Fig. 12 that when D = 7/12 ( $v_g = 10$  V), the converter is unstable with  $R_c = 0.04 \Omega$ , while it is in stable state with  $R_c = 0.05 \Omega$ . When D > 0.5, being close to 0.5 ( $v_g = 11.5$  V), relatively large ESR can make the converter stable. Moreover, when  $v_g = 13$  V (D < 0.5), the unstable phenomenon will always exist and the smaller ESR indicates more serious instability. Results obtained from Fig. 13 agree well with points A ~ F in Figs. 8(a).

Fig. 13. Steady state waveforms of the valley  $V^2$  controlled boost converter under different  $R_c$  and different  $v_g$ . (a)  $R_c = 0.04 \Omega$ , D = 7/12 ( $v_g = 10 V$ ). (b)  $R_c = 0.05 \Omega$ , D = 7/12 ( $v_g = 10 V$ ). (c)  $R_c = 0.05 \Omega$ , D = 25/48 ( $v_g = 11.5 V$ ). (d)  $R_c = 0.2 \Omega$ , D = 25/48 ( $v_g = 11.5 V$ ). (e)  $R_c = 0.05 \Omega$ , D = 11/24 ( $v_g = 13 V$ ). (f)  $R_c = 0.2 \Omega$ , D = 11/24 ( $v_g = 13 V$ ).

Fig. 14 shows the steady state waveforms of the valley  $V^2$  controlled boost converter under different *D* and different  $M_s$ , and fixing other parameters the same with that in Fig. 8(b). It is concluded in Fig. 14 that with the proper ramp compensation, the instability will be eliminated, which agrees well with the points G ~ J in Fig. 8 (b) as well as the points K and L in Fig. 8 (c). In Fig. 14 (a) and Fig. 14 (c), the 2-period attractor behavior appears and it is regarded as the subharmonic oscillation which should be avoided in the designing. The introduction of the ramp compensation can solve the instability caused by occasions with small ESR or D < 0.5.

Fig. 14. Steady state waveforms of the valley  $V^2$  controlled boost converter under different  $M_s$  and D. (a) D = 0.4,  $M_s = 1000$  V/s. (b) D = 0.4,  $M_s = 1200$  V/s. (c) D = 0.6,  $M_s = 300$  V/s. (d) D = 0.6,  $M_s = 500$  V/s.

# C Transient Performance

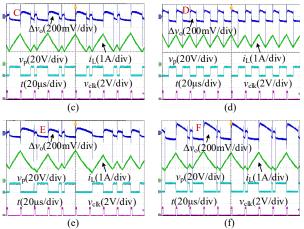

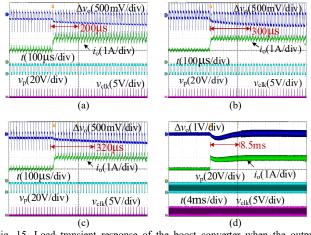

According to above analysis, the ESR and duty ratio D have effects on transient performance of the valley  $V^2$  controlled boost converter which is further studied. Fig. 15 (a) ~ Fig. 15 (c) show the load transient response under different  $R_c$  and D, when the output current steps from 1 A to 2 A. It can be seen that the recovery time with  $R_c = 0.1 \Omega$ ,  $v_g = 10 V$  and  $R_c = 0.2 \Omega$ ,  $v_g = 10 V$  are about 200 µs and 300 µs, while

it will take 320 µs for the valley  $V^2$  controlled boost converter to recover with  $R_c = 0.1 \Omega$ ,  $v_g = 5 V$ . As a result, with the smaller ESR or the larger  $v_g$  (smaller *D*), the valley  $V^2$ controlled boost converter is more likely to have a better load transient performance. Load transient response of the valley current-mode controlled boost converter is tested and the result is shown in Fig. 15(d) when  $R_c = 0.1 \Omega$ ,  $v_g = 10 V$ .

Observing from Fig. 15(a) and Fig. 15(d), the overshoot voltages of the valley  $V^2$  controlled and the valley current-mode controlled boost converter are 0.06 V and 0.4 V while their recovery time are 200 µs and 8.5 ms, respectively, which indicates a better load transient performance of the valley  $V^2$  controlled boost converter.

Fig. 15. Load transient response of the boost converter when the output current steps from 1A to 2A. (a) valley  $V^2$  control,  $R_c = 0.1 \Omega$ ,  $v_g = 10 V$ . (b) valley  $V^2$  control,  $R_c = 0.2 \Omega$ ,  $v_g = 10 V$ . (c) valley  $V^2$  control,  $R_c = 0.1 \Omega$ ,  $v_g = 5 V$ . (d) valley current-mode control,  $R_c = 0.1 \Omega$ ,  $v_g = 10 V$ .

In order to investigate the effects of ramp compensation on the transient performance, experiments under different  $M_s$  are carried out, and fixing other parameters the same with that in Fig. 8(b), as shown in Fig. 16, when the output current steps from 1 A to 2 A. When  $M_s$  is introduced, the instability phenomenon is eliminated. However, with a large  $M_s$ , the transient response may be degraded to some extent, when comparing Fig. 16(a) with Fig. 16(b).

| · Δν <sub>o</sub> (500mV/div)<br>· · · · · · · · · · · · · · · · · · · | Δν <sub>o</sub> (500mV/div)                            |

|------------------------------------------------------------------------|--------------------------------------------------------|

| $t(100 \mu s/div)$ $k_0(1A/div)$                                       | t(100µS/div)                                           |

| $v_{\rm p}(20V/{\rm div})$ $v_{\rm clk}(5V/{\rm div})$                 | $v_{\rm p}(20V/{\rm div})$ $v_{\rm clk}(5V/{\rm div})$ |

|                                                                        | (b)                                                    |

Fig. 16. Load transient response of the valley  $V^2$  controlled boost converter under different  $M_s$ . (a)  $M_s = 500$  V/s. (b)  $M_s = 2000$  V/s.

TABLE I summarizes some methods which are devoted to improve the transient performance of boost converter in recent years and concludes the results in this paper. In order to have a detailed comparison, the normalized values are introduced which make it possible to quantify the comparison for different methods. According to [14], the normalized values for recovery time and peak voltage drop can be calculated by:

$$\lambda_{t} = \frac{\Delta t}{2\pi\sqrt{LC}}$$

(24)

$\lambda_{v} = \frac{\Delta v}{V_{\text{ref}}}$ (25)

where  $\Delta t$  is the recovery time and  $\Delta v$  is the peak voltage drop.

We can also use the normalized value to express the load current step. The relationship of current step and  $Z_0$  is considered. The filter characteristic impedance can be denoted as:

$$Z_0 = \sqrt{\frac{L}{C}}$$

(26)

The normalizing current can be gotten:

$$\dot{u}_{\rm norm} = \frac{V_{\rm ref}}{Z_0} \tag{27}$$

Then, normalizing current step can be gotten as  $\Delta i/i_{norm}$ , which calculated and added in TABLE I.

It can be seen that the [4] and this work have larger normalized value of current step. This work has the smallest normalized values for recovery time and peak voltage drop, which means with relatively large current step, this work has good performance. Based on the normalized values, this work is proved to be attractive.

| References                                                                                                                  | [33]                                                                              | [4]                                                                     | [34]                                                                                         | [35]                                                                                       | This work                                                                                              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| Converter                                                                                                                   | Boost                                                                             | Boost                                                                   | Boost                                                                                        | Synchronous<br>boost                                                                       | Boost                                                                                                  |  |  |

| Controllers                                                                                                                 | Solid-duty-control                                                                | Constant off-time<br>digital<br>current-mode<br>control                 | Fixed-frequency<br>adaptive<br>off-time control                                              | Min-type<br>control                                                                        | Valley V <sup>2</sup><br>control                                                                       |  |  |

| Switching frequency                                                                                                         | 1.4 MHz                                                                           | 500 kHz                                                                 | 1 MHz                                                                                        | 150 kHz                                                                                    | 50 kHz                                                                                                 |  |  |

| Load transient<br>response;<br>Current step<br>(normalized values);<br>(recovery switching<br>cycles, normalized<br>values) | 7 μs;<br>(@ $\Delta i_o = 200 $ mA<br>(0.0167)<br>(10 switching<br>cycles, 0.163) | 64 μs;<br>$@\Delta i_0 = 3$ A (0.12)<br>(32 switching<br>cycles, 0.510) | 84 $\mu$ s;<br>(@ $\Delta i_o = 200 \text{ mA}$<br>(0.004)<br>(84 switching<br>cycles, 1.57) | 5  ms;<br>(@ $\Delta i_o = 270 \text{ mA}$<br>(0.0163)<br>(750 switching<br>cycles, 8.216) | 200 $\mu$ s;<br>( <i>a</i> ) $\Delta i_o = 1 \text{ A}$<br>(0.0192)<br>(10 switching<br>cycles, 0.147) |  |  |

| Output voltage drop<br>(normalized values)                                                                                  | 0.07 V (0.0029)                                                                   | 0.6 V (0.12)                                                            | 0.13 V (0.0062)                                                                              | 2 V (0.025)                                                                                | 0.06 V<br>(0.0025)                                                                                     |  |  |

| Output voltage                                                                                                              | 12 V                                                                              | 5 V                                                                     | 21 V                                                                                         | 80 V                                                                                       | 24 V                                                                                                   |  |  |

| Output capacitor                                                                                                            | 6.8 μF                                                                            | 100 µF                                                                  | 20 µF                                                                                        | 20 µF                                                                                      | 470 μF                                                                                                 |  |  |

| Complexity of<br>design                                                                                                     | Complex                                                                           | Relatively complex                                                      | Complex                                                                                      | Complex                                                                                    | Simple                                                                                                 |  |  |

## TABLE I Comparison of Recent works and This Work

# VI CONCLUSIONS

In this paper, the small signal model of the valley  $V^2$  controlled boost converter is firstly proposed by combing the average concept and the sampled-data modeling. Based on that, the characteristics of the valley  $V^2$  controlled boost converter is investigated, including the transient performance and the stability. Moreover, the PI compensator is adopted to the outer voltage loop of the valley  $V^2$  controlled boost converter. Simulation and experimental results have been presented to verify the theoretical analysis.

It is demonstrated that for the valley  $V^2$  controlled boost converter, the small signal model can be accurate to half the switching frequency. It can also conclude that the inductor current information is contained in the control loop because of the discontinuous output voltage ripple. And its weight, which is equal to the product of ESR and *D*, will influence the transient performance. Moreover, the valley  $V^2$  controlled boost converter can achieve good transient performance with PI compensator, which is simple to be designed. The ramp compensation can provide stability margin for the valley  $V^2$  controlled boost converter, but the transient performance will be degraded with a large ramp compensation.

The small signal modeling method and analysis can be extended to other boost-type converter, like buck-boost converter because of the similar output voltage ripple which is discontinuous, offering a modeling way for this type of converters. The valley  $V^2$  control is found to be an attractive solution to improve the transient performance of non-minimum phase converters.

#### REFERENCES

- A. Ghasemian, and A. Taheri, "Constrained near-time-optimal sliding-mode control of boost converters based on switched affine model analysis," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 887-897, Jan. 2018.

- [2] I. Yazici, and E. K. Yaylaci, "Fast and robust voltage control of DC–DC boost converter by using fast terminal sliding mode controller," *IET Power Electron.*, vol. 9, no. 1, pp. 120-125, Jan. 2016.

- [3] I. H. Kim, and Y. I. Son, "Regulation of a DC–DC boost converter under parametric uncertainty and input voltage variation using nested reduced-order PI observers," *IEEE Trans. Power Electron.*, vol. 64, no. 1, pp. 552-562, Jan. 2017.

- [4] K. Hariharan, S. Kapat, and S. Mukhopadhyay, "Constant off-time

digital current-mode controlled boost converters with enhanced stability boundary," *IEEE Trans. Power Electron.*, doi: 10.1109/TPEL.2019.2893428.

- [5] R. L. C. Olalla, I. Queinnec, and A. E. Aroudi, "Optimal state-feedback control of bilinear DC–DC converters with guaranteed regions of stability," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3868-3880, Oct. 2012.

- [6] V. Paduvalli, R. J. Taylor, and P. T. Balsara, "Analysis of zeros in a boost DC–DC converter: state diagram approach," *IEEE Trans. Circuits and Syst II: Express Briefs*, vol. 64, no. 5, pp. 550-554, May 2017.

- [7] R. J. Wai, and L. C. Shih, "Design of voltage tracking control for DC–DC boost converter via total sliding-mode technique," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2502-2511, Jun. 2011.

- [8] K. Viswanathan, R. Oruganti, and D. Srinivasan, "Nonlinear function controller a simple alternative to fuzzy logic controller for a power electronic converter," *IEEE Trans. Ind. Electron.*, vol. 52, no. 5, pp. 1439-1448, Oct. 2005.

- [9] Y. I. Son, I. H. Kim, D. S. Choi, and H. Shim, "Robust cascade control of electric motor drives using dual reduced-order PI observer," *IEEE Trans. Ind. Electron.*, vol. 62, no. 6, pp. 3672-3682, Jun. 2015.

- [10] P. Karamanakos, T. Geyer, and S. Manias, "Direct voltage control of DC–DC boost converters using enumeration-based model predictive control," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 968-978, Feb. 2014.

- [11] L. Guo, J. Y. Hung, and R. M. Nelms, "Evaluation of DSP-based PID and fuzzy controllers for DC-DC converters," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2237-2248, Jun. 2009.

- [12] J. M. Galvez, M. Ordonez, F. Luchino, and J. E. Quaicoe, "Improvements in boundary control of boost converters using the natural switching surface," *IEEE Trans. Power Electron.*, vol. 26, no. 11, pp. 3367-3376, Nov. 2011.

- [13] I. Galiano Zurbriggen, M. Ordonez and M. Anun, "PWM-geometric modeling and centric control of basic DC–DC topologies for sleek and reliable large-signal response," *IEEE Trans. Ind. Electron.*, vol. 62, no. 4, pp. 2297-2308, Apr. 2015.

- [14] I. G. Zurbriggen and M. Ordonez, "Benchmarking the performance of boost-derived converters under start-up and load transients," *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 3125-3136, May 2016.

- [15] M. Shirazi, R. Zane, and D. Maksimovic, "An auto tuning digital controller for DC–DC power converters based on online frequency response measurement," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2578-2588, Nov. 2009.

- [16] S. Arora, P. Balsara and D. Bhatia, "Input-output linearization of a boost converter with mixed load (constant voltage load and constant power load)," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 815-825, Jan. 2019.

- [17] S. W. Lee, Practical feedback loop analysis for voltage-mode boost converter, *Texas Instruments*, SLVA633, Jan. 2014.

- [18] J. Falin, T. Allag, and B. Hopf, Compensating the current-mode controlled boost converter, *Texas Instruments*, SLVA452, Jul. 2012.

- [19] D. Goder and W. R. Pelletier, " $V^2$  architecture provides ultra-fast transient response in switch mode power supplies," in *Proc. High Frequency Power Convers. Conf.*, 1996, pp. 19-23.

- [20] R. Redl and J. Sun, "Ripple-based control of switching regulators-An overview," *IEEE Trans. Power Electron.*, vol. 24, no. 12, pp. 2669-2680, Dec. 2009.

- [21] S. Tian, F. Lee, P. Mattavelli, K. Cheng, and Y. Yan, "Small signal analysis and optimal design of external ramp for constant on-time V<sup>2</sup> control with multilayer ceramic caps," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4450-4460, Aug. 2014.

- [22] G. Zhou, J. Xu, and J. Wang, "Constant-frequency peak-ripple-based control of buck converter in CCM: review, unification and duality," *IEEE Trans. Ind. Electron.*, vol. 61, no. 3, pp. 1280-1291, Mar. 2014.

- [23] G. Zhou, S. He, X. Chen, and H. Cui, "Can V<sup>2</sup> control be applied to boost converter?" *Electron Lett.*, vol. 50, no. 8, pp. 627-629, Apr. 2014.

- [24] R. B. Ridley, "A new, continuous-time model for current-mode control," *IEEE Trans. Power Electron.*, vol. 6, no. 2, pp. 271-280, Apr. 1991.

- [25] S. Qu, "Modeling and design considerations of V<sup>2</sup> controlled buck regulator," in *Proc. IEEE Appl. Power Electron. Conf.*, 2001, pp. 507-513.

- [26] W. Huang, "A new control for multi-phase buck converter with fast

transient," in Proc. IEEE Appl. Power Electron. Conf., 2001, pp. 273-279.

- [27] J. Cortes, V. Svikovic, P. Alou, J. Oliver, and J. Cobos, "Design and analysis of ripple-based controllers for buck converters based on discrete modeling and Floquet theory," *IEEE 14th Workshop on Control and Modeling for Power Electron*, 2013, pp. 1-9.

- [28] G. Zhou, S. He, X. Zhang, and S. Zhong, "Critical output-capacitor ESR for stability of V<sup>2</sup> controlled buck converter in CCM and DCM," *Electron Lett.*, vol. 50, no. 12, pp. 884-886, Jun. 2014.

- [29] J. Sun, "Characterization and performance comparison of ripple-based control for voltage regulator modules," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 346-353, Mar. 2006.

- [30] S. Tian, F. C. Lee, P. Mattavelli, and Y. Yan, "Small signal analysis and optimal design of constant frequency V<sup>2</sup> control," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1724-1733, Mar. 2015.

- [31] K. Cheng, F. Yu, F. C. Lee, P. Mattavelli, "Digital enhanced V<sup>2</sup>-type constant on-time control using inductor current ramp estimator for a buck converter with small ESR capacitors," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1241-1251, Mar. 2013.

- [32] Y. Y. Yan, F. C. Lee, S. L. Tian, and P. Liu, "Modeling and design optimization of capacitor current ramp compensated constant on-time  $V^2$  control," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 7288-7296, Aug. 2018.

- [33] H. H. Huang, C. L. Chen, D. R. Wu, and K. H. Chen, "Solid-duty-control technique for alleviating the right-half-plane zero effect in continuous conduction mode boost converters," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 354-361, Jan. 2012.

- [34] L. Cheng, J. H. Ni, Y. Qian, M. C. Zhou, W. H. Ki, B. Y. Liu, G. Li, and Z. L. Hong, "On-chip compensated wide output range boost converter with fixed-frequency adaptive off-time control for LED driver applications," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 2096-2107, Apr. 2015.

- [35] A. Sferlazza, C. Albea-Sanchez, L. Martínez-Salamero, G. García and C. Alonso, "Min-type control strategy of a DC–DC synchronous boost converter," *IEEE Trans. Ind. Electron.*, vol. 67, no. 4, pp. 3167-3179, Apr. 2020.

**Minrui Leng** (S'18) received the B.S. degree in electrical engineering and automation from Southwest Jiaotong University, Chengdu, China, in 2014, where she is currently working toward the Ph.D. degree in the School of Electrical Engineering.

She has been a Visiting Ph.D. Student with the Department of Energy Technology, Aalborg University, Aalborg, Denmark, since 2019. Her research interests include small signal modelling and

dynamical modeling of power converter, control techniques of power converter, stability of distributed power systems and model predictive control of dc microgids.

**Guohua Zhou** (S'10–M'12–SM'14) received the B.S. degree in electronic and information engineering and the M.S. and Ph.D. degrees in electrical engineering from Southwest Jiaotong University, Chengdu, China, in 2005, 2008, and 2011, respectively.

From March 2010 to September 2010, he was a Research Assistant with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Kowloon, Hong Kong. From

October 2010 to March 2011, he was a Visiting Scholar (also a Joint Ph.D. student) with the Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA. He is currently a Professor with the School of Electrical Engineering, Southwest Jiaotong University. His current research interests include modulation and control techniques of power electronics systems, dynamical modeling and analysis of switching power converters, and renewable energy applications of power electronics.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2020.2990305, IEEE Transactions on Power Electronics

Qingxin Tian (S'18) was born in Gansu Province, China, in 1994. He received the B.S. degree in electronic and information engineering from Southwest Jiaotong University, Chengdu, China, in 2017. He is currently working toward the Ph.D. degree in electrical engineering at Southwest Jiaotong University.

His research interests include renewable energy system, topology and control of multiport power

converters, energy management and control of dc microgrid system, modelling and control techniques of power converter.

**Guodong Xu** was born in Henan, China, in 1996, He received the B. S. degree in electrical engineering and automation from Huaqiao University, Xiamen, China, in 2018. He is currently working toward the M.S. degree in electrical engineering in the Southwest Jiaotong University, Chengdu, China. His current research interests include modeling and stability analysis of the cascaded system.

**Frede Blaabjerg** (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. He is honoris causa at University Politchnica Timisoara (UPT), Romania

and Tallinn Technical University (TTU) in Estonia.

His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications.

He has received 32 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, the Global Energy Prize in 2019 and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he serves a President of IEEE Power Electronics Society. He is Vice-President of the Danish Academy of Technical Sciences too. He is nominated in 2014-2019 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.