Aalborg Universitet

#### Investigation of Pd/MoO,/n-Si diodes for bipolar transistor and light-emitting device applications

Gupta, Gauray: D. Thammaiah, Shivakumar: Nanver, Lis Karen; Hueting, Raymond J

Published in: Journal of Applied Physics

DOI (link to publication from Publisher): 10.1063/5.0008015

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Gupta, G., D. Thammaiah, S., Nanver, L. K., & Hueting, R. J. (2020). Investigation of Pd/MoO\_/n-Si diodes for bipolar transistor and light-emitting device applications. Journal of Applied Physics, 128(5), Article 055703. https://doi.org/10.1063/5.0008015

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## Investigation of Pd/MoO<sub>x</sub>/n-Si diodes for bipolar transistor and light-emitting device applications

Cite as: J. Appl. Phys. **128**, 055703 (2020); https://doi.org/10.1063/5.0008015 Submitted: 17 March 2020 . Accepted: 21 July 2020 . Published Online: 07 August 2020

Gaurav Gupta 🔟, Shivakumar D. Thammaiah 🔟, Lis K. Nanver 🔟, and Raymond J. E. Hueting 🔟

#### ARTICLES YOU MAY BE INTERESTED IN

Reactivity of contact metals on monolayer WS<sub>2</sub> Journal of Applied Physics **128**, 055306 (2020); https://doi.org/10.1063/5.0014005

Tuning field-emission characteristics of ZnO nanorods through defect engineering via  $O^{\dagger}$  ion irradiation

Journal of Applied Physics 128, 054304 (2020); https://doi.org/10.1063/5.0010948

Progress and perspective on CsPbX<sub>3</sub> nanocrystals for light emitting diodes and solar cells Journal of Applied Physics **128**, 050903 (2020); https://doi.org/10.1063/5.0014045

J. Appl. Phys. **128**, 055703 (2020); https://doi.org/10.1063/5.0008015 © 2020 Author(s).

# Investigation of Pd/MoO<sub>x</sub>/n-Si diodes for bipolar transistor and light-emitting device applications

Cite as: J. Appl. Phys. **128**, 055703 (2020); doi: 10.1063/5.0008015 Submitted: 17 March 2020 · Accepted: 21 July 2020 · Published Online: 7 August 2020

Gaurav Gupta,<sup>1</sup> 🔟 Shivakumar D. Thammaiah,<sup>1,2</sup> 🔟 Lis K. Nanver,<sup>1,2</sup> 🔟 and Raymond J. E. Hueting<sup>1,a)</sup> 🔟

#### AFFILIATIONS

<sup>1</sup>MESA+ Institute for Nanotechnology, University of Twente, P.O. Box 217, 7500 AE Enschede, The Netherlands <sup>2</sup>Department of Materials and Production, Aalborg University, 9220 Aalborg, Denmark

<sup>a)</sup>Author to whom correspondence should be addressed: r.j.e.hueting@utwente.nl

#### ABSTRACT

Sub-stoichiometric molybdenum oxide (MoO<sub>x</sub>) has recently been investigated for application in high efficiency Si solar cells as a "hole selective" contact. In this paper, we investigate the electrical and light-emitting properties of MoO<sub>x</sub>-based contacts on Si from the viewpoint of realizing functional bipolar devices such as light-emitting diodes (LEDs) and transistors without any impurity doping of the Si surface. We realized diodes on n-type Si substrates using e-beam physical vapor deposition of Pd/MoO<sub>x</sub> contacts and compared their behavior to implanted p<sup>+</sup>n-Si diodes as a reference. In contrast to majority-carrier dominated conduction that occurs in conventional Schottky diodes, Pd/MoO<sub>x</sub>/n-Si diodes show minority-carrier dominated charge transport with *I*–*V*, *C*–*V*, and light-emitting characteristics comparable to implanted counterparts. Utilizing such MoO<sub>x</sub>-based contacts, we also demonstrate a lateral bipolar transistor concept without employing any doped junctions. A detailed *C*–*V* analysis confirmed the excessive band-bending in Si corresponding to a high potential barrier (>0.90 V) at the MoO<sub>x</sub>/n-Si interface which, along with the observed amorphous SiO<sub>x</sub>(Mo) interlayer, plays a role in suppressing the majority-carrier current. An inversion layer at the n-Si surface was also identified comprising a sheet carrier density greater than  $8.6 \times 10^{11}$  cm<sup>-2</sup>, and the MoO<sub>x</sub> layer was found to be conductive though with a very high resistivity in the 10<sup>4</sup>  $\Omega$ -cm range. We refer to these diodes as metal/non-insulator/semiconductor diodes and show with our device simulations that they can be mimicked as high-barrier Schottky diodes with an induced inversion layer at the interface.

Published under license by AIP Publishing. https://doi.org/10.1063/5.0008015

#### I. INTRODUCTION

The general trend in advanced Si devices is toward lower processing temperatures and more shallow junctions. This has shifted the research focus to the development of pn junctions that do not rely on the formation of a heavily doped surface region in the Si. Ultimately, it would be attractive to form junctions without any chemical doping at all. Schottky diodes fall in this category but conventional Schottky's are unattractive in many situations due to their relatively high saturation currents and poor minority-carrier injection. More specifically, for high gain bipolar transistors and for photodiodes where low dark currents are required, other solutions should be explored. One proposed solution<sup>1,2</sup> is the use of high-barrier Schottky diodes [see Figs. 1(a) and 1(b)] that significantly suppress the majoritycarrier injection from the substrate and provide a more favorable minority-carrier injection to total current ratio ( $\gamma$ ) in the diode over a wide voltage range. However, experimentally, the search for high-barrier Schottky diodes on Si has not been very successful so far.

Other methods have been found for creating  $p^+n$ -like junctions without doping the n-Si. Besides adopting high-barrier Schottky diodes, the hole injection into the substrate can also be promoted by forming a hole inversion layer at an insulator–Si interface that is contacted via doped regions, as, for example, in photodiodes that need to be sensitive up to the Si surface.<sup>3</sup> In this case, the holes gather at the surface due to the presence of negative charge in an insulating Al<sub>2</sub>O<sub>3</sub> layer. Alternatively, an inversion layer at the interface can be formed by employing a non-insulating layer such as pure boron (PureB) on top of the Si. In these so-called "PureB" diodes, the potential responsible for holding the holes at the interface proposedly originates from a high concentration of fixed negative charge created by the B-to-Si bonds.<sup>4</sup> Due to the overall attractive characteristics of this type of junction, it is now widely applied in high-performance photodiodes.<sup>5</sup>

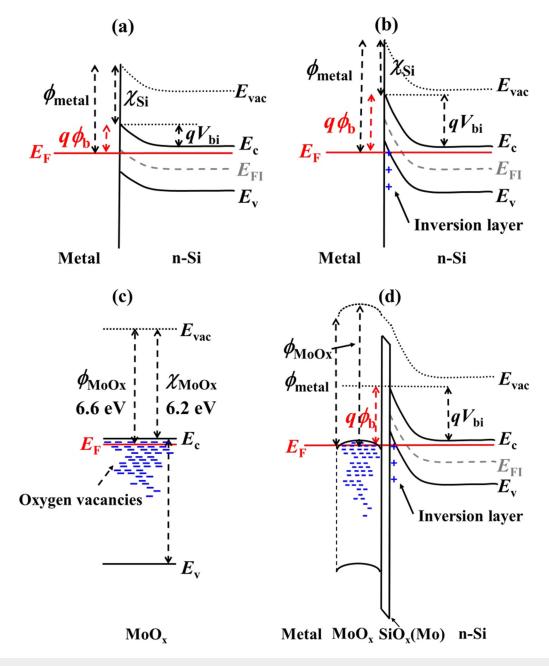

**FIG. 1.** Schematic energy band diagrams at thermal equilibrium for: (a) a conventional n-type Schottky diode, (b) a high-barrier n-type Schottky diode with an hole inversion layer at the interface,<sup>11</sup> (c) a vacuum evaporated  $MoO_x$  layer with oxygen vacancies,<sup>6,10</sup> and (d) metal/MoO<sub>x</sub>/n-Si interfaces.<sup>8,12</sup> As revealed by TEM analysis, an SiO<sub>x</sub>(Mo) interlayer (~2 nm) is formed as a result of a chemical reaction between Si and  $MoO_x$  during the deposition process.

In this paper, we study sub-stoichiometric molybdenumoxide (MoO<sub>x</sub>, with x < 3) based contacts on n-Si. MoO<sub>x</sub> has been reported to be a high work function ( $\phi_m$ ) material<sup>6-9</sup> that forms a diode to n-Si with low electron injection. Due to these properties, it has recently received attention in Si solar-cell research, being termed a "hole selective" contact.<sup>6,8</sup> More correctly, MoO<sub>x</sub> is a wide bandgap transition metal oxide  $(\text{TMO})^{10}$  with a bandgap  $E_{\text{g}} \sim 3.3 \,\text{eV}$ , and a relatively high electron affinity  $\chi > 6 \,\text{eV}$ , where an inherent oxygen deficiency results in a defect-band formation near the conduction band<sup>6</sup> as illustrated in Fig. 1(c). Thin MoO<sub>x</sub> layers are, therefore, treated as (semi-) metals with a high  $\phi_{\text{m}}$ .

The presence of a hole inversion layer at the  $MoO_x/n$ -Si surface [see Fig. 1(d)] was previously investigated using material characterization approaches such as photoelectron spectroscopy, in conjugation with capacitance–voltage (*C*–*V*) measurements.<sup>12,13</sup> In contrast to these methods, we recently performed *I*–*V* measurements along the Si interface of Pd/MoO<sub>x</sub>/n-Si devices using dedicated electrical test structures<sup>14</sup> to directly monitor any inversion, but we were only able to conclude that if an inversion layer was present it would have a sheet resistance higher than ~50 kΩ/□. Importantly however, we further found that the diode *I*–*V* characteristics are similar to those of implanted p<sup>+</sup>n reference counterparts, indicating a strong suppression of the electron injection into the MoO<sub>x</sub> layer. In addition, although the MoO<sub>x</sub> was conductive, we obtained a very high resistivity with values greater than about  $10^4 \Omega$ -cm.

In this paper, we confirm the presence of an inversion layer at the Pd/MoO<sub>x</sub> interface to n-Si as observed in PureB/Si diodes.<sup>4</sup> The origin of the hole inversion layer in the Pd/MoO<sub>x</sub>/n-Si and PureB (metal/B/n-Si) diodes may be quite different, but a common property is that the layer on the Si is conductive albeit with a very high resistivity. Therefore, we will refer to these diodes here as metal/non-insulator/semiconductor (MnIS) diodes. We examine here the bipolar capabilities of experimental MoO<sub>x</sub> MnIS diodes by comparing electrical and optical characteristics to those of implanted p<sup>+</sup>n reference diodes realized on the same wafer. This includes measurement of proof-of-concept surface barrier transistors (SBTs).<sup>15</sup> In addition, using technology computer-aided design (TCAD) simulations and numerical calculations, we examine whether or not such MnIS diodes can effectively be modeled as high-barrier Schottky diodes.

#### II. HIGH-BARRIER SCHOTTKY CONTACTS: BACKGROUND INFORMATION

Conventionally, Schottky diodes are treated as unipolar devices where the current is governed by thermionic(-field) emission (TE) of majority carriers from the substrate to the metal at the metal-semiconductor (MS) interface, while diffusion of minority carriers from the metal to the semiconductor can be ignored at low injection.<sup>16,17</sup> Theoretically, the situation would be different for a Schottky diode with high potential barrier  $(\phi_{\rm b})$  as illustrated in Figs. 1(a) and 1(b). In that case, the TE component can be suppressed to the extent that it becomes comparable to (or even lower than) the diffusion current. Moreover, as a result of extreme band bending, an inversion layer can be induced at the MS interface,<sup>1,18</sup> which helps in sustaining the minority diffusion current even at high bias. In contrast, in conventional Schottky diodes, the diffusion current will readily be limited by series resistance and/or by a poor supply of minority carriers from the contact. The high-barrier contact, also referred to as a bipolar-mode Schottky contact,<sup>19</sup> can have a significant minority-carrier injection ratio,  $\gamma$ , in the whole forward voltage range and, therefore, may enable applications that cannot be served by conventional Schottky counterparts.<sup>1,7</sup>

Early reports on the applications of such a high-barrier contact can be traced back to 1953 when Bradley proposed the concept of the surface barrier transistor (SBT) in Ge.<sup>15</sup> The SBT utilizes the metal-induced inversion charge to obtain bipolar

currents suitable for transistor operation without creating any chemically doped regions.

For an n-type semiconductor, the inversion layer is induced and/or minority-carrier effects become important provided that<sup>1,11</sup>

$$q\phi_{\rm bn} > E_{\rm g} - kT\ln\frac{N_{\rm v}}{N_{\rm d}},\tag{1}$$

where  $\phi_{\rm bn}$  is the barrier height for electrons,  $E_{\rm g}$  is the semiconductor bandgap, k is the Boltzmann constant, T is the temperature,  $N_{\rm v}$  is the valence band effective density of states,  $N_{\rm d}$  is the donor doping density, and q is the elementary charge. Equation (1) basically states that the induced inversion charge (in our case hole) density should be higher than the background doping density of the substrate.

Despite the early interest, after the invention of the planar silicon bipolar junction technology, inversion-layer-based device concepts have not attracted much attention. Only recently, due to the strong technological advancement in nanoscale semiconductor devices, alternatives to conventional doping are being sought. In this context, high-barrier MS contacts could be relevant for electrostatic doping (ED).<sup>11,20</sup> In ultra-thin body (UTB) devices, such 2D surface inversion could effectively result in volume inversion.<sup>21</sup> Both in bulk and UTB semiconductors, such Schottky contacts could be interesting for realizing dopant-free electrical and optical devices. Previously, we reported on minority-carrier effects in Al/ p-Si diodes, where  $\phi_b$ , ~0.78 V, was moderately high.<sup>2</sup> It is, therefore, worthwhile to investigate in this work if an extreme work function property of MoO<sub>x</sub> could be exploited to realize high-barrier Si diodes with bipolar conduction properties.

#### **III. EXPERIMENTAL PROCEDURE**

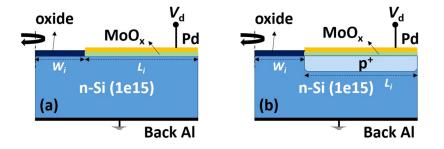

The basic device structure is shown in Fig. 2 for our ringshaped test structures used for both diode and sheet resistance measurements.<sup>14</sup> For C-V measurements, large square-shaped structures with an area of  $A_{\rm E} = 3.1 \times 10^{-3} \, {\rm cm}^2$  were used. Large structures suitable for measuring lateral bipolar transistors and light emission were also included. The substrates used in this work are n-type (100) Si wafers with a resistivity of  $1-10 \Omega$ -cm covered with a 235-nm-thick thermal oxide. Implantations of B<sup>+</sup> annealed in argon at 950 °C were used to form p<sup>+</sup> regions with a junction depth of  $0.5 \,\mu\text{m}$  and a surface doping of  $10^{19} \,\text{cm}^{-3}$ . Windows were then wet-etched in the oxide to give access to both implanted and non-implanted regions. A resist coating suitable for liftoff was used to pattern a layer stack of Pd/MoO<sub>x</sub> deposited in an e-beam physical vapor deposition (EBPVD) system. For the  $MoO_x$  layer, a 99.95% pure material from Kurt J. Lesker in 3-6 mm large pieces was placed in a Fabmate crucible of 99.95% elemental carbon. The MoO<sub>x</sub> layer with a targeted thickness of  $\sim$ 7–8 nm was grown at an evaporation rate of about 0.05 nm/s. Before deposition, the evaporation chamber was pumped down to the base pressure of about  $1.5 \times 10^{-7}$  mbar. The MoO<sub>x</sub> layer was then capped with a Pd layer about 120 nm thick in the same deposition chamber without breaking the vacuum. A lift-off process was used to remove the Pd/  $MoO_x$  layer stack at places other than the oxide windows. As a last step, the backside of the substrate was coated with Al.

**FIG. 2.** (a) Schematic cross sections of the fabricated ring-shaped devices: (a) a Pd/MoO<sub>x</sub>/n-Si diode and (b) an implanted p<sup>+</sup>n Si diode, both with a ring length  $L_i = 200 \,\mu\text{m}$ , width  $W_i = 64 \,\mu\text{m}$ , and area  $A_{\rm E} = 2 \times 10^{-3} \,\text{cm}^2$ . The vertical axis of symmetry is indicated on the left-hand side by a dashed line.

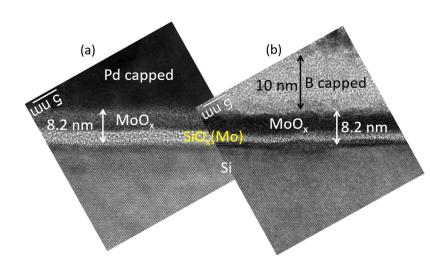

The Pd has a relatively low resistivity and this prevents the use of the structures described above to measure the sheet resistance of the inversion layer along the surface of the Si. Therefore, another sample was prepared where the Pd was replaced by a 10-nm-thick B (boron) layer. The B is known to be chemically very inert in many situations<sup>5</sup> and is expected to protect the MoO<sub>x</sub> from oxidation in air. Moreover, the resistivity of B is so high, >500  $\Omega$ -cm, that it is not likely to influence the sheet resistance measurement.<sup>22</sup> For the B deposition, a 99.5% pure material from Kurt J. Lesker in the form of cylindrical ingots was utilized. No thermal annealing was performed on any of the prepared samples. The structure of the fabricated layer stacks was examined using transmission electron microscopy (TEM, Philips CM300ST-FEG).

We carried out all electrical measurements in the dark and on a temperature-controlled chuck. The electrical measurements were performed using a Keithley 4200 semiconductor characterization system with a preamplifier. An Avaspec UV-Vis/NIR spectrometer from Avantes was used for the optical spectrum measurements. A cooled InGaAs detector based camera (XEVA-320 from Xenics) was used to capture IR micrographs. TCAD simulations wherever mentioned were performed using a Sentaurus device simulator.<sup>23</sup>

#### IV. RESULTS

TEM images of the  $Pd/MoO_x/n-Si$  and  $B/MoO_x/n-Si$  layer stacks are shown in Fig. 3. At the interface with the Si, we observed

an amorphous interlayer of about 2 nm thick in both cases. Such a layer was also reported in other studies,<sup>12</sup> where energy-filtered TEM (EF-TEM) analysis revealed a composition of Si, O, and Mo atoms, referred to as a hybrid a-SiO<sub>x</sub>(Mo). The accompanying SiO<sub>x</sub> (Mo) interlayer, which is possibly formed during the deposition of MoO<sub>x</sub> on Si, could have multiple roles in the charge carrier transport in our devices such as passivating the Si surface, hence suppressing the electron current and inducing a hole inversion layer. This is illustrated in the band diagram shown in Fig. 1(d). The bipolar-mode diode characteristics of the MoO<sub>x</sub> MnIS diodes as studied by electrical and light-emission measurements will be treated in Secs. IV A–IV E.

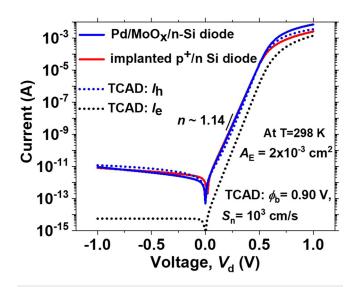

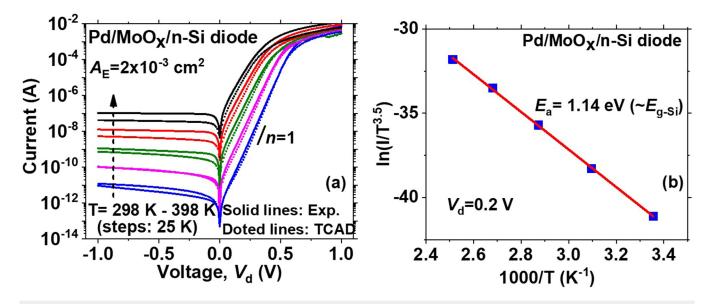

#### A. Diode I-V(-T) characteristics

Typical *I*-*V* characteristics of the fabricated Pd/MoO<sub>x</sub>/n-Si MnIS diodes are shown in Fig. 4. The diode displays a high rectification of  $\sim 10^8$  at  $V_d = \pm 1$  V, a very low leakage current density of about 5 nA/cm<sup>2</sup> and an ideality factor  $n \sim 1.14$ . The *n* value close to unity indicates that charge transport in the diode is mainly governed by processes such as drift-diffusion or thermionic emission. The small non-ideality could be attributed to process related defects or contamination.

The I-V characteristics of an implanted  $p^+n$  reference diode are also shown in Fig. 4. The current levels of the two diodes are practically identical. In the latter, the current is diffusion limited

FIG. 3. TEM cross-sectional images of the fabricated samples: (a)  $Pd/MoO_x/n-Si$  and (b)  $B/MoO_x/n-Si$ .

**FIG. 4.** *I–V* characteristics of a fabricated Pd/MoO<sub>x</sub>/n-Si diode and implanted p<sup>+</sup>n Si reference diode at room temperature. For comparison, TCAD simulation data of a Si Schottky diode with identical geometry modeled using  $\phi_{\rm b} = 0.90$  V and  $S_{\rm n} = 10^3$  cm/s is shown.

and the hole injection is dominant because the Gummel number of the  $p^+$  region is about 10–100 times higher than the substrate Gummel number. Moreover, the hole diffusion current of the two diodes is expected to be the same as both are determined by the same substrate Gummel number. This implies that the hole current,  $I_{\rm h}$ , is dominant even in the Pd/MoO<sub>x</sub>/n-Si diode and the electron current,  $I_{\rm e}$ , is of the same order or less. This also indicates the role of a high potential barrier at the MoO<sub>x</sub>/n-Si interface in suppressing the majority-carrier (electron) TE and that of a hole inversion layer at the interface in supplying the required minority carriers for the diffusion current. In addition, the passivating nature of a MoO<sub>x</sub>-based contact on Si,<sup>12,24</sup> possibly originating from the observed SiO<sub>x</sub>(Mo) interlayer and associated low surface recombination velocity, could also play a role in suppressing the TE further as confirmed by our TCAD simulations.

Our TCAD simulations in which we mimicked the Pd/MoO<sub>x</sub>/ n-Si diode as a Si Schottky diode showed good agreement with the experimental results as indicated in Figs. 4 and 5(a). The Schottky electrode was modeled using the lower limit of the barrier height,  $\phi_{\rm b} = 0.90$  V, that was extracted from the *C*-*V* analysis in Sec. IV C, and at the interface an effective surface recombination velocity for electrons,  $S_{\rm n} = 10^3$  cm/s, was applied. This value of  $S_{\rm n}$  is as much as three decades lower than what is normally found for clean metal-silicon interfaces but it is typical for passivated SiO<sub>x</sub>/Si interfaces.<sup>25</sup> Therefore, adjusting  $S_{\rm n}$  gave an extra means of mimicking the more complex MoO<sub>x</sub>/Si junctions in our simulations.<sup>26</sup> Other fitting parameters we used for the simulations are Shockley-Read–Hall (SRH) lifetimes,  $\tau_{\rm n} = 10 \,\mu \text{s}$ ,  $\tau_{\rm p} = 20 \,\mu \text{s}$ , and  $N_{\rm D} = 5 \times 10^{14} \,\text{cm}^{-3}$ .

For the given values of  $\phi_{\rm b}$  and  $S_{\rm n}$ ,  $I_{\rm h}$  determines the I-V characteristics as also observed experimentally, while  $I_{\rm e}$  appears to be one order of magnitude lower than  $I_{\rm h}$ .  $I_{\rm h}$  is mainly determined by the substrate Gummel number while  $\phi_{\rm b}$  and  $S_{\rm n}$  only affected  $I_{\rm e}$ . It is possible to model the hole-dominated experimental I-V characteristics by other (suitable) combinations of  $\phi_{\rm b}$  (>0.90 V) and  $S_{\rm n}$  such that  $I_{\rm e}$  falls sufficiently below  $I_{\rm h}$ . Nevertheless, our simulations

FIG. 5. (a) Temperature dependent *I*-V characteristics of the fabricated Pd/MoO<sub>x</sub>/n-Si diode compared to those of a simulated Si Schottky diode. (b) Arrhenius plot of the experimental device at  $V_d = 0.2$  V forward bias used to estimate the activation energy  $E_a$ .

confirm the important role of a sufficiently high  $\phi_b$  and well-passivated MoO<sub>x</sub>/Si interface in the observed *I*-*V* characteristics of the Pd/MoO<sub>x</sub>/n-Si diodes.

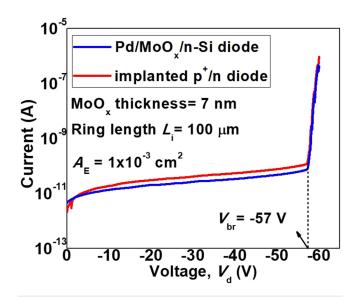

As shown in Fig. 5(a), we also performed temperature dependent I-V measurements in order to analyze the dominant charge transport mechanism and to extract the activation energy,  $E_a$ . In the case of majority-carrier thermionic-emission dominated transport  $[I \propto \exp(-q\phi_{\rm b}/kT)]$ , as in conventional Schottky diodes, the  $E_{\rm a}$  obtained from Arrhenius plots would give the effective  $q\phi_{\rm b}$  at the MS junction. As opposed to this, in the case of minority-carrier diffusion-dominated transport  $[I \propto \exp(-E_g/kT)]$ , we would expect an  $E_{\rm a}$  corresponding to the semiconductor bandgap,  $E_{\rm g}$ . The Arrhenius plot in Fig. 5(b) for the Pd/MoO<sub>x</sub>/n-Si diode under forward bias ( $V_d = 0.2 \text{ V}$ ) displays an  $E_a$  corresponding to the Si  $E_{g}$ . We obtained similar results for the implanted p<sup>+</sup>n Si diode. This confirms that hole injection is indeed dominant in our Pd/MoO<sub>x</sub>/n-Si diodes under forward bias. These results also underline that it is not possible to determine the actual value of  $\phi_{\rm b}$  using I-V-T measurements in such high-barrier diodes where diffusion dominates the current rather than TE. Furthermore, as shown in Fig. 6, the reverse I-V characteristics of the Pd/MoO<sub>x</sub>/n-Si diode were also found to be similar to that of implanted p<sup>+</sup>n Si diodes with identical breakdown voltages,  $V_{\rm br} = -57$  V. This strongly indicates the presence of a hole inversion layer in the Pd/MoO<sub>x</sub>/ n-Si diode that prevents expansion of the depletion layer into the MoO<sub>x</sub> layer. Moreover, the breakdown characteristics are independent of the  $MoO_x$  layer thickness when increased from 5 nm to 33 nm, which suggests that only the substrate doping is determining the depletion width. By calculating the depletion width at breakdown, we estimated the carrier density displaced in the substrate to be about  $8.6 \times 10^{11}$  cm<sup>-2</sup>, which is equivalent to the corresponding carrier density in the p-type region. This value represents

FIG. 6. Reverse bias *I–V* characteristics of a fabricated Pd/MoO<sub>x</sub>/n-Si diode at room temperature compared to those of an implanted p<sup>+</sup>n-Si reference diode.

a lower limit of the hole concentration in the inversion layer at the  $MoO_x/n-Si$  interface.

#### **B.** Sheet resistance measurements

By preparing the MoO<sub>x</sub> samples with a high-resistivity B capping layer, we were able to measure the sheet resistance,  $R_{\rm sh}$ , of the hole inversion layer along the Si surface under the deposited MoO<sub>x</sub>. Following the same methodology as outlined before,<sup>14</sup> we obtained  $R_{\rm sh}$  values in the range of 60–100 kΩ/ $\Box$ . This is much lower than the sheet resistance of the thin B layer that is at least 1 MΩ/ $\Box$ . Hence, the possibility of the B layer contributing to the measured  $R_{\rm sh}$  in any significant way can be safely ruled out. However, it is difficult to obtain a well estimated value for the hole concentration in the inversion layer for the experimental  $R_{\rm sh}$  because the effective mobility at the MoO<sub>x</sub>/Si interface is difficult to predict. Nevertheless, our measured  $R_{\rm sh}$  does not conflict with the lower limit of 8.6 × 10<sup>11</sup> cm<sup>-2</sup> found in Sec. IV A.

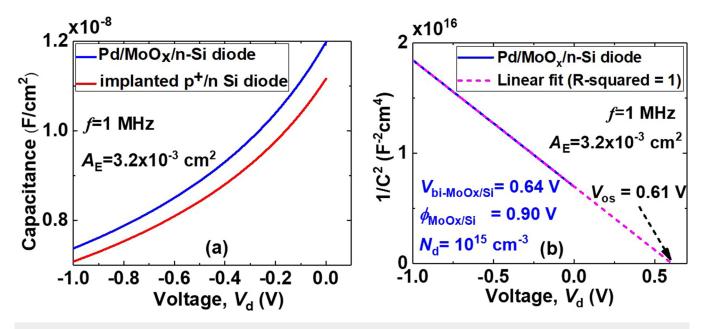

#### C. C-V measurements

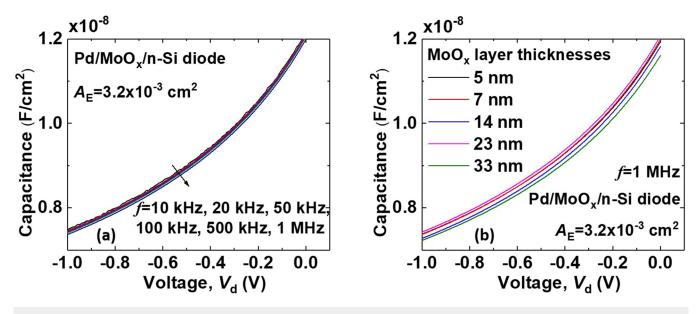

In addition to temperature dependent I-V measurements, reverse biased C-V characteristics are commonly used to extract the  $\phi_b$  of Schottky diodes.<sup>17</sup> The measured C-V profile of a Pd/MoO<sub>x</sub>/n-Si diode is shown in Fig. 7(a) along with that of the implanted p<sup>+</sup>n-Si diode. Notably, the two diodes show similar expansion of the depletion region with increasing reverse voltage, with only a small difference that could be attributed to differences in the p to n transition profile of the implanted and MoO<sub>x</sub>/n-Si junctions.

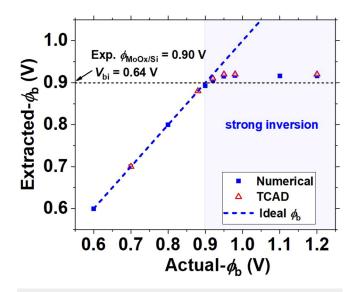

Following the conventional C-V measurement approach,<sup>17</sup> the built-in potential ( $V_{\rm bi}$ ) and  $\phi_{\rm b}$  of the diode can be estimated from the offset voltage,  $V_{\rm os}$ , of the  $C^{-2}-V$  plot. From the measurements shown in Fig. 7(b), we extracted a  $V_{\rm bi}$  of about 0.64 V for our Pd/MoO<sub>x</sub>/n-Si diode with a resulting barrier height ( $\phi_{\rm MoO_x/Si}$ ) of about 0.90 V at the MoO<sub>x</sub>/n-Si interface. However, this approach is only valid when there is only depletion charge near an MS interface. Here, the extracted  $\phi_{\rm b}$  indicates that the interface may be inverted as predicted by Eq. (1), which sets the strong inversion condition at  $\phi_{\rm b} > 0.85$  V when  $N_{\rm d} = 10^{15}$  cm<sup>-3</sup>.

When an inversion layer is present, another formulation should be adopted based on the solution of Poisson's equation with the inclusion of the inversion charge.<sup>27,28</sup> Schwarz and Walsh<sup>27</sup> have previously shown that for a sufficiently high barrier, the measured capacitance is no longer sensitive to the barrier height and is largely determined by the resistivity of the substrate. The inversion charge basically "screens" the depletion charge. Gummel and Scharfetter<sup>29</sup> also reached a similar conclusion for an abrupt (single-sided) p<sup>+</sup>n junction, where the  $V_{os}$  was found to be nearly independent of  $N_a$  for large  $N_a/N_d$  ratios. Therefore, in the presence of inversion charge in a Schottky junction or even in the case of a single-sided p<sup>+</sup>n junction, the  $V_{os}$  from the  $C^{-2}-V$  plot can no longer be used to accurately determine the  $V_{bi}$  or  $\phi_b$  of the junction.

In order to investigate the influence of the inversion charge on the extracted  $V_{\rm bi}$  for our device, we adapted the methodology as outlined earlier<sup>27</sup> and re-visited the solution of Poisson's equation in the presence of a hole inversion layer. From a numerical

FIG. 7. (a) Reverse bias C-V characteristics of the fabricated Pd/MoO<sub>x</sub>/n-Si and implanted p<sup>+</sup>n-Si diodes at room temperature. (b)  $(1/C)^2$  as a function of applied voltage indicating the built-in potential,  $V_{bi}$ , for the Pd/MoO<sub>x</sub>/n-Si diode as extracted by linear fitting.

solution,  $C^{-2}-V$  plots were first calculated for various  $\phi_{\rm b}$  in the reverse bias range of 0–1 V. The  $V_{\rm os}$  extracted from linear fitting was then used to determine  $\phi_{\rm b}$ .

Figure 8 shows the extracted  $\phi_b$  using this numerical approach as a function of the actual  $\phi_b$ . The extracted  $\phi_b$  tends to saturate beyond a certain value (~0.90 V), where the influence of inversion charge starts to become important. The numerical solution is also in good agreement with TCAD simulations. In a more strict sense, which is practically masked by the experimental and computational inaccuracies, the  $C^{-2}-V$  plot in the presence of inversion charge becomes non-linear and  $V_{os}$  is then a function of the applied voltage.<sup>27,29</sup> Hence, for a sufficiently high barrier, the actual  $\phi_b$ cannot be obtained from the *C*-*V* analysis. In such a scenario,  $V_{os}$ at reverse voltages close to zero, could only give an estimate of the lower limit of  $\phi_b$ .<sup>29</sup>

Hence, our experimentally calculated  $\phi_{MoO_x/Si}$  value of 0.90 V may not correspond to the actual  $\phi_b$  but is an indication of the lower limit. For  $\phi_b = 0.90$  V, we estimated a peak hole concentration at the interface of about  $5 \times 10^{15}$  cm<sup>-3</sup> as given by  $p_0 = N_v \exp(-(E_g - \phi_b)/kT))$  which leads to an effective sheet carrier density,  $p_{sh}$ ,  $\sim 10^{10}$  cm<sup>-2</sup>. The obtained value of  $p_{sh}$  here is, however, about two orders of magnitude lower than the one we estimated from reverse breakdown characteristics, which indicate that the actual  $\phi_b$  at the MoO<sub>x</sub>/n-Si interface is indeed higher than 0.90 V.

In addition, we performed C-V measurements at multiple frequencies as shown in the Fig. 9(a). The capacitance remains practically constant for varying frequencies, which rules out the possibility of any trapped charge in the MoO<sub>x</sub> layer influencing the C-V measurements. Furthermore, the C-V measurements in Fig. 9(b) of our samples show no systematic change in the capacitance for various  $MoO_x$  thicknesses. This suggests that the depletion is occurring mainly in the Si, and that the  $MoO_x$  layer is behaving more like a metal or degenerate semiconductor with a

**FIG. 8.** The extracted  $\phi_{\rm b}$  as a function of the actual  $\phi_{\rm b}$ , obtained from a numerical solution of Poisson's equation in the presence of a hole inversion layer and compared with TCAD simulations. The black dashed line indicates the position of our experimentally extracted  $\phi_{\rm MoO_r/Si}$  value.

FIG. 9. Reverse bias C–V characteristics of a fabricated Pd/MoO<sub>x</sub>/n-Si diode: (a) at various frequencies and (b) for various MoO<sub>x</sub> layer thicknesses at a fixed frequency of 1 MHz.

certain series resistance as was reported earlier.<sup>6,9</sup> We drew a similar conclusion before<sup>14</sup> because the diode I-V characteristics were independent of the MoO<sub>x</sub> layer thickness at low current levels, while at high current levels, the series resistance through the MoO<sub>x</sub> layer attenuated the current. These experimental observations indicate that only the MoO<sub>x</sub>/Si interface is determining the device characteristics and the bulk MoO<sub>x</sub> layer is providing the contact to the metal capping layer.

#### D. Light-emission measurements

Forward-bias light emission in Schottky diodes occurs as a result of radiative recombination of injected minority carriers with background majority carriers. Hence, the minority current determines the radiative recombination rate in the device. In conventional Schottky diodes, the minority current gets suppressed before it reaches values high enough for any measurable light output due to its poor supply from the contact or series resistance. Therefore, Schottky diodes are generally disregarded for light-emitting applications. However, a high-barrier diode with an induced inversion layer can sustain a high minority current that, as we discussed in Secs. II and IV A, can become comparable to that of doped junction counterparts.

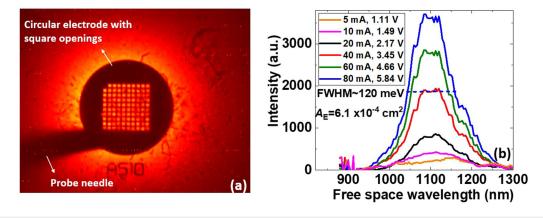

We performed light-emission measurements on our fabricated diodes. The Pd/MoO<sub>x</sub>/n-Si diodes show clear electroluminescence (EL) during forward-bias operation as is evident from the IR micrograph in Fig. 10(a). The IR emission is centered around the wavelength corresponding to the Si bandgap, i.e.,  $1.12 \,\mu$ m as shown in Fig. 10(b). As expected, the emitted EL intensity increases with the injected current level. The observed full-width-half-maximum (FWHM) in excess of ~1.8 kT (Ref. 30) is attributed to the indirect

bandgap in Si where involvement of phonons in the radiative recombination process leads to the EL-broadening.

Moreover, the maximum injected current density ( $J = 165 \text{ A/cm}^2$ ) here falls in the low injection regime ( $J \ll qNv_{\text{sat}} = 1.6 \times 10^3 \text{ A/cm}^2$ where N is the active doping concentration and  $v_{\text{sat}}$  is the saturation velocity). Compared to the p<sup>+</sup>n reference diodes, the light emission in the Pd/MoO<sub>x</sub>/n-Si diode is about the same, being about 1.5 times less bright. Some discrepancy in the observed brightness between the two diodes could be related to a possible difference in their extraction efficiencies caused by their different junction depths, since the  $p \cdot n$  product and thus the light emission is highest at the junction. The junction depth in the case of the implanted p<sup>+</sup>n diode is about 0.5  $\mu$ m below the surface and would, therefore, experience relatively low optical losses at the top electrode compared to the Pd/MoO<sub>x</sub>/n-Si diode, where light is emitted very close to the electrode.

### E. Surface barrier transistor (SBT): Measurements and TCAD simulations

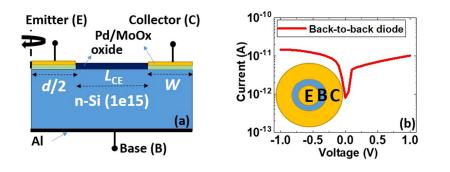

We also realized a lateral bipolar transistor, referred to as a surface barrier transistor (SBT),<sup>15</sup> with high-barrier  $MoO_x$  contacts. Figure 11(a) shows a schematic cross section of the experimental device where two closely spaced top contact electrodes are utilized as emitter (E) and collector (C), while the metallized substrate back surface serves as the base contact (B).

We first checked the two-terminal back-to-back diode characteristics between the collector and emitter electrode as shown in Fig. 11(b). The observed low leakage current between the two electrodes rules out the possibility of any unwanted surface conduction path between the emitter and collector.

**FIG. 10.** (a) Bright field EL IR micrograph of the fabricated  $Pd/MoO_x/n-Si$  diode at a constant forward current drive of 100 mA ( $J = 165 \text{ A/cm}^2$ ). (b) Optical spectrum of the emitted light from the same diode at various forward current levels.

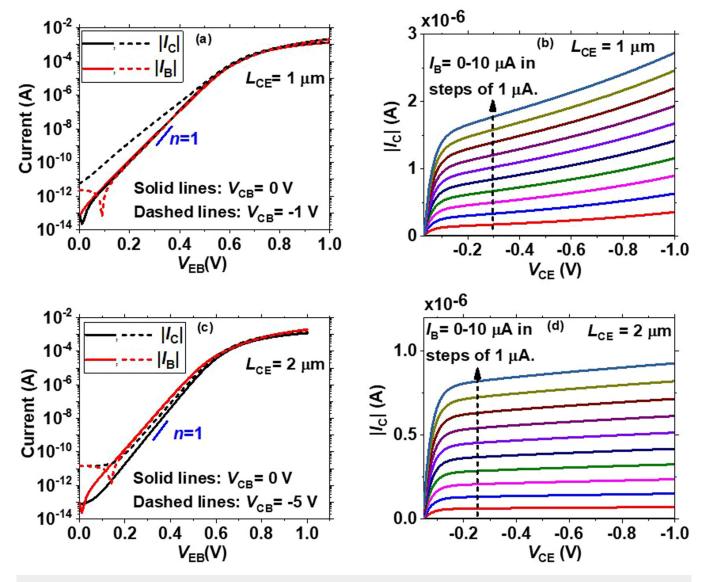

The electrical measurements were performed on devices with two different spacings ( $L_{CE}$ ) between the emitter and collector electrodes, i.e.,  $L_{CE} = 1 \,\mu\text{m}$  and  $L_{CE} = 2 \,\mu\text{m}$ . Figure 12(a) shows the Gummel plot for the device with  $L_{CE} = 1 \,\mu\text{m}$ , where a significant collector current ( $I_C$ ) comparable to the base current,  $I_B$ , is obtained at  $V_{CB} = 0 \,\text{V}$ . The measured  $I_C \sim I_B$  confirms the improved emitter efficiency of the EB junction as compared to that of conventional Schottky counterparts. The control of the EB junction over the  $I_C$  as expected in a bipolar transistor is also clearly visible in the output ( $I_C - V_{CE}$ ) characteristics of the same device as shown in Fig. 12(b).

$I_{\rm C}$  increases further while  $I_{\rm B}$  remains unchanged when the reverse bias at the CB junction is raised to -1 V, which results in the current gain,  $\beta = I_{\rm C}/I_{\rm B} > 1$ . The increased  $I_{\rm C}$  showing non-ideal (n > 1) behavior for  $V_{\rm CB} = -1$  V is attributed to the widening of the depletion width at the CB junction, which eventually results in the punch-through effect, i.e., the depletion regions formed at the EB and CB Schottky junctions gradually start to merge in the gap region between the collector and emitter electrodes. The punch-through effect is also visible in the output characteristics, where a low output resistance can be seen. However, for the specified spacing  $L_{\rm CE}$  and barrier height ( $\phi_{\rm b}$ ), the punch-through effect is not enough to fully eliminate the hole potential barrier as there is control of  $I_{\rm B}$  over  $I_{\rm C}$  as expected for a bipolar transistor.

$\beta$  becomes less than 1 and the observed punch-through effect is practically reduced when the  $L_{CE}$  is increased to 2  $\mu$ m as can be seen in the Gummel plot in Fig. 12(c) and the output characteristics in Fig. 12(d).

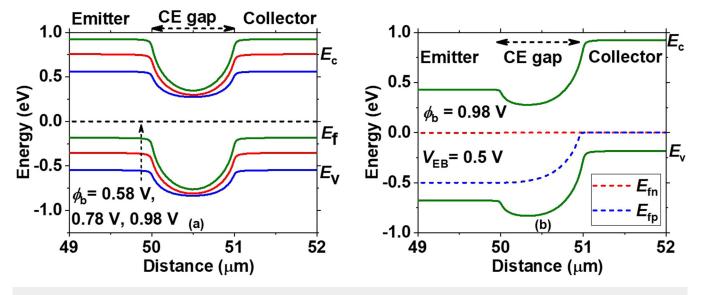

To further illustrate the working of the SBT, we also performed TCAD simulations on the same geometry as shown in Fig. 11(a). The top collector and emitter electrodes were modeled as Schottky contacts with the identical  $\phi_{\rm b}$  and a fixed (default)<sup>23</sup> surface recombination velocity (S $_{\rm n}=2.5\times10^6\,{\rm cm/s}).$  The base electrode was assumed to be an ohmic (neutral) contact. The  $\phi_{\rm b}$  of the top electrodes was then systematically varied. The hole inversion charge density below the collector and emitter electrodes increases with  $\phi_{\rm b}$ , as can be observed from the relative position of the Fermi level from the valence band in the energy band diagram in Fig. 13(a). Figure 13(a) also shows that the substrate depletion or punch-through effect in the collector-emitter gap region increases with  $\phi_{\rm b}$  at the electrodes. However, for  $\phi_{\rm b}$  beyond which the inversion layer effect becomes important, as shown in Fig. 8, the effective barrier for holes and the depletion width do not change anymore with  $\phi_{\rm b}$ . The punch-through effect even at maximum depletion width is not severe and will not affect the bipolar operation, since the barrier to the hole injection is still high enough to ensure a base-controlled collector current. Figure 13(b) re-iterates this point by illustrating the operation of the SBT when the minority (hole) injection into the reverse biased CB

**FIG. 11.** (a) Schematic cross section of the experimental and TCAD simulated device used for bipolar transistor measurements with an inner circle of diameter  $d = 100 \ \mu m$  as the emitter (E) electrode and outer ring with width  $W = 50 \ \mu m$  as the collector (C) electrode for two different spacings  $L_{\rm CE}$  of 1  $\mu m$  and 2  $\mu m$ . (b) *I–V* characteristics of back-to-back diodes measured between the top emitter and collector electrodes. Inset: Schematic top view of the device used for bipolar transistor measurements.

FIG. 12. Electrical measurements of the fabricated bipolar transistors. Gummel plot (left) and output characteristics (right) for [(a) and (b)]  $L_{CE} = 1 \ \mu m$  and [(c) and (d)]  $L_{CE} = 2 \ \mu m$ . Blue solid line: ideality factor n = 1 for reference.

junction can be increased by applying a small forward bias at the EB junction to lower the barrier there.

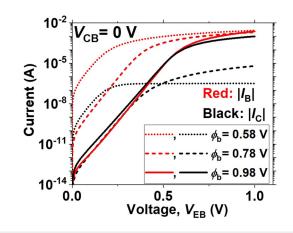

The simulated Gummel plots in Fig. 14 also elucidate the role of  $\phi_{\rm b}$  in determining the emitter efficiency of the contacts.  $I_{\rm B}$  (shown in red) is determined by the TE of majority carriers (electrons) and decreases exponentially with  $\phi_{\rm b}$  at the emitter electrode.  $I_{\rm C}$  on the other hand, for a sufficiently high  $\phi_{\rm b}$ , is determined by the minority-carrier (hole) injection at the EB junction, which is governed by the Gummel number of the base region. Therefore,  $I_{\rm C}$  remains practically unaffected with varying  $\phi_{\rm b}$  as shown in Fig. 14 for  $\phi_{\rm b} = 0.78$  V and  $\phi_{\rm b} = 0.98$  V except at high forward biases, where the series resistance becomes important. The relatively small

discrepancy in the  $I_{\rm C}$  in the exponential region is attributed to the substrate depletion effect, where the effective Gummel number of the base decreases with  $\phi_{\rm b}$  as also illustrated in Fig. 13(a). For low  $\phi_{\rm b} = 0.58$  V,  $I_{\rm C}$  is determined by the reverse bias current of the CB junction as it is higher than the corresponding hole injection level of the forward biased EB junction. The  $\beta$  increased to 15 when  $\phi_{\rm b}$  was raised to approach the value of Si bandgap, i.e., 1.12 V. In general, the improved emitter efficiency, and higher  $\beta$ , with increasing  $\phi_{\rm b}$  for the SBT device is a result of the efficient suppression of  $I_{\rm B}$ . The high  $\phi_{\rm b}$  and resulting inversion layer ensures an efficient supply of minority carriers for sustaining the  $I_{\rm C}$  until high forward biases and also lowers the series resistance.

FIG. 13. Simulated energy band diagram for the bipolar device shown in Fig. 11(a), with  $L_{CE} = 1 \ \mu m$  in the lateral direction 20 nm below the top electrodes: (a) at thermal equilibrium for three different  $\phi_b$ : 0.58 V, 0.78 V, and 0.98 V, and (b) for  $\phi_b = 0.98$  V at  $V_{EB} = 0.5$  V and  $V_{CB} = 0$  V.

However, it is clear that the chosen device geometry, though interesting for a simple proof-of-concept understanding of the SBT, should be optimized. Alternative device architectures based on UTB SOI, such as the one previously investigated by Kumar and Nadda<sup>31</sup> via TCAD simulations, will be more advantageous.

#### **V. DISCUSSION**

In this study, we found that the behavior of the Pd/MoO<sub>x</sub>/n-Si MnIS diodes, with respect to diode I-V, C-V, and bipolar transistor characteristics, are practically identical to that of the deep-implanted p<sup>+</sup>n junctions. This is a result of the high  $\gamma$  of both

**FIG. 14.** Simulated Gummel plots for varying  $\phi_b$  at the CE electrodes with  $L_{CE} = 1 \ \mu$ m, shown for  $\phi_b = 0.58$  V,  $\phi_b = 0.78$  V, and  $\phi_b = 0.98$  V.

types of diodes that have a low hole diffusion current and an electron current that is even lower. We confirmed the presence of a significant inversion layer, which can to some degree explain low electron injection into the p-type region. In the research on PureB MnIS diodes fabricated at B deposition temperatures below 400 °C, and on the same type of substrates as used in the present study, the inversion layer sheet resistance was lower, ~35 kΩ/□, and uniform over the wafer when optimal conditions were applied.<sup>32</sup> Both experiments and simulations supported the conjecture that a layer of fixed negative charge at the interface is responsible for the inversion layer in this case.

There can be several reasons why the MoO<sub>r</sub> diodes display such low electron current levels. First, the  $MoO_x$  is a high work function material, and the simulations performed here substantiate that for barrier heights higher than about 0.9 eV, a significant inversion layer forms. Second, the passivating nature of  $MoO_x$ -based contacts on Si,<sup>12,24</sup> possibly originating from the observed  $SiO_x(Mo)$  interlayer that may be partly insulating and is represented by a low surface recombination velocity, could also play a role in suppressing the electron injection even further. Thirdly, a significant amount of negative fixed charge may also be present in the deposited layer. Unlike in thermally grown SiO<sub>2</sub> layers that most often contain positive fixed charge near the Si interface, it has been shown before<sup>33</sup> that negative fixed charge may appear in plasma-oxidized Si surfaces. The surplus of oxygen in such layers was proposed to accumulate the negative charge. A similar mechanism may also hold true for the  $SiO_x$  interlayer, which is formed during the  $MoO_x$  deposition process.

The partial  $SiO_x$  character of the interfacial layer may also be an important feature for providing a well-passivated Si surface. A similar mechanism has been developed and well-documented for Al<sub>2</sub>O<sub>3</sub> layers that have gained interest as passivation layers on n-type c-Si solar cells.<sup>34</sup> As opposed to the  $Al_2O_3$ , the  $MoO_x$  layers are not insulating and, therefore, they have generated interest as contact layers. The use of  $Al_2O_3$  for creating an inversion-layer diode requires contacting the negative-charge-induced inversion layer via implanted regions.<sup>3</sup>

From electrical analysis on samples with varying  $MOO_x$  thicknesses, we can conclude that only the  $MOO_x/Si$  interface is playing a dominant role in the charge carrier transport of our devices and the bulk properties of  $MOO_x$  only contribute to the series resistance. In another work,<sup>35</sup> the  $MOO_x$  layer was shown to limit the current only at lower voltages, while at higher voltages, the current was limited by the barrier. For situations where the  $MOO_x$  layer does not limit the current, the charge transport across the  $MOO_x/Si$  interface can be modeled by assuming a Schottky electrode on top of Si with a suitable barrier height and surface recombination velocity.<sup>9</sup> For a more generic treatment of charge transport through a transition metal oxide (TMO) layer, by taking into the account the density and the energetic distribution of traps inside the bandgap, one should consider the methodology as described by Messmer *et al.*<sup>26</sup>

The bipolar nature of the MoO<sub>x</sub>-based diode was established from the measured electrical and optical characteristics. Such MoO<sub>x</sub>-based inversion type contacts could also be considered as a possible replacement of doped p<sup>+</sup> regions for applications where doping is challenging or low temperature processing is required. MoO<sub>x</sub>-based contacts could offer a novel dopant-free route for realizing (opto-) electronic devices such as field effect transistors (FETs),<sup>9</sup> bipolar transistors, light emitters, photodetectors,<sup>36</sup> or even as Schottky gate contacts.<sup>37</sup> Moreover, for creating an n-type inversion region, a lower work-function material such as lithium fluoride (LiF<sub>x</sub>)<sup>38</sup> which has been recently reported as an "electron selective" contact should be explored in more detail. In this way, both p-type and n-type regions can be locally created inside a semiconductor body without using any dopants. However, creating a p-type region is more difficult in the case of wide bandgap materials such as GaN where even the highest reported vacuum work function of  $MoO_x$ , i.e., ~6.6 eV, is not high enough to reach the valence band.

For many of these potential device applications, the high resistivity of the MoO<sub>x</sub><sup>8,14</sup> could be a concern. The contact resistivity,  $\rho_c$ , of the Pd/MoO<sub>x</sub>/p-Si stack, with a ~7-nm-thick MoO<sub>x</sub> layer, is measured to be around 1.2 m  $\Omega$  cm<sup>2</sup> as reported earlier, <sup>14</sup> while this could be an order of magnitude higher on n-Si interfaces.<sup>8</sup> In addition to the high  $\rho_c$ , the key properties of MoO<sub>x</sub>, such as the work function and conductivity, are unstable upon exposure to ambient and high temperatures.<sup>39–42</sup> Therefore, it is required to cap them *in situ* with a suitable metal to prevent exposure to air which otherwise may degrade the work function.

The choice of the top electrode metal is also important for efficient carrier transport<sup>26</sup> and for a low contact resistivity. In our work, we used Pd for its reported high work function and relative inert nature at room temperature.<sup>9</sup> We also performed a few experiments with Au capping layers and the results were comparable to those with Pd. Reactive metals such as Al are less preferred for capping MoO<sub>x</sub> as they may reduce the functional MoO<sub>x</sub> layer by forming oxides, thereby creating more oxygen vacancies in the film, and consequently lowering the effective work function.<sup>42,43</sup>

Furthermore, as discussed in Sec. IV B, we were able to prevent undesirable oxidation of the  $MoO_x$  layer by capping it with a pure B layer instead of metal. Such barrier layers may also prove to be indispensable for preventing interactions with metallization layers, particularly in connection with temperature rises during post-processing or device operation. These concerns need to be fully addressed before practical applications become feasible.

#### VI. CONCLUSION

We realized MnIS diodes on n-type Si using  $MoO_x$ -based contacts. The electrical and light-emitting diode characteristics bore strong functional resemblance to implanted p<sup>+</sup>n-Si diodes rather than to conventional Schottky diodes. The presence of a high potential barrier (>0.90 V) and an hole inversion layer at the  $MoO_x/n$ -Si interface was verified and had a sheet carrier density greater than ~8.6 × 10<sup>11</sup> cm<sup>-2</sup>. The bipolar-mode diode behavior of the  $MoO_x$ -based MnIS diodes was underlined by demonstrating a proof-of-concept Si surface barrier bipolar transistor without any impurity doping of the Si surface.

Theoretically, an inversion layer and efficient suppression of electron injection also appears in very high-barrier Schottky diodes. Simulations that approached the  $MoO_x/n$ -Si structure as being a high-barrier Schottky diode could reproduce the experimental findings provided that the surface recombination velocity was set at a relatively low value of  $10^3$  cm/s. This suggests that the surface was passivated, which was supported by the presence of an SiO<sub>x</sub>(Mo) interlayer.

The relatively high resistivity of the bulk  $MoO_x$  material has not deterred possibly attractive implementations for use as solar cell emitters. In contrast, for nanoscale device applications, the associated series resistance could form a serious bottleneck. Therefore, for such applications, thin layers comprising essentially only the interfacial (tunneling) layer should be investigated. Efforts to significantly improve the reproducibility and robustness of the material will also be necessary. If successful, such an MnIS dopant-free hetero-contact processed at a low temperature would be very interesting for fabricating bipolar devices [bipolar junction transistors (BJTs), SBTs, and LEDs] in Si and other material systems, as well as UTB devices where impurity doping is otherwise challenging.

#### ACKNOWLEDGMENTS

The authors acknowledge partial financial support by the NWO Domain Applied and Engineering Sciences (TTW), The Netherlands (OTP 2014, under Project No. 13145) and the Danish Innovation Foundation Project SEMPEL (Semiconductor Materials for Power Electronics). The authors would also like to thank Professor J. Schmitz for critically reading this manuscript and Dr. S. Dutta for experimental support.

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

<sup>1</sup>M. Green and J. Shewchun, "Minority carrier effects upon the small signal and steady-state properties of Schottky diodes," Solid State Electron. **16**, 1141–1150 (1973).

<sup>2</sup>G. Gupta, S. Dutta, S. Banerjee, and R. J. E. Hueting, "Minority carrier injection in high-barrier Si-Schottky diodes," IEEE Trans. Electron Devices 65, 1276–1282 (2018).

<sup>3</sup>M. A. Juntunen, J. Heinonen, H. S. Laine, V. Vähänissi, P. Repo, A. Vaskuri, and H. Savin, "N-type induced junction black silicon photodiode for UV detection," in *Integrated Photonics: Materials, Devices, and Applications IV* (International Society for Optics and Photonics, 2017), Vol. 10249, p. 102490I.

<sup>4</sup>T. Knežević, X. Liu, E. Hardeveld, T. Suligoj, and L. K. Nanver, "Limits on thinning of boron layers with/without metal contacting in pureB Si (photo) diodes," IEEE Electron Device Lett. **40**, 858–861 (2019).

<sup>5</sup>L. K. Nanver, L. Qi, V. Mohammadi, K. Mok, W. B. de Boer, N. Golshani, A. Sammak, T. L. Scholtes, A. Gottwald, U. Kroth *et al.*, "Robust UV/VUV/EUV PureB photodiode detector technology with high CMOS compatibility," IEEE J. Sel. Top. Quantum Electron. **20**, 306–316 (2014).

<sup>6</sup>C. Battaglia, X. Yin, M. Zheng, I. D. Sharp, T. Chen, S. McDonnell, A. Azcatl, C. Carraro, B. Ma, R. Maboudian *et al.*, "Hole selective  $MoO_x$  contact for silicon solar cells," Nano Lett. **14**, 967–971 (2014).

<sup>7</sup>C. Battaglia, S. M. De Nicolas, S. De Wolf, X. Yin, M. Zheng, C. Ballif, and A. Javey, "Silicon heterojunction solar cell with passivated hole selective  $MoO_x$  contact," Appl. Phys. Lett. **104**, 113902 (2014).

<sup>8</sup>J. Bullock, A. Cuevas, T. Allen, and C. Battaglia, "Molybdenum oxide MoO<sub>x</sub>: A versatile hole contact for silicon solar cells," Appl. Phys. Lett. **105**, 232109 (2014).

$^{9}$ S. Chuang, C. Battaglia, A. Azcatl, S. McDonnell, J. S. Kang, X. Yin, M. Tosun, R. Kapadia, H. Fang, R. M. Wallace *et al.*, "MoS<sub>2</sub> p-type transistors and diodes enabled by high work function MoO<sub>x</sub> contacts," Nano Lett. **14**, 1337–1342 (2014). <sup>10</sup>J. Meyer, S. Hamwi, M. Kröger, W. Kowalsky, T. Riedl, and A. Kahn, "Transition metal oxides for organic electronics: Energetics, device physics and

applications," Adv. Mater. **24**, 5408–5427 (2012). <sup>11</sup>G. Gupta, B. Rajasekharan, and R. J. E. Hueting, "Electrostatic doping in semiconductor devices," IEEE Trans. Electron Devices **64**, 3044–3055 (2017).

<sup>12</sup>M. Gao, D. Chen, B. Han, W. Song, M. Zhou, X. Song, F. Xu, L. Zhao, Y. Li, and Z. Ma, "Bifunctional hybrid a-SiO<sub>x</sub>(Mo) layer for hole-selective and interface passivation of highly efficient  $MoO_x/a$ -SiO<sub>x</sub>(Mo)/n-Si heterojunction photovoltaic device," ACS Appl. Mater. Interfaces **10**, 27454–27464 (2018).

<sup>13</sup>T. Sun, R. Wang, R. Liu, C. Wu, Y. Zhong, Y. Liu, Y. Wang, Y. Han, Z. Xia, Y. Zou *et al.*, "Investigation of  $MoO_x/n$ -Si strong inversion layer interfaces via dopant-free heterocontact," Phys. Status Solidi (RRL) **11**, 1700107 (2017).

<sup>14</sup>G. Gupta, S. D. Thammaiah, R. J. E. Hueting, and L. K. Nanver, "In search of a hole inversion layer in Pd/MoO<sub>x</sub>/Si diodes through I–V characterization using dedicated ring-shaped test structures," in 2019 IEEE 32nd International Conference on Microelectronic Test Structures (ICMTS) (IEEE, 2019), pp. 12–17.

<sup>15</sup>W. Bradley, "The surface-barrier transistor: Part I—Principles of the surface-barrier transistor," Proc. IRE **41**, 1702–1706 (1953).

<sup>16</sup>E. H. Rhoderick and R. H. Williams, *Metal-Semiconductor Contacts* (Clarendon Press, Oxford, 1988), Vol. 129.

<sup>17</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (John Wiley & Sons, 2007).

<sup>18</sup>E. Demoulin and F. Van De Wiele, "Inversion layer at the interface of Schottky diodes," Solid State Electron. 17, 825–833 (1974).

<sup>19</sup>Y. Amemiya and Y. Mizushima, "Bipolar-mode Schottky contact and applications to high-speed diodes," IEEE Trans. Electron Devices **31**, 35–42 (1984).

20S. Cristoloveanu, K. H. Lee, H. Park, and M. S. Parihar, "The concept of electrostatic doping and related devices," Solid State Electron. 155, 32–43 (2019).

<sup>21</sup>F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance," IEEE Electron Device Lett. 8, 410–412 (1987). <sup>22</sup>V. Mohammadi, S. Ramesh, and L. Nanver, "Thickness evaluation of deposited PureB layers in micro-/millimeter-sized windows to Si," in *International Conference* on *Microelectronic Test Structures (ICMTS)* (IEEE, 2014), pp. 194–199.

23 Sentaurus TCAD, Synopsys Inc., Mountain View, CA, USA, version l-2016.03 ed. (2016).

<sup>24</sup>L. G. Gerling, C. Voz, R. Alcubilla, and J. Puigdollers, "Origin of passivation in hole-selective transition metal oxides for crystalline silicon heterojunction solar cells," J. Mater. Res. **32**, 260–268 (2017).

<sup>25</sup>A. Stephens, A. Aberle, and M. Green, "Surface recombination velocity measurements at the silicon-silicon dioxide interface by microwave-detected photo-conductance decay," J. Appl. Phys. **76**, 363–370 (1994).

<sup>26</sup>C. Messmer, M. Bivour, J. Schön, S. W. Glunz, and M. Hermle, "Numerical simulation of silicon heterojunction solar cells featuring metal oxides as carrier-selective contacts," IEEE J. Photovoltaics 8, 456–464 (2018).

27 R. Schwarz and J. Walsh, "Part V—The properties of metal to semiconductor contacts," Proc. IRE 41, 1715–1720 (1953).

<sup>28</sup>M. A. Green, "The capacitance of large barrier Schottky diodes," Solid State Electron. 19, 421–422 (1976).

${}^{\mathbf{29}}\text{H.}$  Gummel and D. Scharfetter, "Depletion-layer capacitance of  $p^+$  n step junctions," J. Appl. Phys. **38**, 2148–2153 (1967).

<sup>30</sup>E. F. Schubert, T. Gessmann, and J. K. Kim, *Light Emitting Diodes* (Wiley Online Library, 2005).

<sup>31</sup>M. J. Kumar and K. Nadda, "Bipolar charge-plasma transistor: A novel three terminal device," IEEE Trans. Electron Devices **59**, 962–967 (2012).

<sup>32</sup>L. Qi and L. K. Nanver, "Conductance along the interface formed by 400 °C pure boron deposition on silicon," IEEE Electron Device Lett. 36, 102–104 (2015).

<sup>33</sup>A. Boogaard, A. Y. Kovalgin, and R. Wolters, "Negative charge in plasma oxi-

<sup>33</sup>A. Boogaard, A. Y. Kovalgin, and R. Wolters, "Negative charge in plasma oxidized SiO<sub>2</sub> layers," ECS Trans. **35**, 259 (2011).

<sup>34</sup>G. Dingemans and W. Kessels, "Status and prospects of Al<sub>2</sub>O<sub>3</sub>-based surface passivation schemes for silicon solar cells," J. Vac. Sci. Technol. A **30**, 040802 (2012).

<sup>35</sup>R. García-Hernansanz, E. Garcia-Hemme, D. Montero, J. Olea, A. del Prado, I. Martil, C. Voz, L. Gerling, J. Puigdollers, and R. Alcubilla, "Transport mechanisms in silicon heterojunction solar cells with molybdenum oxide as a hole transport layer," Solar Energy Mater. Solar Cells 185, 61–65 (2018).

<sup>36</sup>Y. Liu, G. Cen, G. Wang, J. Huang, S. Zhou, J. Zheng, Y. Fu, C. Zhao, and W. Mai, "High performance  $MoO_{3-x}/Si$  heterojunction photodetectors with nanoporous pyramid Si arrays for visible light communication application," J. Mater. Chem. C 7, 917–925 (2019).

<sup>37</sup>Y. Lan, C. Hu, H. Deng, L. Sun, S. Yuan, J. Wang, X. Yu, X. Yang, Y. Zhou,

H. Song *et al.*, "MoO<sub>x</sub>/Au Schottky-gated field-effect transistors and their fast inverters," Adv. Electron. Mater. 5, 1900086 (2019).

<sup>38</sup>J. Bullock, P. Zheng, Q. Jeangros, M. Tosun, M. Hettick, C. M. Sutter-Fella, Y. Wan, T. Allen, D. Yan, D. Macdonald *et al.*, "Lithium fluoride based electron contacts for high efficiency n-type crystalline silicon solar cells," Adv. Energy Mater. 6, 1600241 (2016).

**<sup>39</sup>**I. Irfan and Y. Gao, "Effects of exposure and air annealing on  $MoO_x$  thin films," J. Photonics Energy **2**, 021213 (2012).

<sup>40</sup>I. Irfan, A. James Turinske, Z. Bao, and Y. Gao, "Work function recovery of air exposed molybdenum oxide thin films," Appl. Phys. Lett. **101**, 093305 (2012).

<sup>41</sup>S. Essig, J. Dréon, E. Rucavado, M. Mews, T. Koida, M. Boccard, J. Werner, J. Geissbühler, P. Löper, and M. Morales-Masis, "Toward annealing-stable molybdenum-oxide-Based hole-selective contacts for silicon photovoltaics," Solar RRL 2, 1700227 (2018).

<sup>42</sup>G. Gregory, M. Wilson, H. Ali, and K. O. Davis, "Thermally stable molybdenum oxide hole-selective contacts deposited using spatial atomic layer deposition,' in 2018 IEEE 7th World Conference on Photovoltaic Energy Conversion (WCPEC) (IEEE, 2018), pp. 2006–2009.

<sup>43</sup>V. Travkin, A. Y. Luk'yanov, M. Drozdov, E. Vopilkin, P. Yunin, and G. Pakhomov, "Ultrathin metallic interlayers in vacuum deposited  $MoO_x$ /metal/ $MoO_x$  electrodes for organic solar cells," Appl. Surf. Sci. **390**, 703–709 (2016).