Aalborg Universitet

## Ultra-High Step-Up DC-DC Converters Based on Center-Tapped Inductors

Tarzamni, Hadi; Kurdkandi, Naser Vosoughi; Gohari, Homayon Soltani; Lehtonen, Matti; Husev, Oleksandr; Blaabjerg, Frede

Published in: **IEEE** Access

DOI (link to publication from Publisher): 10.1109/ACCESS.2021.3117856

Creative Commons License CC BY 4.0

Publication date: 2021

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Tarzamni, H., Kurdkandi, N. V., Gohari, H. S., Lehtonen, M., Husev, O., & Blaabjerg, F. (2021). Ultra-High Step-Up DC-DC Converters Based on Center-Tapped Inductors. IEEE Access, 9, 136373 - 136383. Article 9558815. https://doi.org/10.1109/ACCESS.2021.3117856

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Received September 17, 2021, accepted September 30, 2021, date of publication October 4, 2021, date of current version October 12, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3117856

# Ultra-High Step-Up DC-DC Converters Based on Center-Tapped Inductors

## HADI TARZAMNI<sup>®1</sup>, (Student Member, IEEE), NASER VOSOUGHI KURDKANDI<sup>®2</sup>, HOMAYON SOLTANI GOHARI<sup>®3</sup>, MATTI LEHTONEN<sup>®1</sup>, OLEKSANDR HUSEV<sup>®2</sup>, (Sector Member, IEEE),

AND FREDE BLAABJERG<sup>1004</sup>, (Fellow, IEEE)

Department of Electrical Engineering and Automation, Aalto University, 02150 Espoo, Finland

<sup>2</sup>Department of Electrical Power Engineering and Mechatronics, Tallinn University of Technology, 12616 Tallinn, Estonia

<sup>3</sup>Faculty of Electrical Engineering, K. N. Toosi University of Technology, Tehran 1969764499, Iran <sup>4</sup>Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark

Department of Energy Technology, Aaborg University, 7220 Aaborg, Denina

Corresponding author: Hadi Tarzamni (hadi.tarzamni@aalto.fi)

This work was supported by FinElib, Finland, through the FinELib consortium's agreement with IEEE.

**ABSTRACT** In this paper, a new family of ultra-high step-up DC-DC converters based on a center-tapped coupled inductor (CI) is proposed. These single-switch converters employ different inductive and capacitive power transfer techniques by utilizing multi-winding CIs, intermediate capacitor links and simple switched-capacitors to improve the transferred power rate, harvest magnetizing and leakage inductance energies, and enhance power density. Achieving high voltage gain in low duty cycle values enables the proposed converters to operate under wide output voltage ranges; meanwhile, distributing the output voltage on two or three output ports alleviates the voltage stress on output terminal components. Low input current ripple, simple pulse width modulation control, low switch voltage stress and operation without circulating current can be listed as other features. In this paper, the proposed family is introduced, theoretically analyzed and compared with other state-of-the-art researches. Finally, the accuracy of analyses are evaluated with some experimental tests of a 1.25 kW experimental prototype.

**INDEX TERMS** DC-DC converter, high step-up power converter, center-tapped coupled inductor.

#### I. INTRODUCTION

In the massive energy harvesting technologies development today, using different types of renewable energies, such as photovoltaic and fuel cells, is inevitable due to the deficiency in fossil fuels and alarming conditions of environmental issues [1], [2]. High performance high step-up DC-DC converters are indispensable for such applications in which the low output voltage (typically lower than 50 V) should be boosted to a desired level [3]. Among different approaches to achieve high voltage gain converters, interleaving and utilizing coupled inductors (CI) and/or voltage multiplier cells (VMC)s obtain the merits of low duty cycle requirement and high efficiency operation for reaching the desired high gain ratio [4]–[7]. Furthermore, numerous features should be considered during a high step-up DC-DC converter's design, among which, amount of power loss, control complexity,

The associate editor coordinating the review of this manuscript and approving it for publication was Ching-Ming Lai<sup>(D)</sup>.

number of operational modes, converter's size, imposed inrush current on semiconductors, required CI turns, power density and desired duty cycle range are the most crucial ones. For example, as a practical consideration, the high voltage gain converter presented in [8] suffers from high conduction loss due to its high operation duty cycle range and high number of components. In addition, using high number of power switches increases the complexity in control system, the problem that is also existed in the suggested converters in [9]–[11].

Reduced input current ripple and continuous input current are the vital specifications of the converters that are utilized in renewable energy-based systems due to the harmful impacts of large and pulsating input current on the energy interfaces. The converters introduced in [12]–[16] suffer from large input current ripple owing to their input-side CI. Adopting interleaving technique and avoiding input CI are the effective solutions for the input current ripple problem. The suggested converter in [17] utilizes interleaving and CI techniques in addition to an active clamp circuit to achieve high output voltage and low current stress values, simultaneously. However, high number of semiconductors and large output voltage ripple limit its industrial applications. The interleaved converters introduced in [18]-[20] focus on the inductor coupling approach alongside with the VCMs to increase voltage gain ratio. Nevertheless, their high number of components, especially the passive ones, causes high size and low reliability. Scholars try to reduce the components' current stress and recycle the CI leakage energy in [21], [22], but the complex control system restricts their chance in real life applications. The converters presented in [23], [24] are suitable for high voltage applications; however, their disability of recycling leakage inductance energy and employing four inductors' cores are their main drawbacks. In [25] and [26], two interleaved DC-DC converters are proposed with passive and active clamp circuits, respectively, in order to solve switch voltage spikes. However, their need for high duty cycle values to enhance output voltage gain is their main disadvantage. The multi-stage high gain converter suggested in [27] utilizes conventional interleaved boost converter in each stage. Unfortunately, this method increases the power losses and circulating current.

The multi-input converter introduced in [28] utilizes a modified VMC in order to increase voltage gain ratio, but it cannot achieve such a high experimental output voltage ratio due to its high loss VMC. The SEPIC-based high step-up converter introduced in [29] uses CI and VMC to increase voltage gain ratio, but it suffers from low efficiency and high components count. In [30], authors tried to achieve high voltage gain and reduced input current ripple by adopting interleaving and switched-capacitor techniques, but the high number of components, either passive or active components, is its main drawback. Authors introduced a non-isolated high gain DC-DC converter and tried to achieve soft-switching performance in [31], but its high input current ripple and the need for high duty cycle are its main disadvantages that restrict its applications and increase conduction loss. In [32], scholars proposed an ultra-high gain DC-DC converter and used the interleaving technique to reduce the size of filter components and switching loss. However, utilizing two threewinding CIs, nine diodes, eight capacitors, and two switches are its main drawbacks that increase its cost and volume.

In order to fulfill the desired factors and resolve the problems of the above-mentioned converters, a family of centertapped inductor based DC-DC converters are introduced in this paper that are able to provide ultra-high voltage gain ratio. Their low input current ripple makes them suitable for renewable energy-based systems. Additionally, the ability to optimize output voltage ripple is another feature of the proposed single-switch converters. In this paper, the proposed converters are introduced, analyzed and designed comprehensively. Then, they are evaluated by the comparison of operational characteristics with other state-of-the-art researches. Eventually, the theoretical analytics are validated through some experimental results of a  $1.25 \ kW$  prototype.

### **II. PROPOSED CONVERTERS**

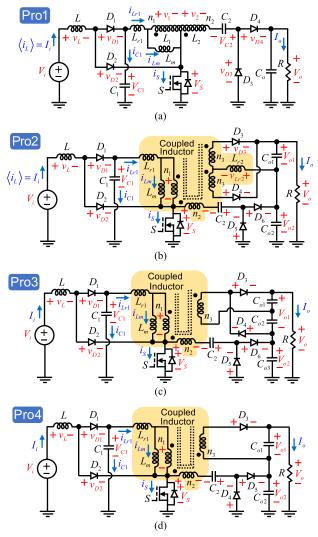

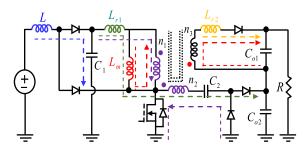

Fig. 1 indicates the circuit of the proposed single-switch converters which are named as  $Pro1 \sim Pro4$ . The converter Pro1 is the basic proposed topology and Pro2  $\sim$  Pro4 are the improved versions. Operation principle of all the proposed converters are almost the same with some differences that will be explained in the following. As shown in Fig. 1 (a)-(d), all introduced converters consist of some similar components such as: one two-, three- or four-winding center-tapped CI, that is modeled with an ideal transformer in addition to a parallel magnetizing inductor  $(L_m)$  and leakage inductances  $(L_{r1} \text{ and } L_{r2})$ , one input inductor (L), one intermediate link capacitor  $(C_1)$ , one power switch (S), one switched capacitor ( $C_2$ ), some diodes ( $D_{(i)}$ ) and output capacitors ( $C_{o(i)}$ ). The fourth topology (Pro4) is assumed as the main converter in this paper; so the comprehensive analysis of Pro4 is provided besides a brief analysis of other topologies.

FIGURE 1. Classification of the DC-DC converters.

## A. FIRST PROPOSED CONVERTER (PRO1)

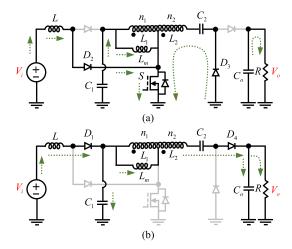

Current flow paths of the Pro1 converter in its two operational intervals of continuous conduction mode (CCM) are shown

in Fig. 2. The operational modes of this converter are evaluated as follows:

## 1) MODE 1 (0 $< t < \text{DT}_{\text{S}}$ ) [FIG. 2(a)]

In this time interval, the switch *S* is turned ON; therefore, the input and magnetizing inductors are charged with the energy of the input source and  $C_1$ , respectively. Diodes  $D_3$  and  $D_4$  are forward and reverse biased, respectively, and  $C_2$  is charged through the secondary winding of the CI, consequently. Considering  $n_2/n_1 = N_2$  and  $n_3/n_1 = N_3$ , voltages of *L* and  $L_m$  are calculated as

$$v_L = V_i \tag{1}$$

$$v_{Lm} = V_{C1} \tag{2}$$

$$V_{C2} = N_2 V_{Lm} \tag{3}$$

2) MODE 2 (DT<sub>s</sub>  $< t < T_s$ ) [FIG. 2(b)]

Finishing the switch ON-state leads to the forward bias of  $D_1$  and  $D_4$ . Hence, the current paths are changed according to Fig. 2(b).

$$v_L = V_i - V_{C1} \tag{4}$$

$$v_{Lm} = \frac{1}{N_2 + 1} (V_{C1} + V_{C2} - V_o)$$

(5)

FIGURE 2. Equivalent circuits of Pro1 in; (a) Mode 1. (b) Mode 2.

## B. FOURTH PROPOSED CONVERTER (PRO4)

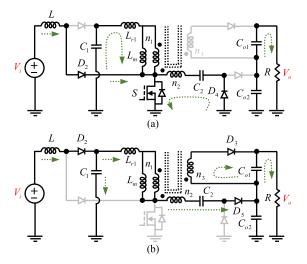

Equivalent circuits of the proposed double-output port Pro4 converter are demonstrated in Fig. 3, which result in the key voltage and current waveforms of Fig. 4.

## 1) MODE 1 (0 $< t < \text{DT}_{\text{S}}$ ) [FIG. 3(a)]

At first, the power switch S is turned ON, so the diodes  $D_1$ and  $D_2$  are revere and forward biased, respectively, and L is magnetized with  $V_i$ , consequently. In this condition, the capacitor  $C_1$  is discharged to the  $L_m$  and the capacitor  $C_2$  is charged with the transferred power of the CI in its secondary winding.

$$v_L = V_i \tag{6}$$

$$v_{Lm} = V_{C1} \tag{7}$$

$$V_{C2} = N_2 V_{Lm} = N_2 V_{C1} \tag{8}$$

2) MODE 2 (DTs  $< t < T_{S}$ ) [FIG. 3(b)]

At  $t = DT_s$ , the power switch duty cycle is completed and the diodes  $D_1$  and  $D_5$  start conducting; hence, the stored energies of L,  $L_m$ , and  $C_2$  are transferred to the  $C_1$ ,  $C_{o1}$  and  $C_{o2}$ , respectively. The main equations of this mode are listed as

$$v_L = V_i - V_{C1} \tag{9}$$

$$v_{Lm} = \frac{1}{N_2 + 1} \left[ V_{C1} + V_{C2} - V_{o2} \right] \tag{10}$$

$$V_{o1} = -N_3 V_{Lm}$$

(11)

FIGURE 3. Equivalent circuits of Pro4 in; (a) Mode 1. (b) Mode 2.

FIGURE 4. Typical voltage and current waveforms of Pro4 in CCM operation.

## III. STEADY-STATE PERFORMANCE ANALYSIS OF THE PROPOSED CONVERTERS

## A. VOLTAGE GAIN CALCULATION

Voltage gain of the Pro4 converter is calculated by volt-second balance law and the resulted equations of

the previous section as

$$DV_i + (1 - D)(V_i - V_{C1}) = 0$$

(12)

$$DV_{C1} + (1-D)(\frac{V_{C1} + V_{C2} - V_{o2}}{1+N_2}) = 0$$

(13)

Using (12), the voltage of  $C_1$  can be expressed as follows:

$$V_{C1} = \frac{V_i}{1 - D} \tag{14}$$

By substituting (14) into (8), the voltage of capacitor  $C_2$  is obtained as

$$V_{C2} = \frac{N_2 V_i}{1 - D}$$

(15)

Then, substituting (14) and (15) into (13) leads to

$$V_{o2} = \frac{(N_2 + 1)V_i}{(1 - D)^2} \tag{16}$$

Regarding to Mode 2, and (11) and (14)-(16), the voltage across  $C_{o1}$  is calculated as

$$V_{o1} = \frac{N_3 D V_i}{(1-D)^2} \tag{17}$$

Due to the attained output capacitors' voltages, the voltage gain of the Pro4 converter in CCM operation is concluded as

$$M_{Pro4} = \frac{V_{o1} + V_{o2}}{V_i} = \frac{1 + N_2 + N_3 D}{(1 - D)^2}$$

(18)

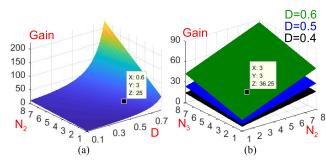

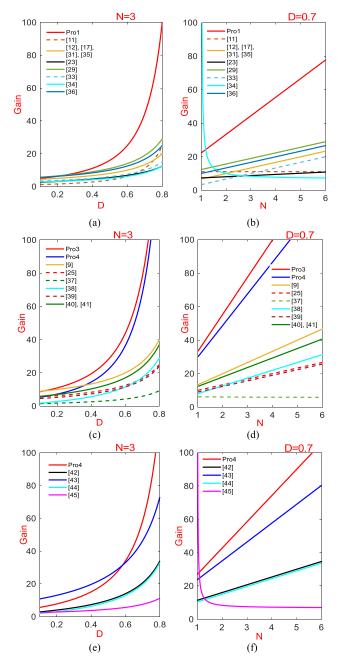

Voltage gain of the Pro1, Pro2, and Pro3 converters are calculated with the same procedure and the results are given in Table. 1 and Fig. 5. It is worth to mention that volt-second balancing law should be applied on  $L_{r2}$  as well as L and  $L_m$  to obtain voltage gain of the Pro2 converter.

#### TABLE 1. Voltage gain of pro1~Pro3.

| Converter | Voltage Gain                                                      |  |  |

|-----------|-------------------------------------------------------------------|--|--|

| Pro1      | $M_{Pro1} = \frac{1 + N_2}{\left(1 - D\right)^2}$                 |  |  |

| Pro2      | $M_{Pro2} = \frac{1+N_2}{\left(1-D\right)^2} + \frac{2N_3D}{1-D}$ |  |  |

| Pro3      | $M_{Pro3} = \frac{1 + N_2 + N_3}{\left(1 - D\right)^2}$           |  |  |

FIGURE 5. Voltage gain. (a) Pro1. (b) Pro4.

#### TABLE 2. Voltage stress analysis of Pro1~Pro3.

| Voltage<br>stress | Pro1                                  | Pro2                                  | Pro3                                |  |  |  |  |

|-------------------|---------------------------------------|---------------------------------------|-------------------------------------|--|--|--|--|

| $V_S$             | $\frac{1}{\left(1-D\right)^2}V_i$     |                                       |                                     |  |  |  |  |

| $V_{D1}$          | $\frac{1}{1-D}V_i$                    |                                       |                                     |  |  |  |  |

| $V_{D2}$          | $\frac{D}{\left(1-D\right)^2}V_i$     |                                       |                                     |  |  |  |  |

| $V_{D3}$          | $1 + N_2 V$                           | $\frac{2DN_3}{\left(1-D\right)^2}V_i$ |                                     |  |  |  |  |

| V <sub>D4</sub>   | $\frac{1+N_2}{\left(1-D\right)^2}V_i$ | $\frac{2N_3}{1-D}V_i$                 | $\frac{N_3}{\left(1-D\right)^2}V_i$ |  |  |  |  |

| $V_{D5}$          |                                       | $1 + N_2 = V_1$                       |                                     |  |  |  |  |

| $V_{D6}$          |                                       | $\frac{1+N_2}{(1-D)^2}V_i$            |                                     |  |  |  |  |

#### **B. VOLTAGE AND CURRENT STRESS ANALYSES**

The equivalent circuit of the Pro4 converter during switch OFF-state (Mode 2) should be analyzed to obtain switch voltage stress. According to (15), (16) and Fig. 4(b), the switch voltage stress can be calculated as

$$V_S = \frac{1}{(1-D)^2} V_i \tag{19}$$

Similarly, voltage stress of the diodes are given as

$$V_{D1} = \frac{1}{1 - D} V_i \tag{20}$$

$$V_{D2} = \frac{D}{(1-D)^2} V_i \tag{21}$$

$$V_{D3} = \frac{N_3}{(1-D)^2} V_i \tag{22}$$

$$V_{D4} = V_{D5} = \frac{1+N_2}{(1-D)^2} V_i$$

(23)

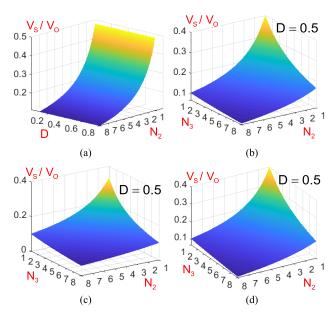

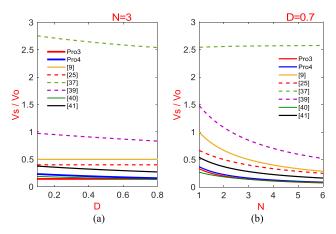

In addition, voltage stress of the semiconductors in Pro1~Pro3 are tabulated in Table. 2, and their normalized values are plotted in Fig. 6. In order to calculate current stress of the semiconductors, the current paths during their on-state should be analyzed. Hence, according to Fig. 4, average current of the switch and diodes of the Pro4 converter are obtained as

$$I_S = I_i + I_{Lr1} + \frac{1}{N_2}(I_{Lr1} - I_{Lm})$$

(24)

$$I_{D1} = I_{D2} = I_i (25)$$

$$I_{D3} = \frac{1}{N_3} I_{Lm}$$

(26)

$$I_{D4} = \frac{1}{N_2} (I_{Lr1} - I_{Lm})$$

(27)

$$I_{D5} = I_{Lr1} \tag{28}$$

where,  $I_{Lr1}$  and  $I_{Lm}$  are the average values of leakage and magnetizing inductance currents, respectively. The same procedure can be followed to obtain current stress of active components of Pro1~Pro3.

Pro1

Pro2

Pro3

Pro4

8

8

2I<sub>ов</sub>f<sub>s</sub>L / V<sub>o</sub>

0.004

0.003

Pro1

Pro2

FIGURE 6. Normalized switch voltage stress. (a) Pro1. (b) Pro2. (c) Pro3. (d) Pro4.

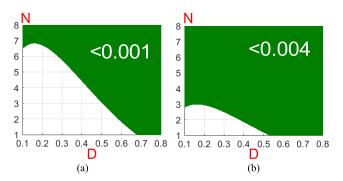

## C. DISCONTINUOUS CONDUCTION MODE (DCM) **BOUNDARY**

In the DCM-CCM boundary of the proposed converters, their average input current in the boundary conduction mode  $(I_{iB})$ is equal to

$$I_{iB} = \frac{\Delta i_L}{2} \tag{29}$$

According to the proposed converters' voltage gain, output load and the current path during switch ON-state, output current and load resistance in the boundary conduction mode  $(I_{oB})$  is obtained as

$$I_{oB} = \frac{DV}{2f_S LM^2} \tag{30}$$

$$R_B = \frac{2f_S L M^2}{D} \tag{31}$$

Normalized form of the boundary conduction mode output current and load resistance of the proposed converters are plotted in Fig. 7 with respect to the duty cycle and the CI turns ratio to identify the CCM and DCM operation regions. As can be seen, the larger the duty cycle and the turns ratio, the wider the solution area in CCM for normalized load resistance and output current, respectively.

#### **IV. DESIGN CONSIDERATIONS**

According to the CCM performance of the Pro4 converter, and the desired voltage and current ripple values of passive components, they can be designed as

$$L = \frac{DV_i}{f_S \Delta i_L} \tag{32}$$

$$L_m = \frac{DV_i}{f_S \Delta i_{Lm}(1-D)} \tag{33}$$

2I<sub>oB</sub>f<sub>s</sub>L / V<sub>o</sub>

0.006

0.004

$$C_1 = \frac{DI_{Lr1}}{f_S \Delta V_{C1}} \tag{34}$$

$$C_2 = \frac{(1-D)I_{Lr1}}{f_S \Delta V_{C2}}$$

(35)

$$C_{o1} = \frac{DI_o}{f_s \Delta V_{Co1}} \tag{36}$$

$$C_{o2} = \frac{DI_o}{f_S \Delta V_{Co2}} \tag{37}$$

Continuous input current with low ripple is a feature of the proposed converters that makes them suitable for renewable application. In order to achieve minimum input current ripple, the effects of different parameters such as turns ratio and duty cycle should be analyzed. According to Fig. 3, the input current ripple of the Pro4 converter is obtained as

$$\Delta i_L = \frac{DV_o}{f_S L M} \tag{38}$$

Substituting (18) into (38) leads to

$$\Delta i_L = \frac{V_O}{f_S L} \frac{D(1-D)^2}{1+N_2+N_3 D}$$

(39)

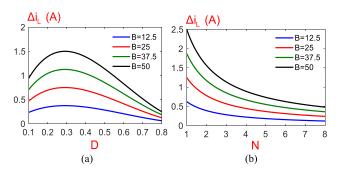

Fig. 8 illustrates the variation of the input current ripple with respect to CI turns ratio and duty cycle in different  $B = V_o/f_S L$  values, where B is utilize to normalize the calculated input current ripple with respect to the converters' output voltage, switching frequency and input inductor. This helps to compare the converters in the same operation and design conditions. It is clear in Fig. 8 that (i)  $\Delta i_L$  reduces by the turns ratio rise, and (ii)  $\Delta i_L$  reaches to its maximum

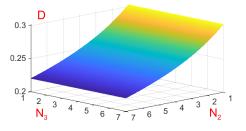

value in a particular duty cycle. Fig. 9 shows the duty cycle values which belong to the  $\Delta i_L$  maximum points with respect to the turns ratios. Due to this figure, the duty cycle values that lead to maximum  $\Delta i_L$  are less than 0.302; therefore, it does not restrict the operational duty cycle range of the proposed converters. In other words, it is mostly preferred to utilize the high step-up converters in D > 0.4 to reach high voltage gain which does not coincide with the maximum input current ripple area. This makes the proposed converter an appropriate candidate for renewable energy applications such as photovoltaics and fuel cells. Fig. 10 presents the desired operation region for duty cycle and turns ratio to achieve specific normalized input current ripple ( $\Delta i_L f_S L/RI_i = D/M^2$ ). According to this figure, high N and D values, which are preferred in high step-up converters, are located in the desired operation area.

**FIGURE 8.** Variation of input current ripple in Pro4 with respect to *B* and: (a) duty cycle in  $N_2 = N_3 = N = 3$ . (b) turns ratio in D = 0.5.

FIGURE 9. Maximum input current ripple realization in Pro4 with respect to duty cycle and CI turns ratios.

## **V. EFFICEINT INDUCTIVE OPERATION**

In order to enhance the performance of the proposed converters, the stored energies in all capacitive and inductive circuit components are recycled and transferred to the output capacitors due to the performance of semiconductors during operational modes. Power flow paths of the Pro4 converter are depicted in Fig. 11, where (i) the stored energy in *L* is transferred to  $C_1$  in  $(1-D)T_s$  (blue path), (ii) the energy of  $C_1$  is discharged to  $C_2$  via  $n_1$  and  $n_2$  in  $DT_s$  (purple path), (iii) the energy of  $Lr_1$  is recycled to  $C_{o2}$  in  $(1-D)T_s$  (green path), (iv) the magnetizing energy is guided to  $C_{o1}$  via  $n_1$  and  $n_3$  in  $(1-D)T_s$  (red path), and (v) the energy of  $Lr_2$  is transferred to  $C_{o1}$  in  $(1-D)T_s$  (yellow path).

**FIGURE 10.** Desired operation region of normalized input current ripple  $(\Delta i_L f_S L/RI_i)$  with respect to duty cycle and turn ration in Pro4.

FIGURE 11. Power flow paths in Pro4 converter.

#### **VI. COMPARISON**

In real industrial applications, introducing a flawless converter is not possible due to the existence of numerous evaluation parameters and desired factors. However, in this study, it is tried to achieve a family of converters with acceptable parameters and valuable features that make them suitable for different industrial applications.

In this section, a fair comparison is performed between the proposed converters and recently introduced ones to clarify their pros and cons. For this purpose, the converters are classified into three categories based on the count of utilized windings in their coupled inductors, and the results are presented in Table 3 and Figs. 12 and 13. Quantities of active and passive components are considered as the first factor in Table 3 since it affects the volume, cost, efficiency, and power density of the converters. From this point of view: (i) [12], [29], [40], [43], [44] and the proposed converters have the least number of power switches and gate drivers, (ii) although the number of semiconductors in [12], [38] and [44] is the lowest, they present low voltage gain. Therefore, by considering the realized voltage gain of the converters, the number of utilized semiconductors is not high in the proposed converters, (iii) [9], [17], [23], [25] and [34] have the highest number of magnetic cores, and (iv) [11], [12], [17], [23], [25], [31], [34]–[38], [40], [42], [44] and Pro1 have the least number of capacitors. Hence, the proposed converters employ acceptably low number of components.

Input current ripple is another significant parameter that specifies whether the converter is suitable for some application such as renewable sources or not. Therefore, low input

#### TABLE 3. Comparison of proposed converter with other state-of-the-art researches.

|                                  | Refs. | S/D/C/CI+L               | LICR | NOM | Voltage Gain (M)                               | Voltage Stress of Switch(s)<br>$(\Sigma V_S)$ | Voltage Stress of Diodes $(\Sigma V_D)$        |

|----------------------------------|-------|--------------------------|------|-----|------------------------------------------------|-----------------------------------------------|------------------------------------------------|

| Topologies with Two-winding CI   | [11]  | 4/0/2/1 <sup>2w</sup> +0 | No   | 2   | $\frac{1}{\left(1-D\right)^2}$                 | $\frac{4-2D}{1-D}V_{o}$                       | 0                                              |

|                                  | [12]  | 1/2/2/1 <sup>2w</sup> +0 | No   | 5   | $\frac{N+1}{1-D}$                              | V <sub>o</sub>                                | $\frac{1+2N}{1+N}V_o$                          |

|                                  | [17]  | 4/4/3/1 <sup>2w</sup> +2 | Yes  | 8   | $\frac{N+1}{1-D}$                              | $\frac{4V_o}{1+N}$                            | $4V_o$                                         |

|                                  | [23]  | 2/4/3/1 <sup>2w</sup> +2 | No   | 4   | $\frac{2}{1-D} + ND$                           | $\frac{2V_o}{2 + ND - ND^2}$                  | $(\frac{3}{2} + \frac{4N - 3ND}{2M})V_o$       |

|                                  | [29]  | 1/4/5/1 <sup>2w</sup> +1 | Yes  | 5   | $\frac{N+D+2}{1-D}$                            | $\frac{V_o}{2+N+D}$                           | $\frac{4+2N}{2+N+D}V_o$                        |

|                                  | [31]  | 2/2/3/1 <sup>2w</sup> +0 | No   | 10  | $\frac{N+1}{1-D}$                              | $\frac{2V_o}{1+N}$                            | $\frac{2N}{1+N}V_o$                            |

|                                  | [33]  | 2/2/4/1 <sup>2w</sup> +1 | Yes  | 6   | $\frac{N}{1-D}$                                | $\frac{2V_o}{N}$                              | $2V_o$                                         |

|                                  | [34]  | 4/0/3/1 <sup>2w</sup> +2 | No   | 5   | $\frac{2N-1}{(N-1)(1-D)}$                      | $2V_o$                                        | 0                                              |

|                                  | [35]  | 4/0/3/1 <sup>2w</sup> +0 | No   | 5   | $\frac{N+1}{1-D}$                              | $\frac{2+3N-2ND}{1+N}\boldsymbol{V}_{o}$      | 0                                              |

|                                  | [36]  | 4/0/3/1 <sup>2w</sup> +0 | No   | 5   | $\frac{N+2}{1-D}$                              | $2V_o$                                        | 0                                              |

|                                  | Pro1  | 1/4/3/1 <sup>2W</sup> +1 | Yes  | 2   | $\frac{1+N_2}{(1-D)^2}$                        | $\frac{V_o}{(1-D)^2 M_{Pro1}}$                | $\frac{3+2N_2}{(1-D)^2 M_{Pro1}} V_o$          |

| Topologies with Three-winding CI | [9]   | 4/6/9/2 <sup>3w</sup> +2 | No   | 11  | $\frac{2(N+1)}{1-D}$                           | $\frac{2V_o}{1+N}$                            | $\frac{3+4N}{1+N}V_o$                          |

|                                  | [25]  | 2/4/3/1 <sup>3w</sup> +2 | Yes  | 10  | $\frac{N+2}{1-D}$                              | $\frac{2V_o}{2+N}$                            | $\frac{4+N}{2+N}V_o$                           |

|                                  | [37]  | 4/1/3/1 <sup>3w</sup> +0 | No   | 8   | $\frac{2 + N_1 D + N_2}{1 + N_2 - D(1 + N_2)}$ | $\left[2 + \frac{1}{(1-D)M}\right] V_o$       |                                                |

|                                  | [38]  | 3/0/2/1 <sup>3w</sup> +0 | No   | 7   | $\frac{1+D(n+n_a)}{1-D}$                       |                                               | 0                                              |

|                                  | [39]  | 4/2/4/1 <sup>3w</sup> +0 | No   | 9   | $\frac{1+N+D}{1-D}$                            | $\frac{4V_o}{1+N+D}$                          | $\frac{2N}{1+N+D}V_o$                          |

|                                  | [40]  | 1/3/3/1 <sup>3w</sup> +0 | No   | 4   | $\frac{2 + N_3 D + N_2}{1 - D}$                | $\frac{V_o}{2+N+ND}$                          | $\frac{3+3N}{2+N+ND}V_o$                       |

|                                  | [41]  | 2/3/4/1 <sup>3w</sup> +0 | No   | 9   | $\frac{Dn_t + n_s + 2}{1 - D}$                 | $\frac{2V_o}{2+N+ND}$                         | $\frac{2+ND+2N}{2+N+ND}V_o$                    |

|                                  | Pro3  | 1/6/5/1 <sup>3W</sup> +1 | Yes  | 2   | $\frac{1 + N_2 + N_3}{(1 - D)^2}$              | $\frac{V_o}{(1-D)^2 M_{Pro3}}$                | $\frac{3+2N_2+2N_3}{(1-D)^2M_{Pro3}}V_o$       |

|                                  | Pro4  | 1/5/4/1 <sup>3w</sup> +1 | Yes  | 2   | $\frac{1 + N_2 + N_3 D}{\left(1 - D\right)^2}$ | $\frac{V_o}{\left(1-D\right)^2 M_{Pro4}}$     | $\frac{3+2N_2+N_3}{(1-D)^2M_{Pro4}}V_o$        |

| Topologies with Four-winding CI  | [42]  | 4/0/3/14w+0              | No   | 4   | $\frac{2(1+nD)}{1-D}$                          | $\frac{(2+N)V_o}{1+ND}$                       | 0                                              |

|                                  | [43]  | 1/9/8/1 <sup>4w</sup> +0 | No   | 5   | $\frac{(1+2n)(1+D)+2}{1-D}$                    | $\frac{2V_o}{(1+2N)(1+D)+2}$                  | $\frac{8+6N}{(1+2N)(1+D)+2}V_{o}$              |

|                                  | [44]  | 1/2/3/1 <sup>4w</sup> +0 | No   | 4   | $\frac{1+(1+2n)D}{1-D}$                        | $\frac{V_o}{1+(1+2n)D}$                       | $\frac{2+2N}{1+(1+2n)D}V_o$                    |

|                                  | [45]  | 2/6/6/14w+0              | No   | 6   | $\frac{2N-1.5}{(N-1)(1-D)}$                    | $\frac{N-1}{2N-1.5}V_o$                       | $\frac{3N-2}{2N-1.5}V_o$                       |

|                                  | Pro2  | 1/6/4/1 <sup>4W</sup> +1 | Yes  | 2   | $\frac{1+N_2}{(1-D)^2} + \frac{2N_3D}{1-D}$    | $\frac{V_o}{(1-D)^2 M_{Pro2}}$                | $\frac{3+2N_2+2N_3+2DN_3}{(1-D)^2M_{Pro2}}V_o$ |

\* Note: In the CI count, a<sup>bw</sup> indicates "a" coupled inductor coils with "b" windings.

current ripple (LICR) is considered as the second evaluation parameter. For this purpose, the converters with discontinuous input current, voltage fed input port and coupled input inductor are considered as the converters with higher input current ripple. On the other hand, the converters with a singlewinding inductor or single-winding interleaved inductors in

**FIGURE 12.** Comparison of converters' voltage gain with: (a, b) a two-winding coupled inductor. (c, d) a three-winding coupled inductor. (e, f) a four-winding coupled inductor.

the input port are considered as the LICR converters. According to Table 3, [17], [25], [29], [33] and the proposed converters operate with the lowest input current ripple. The number of operational modes (NOM) is the next parameter evaluated in Table 3, which affects on the converter control complexity and duty cycle range. The last columns of Table 3 are dedicated to the voltage gain ratio, accumulative switch(s) voltage stress, and accumulative diodes voltage stress, respectively. According to Table 3, the comparison of the above-mentioned parameters clarify the superiority of the proposed converters with less active and passive components, and low input current ripple and NOM. In addition, voltage gain and normalized accumulative switch voltage stress of the converters are plotted in Fig. 12 and Fig. 13 with respect to the duty cycle and turns ratio. As can be seen, the proposed converters achieve the highest voltage gain and the lowest normalized accumulative switch voltage stress in both conditions.

FIGURE 13. Normalized switch voltage stress comparison of converters' with a three-winding coupled inductor with respect to: (a) duty cycle. (b) coupled inductor turns ratio.

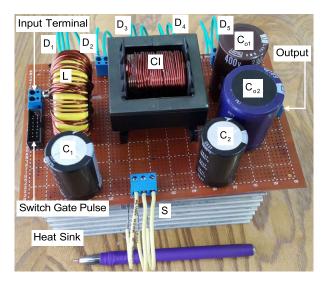

FIGURE 14. Experimental prototype of Pro4. (The switch and diodes are implemented under the board.)

#### **VII. EXPERIMENTAL RESULTS**

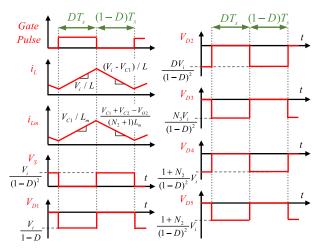

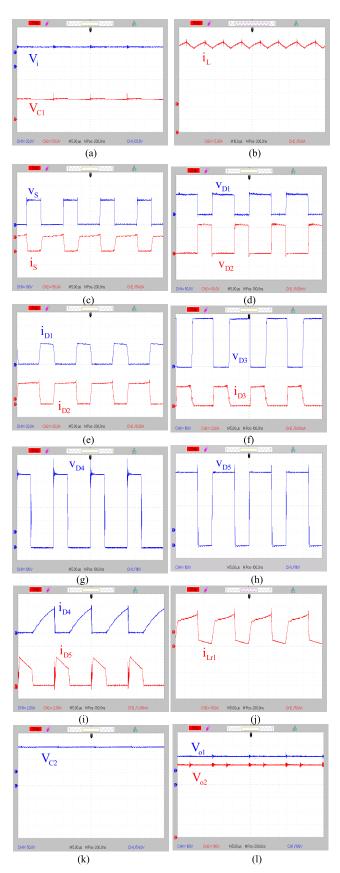

In order to validate the performance and theoretical analytics of the proposed converters, the Pro4 topology is selected for experimental prototyping, where the experimental circuit and the obtained results are shown in Fig. 14 and Fig. 15, respectively. This circuit is designed for the nominal power of  $P_o = 1.25 \ kW$  and the experimental results are obtained in the test point of  $P_o = 1014 \ W$ . The switching frequency is equal to 50 kHz, and  $N_2 = N_3 = 2$ . The passive components are designed as  $L = 122\mu \text{H}$ ,  $n_1 = 12$ ,  $n_2 = n_3 = 24$ ,  $C_1 = C_2 = 470 \ \mu\text{F}$ ,  $C_{o1} = 330 \ \mu\text{F}$  and  $C_{o2} = 150 \ \mu\text{F}$ .

FIGURE 15. Experimental results.

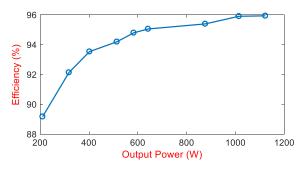

FIGURE 16. Efficiency with respect to the output power.

Furthermore, the specifications of semiconductors are listed as follows: UJ4C075018K3S for S, VS-60EPU06-N3 for  $D_1$ and  $D_2$ , MUR1560 for  $D_3$  and DSEP30-12AR for  $D_4$  and  $D_5$ .

Fig. 15(a) shows the input voltage and voltage across  $C_1$ with  $V_i = 30 V$  and  $V_{C1} = 73.9 V$ , which verifies (14). Input current  $(I_i = I_L)$  with the approximate 10% peak-peak ripple value is depicted in Fig. 15(b). In order to evaluate the switch performance, its drain-source voltage and current are illustrated in Fig. 15(c). As expected, its voltage stress is approximate 185 V that confirms (19). Voltage and current of diodes are shown in Figs. 15(d)-(i). As can be seen, the applied voltage stress across the diodes match with the results in (20)-(23). One of the significant features of this experiment is the absence of the high-voltage spikes during the switching transitions. Current profile of the leakage inductance is also demonstrated in Fig. 15(j). Using (15)-(17),  $V_{C2}$ ,  $V_{o1}$ , and Vo2 are calculated as 150 V, 225 V, and 562 V, respectively. As shown in Fig. 15(k)-(l), the experimental voltage across C1, C<sub>01</sub>, and C<sub>02</sub> are measured as 145.5 V, 220 V, and 556 V, respectively. Eventually, the efficiency of the Pro4 converter is measured in different output power values which is shown in Fig. 16. According to this figure, the maximum efficiency of this converter is equal to 95.94%.

#### **VIII. CONCLUSION**

A new family of high step-up DC-DC converters was proposed in this paper, which employs a center-tapped coupled inductor. Wide output voltage gain, low input current ripple, low normalized voltage stress across switching components, recycling all inductive and capacitive energies, no circulating current, simple control, low switching voltage spikes and operation of the coupled inductor with high power density are the main features of the proposed converters. Specifically, the main operational characteristic of these converters is employing different capacitive and inductive approaches to harvest the stored energies in capacitors and inductors such as leakage and magnetizing inductances, and transfer them toward output load. In this paper, comprehensive theoretical analytics, design considerations, comparison study and experimental results were provided to validate the performance and applicability of the proposed converters. The experimental results showed the approximate efficiency range of 89.18% to 95.94% from light to nominal test points.

#### REFERENCES

- E. Babaei, H. Tarzamni, F. Tahami, H. K. Jahan, and M. B. B. Sharifian, "Multi-input high step-up inverter with soft-switching capability, applicable in photovoltaic systems," *IET Power Electron.*, vol. 13, no. 1, pp. 133–143, Jan. 2020.

- [2] P. Kolahian, H. Tarzamni, A. Nikafrooz, and M. Hamzeh, "Multi-port DC– DC converter for bipolar medium voltage DC micro-grid applications," *IET Power Electron.*, vol. 12, no. 7, pp. 1841–1849, Jun. 2019.

- [3] H. Trazamni, E. Babaei, and M. Sabahi, "Full soft-switching high stepup DC–DC converter based on active resonant cell," *IET Power Electron.*, vol. 10, no. 13, pp. 1729–1739, Oct. 2017.

- [4] H. Tarzamni, E. Babaei, A. Z. Gharehkoushan, and M. Sabahi, "Interleaved full ZVZCS DC–DC boost converter: Analysis, design, reliability evaluations and experimental results," *IET Power Electron.*, vol. 10, no. 7, pp. 835–845, Jun. 2017.

- [5] H. K. Jahan, H. Tarzamni, P. Kolahian, S. H. Hosseini, F. Tahami, and F. Blaabjerg, "A switched-capacitor inverter with optimized switch-count considering load power factor," in *Proc. IECON 45th Annu. Conf. IEEE Ind. Electron. Soc.*, Oct. 2019, pp. 4959–4964.

- [6] H. Tarzamni, E. Babaei, F. P. Esmaeelnia, P. Dehghanian, S. Tohidi, and M. B. B. Sharifian, "Analysis and reliability evaluation of a high step-up soft switching push-pull DC–DC converter," *IEEE Trans. Rel.*, vol. 69, no. 4, pp. 1376–1386, Dec. 2020.

- [7] S. H. Hosseini, A. Z. Gharehkoushan, and H. Tarzamni, "A multilevel boost converter based on a switched-capacitor structure," *Proc. 10th Int. Conf. Electr. Electron. Eng. (ELECO)*, Dec. 2017, pp. 249–253.

- [8] T. Zeng, Z. Wu, and L. He, "An interleaved soft switching high step-up converter with low input current ripple and high efficiency," *IEEE Access*, vol. 7, pp. 93580–93593, 2019.

- [9] L. He, X. Xu, J. Chen, J. Sun, D. Guo, and T. Zeng, "A plug-play active resonant soft switching for current-auto-balance interleaved high step-up DC/DC converter," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7603–7616, Aug. 2019.

- [10] M. Forouzesh, Y. Shen, K. Yari, Y. P. Siwakoti, and F. Blaabjerg, "Highefficiency high step-up DC–DC converter with dual coupled inductors for grid-connected photovoltaic systems," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5967–5982, Jul. 2018.

- [11] A. R. N. Akhormeh, K. Abbaszadeh, M. Moradzadeh, and A. Shahirinia, "High-gain bidirectional quadratic DC–DC converter based on coupled inductor with current ripple reduction capability," *IEEE Trans. Ind. Electron.*, vol. 68, no. 9, pp. 7826–7837, Sep. 2021.

- [12] R. Afzal, Y. Tang, H. Tong, and Y. Guo, "A high step-up integrated coupled inductor-capacitor DC–DC converter," *IEEE Access*, vol. 9, pp. 11080–11090, 2021.

- [13] M. Rezaie and V. Abbasi, "Ultrahigh step-up DC–DC converter composed of two stages boost converter, coupled inductor and multiplier cell," *IEEE Trans. Ind. Electron.*, early access, Jun. 29, 2021, doi: 10.1109/TIE.2021.3091916.

- [14] M. E. Azizkandi, F. Sedaghati, H. Shayeghi, and F. Blaabjerg, "A high voltage gain DC–DC converter based on three winding coupled inductor and voltage multiplier cell," *IEEE Trans. Power Electron.*, vol. 35, no. 5, pp. 4558–4567, May 2020.

- [15] M. E. Azizkandi, F. Sedaghati, H. Shayeghi, and F. Blaabjerg, "Two-and three-winding coupled-inductor-based high step-up DC–DC converters for sustainable energy applications," *IET Power Electron.*, vol. 13, no. 1, pp. 144–156, Jan. 2020.

- [16] W. Hassan, Y. Lu, M. Farhangi, D. D. Lu, and W. Xiao, "Design, analysis and experimental verification of a high voltage gain and highefficiency DC–DC converter for photovoltaic applications," *IET Renew. Power Gener.*, vol. 14, no. 10, pp. 1699–1709, Jul. 2020.

- [17] W. Li, W. Li, X. He, D. Xu, and B. Wu, "General derivation law of nonisolated high-step-up interleaved converters with built-in transformer," *IEEE Trans. Ind. Electron.*, vol. 59, no. 3, pp. 1650–1661, Mar. 2012.

- [18] W. Li, Y. Zhao, Y. Deng, and X. He, "Interleaved converter with voltage multiplier cell for high step-up and high-efficiency conversion," *IEEE Trans. Power Electron.*, vol. 25, no. 9, pp. 2397–2408, Sep. 2010.

- [19] W. Li, Y. Zhao, J. Wu, and X. He, "Interleaved high step-up converter with winding-cross-coupled inductors and voltage multiplier cells," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 133–143, Jan. 2012.

- [20] W. Li, W. Li, X. Xiang, Y. Hu, and X. He, "High step-up interleaved converter with built-in transformer voltage multiplier cells for sustainable energy applications," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2829–2836, Jun. 2014.

- [21] K.-C. Tseng and C.-C. Huang, "High step-up high-efficiency interleaved converter with voltage multiplier module for renewable energy system," *IEEE Trans. Power Electron.*, vol. 61, no. 3, pp. 1311–1319, Mar. 2014.

- [22] K.-C. Tseng, J.-Z. Chen, J.-T. Lin, C.-C. Huang, and T.-H. Yen, "High step-up interleaved forward-flyback boost converter with threewinding coupled inductors," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 4696–4703, Sep. 2015.

- [23] C.-M. Lai, C.-T. Pan, and M.-C. Cheng, "High-efficiency modular high step-up interleaved boost converter for DC-microgrid applications," *IEEE Trans. Ind. Appl.*, vol. 48, no. 1, pp. 161–171, Jan./Feb. 2012.

- [24] F. Sedaghati, M. Eskandarpour Azizkandi, S. H. L. Majareh, and H. Shayeghi, "A high-efficiency non-isolated high-gain interleaved DC– DC converter with reduced voltage stress on devices," in *Proc. 10th Int. Power Electron., Drive Syst. Technol. Conf. (PEDSTC)*, Feb. 2019, pp. 729–734.

- [25] K.-C. Tseng, C.-A. Cheng, and C.-T. Chen, "High step-up interleaved boost converter for distributed generation using renewable and alternative power sources," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 2, pp. 713–722, Jun. 2017.

- [26] S. Dwari and L. Parsa, "An efficient high-step-up interleaved DC-DC converter with a common active clamp," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 66–78, Jan. 2011.

- [27] B. M. Alharbi, M. A. Alhomim, and R. A. McCann, "A high voltage ratio three-stage cascaded interleaved boost converters for PV application," in *Proc. IEEE Power Energy Conf. Illinois (PECI)*, Feb. 2020, pp. 1–5.

- [28] B. P. Baddipadiga and M. Ferdowsi, "A high-voltage-gain DC-DC converter based on modified Dickson charge pump voltage multiplier," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7707–7715, Oct. 2017.

- [29] R. Moradpour, H. Ardi, and A. Tavakoli, "Design and implementation of a new SEPIC-based high step-up DC/DC converter for renewable energy applications," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1290–1297, Feb. 2018.

- [30] H. Lei, R. Hao, X. You, and F. Li, "Nonisolated high step-up softswitching DC–DC converter with interleaving and Dickson switchedcapacitor techniques," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 3, pp. 2007–2021, Sep. 2020.

- [31] H.-W. Seong, H.-S. Kim, K.-B. Park, G.-W. Moon, and M.-J. Youn, "High step-up DC–DC converters using zero-voltage switching boost integration technique and light-load frequency modulation control," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1383–1400, Mar. 2012.

- [32] S. M. Salehi, S. M. Dehghan, and S. Hasanzadeh, "Interleaved-input series-output ultra-high voltage gain DC–DC converter," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3397–3406, Apr. 2019.

- [33] A. Kumar and P. Sensarma, "Ripple-free input current high voltage gain DC-DC converters with coupled inductors," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3418–3428, Apr. 2019.

- [34] H. Liu, L. Wang, Y. Ji, and F. Li, "A novel reversal coupled inductor highconversion-ratio bidirectional DC–DC converter," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 4968–4979, Jun. 2018.

- [35] M. P. Shreelakshmi, M. Das, and V. Agarwal, "Design and development of a novel high voltage gain, high-efficiency bidirectional DC–DC converter for storage interface," *IEEE Trans. Ind. Electron.*, vol. 66, no. 6, pp. 4490–4501, Jun. 2019.

- [36] Z. Hosseinzadeh, N. Molavi, and H. Farzanehfard, "Soft-switching high step-up/down bidirectional DC–DC converter," *IEEE Trans. Ind. Electron.*, vol. 66, no. 6, pp. 4379–4386, Jun. 2019.

- [37] M. Vesali, M. Delshad, E. Adib, and M. R. Amini, "A new nonisolated soft switched DC–DC bidirectional converter with high conversion ratio and low voltage stress on the switches," *Int. Trans. Electr. Energy Syst.*, vol. 31, no. 1, Jan. 2021, Art. no. e12666.

- [38] M. Packnezhad and H. Farzanehfard, "Soft-switching high step-up/down converter using coupled inductors with minimum number of components," *IEEE Trans. Ind. Electron.*, vol. 68, no. 9, pp. 7938–7945, Sep. 2021.

- [39] Y. Tang, H. Tong, R. Afzal, and Y. Guo, "High step-up ZVT converter based on active switched coupled inductors," *IEEE Access*, early access, Nov. 27, 2020, doi: 10.1109/ACCESS.2020.3041004.

- [40] M. Mahmoudi, A. Ajami, and E. Babaei, "A non isolated high step up DC–DC converter with integrated 3 winding coupled inductor and reduced switch voltage stress," *Int. J. Circuit Theory Appl.*, vol. 46, no. 10, pp. 1879–1898, 2018.

- [41] X. Zhang, L. Sun, Y. Guan, S. Han, H. Cai, Y. Wang, and D. Xu, "Novel high step-up soft-switching DC–DC converter based on switched capacitor and coupled inductor," *IEEE Trans. Power Electron.*, vol. 35, no. 9, pp. 9471–9481, Sep. 2020.

## IEEE Access

- [42] E. Babaei, Z. Saadatizadeh, and V. Ranjbarizad, "A new nonisolated bidirectional DC–DC converter with ripple-free input current at low-voltage side and high conversion ratio," *Int. Trans. Elect. Energy Syst.*, vol. 28, no. 2, pp. 1–21, Dec. 2017.

- [43] M. Moradzadeh, E. Babaei, E. Zamiri, and S. Hamkari, "A new high stepup DC/DC converter structure by using coupled inductor with reduced switch-voltage stress," *Elect. Power Compon. Syst.*, vol. 45, no. 15, pp. 1705–1719, 2017.

- [44] Y. Hao, H. Li, K. Li, C. Fang, and X. Ding, "Single-switch boost converter with extremely high step-up voltage gain," *J. Power Electron.*, vol. 20, no. 6, pp. 1375–1385, Nov. 2020.

- [45] F. Li, S. Ji, N. Geng, J. Yang, S. Liang, L. Liu, Z. Yue, P. Gao, Q. Xue, X. Liu, F. Zhu, X. Sun, and Y. Yao, "High step-up three level boost converter with inverse characteristic," *J. Eng.*, vol. 2018, no. 17, pp. 1844–1850, Nov. 2018.

**HOMAYON SOLTANI GOHARI** was born in Kerman, Iran, in December 1994. He received the M.Sc. degree in electrical power engineering, power electronics, from K. N. Toosi University of Technology, Tehran, Iran, in 2020. His research interests include power electronics, EVs power converter, energy management, high-voltage gain dc-dc converters, and rectifiers with PFC.

**MATTI LEHTONEN** received the master's and Licentiate degrees in electrical engineering from Helsinki University of Technology, Finland, in 1984 and 1989, respectively, and the D.Tech. degree from Tampere University of Technology, Finland, in 1992. Since 1999, has been a Professor with Helsinki University of Technology. He is currently the Head of Power Systems and High Voltage Engineering with Aalto University, Finland. His research interests include power system planning and asset management.

**OLEKSANDR HUSEV** (Senior Member, IEEE) received the B.Sc. and M.Sc. degrees in industrial electronics from Chernihiv State Technological University, Chernihiv, Ukraine, in 2007 and 2008, respectively. He defended the Ph.D. thesis from the Institute of Electrodynamics, National Academy of Science of Ukraine, in 2012. He is currently a Senior Researcher with the Department of Electrical Power Engineering and Mechatronics, TalTech University. He has over 100 publica-

tions and is the holder of several patents. His research interests include power electronics systems, design of novel topologies, control systems based on a wide range of algorithms, including modeling, design, and simulation, and applied design of power converters and control systems and application, stability investigation.

**FREDE BLAABJERG** (Fellow, IEEE) received the Ph.D. degree in electrical engineering from Aalborg University, in 1995. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia.

From 1987 to 1988, he was with ABB-Scandia, Randers, Denmark. He became an Assistant Professor, in 1992, an Associate Professor, in 1996, and a Full Professor of power electronics and

drives, in 1998, in the Department of Energy Technology, Aalborg University, Denmark. Since 2017, he became a Villum Investigator. He has published more than 600 journal articles in the fields of power electronics and its applications. He is the coauthor of four monographs and an editor of ten books in power electronics and its applications. His current research interests include power electronics and its applications, such as in wind turbines, PV systems, reliability, harmonics, and adjustable speed drives.

Dr. Blaabjerg has received 30 IEEE prize paper awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, and the Villum Kann Rasmussen Research Award 2014. From 2006 to 2012, he was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS. From 2019 to 2020, he served as the President of the IEEE Power Electronics Society. He is the Vice-President of the Danish Academy of Technical Sciences too. He is nominated in 2014–2018 by Thomson Reuters to be between the most 250 cited researchers in engineering in the world. He has been a Distinguished Lecturer of the IEEE Power Electronics Society, from 2005 to 2007, and the IEEE Industry Applications Society, from 2010 to 2011 as well as from 2017 to 2018.

**HADI TARZAMNI** (Student Member, IEEE) was born in Tabriz, Iran, in 1992. He received the B.Sc. and M.Sc. degrees (Hons.) in power electrical engineering from the Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz, in 2014 and 2016, respectively. He is currently pursuing the Ph.D. degree in power electronics engineering under a dual-degree doctoral program with the Department of Electrical Engineering, Sharif University of Technology, Tehran,

Iran, and the Department of Electrical Engineering and Automation, Aalto University, Finland. Since January 2021, he has been a Researcher with the Department of Electrical Engineering and Automation; and the Department of Electronics and Nanoengineering, Aalto University. He has authored or coauthored more than 20 journal articles and conference papers. He also holds six patents in the area of power electronics. His research interests include power electronic converters analysis and design, dc–dc converters, high step-up power conversion, wireless power transfer, soft-switching and resonant converters, wide band gap (WBG) devices, and reliability analysis. He was a recipient of the Best Paper Award in 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC) in 2019.

**NASER VOSOUGHI KURDKANDI** was born in Bostanabad, East Azerbaijan, Iran, in 1989. He received the B.Sc. degree in electrical engineering from Islamic Azad University, South Tehran Branch, Tehran, Iran, in 2011, and the M.Sc. and Ph.D. degrees in electrical engineering and power electronics from the University of Tabriz, Tabriz, Iran, in 2014 and 2019, respectively. From 2019 to 2020, he was a Postdoctoral Researcher with the University of Tabriz. Since 2020, he has been a

Postdoctoral Researcher with Tallinn University of Technology. His current research interests include multilevel inverters, grid-connected PV inverters, dc-dc switched-capacitor and switched-inductor converters, fast charge station for electric vehicles, battery-based energy storage systems, and induction motor drives.