Aalborg Universitet

# Effect of Current Distortion and Unbalanced Loads on Semiconductors Reliability

Lledo-Ponsati, Tomas; Bahman, Amir Sajjad; Iannuzzo, Francesco; Montesinos-Miracle, Daniel; Galceran-Arellano, Samuel

Published in: **IEEE** Access

DOI (link to publication from Publisher): 10.1109/ACCESS.2021.3133019

Creative Commons License CC BY 4.0

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Lledo-Ponsati, T., Bahman, A. S., Iannuzzo, F., Montesinos-Miracle, D., & Galceran-Arellano, S. (2021). Effect of Current Distortion and Unbalanced Loads on Semiconductors Reliability. IEEE Access, 9, 162660-162670. https://doi.org/10.1109/ACCESS.2021.3133019

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Received November 15, 2021, accepted December 1, 2021, date of publication December 6, 2021, date of current version December 16, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3133019

# **Effect of Current Distortion and Unbalanced Loads on Semiconductors Reliability**

TOMÀS LLEDÓ-PONSATI<sup>®1</sup>, (Graduate Student Member, IEEE), AMIR SAJJAD BAHMAN<sup>®2</sup>, (Senior Member, IEEE), FRANCESCO IANNUZZO<sup>®2</sup>, (Senior Member, IEEE), DANIEL MONTESINOS-MIRACLE<sup>®1</sup>, (Senior Member, IEEE), AND SAMUEL GALCERAN-ARELLANO<sup>1</sup>

<sup>1</sup>Centre d'Innovació Tecnològica en Convertidors Estàtics i Accionaments (CITCEA-UPC), Departament d'Enginyeria Elèctrica, ETS d'Enginyeria Industrial de Barcelona, Universitat Politècnica de Catalunya, 08028 Barcelona, Spain 2/Contex of Balieble Pouver Electronics (CORPE), Achberg Departed (A ALD, 0220 Achberg, Departed)

<sup>2</sup>Center of Reliable Power Electronics (CORPE), Aalborg University (AAU), 9220 Aalborg, Denmark

Corresponding author: Tomàs Lledó-Ponsati (tomas.lledo@upc.edu)

**ABSTRACT** This article presents a reliability analysis of a 4-wire grid-tied inverter under different loading conditions, considering unbalanced loads and harmonic distortion in the current consumed. The proposed power converter is used as a case study to assess the impact of current disturbances on the semiconductors' reliability. The 4-wire inverter analyzed is implemented with a 3-leg SiC MOSFET power module and a neutral wire connected to the midpoint of the DC-link. The analysis is founded on the literature's reliability curves for power switches. As key take-home findings, the addition of harmonic content in the load current plays a dominant role in the semiconductors' expected lifetime, especially for the low-frequency harmonics, e.g., third harmonic. Furthermore, the phase delay of the harmonic current content is revealed as a critical factor in the semiconductor's reliability. Additionally, the existence of unbalanced loads substantially modifies the reliability of the semiconductors of the inverter. The results confirm that converters' reliability is highly dependent on the loading conditions and harmonic content, so identifying the most critical conditions is inevitable.

**INDEX TERMS** Reliability, silicon carbide, MOSFETs, harmonic distortion, current imbalances.

# I. INTRODUCTION

The reliability of grid-tied converters has been extensively studied in the past years. Multiple analyses can be found in the literature. However, such analyses have often been performed only for ideal operating conditions without regard to possible disturbances to these systems.

For example, the presence of low-frequency harmonic distortion in the grid voltage may lead the converters connected to it to operate with a distorted current. The presence of harmonics can change the shape of the current and, thus, the inverter's thermal load, which, if not taken into account, can affect the expected lifetime of the equipment [1].

This paper analyzes the effect on the semiconductors' reliability of unbalanced and harmonic distorted currents for a 4-wire inverter. The obtained results can be extrapolated to any kind of equipment that operates under these conditions

The associate editor coordinating the review of this manuscript and approving it for publication was Paolo Giangrande<sup>(D)</sup>.

such as, 4-wire inverters for isolated microgrids [2], threephase power factor correction (PFC) rectifiers [3], uninterruptable power supplies (UPS) [4], active filters [5], or inverters for drives and EV traction systems [6].

The increasing use of microgrids and isolated grids leads to systems that inherently operate under these conditions [7]–[9]. In a microgrid, the presence of nonlinear loads, i.e., with high current THD, and single-phase type, can be high. Consequently, converters operating as power sources for these microgrids, [10]–[12], need to work reliably with these types of loads, and their estimated operating lifetime must consider them. The same considerations apply to UPS systems as portrayed in [4].

Typically, PFC rectifiers consume unbalanced currents when connected to unbalanced grids [13]. As pointed out in [14], this is also a common situation for AC/DC grid-tied inverters with a dq0-based control.

Finally, active filters are typically used to balance the current consumed from the grid and, at the same time, eliminate

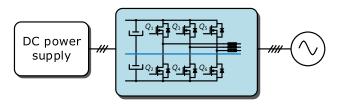

FIGURE 1. Platform simplified diagram.

the current harmonic content [15]–[18]. Consequently, its current usually is unbalanced between phases and presents a high harmonic distortion.

As it has been exposed, these operating conditions are not uncommon and shall be considered. However, the effect of these disturbances has generally been overlooked in the literature, and few examples are reported. In [19], the authors analyze the impact of reactive power injection on PV inverters' reliability. In [20], the effect of grid voltage unbalances on the reliability of adjustable speed drives is studied. However, only the capacitors' reliability is analyzed.

In [21] and [22], the authors analyze the reliability of single-phase transformerless PV inverters. In [23], the authors propose an optimized design method for transformerless PV inverters considering its reliability. In all the cases, the analyses are performed considering a null THD. Therefore, the possibility of operating with a current with harmonic content is not considered.

Reducing the harmonic content and current unbalances in motor control algorithms is a hot topic in the literature [24]-[28]. However, most of the solutions proposed are complex. Usually, the inverters used for motor control applications do not include these features. Therefore, it is interesting to analyze the effect of the disturbances on reliability. In [29], the semiconductor reliability for a three-phase inverter used in a wind turbine is analyzed. By the nature of the study, the presence of unbalanced loads is unlikely. However, the presence of low-frequency harmonics in the current cannot be ruled out. Due to AC machines' manufacturing limitations, the back electromotive force (EMF) is not purely sinusoidal and has harmonic content [30]. Consequently, it is likely to have a harmonic distortion in the currents [31]. Its effect may be relevant for the semiconductors' reliability, and it has not been considered. Finally, [32] presents a three-phase inverter reliability analysis for more electric aircraft. An airplane can be regarded as a microgrid. Therefore, as mentioned previously, it can have single-phase and nonlinear loads, which increase the current imbalances in the inverter and the harmonic current content. Again, the effect that such disturbances may have on semiconductors' reliability has not been considered.

In [33], the authors analyze an active filter's IGBTs' reliability. However, it does not consider the phase delay of the harmonics compensated. As proved in our paper, this is a critical point in the semiconductors' reliability.

It is critical to analyze the effect of imbalances and harmonic current distortion on semiconductors' reliability for all

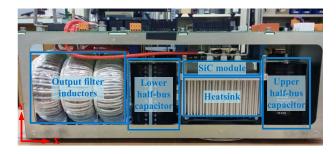

FIGURE 2. The proposed platform. The lateral of the platform is opened to show the internal elements.

the reasons mentioned above. This paper proposes a comparative methodology to establish the impact on the semiconductors' reliability of current imbalances and harmonic content. In [34], the authors present a similar analysis to assess the effect of different modulation strategies on semiconductors' reliability. The authors use a power converter as a case study and, with the help of established lifetime models, assess the variation in reliability with different modulation strategies.

Both disturbances are analyzed separately, considering different cases. The reliability values for each case are compared against a base case. The results show that unbalanced loads reduce the semiconductors' reliability if some phases are overloaded. Furthermore, the harmonic content is proved to be a stress factor that can substantially reduce the semiconductors' reliability. Additionally, the phase delay of the harmonic is confirmed to play an extremely relevant role in the semiconductors' reliability.

The paper is organized as follows. First, a brief description of the 4-wire inverter is done. Next, the different operation cases analyzed in the paper are presented. The reliability models used for the comparative analysis are presented, and the results are discussed. Next, the cases with harmonic content are analyzed in-depth to understand their differences. Finally, conclusions are drawn.

#### **II. HARDWARE DESCRIPTION**

Fig. 1 shows a simplified diagram of the 4-wire inverter analyzed. The inverter is supplied by an adjustable DC voltage source providing between 680 V and 800 V. The inverter itself consists of a three-branch module of SiC MOSFETs (Wolfspeed CCS050M12CM2 [35]). The DC-link is split into two half-buses. Like this, the midpoint can be accessed to connect the neutral line and easily implement a 4-wire system. The DC-link consists of two capacitors (EPCOS B43564A6278M000 [36]). The capacitors' reliability is not under this paper's scope and is analyzed separately in another paper [37].

The outputs of the semiconductors are connected to an output filter implemented with three inductors. Each phase's current is independently controlled using Fractional Proportional Resonant (FPR) controllers [38].

Fig. 2 shows the inverter with open sides to see the internal elements. On the left, the three inductors of the output filter

#### TABLE 1. Inverter parameters.

| Parameter                                           | Value |

|-----------------------------------------------------|-------|

| Phase nominal apparent power: $S_{ph}$ (kVA)        | 6.0   |

| Phase nominal current: $I_{ph}$ (A <sub>RMS</sub> ) | 26.0  |

| Output current maximum THD (%)                      | 30    |

| DC-link capacitance ( $\mu$ F)                      | 2700  |

| DC-link nominal voltage (V)                         | 800   |

| Grid frequency (Hz)                                 | 50    |

| Grid line voltage (V <sub>RMS</sub> )               | 400   |

can be seen. Next to them is the lower half-bus capacitor. The SiC power module is mounted on a heatsink with forced convection. The fan is mounted under the heatsink and includes an air inlet. Finally, on the right-hand side is mounted the upper half-bus capacitor. For the current application, the converter is mounted rotated 90 degrees on the X-axis shown in Fig. 2. The converter is completely closed on the sides for the platform analyzed, and only an air outlet is left on the left-hand side to let out the hot air. Table 1 summarizes the main parameters of the power converter.

The converter is mounted on a large cabinet with other elements, such as the DC power supply, a low-frequency isolation transformer for the DC power supply, and the necessary switchgear to connect the inverter to the AC grid and the control boards. Because of its size and multiple elements, the cabinet can be modeled as an environment with a constant temperature since its thermal inertia is substantial. For this paper, the cabinet temperature is assumed to be a constant value of 25 °C.

# **III. WORKING CASES**

The effect of current imbalances and harmonic distortion is analyzed separately. The obtained results are compared with a base case to get a good picture of the reliability variation.

The base case selected is the operation of the power converter with a three-phase balanced load and each phase with the nominal active power. Therefore, the active power ( $P_{\text{base}}$ ) is 18 kW.

Three different cases are analyzed to assess the reliability variation with unbalanced loads. One of the phases is operated with 0 current in all of them. The other two phases are operated with the following current and total output power

- a)  $I_{ph}$  and  $0.66P_{base}$

- b)  $1.05I_{\text{ph}}$  and  $0.7P_{\text{base}}$

- c)  $1.20I_{ph}$  and  $0.8P_{base}$

For cases b and c, the converter is operated with a slight current overload in two phases.

Last, four different cases are analyzed to assess the reliability variation with loads with harmonic distortion. The three phases are operated with the nominal balanced current at the fundamental frequency (f). A 30% content of the third harmonic is added in each phase.

- a)  $I_{\text{ph}}$  at f and  $0.3I_{\text{ph}}$  at 3f with phase delay 0 rad.

- b)  $I_{\rm ph}$  at f and  $0.3I_{\rm ph}$  at 3f with phase delay  $\pi/2$  rad.

- c)  $I_{\rm ph}$  at f and  $0.3I_{\rm ph}$  at 3*f* with phase delay  $\pi$  rad.

- d)  $I_{\rm ph}$  at f and 0.3 $I_{\rm ph}$  at 3f with phase delay  $3\pi/2$  rad.

The harmonic distortion added is limited to the third harmonic. As analyzed in [1], the low-frequency harmonics have a higher impact on the semiconductors' thermal load and, consequently, a higher impact on the reliability [39].

The currents and power for all the cases are summarized in Table 2.

All the cases analyzed are not realistic operation profiles for a power converter. Nevertheless, they are helpful in the analysis of the reliability variation.

## **IV. RELIABILITY MODELS**

#### A. SIMULATION MODEL

Simulations are performed with a power electronics simulation software to determine  $T_{jm}$  and  $\Delta T_j$  for each scenario. The power electronics simulation software integrates into one simulation, the electrical simulation, including the control implemented in discrete-time and the thermal simulation.

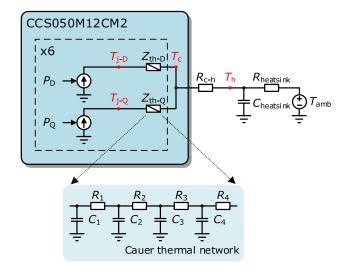

FIGURE 3. Semiconductors thermal network.

The models provided by the manufacturer on their website [40] are used to implement the thermal simulation. The models include look-up tables to determine both switching and conduction losses. The turn-on and turn-off energies are provided at different currents, voltages, and temperatures. The gate resistance is taken into account for calculating the switching losses as well. The voltage drop on the MOSFET is also provided for different currents and temperatures to calculate the conduction losses.

Additionally, the model includes a thermal network of the module. The radiator with forced convection [41] used has been simplified as a thermal resistance,  $R_{\text{heatsink}}$ , 0.103 K · W<sup>-1</sup>, and a thermal capacitance,  $C_{\text{heatsink}}$ , 1.67 kJ · K<sup>-1</sup>. Fig. 3 shows the resulting thermal network. As stated previously, for all the cases analyzed, the ambient temperature ( $T_{\text{amb}}$ ) was set at 25 °C.

The software calculates the losses by interpolating from the temperature, current, and operating voltage.

#### TABLE 2. Electrical parameters of the different cases.

| Case      | I <sub>a-50Hz</sub><br>(A <sub>RMS</sub> ) | I <sub>a</sub><br>(A <sub>RMS</sub> ) | P <sub>a</sub><br>(kW) | I <sub>b-50Hz</sub><br>(A <sub>RMS</sub> ) | I <sub>b</sub><br>(A <sub>RMS</sub> ) | <i>P</i> <sub>b</sub><br>(kW) | I <sub>c-50Hz</sub><br>(A <sub>RMS</sub> ) | I <sub>c</sub><br>(A <sub>RMS</sub> ) | <i>P</i> <sub>c</sub><br>(kW) | 3rd harmonic<br>content (%) | 3rd harmonic<br>phase delay (rad) |

|-----------|--------------------------------------------|---------------------------------------|------------------------|--------------------------------------------|---------------------------------------|-------------------------------|--------------------------------------------|---------------------------------------|-------------------------------|-----------------------------|-----------------------------------|

| 1         | 26.0                                       | 26.0                                  | 6.0                    | 26.0                                       | 26.0                                  | 6.0                           | 26.0                                       | 26.0                                  | 6.0                           | 0                           |                                   |

| 2a        | 26.0                                       | 26.0                                  | 6.0                    | 26.0                                       | 26.0                                  | 6.0                           | 0                                          | 0                                     | 0                             | 0                           |                                   |

| 2b        | 27.3                                       | 27.3                                  | 6.3                    | 27.3                                       | 27.3                                  | 6.3                           | 0                                          | 0                                     | 0                             | 0                           |                                   |

| 2c        | 31.2                                       | 31.2                                  | 7.2                    | 31.2                                       | 31.2                                  | 7.2                           | 0                                          | 0                                     | 0                             | 0                           |                                   |

| 3a        | 26.0                                       | 27.1                                  | 6.0                    | 26.0                                       | 27.1                                  | 6.0                           | 26.0                                       | 27.1                                  | 6.0                           | 30                          | 0                                 |

| 3b        | 26.0                                       | 27.1                                  | 6.0                    | 26.0                                       | 27.1                                  | 6.0                           | 26.0                                       | 27.1                                  | 6.0                           | 30                          | $\pi/2$                           |

| 3c        | 26.0                                       | 27.1                                  | 6.0                    | 26.0                                       | 27.1                                  | 6.0                           | 26.0                                       | 27.1                                  | 6.0                           | 30                          | π                                 |

| <u>3d</u> | 26.0                                       | 27.1                                  | 6.0                    | 26.0                                       | 27.1                                  | 6.0                           | 26.0                                       | 27.1                                  | 6.0                           | 30                          | 3π/2                              |

#### TABLE 3. Simulation results.

| Q1 & Q2 |       |              |                    |             | Q3 & Q4              |              |                    |             | Q5 & Q6              |              |                    |       |                      |

|---------|-------|--------------|--------------------|-------------|----------------------|--------------|--------------------|-------------|----------------------|--------------|--------------------|-------|----------------------|

|         | Th    | $T_{\rm jm}$ | $\Delta T_{\rm j}$ | $I_{\rm B}$ | $N_{ m f}$           | $T_{\rm jm}$ | $\Delta T_{\rm j}$ | $I_{\rm B}$ | $N_{ m f}$           | $T_{\rm jm}$ | $\Delta T_{\rm j}$ | IB    | $N_{ m f}$           |

| Case    | (°C)  | (°C)         | (°C)               | (A)         | (cycles)             | (°C)         | (°C)               | (A)         | (cycles)             | (°C)         | (°C)               | (A)   | (cycles)             |

| 1       | 45.56 | 61.93        | 7.47               | 17.34       | $2.42 \cdot 10^{10}$ | 61.93        | 7.47               | 17.34       | $2.42 \cdot 10^{10}$ | 61.93        | 7.47               | 17.34 | $2.42 \cdot 10^{10}$ |

| 2a      | 40.49 | 55.81        | 7.44               | 17.34       | $2.66 \cdot 10^{10}$ | 55.81        | 7.44               | 17.34       | $2.66 \cdot 10^{10}$ | 46.98        | 0.49               | 1.92  | $2.44 \cdot 10^{16}$ |

| 2b      | 41.12 | 57.09        | 7.82               | 18.20       | $2.03 \cdot 10^{10}$ | 57.09        | 7.82               | 18.20       | $2.03 \cdot 10^{10}$ | 47.73        | 0.49               | 1.92  | $2.42 \cdot 10^{16}$ |

| 2c      | 46.88 | 61.48        | 9.14               | 20.67       | $0.84 \cdot 10^{10}$ | 61.48        | 9.14               | 20.67       | $0.84 \cdot 10^{10}$ | 50.27        | 0.49               | 1.92  | $2.33 \cdot 10^{16}$ |

| 3a      | 45.41 | 61.69        | 8.43               | 18.25       | $1.38 \cdot 10^{10}$ | 61.69        | 8.43               | 18.25       | $1.38 \cdot 10^{10}$ | 61.69        | 8.43               | 18.25 | $1.38 \cdot 10^{10}$ |

| 3b      | 46.58 | 63.75        | 7.58               | 18.08       | $2.17 \cdot 10^{10}$ | 63.75        | 7.58               | 18.08       | $2.17 \cdot 10^{10}$ | 63.75        | 7.58               | 18.08 | $2.17 \cdot 10^{10}$ |

| 3c      | 46.92 | 64.25        | 7.42               | 17.74       | $2.39 \cdot 10^{10}$ | 64.25        | 7.42               | 17.74       | $2.39 \cdot 10^{10}$ | 64.25        | 7.42               | 17.74 | $2.39 \cdot 10^{10}$ |

| 3d      | 46.59 | 63.75        | 8.48               | 18.00       | $1.32 \cdot 10^{10}$ | 63.75        | 8.48               | 18.00       | $1.32 \cdot 10^{10}$ | 63.75        | 8.48               | 18.00 | $1.32 \cdot 10^{10}$ |

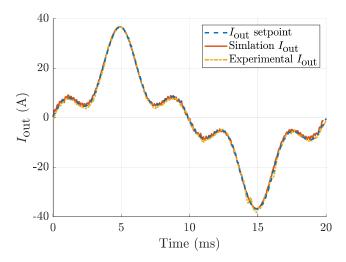

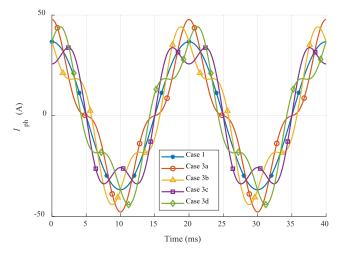

FIGURE 4. Current waveforms comparison between the experimental and the simulation results.

Fig. 4 shows the response of the power converter for an output current ( $I_{out}$ ) setpoint of 15.6 A<sub>RMS</sub> at 50 Hz, 5.2 A<sub>RMS</sub> at 150 Hz, and 5.2 A<sub>RMS</sub> at 250 Hz, marked in blue. In orange is shown the output current calculated with the simulations, and in yellow is shown the output current measured in the experimental setup. The output current is sampled at the converter's switching frequency,  $f_{sw}$ , 30 kHz. For the sake of clarity, only one phase is measured.

The inverter analyzed is a piece of commercial equipment designed bearing in mind its compactness. Consequently, the gate drivers are placed on top of the power module, making it impossible to access the semiconductors to measure their temperature directly. Therefore, it is not possible to

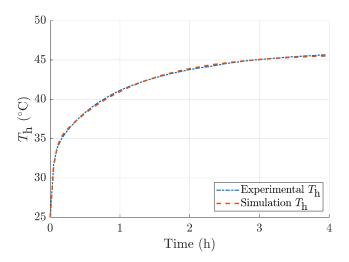

**FIGURE 5.** Experimental setup results. Heatsink temperature measurement operating in case 1 conditions. Refer to Table 2 for cases reference.

validate the simulation results with experimental measurements. Nevertheless, as pointed out before, the goal is to compare different cases without obtaining exact reliability values. Consequently, the simulation results are sufficient for the current analysis.

The simulation results are summarized in Table 3. For each case is provided the heatsink temperature  $(T_h)$ , the average junction temperature  $(T_{jm})$ , the junction temperature swing  $(\Delta T_j)$ , and the bond wire current  $(I_B)$  of each MOSFET and their estimated number of cycles to failure  $(N_f)$ . The MOSFET's labeling is depicted in Fig. 1.

For the unbalanced load cases (2a-2c), the load current on phase c is null. Despite this, the MOSFETs switch, and their

FIGURE 6. Reliability block diagram.

currents are not null due to the current ripple at the high-frequency switching.

Fig. 5 shows, in blue, the experimental setup heatsink temperature ( $T_h$ ) measured with a K-type thermocouple sampled every 5 minutes with a thermocouple data logger. With the power converter operating in case 1 conditions. And, in orange, the heatsink temperature calculated with the simulations. The simulation results match the dynamic response of the experimental setup closely. Moreover, the steady-state experimental heatsink temperature, 45, 78 °C, matches the temperature simulation results closely, Table 3.

#### **B. LIFETIME MODEL**

For the inverter analyzed, a power module based on SiC MOSFETs is used. From the analyses performed by different authors, [42]–[47], it is clear that the number of cycles to failure,  $N_{\rm f}$ , is closely related to the average junction temperature,  $T_{\rm jm}$ , and the junction temperature swing,  $\Delta T_{\rm j}$ .

Considering this, we propose calculating the  $N_{\rm f}$  value with the CIPS2008 model [48]. The CIPS2008 model is based on the model obtained from the LESIT project [49]. The CIPS2008 model calculates  $N_{\rm f}$  based on the average semiconductor temperature ( $T_{\rm jm}$ ) and the temperature swing in a period ( $\Delta T_{\rm j}$ ). Additionally, it considers other parameters such as the power-on-time ( $t_{\rm on}$ ), the current for each bond wire ( $I_{\rm B}$ ), the voltage class of the chip ( $V_{\rm C}$ ), and the diameter of the bond wires ( $D_{\rm B}$ ). The different parameters' effect is adjusted with experimental constants (A and  $\beta_1 - \beta_6$ ). The calculation of the number of cycles to failure is expressed as

$$N_{\rm f} = A \cdot \Delta T_{\rm j}^{\beta_1} \cdot e^{\frac{\beta_2}{T_{\rm jm} + 273.15}} \cdot t_{\rm on}^{\beta_3} \cdot I_{\rm B}^{\beta_4} \cdot V_{\rm C}^{\beta_5} \cdot D_{\rm B}^{\beta_6}.$$

(1)

The authors of the CIPS2008 model developed it as a lifetime model for power modules. Therefore,  $N_f$  is calculated considering the typical failure mechanisms for power modules, such as bond wire liftoff and thermal fatigue of solder joints, [49], which are still present in a SiC MOSFET power module. Consequently, it is suitable for our analysis.

The constants of a lifetime model (A and  $\beta_1-\beta_6$ ) shall be adjusted for every power module. When it comes to a comparative analysis, identifying the model parameters is not crucial. The constants contain the semiconductors' technologic factor, which is irrelevant to performing comparisons among different cases. This paper's scope is to get a series of comparable results to assess the importance of current disturbances in semiconductors' reliability. The interest is not in

| TABLE 4. | Parameters | of the | <b>CIPS2008</b> | lifetime | model. |

|----------|------------|--------|-----------------|----------|--------|

|----------|------------|--------|-----------------|----------|--------|

| Parameter              | Value                |

|------------------------|----------------------|

| A (cycles)             | $2.03 \cdot 10^{14}$ |

| $\beta_1$              | -4.416               |

| $\beta_2$              | 1285                 |

| $\beta_3$              | -0.463               |

| $\beta_4$              | -0.716               |

| $\beta_5$              | -0.761               |

| $\beta_6$              | -0.5                 |

| $t_{\rm on}(s)$        | 10-2                 |

| $V_{\rm C}$            | 12                   |

| $D_{\rm B}(\mu{ m m})$ | 380                  |

|                        | ÷                    |

the exact  $N_{\rm f}$  value for each case, but  $N_{\rm f}$ 's variations depending on the case analyzed. The same approach is followed in other comparative reliability analyses [33], [34].

The parameters used in (1) are summarized in Table 4 and were extracted from [50], or they can be obtained from the manufacturer's datasheet [35].

The diameter of the bond wires was obtained by performing direct microscopic measurements on a module. The number of bond wires in parallel is three. For the case under study,  $t_{on}$  is 10 ms. It corresponds to half period of the grid. The  $t_{on}$ ,  $V_C$ , and  $D_B$  parameters are constant for the four cases analyzed.  $I_B$  is dependent on the case and phase analyzed. The MOSFET RMS current for each case is determined with the help of simulations.

The semiconductors module includes a freewheeling SiC Schottky diode [51] in parallel with the MOSFETs' body diode. This diode is usually no longer included because the body diode provides a good enough switching performance.

Additionally, the MOSFETs can drive current in both directions. In the studied module, when the current flows from source to drain, it is shared between the MOSFET, the body diode, and the external freewheeling diode. Therefore, the current flowing through the freewheeling diode is low, and consequently, its thermal load is low [1]. Notably, the temperature swing,  $\Delta T_j$ , is low. From (1), it can be deduced that a low  $\Delta T_j$  leads to an unrealistic  $N_f$  estimation,

$$\lim_{\Delta T_{j} \to 0} N_{f} = \infty, \tag{2}$$

for this reason, these diodes are excluded from the study.

It is worth noting that, according to (1), we expect a decrease in the number of cycles to failure with  $T_{jm}$ , which increases with  $T_{amb}$ . However, in this paper, the ambient temperature was held constant.

TABLE 5. Semiconductors' reliability function parameters.

|      | Q1 t      | o Q4 | Q5 & Q6   |      |  |  |

|------|-----------|------|-----------|------|--|--|

| Case | η [years] | β    | η [years] | β    |  |  |

| 1    | 16.83     | 5.56 | 16.83     | 5.56 |  |  |

| 2a   | 18.44     | 5.57 | >1000     | 8.61 |  |  |

| 2b   | 14.13     | 5.48 | >1000     | 8.60 |  |  |

| 2c   | 6.17      | 5.22 | >1000     | 8.67 |  |  |

| 3a   | 9.60      | 5.36 | 9.60      | 5.36 |  |  |

| 3b   | 15.01     | 5.55 | 15.01     | 5.55 |  |  |

| 3c   | 16.61     | 5.57 | 16.61     | 5.57 |  |  |

| 3d   | 9.22      | 5.36 | 9.22      | 5.36 |  |  |

# **V. DISCUSSION**

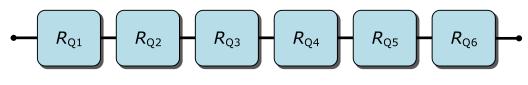

A reliability block diagram (RBD) has been chosen to model the system-level reliability. This approach is the most appropriate since the system does not have redundancies [52]. Failure of a single semiconductor would cause a system failure. Fig. 6 shows the RBD used for the reliability analysis.

The system reliability function  $(R_{sys})$  can be determined from the MOSFETs reliability function  $(R_{Qi})$  as

$$R_{\rm sys} = \prod R_{\rm Qi}, \qquad (3)$$

with  $i = 1 \dots 6$ .

A computational software was used to implement Monte Carlo simulations to obtain the reliability functions of each MOSFET considering variability in the parameters of (1). One hundred thousand simulations have been performed for each case to obtain the probabilistic distribution of the estimated lifetime ( $N_{\rm f}$ ) of each MOSFET.

Typically, semiconductors fail because of wearout mechanisms. Mostly, bond wire liftoff or substrate delamination, which are accelerated over time [39].

Consequently, it has been considered that the probabilistic distributions follow a two-parameter Weibull distribution. Therefore, their probability density function (pdf) can be expressed as

$$f(t) = \frac{\beta}{\eta^{\beta}} \cdot t^{\beta-1} \cdot e^{-\left(\frac{t}{\eta}\right)^{\beta}},\tag{4}$$

being  $\eta$  the scale parameter and  $\beta$  the shape parameter of the Weibull distribution.

It has been considered for (1) that the parameters A,  $\Delta T_j$ ,  $\beta_1$ ,  $\beta_2$ ,  $\beta_4$ , and  $T_{jm}$  follow a normal distribution with the mean value ( $\mu$ ) described in Table 3 and Table 4 and a standard deviation ( $\sigma$ ) such that  $3\sigma$  is equivalent to 5% of the average value.

From the pdf, the reliability function (R(t)) can be obtained from the cumulative distribution function (cdf)(F(t)), leaving the expression as

$$R(t) = 1 - F(t) = 1 - \int_0^t f(t) dt = e^{-\left(\frac{t}{\eta}\right)^{\beta}}.$$

(5)

Table 5 summarizes the values of the MOSFET's reliability functions for the different cases analyzed.

The results shown in Table 5 already offer some interesting results. The scale parameter  $(\eta)$  for the different MOSFETs

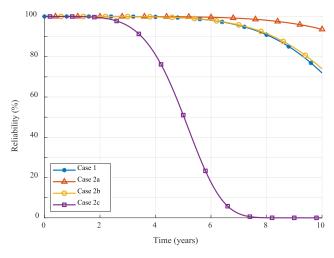

FIGURE 7. Reliability comparison with the presence of unbalanced loads. Cases 1 and 2a to 2c. Refer to Table 2 for cases reference.

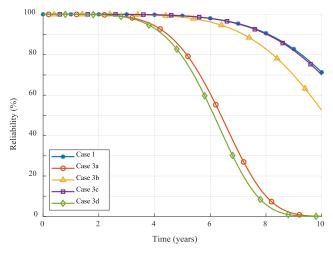

FIGURE 8. Reliability comparison with the presence of harmonic distortion. Cases 1 and 3a to 3d. Refer to Table 2 for cases reference.

is similar except for the MOSFETs with a 0 load current, cases 2a to 2c. Nevertheless, the addition of harmonic content can reduce it by more than 40%, case 3d. Moreover, the unbalanced operation can reduce it even further, more than 60%, case 2c.

With these values, the reliability curves have been obtained. Fig. 7 shows a comparison of the power converter reliability with unbalanced loads. Fig. 8 compares the power converter reliability with distorted harmonic loads.

Table 6 summarizes the  $B_{10}$  value, i.e., the point in which 10% of the samples have failed, for each case.

From Fig. 7 and Table 6, we can conclude that unbalanced loads affect the system's reliability. If the legs' current does not exceed the nominal value, 2a, the reliability is increased. However, if the phase current is increased to partially compensate for the power reduction, 2b, and 2c, the reliability can rapidly decrease. For case 2b, we can see that despite the total output power being only 70% of the nominal power, the

**TABLE 6.** *B*<sub>10</sub> value for each case.

| Case | B <sub>10</sub> [years] |

|------|-------------------------|

| 1    | 8.1                     |

| 2a   | 10.8                    |

| 2b   | 8.2                     |

| 2c   | 3.5                     |

| 3a   | 4.5                     |

| 3b   | 7.2                     |

| 3c   | 8.0                     |

| 3d   | 4.3                     |

$B_{10}$  value is almost the same as the base case. For case 2c, with a total output power of 80% of the nominal power, the  $B_{10}$  value has substantially decreased by almost 60%.

From Fig. 8 and Table 6, we can conclude that harmonic distortion can also reduce the system's reliability. Case 3d has a  $B_{10}$  value almost 50% smaller than the base case. On the contrary, case 3c shows similar reliability. It can be seen that the phase delay of the harmonic current plays a highly relevant role. Therefore, harmonic distortion must be analyzed carefully and cannot be limited to the RMS value. The shape of the current is relevant.

Consequently, for power converters used in applications prone to the appearance of these disturbances, microgrids [7], [8], [10]–[12], PFCs [13], [14] or active filters [15]–[18], the reliability analysis has to take into account the appearance of these disturbances. Omitting them from the analysis can lead to wrong estimations of the system's reliability.

FIGURE 9. Phase current for cases 1 and 3a to 3d. Refer to Table 2 for cases reference.

## **VI. HARMONIC DISTORTION ANALYSIS**

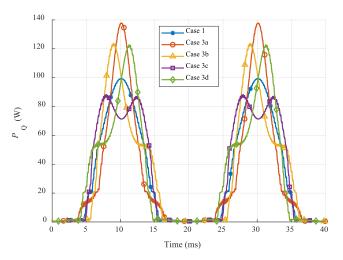

The results obtained for the cases with harmonic distortion, 3a to 3d, are counter-intuitive. One could expect a more significant reliability reduction with the cases with a higher peak current. However, it is not like this.

Fig. 9 shows the output currents for cases 1 and 3a to 3d. As it can be seen, the larger peak current corresponds to case 3a; however, the reliability reduction is higher for case 3d, which has a lower peak current. Additionally, cases

FIGURE 10. MOSFET junction temperature for cases 1 and 3a to 3d. Refer to Table 2 for cases reference.

3b and 3d have the same peak current but highly different  $B_{10}$  values.

The results in Table 3 help to explain the significant differences. Among cases 1 and 3a to 3d, the only parameters of (1) that change are  $T_{\text{im}}$ ,  $\Delta T_{\text{j}}$ , and  $I_{\text{B}}$ .

The parameter that is causing the most significant  $N_{\rm f}$  variations is  $\Delta T_{\rm j}$ . The variation of  $T_{\rm jm}$  is always lower than 4%, and the effect on the exponential term of (1) is low, less than 3%. The maximum  $\Delta T_{\rm j}$  variation is a 13.5% increase between case 1 and case 3d, and the parameter  $\beta_1$  is substantially bigger than the other exponential coefficients ( $\beta_3$  to  $\beta_6$ ). Consequently, the main drive for the  $N_{\rm f}$  variation is  $\Delta T_{\rm j}$ .

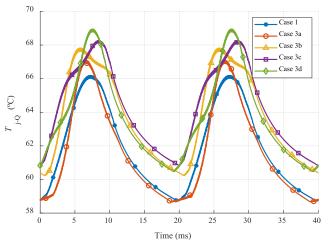

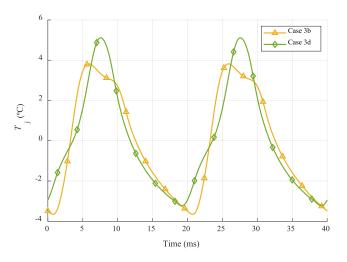

Consequently, the  $\Delta T_j$  variation caused by the harmonic content addition is the root of the reliability variation. Fig. 10 shows the junction temperature of the MOSFETs for cases 1 and 3a to 3d. As expected from the values shown in Table 3, the mean junction temperature is similar in all the cases, but the temperature swing varies.

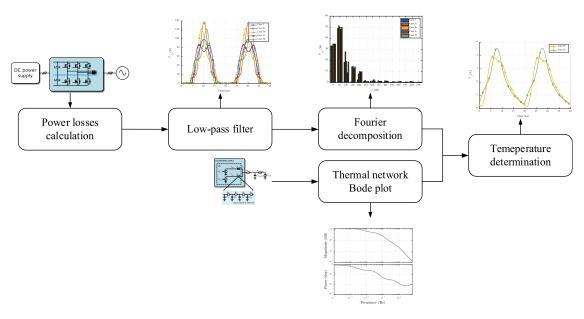

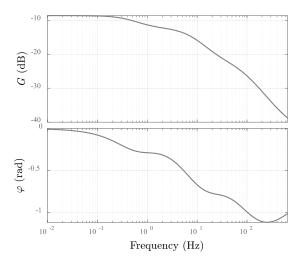

Fig. 11 summarizes the procedure followed to analyze the difference in the temperature swing among the different cases. First, with the help of a power electronics simulation software, PLECS, the MOSFET power losses are calculated. Next, with the help of a computational software, MATLAB, the power losses are low-pass filtered to eliminate the components at frequencies equal or greater than the switching frequency. Using the Fourier transform, the power losses are decomposed into fundamental (50 Hz) and its harmonics. Finally, with each harmonic's magnitude ( $\alpha_k$ ) and argument ( $\phi_k$ ), the effect in  $\Delta T_j$  amplitude and shape of the MOSFET thermal network is analyzed.

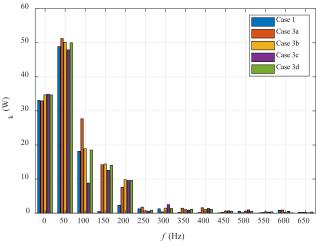

Fig. 12 shows the filtered power losses for cases 1 and 3a to 3d. Fig. 13 shows each harmonic's magnitude. The power losses at frequencies greater than 0 Hz contribute to the temperature swing.

These two figures provide relevant information. First, it can be seen that, as expected, case 3a shows a higher peak in the power losses than the other cases. The power losses at

FIGURE 11. Methodology followed for the temperature swing analysis.

**FIGURE 12.** MOSFET power losses for cases 1 and 3a to 3d. Refer to Table 2 for cases reference.

frequencies greater than 0 Hz are the highest among all the cases. Despite this, the temperature swing is not the biggest.

Additionally, the power losses between cases 3b and 3d are similar in shape. Furthermore, their Fourier decompositions have similar magnitude ( $\alpha_k$ ) values, as shown in Fig. 13. Nevertheless, their temperature swing and reliability differ substantially.

The key point is the thermal network's frequency response and its interaction with the power losses argument ( $\phi_k$ ) for each harmonic. Fig. 14 shows the MOSFET's thermal network bode diagram. The transfer function of the thermal network is a complex equation that can be calculated following the detailed approach proposed in [53],

$$Z_{i}(s) = \frac{1}{\frac{1}{Z_{i+1} + R_{i}} + C_{i}s},$$

(6)

FIGURE 13. Magnitude ( $\alpha_k$ ) of the MOSFET power losses Fourier decomposition for cases 1 and 3a to 3d. Refer to Table 2 for cases reference.

being  $C_i$  and  $R_i$  the thermal capacitance and resistance of the different layers, see Fig. 3.

With the thermal network gain ( $G_k$ ) and phase ( $\varphi_k$ ) for each harmonic obtained from Fig. 14 together with the power losses Fourier decomposition coefficients ( $\alpha_k$ ,  $\phi_k$ ), it is possible to calculate the temperature swing as the superposition of multiple sinusoidal waveforms,

$$\Delta T_{j}(t) = \sum_{k=1}^{13} G_{k} \cdot \alpha_{k} \cdot \cos\left(2\pi kft + \varphi_{k} + \phi_{k}\right).$$

(7)

Fig. 15 shows the  $\Delta T_j$  calculated with this methodology for cases 3b and 3d. As it can be seen, it matches the simulation results as expected. It confirms that 2 cases with similar power dissipation in absolute values can have different temperature swings. The phase delay of the harmonic decomposition is crucial regarding the junction temperature swing.

FIGURE 14. MOSFET thermal network bode diagram.

**FIGURE 15.** MOSFET junction temperature for cases 3b and 3d, calculated following the methodology proposed in Fig. 11. Refer to Table 2 for cases reference.

#### **VII. CONCLUSION**

This paper proposes a comparative methodology to assess the impact of current imbalances and harmonic distortion on the semiconductor's reliability. The analysis has been done using a three-phase four-wire inverter. Still, the results can be extrapolated to other topologies.

In the paper, we have proved that the presence of unbalanced loads substantially distorts the reliability of the semiconductors, especially if some phases are overloaded to compensate for the loss of power in other phases.

The paper demonstrates that overloading more than 5% two phases while the third one operates with 0 current is harmful to the semiconductor's reliability. A 20% overload in two phases with the third phase operating with 0 current implies a 57% reduction in reliability compared with a balanced load.

Furthermore, we proved that harmonic content in the load current substantially decreases the semiconductor's reliability.

A 30% of third harmonic content in the load current can reduce the semiconductor's reliability to half compared with a load without harmonic content.

Finally, the analysis shows that the harmonic content's phase delay is crucial in determining the semiconductor's reliability. Cases 3b and 3d have the same harmonic content but different phase delays,  $\pi/2$  and  $3\pi/2$ . Both cases show similar peak current and similar power losses in magnitude. However, the different shape in the MOSFET power losses results in a different junction temperature swing and a substantially different semiconductor's reliability. Case 3d shows a *B*10 value 40% lower than case 3b.

For all the reasons mentioned above, the reliability analyses of power converters for microgrids, PFCs, UPS, or active filters should not overlook these disturbances.

#### REFERENCES

- [1] T. Lledo-Ponsati, A. S. Bahman, F. Iannuzzo, D. Montesinos-Miracle, and S. G. Arellano, "Reliability analysis of a 3-leg 4-wire inverter under unbalanced loads and harmonic injection," in *Proc. 20th Workshop Control Modeling Power Electron. (COMPEL)*, Jun. 2019, pp. 1–8.

- [2] C. Burgos-Mellado, J. J. Llanos, R. Cardenas, D. Saez, D. E. Olivares, M. Sumner, and A. Costabeber, "Distributed control strategy based on a consensus algorithm and on the conservative power theory for imbalance and harmonic sharing in 4-wire microgrids," *IEEE Trans. Smart Grid*, vol. 11, no. 2, pp. 1604–1619, Mar. 2020.

- [3] J. W. Kolar and T. Friedli, "The essence of three-phase PFC rectifier systems—Part I," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 176–198, Jan. 2013.

- [4] G. Escobar, P. Mattavelli, A. M. Stanković, A. A. Valdez, and J. Leyva-Ramos, "An adaptive control for UPS to compensate unbalance and harmonic distortion using a combined capacitor/load current sensing," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 839–847, Apr. 2007.

- [5] O. Vodyakho and C. C. Mi, "Three-level inverter-based shunt active power filter in three-phase three-wire and four-wire systems," *IEEE Trans. Power Electron.*, vol. 24, no. 5, pp. 1350–1363, May 2009.

- [6] E. Ghosh, A. Mollaeian, W. Hu, and N. C. Kar, "A novel control strategy for online harmonic compensation in parametrically unbalanced induction motor," *IEEE Trans. Magn.*, vol. 52, no. 7, pp. 7–10, Jun. 2016.

- [7] F. Gothner, O.-M. Midtgard, R. Torres-Olguin, and J. Roldan-Perez, "Virtual impedance design for power quality and harmonic sharing improvement in microgrids," in *Proc. 20th Workshop Control Modeling Power Electron. (COMPEL)*, Jun. 2019, pp. 1–7.

- [8] J. Zhou, S. Kim, H. Zhang, Q. Sun, and R. Han, "Consensus-based distributed control for accurate reactive, harmonic, and imbalance power sharing in microgrids," *IEEE Trans. Smart Grid*, vol. 9, no. 4, pp. 2453–2467, Jul. 2018.

- [9] D. De and V. Ramanarayanan, "Decentralized parallel operation of inverters sharing unbalanced and nonlinear loads," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 3015–3025, Dec. 2010.

- [10] F. Shahnia, R. Majumder, A. Ghosh, G. Ledwich, and F. Zare, "Operation and control of a hybrid microgrid containing unbalanced and nonlinear loads," *Electr. Power Syst. Res.*, vol. 80, no. 8, pp. 954–965, Aug. 2010.

- [11] D. Heredero-Peris, C. Chillón-Antón, M. Pagès-Giménez, G. Gross, and D. Montesinos-Miracle, "Implementation of grid-connected to/from offgrid transference for micro-grid inverters," in *Proc. 39th Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Nov. 2013, pp. 840–845.

- [12] W. Du, Q. Jiang, M. J. Erickson, and R. H. Lasseter, "Voltage-source control of PV inverter in a CERTS microgrid," *IEEE Trans. Power Del.*, vol. 29, no. 4, pp. 1726–1734, Aug. 2014.

- [13] X. Guo, H.-P. Ren, and J. Li, "Robust model-predictive control for a compound active-clamp three-phase soft-switching PFC converter under unbalanced grid condition," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 2156–2166, Mar. 2018.

- [14] M. A. Santoyo-Anaya, N. M. Salgado-Herrera, J. R. Rodriguez-Rodriguez, L. M. Castro, E. L. Moreno-Goytia, and V. Venegas-Rebollar, "New phasorial oriented single-PI loop control for industrial VSC-PFC rectifiers operating under unbalanced conditions," *IET Power Electron.*, vol. 13, no. 4, pp. 844–853, 2020.

- [15] H. Akagi, "New trends in active filters for power conditioning," *IEEE Trans. Ind. Appl.*, vol. 32, no. 6, pp. 1312–1322, Nov./Dec. 1996.

- [16] M. El-Habrouk, M. K. Darwish, and P. Mehta, "Active power filters: A review," *IEE Proc., Electr. Power Appl.*, vol. 147, no. 5, pp. 403–413, Sep. 2000.

- [17] C. A. Quinn and N. Mohan, "Active filtering of harmonic currents in threephase, four-wire systems with three-phase and single-phase nonlinear loads," in *Proc. 7th Annu. Appl. Power Electron. Conf. Expo. (APEC)*, 1992, pp. 829–836.

- [18] J. Crepaldi, M. M. Amoroso, and O. H. Ando, "Analysis of the topologies of power filters applied in distributed generation units—Review," *IEEE Latin Amer. Trans.*, vol. 16, no. 7, pp. 1892–1897, Jul. 2018.

- [19] A. Anurag, Y. Yang, and F. Blaabirg, "Thermal performance and reliability analysis of single-phase PV inverters with reactive power injection outside feed-in operating hours," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 3, no. 4, pp. 870–880, Dec. 2015.

- [20] H. Wang, P. Davari, H. Wang, D. Kumar, F. Zare, and F. Blaabjerg, "Lifetime estimation of DC-link capacitors in adjustable speed drives under grid voltage unbalances," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4064–4078, May 2019.

- [21] Y. Yang, H. Wang, F. Blaabjerg, and K. Ma, "Mission profile based multidisciplinary analysis of power modules in single-phase transformerless photovoltaic inverters," in *Proc. 15th Eur. Conf. Power Electron. Appl.* (*EPE*), Sep. 2013, pp. 1–10.

- [22] Y. Yang, K. Ma, H. Wang, and F. Blaabjerg, "Mission profile translation to capacitor stresses in grid-connected photovoltaic systems," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2014, pp. 5479–5486.

- [23] E. Koutroulis and F. Blaabjerg, "Design optimization of transformerless grid-connected PV inverters including reliability," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 325–335, Jan. 2013.

- [24] K. Gulez, A. A. Adam, and H. Pastaci, "A novel direct torque control algorithm for IPMSM with minimum harmonics and torque ripples," *IEEE/ASME Trans. Mechatronics*, vol. 12, no. 2, pp. 223–227, Apr. 2007.

- IEEE/ASME Trans. Mechatronics, vol. 12, no. 2, pp. 223–227, Apr. 2007.

Y. Hu, Z. Q. Zhu, and K. Liu, "Current control for dual three-phase permanent magnet synchronous motors accounting for current unbalance and harmonics," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 2, pp. 272–284, Jun. 2014.

- [26] G. Schoonhoven and M. N. Uddin, "Harmonic injection-based adaptive control of IPMSM motor drive for reduced motor current THD," *IEEE Trans. Ind. Appl.*, vol. 53, no. 1, pp. 483–491, Jan./Feb. 2017.

- [27] A. G. Yepes, J. Doval-Gandoy, F. Baneira, D. Perez-Estevez, and O. Lopez, "Current harmonic compensation for *n*-phase machines with asymmetrical winding arrangement and different neutral configurations," *IEEE Trans. Ind. Appl.*, vol. 53, no. 6, pp. 5426–5439, Nov./Dec. 2017.

- [28] K. Abe, H. Haga, K. Ohishi, and Y. Yokokura, "Fine current harmonics reduction method for electrolytic capacitor-less and inductor-less inverter based on motor torque control and fast voltage feedforward control for IPMSM," *IEEE Trans. Ind. Electron.*, vol. 64, no. 2, pp. 1071–1080, Feb. 2017.

- [29] K. Ma, M. Liserre, F. Blaabjerg, and T. Kerekes, "Thermal loading and lifetime estimation for power device considering mission profiles in wind power converter," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 590–602, Feb. 2015.

- [30] D. C. Hanselman, Brushless Permanent Magnet Motor Design, 2nd ed. Madison, Wisconsin, WI, USA: Magna Physics Publishing, 2003.

- [31] D. C. Hanselman, Brushless Permanent-Magnet Motor Design. New York, NY, USA: McGraw-Hill, 1994.

- [32] R. Burgos, G. Chen, F. Wang, D. Boroyevich, W. G. Odendaal, and J. D. Van Wyk, "Reliability-oriented design of three-phase power converters for aircraft applications," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 48, no. 2, pp. 1249–1263, Apr. 2012.

- [33] L. G. Reddy, L. M. Tolbert, B. Ozpineci, Y. Xu, and D. T. Rizy, "Reliability of IGBT in a STATCOM for harmonic compensation and power factor correction," in *Proc. 27th Annu. IEEE Appl. Power Electron. Conf. Expo.* (APEC), Feb. 2012, pp. 783–788.

- [34] P. Liu, J. Xu, Y. Yang, H. Wang, and F. Blaabjerg, "Impact of modulation strategies on the reliability and harmonics of impedance-source inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 4, pp. 3968–3981, Dec. 2020.

- [35] Cree. (2018). CCS050M12CM2 1.2kV, 25 mΩ All-Silicon Carbide Six-Pack (Three Phase) Module. Accessed: Apr. 9, 2020. [Online]. Available: https://www.wolfspeed.com/downloads/dl/file/id/189/product/104/ ccs050m12cm2.pdf

- [36] EPCOS AG. (2012). Aluminum Electrolytic Capacitors—Capacitors With Screw Terminals B43564, B43584. Accessed: Apr. 21, 2020. [Online]. Available: https://www.mouser.es/datasheet/2/400/epcos\_15-1206947.pdf

- [37] T. Lledó-Ponsati, A. S. Bahman, F. Iannuzzo, D. Montesinos-Miracle, and S. Galceran-Arellano, "Thermal modeling of large electrolytic capacitors using FEM and considering the internal geometry," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 5, pp. 6315–6328, Oct. 2021.

- [38] D. Heredero-Peris, C. Chillón-Antón, E. Sánchez-Sánchez, and D. Montesinos-Miracle, "Fractional proportional-resonant current controllers for voltage source converters," *Electr. Power Syst. Res.*, vol. 168, pp. 20–45, Sep. 2019.

- [39] H. S.-H. Chung, H. Wang, F. Blaabjerg, and M. Pecht, *Reliability of Power Electronic Converter Systems*. Herts, U.K.: The Institution of Engineering and Technology, 2016.

- [40] Wolfspeed. Wolfspeed PLECS and LTspice Models. Accessed: Apr. 9, 2020. [Online]. Available: https://go.wolfspeed.com/all-models

- [41] Cool Innovations. 3-505025M Heatsink Datasheet. Accessed: Apr. 17, 2020. [Online]. Available: https://www.coolinnovations.com/ technology/pin-fin-heat-sinks/

- [42] A. S. Bahman, F. Iannuzzo, and F. Blaabjerg, "Mission-profile-based stress analysis of bond-wires in SiC power modules," *Microelectron. Rel.*, vol. 64, pp. 419–424, Sep. 2016.

- [43] H. Luo, N. Baker, F. Iannuzzo, and F. Blaabjerg, "Die degradation effect on aging rate in accelerated cycling tests of SiC power MOSFET modules," *Microelectron. Rel.*, vol.s. 76–77, pp. 415–419, Sep. 2017.

- [44] H. Luo, F. Iannuzzo, F. Blaabjerg, M. Turnaturi, and E. Mattiuzzo, "Aging precursors and degradation effects of SiC-MOSFET modules under highly accelerated power cycling conditions," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Oct. 2017, pp. 2506–2511.

- [45] C. Herold, M. Schäfer, F. Sauerland, T. Poller, J. Lutz, and O. Schilling, "Power cycling capability of Modules with SiC-diodes," in *Proc. 8th Int. Conf. Integr. Power Syst. (CIPS)*, 2014, pp. 25–27.

- [46] B. Hu, J. O. Gonzalez, L. Ran, H. Ren, Z. Zeng, W. Lai, B. Gao, O. Alatise, H. Lu, C. Bailey, and P. Mawby, "Failure and reliability analysis of a SiC power module based on stress comparison to a Si device," *IEEE Trans. Device Mater. Rel.*, vol. 17, no. 4, pp. 727–737, Dec. 2017.

- [47] M. Akbari, A. S. Bahman, P. D. Reigosa, F. Iannuzzo, and M. T. Bina, "Thermal modeling of wire-bonded power modules considering nonuniform temperature and electric current interactions," *Microelectron. Rel.*, vol.s. 88–90, pp. 1135–1140, Sep. 2018.

- [48] R. Bayerer, T. Herrmann, T. Licht, J. Lutz, and M. Feller, "Model for power cycling lifetime of IGBT modules—Various factors influencing lifetime," in *Proc. 5th Int. Conf. Integr. Power Electron. Syst.*, 2008, pp. 1–6.

- [49] M. Held, P. Jacob, G. Nicoletti, P. Scacco, and M.-H. Poech, "Fast power cycling test of IGBT modules in traction application," in *Proc. 2nd Int. Conf. Power Electron. Drive Syst.*, 1997, pp. 425–430.

- [50] A. Wintrich, U. Nicolai, W. Tursky, and T. Reimann, *Application Manual Power Semiconductors*, 2nd ed. Ilmenau, Germany: ISLE Verlag, 2015.

- [51] Cree. (2014). CPW5-1200-Z050B Silicon Carbide Schottky Diode Chip Z-REC. Accessed: Apr. 9, 2020. [Online]. Available: https://www. wolfspeed.com/downloads/dl/file/id/27/product/38/cpw5\_1200\_z050b.pdf

- [52] H. Guo and X. Yang, "A simple reliability block diagram method for safety integrity verification," *Rel. Eng. Syst. Saf.*, vol. 92, no. 9, pp. 1267–1273, Sep. 2007.

- [53] K. Ma, N. He, M. Liserre, and F. Blaabjerg, "Frequency-domain thermal modeling and characterization of power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 7183–7193, Oct. 2016.

**TOMÀS LLEDÓ-PONSATI** (Graduate Student Member, IEEE) was born in Barcelona, Spain, in 1990. He received the M.Sc. degree in industrial engineering from the Technical University of Catalunya (UPC), in 2013. He is currently pursuing the Ph.D. degree. After graduating, he worked with teknoCEA, developing power converters. In 2018, he joined CITCEA-UPC to work on research projects related to power electronics. His main research interests include power converters

based on wide-bandgap semiconductors and reliability analysis.

AMIR SAJJAD BAHMAN (Senior Member, IEEE) received the B.Sc. degree from the Iran University of Science and Technology, in 2008, the M.Sc. degree from the Chalmers University of Technology, Sweden, in 2011, and the Ph.D. degree from Aalborg University, Denmark, in 2015, all in electrical engineering. He was a Visiting Scholar with the Department of Electrical Engineering, University of Arkansas, USA, in 2014. Moreover, he was with Danfoss Silicon

Power, Germany, in 2014, as a Thermal Design Engineer. He is currently an Associate Professor with the Center of Reliable Power Electronics (CORPE), Aalborg University. His research interests include electro-thermomechanical modeling, packaging, and reliability of power electronic systems and components. He also serves as an Associate Editor for the IEEE TRANSACTIONS ON TRANSPORTATION ELECTRIFICATION and *Microelectronics Reliability* (Elsevier).

**DANIEL MONTESINOS-MIRACLE** (Senior Member, IEEE) was born in Barcelona, Spain, in 1975. He received the M.Sc. degree in electrical engineering from the School of Industrial Engineering of Barcelona (ETSEIB), Technical University of Catalonia (UPC), Barcelona, in 2000, and the Ph.D. degree from UPC, in 2008. In 2001, he joined Salicru Electronics, S.A., Santa Maria de Palautordera, Spain, as a Research and Development Engineer. Since 2001, he has been involved

at the Centre of Technological Innovation in Static Converters and Drives (CITCEA-UPC), as a Research Collaborator. In 2005, he became a Lecturer with the Electrical Engineering Department, UPC, where he has been an Associate Professor, since 2012. In 2016, he became the CITCEA-UPC Director. In 2012, he co-founded teknoCEA, a spin-off company providing components, systems, and power electronics research and manufacturing services. His primary research interests include power electronics, drives, and green energy converters.

**FRANCESCO IANNUZZO** (Senior Member, IEEE) is currently a Professor with Aalborg University, Denmark, where he is also a part of the Center of Reliable Power Electronics (CORPE). He is the author or coauthor of more than 250 publications on journals and international conferences, three book chapters, and four patents. His research interests include reliability of power devices, including mission-profile-based life estimation, condition monitoring, failure modeling,

and testing up to MW-scale modules under extreme conditions, like overvoltage, overcurrent, overtemperature, and short circuits. He has edited the recently-published *Modern Power Electronic Devices: Physics, Applications, and Reliability* book. Besides publication activity, over the past years, he has been invited for several technical seminars about reliability at first conferences as ISPSD, EPE, ECCE, PCIM, and APEC. He is also the Founder of the newborn *Power Electronic Devices and Components* journal (Elsevier) and serves as an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, and *Microelectronics Reliability* (Elsevier). He is also the Vice-President of the IEEE IAS Power Electronic Devices and Components Committee. He was the General Chair of ESREF 2018 and the 29th European Symposium on Reliability of Electron Devices, Failure Physics, and Analysis, and has been appointed as the EPE-ECCE Europe General Chair in 2023.

**SAMUEL GALCERAN-ARELLANO** was born in Lleida, Spain, in 1971. He received the M.Sc. degree in electrical engineering and the Ph.D. degree from the Polytechnic University of Catalonia (UPC), Barcelona, Spain, in 1997 and 2002, respectively. In 1997, he joined the Electrical Engineering Department, UPC, as an Assistant Professor, where he has been the Head, since 2014. He developed several projects for industry, and in 2001, he joined the Center of Technological

Innovation in Static Converters and Drives (CITCEA-UPC), UPC, where he belongs to the CITCEA-UPC Directorate Staff. His primary research interests include motor control and converters for power supplies and drives.