Aalborg Universitet

# A New Hybrid Zeta-Boost Converter with Active Quad Switched Inductor for High Voltage Gain

Bhaskar, M. S.; Gupta, Nikita; Selvam, Sivakumar; Almakhles, Dhafer J.; Sanjeevikumar, P.; Ali, Jagabar Sathik Mohamed; Umashankar, S.

Published in: **IEEE** Access

DOI (link to publication from Publisher): 10.1109/ACCESS.2021.3054393

Creative Commons License CC BY 4.0

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Bhaskar, M. S., Gupta, N., Selvam, S., Almakhles, D. J., Sanjeevikumar, P., Ali, J. S. M., & Umashankar, S. (2021). A New Hybrid Zeta-Boost Converter with Active Quad Switched Inductor for High Voltage Gain. *IEEE* Access, 9, 20022-20034. Article 9335588. https://doi.org/10.1109/ACCESS.2021.3054393

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Received January 1, 2021, accepted January 15, 2021, date of publication January 25, 2021, date of current version February 4, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3054393

# A New Hybrid Zeta-Boost Converter With Active Quad Switched Inductor for High Voltage Gain

M. S. BHASKAR<sup>®1</sup>, (Senior Member, IEEE), NIKITA GUPTA<sup>®2</sup>, (Member, IEEE), SIVAKUMAR SELVAM<sup>®1</sup>, (Member, IEEE), DHAFER J. ALMAKHLES<sup>®1</sup>, (Senior Member, IEEE), P. SANJEEVIKUMAR<sup>®3</sup>, (Senior Member, IEEE), JAGABAR SATHIK MOHAMED ALI<sup>®1</sup>, (Senior Member, IEEE),

AND S. UMASHANKAR<sup>®1</sup>, (Senior Member, IEEE)

<sup>1</sup>Renewable Energy Laboratory, Department of Communications and Networks Engineering, College of Engineering, Prince Sultan University, Riyadh 11586, Saudi Arabia

<sup>2</sup>Department Electrical Engineering, University Institute of Technology, Himachal Pradesh University, Shimla 171005, India

<sup>3</sup>Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark

Corresponding author: Nikita Gupta (guptanikita08@gmail.com)

This work was supported by the Renewable Energy Laboratory (REL), Department of Communications and Network Engineering, College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia.

**ABSTRACT** For renewable sources application like smart grids, microgrids, etc. high voltage gain converter becomes a fundamental unit. In this article, a new hybrid circuit of zeta and boost converter based on active-quad-switched-inductor (AQSL) is proposed. The discontinuous input current in classical zeta circuit determines the less consumption of input source. However, the proposed hybrid zeta-boost converter provides a higher voltage gain with continuous input and output currents. It achieves higher voltage gain devoid of the high-frequency transformer, and multiple stages of diode and capacitor circuit. The mode of operation, boundary region, and non-ideal model of the proposed converter are presented. Design consideration and a comparison study with recent circuits are provided. The design circuitry of the proposed converter investigated and the functionality of the suggested circuit is validated.

**INDEX TERMS** Active-quad-switched-inductor, boost circuit, high voltage gain, hybrid configuration, zeta circuit.

# I. INTRODUCTION

Nowadays, DC-DC converter circuits are gaining more popularity in the renewable energy system [1]; since the basic boost converter circuits does not provide expected characteristics in terms of voltage gain [2]. Conventional converters appear inappropriate for high voltage gain applications as an increment in duty ratio leads to the degradation in performance of converter in the form of rising conduction losses, decimating the voltage gain and its performance. The high voltage across switches that causes the need for high rating switches, further increasing the power losses [3]. Isolated DC-DC converters introduced to overcome these disadvantages of conventional converters for delivering high output voltage [4]. Nonetheless, high voltage spike causes the use of energy recycle techniques, non-dissipative snubber circuit, high-frequency transformer, and clamping techniques

The associate editor coordinating the review of this manuscript and approving it for publication was Ramazan Bayindir<sup>(D)</sup>.

to decrease the voltage spike and stress [5]. Therefore, the circuit is costly and large in volume due to the supplementary circuit which decreases its efficiency. Therefore, the non-isolated circuits are becoming an attractive solution compared to isolated configurations [6]. In coupled inductor based converter, weith the variation in turn ratio of a coupled inductor, high output voltage can be generated. However, the coupled inductor converters suffer the problems of leakage inductances, voltage spikes, etc. [7]. Non-coupled inductor DC-DC converter includes multilevel converters [8], utilization of boost converter with switching capacitor network [9], switching inductor network [10], XY converter family [11], cascaded converter [12], quadratic converter [13], Luo converter [14], and voltage multiplier based converter [15], [16]. Switched capacitor converters can provide high voltage gain reliant on capacitors units in the switched capacitor cell [17]. However, switched capacitor converters have disadvantages of pulsating input current and poor voltage regulation. Switched inductor passive cells have been applied to enhance the output voltage [18], [19]. Lower current rating of the inductor is one advantage of switched inductor based converters. The active switch voltage stress is the major disadvantages of the structure. The switched capacitor-inductor passive cell combines the features of the switched capacitor and switched inductor converters, but the input current is discontinuous [10], [19]. The XY converter family also provides high voltage gain; however, discontinuous input current, switch voltage, and capacitor stack is a major drawback [11]. Cascading of several converters increases the voltage gain compared to the conventional converter, but complexity and cost increase as several components increases [12]. The quadratic converter can somehow lessen the problems of cascade circuits by adopting a single switch but required high voltage and current rating devices [13]. Luo converters provide high voltage, but topological complexity, cost, volume, and losses increase at the same time [14], [17]. Capacitor-diode voltage multiplier cell-based converters are a useful approach to increase voltage gain with increased efficiency and reliability in combination with classical converter topologies [15]. However, the number of capacitors and diodes increase, and also current snubber is needed to decrease di/dt. Also, the size and cost of converter increases [20].

This article proposes a new hybrid converter based on zeta converter, boost converter, an active-quad-switched-inductor (AQSL) structure for high voltage gain. The main features of the suggested converter are 1) voltage gain is high without using multiplier circuitry, 2) continuous input current, 3) low current rating inductor, 4) low voltage/current rating devices. Section II describes the proposed converter configuration and operation. The non-ideality characteristics of the proposed converter are examined in section III and comparison is given section IV. The performance of the designed prototype of the proposed converter is discussed in Section V. The article is concluded in section VI.

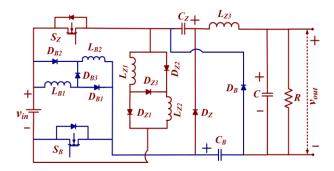

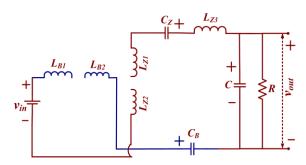

FIGURE 1. Hybrid zeta-boost converter.

#### **II. HYBRID ZETA BOOST CONVERTER**

Fig. 1 depicts the proposed circuit of the converter. The circuit is designed by combining zeta and boost converter, active quad switched-inductor (AQSL). The AQSL network contains diodes  $D_{Z1}$ ,  $D_{Z2}$ , and  $D_{Z3}$ , inductors  $L_{Z1}$  and  $L_{Z2}$ ,

and switch  $S_Z$  for zeta converter; and diodes  $D_{B1}$ ,  $D_{B2}$ , and  $D_{B3}$ , and inductors  $L_{B1}$  and  $L_{B2}$ , and switch  $S_B$  for the boost converter. The switch  $S_Z$  of zeta converters is connected at the positive polarity of the input supply, and switch  $S_B$  of the boost converter is connected at the negative polarity of the input supply. The diodes  $D_B$  and  $D_Z$  operate complimentary to the switches; and inductor  $L_{Z3}$  and capacitor C act as a low pass LC filter connected between the AQSL network and load.

#### A. CONTINUOUS CONDUCTION MODE

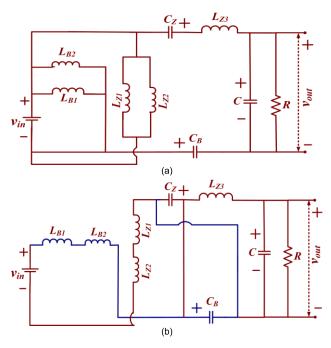

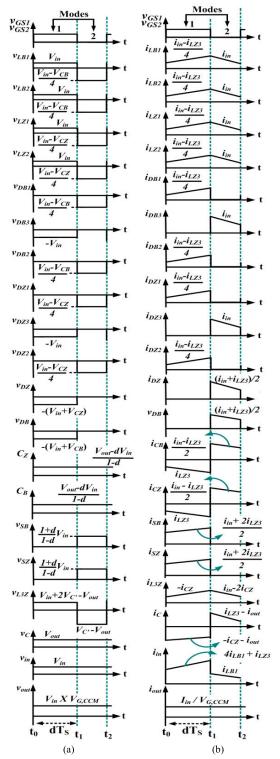

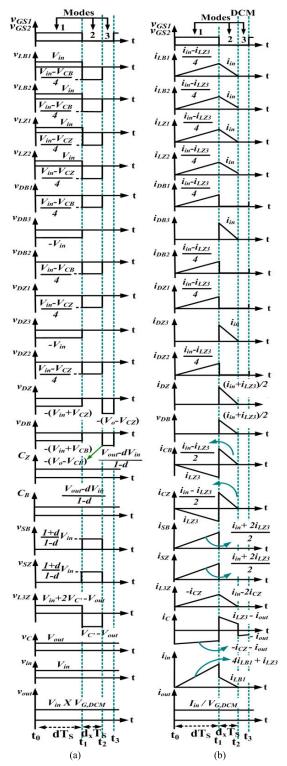

The equivalent circuit for different modes is illustrated in Fig. 2. The converter operates in two modes, one when switches  $S_B$  and  $S_Z$  are turned ON and another when switches  $S_B$  and  $S_Z$  are turned OFF. Fig. 3 shows the typical waveforms when the circuit operates in ON and OFF modes.

FIGURE 2. Equivalent circuitry of proposed hybrid zeta-boost converter (a) ON mode, (b) OFF mode.

1) MODE-1 ( $t_0 < t < t_1$ )

The proposed converter operates in this mode when switches  $S_B$  and  $S_Z$  are turned ON simultaneously. During this mode, the input source charged the inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$  and  $L_{Z2}$  in parallel and inductor  $L_{Z3}$  charged by input source and capacitors  $C_Z$  and  $C_B$ . The diodes  $D_{B1}$ ,  $D_{B2}$ ,  $D_{z1}$  and  $D_{z2}$  are forward bias, and diodes  $D_{B3}$ ,  $D_{Z3}$ ,  $D_B$  and  $D_Z$  are reversed bias. The inductors voltages are,

$$V_{LB1,on} = V_{LB2,on} = V_{LZ1,on} = V_{LZ2,on} = V_{in}$$

(1)

$$V_{LZ3,on} = V_{in} + V_{CZ} + V_{CB} - V_{out}$$

(2)

where  $V_{in}$  and  $V_{out}$  are voltage at the input and output terminal;  $V_{LB1,on}$ ,  $V_{LB2,on}$ ,  $V_{LZ1,on}$ ,  $V_{LZ2,on}$ , and  $V_{LZ3,on}$  are

FIGURE 3. Typical characteristics of proposed converters in CCM operation.

the voltage across inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  in mode-1,  $V_{CZ}$  is capacitor  $C_Z$  voltage,  $V_{CB}$  is capacitor  $C_B$  voltage. The input current is,

$$i_{in,on} = i_{LB1,on} + i_{LB2,on} + i_{LZ1,on} + i_{LZ2,on} + i_{LZ3,on}$$

(3)

where  $i_{in,on}$  is current through input terminal mode-1;  $i_{LB1,on}$ ,  $i_{LB2,on}$ ,  $i_{LZ1,on}$ ,  $i_{LZ2,on}$ , and  $i_{LZ3,on}$  are the current through

inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  in mode-1, respectively. The current through capacitors  $C_Z$ ,  $C_B$ , and C are obtained as,

$$i_{CZ,on} = -i_{LZ3,on}; \quad i_{CB,on} = -i_{LZ3,on}$$

(4)

$$i_{C,on} = i_{LZ3,on} - \frac{V_{out}}{R}$$

<sup>(5)</sup>

where  $i_{CZ, on}$ ,  $i_{CB, on}$ , and  $i_{C, on}$  are the current through capacitors  $C_Z$ ,  $C_B$ , and C in mode-1, respectively. The current through diodes  $D_{Z1}$ ,  $D_{Z2}$ ,  $D_{B1}$ , and  $D_{B2}$  are obtained as,

$$i_{DZ1,on} = i_{LZ1,on}; \quad i_{DZ2,on} = i_{LZ2,on}; \quad i_{DZ3,on} = 0$$

(6)

$$i_{DB1,on} = i_{LB1,on}; \quad i_{DB2,on} = i_{LB2,on}; \quad i_{DB3,on} = 0$$

(7)

$$i_{DB,on} = 0; \quad i_{DZ,on} = 0$$

(8)

where  $i_{DZ1,on}$ ,  $i_{DZ2,on}$ , and  $i_{DZ3,on}$  are current through diodes  $D_{Z1}$ ,  $D_{Z2}$ , and  $D_{Z3}$  in mode-1, respectively;  $i_{DB1,on}$ ,  $i_{DB2,on}$ , and  $i_{DB3,on}$  are current through diodes  $D_{B1}$ ,  $D_{B2}$ , and  $D_{B3}$  in mode-1, respectively;  $i_{DZ,on}$  and  $i_{DB,on}$  are current through diodes  $D_Z$  and  $D_B$  in mode-1, respectively.

## 2) MODE-2 ( $t_1 < t < t_2$ )

During this mode, switches are turned OFF and the inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$  and  $L_{Z2}$  are discharged in series. The input voltage source and inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$  and  $L_{Z2}$  provides energy to capacitors  $C_Z$  and  $C_B$ . The capacitors  $C_Z$  and  $C_B$  are charged in parallel. Also, the inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$ , and  $L_{Z3}$  provides energy to R and C. The diodes  $D_{B1}$ ,  $D_{B2}$ ,  $D_{Z1}$ , and  $D_{Z2}$  are reversed bias, and diodes  $D_{B3}$  and  $D_{Z3}$ ,  $D_B$  and  $D_Z$  are forward bias. The inductor voltages are,

$$V_{LB1,off} = V_{LB2,off} = V_{LZ1,off} = V_{LZ2,off}$$

$$= \frac{V_{in} - V_{CZ}}{4} = \frac{V_{in} - V_{CB}}{4}$$

(9)

$$V_{LZ3,off} = V_{CZ} - V_{out} = V_{CB} - V_{out}$$

(10)

where  $V_{LB1,off}$ ,  $V_{LB2,off}$ ,  $V_{LZ1,off}$ ,  $V_{LZ2,off}$ , and  $V_{LZ3,off}$  are the voltage across inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  in mode-2, respectively. The current through capacitors  $C_Z$ ,  $C_B$ , and C are obtained as,

$$i_{CZ,off} = \frac{i_{in,off} - i_{LZ3,off}}{2}, \quad i_{CB,off} = \frac{i_{in,off} - i_{LZ3,off}}{2}$$

(11)

$$i_{C,off} = i_{LZ3,off} - \frac{V_{out}}{R}$$

(12)

where  $i_{CZ,off}$ ,  $i_{CB,off}$ , and  $i_{C,off}$  are the current through capacitors  $C_Z$ ,  $C_B$ , and C in mode-2, respectively. The current through diodes  $D_{Z1}$ ,  $D_{Z2}$ ,  $D_{B1}$ , and  $D_{B2}$  are obtained as,

$$i_{DZ1,off} = 0; \quad i_{DZ2,off} = 0; \ i_{DZ3,off} = i_{LZ1,off} = i_{LZ2,off}$$

(13)

$i_{DB1,off} = 0; \quad i_{DB2,off} = 0; \ i_{DB3,off} = i_{LB1,off} = i_{LB2,off}$ (14)

$$i_{DB,on} = \frac{i_{in,off} + i_{LZ3,off}}{2}; \quad i_{DZ,on} = \frac{i_{in,off} + i_{LZ3,off}}{2}$$

(15)

The voltage across intermediate capacitor  $C_Z$  and  $C_B$  are as follows,

$$V_{C'} = V_{CZ} = V_{CB} \tag{16}$$

As the average voltage across an inductor is null in steadystate, the following expression can be obtained,

$$\langle v_{LZ3} \rangle = (V_{in} + 2V_{C'} - V_{out}) d + (V_{C'} - V_{out}) (1 - d) = 0$$

(18)

where d is the duty cycle. From (18), an expression for voltage  $V_{C'}$  i.e. the voltage across capacitors  $C_Z$  or  $C_B$  is obtained as follows,

$$V_{C'} = \frac{V_{out} - V_{in}d}{1+d} = \frac{1+3d}{1-d}V_{in}$$

(19)

Using (17) and (19), the voltage gain is obtained as follows,

$$V_{M,CCM} = \frac{V_{out}}{V_{in}} = \frac{1 + 5d + 2d^2}{1 - d}$$

(20)

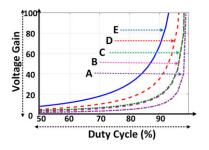

where,  $V_{M,CCM}$  is the CCM voltage gain. Fig. 4 shows the plot of voltage across capacitor  $C_Z$  and  $C_B$  i.e.  $V_{C'}$  and voltage gain with variation in duty cycle and observed that the voltage ratio can be obtained by selecting appropriate duty cycle.

FIGURE 4. Plots (a) Ratio of capacitor voltage and input voltage versus duty cycle, (b) Voltage gain versus duty cycle.

When the inductances are unequal the current profile of the inductors are different. Hence, the operating modes of the converter are quite different when the inductances are unequal. However, the voltage gain of the converter is the same as the situation when the inductances are equal [21], [22].

#### **B. DISCONTINUOUS CONDUCTION MODE**

The typical waveforms for discontinuous conduction mode are shown in Fig. 5.

## 1) MODE-1 ( $t_0 < t < t_1$ )

The equivalent circuit is shown in Fig. 2(a). The maximum value of inductors  $L_{Z1}$ ,  $L_{Z2}$ ,  $L_{B1}$ ,  $L_{B2}$ , and  $L_{Z3}$  currents are obtained as follows,

$$I_{LZ1,\max} = \frac{V_{in}d}{f_s L_{Z1}} + I_{LZ1,\min}$$

(21)

$$I_{LZ2,\max} = \frac{V_{in}d}{f_s L_{Z2}} + I_{LZ2,\min}$$

(22)

$$I_{LB1,\max} = \frac{V_{in}d}{f_s L_{B1}} + I_{LB1,\min}$$

(23)

$$I_{LB2,\max} = \frac{V_{in}d}{f_s L_{B2}} + I_{LB2,\min}$$

(24)

$$I_{LZ3,\max} = \frac{(V_{in} + V_{CZ} + V_{CB} - V_{out})d}{f_s L_{Z3}} + I_{LZ3,\min} \quad (25)$$

where,  $I_{LZ1,max}$ ,  $I_{LZ2,max}$ ,  $I_{LB1,max}$ ,  $I_{LB2,max}$ , and  $I_{LZ3,max}$  are the maximum value of current through inductors  $L_{Z1}$ ,  $L_{Z2}$ ,  $L_{B1}$ ,  $L_{B2}$ , and  $L_{Z3}$  respectively;  $I_{LZ1,min}$ ,  $I_{LZ2,min}$ ,  $I_{LB1,min}$ ,  $I_{LB2,min}$ , and  $I_{LZ3,min}$  are the minimum values of current through inductors  $L_{Z1}$ ,  $L_{Z2}$ ,  $L_{B1}$ ,  $L_{B2}$ , and  $L_{Z3}$ , respectively.

2) MODE-2 ( $t_1 < t < t_2$ )

The equivalent circuit is shown in Fig. 2(b). Let's assume, when  $t_2 = dT_S + d_x T_S$ , the diodes  $D_Z$ ,  $D_B$ ,  $D_{B2}$ ,  $D_{Z2}$ , and inductors  $L_{Z1}$ ,  $L_{Z2}$ ,  $L_{B1}$ ,  $L_{B2}$ , and  $L_{Z3}$  current reached to zero. The minimum value of inductor  $L_{Z1}$ ,  $L_{Z2}$ ,  $L_{B1}$ ,  $L_{B2}$ , and  $L_{Z3}$ currents are obtained as follows,

$$I_{LZ1,\min} = \frac{(V_{in} - V_{CZ}) d_x}{4f_s L_{Z1}} + I_{LZ1,\max} = 0$$

(26)

$$I_{LZ2,\min} = \frac{(V_{in} - V_{CZ}) d_x}{4f_s L_{Z2}} + I_{LZ2,\max} = 0$$

(27)

$$I_{LB1,\min} = \frac{(V_{in} - V_{CB}) d_x}{4f_s L_{B1}} + I_{LB1,\max} = 0$$

(28)

$$I_{LB2,\min} = \frac{(V_{in} - V_{CB}) d_x}{4f_s L_{B2}} + I_{LB2,\max} = 0$$

(29)

$$I_{LZ3,\min} = \frac{(V_{CB} - V_{out}) d_x}{f_s L_{Z3}} + I_{LZ3,\max} = 0$$

(30)

3) MODE-3 (t<sub>2</sub> < t < t<sub>3</sub>)

For this period, the current through the diodes becomes zero and the converter circuitry is illustrated in Fig. 6. The inductors  $L_{Z1}$ ,  $L_{Z2}$ ,  $L_{B1}$ ,  $L_{B2}$ , and  $L_{Z3}$  currents are obtained as follows,

$$I_{LZ1,\min} = I_{LZ2,\min} = 0$$

(31)

$$I_{LB1,\min} = I_{LB23,\min} = 0$$

(32)

**FIGURE 5.** Typical Characteristics of proposed converters in DCM operation.

$$I_{LZ3,\min} = 0 \tag{33}$$

The current through capacitor  $C_Z$  and  $C_B$  for time period ( $t_2$  to  $t_3$ ) is as follows,

$$i_{CZ} = i_{CB} = 0 \tag{34}$$

FIGURE 6. DCM operation of proposed converter.

The current through diodes of zeta converter, i.e.  $D_{Z1}$ ,  $D_{Z2}$ ,  $D_{Z3}$ , and  $D_Z$  for time period ( $t_2$  to  $t_3$ ) is as follows,

$$i_{DZ1} = i_{DZ2} = i_{DZ3} = i_{DZ} = 0 \tag{35}$$

The current through diodes of boost converter, i.e.  $D_{B1}$ ,  $D_{B2}$ ,  $D_{B3}$ , and  $D_B$  for time period ( $t_2$  to  $t_3$ ) is as follows,

$$i_{DB1} = i_{DB2} = i_{DB3} = i_{DB} = 0 \tag{36}$$

The value of  $d_x$  (note: duration of mode 2 is  $d_x T_s$ ) and capacitor C voltage are calculated as,

$$d_x = \frac{4V_{in}d}{V_C - V_{in}} \tag{37}$$

$$V_C = \frac{2V_{out} + V_{in}(1+d)}{3+d}$$

(38)

By substituting (37) in (36),

$$d_x = \frac{2V_{in}d(3+d)}{V_{out} - V_{in}}$$

(39)

The relation between the current through diode  $D_Z$  and  $D_B$  and output current can be obtained as follows,

$$I_{out} = I_{DZ,\max} \frac{d_x}{2} = I_{DB,\max} \frac{d_x}{2} = \frac{V_{out}}{R}$$

(40)

$$I_{DZ,\max} = I_{DB,\max} = \frac{I_{LZ1,\max} + I_{LZ3,\max}}{2}$$

(41)

$$I_{out} = \frac{V_{out}}{R} = \frac{V_{in}^2 d^2 (3+d)}{2f_s L_{eq} (V_{out} - V_{in})}$$

(42)

where  $L_{eq}$  is considered as equivalent inductance and it is obtained as,

$$L_{eq} = \frac{2L_{Z3}L}{2(1+d)L + L_{Z3}}$$

(43)

where,  $L = L_{Z1} = L_{Z2} = L_{B1} = L_{B2}$ .

From (42), the DCM voltage gain is expressed as,

$$V_{M,DCM} = \frac{V_{out}}{V_{in}} = \frac{1}{2} + \frac{1}{2}\sqrt{1 + \frac{4d^2(3+d)}{K}}$$

(44)

where k is a dimensionless parameter obtained as,

$$K = \frac{f_s L_{eq}}{R} \tag{45}$$

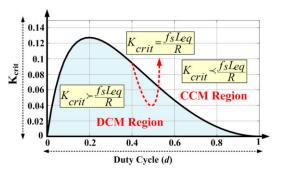

# C. CCM AND DCM BOUNDARY OPERATING CONDITION

DCM operation occurs when the inductor current reaches zero. By equating equations (20) and (44), the critical value of K, *i.e.*  $K_{crit}$  is obtained as,

$$K_{crit} = \frac{4d (3+d) (1-d)^2}{4d^3 + 11d^2 + 32d + 6}$$

(46)

FIGURE 7. CCM and DCM boundary.

Fig. 7 shows that converter works in CCM when  $K > K_{crit}$ . Also, critical load resistance is computed, and parameter  $\gamma$  which signify the parameterized converter output current is defined as,

$$R_{crit} = \frac{4f_s L_{eq} \left(1 + 5d + 2d^2\right)}{d \left(1 - d\right)^2} \tag{47}$$

$$\gamma = \frac{I_{out} f_s L_{eq}}{V_{in}} \tag{48}$$

The critical value  $\gamma$  is stated in the form of the static gain.

$$\gamma crit = \frac{d^2 (3+d)}{2 (V_M - 1)}$$

(49)

$$\gamma crit = \frac{d \left(1 - d\right)}{4} \tag{50}$$

# **III. DESIGN CONSIDERATION**

Concerning the converter operation in CCM, a detailed study can be achieved for getting the basic equations describing the current and voltage stresses of the elements.

The inductance  $L_{Z3}$  can be obtained by,

$$L_{Z3} = \frac{2v_{in} \left(1 + d\right) d}{\Delta I_{LZ3} f_s}$$

(51)

The average current in output capacitor  $C_o$  is zero during the steady-state situation, the average current flowing through output inductor  $I_{LZ3}$  becomes equal to the average current flowing through load  $I_o$ . Therefore,

$$I_{LZ3} = I_{out} = \frac{1-d}{1+5d+2d^2} I_{in}$$

(52)

$$I_{LZ3} = \frac{P(1-d)}{v_{in}\left(1+5d+2d^2\right)}$$

(53)

The inductance  $L_{Z1}$  and  $L_{Z1}$  can be obtained by,

$$L_{Z1} = \frac{V_{in}d}{\Delta I_{LZ1}f_s}, \quad L_{Z2} = \frac{V_{in}d}{\Delta I_{LZ2}f_s}$$

(54)

The inductance  $L_{B1}$  and  $L_{ZB2}$  can be obtained by,

$$L_{B1} = \frac{V_{in}d}{\Delta I_{LB1}f_s}, \quad L_{B2} = \frac{V_{in}d}{\Delta I_{LB2}f_s}$$

(55)

The average value of the input current is,

$$I_{in} = (4I_L + I_{LZ3}) d + I_L (1 - d)$$

(56)

where, the average current through inductor  $L_{Z1}$ ,  $L_{Z1}$ ,  $L_{B1}$  and  $L_{ZB2}$  be obtained by,

$$I_{L} = I_{LB1} = I_{LB2} = I_{LZ1} = I_{LZ2}$$

=

$$\frac{P(1 + 4d + 3d^{2})}{v_{in}(1 + 5d + 2d^{2})(1 + 3d)}$$

(57)

where *P* is output power. The critical values of capacitors  $C' = C_Z = C_B$  can be obtained by,

$$C' = C_B = C_Z = \frac{Pd (1-d)}{V_{in} f_s \left(1 + 5d + 2d^2\right) \Delta V_C}$$

(58)

The average voltage across capacitor  $C_B$ ,  $C_Z$  and C is obtained by,

$$V_{C'} = V_{CB} = V_{CZ} = \frac{v_{in} \left(1 + 4d + 3d^2\right)}{(1 - d) \left(1 + d\right)}$$

(59)

$$V_C = \frac{1 + 5d + 2d^2}{1 - d} V_{in} \tag{60}$$

The peak voltage across diodes are as follows,

$$V_{DZ1,peak} = V_{DZ2,peak} = \frac{V_{in} - V_C}{4}, \quad V_{DZ3,peak} = -V_{in}$$

(61)

$$V_{DB1,peak} = V_{DB2,peak} = \frac{V_{in} - V_C}{4}, \quad V_{DB3,peak} = -V_{in}$$

(62)

$$V_{DZ,peak} = -V_{in} - V_{C'}, \quad V_{DB,peak} = -V_{in} - V_{C'}$$

(63)

The average current through diodes of switched inductors can be obtained as follows,

$$I_{DZ1} = I_{DZ2} = \frac{P\left(1 + 4d + 3d^2\right)}{V_{in}\left(1 + 5d + 2d^2\right)\left(1 + 3d\right)}d$$

(64)

$$I_{DB1} = I_{DB2} = \frac{P(1+4d+3d^2)}{V_{in}(1+5d+2d^2)(1+3d)}d$$

(65)

$$I_{DZ3} = I_{DB3} = \frac{P(1+4d+3d^2)}{V_{in}(1+5d+2d^2)(1+3d)}(1-d) \quad (66)$$

$$I_{DB1} = I_{DB2} = \frac{P(1+4d+3d^2)}{V_{in}(1+5d+2d^2)(1+3d)}d$$

(67)

The maximum voltage across switches are,

$$V_{SB} = \frac{(1+d)}{(1-d)} V_{in}, \quad V_{SZ} = \frac{(1+d)}{(1-d)} V_{in}$$

(68)

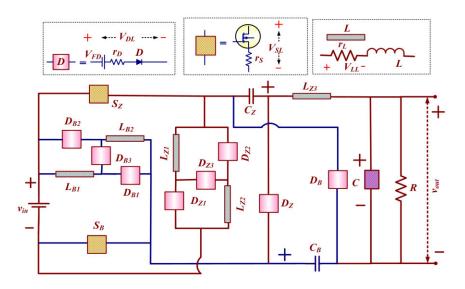

FIGURE 8. Hybrid zeta-boost converter with parasitic of active and passive components.

(69)

#### **IV. NON-IDEAL MODEL OF CONVERTER**

Fig. 8 depicts the power circuit with non-idealities of elements of the converter, where  $r_L$  is resistance of inductor,  $r_S$  is resistance of switch,  $r_D$  and  $V_{FD}$  is resistance and the threshold voltage of the diode.

#### A. VOLTAGE GAIN WITH NON-IDEAL INDUCTORS

The effect of ESR of inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  is analyzed while ignoring other parasitic components, i.e.  $r_S = 0$ ,  $r_D = 0$ , and  $V_{FD} = 0$ . The inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  voltages are,

$$V_{LB1} \approx V_{in} - i_{LB1}r_L, V_{LB2} \approx V_{in} - i_{LB2}r_L$$

$$V_{LZ1} \approx V_{in} - i_{LZ1}r_L, V_{LZ2} \approx V_{in} - i_{LZ2}r_L$$

$$V_{LZ3} = V_{in} + V_{CZ} + V_{CB} - V_{out} - i_{LZ3}r_L$$

mode-1

$$\begin{cases} V_{LB1} \approx V_{LB2} \approx V_{LZ1} \approx V_{LZ2} \\ \approx \frac{V_{in} - V_{C'} - i_{LB1}r_L - i_{LB2}r_L - i_{LZ1}r_L - i_{LZ2}r_L}{4} \\ V_{LZ3} = V_{CZ} - V_{out} - i_{LZ3}r_L \end{cases}$$

mode-2 (70)

Consider, the drop in voltage across each inductor due to  $r_L$  is  $V_{LL}$ . Therefore,

$$V_{LB1} = V_{LB2} = V_{LZ1} = V_{LZ2} \approx V_{in} - V_{LL} \\ V_{LZ3} = V_{in} + V_{CZ} + V_{CB} - V_{out} - V_{LL} \\ V_{LB1} \approx V_{LB2} \approx V_{LZ1} \approx V_{LZ2} \approx \frac{V_{in} - V_{C'} - 4V_{LL}}{4} \\ V_{LZ3} = V_{CZ} - V_{out} - V_{LL}$$

(71)

(72)

As the average voltage across an inductor is null in steadystate, the following expression can be obtained,

$$(V_{in} - V_{LL})d + \left(\frac{V_{in} - V_{C'} - 4V_{LL}}{4}\right)(1 - d) = 0$$

(73)

$$(V_{in} + 2V_{C'} - V_{out} - V_{LL}) d + (V_{C'} - V_{out} - V_{LL}) (1 - d) = 0$$

(74)

The expression for voltage  $V_{C'}$  i.e. voltage across capacitors  $C_Z$  or  $C_B$  is obtained as follows,

$$V_{C'} = \frac{V_{out} - V_{in}d + V_{LL}}{1 + d}$$

(75)

The converter voltage gain is obtained as follows,

$$V_{M,CCM} = \frac{\left(1 + 5d + 2d^2\right) - \left\{(5 + 3d) V_{LL} / V_{in}\right\}}{1 - d}$$

(76)

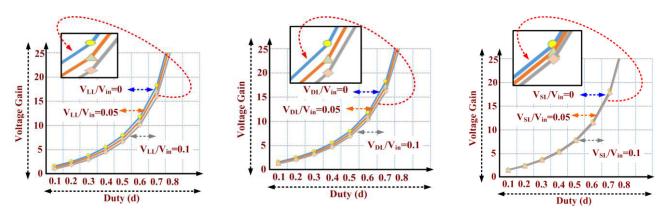

Equation (76) is plotted in Fig 9(a) with variation in duty cycle, and the effect of non-ideal inductors on voltage gain is presented.

#### **B. VOLTAGE GAIN WITH NON-IDEAL DIODES**

The effect of diodes  $D_{B1}$ ,  $D_{B2}$ ,  $D_{B3}$ ,  $D_{Z1}$ ,  $D_{Z2}$  and  $D_{Z3}$ , and diodes  $D_B$  and  $D_S$  are analyzed while ignoring other parasitic components, i.e.  $r_L = 0$ , and  $r_S = 0$ . The inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  voltages are,

$$V_{LB1} = V_{LB2} = V_{LZ1} = V_{LZ2} \approx V_{in} - i_L r_D - V_{FD} \\ V_{LZ3} = V_{in} + 2V_{C'} - V_{out} \times \text{mode-1}$$

(77)

$$V_{LB1} \approx V_{LB2} \approx V_{LZ1} \approx V_{LZ2} \approx \frac{V_{in} - V_{C'} - 3i_L r_D - 3V_{FD}}{4} \\ V_{LZ3} = V_{C'} - V_{out} - i_L r_D - V_{FD} \times \text{mode-2}$$

(78)

Consider, the drop in voltage across each inductor due to parasitic of diode is  $V_{DL}$ . Therefore,

$$V_{LB1} = V_{LB2} = V_{LZ1} = V_{LZ2} \approx V_{in} - V_{DL}$$

$$V_{LZ3} = V_{in} + 2V_{C'} - V_{out}$$

(79)

FIGURE 9. Effect of parasitic on voltage gain, (a) voltage gain by considering ESR of inductor, (b) voltage gain by considering diode forward resistance and threshold voltage, (c) voltage gain by considering switch resistance.

$$V_{LB1} \approx V_{LB2} \approx V_{LZ1} \approx V_{LZ2} \approx \frac{V_{in} - V_{C'} - 3V_{DL}}{4}$$

$$V_{LZ3} = V_{C'} - V_{out} - V_{DL}$$

$$(80)$$

As the average voltage across an inductor is null in steadystate, the following expression can be obtained,

$$(V_{in} - V_{DL}) d + \left(\frac{V_{in} - V_{C'} - 3V_{DL}}{4}\right)(1 - d) = 0 \quad (81)$$

$$(V_{in} + 2V_{C'} - V_{out}) d + (V_{C'} - V_{out}) (1 - d) = 0$$

(82)

The expression for voltage  $V_{C'}$  i.e. voltage across capacitors  $C_Z$  or  $C_B$  is obtained as follows,

$$V_{C'} = \frac{V_{out} - V_{in}d}{1+d}$$

(83)

The converter voltage gain is obtained as follows,

$$V_{M,CCM} = \frac{\left(1 + 5d + 2d^2\right) - \left\{\left(1 + d\right)\left(3 + d\right)V_{DL}/V_{in}\right\}}{1 - d}$$

(84)

Equation (84) is plotted in Fig 9(b) with variation in duty cycle, and the effect of non-ideal diodes on voltage gain is presented.

#### C. VOLTAGE GAIN WITH NON-IDEAL SWITCHES

The effect of parasitic of switches  $S_Z$  and  $S_B$  is analyzed while ignoring other parasitic components, i.e.  $r_L = 0$ ,  $r_D = 0$ , and  $V_{FD} = 0$ . The inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  and  $L_{Z3}$  voltages are,

$$V_{LB1} = V_{LB2} \approx V_{in} - i_{S1}r_S, V_{LZ1} = V_{LZ2} \approx V_{in} - i_{S2}r_S \\ V_{LZ3} = V_{in} + 2V_{C'} - V_{out} - i_{S1}r_S - i_{S2}r_S \\ \times \text{mode-1}$$

(85)

$$V_{LB1} \approx V_{LB2} \approx V_{LZ1} \approx V_{LZ2} \approx \frac{V_{in} - V_{C'}}{4}$$

$$V_{LZ3} = V_{C'} - V_{out}$$

$$\left. \right\} \text{ mode-2 (86)}$$

Consider, the drop in voltage across each inductor due to parasitic of the diode is  $V_{SL}$ . Therefore,

$$V_{LB1} = V_{LB2} = V_{LZ1} = V_{LZ2} \approx V_{in} - V_{SL}$$

$$V_{LZ3} = V_{in} + 2V_{C'} - V_{out} - 2V_{SL}$$

mode-1 (87)

$$V_{LB1} \approx V_{LB2} \approx V_{LZ1} \approx V_{LZ2} \approx \frac{V_{in} - V_{C'}}{4}$$

mode-2 (88)

$$V_{LZ3} = V_{C'} - V_{out}$$

As the average voltage across an inductor is null in steadystate, the following expression can be obtained,

$$(V_{in} - V_{SL}) d + \left(\frac{V_{in} - V_{C'}}{4}\right)(1 - d) = 0$$

(89)

$$(V_{in} + 2V_{C'} - V_{out} - 2V_{SL}) d + (V_{C'} - V_{out})(1 - d) = 0$$

(90)

The expression for voltage  $V_{C'}$  i.e. voltage across capacitors  $C_Z$  or  $C_B$  is obtained as follows,

$$V_{C'} = \frac{V_{out} - V_{in}d}{1+d}$$

(91)

The converter voltage gain is obtained as follows,

$$V_{M,CCM} = \frac{\left(1 + 5d + 2d^2\right) - \left\{(1 + d)di_s r_s / V_{in}\right\}}{1 - d}$$

(92)

Equation (92) is plotted in Fig 9(c) with variation in duty cycle, and the effect of non-ideal switches on voltage gain is presented.

#### V. COMPARISON

This section presents a comparative study between proposed converter, classical boost converter [1], converter presented in [7], switched capacitor converter [8], switched inductor converter [9], symmetric hybrid- switched inductor converter [10], and active switched-inductor step-up 2 cell converter [20]. Table 1 shows the comparison in terms of number of components, voltage gain, switches and the diodes voltage stress, type of input current and load. The variation in voltage gain at various duty cycle is shown in Fig. 5. shows the variation of voltage gain with duty cycle. Converter [7] and [9] provide the same gain and similarly, converter [10] and [20] provides the same gain. The main advantages of the proposed circuit against the classical boost converter and compared converter are its low voltage stress and high voltage gain for a given duty cycle. This allows the use of reduced resistance switches that further decreases the conduction losses.

#### TABLE 1. Comparison of converters.

| Converter                                    | Boost [1]       | Converter [7]     | SC [8]          | SI [9]                        | SH-SL [10]                    | ASL-SU2C [20]      | Proposed Converter                 |

|----------------------------------------------|-----------------|-------------------|-----------------|-------------------------------|-------------------------------|--------------------|------------------------------------|

| Inductor                                     | 1               | 1                 | 1               | 2                             | 4                             | 3                  | 5                                  |

| Diode                                        | 1               | 1                 | 3               | 4                             | 7                             | 2                  | 8                                  |

| Switches                                     | 1               | 2                 | 1               | 1                             | 2                             | 2                  | 2                                  |

| Capacitor                                    | 1               | 1                 | 3               | 1                             | 1                             | 3                  | 3                                  |

| Voltage gain                                 | $\frac{1}{1-d}$ | $\frac{1+d}{1-d}$ | $\frac{2}{1-d}$ | $\frac{1+d}{1-d}$             | $\frac{1+3d}{1-d}$            | $\frac{1+3d}{1-d}$ | $\frac{1+5D+2D^2}{1-d}$            |

| Noramlised Voltage stress of Switches        | 1               | $\frac{G+1}{2G}$  | $\frac{1}{2}$   | 1                             | $\frac{G+1}{2G}$              | $\frac{1}{1+3d}$   | $\frac{1+d}{(1-d)G}$               |

| Normalised Voltage<br>stress of P-SL Diode   | -               | -                 | -               | $\frac{G-1}{2G}, \frac{1}{G}$ | $\frac{G-1}{4G}, \frac{1}{G}$ | -                  | $\frac{1-G}{4G(1-d)}, \frac{1}{G}$ |

| Normalised Voltage stress of SC Diode        | -               | -                 | -               | -                             | -                             | $\frac{2}{1+3d}$   | $\frac{2}{G(1-d)}$                 |

| Normalised Voltage stress<br>of Output Diode | 1               | $\frac{G+1}{G}$   | $\frac{1}{2}$   | 1                             | $\frac{G+1}{G}$               | -                  | -                                  |

| Constant input current                       | No              | No                | Yes             | Yes                           | No                            | No                 | No                                 |

| Load Type                                    | Grounded        | Floating          | Grounded        | Grounded                      | Grounded                      | Grounded           | Grounded                           |

#### TABLE 2. Simulation parameters.

| Parameters              | Values                                                              |  |  |  |

|-------------------------|---------------------------------------------------------------------|--|--|--|

| Output Power            | 500 W                                                               |  |  |  |

| $V_{in}$                | 50 V                                                                |  |  |  |

| $V_{out}$               | 400 V                                                               |  |  |  |

| Switching Frequency (f) | 50 kHz                                                              |  |  |  |

| Inductors               | $L_{B1}$ , $L_{B2}$ , $L_{Z1}$ , $L_{Z2}$ =180 µH, $L_{Z3}$ =300 µH |  |  |  |

| Capacitors              | $C_Z$ , $C_B$ =470 $\mu$ F                                          |  |  |  |

|                         | <i>C<sub>0</sub></i> =470 µF                                        |  |  |  |

| Load (Resistive)        | 320 Ω                                                               |  |  |  |

#### TABLE 3. Experimental parameters.

| Parameters                            | Typical Values                                 |

|---------------------------------------|------------------------------------------------|

| V <sub>in</sub>                       | 50 V                                           |

| $V_{out}$                             | 400 V                                          |

| Output Power                          | 500 W                                          |

| Switching Frequency (f)               | 50 kHz                                         |

| Inductors                             | $L_{B1}, L_{B2}, L_{Z1}, L_{Z2} = 180 \ \mu H$ |

|                                       | $L_{Z3}$ =300 µH (Core type)                   |

| Capacitors                            | $C_Z, C_B = 470 \mu F / 400 V$                 |

|                                       | $C_O = 470 \mu F / 450 V$                      |

| Diodes $D_{B1}$ , $D_{B2}$ , $D_{B3}$ | NTE5812HC                                      |

| Diodes $D_{B1}$ , $D_{B2}$ , $D_{B3}$ | NTE5812HC                                      |

| Diode $D_B$ and $D_Z$                 | NTE5814HC                                      |

| Switches $S_B$ and $S_Z$              | IXTH16N20D2                                    |

**FIGURE 10.** Comparison of converter in terms of voltage gain versus duty ratio. A: conventional boost converter, B: converter in [7] and [9], C: converter in [8], D: converter in [10]–[20], E: Proposed converter.

#### **VI. SIMULATION AND EXPERIMENTAL RESULTS**

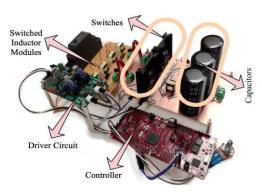

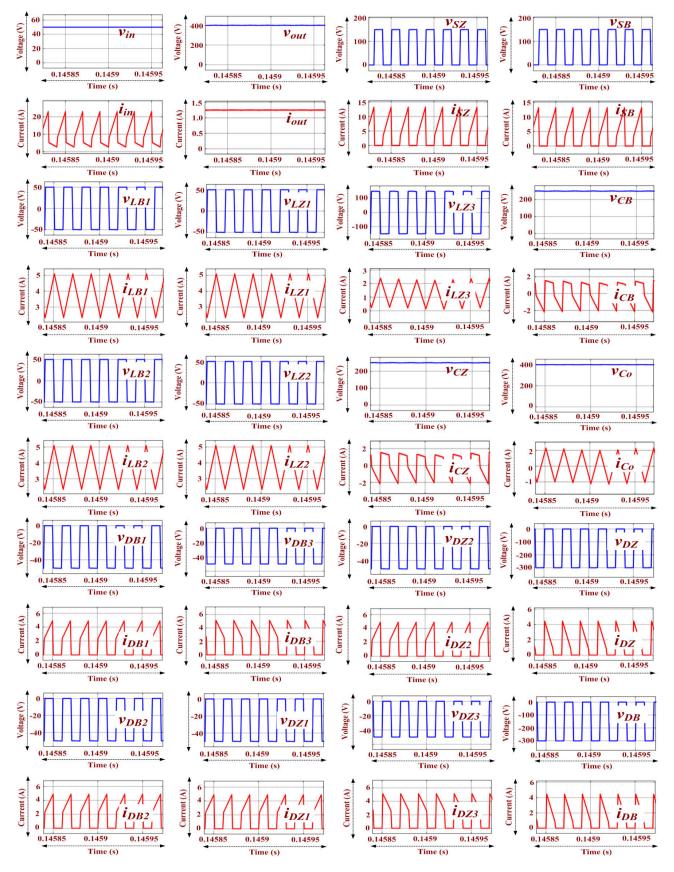

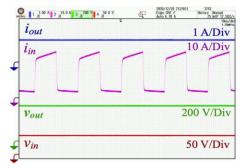

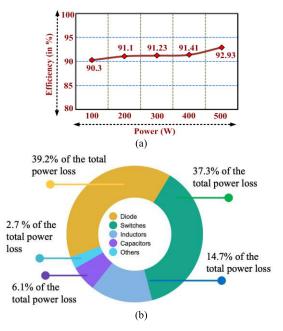

Table 2 shows the simulation parameters of the proposed hybrid zeta-boost converter. The performance of the proposed converter is tested in the Renewable Energy Lab (REL) at various power level, and the experimental parameters are given in Table 3. Fig. 11 shows the designed prototype of the proposed converter for power 500 W. Initially, the converter is simulated with ideal component and operates to generate output voltage 400 V. Fig. 12 shows the waveforms obtained during steady-state operation. From Fig 12, it is observed that the voltage and current at the output terminal are 400.1 V and 1.25 A, respectively for the input voltage values of 50 V.

FIGURE 11. Prototype of proposed converter (500W).

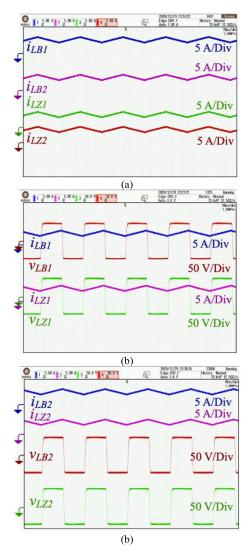

The input current is continuous and has an average value of 10.01 A. When the switches  $S_Z$  and  $S_B$  turned ON, the voltage across switches  $S_Z$  and  $S_B$  is 150 V, and the average value of current through  $S_Z$  and  $S_B$  is 4.1 A, respectively. When the switches  $S_Z$  and  $S_B$  turned ON, the inductors currents increases with a positive slope due to magnetization, the voltages across inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  is 50 V, and the voltage across inductor  $L_{Z3}$  is 150 V.

FIGURE 12. Simulation results for the proposed converter under steady-state conditions.

FIGURE 13. Voltage and current at input and output terminal.

**FIGURE 14.** Switched inductors waveforms, (a) Current through inductors of switched inductor modules, (b) Current and voltage for inductors  $L_{B1}$  and  $L_{Z1}$ , (c) Current and voltage for inductors  $L_{B2}$  and  $L_{Z2}$ .

When the switches  $S_Z$  and  $S_B$  turned OFF, the inductors currents through the inductors decreases with a negative slope due to demagnetization, the voltages across inductors  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$ ,  $L_{Z2}$  is -50 V, and the voltage across inductor  $L_{Z3}$  is equal to -150 V. The average current through inductors  $L_{B1}$ ,

**FIGURE 15.** Voltage and current waveforms for (a) inductor  $L_{Z3}$  and capacitor  $C_0$ , (b) switches  $S_B$  and  $S_Z$ .

$L_{B2}$ ,  $L_{Z1}$ , and  $L_{Z2}$  is equal to 3.757 A, and the average current through inductor  $L_{Z3}$  is 1.25 A. The observed value of voltage across  $C_Z$  and  $C_B$  capacitors is equal to 250 V, and the voltage across  $C_o$  capacitor is 400 V. When the switches  $S_Z$  and  $S_B$ turned ON, the diodes  $D_{B1}$ ,  $D_{B2}$ ,  $D_{Z1}$  and  $D_{Z2}$  are forward biased, and diodes  $D_{B3}$ ,  $D_{Z3}$ ,  $D_B$  and  $D_Z$  are reversed biased and vice versa when switches  $S_Z$  and  $S_B$  turned OFF. The blocking voltage of diodes  $D_{B1}$ ,  $D_{B2}$ ,  $D_{Z1}$ ,  $D_{Z2}$ ,  $D_{B3}$ ,  $D_{Z3}$ is -50 V, and blocking voltage of diodes  $D_B$  and  $D_Z$  are -300 V, respectively. The average current through diodes  $D_{B1}$ ,  $D_{B2}$ ,  $D_{Z1}$ ,  $D_{Z2}$  is 1.779 A, the average current through diodes  $D_{B3}$ ,  $D_{Z3}$  is 1.979 A, and the average current through diodes  $D_B$  and  $D_Z$  are 1.388 A.

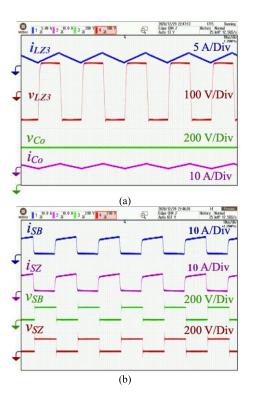

From Fig. 13, it is observed that output voltage 399.6 V is generated at the output when input voltage 50.1 V given at the input terminal and load is 320  $\Omega$ . The average input and output currents are 10.72 A and 1.25 A, respectively. Fig. 14(a) shows the waveforms of the current through inductors of switched inductor during steady-state conditions. The inductor  $L_{B1}$ ,  $L_{B2}$ ,  $L_{Z1}$  and  $L_{Z2}$  are magnetized during ON state and demagnetized in ON state with the average current 3.84 A, 3.81 A, 3.84 A and 3.86 A, respectively. From Fig.14(b), it is observed that the inductors  $L_{B1}$  and  $L_{Z1}$  charged with voltage 49.9 V and -49.8 V, and discharged with voltage 49.4 V and -49.3 V, respectively.

From Fig. 14(c), it is observed that the inductors  $L_{B2}$  and  $L_{Z2}$  charged with voltage 49.8 V and -49.9 V, and discharged with voltage 49.4 V and -49.5 V, respectively. From Fig. 15(a), it is observed that the voltage across inductor

$L_{Z3}$  in ON and OFF states are 149.8 V and -149.3 V, respectively with the average current 1.24 A. It is seen that the capacitor  $C_o$  charged and discharged in ON and OFF state, respectively with the average voltage 399.6 V. From Fig. 15(b), it is observed that the voltage across switches  $S_B$ and  $S_Z$  is 150.1 V and 149.1 V, respectively. The average current through switches  $S_B$  and  $S_Z$  is 4.34 A and 4.4 A, respectively. The efficiency of the converter is observed for various power level 100 W to 500 W. The efficiency and power loss distribution plots at power 500 W are depicted in Fig. 16. The 92.93% efficiency is observed when load power is 500 W. It is observed that 39.2% and 37.3% of total power loss observed in the diode and switches, respectively.

FIGURE 16. Plot (a) Efficiency versus power (b) Power loss distribution of the proposed converter at power 500W and voltage gain 8.

## VII. CONCLUSION

A novel hybrid converter based on zeta and boost converter, with active quad switched-inductor (AQSL) is proposed to achieve high voltage gain. The input current division between the switches due to AQSL reduces the inductor and switch current stress. Moreover, the voltage across semiconductor devices are low compared to the output voltage. Therefore, low voltage and current stress across semiconductor components lead to the use of low rating components, reducing the cost and conduction losses. The voltage gain offered by the proposed circuit is more than conventional boost converter and various other switched capacitor/ switched inductor based converters. The CCM and DCM analysis, boundary condition, design consideration, effect of parasitic on voltage gain and comparison with other high-gain converters are explained in detail. The proposed configuration, in comparison with topologies employing the same concepts, provides the merits like the high voltage gain with low voltage stresses across the semiconductor components. The performance of the proposed topology is verified through simulation and experimental work, and efficiency of the designed prototype is 92.93% at power 500W.

# ACKNOWLEDGMENT

The authors express their gratitude to the Renewable Energy Laboratory (REL), Department of Communications and Networks Engineering, College of Engineering, Prince Sultan University, Riyadh 11586, Saudi Arabia, for financial and technical knowledge transfer. Authors would also like to acknowledge the technical support they received from Typhoon HIL. The authors would like to acknowledge the support of Prince Sultan University for paying the Article Processing Charges (APC) of this publication.

#### REFERENCES

- [1] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg, and B. Lehman, "Step-up DC–DC converters: A comprehensive review of voltage-boosting techniques, topologies, and applications," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9143–9178, Dec. 2017.

- [2] P. K. Maroti, S. Padmanaban, S. M. Bhaskar, J. B. Holm-Nielsen, F. Blaabjerg, D. M. Ionel, and J. He, "A non-isolated inverting high gain modified new series of landsman converter," in *Proc. 45th Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Lisbon, Portugal, Oct. 2019, pp. 4077–4082.

- [3] M. Sagar Bhaskar, M. Meraj, A. Iqbal, S. Padmanaban, P. Kiran Maroti, and R. Alammari, "High gain transformer-less double-dutytriple-mode DC/DC converter for DC microgrid," *IEEE Access*, vol. 7, pp. 36353–36370, 2019.

- [4] J. Wei, K. Yao, M. Xu, and F. C. Lee, "Applying transformer concept to nonisolated voltage regulators significantly improves the efficiency and transient response," in *Proc. IEEE 34th Annu. Conf. Power Electron. Spec. (PESC)*, vol. 4. Acapulco, Mexico, Jun. 2003, pp. 1599–1604.

- [5] P. K. Maroti, S. Padmanaban, J. B. Holm-Nielsen, M. Sagar Bhaskar, M. Meraj, and A. Iqbal, "A new structure of high voltage gain SEPIC converter for renewable energy applications," *IEEE Access*, vol. 7, pp. 89857–89868, 2019.

- [6] W. Li and X. He, "Review of nonisolated high-step-up DC/DC converters in photovoltaic grid-connected applications," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1239–1250, Apr. 2011.

- [7] L.-S. Yang, T.-J. Liang, and J.-F. Chen, "Transformerless DC–DC converters with high step-up voltage gain," *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp. 3144–3152, Aug. 2009.

- [8] J. C. Rosas-Caro, J. M. Ramirez, F. Z. Peng, and A. Valderrabano, "A DC–DC multilevel boost converter," *IET Power Electron.*, vol. 3, no. 1, pp. 129–137, 2010.

- [9] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Switchedcapacitor/switched-inductor structures for getting transformerless hybrid DC-DC PWM converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 2, pp. 687–696, Mar. 2008.

- [10] Y. Tang, D. Fu, T. Wang, and Z. Xu, "Hybrid switched-inductor converters for high step-up conversion," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1480–1490, Mar. 2015.

- [11] M. S. Bhaskar, S. Padmanaban, P. Wheeler, F. Blaabjerg, and P. Siano, "A new voltage doubler based DC–DC 2LCm-Y power converter topologies for high-voltage/low-current renewable energy applications," in *Proc. IEEE Transp. Electrific. Conf. Expo (ITEC)*, Jun. 2018, pp. 1–6.

- [12] S.-M. Chen, T.-J. Liang, L.-S. Yang, and J.-F. Chen, "A cascaded high stepup DC–DC converter with single switch for microsource applications," *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1146–1153, Apr. 2011.

- [13] J. E. Valdez-Resendiz, J. C. Rosas-Caro, J. C. Mayo-Maldonado, and A. Llamas-Terres, "Quadratic boost converter based on stackable switching stages," *IET Power Electron.*, vol. 11, no. 8, pp. 1373–1381, Jul. 2018.

- [14] F. Lin Luo, "Six self-lift DC-DC converters, voltage lift technique," *IEEE Trans. Ind. Electron.*, vol. 48, no. 6, pp. 1268–1272, Dec. 2001.

- [15] D. Zhou, A. Pietkiewicz, and S. Cuk, "A three-switch high-voltage converter," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 177–183, Jan. 1999.

- [16] J.-W. Baek, M.-H. Ryoo, T.-J. Kim, D.-W. Yoo, and J.-S. Kim, "High boost converter using voltage multiplier," in *Proc. 31st Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Nov. 2005, pp. 567–572.

- [17] F. L. Luo, "Switched-capacitorized DC/DC converters," in Proc. 4th IEEE Conf. Ind. Electron. Appl., May 2009, pp. 1074–1079.

- [18] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Transformerless DC-DC converters with a very high DC line-to-load voltage ratio," in *Proc. Int. Symp. Circuits Syst. (ISCAS)*, vol. 3, May 2003, pp. 435–438.

- [19] B. Axelrod, Y. Berkovich, S. Tapuchi, and A. Ioinovici, "Steep conversion ration Cuk, Zeta, and Sepic converters based on a switched coupled-inductor cell," in *Proc. IEEE Power Electron. Spec. Conf. (PESC)*, Jun. 2008, pp. 3009–3014.

- [20] M. Antonio Salvador, T. Brunelli Lazzarin, and R. Francisco Coelho, "High step-up DC–DC converter with active switched-inductor and passive switched-capacitor networks," *IEEE Trans. Ind. Electron.*, vol. 65, no. 7, pp. 5644–5654, Jul. 2018.

**M. S. BHASKAR** (Senior Member, IEEE) received the bachelor's degree in electronics and telecommunication engineering from the University of Mumbai, Mumbai, India, in 2011, the master's degree in power electronics and drives from the Vellore Institute of Technology, VIT University, India, in 2014, and the Ph.D. degree in electrical and electronic engineering from the University of Johannesburg, South Africa, in 2019. He is currently with the Renewable Energy Laboratory,

Department of Communications and Networks Engineering, College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia. His research interests include dc/dc and dc/ac converter, high-gain converter, power electronics applications in renewable energy, and microgrid. He is also an Associate Editor of *IET Power Electronics*.

**NIKITA GUPTA** (Member, IEEE) received the B.Tech. degree in electrical and electronics engineering from the National Institute of Technology, Hamirpur, India, in 2011, the M.Tech. degree in power system from Delhi Technological University, Delhi, India, in 2014, and the Ph.D. degree from the Department of Electrical Engineering, Delhi Technological University, Delhi, in December 2018. She is currently working as an Assistant Professor with the University Institute

of Technology, Himachal Pradesh University, Shimla, India. Her research interests include power system analysis, power quality, power electronics applications in renewable energy, and microgrid.

**SIVAKUMAR SELVAM** (Member, IEEE) was born in Tamilnadu, India, in 1991. He received the B.E. degree in electrical and electronics engineering and the M.E. degree specialized in power electronics and drives from Anna University, Chennai, in 2013 and 2015, respectively. He worked as an Assistant Professor with the Saranathan College of Engineering, India, from 2015 to 2020. He is currently working as a Research Assistant with the Renewable Energy Laboratory, Prince Sultan

University, Saudi Arabia. He has authored more than ten articles in international journals and conferences proceedings. His research interests include grid interfaced solar PV systems, multilevel inverters, dc–dc converters for microgrid applications, and digital control of power converters. He is a member of IEEE Industrial Electronics Society, IEI-India, and IEANG. He was a recipient of Best Paper Award at National Conference on Automation, Robotics and Mechatronics Systems 2016, MIT Chennai.

**DHAFER J. ALMAKHLES** (Senior Member, IEEE) received the B.E. degree in electrical engineering from the King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, in 2006, and the master's (Hons.) and Ph.D. degrees from The University of Auckland, New Zealand, in 2011 and 2016, respectively. Since 2016, he has been with Prince Sultan University, Saudi Arabia. He is also the Leader of the Renewable Energy Research Team and Lab-

oratory. His research interests include power electronics, control theory, unmanned aerial vehicles, renewable energy systems, and FPGA applications.

**P. SANJEEVIKUMAR** (Senior Member, IEEE) received the bachelor's degree in electrical engineering from the University of Madras, Chennai, India, in 2002, the master's degree (Hons.) in electrical engineering from Pondicherry University, Puducherry, India, in 2006, and the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012. He was an Associate Professor with VIT University, from 2012 to 2013. In 2013, he joined the National

Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. He was an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He has authored more than 300 scientific articles. He is a Fellow of the Institution of Engineers, India, the Institution of Electronics and Telecommunication Engineers, India, and the Institution of Engineering and Technology, U.K. He was a recipient of the Best Paper Cum Most Excellence Research Paper Award from IET-SEISCON 2013, IET-CEAT 2016, IEEE-EECSI 2019, and IEEE-CENCON 2019, and five best paper awards from ETAEERE 2016 sponsored Lecture Notes in Electrical Engineering, Springer book. He is an Editor/Associate Editor/Editorial Board of refereed journals, in particular the IEEE Systems JOURNAL, the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, IEEE ACCESS, IET Power Electronics, and International Transactions on Electrical Energy Systems (Wiley), and a Subject Editor of the IET Renewable Power Generation, IET Generation, Transmission and Distribution, and FACTS journal, Canada.

JAGABAR SATHIK MOHAMED ALI (Senior Member, IEEE) was born in Thanjavur, India, in 1979. He received the B.E. degree in electronics and communication engineering from Madurai Kamarajar University, Madurai, India, in 2002, and the M.E. and Ph.D. degrees from the Faculty of Electrical Engineering, Anna University, Chennai, India, in 2004 and 2016, respectively.

He is currently a Postdoctoral Fellow with the Renewable Energy Laboratory, College of Engi-

neering, Prince Sultan University, Riyadh, Saudi Arabia. His current research interests include multilevel inverters, grid-connected inverters, and power electronics converters and its applications to renewable energy systems.

**S. UMASHANKAR** (Senior Member, IEEE) is currently with the Renewable Energy Laboratory, College of Engineering, Prince Sultan University, Saudi Arabia, and has more than 15 years of teaching, research, and industrial research and development experience. Previously, he has worked as an Associate Professor and the Head of VIT Vellore as well as a Senior Research and Development and Senior Application Engineer in the field of power electronics, renewable energy,

and electrical drives. He has published more than 250 research articles in national and international journals and conferences. He has also authored/coauthored/contributed 12 books/chapters and 12 technical articles on power electronics applications in renewable energy and allied areas. He is an Editor of *Heliyon* (Elsevier) journal.