Aalborg Universitet

## A review on IGBT module failure modes and lifetime testing

Abuelnaga, Ahmed; Narimani, Mehdi; Bahman, Amir Sajjad

Published in: **IEEE** Access

DOI (link to publication from Publisher): 10.1109/ACCESS.2021.3049738

Creative Commons License CC BY 4.0

Publication date: 2021

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

*Citation for published version (APA):* Abuelnaga, A., Narimani, M., & Bahman, A. S. (2021). A review on IGBT module failure modes and lifetime testing. IEEE Access, 9, 9643-9663. Article 9316255. https://doi.org/10.1109/ACCESS.2021.3049738

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Received December 14, 2020, accepted December 27, 2020, date of publication January 6, 2021, date of current version January 19, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3049738

# A Review on IGBT Module Failure Modes and Lifetime Testing

AHMED ABUELNAGA<sup>(0)</sup>, (Graduate Student Member, IEEE), MEHDI NARIMANI<sup>(0)</sup>, (Senior Member, IEEE), AND AMIR SAJJAD BAHMAN<sup>2</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON L8S 4L8, Canada <sup>2</sup>Center of Reliable Power Electronics (CORPE), Aalborg University, 9220 Aalborg, Denmark

Corresponding author: Ahmed Abuelnaga (abuelnaa@mcmaster.ca)

This work was supported in part by the Natural Sciences and Engineering Research Council of Canada.

**ABSTRACT** This article focuses on failure modes and lifetime testing of IGBT modules being one of the most vulnerable components in power electronic converters. IGBT modules have already located themselves in the heart of many critical applications, such as automotive, aerospace, transportation, and energy. They are required to work under harsh operational and environmental conditions for extended target lifetime that may reach 30 to 40 years in some applications. Therefore, addressing the reliability of IGBT modules is of paramount importance. The paper provides a comprehensive review on IGBT modules dominant failure modes, and long-term reliability. A detailed discussion on accelerated testing, and lifetime and degradation characterization considering thermo-mechanical stress is also presented in details.

**INDEX TERMS** Long-term reliability, IGBT failure modes, power cycling, lifetime models, degradation.

## I. INTRODUCTION

According to field experience, power electronic converters are considered a weak link that has significant influence on overall electrical system reliability [1], [2]. In wind farms [3]–[5], power electronic converters used for energy conversion are responsible for about 13% of the failures and 18% of the downtime. In utility scale PV installation [6], [7], PV inverters cause about 37% of the unscheduled maintenance events.

In an industry-based survey [7], [9], semiconductor switches and capacitors are the most vulnerable components of the power converters. Unexpected overloads and system transients are main reasons for random failures, while thermal stresses followed by mechanical vibrations then humidity are the main causes for failures caused by long-term wear-out. According to motor drive manufacturers [10]–[12], drives may end up working in tough environments, which are impossible to know before leaving the factory; thereby qualification test conditions may not match field operation. As a result, motor drive component such as power switches usually do not satisfy their specified target lifetime.

The associate editor coordinating the review of this manuscript and approving it for publication was Cristian Zambelli<sup>(D)</sup>.

IGBT lifecycle passes through different stages [13]–[16]. It starts with qualification at the IGBT manufacturer site. Then through storage and transportation stage until it reaches the power converter manufacturer's facility. The module is then assembled into the converter and the whole system is tested for converter qualification. Afterwards, the converter is transported to the customer site for commissioning and operation. Mechanical, and temperature shock events, or incorrect handling and assembly of IGBT modules may take place before site commissioning [10], [16]. This may affects module's reliability and may cause early failures. In field, IGBT modules are subjected to a multitude of stresses [1], [17]-[20]. IGBT modules may fail due to random system overstress events such as overvoltage and overcurrent. Moreover, modules may fail under sustained loading conditions due to long-term degradation caused by wear-out failure modes.

Overstress and wear-out may cause IGBT modules to reach end-of-life early before the product target lifetime, which represents a serious challenge to both power converter and IGBT modules manufacturers [21]–[24]. The power converters manufacturers invest into improved converter design, control, and protection to mitigate the effect of system overstress events and demanding mission profiles on IGBT modules. Also, IGBT modules manufacturers invest in improved modules designs to withstand against harsher operating conditions.

In order to do so; both power converter and IGBT modules manufacturers respective to their targets adopt a designfor-reliability approach. This approach is meant to consider the knowledge of field failures, failure mechanisms, and the expected operational conditions into design stage. Addressing long-term reliability and making lifetime predictions is a key element in the design-for-reliability approach. Typically, accelerated lifetime tests are used in order to study long-term reliability issues. In these tests, IGBT modules are subjected to stresses higher than typical field conditions to accelerate wear-out failure modes [25]–[28].

This article provides a comprehensive review on the failure modes and long-term reliability of IGBT modules. In the first part of paper, field failure analysis is discussed in details including random failure modes, wear-out failure modes, and the interaction between different failure modes, their root causes, and their physics-of-failure. The second part of the paper provides a detailed discussion on IGBT modules' failures, accelerated lifetime testing, lifetime modes, and degradation characterization associated to electro-thermal stresses. Since a significant portion of IGBT modules' field failures are attributed to extensive electro-thermal stresses due to temperature cycling [1], [17]–[20]. The paper is organized as follows. To recap the underlying physics-of-failure, a brief review on the IGBT module's structure including chip and package is presented in section II. In section III, IGBT module failure analysis is discussed comprehensively. Section IV reviews IGBT modules' failures and reliability issues associated to electro-thermal stresses. Discussion on accelerated testing platforms is covered in section V. Section VI goes through detailed examination of long-term reliability characterization through accelerated testing. Then, section VII scrutinizes the concept of separation of failure modes. Section VIII concludes and discusses the challenges and trends.

#### **II. IGBT MODULE STRUCTURE**

## A. IGBT CHIP

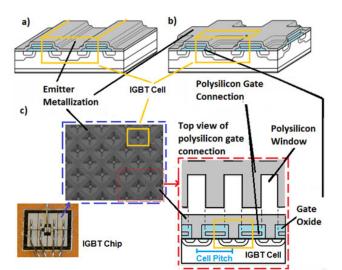

Typically, an IGBT chip or die is composed of several cells per chip area spaced by cell pitch [29]. The cell pitch and the number of cells per chip area determine the current density of the IGBT chip. Fig. 1 shows planar gate IGBT cells integrated to form a chip. Fig. 1a and 1b show linear and square-meshed polysilicon gate-connection layout, respectively. Gate-connection layout determines how multiple IGBT cells per unit area are connected together in parallel. Factors such as current density, cell technology, cell performance, and manufacturing affect the choice of gate. The interconnection of IGBT cells forms the active area of the device as shown in Fig. 1c. The polysilicon gate connections running across the chip underneath the emitter gate bonding pads are required to connect the gate terminal to external gate driver circuit.

FIGURE 1. Cells layout [29]: a) linear gate connection, b) squared mesh gate connection, c) active area in zoom-in view.

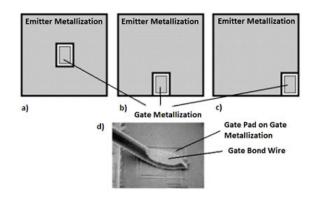

FIGURE 2. Gate metallization layout: a) centric b) edge, c) corner, d) gate metallization in zoom-in view [29].

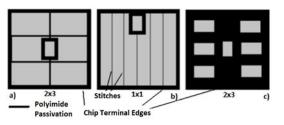

Fig. 2a, 2b, and 2c show possible gate pad layouts. Fig. 2d shows aluminum gate bonding. The gate pad layout is determined based on the bond wire scheme used in the IGBT module design and it has an impact on the switching performance of the IGBT chip. The emitter metallization is made from aluminum alloy for aluminum wire bonding to form an electric connection between emitter and an external terminal. Most of the emitter metallization designs consider multiple bonding pads ordered in a matrix formation  $(1 \times 1, 2 \times 2, 2 \times 3, 2 \times 3)$  $2 \times 4$  etc.) as shown in Fig. 3. The main reason behind having several emitter bonding designs is to ensure uniform current distribution on the emitter metallization and the bond wires, thereby, preventing the formation of hotspots [30]. On the other side of the chip, the collector metallization has three roles. First, it works as electrical connection between the collector and the package. Second, it acts as thermal interface between the die and the package [23]. Third, it functions as an adhesion layer between chip and the solder layer which is used to attach the chip to the package. Extra layers are added to the backside metallization to protect the die from

FIGURE 3. Common emitter metallization layouts [30].

contamination either by diffusion of particles coming from the solder or oxidation [23].

## B. IGBT STANDARD MODULE

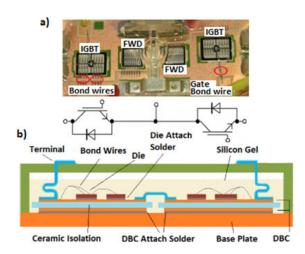

In IGBT modules, several IGBT chips and free-wheeling diode (FWD) chips are packaged together. One reason is to form new power electronic building blocks such as chopper, half-bridge, six-pack, etc. Another reason is to achieve higher current carrying capability through optimal paralleling IGBT cells and FWD cells of lower current carrying capability inside the module. In addition, the package provides electrical conduction paths between the IGBT/FWD chips and the external circuitry. Also, it transfers heat generated at the chips to a heat sink. Moreover, it provides a means for mechanical mounting and protection against environment.

Fig. 4a shows the architecture of a standard 34 mm IGBT module [31]. The module forms a half-bridge connection. Fig. 4b presents structure of the IGBT module [21]–[24]. The metallization layers on the top side of IGBT/FWD chips (dies) are connected to the top copper layer of DBC (direct bonded copper layer) through aluminum bond wires. This copper layer serves as power track to connect devices to each other and to module terminals. The metallization layers on the bottom side of the chips are soldered to the top copper layer of DBC. These solder layers are called die attach or chip attach which serves three functions. First, it conducts

FIGURE 4. Power Module [31]: a) internal view of standard 34mm IGBT half bridge module, b) the structure of standard 34mm IGBT half bridge module.

current from the chips to top copper layer of DBC. Second, it transfers heat from the chips to DBC. Third, it fixes the chips into the DBC. DBC consists of two copper layers sandwiching a ceramic layer to provide electrical isolation between the chips and the base plate. DBC is soldered to a copper base plate. This solder layer is called DBC attach which serves two functions. First, it transfers heat from DBCs to the base plate. Second, it fixes DBCs to the base plate that is mounted on a heat sink [22], [23], [30], [32]. On mounting the module on the heat sink, thermal interface layer (TIM) is used to improve the thermal conductivity of the base plate to heat sink interface.

## **III. IGBT MODULE FAILURE ANALYSIS**

As illustrated in the previous section, IGBT modules are complex structures of different material layers, which are brought together to form the chip and the package. Therefore, the failure of IGBT module is linked to many possible failure modes. However, there are dominant failure modes to which most of the failures are related. These failure modes can be categorized into two main groups: failure modes associated to chips and failure modes related to the package as shown in Table 1.

## A. CHIP-RELATED FAILURE MODES

Chip-related failure modes can be further grouped into failures caused by overstresses and wear-out failures.

## 1) OVERSTRESS FAILURE MODES

Overstress failure modes are mainly due to events such as gate overvoltage, collector-emitter overvoltage, overcurrent, burnout due to cosmic rays [21], [34]. These events may cause bond wire lift-off or rupture, latch-up, loss of block-ing capability, rapid rise in junction temperature (thermal runaway) due to energy shocks (high-energy dissipation), secondary breakdown in the inherent BJT structure of the IGBT [35], [41], [42]. These modes may destroy IGBT chips. Although in some cases, they cause the IGBT to show up as an open circuit, in majority of the cases IGBT ends to be a short circuit [23], [24], [35], [41], [42].

#### 2) WEAR-OUT FAILURE MODES

The most common IGBT chip wear-out failure modes are Time Dependent Dielectric Breakdown (TDDB), and Hot Carrier Injection (HCI) [33], [34]. Both failure modes cause deterioration to the gate-oxide-layer characteristics. Nonetheless, according to [33], [34], these failure modes were considered an issue for IGBT in its old days and have not been issue anymore.

Another important wear-out failure mode is electrochemical migration. In humid environments, under high voltage and temperature, electro-chemical migration at chip passivation layer and terminal structure cause an increase in leakage currents and gradual loss of blocking capability [36]–[40], [43]. Due to the importance of TDDB and

|                          |                                           |                                            | a =                                                                   |

|--------------------------|-------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------|

|                          | Overstress<br>[18, 19, 20,<br>21, 23, 35] | Gate overvoltage (Voltage breakdown)       | System Effects:                                                       |

|                          |                                           | Overvoltage (Voltage breakdown)            | <ul> <li>Open circuit faults</li> </ul>                               |

|                          |                                           | Overcurrent                                | - Short circuit faults (Majority of the                               |

| Chip-related             | 21, 25, 55]                               | Cosmic rays burnout                        | cases)                                                                |

| Failure Modes            |                                           | Time dependent dielectric breakdown (TDDB) | System Effects:                                                       |

| Fanure modes             | Wear-out                                  | Hot carrier injection (HCI)                | - Mal-operation of gate drivers &                                     |

|                          | [23, 33,                                  |                                            | switches.                                                             |

|                          | 36-40]                                    | Electro-chemical migration                 | <ul> <li>Loss of chip's voltage blocking</li> </ul>                   |

|                          | _                                         |                                            | capability                                                            |

|                          |                                           | Mechanical shock and stresses              | System Effects:                                                       |

|                          | Overstress<br>[23, 24,<br>34]             | Thermal shock                              | <ul> <li>Open, or short circuit faults</li> </ul>                     |

|                          |                                           | Thermai shoek                              | <ul> <li>Accelerate wear-out</li> </ul>                               |

| Destaura                 |                                           | Thermal runaway                            | - Melting & Burnouts (More common in                                  |

| Package-                 |                                           | & Flashovers                               | harsh environments)                                                   |

| related<br>Failure Modes | Wear-out                                  | Thermo-mechanical fatigue                  | System Effects:                                                       |

| ranure would             |                                           | Thermo-mechanical creep                    | - Thermal issues (Majority of the cases).                             |

|                          | [23, 24,                                  | Electro & electro-chemical migration       | - Stray (leakage) current issues.                                     |

|                          | 34,36-40]                                 | Insulation degradation                     | <ul> <li>Loss of module's voltage blocking<br/>capability.</li> </ul> |

#### TABLE 1. IGBT failure mode classification.

electro-chemical migration since the dawn of IGBT, standard reliability demonstration tests have been designed to address them [23], [43].

## **B. PACKAGE-RELATED FAILURE MODES**

Thermal shocks, mechanical shocks and stresses, and thermal runaways are the main causes of overstress packagerelated failures. For example, mechanical shock can cause degradation of package's internals, which compromises voltage blocking capability resulting in voltage breakdown [44], Another important cause for package overstresses is thermal runaway, that may occur under high temperature, resulting in melting of package interconnects [23], [24], [34]. In addition, in humid and contaminated environments, burnouts due to flashovers are more common [23], [24].

On the other side, thermo-mechanical fatigue, thermomechanical creep, electro-migration, and corrosion are the main causes of wear-out package-related failure modes [24], [34], [45]. Because of different coefficients of expansion between the package materials, temperature cycling inside the package results in thermo-mechanical fatigue. As a result, bond-wire cracks and lift-off; delamination and cracking of solder layers; and degradation of chip metallization may occur [34], [46]. Thermo-mechanical creep, caused by high operating temperature, leads to weakening of the mechanical strength of different package layers. This accelerates the process of cracks and voids formation [34], [47]. High currents cause electro-migration in bond wires and metallization layers, which leads to creation of voids and hot spots [34], [48]. High levels of humidity and corrosive chemicals existing in many industrial applications, e.g., mining, cement, oil and gas, and marine, may result in corrosion of bond wires accelerating their mechanical degradation, and eventually leading to their rupture [24], [34], [36]. In addition, humidity severely degrades the insulation characteristics of module encapsulation materials such as Si-gel [36].

## C. FIELD FAILURE ANALYSIS

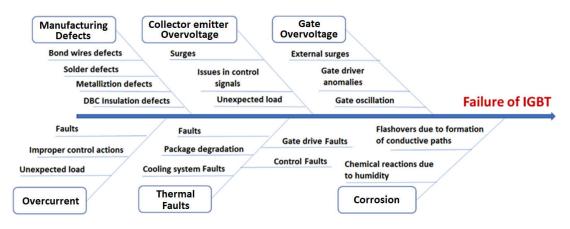

According to [1], [18] and the previous discussion, IGBT modules are described as one of the most vulnerable components in the power converters. However, "vulnerable" does not indicate inherent weakness, it indicates that power converter faults usually end to show up as IGBT modules' failures. Fig. 5 shows fishbone diagram representing field failures of IGBT modules [4], [20]–[24]. IGBT modules' field failures can be linked to manufacturing defects including chip defects, and module defects such as bond wire, solder, metallization, and insulation defects. Use and environmental conditions accelerate the latent defects into the failures [20]–[24].

Collector-emitter overvoltage may take place due to surges, control signal and measurement signal anomalies, and unexpected load condition [20], [24], [35]. Gate overvoltage may happen due to external surge, gate driver anomalies, and gate oscillation especially during short circuits [20], [24], [35], [37]. Overcurrent may occur due to internal or external faults, improper control actions, and unexpected load events [20], [24], [35].

In addition to overvoltage and overcurrent, thermal issues play a significant role in IGBT modules' field failures. They compromise both short-term and long-term reliability of IGBT modules depending on their magnitude. Energy shocks, thermal runaway, or secondary breakdown destroy IGBT modules in a short time scale [35], [49], [50].

Elevated operation temperatures and temperature cycling result in long-term issues such as the degradation of module interconnections, solder layers, and insulation layer [34], [45]–[47]. These thermal stresses may show up at the IGBT module due to defects in the cooling system design,

FIGURE 5. Fishbone diagram categorizing causes of field failures of IGBT modules.

improper operation of the cooling system, degradation of the thermal interface layer (TIM), improper gate voltage, gate open circuit, and abnormal switching speeds [51].

Corrosion driven by field environmental conditions is another important cause of IGBT modules' failures [34], [36]–[40]. Insufficient protection of the converter hardware against the environment leads to the build-up of salt traces and other conductive formations on IGBT module terminals and gate driver boards. They may cause flashovers and improper operation of gate driver. In addition, external particles assisted by humidity may get into IGBT modules and react with the internals, resulting in long-term degradation.

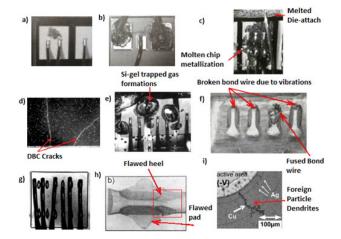

Fig. 6 presents samples of defective or failed IGBTs. Fig. 6a shows overvoltage failure. It causes a melting spot in the metallization where loss of blocking capability takes place. However, if loss of blocking capability associated with overvoltage results in overcurrent, wider scale melting happens. Fig. 6b shows large melting spots in metallization localized next to bond wires caused by overcurrent failure. In Fig. 6c, large scale melting of chip metallization and die-attach solder due to thermal runaway caused by high-energy dissipation during the fault. Fig. 6d shows cracks formed in DBC ceramic due to bending stress, which can arise from pressing the module's bowed base plate onto a flat heat sink. The development of these cracks eventually results in insulation failures. Fig. 6e shows gas bubbles formation in Si-gel under chip heating. This can lead to insulation failure due to Si-gel degradation, or the trapped gases can lead to aluminum corrosion. In Fig. 6f, weaker bond wires broke due to vibrational forces, while remaining bond wires fused due to current crowding. In Fig. 6g, bond wire lift-off took place under thermos-mechanical stresses. Fig. 6h shows defected bond wires due to manufacturing flaws, which compromises IGBT modules' reliability under thermo-mechanical stresses. Fig 6i shows IGBT chip passivation degradation due to electro-chemical migration. This reduces chip voltage blocking capability, and eventually, results in voltage breakdown. The following sections focus on long-term reliability issues

FIGURE 6. A sample of IGBT modules' field failures [23], [34], [40]: a) overvoltage, b) overcurrent, c) over-temperature, d) cracks in the ceramic layer due mechanical stresses, e) gases bubbles in Si- gel due to surface corrosion, f) cut-off of bond wires due to vibration, g) bond wire lift-off due to thermo-mechanical fatigue, h) defective IGBT module interconnections, and i) chip passivation degradation.

arising in the packages due to thermal stresses common in most applications.

## **IV. IGBT MODULE SUBJECTED TO THERMAL STRESSES**

## A. ANALYSIS OF THERMAL STRESSES IN MODULES

In normal operation, IGBTs keep switching between on and off states. Conduction and switching power losses associated with IGBT operation generate pulsating heat flux at the chip (junction). The repetitive heating and cooling of the junction results in temperature cycling. This temperature cycling caused by actively heating and cooling of the junction is called power cycling, while temperature cycling due to passive heating and cooling is called thermal cycling.

The heat flux produced at the junction flows through the thermal path across the different layers of the IGBT module towards the case (or heat sink). Since different layers of the IGBT module have different thermal conductivity and capacitance as shown in Fig. 7, a temperature gradient along the thermal path takes place.

|                    | Material                       | Conduct<br>-ivity<br>(W/mK) | Capacit<br>-ance<br>(J/kgK) | CTE<br>(10 <sup>-6</sup> /K) | IGBT<br>Thermal Network |  |

|--------------------|--------------------------------|-----------------------------|-----------------------------|------------------------------|-------------------------|--|

| Bond<br>wire       | Al-Alloy                       | 220                         | 896                         | 23                           |                         |  |

| Metalli-<br>zation | Al-Alloy                       |                             |                             | 25                           | Silicon Die             |  |

| Chip/Die           | Si                             | 100                         | 741                         | 3                            | 4                       |  |

| Die<br>attach      | Solder                         | 28                          |                             | 57                           | Copper (DBC)            |  |

| DBC<br>attach      | SnAg<br>3.5                    | 20                          |                             | 57                           | Copper (Baseplate)      |  |

| DBC<br>layer 1     |                                |                             |                             |                              | Heat Sink               |  |

| DBC<br>layer 2     | Cu                             | 380                         | 381                         | 17                           | Ĭ I                     |  |

| Base<br>plate      |                                |                             |                             |                              | To Amblent              |  |

| DBC                | Al <sub>2</sub> O <sub>3</sub> | 25                          | 850-10 <sup>3</sup>         | 8                            | ‡→τ <sub>a</sub>        |  |

| Ceramic            | AIN                            | 180                         | 700-760                     | 5                            |                         |  |

FIGURE 7. Typical thermal properties of standard package materials and thermal network model of an IGBT [23].

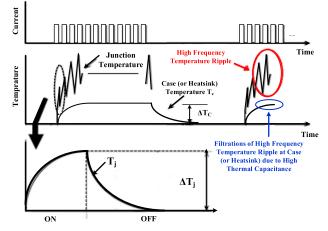

Fig. 8 shows the temperature cycles at the junction and the case under power cycling. At the junction, average and the peak-to-peak temperature fluctuations are higher than that at the case. The thermal capacitance along the thermal path has a filtering effect on high frequency temperature fluctuations. Therefore, high frequency heating and cooling cause temperature fluctuations that increase in magnitude near the junction, and decrease near the case. On the other hand, the filtering nature of the thermal path is ineffective in front of the low frequency heating and cooling causing temperature fluctuations to be uniform throughout the thermal path as illustrated in Fig. 8. This filtering nature has a significant influence on the long-term reliability of the thermal path, which will be addressed later in section V.

**FIGURE 8.** Temperature fluctuations at the junction and the case under repetitive heating and cooling of the junction [24].

Temperature fluctuations along the thermal path cause repetitive expansion and contraction of the layers forming the path. Due to the difference in the coefficient of thermal expansion (CTE) between adjacent layers in the package as shown in Fig. 7, shear stresses are exerted on

9648

interfaces between different material layers. These stresses result in thermo-mechanical fatigue of material layers of the package.

According to [52], even a package with identical CTE values in each layer would not be stress-free in the presence of a temperature gradient. It is impossible theoretically to design a stress-less package for the whole range of operation conditions. However, it is possible to optimize the selection of the materials properties of the adjacent layers to reduce stresses according to application requirements. For example, industrial modules typically use aluminum oxide as the ceramic layer and use copper base plates [23], [53]. To cope with higher thermal stresses and to account for more stringent reliability requirements, traction modules use aluminum nitride as the ceramic layer and aluminum silicon copper alloy for base plate [23], [53]. These material choices reduces the mismatch in the CTE along the thermal path [53]. However, this comes at the expense of more complex manufacturability and higher costs.

New interconnection and soldering technologies have been proposed by IGBT module manufacturers to improve long-term reliability of the module [54]–[60]. Some of these innovations are Copper bond wire, metallization and diffusion soldering used in .XT technology from Infineon [61]; and Al-clad Copper bonds, and silver sintering, baseplate-free in SKIM technology from Semikron [62]. The focus is not to produce a stress-free modules, their focus is to postpone the onset of degradation caused by thermo-mechanical fatigue beyond application lifetime requirement given the operation conditions.

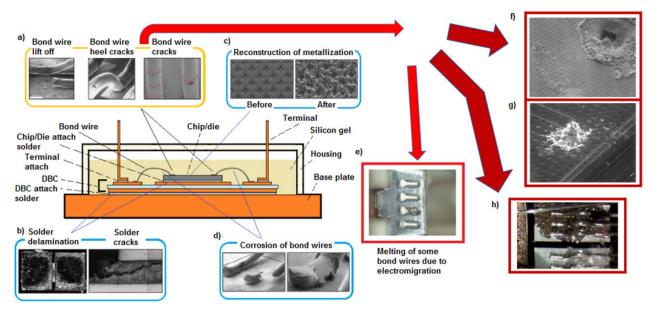

## B. MODULE FAILURE MODES DUE TO THERMAL STRESSES

Fig. 9 shows the interaction between several thermomechanical failure modes. These failure modes degrade the mechanical structure of the package and eventually cause IGBT module to fail [20], [21], [63]–[68]. Peak-to-peak temperature fluctuation at the junction degrades the bond wires due to fatigue as seen in Fig. 9a. Consequently, bond wire liftoff, heel cracks, or pad cracks take place depending on several factors including the geometry of the bond wires and the inherent manufacturing defects [34], [63]. Bond wire degradation results in increase of IGBT module collector-emitter voltage during on state due to the increase of the equivalent resistance of bond wires after the lift-off of some of them. This raises power losses, which increases the peak-to-peak temperature fluctuation at the junction causing an acceleration in degradation.

Bond wires fatigue is not a strong function of maximum or mean junction temperature. Conversely, solder degradation, metallization degradation, and bond wire stress corrosion depend strongly on junction temperature. Solder degradation is driven by temperature cycling [46], [47], [68], [69]. It either takes the form of solder cracks or solder delamination as shown in Fig. 9b. When solder temperature exceed its homologous temperature (2/5 of the solder melting point) [67], [70],

FIGURE 9. IGBT module degradation and related failures under thermal stresses [23], [34], [63]: a) bond wire degradation, b) solder degradation, c) metallization degradation, d) stress corrosion of bond wires, e) melting due to electro-migration, f) localized melting of the metallization near bond wire pads due to current crowding, g) localized melting of metallization due to hot stops formation, h) melting of metallization due to over temperature.

creep failure mechanism causes localized plastic deformation in sporadic sites. These creep sites lose strength as time proceeds accelerating the growth of micro cracks under cyclic loading, and eventually lead to solder cracks or solder delimitation. In addition to temperature value, temperature fluctuation frequency assists creep action accelerating solder degradation.

Metallization degradation takes the form of metallization reconstruction as shown in Fig. 9c. Due to the temperature cycling, tensile or compressive forces are imposed on the thin metallization layer due to the difference between the CTE of the chip and the metallization. According to [71]–[73], plastic deformation due to creep is the reason for reconstruction. There are three creep mechanisms, which are referred to as diffusion, gain boundary sliding, and dislocation creep in action. Each of these mechanisms is activated depends on certain factors including temperature. Reconstruction is more severe under elevated junction temperatures. The main consequence of reconstruction is the increase of metallization resistance raising the IGBT module's collector-emitter on-state voltage.

Corrosion of bond wires, shown in Fig. 9d, takes place due to the attack of traces of external chemicals on bond wires under elevated junction temperature. As a result, corrosion of the bond wire and their bond pads occur. Another corrosion mechanism called stress corrosion cracking do happen in bond wires under tensile stress. In this mechanism, cracks growth is driven by chemical reaction under sustained tension stress and elevated temperatures. First, it results in an increase in bond wire resistance and finally causes breaking of the bond wire. In both corrosion mechanisms, disruption of the current distribution occurs [34], [74].

VOLUME 9, 2021

#### C. INTERACTIONS BETWEEN FAILURE MODES

In real case situation, failure modes compete against and interact with each other to accelerate module degradation [21], [34], [75]-[78]. For example, solder degradation competes with bond wire degradation [34], [77]. The degradation of solder layer deteriorates the integrity of the thermal path causing an increase in thermal resistance. If the solder layer degradation dominates, the peak-to-peak fluctuation of the junction temperature will increase in a way that accelerates the degradation of the bond wire and accelerates the degradation of the solder as well. Failure modes keep accelerating one another until the complete deterioration of the package. Assuming a perfect solder layer that does not degrade, still the bond wires degrades due to temperature cycling. However, bond wire lift-off will start after a considerable time compared to the case when both bond wire degradation and solder degradation are present.

Another example is about the interaction between metallization degradation and bond wire degradation [35], [77]. Metallization degradation raises the resistance of the metallization leading to the increase of IGBT module collector-emitter on-state voltage. Consequently, power losses generated inside the junction increase raising the magnitude of the peak-to-peak temperature fluctuation. This in turn accelerates the bond wire degradation, which further elevates the junction temperature accelerating metallization degradation. In the end, this vicious cycle destroys the package mechanical structure. This concept of interaction and isolation of failure modes is discussed in more details in section VII.

As shown in Fig. 9, degradation of the bond wires, solder, and metallization eventually leads to more serious

consequences. Bond wire lift-off, heel cracks, or corrosion raises the current density in the intact bond wires. High current densities may cause electro-migration in the bond wires, which results in resistance increase of the intact bond wires. This gives rise to hot spots and finally leads to the melting of the bond wire as shown in Fig. 9e. Instead of the formation of the hot spots in the bond wires themselves, local hot spots may form at the bond wire pads. As a result, melting of the metallization near the intact bond wire takes place as seen in Fig. 9f. Another possibility for the formation of the local hot spots is shown in Fig. 9g, in which the current distribution formed by interaction of bond wire degradation and metallization reconstruction results in sporadic melting across the metallization. The damage shown in Fig. 9h may happen, when junction temperature reaches a level at which wide spread melting of the metallization layer starts. This may happen mainly due to severe degradation of the solder, however, it may also be caused due to wide scale metallization reconstruction.

## **V. ACCELERATED TESTING**

#### A. POWER CYCLING TESTS

In order to assess long-term reliability of IGBT modules, accelerated testing is required to achieve the equivalent degradation, which may take many years in the field, in few days in lab setting [21]. Semiconductor manufacturers set reliability demonstration tests to display long-term reliability of their IGBT modules. Table 2 presents a selection of tests for standard IGBT modules to verify the long-term reliability under thermal stresses according to IEC 60749-34 [21], [23]. Power cycling tests (PCTs) can be grouped into PCT<sub>sec</sub> in which the temperature cycling period  $(t_{cycle})$  is set in the range of few seconds, and PCT<sub>min</sub> in which t<sub>cycle</sub> is in the range of few minutes. PCT<sub>min</sub> is referred to as thermal cycling (TC) if the package is heated and cooled passively in a temperature chamber. Due to thermal capacitance of layers, few seconds are required to heat the core while few minutes are required to heat outer layers of the package as discussed in section IV. As a result, PCTsec are intended to assess the reliability of bond wires, die attach solder,

| TABLE 2. Reliabili | ty demonstration | for thermal | stresses | [21], [23]. |

|--------------------|------------------|-------------|----------|-------------|

|--------------------|------------------|-------------|----------|-------------|

| Testing                                 | Condition/Criteria                                                                                                                                                              | Failure Site                                                                                                   |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Thermal cycling $(t_{cycle} \sim mins)$ | Internal heating,<br>$\Delta T_j = 50\text{-}100\text{K},$<br>$T_{j,\text{max}} = 150^{\circ}\text{C},$<br>$t_{\text{on}} > 15 \text{ sec},$<br>$R_{\text{th}}$                 | <ul> <li>Bond wire</li> <li>Die attach<br/>solder</li> <li>DBC attach<br/>solder</li> <li>TIM layer</li> </ul> |

| Power cycling $(t_{cycle} \sim secs)$   | Internal heating,<br>$\Delta T_{j} = 50\text{-}100\text{K},$<br>$T_{j,\text{max}} = 150^{\circ}\text{C},$<br>$t_{on} < 5 \text{ sec},$<br>$V_{CE,\text{sat}}$ , $R_{\text{th}}$ | <ul> <li>Bond wire</li> <li>Die attach<br/>solder</li> </ul>                                                   |

and metallization.  $PCT_{min}$  or TC are intended to assess the reliability of DBC attach, ceramic insulation, and mechanical assembly [21], [23], [75]–[77].

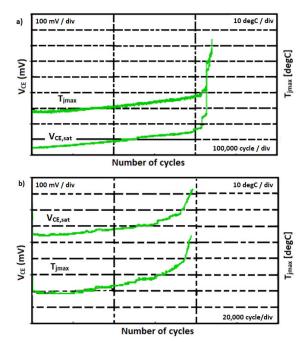

In order to keep track of degradation, degradation precursors are monitored. IGBT module collector-emitter on state (saturation) voltage is utilized as a precursor for bond wires degradation. Collector-emitter saturation voltage  $(V_{CE}, sat)$ measured at the IGBT module terminals is composed of IGBT chip collector-emitter saturation voltage and the voltage drop on the modules interconnects including bond wires and emitter metallization. As bond wires degrade, their equivalent resistance increases. This raises the collector-emitter saturation voltage  $(V_{CE}, sat)$  measured at the IGBT module terminals. IGBT chip collector-emitter saturation voltage is not affected directly by packaging degradation. However, it is affected by the increase in junction temperature caused by packaging degradation. For solder degradation, thermal resistance  $(R_{th})$  is used as a precursor. The capability of solder layer to transfer heat from the chip to the base plate reduces in case of solder degradation, which is equivalent to the increase of overall  $R_{\rm th}$ . It should be noted that a degradation in the thermal interface layer (TIM) increases the overall  $R_{\rm th}$  as well. For gate oxide degradation either gate current  $(I_g)$  or gate threshold voltage (Vth) are used as precursors. End-oflife is reached if  $V_{CE,sat}$  increases by 5%;  $R_{th}$  increases by 20%;  $I_g$  and  $V_{th}$  increase by 20% with respect to the initial healthy conditions [21], [23], [78]-[85].

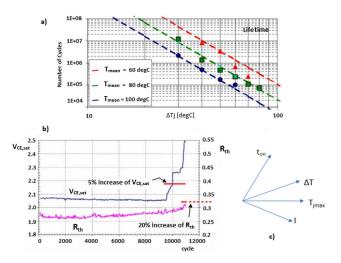

In addition to reliability demonstrations, power cycling tests may be performed to study lifetime (number of stressor's cycles to a degradation limit for a given stressor level) and degradation modeling (evolution of degradation precursors with stressor's cycles under given stressor level) as seen in Fig. 10a and 10b, respectively, under a multitude of lab emulated stresses. Focusing on thermo-mechanical degradation, the stressor variable space is multidimensional including  $\Delta T_i$ ,  $T_{imax}$ ,  $t_{on}$ , I, etc. as shown in Fig. 10c [21], [78].

**FIGURE 10.** Accelerated tests: a) number of cycles to failure (time to failure) as a function of  $\Delta T_j$  [78], b) variation of degradation precursors as a function of number of cycles [78], c) stressor variable [21], [78].

However, it should be noted that these variables are not independent. For example, increasing  $t_{on}$  raises the  $\Delta T_j$ . Therefore, attention should be paid while setting test conditions to account for correlation of test variables.

Another important aspect of performing accelerated test for lifetime and degradation modeling is the use of stresses similar to, but higher in magnitudes than, stresses experienced by the component in the field. The purpose of applying the stresses is to accelerate one of the dominant failure modes that are seen by the component in the field.

Irrelevant stresses, either different from or of very high magnitude compared to expected field stresses, may give rise to failures that are not dominant in the field [15], [21].

## **B. POWER CYCLING PLATFORMS**

In general, there is no standard architecture for power cycling tests [21], [86]–[89]. However, power cycling test platforms can be categorized into two main groups: DC and AC power cycling tests [90]–[92]. Table 3 compares between DC and AC power cycling tests.

In DC power cycling platforms, DC current injection induces thermal stress by forming a thermal flux in the module due to IGBT conduction losses only. In this test platform, IGBT module is kept turned on by supplying constant gate voltage, for instance 15 Volts. The required IGBT module collector current is periodically changed between zero and *I* with period  $t_{cycle}$  and duty cycle  $t_{on}/t_{cycle}$ . This is achieved by controlling the output voltage of the power supply connected between the collector and emitter terminals of the IGBT module, so that the required supply current is set. In addition to the main power supply, an auxiliary supply is required to flow a milliampere current through IGBT device collector for junction temperature estimation as will be discussed later in this section.

On the other side, in AC platforms, the IGBT is switched on and off repeatedly against high voltage, through imposing a PWM voltage signal to its gate terminal. Both conduction and switching losses generated in the junction creates a heat flux in the module resulting in thermal stresses. A possible implementation of AC testing platform comprises of two half bridge modules connected in H-bridge topology. Given the inductive load, the H-bridge is controlled to provide a sinusoidal current with fixed amplitude for time  $t_{on}$  and zero for  $t_{off}$ .

In comparison to DC platforms, AC platforms generate temperature cycles based on more realistic electrical stresses in power devices as they involve both conduction and switching losses and not only conduction losses. In addition, both IGBT and FWD losses contribute to the heating process, in contrast to DC test in which only IGBT losses contribute to the heating, which affects the temperature distribution inside the module. However, DC platforms are simple to set up, and more importantly, the monitoring of degradation precursors is much easier to implement. That is why semiconductor manufacturers adopt DC platforms, and most of the work on lifetime testing and degradation studies have been

VOLUME 9, 2021

done using DC platforms [21], [23]. Accordingly, the focus of this article is on DC power cycling test. This does not mean that there is no interest in AC-based platforms. In fact, researchers are interested in AC platforms to study the effect of realistic electrical stresses on degradation and to compare to the degradation in case of using DC platforms. This is important for the verification of models generated from DC platforms [21], [28], [90], [91].

## C. DC POWER CYCLING TESTS

In DC power cycling tests, as mentioned previously, IGBT current is switched on and off through an external circuit to produce repetitive heating and cooling in a constantly turned on IGBT. Additionally, in order to keep track of package deterioration, degradation precursors ( $V_{CE, \text{sat}}$ ,  $R_{\text{th}}$ , and  $I_{\text{g}}$ ) and test variables such as  $T_i$ ,  $\Delta T_i$ , and  $T_C$  need to be monitored.

## 1) TEMPERATURE ESTIMATION

There are several means to detect junction temperature including IR cameras, chip-embedded temperature sensors, etc. [93]–[100]. Nonetheless, more commonly, temperature sensitive electrical parameters (TSEPs) are used to estimate junction temperature without the need to specialized sensors. There are several candidates to employ as TSEPs such as collector-emitter saturation voltage, gate current, gate threshold voltage, etc [93]–[96].  $V_{CE,sat}$  is highly sensitive to temperature and relatively easy to measure, therefore, it is used frequently for estimating junction temperature.

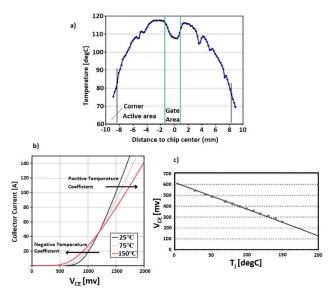

Fig. 11a illustrates a typical temperature distribution across the chip. On using embedded temperature sensors, the position of the sensor on the chip affects the temperature measurements. Usually sensors are embedded in vicinity of gate

**FIGURE 11.** Junction temperature estimation through VCE<sub>sat</sub> [21]: a) Temperature distribution across the chip, b) Relation between V<sub>CE</sub> and collector current for 1200V 150A Trench field stop IGBT, c) Linear relationship between V<sub>CE,sat</sub> and temperature under milliampere range collector current excitation.

## TABLE 3. Power cycling platforms.

|                                                                 | DC Platforms                                                                                                                                                                                              | AC Platforms                                                                                                                                                                                                                           |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Cycle<br>[77, 91]                                         | 140<br>120<br>100<br>100<br>100<br>100<br>100<br>100<br>10                                                                                                                                                | Load Current<br>100<br>100<br>100<br>100<br>100<br>100<br>100<br>10                                                                                                                                                                    |

| <b>Circuit Setup</b><br>[90, 91]<br>(DUT: Device under<br>Test) | Load<br>Current<br>Current<br>Constant Gate<br>Voltage                                                                                                                                                    | Supply<br>Voltage<br>Wodule 1<br>Hodule 2<br>Inductive<br>Load<br>Current Control                                                                                                                                                      |

| Heating &<br>Stress [27, 63]                                    | <ul> <li>Conduction losses</li> <li>No switching and high voltage applied</li> <li>Higher current than typical application levels<br/>are required to achieve a given power loss</li> </ul>               | <ul><li>Conduction Losses and Switching Losses</li><li>Reproduce real application scenarios</li></ul>                                                                                                                                  |

| Device under<br>heating[27]                                     |                                                                                                                                                                                                           |                                                                                                                                                                                                                                        |

| Precursors [27]                                                 | $(V_{CE,sat}, R_{th}, I_g)$ , Easier to Implement,                                                                                                                                                        | $(V_{CE,sat}, R_{th}, I_g)$ , More Challenging to implement                                                                                                                                                                            |

| Junction<br>temperature<br>monitoring [63]                      | $V_{CE,sat}$ measurement with low current after<br>thermal calibration)<br>$T_j$<br>$T_j$<br>$T_{jmax}$<br>$T_{jmax}$<br>$T_{jmax}$<br>$T_{jmax}$<br>$T_{jmax}$<br>$T_{jmax}$<br>$T_{jmax}$<br>$T_{jmax}$ | V <sub>CE,sat</sub> measurement with low current after thermal calibration)                                                                                                                                                            |

| Precursors<br>measurement<br>[27]                               | <ul> <li>Performed every cycle.</li> <li>Structure function estimation performed every<br/>few thousand cycles (from 1000 to 5000,<br/>depending on the ageing process).</li> </ul>                       | <ul> <li>Performed every few thousand cycles (from 1000 to 5000, depending on the ageing process)</li> <li>PWM stopped and the high-voltage source disconnected.</li> <li>A circuity for accurate low-level signals is used</li> </ul> |

| Test Results<br>[27, 101-103,<br>104]                           | Die attach<br>degradation<br>Bondwire Liftoff<br>Number of Cycles                                                                                                                                         | Metallization<br>Damage<br>Number of Cycles                                                                                                                                                                                            |

area, so they detect the temperature values at the gate area. For temperature estimation based on  $V_{CE,sat}$ , the measured value of temperature is equivalent to the average temperature across the chip area [99-99]. This average temperature value is commonly referred to as virtual junction temperature as shown in Fig. 11a. From now onwards, any reference to junction temperature is intended to indicate virtual junction temperature. In addition to the high sensitivity of  $V_{CE,sat}$  with respect to temperature, it is sensitive to collector current.

Fig. 11b presents the relationship between  $V_{CE,sat}$  and collector current. In order to isolate the effect of collector current on temperature estimation,  $V_{CE,sat}$  measurement for temperature estimation should be done at very low collector current. This is achieved by sending milliampere range sense current during junction temperature estimation. This current depends on the IGBT's structure and size. Another reason for this milliampere range is that the IGBT is to be operated under the knee of its IV characteristics as shown in Fig. 11b. This guarantees a linear relationship between the junction temperature and measured  $V_{CE, sat}$  as shown in Fig11.c. This relationship between temperature and VCE, sat is derived during the calibration process. At calibration, the IGBT module under test is kept in a temperature-controlled environment,  $V_{CE,sat}$  is measured at different temperature set points while injecting the sense current into the IGBT module under test.

In addition to junction temperature,  $T_C$  is required for controlling test conditions and the estimation of  $R_{\text{th}}$ . Commonly PT100 sensors or thermocouples are used to measure  $T_C$  [21].

## 2) DEGRADATION PRECURSORS ESTIMATION

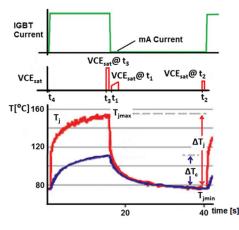

Fig. 12 presents a typical measurement sequence per heatingcooling cycle required to estimate degradation precursors  $(V_{CE,sat}, R_{th}, and I_g)$  and junction temperature [21].  $V_{CE,sat}$ is measured three times per cycle [21], [78], [110]. At time instant  $t_1$ , the supply current is diverted from the IGBT module under the test and is replaced with a milliampere current for  $V_{CE,sat1}$  measurement. This is required to estimate the maximum junction temperature during the power cycle.

FIGURE 12. Measurements sequence for degradation precursors estimation [21].

$V_{CE,sat1}$  measurement should be taken just after diverting the main supply current. This ensures that the fall down of temperature after removing the supply is going to produce an error of less than few degrees in maximum junction estimation. Minimum junction temperature is estimated at time instant  $t_2$  by measuring  $V_{CE,sat2}$  and peak-to-peak junction temperature ripple can be calculated.

In order to use  $V_{CE,sat}$  as a degradation precursor,  $V_{CE,sat}$  should be measured under supply current and maximum junction temperature. Therefore,  $V_{CE,sat3}$  measured at time instant  $t_3$  is used. This ensures that the effect of bond wire degradation, and metallization degradation have been captured in the measured  $V_{CE,sat}$ . Also, it ensures capturing the degradation acceleration effect of junction temperature increase on both bond wire and metallization.

In order to estimate  $R_{\text{th}}$ ,  $V_{CE, \text{sat3}}$  is measured at time instant  $t_3$  just before diverting the main supply current away from the IGBT. Knowing  $V_{CE, \text{sat3}}$  and supply current, conduction power loss at time instant  $t_3$  is calculated.  $R_{\text{th}}$  then can be estimated through dividing difference between maximum junction and case temperatures estimated at time  $t_1$  by power loss estimated at time instant  $t_3$ . The trace of  $R_{\text{th}}$  with number of cycles can be used to track degradation in the thermal path.

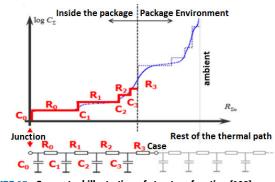

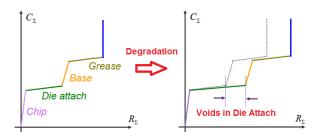

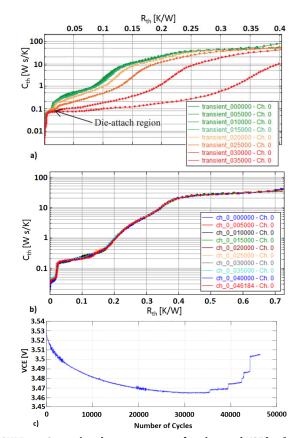

A more insightful method to track degradation in the thermal path is through the estimation of the structure function of the package [101]–[109]. Fig. 13 illustrates the concept behind the structure function. It is a graphical representation of thermal network model estimated from transient thermal impedance. In order to estimate the structure function; after every N load cycles, where N can be fixed number or varied based on the degradation, the load cycles are halted. Subsequently, a current is injected into the IGBT module to heat the junction, then it is removed to let the junction to cool down. Based on the recorded transient variation of junction temperature, structure function is estimated. As the degradation increases with power cycling, changes in the estimated structure function take place as shown in Fig. 14.

FIGURE 13. Conceptual illustration of structure function [109].

## 3) DC POWER CYLCLING CONTROL STRATEGIES

Four control strategies can be adopted while running DC power cycling test [110], [111]. These strategies are constant-turn-on-time, constant peak-to-peak case temperature,

**FIGURE 14.** Depiction of how degradation affects the structure function [109].

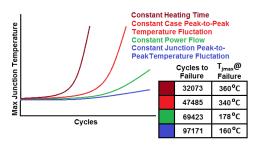

constant power loss, and constant peak-to-peak junction temperature. The main idea behind these control strategies is to provide different degrees of compensation for degradation. Fig. 15 shows the number of cycles to failure under the four control strategies. Assuming an initial maximum junction temperature, as time goes through the test, the maximum junction temperature increases due to degradation. The increase in junction temperatures accelerates degradation until end-of-life as indicated by the degradation precursors.

**FIGURE 15.** Junction temperature evolution with number of cycles due to degradation under different DC power cycling test control strategies [110].

Keeping the heating duty cycle constant is the harshest degradation scenario, as there is no compensation to reduce the rate at which degradation accelerates. This is equivalent to realistic degradation scenarios in the field. A weak act to slow down the rate of degradation is to fix the peakto-peak case temperature. This reduces the rate of increase of peak-to-peak junction temperature and compensates for degradation in thermal interface layer (TIM). A stronger act to brake degradation rate is by fixing the dissipated power in the junction. This act compensates for the increase in power losses caused by increasing temperatures. The strongest way to cut down degradation rate is to fix peak-to-peak junction temperature. This compensates for package interconnections and thermal path degradation [110]. In sections VI and VII, PC tests are based on constant-turn-on-time control strategies.

## **VI. LIFETIME MODELS**

Table 4 presents a summary for generic lifetime models associated with some important failure mechanisms. Lifetime models in this case are derived assuming that each failure mechanism works in complete isolation. This is not

| TABLE 4. | Lifetime models | of important | failure mechanisms. |

|----------|-----------------|--------------|---------------------|

|----------|-----------------|--------------|---------------------|

| Failure<br>Mechanisms | Failure modes                                     | Relevant<br>Stressors                                       | Lifetime<br>Model                                 |

|-----------------------|---------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|

| Fatigue               | -Bond wire<br>cracks.<br>-Bond wire lift-<br>off. | -Peak-to-peak<br>temperature<br>fluctuation                 | Empirical<br>[112,113]                            |

| Surface<br>Fatigue    | -Metallization reconstruction                     | -Peak-to-peak<br>temperature<br>fluctuation<br>-Temperature | Empirical<br>[34, 113]                            |

| Solder Joint          | -Die-attach,<br>-DCB-attach<br>-Terminal lead     | -Peak-to-peak<br>temperature<br>fluctuation                 | Models based<br>on Coffin-<br>Manson<br>[22, 113] |

| Fatigue               | -solder cracks<br>and<br>delamination             | -Temperature                                                | Empirical as<br>Norris-<br>Landzberg<br>[23, 24]  |

| Ceramic<br>Fatigue    | -DCB substrate cracks                             | -Vibration<br>-Mechanical<br>Forces                         | Empirical<br>[22, 34, 113]                        |

| Electro-<br>Migration | -Void formation<br>in bond wires<br>metallization | -Current<br>density<br>-Temperature                         | Empirical as<br>Black's law<br>[32, 33, 113]      |

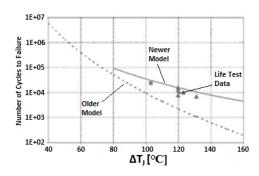

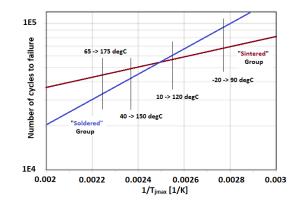

the case in the IGBT module. As was discussed before, several failure mechanisms compete until the end-of-life of the package. Thereby, IGBT specific lifetime models are required to capture the effect of competing failure mechanisms on life. In addition to the presence of interacting failure mechanisms, new package technologies entails changes in the manners by which the mechanisms interact [21], [23]. Therefore, in order to cope with technological advancements in package, IGBT module manufacturers run projects aiming for deriving empirical lifetime models for the state-of-art packaging technologies [21], [23]. This is required when the previous models predictions deviate from actual results of life tests as shown in Fig. 16.

FIGURE 16. Comparison between the predicted number of cycles to failure and life test data [21].

M. Held *et al.* conducted one of the earliest attempts to generate an empirical lifetime model of IGBT module in LESIT project [21], [76], [114]. In this project, the effect of  $\Delta T_j$  and  $t_{cycle}$  on module lifetime has been studied. Another attempt was done by R. Bayerer *et al.* and was published in

#### TABLE 5. Lifetime models of power modules under power cycling.

|                   | LESIT [21, 77, 114]                                                                                                                                                                                                                                                               | CIPS 2008 [21, 115, 116]                                                                                                                                                                                                                                                                                  | SKiM63 [21, 117-120]                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test<br>Variables | $- \Delta T_{j}$<br>- $T_{jmean}$                                                                                                                                                                                                                                                 | <ul> <li>ΔT<sub>j</sub>,</li> <li>T<sub>jmin</sub></li> <li>t<sub>on</sub> (heating time)</li> <li>I (current per bond stitch on the chip)</li> <li>V (voltage range of the device).</li> <li>D (bond wire diameter)</li> </ul>                                                                           | <ul> <li>ΔT<sub>j</sub></li> <li>T<sub>jmean</sub></li> <li>ton</li> <li>ar (bond wire aspect ratio)</li> <li>f<sub>diode</sub> (effect of the difference in the chip thickness between igbt and fwd with same voltage class on lifetime)</li> </ul> |

| Study<br>Purpose  | <ul> <li>Analyzing the effect of <i>t</i><sub>cycle</sub> on<br/>module life assuming bond wire<br/>lift-off is the main failure mode</li> </ul>                                                                                                                                  | <ul> <li>Analyzing the effect of different<br/>chip thicknesses, bond wires<br/>diameters, and numbers of bond<br/>wires per chip on module life.</li> </ul>                                                                                                                                              | <ul> <li>Analyze life of 100% solder-free<br/>modules.</li> </ul>                                                                                                                                                                                    |

| Main Results      | <ul> <li>The change of t<sub>cycle</sub> causes<br/>approximately the same damage<br/>and failure modes.</li> <li>Fast power cycling to reproduce<br/>millions of temperature changes<br/>in a short time.</li> <li>Damage depends on ΔT<sub>j</sub>,T<sub>jmean</sub></li> </ul> | <ul> <li>Δ<i>T</i><sub>j</sub>, <i>T</i><sub>jmin</sub>, and <i>t</i><sub>on</sub> alone cannot<br/>uniquely characterize the<br/>conditions of a power cycling test.</li> <li>Stresses distribution and<br/>geometrical factors affects<br/>different degradation mechanisms<br/>differently.</li> </ul> | <ul> <li>Degradation of the wire bond<br/>connection to the chip<br/>determines module lifetime.</li> <li>The model is considered: a bond<br/>wire lifetime model.</li> </ul>                                                                        |

| Life<br>Equation  | $A\Delta T^{lpha}_{j}e^{\left(rac{E_{a}}{k_{B}\cdot T_{jmean}} ight)}$                                                                                                                                                                                                           | $A\Delta T_{j}^{\beta_{1}}t_{on}^{\beta_{3}}I^{\beta_{4}}V^{\beta_{5}}D^{\beta_{6}}e^{\left(\frac{\beta_{2}}{T_{j\min}+273}\right)}$                                                                                                                                                                      | $A\Delta T_{j}^{\alpha}ar^{\beta_{i}T_{j}+\beta_{0}}\left(\frac{C+t_{on}^{\gamma}}{C+1}\right)e^{\left(\frac{E_{a}}{k_{g}\cdot T_{jmax}}\right)}f_{Diode}$                                                                                           |

| Usage             | <ul> <li>Standard modules with Al<sub>2</sub>O<sub>3</sub><br/>substrates.</li> </ul>                                                                                                                                                                                             | <ul> <li>Standard modules with Al<sub>2</sub>O<sub>3</sub><br/>substrates.</li> <li>Not valid for modules built with<br/>AlN and AlSiC.</li> </ul>                                                                                                                                                        | – Solder-free module.                                                                                                                                                                                                                                |

| Parameters        | $k_B$ [JK <sup>-1</sup> ] = 1.380 x 10 <sup>-23</sup> (Boltzman's constant)<br>$E_a$ [eV] = 0.618 (activation energy)<br>$\alpha$ = -5.039<br>Packages built with 1990 technology                                                                                                 | $\beta_1 = -4.416, \beta_2 = 1285$<br>$\beta_3 = -0.463, \beta_4 = -0.716$<br>$\beta_5 = -0.761, \beta_6 = -0.5$<br>Packages built with 2000 technology                                                                                                                                                   | $\alpha = -4.923, \beta_l = -9.012 \ge 10^{-3}, \beta_0 =$<br>1.942<br>$C = 1.434, \gamma = -1.208, E_a [eV] =$<br>0.06606<br>$f_{Diode} = 0.6204$<br>Solder-free packages                                                                           |

CIPS 2008 [21], [115], [116]. In this work, a new model was proposed to cope with the advances in module technologies from the time of LESIT project. A large power cycling dataset from standard modules of different structures and geometries were analyzed.

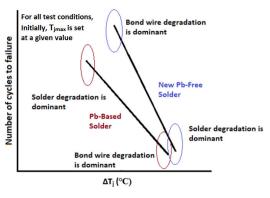

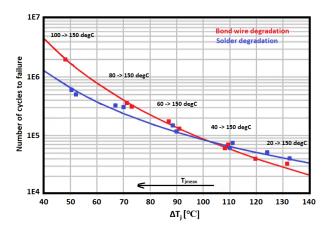

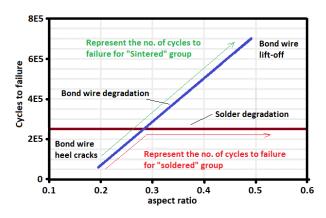

In another important attempt, U. Scheuermann et al. developed the SKiM63 lifetime model based on power cycling test results performed with the SKiM63 solder-free module [21], [117]–[120]. Table 5 provides a comprehensive comparison between these models. The SKiM63 model is different from previous empirical lifetime models that do not differentiate between different failure modes [121]. If the dominant failure mode in the accelerated test differs from the dominant failure mode in the application. The extrapolation of the lifetime data generated from accelerated testing to applications conditions may lead to wrong lifetime estimations. Therefore, solder fatigue and wire bond degradation should be studied separately to isolate the individual impact on lifetime. SKiM63 lifetime model was a leading effort in the aim to separate failure modes. The main method to realize separation of failure modes is through combining advanced package technologies with classical technologies. Having so, lifetime of classical interconnections can be studied without

VOLUME 9, 2021

interaction [21]. This will be discussed in detail in the next section.

So far, all lifetime models discussed are derived to represent IGBT module's lifetime subjected to identical power cycles. However, real applications are characterized by complex load profiles, resulting in complex junction temperature profiles as shown in Fig. 17a [21], [113], [12], [123], [124]. The first step for lifetime prediction is to decompose these complex profiles into sets of simpler identical power cycles as given in Fig. 17b. Commonly, this is achieved by Rainflow counting algorithm [94], [125], [126].

The second step is to estimate lifetime using cumulative degradation (damage) model [21], [23], [127], [128]. Fig. 17c summaries the process required to estimate lifetime of IGBT module subjected to electro-thermal stresses for a given mission profile. Mission profile data including load and climatic conditions (such as ambient temperature) are fed to the process. Device related characteristics (electrical and thermal) are then used to calculate IGBT module's losses and junction temperature profile. Consequently, the temperature profile is fed to cycles counting algorithms (such as Rainflow) to count junction temperature cycles at  $\Delta T_j$  as shown in Fig. 17b. Then through using a lifetime model, for instance CIPS2008,

| Cumulative Damage<br>Models                                                                                                                                           | Characteristics                                                                                                                               | Model Equations                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Linear damage rule<br>(Miner's)<br>[30, 113, 130]                                                                                                                     | <ul> <li>LDE, nLLD, nLSC, nLIC.</li> <li>Analytic</li> <li>Many Applications</li> <li>Popular in IGBT lifetime).</li> <li>Simplest</li> </ul> | $D = \sum \frac{n}{N_f} = 1$                                                                                     |

| Double linear damage rule<br>[113, 129, 130]                                                                                                                          | <ul> <li>LDE, LLD, LSC, nLIC.</li> <li>Analytic</li> <li>Many Applications</li> <li>Simple</li> </ul>                                         | $D_{t} = \sum \frac{n}{N_{t}} = 1$ $D_{u} = \sum \frac{n}{N_{u}} = 1$ $N_{t} = f(N_{f})$ $N_{u} = N_{f} - N_{t}$ |

| Non linear damage rule<br>[113, 120, 131]                                                                                                                             | <ul><li>nLDE, LLD, LSC, nLIC.</li><li>Analytic</li><li>Some Applications</li></ul>                                                            | $D = \left(\frac{n}{N_f}\right)^{g(\Delta T_f)} = 1$                                                             |

| Crack growth <sup>1</sup><br>[113, 131, 132]                                                                                                                          | <ul><li>nLDE, LLD, LSC, nLIC.</li><li>Some Applications</li><li>Complex</li></ul>                                                             | $\frac{da}{dN} = g\left(a, \Delta T_{j}, T_{j\max}\right)$ $D = \frac{a}{a_{c}} = 1$                             |

| Crack growth and<br>retardation <sup>2</sup><br>[132 - 135]                                                                                                           | <ul> <li>nLDE, LLD, LSC, nLIC.</li> <li>Some Applications</li> <li>Complex</li> </ul>                                                         | $\frac{da}{dN} = C(\Delta T_j) * g(a, \Delta T_j, T_{j\max})$ $D = \frac{a}{a_c} = 1$                            |

| LDE: linear damage evolution; LL<br>LSC: load sequence considered; L<br><sup>1</sup> Damage is modeled as growth of<br><sup>2</sup> Damage retardation due to load in | IC load interaction considered a hypothetical crack.                                                                                          |                                                                                                                  |

## TABLE 6. Analytic cumulative degradation models.

FIGURE 17. IGBT module's lifetime estimation, a) Junction temperature variations, b) Temperature variation peak counting, c) Lifetime estimation procedure (Rectangular boxes represent in/out data, Rounded cornered boxes represent calculation. Blue arrows represent input data flow. Dark red arrows represent output data flow. Red arrow represent the final estimation.)

number of cycles to failure at  $\Delta T_j$  is calculated. Finally, the counted junction temperatures cycles at  $\Delta T_j$  and number of cycles to failure at  $\Delta T_j$  are fed to one of damage models

shown in Table 6 to estimate the IGBT lifetime given the mission profile.

Miner's model, a popular damage model, assumes that the degradation caused by the contribution of each set can be aggregated linearly to obtain the accumulated damage. Nonetheless, factor such as the nonlinear relationship between cycle magnitude and damage, interaction between cycles, multiple damage stages, and, nonlinear damage evolution, limit the accuracy of prediction of lifetime made based on linear degradation theory. In addition, a modified Rainflow counting method should be used to account for load sequences. Table 6 summaries important analytic cumulative degradation models. Many cumulative degradation models have been proposed in fracture mechanics literature to account for limitations of using linear degradation rule. Nevertheless, linear degradation rule with simple Rainflow counting algorithm remains most widely used in IGBT lifetime estimation.

The estimated lifetime only considers the impact of power cycles. High humidity, corrosive environments and cosmic ray can lead to a much lower lifetime. Therefore, lifetime estimated based on power cycles represents an upper bound for the lifetime of power modules in a specific application [21].

## **VII. SEPARATION OF FAILURE MODES**