**Aalborg Universitet**

#### Grid converter for LED based intelligent light sources

Török, Lajos

Publication date: 2011

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Török, L. (2011). Grid converter for LED based intelligent light sources. Department of Energy Technology, Aalborg University.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## GRID CONVERTER FOR LED BASED INTELLIGENT LIGHT SOURCES

$\begin{array}{c} \text{AALBORG UNIVERSITY} \\ 2011 \end{array}$

Lajos Török

Department of E.T. **ENERGY TECHNOLOGY**

## Preface

This thesis is submitted in a partial fulfillment of the requirement for the Degree of Doctor of Philosophy. The work has been carried out at Aalborg University, Department of Energy Technology in cooperation with Martin Professional A/S. The project period was from September 2008 to September 2011.

During my research time much help was given by many people from the Department of Energy Technology and Martin Professional A/S. I would like to thank my supervisor Associate Professor Stig Munk-Nielsen, for his dedicated support and guidance in the field of power converters. I would like to thank also Carsten Karup Nielsen who helped and guided me in the hardware design and construction.

Thanks goes to industrial partners, Thomas Mansachs Frederiksen and Mikkel Holch, who helped me in power electronic design and in the field of digital controllers.

I would like to address my thanks to all the people at the Department of Energy Technology, who have followed and helped my research.

Aalborg, September 2011 M.Sc.EE Lajos Török

## Summary

The purpose of this thesis was to investigate the applicability and effects of digital control to line connected switched mode power supplies with power factor correction. The main approach was cost effectiveness with high efficiency. This involved hardware design for increased switching frequency to reduce the size of the magnetic components. A description of different grid regulations was given followed by a set of converter topologies and controllers. Different control techniques were pointed out. Among the listed topologies and control solutions few were selected for further analysis, design and implementation.

Many of different hardware and control solutions available on the market were investigated. Most of the commercial power supplies are controlled by dedicated analog controllers in form an integrated circuit. Thus a survey was conducted to analyze the available state-of-art analog controllers and their implemented control algorithms. As digital control has to be competitive with the existing solutions it was investigated what digital signal processing solutions exist. A performance and cost comparison was also presented.

The chosen converter topologies were thoroughly analyzed. Different converters were chosen for different power levels. At low power simple boost converter as power factor corrector (PFC) and a RCD-clamped forward converter was chosen as DC-DC converter. This with has double output and coupled filter inductor. To design a digital controller with the tools of the classical control theory a small signal linearized model of the converter is needed. Detailed modeling and linearizing of the boost converter is presented.

At high power level interleaving technique is frequently used to reduce the current stress on the switching components. Though the number of magnetic components is increased they became smaller in size resulting in smaller current ripple through them. An interleaved boost converter with two legs is selected as PFC converter. It was shown that the small signal model of the interleaved converter is similar to the simple boost converter. Only the simple inductor has to be replaced by the paralleled inductors of each leg. This statement is valid only if the total inductor current is controlled rather than controlling the current in each leg. As second stage a phase-shifted full-bridge converter with synchronous rectification and current doubler was selected. It was shown that for output current and voltage control this topology can be modeled as a interleaved synchronous buck converter. As it can be seen interleaving technique is also present in this topology. For this topology a fuzzy logic voltage controller is proposed and compared to the traditional PI controller.

After modeling the converters controllers can be designed. The controller design was

interconnected with the hardware design and control platform. Thus two different prototypes were designed and built with two different digital controllers and the controller design, analysis and implementation was based on these two case studies.

The first prototype was a 70 W two-stage PFC and DC-DC converter with boost and forward converters. Average current mode control was selected, designed, simulated an implemented for the boost PFC converter. The two-loop control structure (fast internal current loop and lower bandwidth external voltage loop) was designed for nominal power but system behavior was also analyzed for low-load conditions. The controller was simulated in Matlab/Simulink using PLECS library and embedded Matlab function. All the parameters were treated and scaled just as they appear in the ADC interrupt of the 16 bit fixed point dsPIC30F1010 microcontroller. Peak current control was implemented for the forward converter, using analog comparator module of the digital-signal-controller. The waveforms, efficiency and power factor results were compared to the performance of an identical two stage 70 W power supply controlled with an analog PFC/PWM integrated circuit.

The second prototype was a 600 W two-stage PFC and DC-DC converter with interleaved boost and phase-shifted full-bridge (PSFB) converters. Average current mode control was designed simulated and implemented for both converters. The sum of the boost inductor current was controlled to shape the line current and the sum of the filter inductor currents in the PSFB converter was controlled to limit over-currents. Low bandwidth PI controllers control the boost DC and the output DC voltages. A fuzzy logic output voltage controller was also simulated and compared to the performance of the PI controller. All four control loops were implemented in a 16 bit fixed point dsPIC33FJ32GS406 microcontroller driving at the same time 8 PWM channels.

Finally a brief analysis was done on the effect of the grid disturbances, especially voltage sags on the digital controller. Different grid codes and compatibility requirements and system behavior through a boost converter with digital control was presented.

In this thesis a deep knowledge of design and digital control of line connected switched mode power supplies with power factor correction was gathered and appropriate solutions were presented. The advancement of this thesis will enable improved design and digital control of high frequency switched mode power supplies in the future. It is concluded that the digital signal processors available today are competitive in performance with the state-of-art analog ICs. The economic reasons for using digital control is not so clear but with falling prices of microcontrollers and increasing demands on the performance of power converters introducing digital control seems to be a reasonable option for the future development of power converters. Advanced control structures can be implemented to improve the performance of switched-mode power-supplies and power factor corrector circuits.

Main contributions of this work are:

- An investigation on the effect of the use of digital control in switch-mode powersupply applications.

- Development of a simulation platform in Matlab/Simulink using triggered embedded

Matlab functions to model digital control, suitable for different power converters with close to real life conditions.

- Digital signal processor-based control of four different power converter topologies with embedded low cost 16 bit fixed point microcontroller.

- Comparison of analog control and digital control of two identical 70W two-stage power factor corrector and DC-DC converters regarding cost effectiveness, power factor and efficiency.

- Digital fuzzy logic controller proposed for low bandwidth voltage control to high frequency switched-mode power supplies.

- Investigation on the effect of grid disturbances on the control of low-voltage-gridconnected power supplies.

## Nomenclature

- $\Delta D$  Duty cycle deviation due to the finite slope of the primary current

- $\Delta I$  Inductor average-to-peak current ripple

- $\Delta i_L$  Inductor average-to-peak current ripple

- $\Delta I_{Lf}$  Filter inductor peak-to-peak current ripple in modeling of the PSFB converter

- $\Delta t$  Shift variation in the PSFB converter

- $\Delta v_o$  Output voltage ripple

- $\eta$  Efficiency

- $\hat{d}$  Duty cycle perturbation

- $\hat{d}_{eff}$  Effective duty cycle perturbation

- $\hat{d}_i$  Duty cycle perturbation due to filter inductor variation

- $\hat{d}_v$  Duty cycle perturbation due to input voltage variation

- $\hat{i}_L$  Inductor current perturbation

- $\hat{i}_o$  Output current perturbation

- $\hat{i}_{L1}, \hat{i}_{L2}$  Interleaved boost inductors current perturbation

- $\hat{i}_{Lf1}, \hat{i}_{Lf2}$  Filter inductor current perturbation

- $\hat{i}_{Lp}$  Paralleled inductor voltage perturbation

- $\hat{v}$  Output voltage perturbation

- $\hat{v}_g$  Supply voltage perturbation

- $\hat{v}_{L1}, \hat{v}_{L2}$  Interleaved boost inductor voltage perturbation values

$\hat{v}_{Lf1}, \hat{v}_{Lf2}$  Filter inductor voltage perturbation

- $\hat{v}_{Lp}$  Paralleled inductor voltage perturbation

- $\hat{v}_L$  Boost inductor voltage perturbation

- $\omega_n$  Natural frequency

- $\omega_{iz}$  Frequency of the zero

- $\omega_{vz}$  Frequency of the zero

- $\zeta$  Damping

- C Filter capacitor

- C1, C2 Half bridge capacitors

- $C_f$  Filter capacitor

- $C_b$  Blocking capacitor

- $C_{internal}$  Internal capacitance of the converter components

- Cdc Boost capacitor

- Cf EMI filter capacitor

- Co Forward filter capacitor

- $cos\phi$  Displacement factor

- D Duty cycle  $(0 \le D \le 1)$  steady state value

- D Switching diode

- *d* Duty cycle instantaneous value

D1, .., 4 Bridge rectifier

- D' 1-D steady state value

- *d*′ 1-d

- $D_{eff}$  effective duty cycle of the PSFB Converter

- $D_{max}$  Maximum allowed duty cycle

- $d_{vmax}$  Saturation point of the voltage controller output, presented in Q.15 format

- dev Voltage error variation

- $di_L$  Boost inductor current variation

- $di_{L1}, di_{L2}$  Interleaved boost inductor current variations

- $di_{Lf1}, di_{Lf2}$  Filter inductor current variations

- dv Output voltage variation

- *e* Controller input

- $e_i$  Current error

- $e_v$  Voltage error

- ev Voltage error

$Ext\_ref$  Reference signal TL431 shunt regulator to the analog comparator

- $f_L$  Line frequency

- $f_S$  Switching frequency

- $G_{HALL}$  Hall-sensor gain

- $G_{id0}$  Current transfer function gain

- $G_{id}$  Duty cycle-to-inductor current transfer function

- $G_{iq}$  Input voltage-to-inductor current transfer function

$G_{INA193}$  Amplifier gain

- $G_{sysv}$  Voltage loop transfer function

- $G_{vd0}$  Voltage transfer function gain

- $G_{vd}$  Duty cycle-to-output voltage transfer function

- $G_{vq}$  Input voltage-to-output voltage transfer function

- *Gm* Gain margin

- *I* integral component

- $I_C$  Capacitor current Steady-state value

- $i_C$  Boost capacitor current

- $I_L$  Inductor current Steady-state value

- $I_n \qquad n^{th}$  harmonic of the input current

- $I_o$  Output current Steady-state value

- $I_1$  The fundamental of the input current

- $i_{ds}$  Forward drain-source current

- $i_g$  Input current instantaneous value

$I_{L1}, I_{L2}$  Interleaved boost inductor current - Steady-state values

$I_{Lf1}, I_{Lf2}$  Filter inductor current - Steady-state values

$I_{lf}$  Filter inductor current - Steady-state value

*I*<sub>load</sub> Load current

$I_{peak\_L1}, I_{peak\_L2}$  Interleaved boost inductor currents - peak values

- $I_p$  Peak value of the primary current

- $i_p$  Primary current

- $i_{ref}$  Current reference

- $I_{rms}$  The rms value of the input current

- K Scaling factor

- $K_d$  Distortion factor

- $K_{dev}$  Error variation coefficient

- $K_{ev}$  Error coefficient

- Ka Anti-windup coefficient

- Ki Integral coefficient

- *Kii* Current Ki coefficient

- Kiv Voltage Ki coefficient

- *Kp* Proportional coefficient

- *Kpi* Current Kp coefficient

- Kpv Voltage Kp coefficient

- L Inductor

- $L_1, L_2$  Interleaved boost inductors

- $L_C$  Critical inductance value

- $L_f$  Filter inductor

- $L_{lk}$  Leakage inductance of the PSFB transformer

- $L_m$  Magnetizing inductance of the PSFB transformer

- $L_p$  Paralleled interleaved boost inductors

- Lf EMI filter inductor

- Lf1, Lf2 Output filter inductors of the current doubler

- *Lo* Forward filter inductor

- M The peak value of the input current

$M_p$  Maximum overshoot in %

$n = N_s/N_p$

- $n_1, n_2$  Number of turns in the primary and secondary windings

- $n_3$  Number of turns in the secondary of the forward transformer

- $N_p, N_s$  Number of turns in the primary and secondary winding of the PSFB transformer

- *P* Proportional component

- PIi Current PI controller

- *PIv* Voltage PI controller

- Pm Phase margin

- Po Output power

- Q Switching MOSFET

- QA, QB, QC, QD Full bridge MOSFETs

- R Load resistance

- $R_{div}$  Voltage divider gain

- $R_{ids}$  Forward drain-source current measurement resistor

- $R_{iL}$  Inductor current measurement resistor

- $R_{inrush}$  Inrush protection thermistor

- Rs, Cs, Ds RCD snubber resistor, capacitor and diode

- SR1, SR2 Synchronous rectifier MOSFETs

- $T_s$  Switching period

- $T_{si}$  Current sampling time

- $T_{sv}$  Voltage sampling time

- Tr Transformer

- *u* Controller output

- V Output voltage Steady-state value

- v Output voltage instantaneous value

- $V_D$  Diode voltage drop

- $V_g$  Supply voltage Steady-state value

- $v_g$  Supply voltage instantaneous value

- $v_L$  Inductor voltage

- $V_o$  Output voltage average value

- $V_{ac-min}$  Low line voltage rms value

$V_{ac\_meas}$  Measured rectified line voltage

$V_{ac}$  AC voltage source

- $V_{dc\_meas}$  Measured rectified line voltage

- $V_{max}$  maximum of the line voltage, presented in Q.15 format

- $V_{ref}$  Reference voltage

- $V_{rms}$  The rms value of the input voltage

- Vdc DClink voltage, input voltage for the DC-DC converter

- Vf Forward output voltage

- $V f_{meas}$  Measured forward output voltage

Vp, Vs Voltages in the primary and the secondary winding of the PSFB transformer

X(Q.15) measured value transferred to Q.15 value

$x_{measured}$  Measured value, sent to ADC converter

$Z_b$  Factor including leakage inductance and switching frequency

## Abbreviations

- ADC Analog digital converter

- ALU Arithmetical logical unit

- CBEMA The Computer and Business Electronic Manufactures Association

- CCM Continuous conduction mode

- ${\cal C}{\cal M}$ Common mode

- CRM Critical conduction mode

- DCM Discontinuous conduction mode

- DKK Danish currency

- DMDifferential mode

- DSP Digital signal processor

- EMC Electromagnetic compatibility

- EMI Electromagnetic interference

- FOH First order hold

- FPGA Field-programmable gate array

- ICD2/3 In-circuit debugger

- ITIC Information Technology Industrial Council

- PCB Printed circuit board

PF Power factor

PFC Power factor correction

PLL Phase locked loop

PSFB Phase-shifted full-bridge

PWM Pulse width modulation

rms Root-mean-square value of an alternating signal

SEMI Semiconductor Equipment and Materials International

THD Total harmonic distortion

VCC Supply voltage of the analog controller

VDD dsPIC supply voltage

VEE dsPIC ground = primary ground

ZOH Zero order hold

ZVS Zero voltage switching

## Contents

| 1        | Introduction                                                                                                     | 1  |

|----------|------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1 Motivation $\ldots$         | 1  |

|          | 1.2 Problem Formulation                                                                                          | 2  |

|          | 1.3 Contributions                                                                                                | 4  |

|          | 1.4 Related Presentations and Publications                                                                       | 4  |

|          | 1.5 Outline                                                                                                      | 5  |

| <b>2</b> | Converters, controllers and control methods                                                                      | 7  |

|          | 2.1 International standards                                                                                      | 8  |

|          | 2.2 Power factor correction - terminology                                                                        | 11 |

|          | 2.3 Converter topologies                                                                                         | 12 |

|          |                                                                                                                  | 12 |

|          | 2.3.2 Active PFC topologies                                                                                      | 14 |

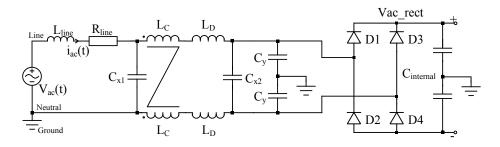

|          | 2.3.3 Electro-magnetic compatibility - EMI filters                                                               | 17 |

|          | 2.3.4 DC-DC converter topologies                                                                                 | 18 |

|          | 2.4 Analog and digital controllers on the market                                                                 | 24 |

|          | 2.5 Control strategies $\ldots$ | 27 |

|          | 2.6 Summary                                                                                                      | 30 |

| 3        | Digital control for switched-mode power supplies                                                                 | 31 |

|          | · · · ·                                                                                                          | 32 |

|          | 3.2 Modeling the chosen converters                                                                               | 32 |

|          | 3.2.1 Modeling of the simple boost converter                                                                     | 32 |

|          | 3.2.2 Modeling of an interleaved boost converter                                                                 | 39 |

|          | 3.2.3 Modeling of phase-shifted full-bridge converter with current doubler                                       | 42 |

|          | 3.2.4 Model discretization                                                                                       | 51 |

|          | 3.3 Chosen control solutions                                                                                     | 52 |

|          | 3.3.1 Linear PI controller                                                                                       | 53 |

|          | 3.3.2 Nonlinear Fuzzy controller                                                                                 | 54 |

|          | 3.4 Summary                                                                                                      | 56 |

| 4        | Digital control in application                                                                                   | 57 |

|          | о́                                                                                                               | 57 |

|          |                                                                                                                  | 59 |

|          |                                                                                                                  | 62 |

|          | 4.1.3 Simulations                                                                                                | 71 |

|              |            | <ul><li>4.1.4 Auxiliary power supply</li></ul>                                                  |      |

|--------------|------------|-------------------------------------------------------------------------------------------------|------|

|              |            | 4.1.6 Comparison of the digital controlled converter to and identical but analog controlled one |      |

|              | 4.2        | 600W Two-stage PFC/DC-DC power supply                                                           |      |

|              |            | 4.2.1 Converter description                                                                     |      |

|              |            | 4.2.2 Controller design and description                                                         |      |

|              |            | 4.2.3 Simulations                                                                               |      |

|              |            | 4.2.4 Digital control implementation                                                            | 102  |

|              |            | 4.2.5 Auxiliary power supply                                                                    |      |

|              |            | 4.2.6 Discussion                                                                                | 105  |

|              | 4.3        | Summary                                                                                         | 108  |

| <b>5</b>     |            |                                                                                                 | 111  |

|              | 5.1        | Need for immunity to line disturbances                                                          |      |

|              | 5.2        | Immunity of the digitally controlled boost PFC converter $\ldots$                               |      |

|              | 5.3        | Summary                                                                                         | 117  |

| 6            |            | clusions                                                                                        | 119  |

|              | 6.1        | Future work                                                                                     | 121  |

| Bi           | bliog      | graphy                                                                                          | 123  |

| A            |            | uctor and transformer designs                                                                   | 135  |

|              |            | Boost inductor design                                                                           |      |

|              |            | Forward transformer design                                                                      |      |

|              |            | Boost inductor design for interleaved PFC converter                                             |      |

|              | A.4        | Full-bridge transformer design                                                                  | 139  |

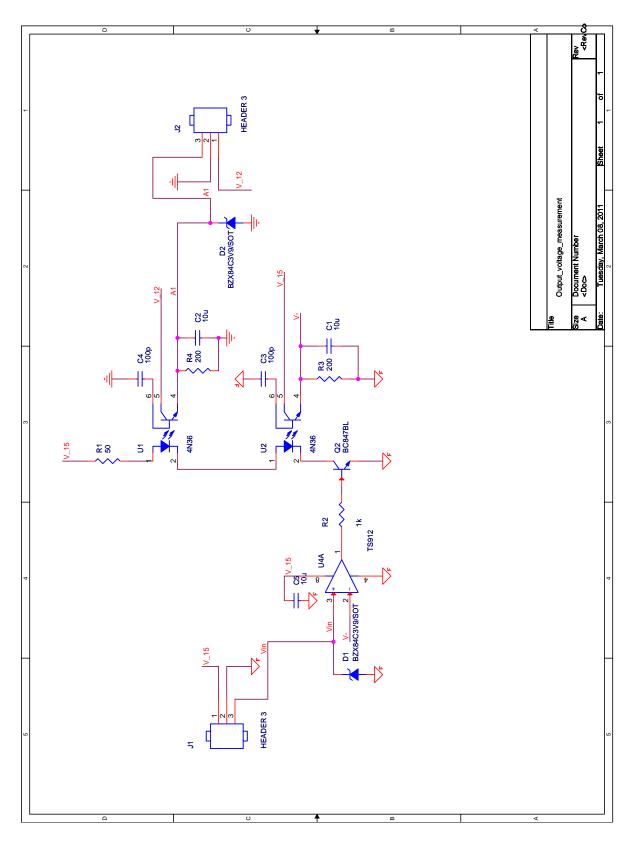

| В            |            | ematics                                                                                         | 141  |

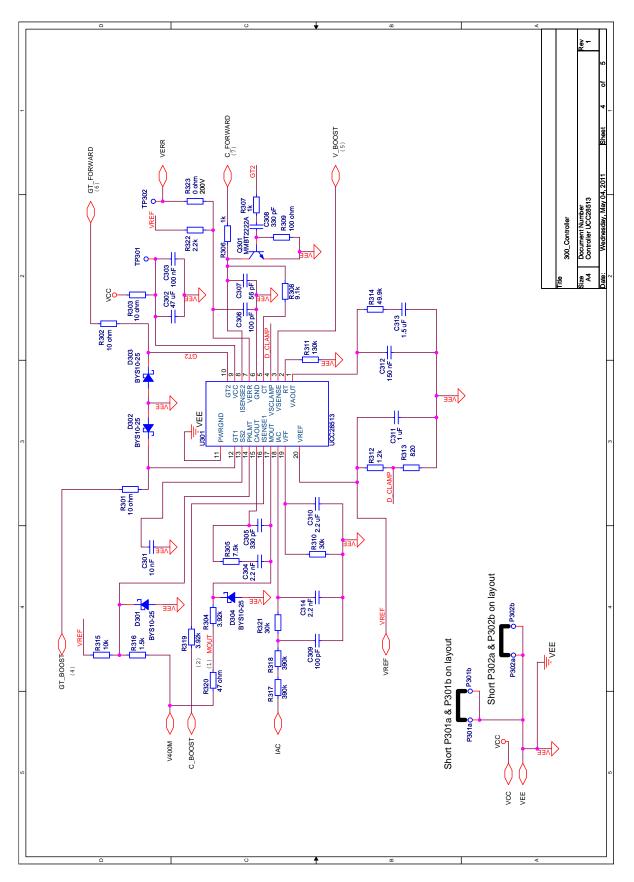

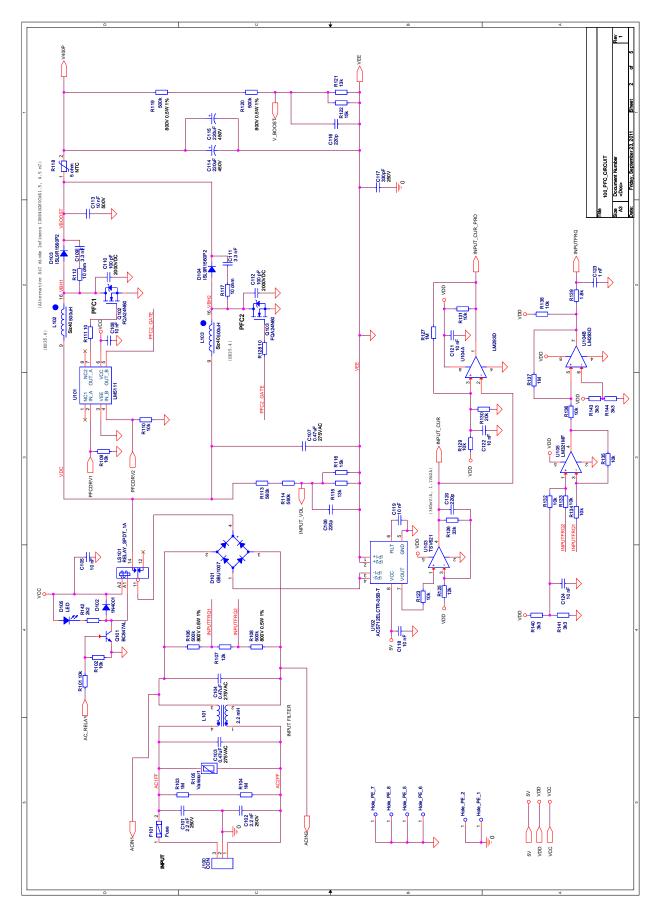

|              | B.1        | 70 W converter schematics                                                                       |      |

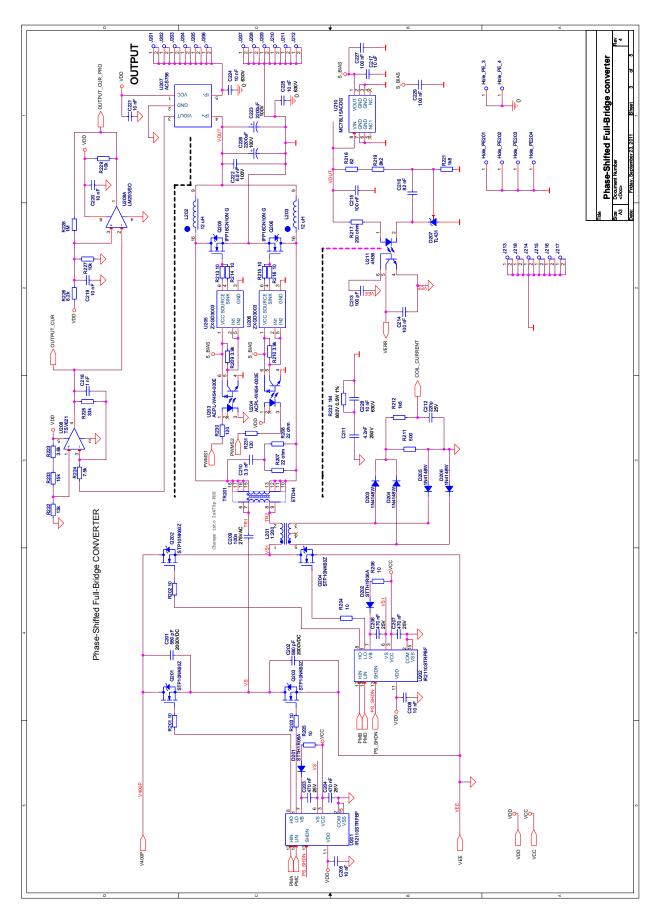

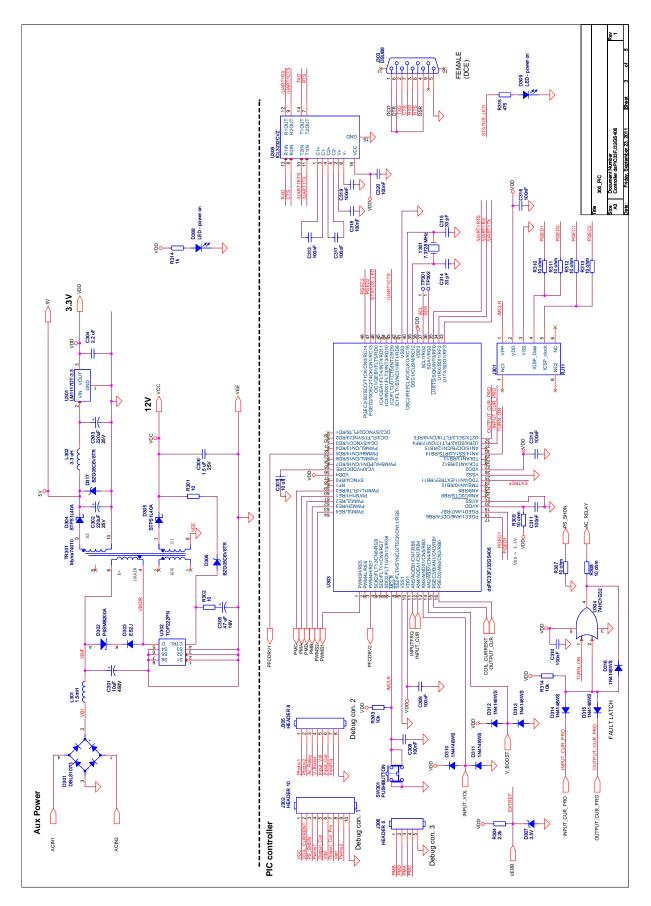

|              | B.2        | 600 W converter schematics                                                                      | 147  |

| $\mathbf{C}$ |            | lications                                                                                       | 153  |

|              | C.1        |                                                                                                 |      |

|              | <b>C</b> • | croprocessor                                                                                    | 154  |

|              | C.2        | Efficiency and hardware comparison of analog control-based and digital                          | 1.00 |

|              | C a        | control-based 70 W two-stage power factor corrector and DC-DC converters                        | 5160 |

|              | C.3        | Digital Fuzzy logic and PI control of phase-shifted full-bridge current-                        | 1 20 |

|              | <b>C</b> 4 | doubler converter                                                                               |      |

|              |            | High Output LED-Based Profile Lighting Fixture                                                  | 178  |

|              | C.5        | Effect of voltage sags on digitally controlled line connected switched-mode                     | 100  |

|              |            | power supplies                                                                                  | 180  |

# List of Figures

| 2.1  | Capacitive filtered single-phase diode rectifier a.) Schematic b.) Waveforms |    |

|------|------------------------------------------------------------------------------|----|

|      | - Top: Blue - Normalized line voltage, Green - Normalized line current;      |    |

|      | Bottom: Normalized Line current spectrum                                     | 7  |

| 2.2  | Green - envelop of the input current to define the 'special wave shape and   |    |

|      | to classify equipment as Class D' [8]; blue - simulated current waveform     |    |

|      | (overloaded 70 W boost PFC converter with saturated current controller).     | 9  |

| 2.3  | Limits for Class A equipment [8]                                             | 9  |

| 2.4  | Limits for Class C equipment [8]                                             | 9  |

| 2.5  | Limits for Class D equipment [8]                                             | 10 |

| 2.6  | Limits for conducted disturbances at the mains ports of class A equipment    |    |

|      | [50]                                                                         | 10 |

| 2.7  | Limits for conducted disturbances at the mains ports of class B equipment    |    |

|      | [50]                                                                         | 10 |

| 2.8  | Limits for conducted common mode disturbances of class A equipment [50]      | 11 |

| 2.9  | Limits for conducted common mode disturbances of class B equipment [50]      | 11 |

| 2.10 | Rectifier with inductor filter [17]                                          | 13 |

|      | Rectifier with resonant passive filter [25]                                  | 14 |

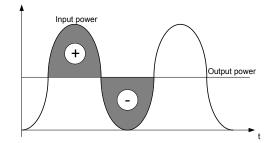

| 2.12 | Pulsating input and constant output power                                    | 14 |

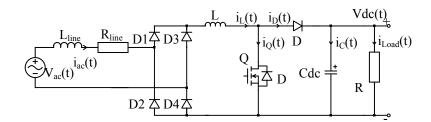

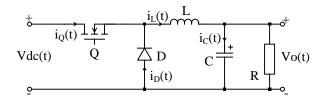

| 2.13 | Boost PFC circuit - Basic topology                                           | 15 |

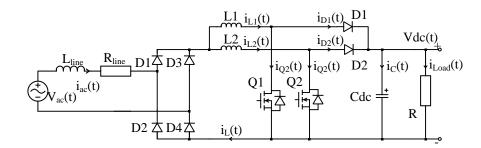

| 2.14 | Interleaved boost PFC circuit                                                | 17 |

| 2.15 | Basic EMI filter topology for line connected power supplies                  | 18 |

| 2.16 | Buck converter - Basic topology                                              | 18 |

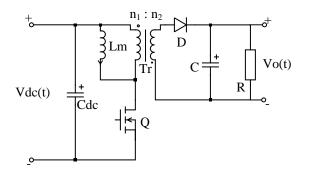

| 2.17 | Flyback converter                                                            | 20 |

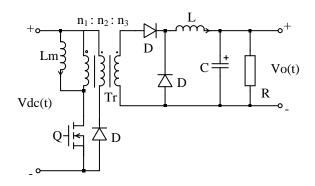

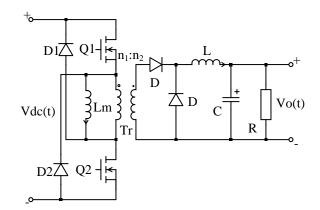

| 2.18 | Forward converter - Basic topology                                           | 20 |

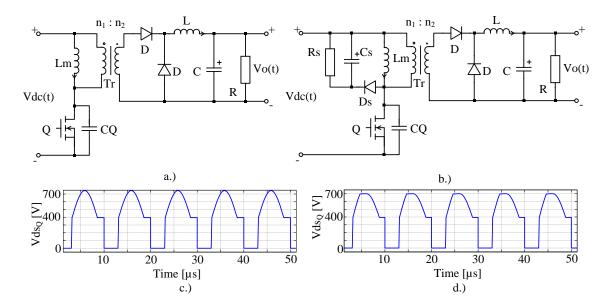

| 2.19 | a.) Resonant reset forward converter; c.) Drain-source voltage of the MOS-   |    |

|      | FET in case of resonant reset; b.) RCD clamped forward converter; d.)        |    |

|      | Drain-source voltage of the MOSFET in case of RCD clamp;                     | 21 |

|      | Forward converter - Basic topology                                           | 22 |

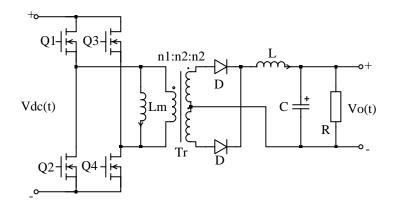

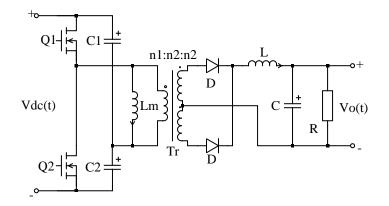

| 2.21 | Full-bridge converter - Basic topology                                       | 22 |

| 2.22 | Half-bridge converter - Basic topology                                       | 23 |

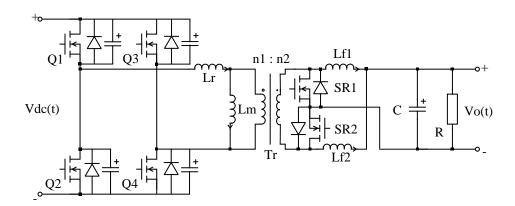

| 2.23 | Phase-shifted full-bridge converter with current doubler                     | 24 |

| 2.24 | The PFC controller ICs available on the market                               | 25 |

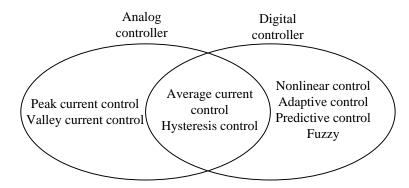

| 3.1  | Analog controller vs. digital controller                                     | 31 |

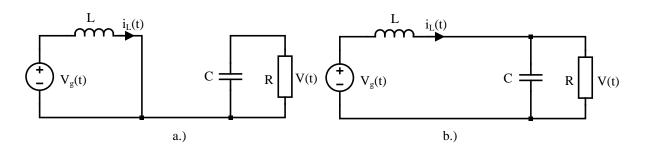

| 3.2  | Switching states                                                             | 33 |

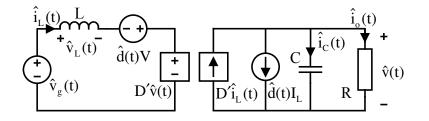

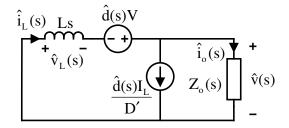

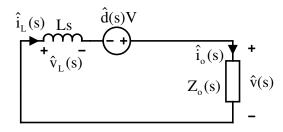

| 3.3  | Small signal model of a boost converter                                      | 36 |

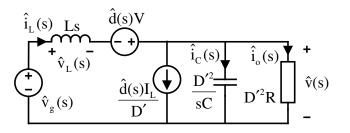

| 3.4  | Small signal model of a boost converter in frequency domain                  | 36 |

| 3.5  | Circuit describing the effect of $\hat{d}$ on $\hat{v}$                       | 37 |  |

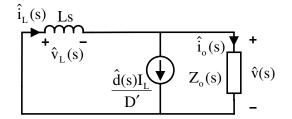

|------|-------------------------------------------------------------------------------|----|--|

| 3.6  | The small signal model when $I_L \cdot \hat{d}(s) = 0$                        | 38 |  |

| 3.7  | The small signal model when $V \cdot \hat{d}(s) = 0$                          | 38 |  |

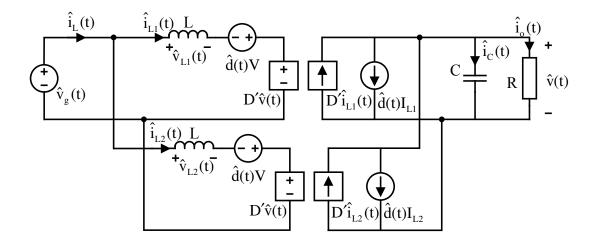

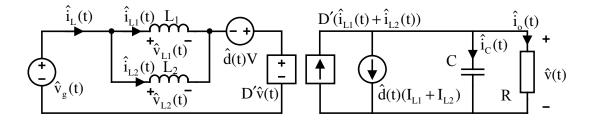

| 3.8  | Small signal model of an interleaved boost converter                          | 40 |  |

| 3.9  | Simplified small signal model of an interleaved boost converter               | 41 |  |

| 3.10 | Small signal model of an interleaved boost converter in frequency domain . 41 |    |  |

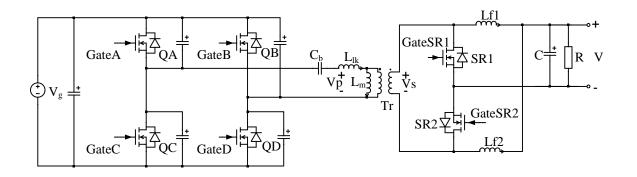

| 3.11 | Schematic of the phase-shifted full-bridge converter with current doubler .   | 42 |  |

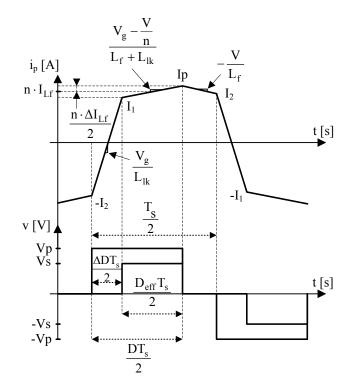

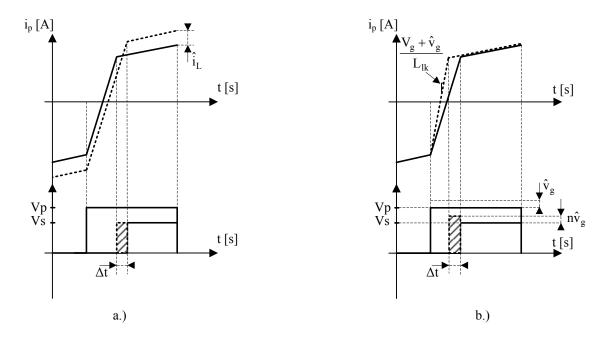

| 3.12 | Primary current, primary and secondary voltage waveforms [74]                 | 43 |  |

|      | Duty cycle variation due to: a.) changes in filter inductor current; b.)      |    |  |

|      | changes in input voltage [74]                                                 | 45 |  |

| 3.14 | Interleaved synchronous buck converter                                        | 46 |  |

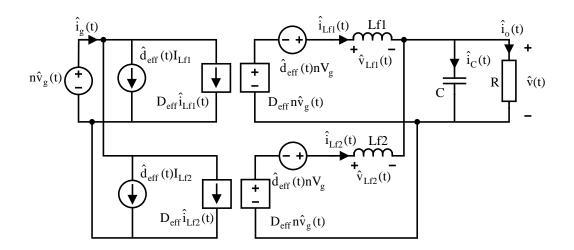

|      | Current and drain-source voltage waveforms                                    | 47 |  |

|      | Small signal model of a synchronous buck converter                            | 48 |  |

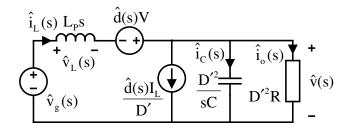

|      | Contracted small signal model of a synchronous buck converter                 | 49 |  |

|      | Simplified small signal model of a synchronous buck converter                 | 49 |  |

| 3.19 | Small signal model of a synchronous buck converter in 's' domain              | 50 |  |

|      | Simplified small signal model of a synchronous buck converter in 's' domain   | 50 |  |

| 3.21 | Bode plot of the continuous and discrete system with different discretization |    |  |

|      | methods                                                                       | 52 |  |

| 3.22 | Basic control structure of a power converter                                  | 52 |  |

| 3.23 | Control structure of a power converter, using duty cycle as control variable  | 53 |  |

| 3.24 | PI control structure                                                          | 54 |  |

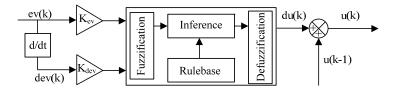

| 3.25 | Fuzzy incremental controller                                                  | 55 |  |

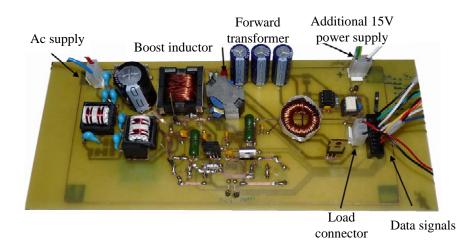

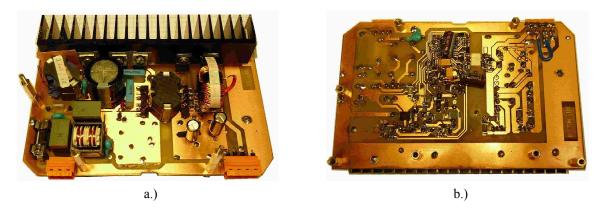

| 4.1  | First prototype                                                               | 58 |  |

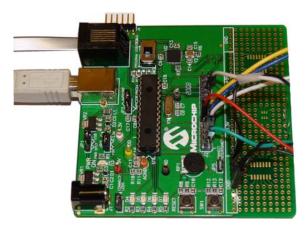

| 4.2  | 16 bit 28 pin control board                                                   | 58 |  |

| 4.3  | Power supply with digital controller                                          | 58 |  |

| 4.4  | Power supply with analog controller                                           | 59 |  |

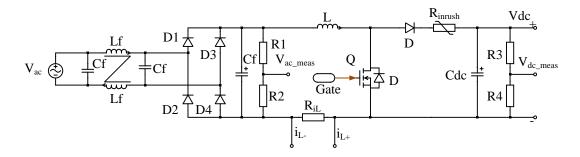

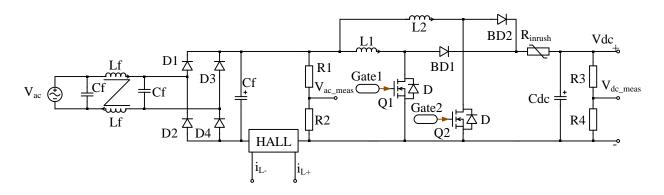

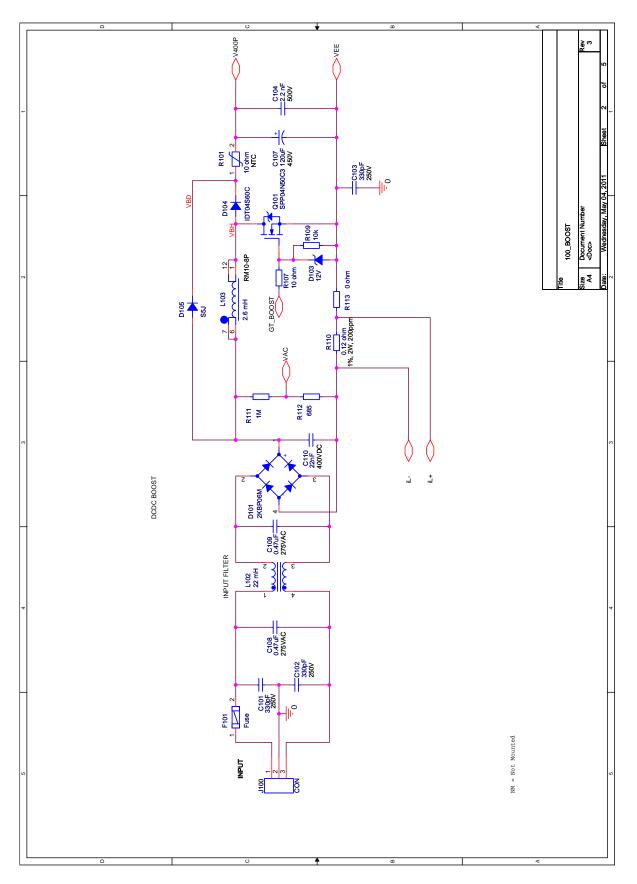

| 4.5  | Boost converter schematic                                                     | 59 |  |

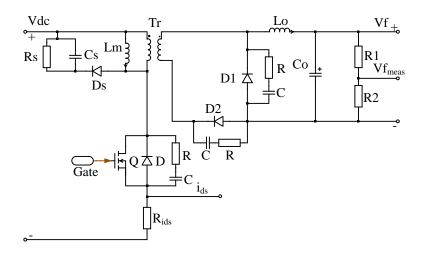

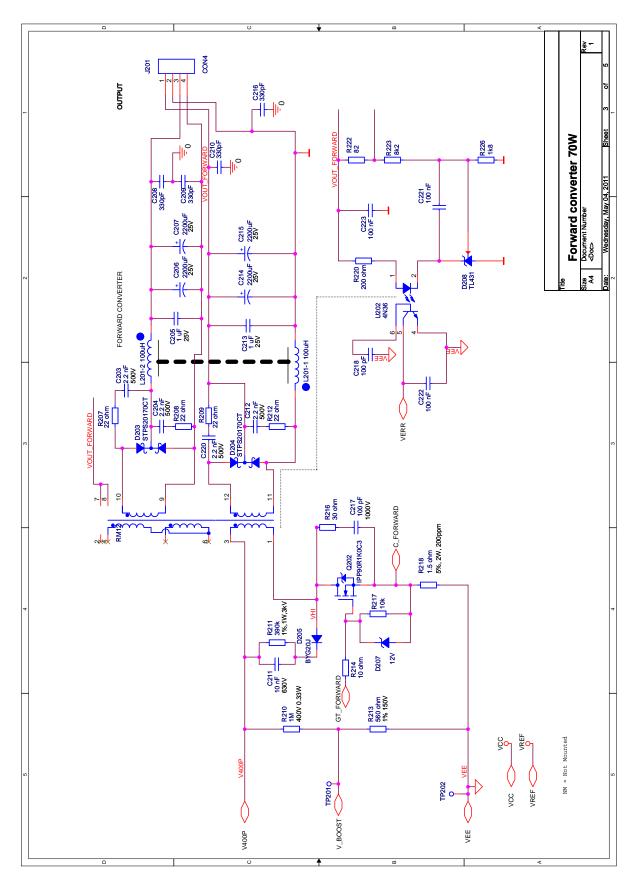

| 4.6  | Forward converter schematic                                                   | 60 |  |

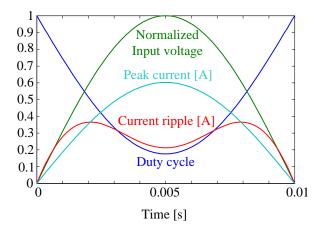

| 4.7  | Inductor current and duty cycle variation                                     | 61 |  |

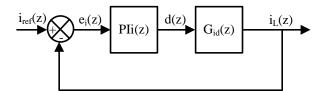

| 4.8  | Current loop                                                                  | 64 |  |

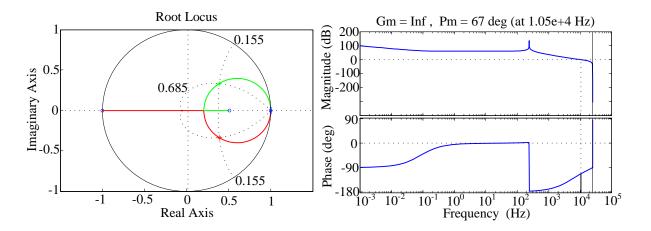

| 4.9  | Current controller design light load                                          | 65 |  |

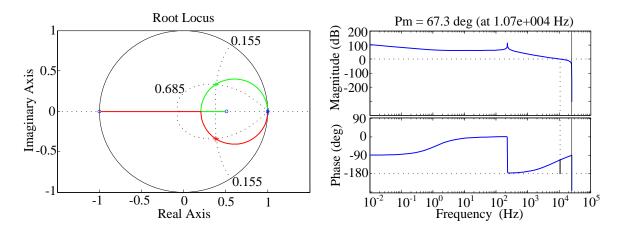

| 4.10 | Current controller design for full load                                       | 66 |  |

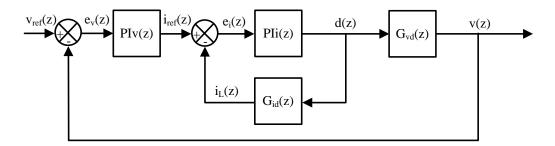

|      | Voltage loop                                                                  | 67 |  |

| 4.12 | Voltage controller design for light load                                      | 69 |  |

|      | Voltage controller design for full load                                       | 70 |  |

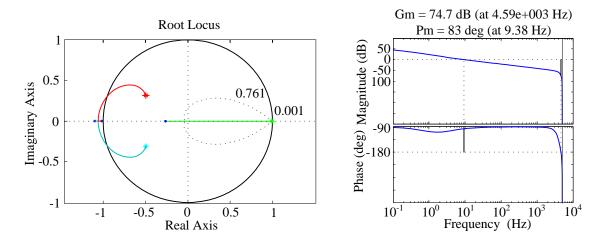

|      | TL431 voltage controller with optical isolation                               | 71 |  |

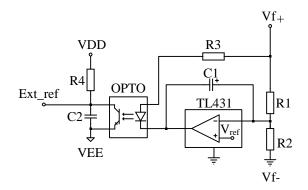

|      | Simulation block diagrams                                                     | 72 |  |

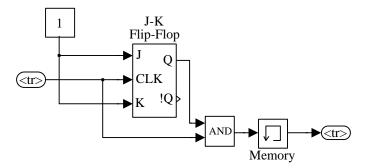

| 4.16 | ADC trigger - frequency divider                                               | 72 |  |

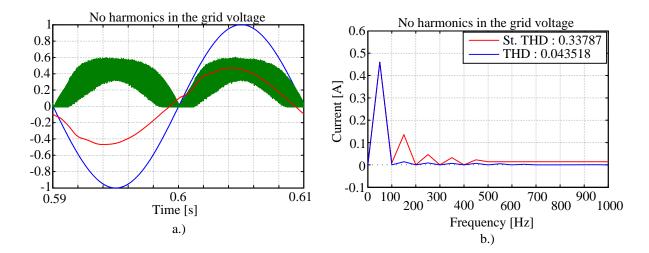

|      | Simulation results: a.) One line period - red: line current, green: boost     |    |  |

|      | inductor current, blue: normalized line voltage without voltage harmonics,    |    |  |

|      | b.) The current harmonic spectrum - red: Standard EN 61000-3-2, blue:         |    |  |

|      | simulated                                                                     | 74 |  |

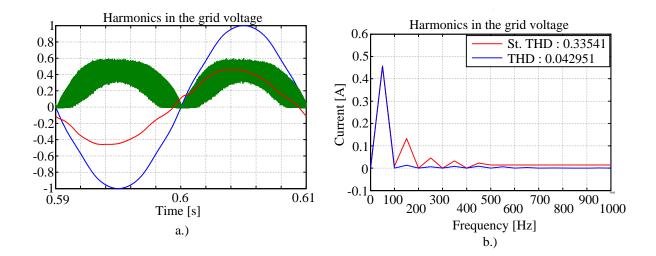

| 4.18 | Simulation results: a.) One line period - red: line current, green: boost in-                   |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | ductor current, blue: normalized line voltage with voltage harmonics added,                     |     |

|      | b.) The current harmonic spectrum - red: Standard EN 61000-3-2, blue:                           |     |

|      | simulated                                                                                       | 75  |

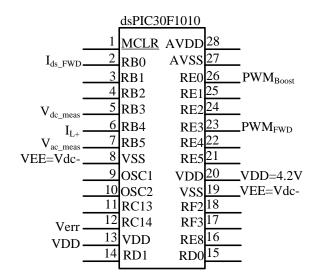

| 4.19 | dsPIC30F1010 microcontroller                                                                    | 76  |

| 4.20 | Peak current control - PWM reset                                                                | 76  |

| 4.21 | First boost measurements - pink: rectified line voltage, cyan: line current,                    |     |

|      |                                                                                                 | 77  |

| 4.22 | First forward measurements - pink: rectified secondary voltage, cyan: for-                      |     |

|      | ward MOSFET drain-source current, blue: drain-source voltage, green: gate                       |     |

|      | signals                                                                                         | 78  |

| 4.23 | Boost converter waveforms a.) Green: line current, pink: rectified line volt-                   |     |

|      | age, blue: boost voltage, red: line current harmonics. b.) Startup condition                    |     |

|      |                                                                                                 | 78  |

| 4.24 | Loadstep: a.) Full load to light load (green: line current, blue: Vdc boost                     |     |

|      | voltage). b.) Light load to full load (green: line current, blue: Vdc boost                     |     |

|      | voltage).                                                                                       | 79  |

| 4.25 | Green: Forward converter control signal. Orange: Drain-source current                           | 79  |

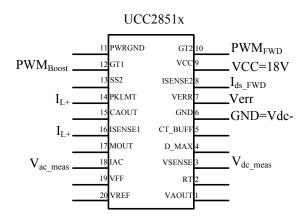

| 4.26 | Analog controller UCC28510                                                                      | 80  |

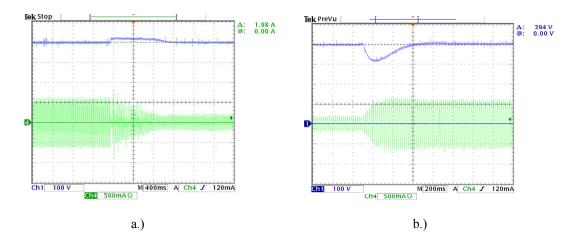

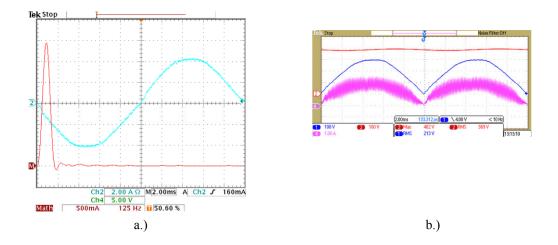

| 4.27 | a.) Boost converter waveforms b.) Forward converter waveforms                                   | 81  |

| 4.28 | a.) Boost inductor current b.) Forward drain source voltage                                     | 81  |

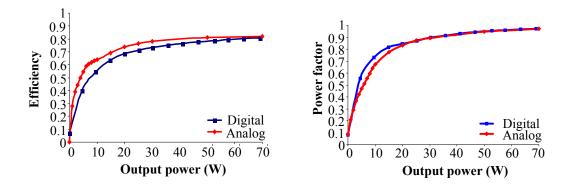

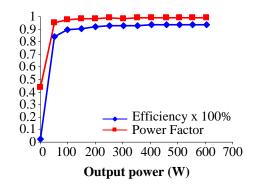

| 4.29 | Measure efficiency and power factor                                                             | 81  |

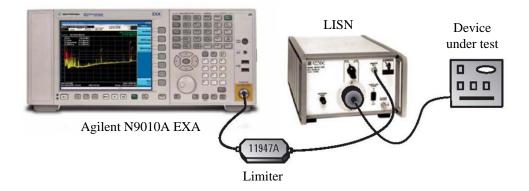

| 4.30 | Conducted emission measurement setup $[109]$                                                    | 82  |

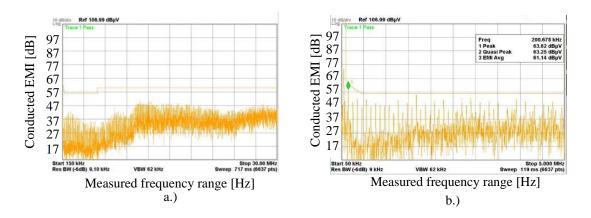

| 4.31 | Conducted EMI test results for a.) analog and b.) digital controlled converter                  | 82  |

| 4.32 | Interleaved boost converter                                                                     | 84  |

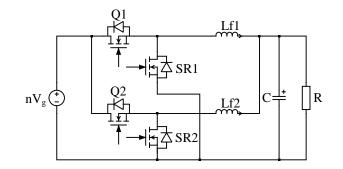

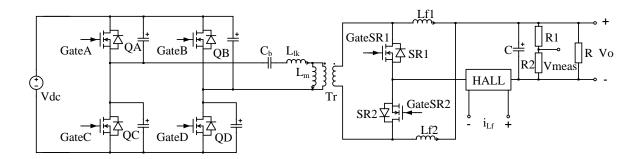

| 4.33 | Phase-shifted full-bridge converter with current doubler                                        | 85  |

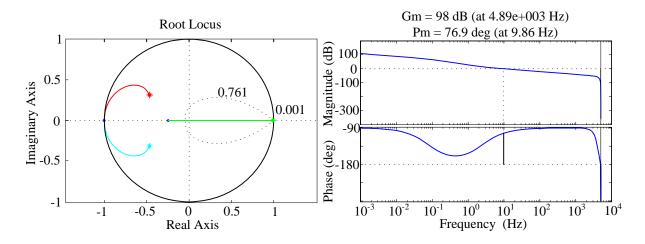

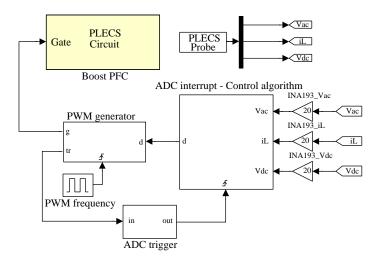

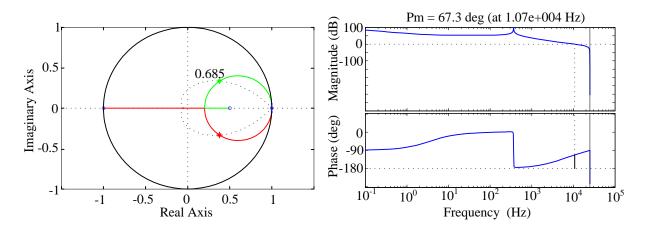

| 4.34 | Current loop - Root locus with closed loop poles and open loop bode diagram                     | 88  |

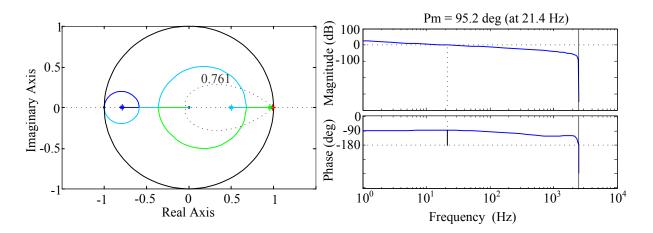

| 4.35 | Voltage loop - Root locus with closed loop poles and open loop bode diagram                     | 90  |

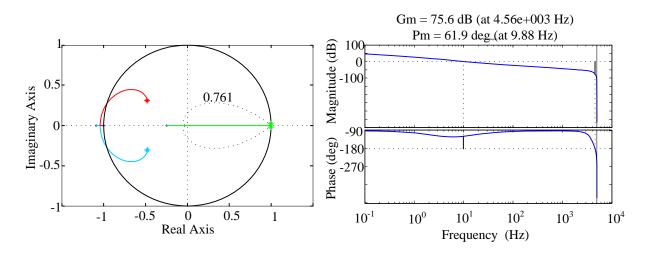

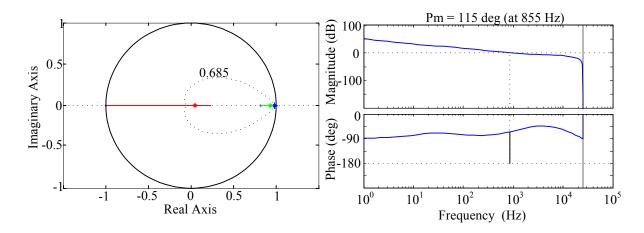

| 4.36 | Phase-shifted full-bridge converter - current loop design                                       | 92  |

| 4.37 | Phase-shifted full-bridge converter - voltage loop design with PI controller                    | 93  |

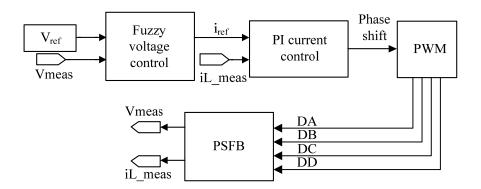

| 4.38 | Block diagram of the Fuzzy control system                                                       | 94  |

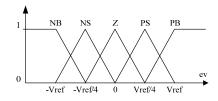

| 4.39 | The voltage error $ev$ membership functions                                                     | 95  |

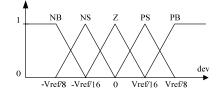

| 4.40 | The voltage error $dev$ membership functions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 95  |

| 4.41 | Output singleton membership functions                                                           | 95  |

| 4.42 | Fuzzy incremental control block                                                                 | 96  |

| 4.43 | Simulation blocks for interleaved boost converter                                               | 97  |

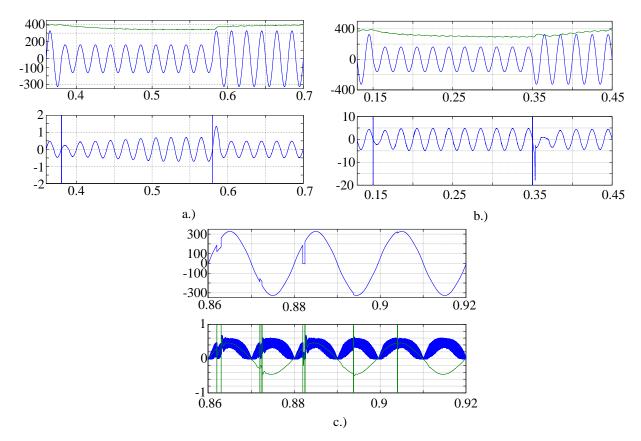

| 4.44 | a.) Normalized line voltage (blue) and line current (red) b.)Boost inductor                     |     |

|      | currents (blue and green) and the total inductor current (red) $\ldots \ldots$                  | 98  |

| 4.45 | Line current harmonics compared to EN 61000-3-2 Class C                                         | 99  |

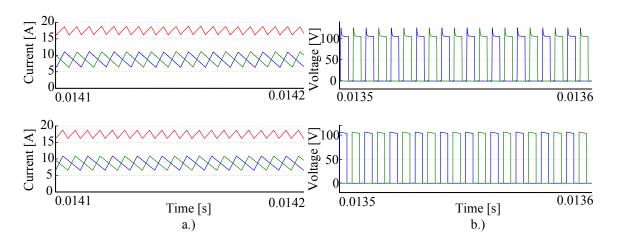

| 4.46 | 600W PSFB simulated waveforms                                                                   | .00 |

| 4.47 | Phase-shifted full-bridge converter - simulation blocks                                         | 01  |

| 4.48 | Load step with Fuzzy controlled voltage loop: blue - output voltage (V),                        |     |

|      | green - summed filter inductor current (A), red - output current (A) 1                          | 02  |

| 4.49 | Load step with PI controlled voltage loop: blue - output voltage (V), green                     |     |

|      | - summed filter inductor current (A), red - output current (A) 1                                | 02  |

| 4.50         | dsPIC33FJ32GS406 microcontroller                                                                                                                         | , |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4.51         | Controlled optocoupler for voltage measurement                                                                                                           | - |

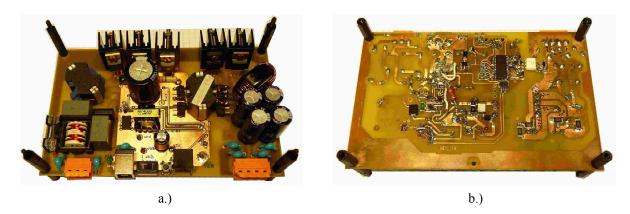

| 4.52         | The 600W power supply                                                                                                                                    | ) |

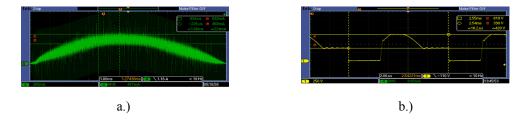

| 4.53         | Sampled data in numerical form sent back from dsPIC to Matlab: a.) Inter-                                                                                |   |

|              | leaved boost waveforms: Top - rectified line voltage, Middle - uncontrolled                                                                              |   |

|              | inductor current, Bottom - uncontrolled DC link voltage; b.) PSFB wave-                                                                                  |   |

|              | forms: Top - sum of the filter inductor currents, Bottom - uncontrolled                                                                                  |   |

|              | output voltage                                                                                                                                           | Ì |

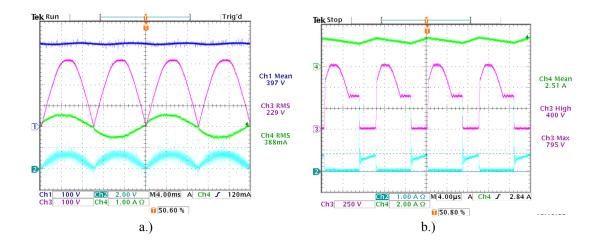

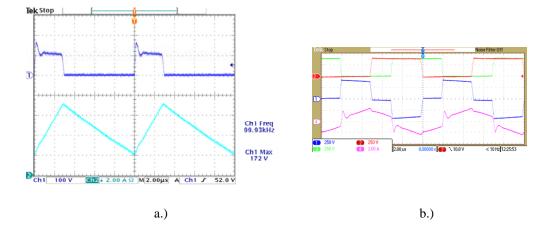

| 4.54         | 600W interleaved boost converter waveforms: a.) Cyan - sinusoidal line                                                                                   |   |

|              | current, Red - harmonic content of the line current; b.) Blue - rectified line                                                                           |   |

|              | voltage, Pink - interleaved boost inductor current $i_{L1}$ , Red - interleaved                                                                          |   |

| 4 55         | boost capacitor voltage                                                                                                                                  |   |

|              | Measured efficiency and power factor of the interleaved boost converter 107                                                                              |   |

| 4.30         | 600W PSFB waveforms a.) Blue - drain-source voltage on one synchronous rectifier SR1, Cyan - filter inductor current $i_{Lf1}$ b.) Blue - Voltage on the |   |

|              | primary side of the transformer, Red - drain-source voltage on QA, Green                                                                                 |   |

|              | - drain-source voltage on QD, Pink - current in the primary winding of the                                                                               |   |

|              | transformer $\ldots$                                                    | , |

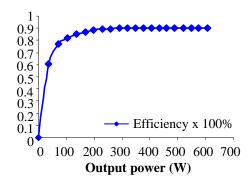

| 4.57         | Measured efficiency of the PSFB converter                                                                                                                |   |

|              |                                                                                                                                                          |   |

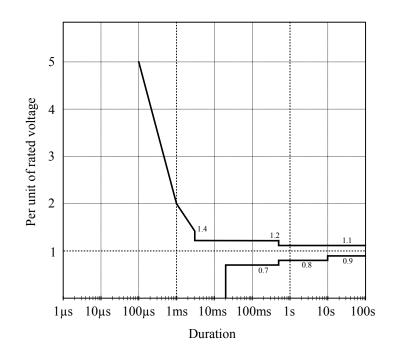

| 5.1          | ITIC (CBEMA) voltage sag immunity curves $[120]$                                                                                                         |   |

| $5.2 \\ 5.3$ | SEMI E10 voltage sag ride-through curves: $[130]$                                                                                                        | : |

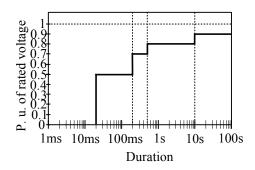

| 0.0          | a.) Voltage sag of 50% of the line voltage lasting 200 ms for the 70W converter at nominal power - top: green - DC boost voltage, blue - line            |   |

|              | voltage, bottom: line current; b.) Voltage sag of 50% of the line voltage                                                                                |   |

|              | lasting 200 ms for the 600W at nominal power - top: green - DC boost                                                                                     |   |

|              | voltage, blue - line voltage, bottom: line current; c.) Notches in the line                                                                              |   |

|              | voltage - top: line voltage, bottom: green - line current, blue - boost inductor                                                                         |   |

|              | current                                                                                                                                                  | ) |

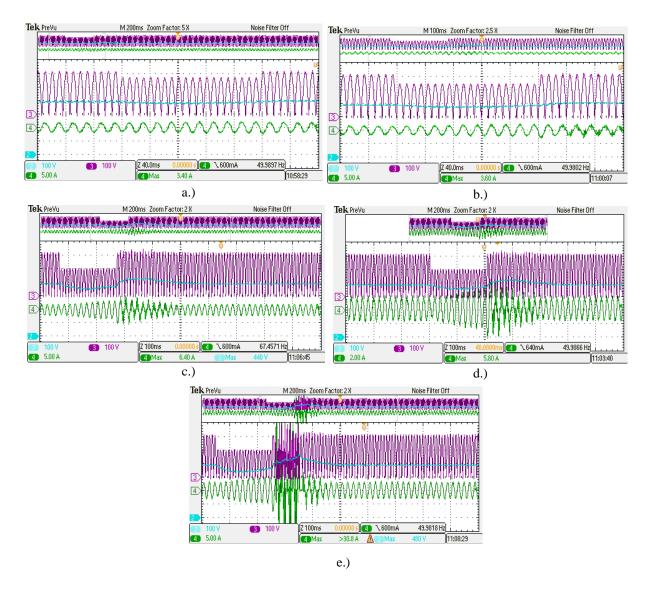

| 5.4          | Cyan - DC boost voltage, purple - rectified line voltage, green - line current;                                                                          |   |

|              | a.) Voltage sag to 200V from 230V of the line voltage lasting 200 ms at                                                                                  |   |

|              | 250W b.) Voltage sag to 180V from 230V of the line voltage lasting 200 ms                                                                                |   |

|              | at 250W; c.) Voltage sag to 150V from 230V of the line voltage lasting 200                                                                               |   |

|              | ms at 250W; d.) Voltage sag to 150V from 230V of the line voltage lasting                                                                                |   |

|              | 200 ms at 350W; e.) Voltage sag to 150V from 230V of the line voltage lasting 200 ms at 450W                                                             |   |

|              | lasting 200 ms at 450 w                                                                                                                                  |   |

| B.1          | Boost converter schematic                                                                                                                                | 1 |

| B.2          | Two output forward converter schematic                                                                                                                   | , |

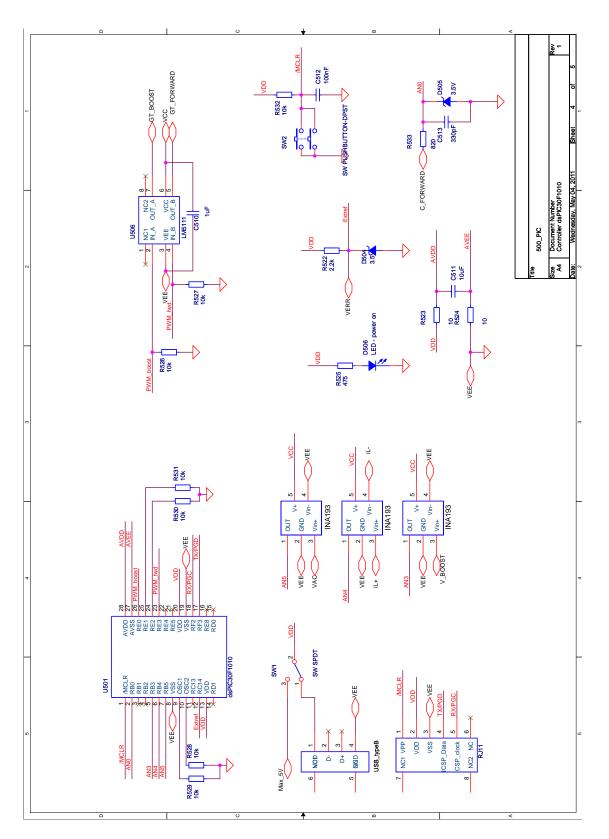

| B.3          | dsPIC connections - dsPIC30F1010 - schematic                                                                                                             | : |

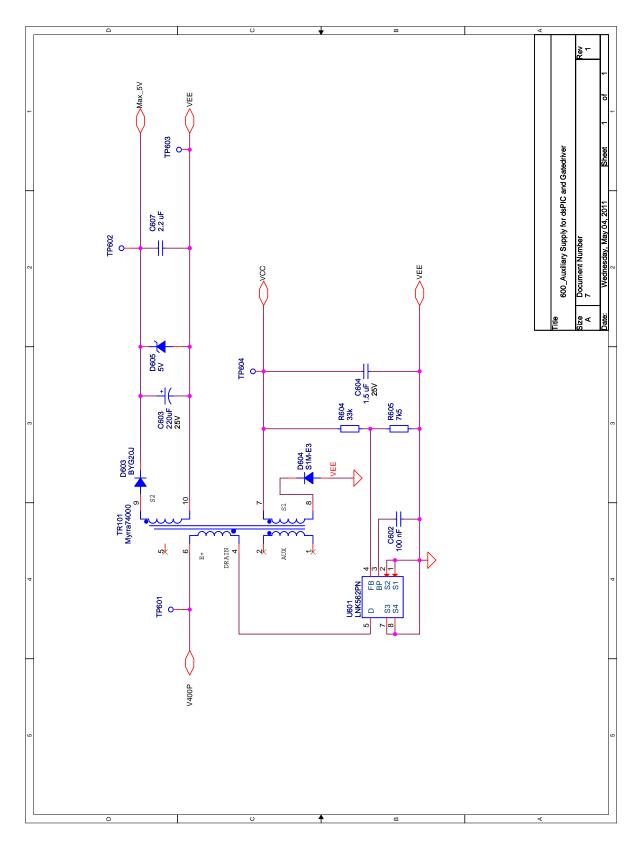

| B.4          | Auxiliary power supply schematic                                                                                                                         |   |

| B.5          | Analog controller - UCC2851x - schematic                                                                                                                 |   |

| B.6          | Interleaved boost converter schematic                                                                                                                    |   |

| B.7          | PSFB converter with synchronous rectification and current doubler schematic149                                                                           |   |

| B.8          | Auxiliary power supply and dsPIC connections - dsPIC33FJ32GS406 schematic15                                                                              |   |

| B.9          | Voltage feedback with optical isolation schematic                                                                                                        |   |

## List of Tables

| 4.1 | Most significant harmonic components present in the line voltage 74 |

|-----|---------------------------------------------------------------------|

| 4.2 | Inference table - I                                                 |

| A.1 | Boost inductor design parameters                                    |

| A.2 | N87 ferrite material properties                                     |

| A.3 | RM10 core parameters                                                |

| A.4 | Forward transformer design parameters                               |

| A.5 | Interleaved boost inductor design parameters                        |

| A.6 | Kool Mu 0077324A7 core parameters                                   |

| A.7 | PSFB transformer design parameters                                  |

| A.8 | ETD44 core parameters                                               |

# Chapter 1 Introduction

This thesis was meant to present the advantages and disadvantages using digital signal processors in grid connected switched mode power supply applications. The aim is to show that digital controllers are competitive and cost effective in controlling most of the high frequency converters in comparison to the state-of-the-art analog controllers. Limitations for digital control like special types of converters and control methods are also highlighted.

#### 1.1 Motivation

Recent developments in digital signal processor technology show a way of changing from analog controllers, which are widely used nowadays in power supply applications, to digital controllers. The cost of digital microprocessors has dropped in the last years [1]. Programming digital controllers in high level languages makes them easy to use: allows flexibility in control algorithm modifications without significant hardware changes. The absence of the phenomenon of aging and less thermal and noise sensitivity, present in analog controllers [2], is on the favor of digital solutions. Also the demand for system-module communication requires more sophisticated control platform than analog controllers. Beside the advantages of digital controllers there are many drawbacks like system integration, auxiliary power supply, discretizing and sampling errors, data transport delay, number representation etc... Also communication between system and module is getting an essential need in order to prevent faults and react in time with redundant elements in case of errors. All these issues together with the design of the power converters to suit the demands of digital control, different standards and requirements make an interesting research subject.

This work is part of the INLED (Intelligent Light Emitting Diodes) project and it has been carried out in cooperation with Martin Professional A/S and Aalborg University, Department of Energy Technology with the objective of investigating and developing grid converters for LED-based intelligent light sources. The project was co-funded by Højteknologifonden, Danmark. The objective of the project is to increase the knowledge in LED based luminaire technology and using this knowledge substitute the existing technologies. The project focuses on creating: optics with nano scale coatings that would maximize the light transmission from LED diodes to the output port, efficient power electronic drivers supplying power to the diodes and a heat management system for the

#### luminaire.

The term *intelligent lighting* means the ability to control position, beam, color-mixing of a lighting fixture. The products today use traditional technologies like discharge and incandescent lamps. A rapidly growing percentage of new products are based on LED technologies, due to some benefits of it: longer lifetime, potentially reduced energy usage, smaller size and weight. To power the LED a voltage of 4-6 V is required, obtained from the single phase grid (universal line voltage of 85V to 270V). The power consumed by the LEDs has to be converted in 3 power stages (PFC, step-down DC-DC and LED driver DC-DC converters), and each conversion step dissipates heat. In this project the AC-DC and DC-DC stages was optimized to minimize the material usage of EMI filter, magnetic components and cooling systems. To maintain system performance an increased level of semiconductors and signal processing was introduced. Digital control of the converters was implemented in embedded digital signal processors (DSP).

The thesis also presents the results of the research done in the SECURITAC project -7th Framework Programme - High reliability, low cost, stackable power supply for security systems. Security systems (including fire, intrusion, access control, and voice alarm) typically contain an AC-DC power supply to deliver power to the system and to charge and maintain 12V batteries, which provide the secondary source during a mains failure. The combined power supply-charger-battery system represents a key component of such systems in terms of cost and contribution to system reliability. In addition, as amendments were made to the applicable EN standards (EN54-4/A2, EN50131-6, EN60849, etc) manufacturers are often required to re-design, re-test and re-certify each power supply design, which represents significant actual and opportunity costs. As such, the objective of this project was to address the costs associated with existing security system power supplies, and at the same time significantly improve the manufacturability, reliability and the feature set of these key components. The stackable (load sharing) approach offered increased reliability through design and redundancy and cooler operation by spreading component heat over a larger surface area. Manufacturing costs were minimized via the manufacture of high volumes of a common module to suit a wide product range.

#### **1.2** Problem Formulation

The increased number of electrical equipment connected to the mains arise different potential side effects such as voltage distortion and pulsating, non-sinusoidal line currents causing functional disorders to other consumers and affecting the power distribution system. The most common malfunctions that can appear in power electrical systems are overheating of the components due to current distortion, fast deterioration of switching components, mechanical oscillations of motors, isolation failure due to possible over-voltages, audio noise and radio interferences. This is due to the nonlinear characteristic of the power circuits and loads [3]. The nonlinear loads need some power conditioning. To reduce the negative impacts of power electronic systems to the utility grids and their electrical environment the engineers have big responsibility to design the power conditioning circuits to prevent generating and distributing harmonic currents and reduce electro-magnetic interferences.

Not only designing but also controlling these power converters needs distinguished

attention. Although numerous integrated analog solutions exist the evolution of low-cost and high speed microprocessors makes digital control cost-effective and real possibility and opens new perspectives in controlling high frequency switched-mode power supplies. Also it have to be considered the recent needs for a human-machine interface, which allows the user to monitor the behavior of the equipment. This is impossible without involving microprocessors. To make digital control really competitive to analog controllers problems like integration of the microcontrollers, power consumption, metering errors at high speed sampling has to be investigated.

The first aim of the research project is:

• To examine and compare the suitable topologies for digital control in order to have the required power conditionings: power factor correction, isolation and have the required nominal output power.

In order to implement digital control there are different issues which have to be considered. Additional cost is one major issue which comprehends the price of digital controller and addition components compared to analog controllers, but also technical problems, like supply for the controller and auxiliary components (sensors, amplifiers, gate drivers) has to be taken into account. So, the second objective is

• To investigate the technical and economical problems integrating digital controllers on-board a power converter. Is it feasible to replace analog controllers with digital controllers?

Digital control, regardless how big the computational power of the controller is, it introduces errors in the real system due to PWM and sampling resolution and transport delay of the system. These errors have to be considered and compensated when designing the control algorithm. Therefore the third objective is:

• To develop, implement and evaluate digital control firmware considering all challenges in digital control.

Different limitations and regulations exist for grid connected converters from harmonic distortion (standards) to efficiency and stand-by operation mode (efficiency compliance regulations). Different components might influence the converter behavior such as magnetic components with core losses, saturation of the magnetic components, switching components with switching and conduction losses, the routing might introduce radiation. The converters needs to meet these regulations to be competitive with the market so the fourth objective is:

• To analyze the converter efficiency from no-load condition to full power operation and identify the different loss sources.

The increased demand for using the power supply network many times ends up in different unwanted events which can cause different deviations of the normal operation of the power grid - voltage sags, voltage fluctuations, frequency deviation etc.... In this condition grid connected power supplies have to be resistant to line faults. The last objective is:

• To analyze the converter behavior in response to line faults and investigate different safety mechanisms.

## **1.3** Contributions

- An investigation on the effect of the use of digital control in switch-mode powersupply applications was carried out. Controllers were designed for linearized discrete models of the power converters in discrete space and advantages and limitations such as processor speed, transport delay and sampling and PWM resolution were highlighted.

- A simulation platform was developed in Matlab/Simulink using triggered embedded Matlab functions to model digital control of different power converters with close to real life conditions.

- Digital signal processor-based control of four different converters (boost and interleaved boost PFC, forward and phase shifted full bridge DC-DC converters) with embedded processor to the main PCB was designed, built and tested. A low cost 16 bit fixed point dsPIC microcontroller was used, the firmware was written in C programming language. By scaling the measured data in a proper way, the algorithm can be implemented indifferent on the power level.

- Comparison of analog control and digital control of two identical 70W two-stage power facto corrector and DC-DC converters. The purpose was to investigate the cost effectiveness and efficiency of two stage PFC and DC/DC converters.

- Digital fuzzy logic voltage control proposed for output voltage regulation of a 600W phase-shifted full-bridge converter with synchronous rectification and current doubler. The designed controller shows better results in the system dynamics compared to a PI voltage controller using the same parameters. The Fuzzy algorithm was programmed in 16 bit fixed point dsPIC microprocessor.

- Analysis on the effect of grid disturbances on digitally controlled low-voltage-gridconnected power supplies.

## **1.4 Related Presentations and Publications**

Parts of the work presented in the thesis were published in different conference proceedings and reports:

Lajos, Török; Stig, Munk-Nielsen - "Simple digital control of a two-stage PFC converter using dsPIC30F microprocessor" - PEMD 2010 - The 5th IET International Conference on Power Electronics, Machines and Drives - 2010, Brighton, United Kingdom

Lajos, Török; Stig, Munk-Nielsen - "Efficiency and hardware comparison of analog control-based and digital control-based 70 W two-stage power factor corrector and DC-DC converters" EPE 2011 - EPE 2011 - The 14th European Conference on Power Electronics and Applications - 2011, Birmingham, United Kingdom

Lajos, Török; Stig, Munk-Nielsen - "Digital Fuzzy logic and PI control of phase-shifted full-bridge current-doubler converter", - INTELEC 2011 - The International Telecommunications Energy Conference - 2011, Amsterdam, The Netherlands

Lajos, Török; Szymon, Beczkowski; Jesper, Gadegaard; Thøger, Kari; Stig, Munk-Nielsen; Kjeld, Pedersen - "High Output LED-Based Profile Lighting Fixture" -IECON 2011 - 37th Annual Conference of the IEEE Industrial Electronics Society - 2011, Melbourne, Australia

Last paper sent for review:

Lajos, Török; Stig, Munk-Nielsen - "Effect of voltage sags on digitally controlled line connected switched-mode power supplies" - 13th International Conference on Optimization of Electrical and Electronic Equipment - OPTIM 2012, Brasov, Romania

## 1.5 Outline

The document is collected into the following six chapters:

*Chapter 1 Introduction* is the chapter where the motivation, background and problem statement is presented. It contains also a brief description of the contributions and acknowledgment of the knowledge. Finally the outline of the individual chapters is given.

Chapter 2 Converters, controllers and control methods is the chapter where the related previous work is presented. It starts with presenting the limitations and regulations regarding connecting power converters to the grid. For different power levels different power converters are recommended. A brief description of these converters is included. A market survey has been carried out regarding analog and digital controllers for different power supply applications. Different manufacturers produce switched mode power supplies with active power factor correction, controlled either by analog either by digital controllers. A market survey is presented also on this topic. To be able to implement an embedded power converter and controller system, auxiliary power supplies are required for the controller. Different solutions were investigated and presented in this chapter. The last part presents different control strategies suitable and less suitable for digital implementation.

Chapter 3 Digital control design presents the design requirements for digital control. It starts with the modeling of the power converter, in order to analyze its frequency behaviors. Discretizing the continuous model and the digital control itself it bears some challenges: the inadequate sampling frequency might introduce unexpected sampling errors, different digital controllers have different ADC and PWM resolutions resulting in quantization error. The delay between the calculation and updating of the duty cycle register also influences the the control stability. These challenges are presented within this chapter. The final part part describes the control design procedure: requirements for selecting the right control bandwidth, the characteristics of a fast current and a low bandwidth voltage loop design.

Chapter 4 Digital control in application presents a case study on two different power converters. A 70W two-stage PFC and DC-DC converter and a 600W two-stage PFC and DC-DC converter. Both with embedded digital controller. The 70W power supply is compared with an identical but analog controller driven one.

Chapter 5 The influence of grid disturbances on switched-mode power supplies describes different grid disturbances, analysis the grid codes and different requirements regarding switch mode power supplies. Also PFC converter control issues and dynamic behavior is presented.

Chapter 6 Conclusions and future work, is the chapter which concludes the work, points out the main contributions and suggests opportunities for future works.

## Chapter 2

# Converters, controllers and control methods

To supply any electrical equipment connected to the grid some power conditioning circuits are needed. These circuits and loads have highly nonlinear characteristics. The following chapter will present the different regulations that limit the line current and voltage distortion caused by the nonlinear loads and discuss upon a series of power factor corrector and DC-DC converter topologies and control strategies that are suitable for digital implementation. Also a market survey was carried out to present different analog and digital controllers.

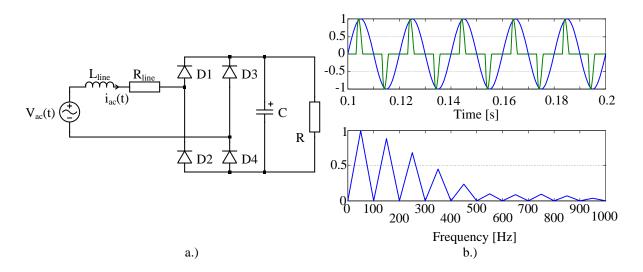

The simplest power conditioning circuit with the worst characteristic is the singlephase diode rectifier with capacitive output voltage filter (Figure 2.1 a.)). The AC side is influenced by the network impedance, the DC side ripple is determined by the filtering capacitor [5]. The line current is polluted with odd harmonics, the amplitude of the  $3^{rd}$ ,  $5^{th}$ ,  $7^{th}$  and  $9^{th}$  order harmonics are significant (Figure 2.1 b.)).

**Figure 2.1:** Capacitive filtered single-phase diode rectifier a.) Schematic b.) Waveforms - Top: Blue - Normalized line voltage, Green - Normalized line current; Bottom: Normalized Line current spectrum

#### 2.1 International standards

To overcome the problems caused by the current distortion and limit the line current harmonics different national and international standards were released. In the United States in 1981 was introduced standard IEEE-519-1981 with name: '*IEEE guide for harmonic control and reactive compensation of static power converters*' which deals only with voltage fluctuations. This was updated in 1992 to ANSI/IEEE-519-1992, '*IEEE recommended practices and requirements for harmonic control in electrical power systems*, which determines limits to voltage fluctuations and also current harmonics [6].

The International Electrotechnical Committee in 1982 published three-part standard IEC 555: part 1 - Definitions, part 2 - Harmonics [7], part 3 - Voltage fluctuations, which was later adopted by the European Committee for Electrotechnical Standardization as DS/EN 60555. In 1995 standard IEC 555 became part of the IEC 1000 standard family (respectively DS/EN 61000 standard family) and Part 3 of it considering limits of voltage and current harmonics.

Standard IEC 61000-3-2 is applied to to electrical equipment with an input current lower or up to 16  $A_{rms}$  per phase which are intended to be connected to low voltage (single phase 50 Hz system with 220-240  $V_{rms}$  and three phase systems with 380-415  $V_{rms}$ ) power distribution system. The standard limits the harmonic content of the injected currents to the supply system. The electrical equipment are classified in four groups (**A**,**B**,**C**, and **D**) [8].

Class A includes balanced three phase equipment, audio equipment, but excludes those equipment identified as belonging to Class D. The harmonic limits of the input current for Class A should not exceed the absolute values in given in table from Figure 2.3

Class **B** includes portable tools, non-professional arc welding equipment. The limits of the input current harmonics are shown in table from Figure 2.3 multiplied by a factor of 1.5

Class C includes lightning equipment. For lighting equipment the limit for input harmonic currents is shown in Figure 2.4

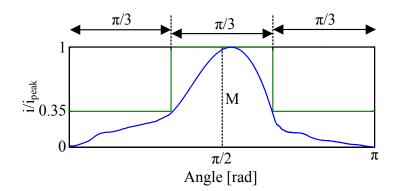

Equipment included in Class **D** should have a special input current shape and an active power  $P \leq 600W$  (Figure 2.2). The limits for input harmonics are presented in table from Figure 2.5 The input current shape should fit in the envelope, presented in Figure 2.2, in every half period in 95%. So if the current has small peaks outside the envelope the equipment can be considered as class D equipment. The center line M coincide with the peak value of the input current [8]. The current wave shape presented in Figure 2.2 can be achieved with open loop fixed duty cycle switching or simply turning off the switching devices in the middle of the interval. This will result in reduced switching losses around peak current. Since 2005 the requirements for Class D equipment has been extended to equipment with an input power  $P \geq 50W$ .

Standard IEC 61000-3-3 is concerned with the limitations of voltage fluctuations and flicker. It is applied to electrical equipment with an input current up to and including 16A per phase and intend to be connected to public low-voltage distribution system [9].

**Figure 2.2:** Green - envelop of the input current to define the 'special wave shape and to classify equipment as Class D' [8]; blue - simulated current waveform (overloaded 70 W boost PFC converter with saturated current controller)

| Harmonic order    | Maximum permissible       |

|-------------------|---------------------------|

|                   | harmonic current          |

| n                 | Α                         |

| Odd               | harmonics                 |

| 3                 | 2.30                      |

| 5                 | 1.14                      |

| 7                 | 0.77                      |

| 9                 | 0.40                      |

| 11                | 0.33                      |

| 13                | 0.21                      |

| $15 \le n \le 39$ | $0.15 \cdot \frac{15}{n}$ |

| Ever              | h harmonics               |

| 2                 | 1.08                      |

| 4                 | 0.43                      |

| 6 0.30            |                           |

| $8 \le n \le 40$  | $0.23 \cdot \frac{8}{n}$  |

Figure 2.3: Limits for Class A equipment [8]

| Harmonic order                          | Maximum permissible harmonic current   |  |

|-----------------------------------------|----------------------------------------|--|

|                                         | expressed as a percentage of the input |  |

|                                         | current at the fundamental frequency   |  |

| n                                       | %                                      |  |

| 2                                       | 2                                      |  |

| 3                                       | $30 \cdot PF^*$                        |  |

| 5                                       | 10                                     |  |

| 7                                       | 7                                      |  |

| 9                                       | 5                                      |  |

| $11 \le n \le 39$                       | 3                                      |  |

| (odd harmonics only)                    |                                        |  |

| * <i>PF</i> is the circuit power factor |                                        |  |

Figure 2.4: Limits for Class C equipment [8]

| Harmonic order      | Maximum permissible<br>harmonic current | Maximum permissible<br>harmonic current |

|---------------------|-----------------------------------------|-----------------------------------------|

|                     | per watt                                |                                         |

| n                   | mA/W                                    | Α                                       |

| 3                   | 3.4                                     | 2.3                                     |

| 5                   | 1.9                                     | 1.14                                    |

| 7                   | 1.0                                     | 0.77                                    |

| 9                   | 0.5                                     | 0.40                                    |

| 11                  | 0.35                                    | 0.33                                    |

| $13 \le n \le 39$   | $\frac{3.85}{n}$                        | As in Class A                           |

| (odd harmonic only) |                                         |                                         |

Figure 2.5: Limits for Class D equipment [8]

The EMI (electromagnetic interference) is the amount of radiation emitted by electrical equipment when operating. EMI is caused caused by emissions in the radio spectrum due to rapid voltage or current changes, which not only interfere with radio systems but also can cause other equipment to malfunction. This interference might not be so harmful when it appears in household equipment like radio, television but it could result in severe catastrophes when it appears for example in the control system of the airplanes.

Due to universal presence of the electromagnetic devices and their possible negative effects different agencies have tried to put regulations to minimize the electromagnetic emission levels. The European standard [50] considers two different equipment categories. Class B equipment are residential use equipment with no fix place of use with built-in battery, telecommunication terminals, personal computers and auxiliary connected equipment. These equipment should meet the limits described in Figure 2.7. Class A equipment are industrial equipment and should meet the limits shown in Figure 2.6. These equipment are not restricted in their sale but should be considered that in domestic use they might cause radio interferences. The limitations are set for conducted common mode electromagnetic noise in a frequency bandwidth from 150kHz to 30MHz and are measured in  $\mu V$  units with a line impedance stabilization network (LISN).

| Frequency range | Limits     |         |

|-----------------|------------|---------|

|                 | $dB(\mu)$  | V)      |

| MHz             | Quasi-peak | Average |

| 0.15 to $0.50$  | 79         | 66      |

| 0.50  to  30    | 73         | 60      |

Figure 2.6: Limits for conducted disturbances at the mains ports of class A equipment [50]

| Frequency range | Limits               |          |

|-----------------|----------------------|----------|

|                 | $\mathrm{dB}(\mu V)$ |          |

| MHz             | Quasi-peak           | Average  |

| 0.15 to 0.50    | 66 to 56             | 56 to 46 |

| 0.50 to 5       | 56                   | 46       |

| 5 to 30         | 60                   | 50       |

Figure 2.7: Limits for conducted disturbances at the mains ports of class B equipment [50]

The following two tables present limitations of conducted common mode disturbances for equipment which are connected to telecommunication lines (ex. telephone cables connected to ADSL modems can be affected by the PC supply).

|   | Frequency range | Voltage limits       |          | Current limits       |          |

|---|-----------------|----------------------|----------|----------------------|----------|

|   |                 | $\mathrm{dB}(\mu V)$ |          | $\mathrm{dB}(\mu A)$ |          |

|   | MHz             | Quasi-peak           | Average  | Quasi-peak           | Average  |

| ĺ | 0.15 to $0.50$  | 97 to 87             | 84 to 74 | 53  to  43           | 40 to 30 |

| Ì | 0.50 to 30      | 87                   | 74       | 43                   | 30       |

Figure 2.8: Limits for conducted common mode disturbances of class A equipment [50]

| Frequency range | Voltage limits       |            | Current limits       |          |

|-----------------|----------------------|------------|----------------------|----------|

|                 | $\mathrm{dB}(\mu V)$ |            | $\mathrm{dB}(\mu A)$ |          |

| MHz             | Quasi-peak           | Average    | Quasi-peak           | Average  |

| 0.15 to 0.50    | 84 to 74             | 74  to  64 | 40 to 30             | 30 to 20 |

| 0.50 to 30      | 74                   | 64         | 30                   | 20       |

Figure 2.9: Limits for conducted common mode disturbances of class B equipment [50]

#### 2.2 Power factor correction - terminology

As a result of applying different standards, a new research topic has become very popular in power electronics: Power Factor Correction.

In case of pure sinusoidal waveforms the *Power Factor* (PF) can be defined like in equation 2.1. It is always a value between 0 and 1 [11]:

$$PF = \cos\phi = \frac{P}{V_{rms(sin)} \cdot I_{rms(sin)}}$$

(2.1)

where P is the average power,  $V_{rms(sin)}$  and  $I_{rms(sin)}$  are the rms voltage and current. The angle  $\phi$  is the phase angle between the current and voltage. This factor is usually called the *displacement factor*. The unity power factor occurs only for pure resistive loads. In this case the current is in phase, has the same shape and has same harmonic spectrum as the line voltage.

Although the line voltage is assumed to be sinusoidal because the harmonic distortion in most of the cases is quite low, the line current is non-sinusoidal due to the nonlinear loads. Therefore the classical definition of the power factor can not be applied. The power factor equation for general voltage and current waveforms can be written as:

$$PF = \frac{V_{rms} \cdot I_{1,rms} \cdot \cos\phi}{V_{rms} \cdot I_{rms}} = \frac{I_{1,rms}}{I_{rms}} \cdot \cos\phi = K_d \cdot \cos\phi$$

(2.2)

The factor  $K_d$  is called *distortion factor* and it is the ratio of the current to the fundamental and defines the harmonic content of the current. The power factor is dependent on the shift between the current and voltage (displacement factor) and the harmonic content of the current (distortion factor). The distortion factor can be defined in function of the *Total Harmonic Distortion* (THD). The THD is defined as a ratio of the rms value of the current not including the fundamental to the rms fundamental magnitude [10]:

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} I_n^2}}{I_1} \tag{2.3}$$

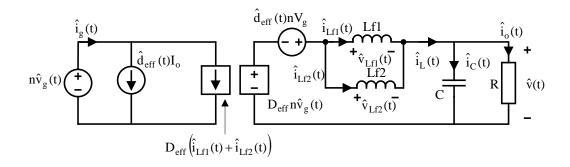

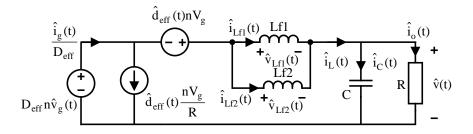

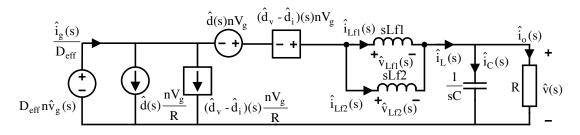

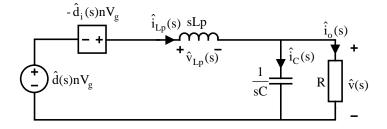

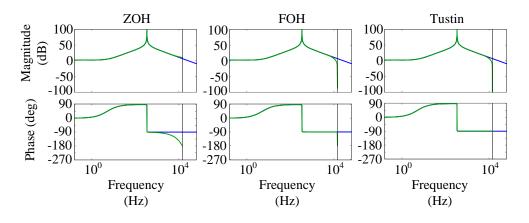

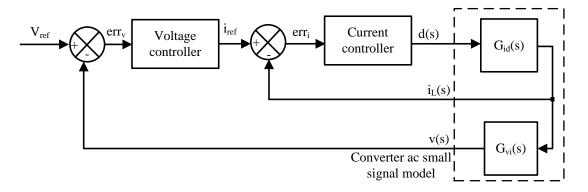

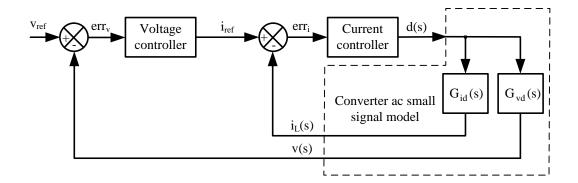

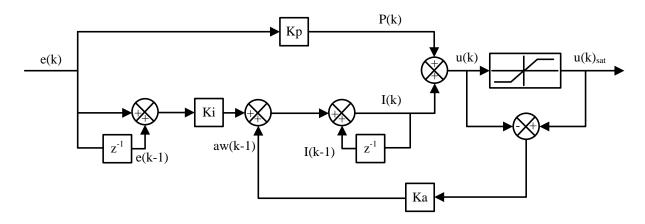

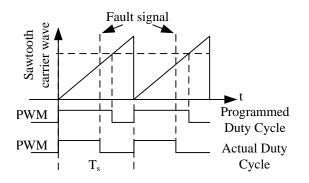

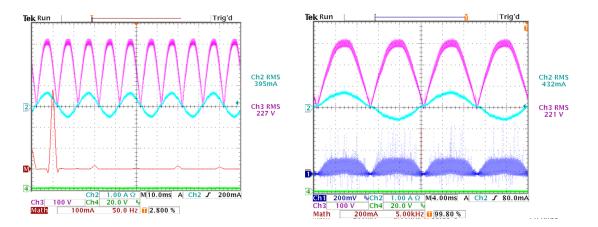

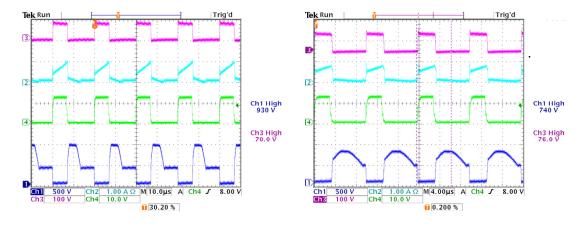

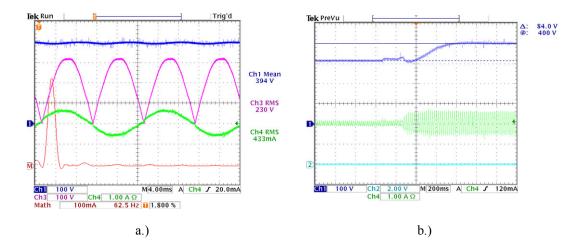

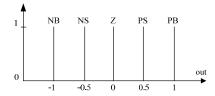

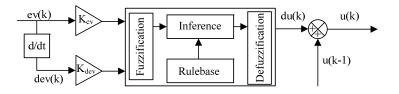

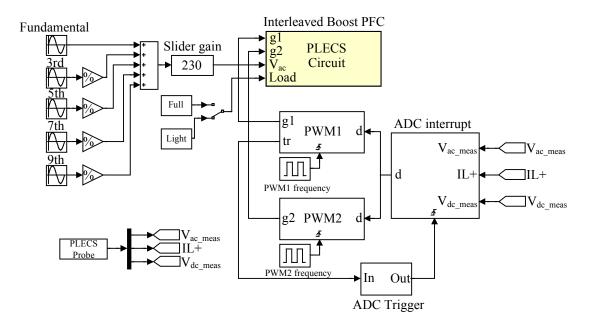

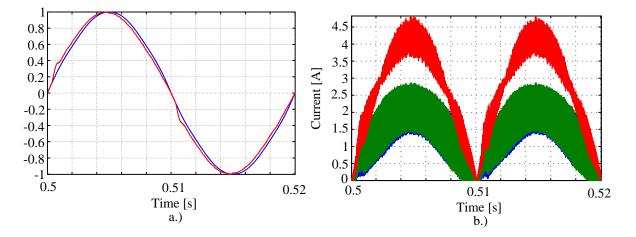

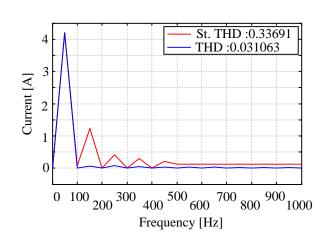

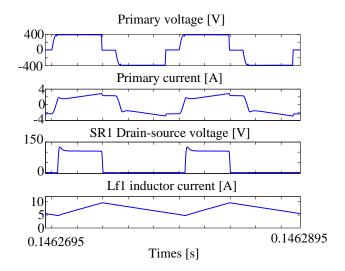

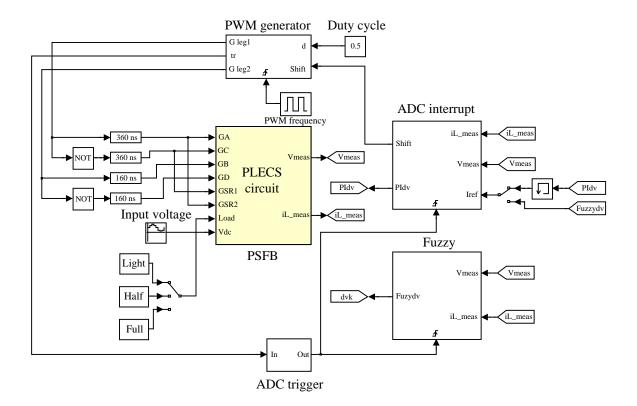

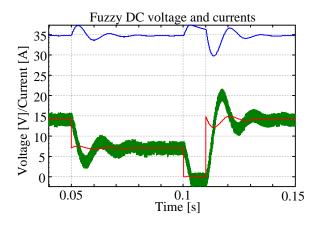

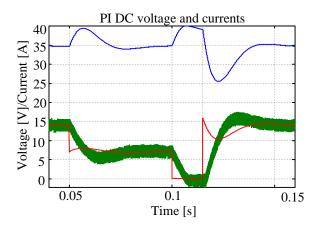

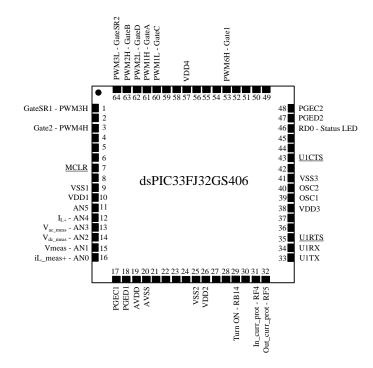

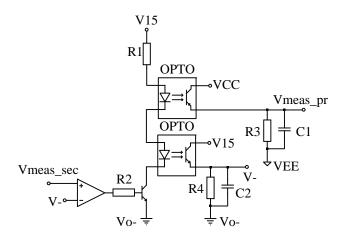

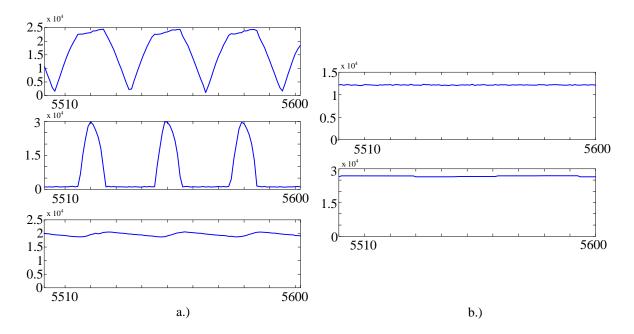

The  $K_d$  is closely related to the THD: