#### **Aalborg Universitet**

#### Mapping Framework for Heterogeneous Reconfigurable Architectures

Combining Temporal Partitioning and Multiprocessor Scheduling Popp, Andreas

Publication date:

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Popp, A. (2010). *Mapping Framework for Heterogeneous Reconfigurable Architectures: Combining Temporal Partitioning and Multiprocessor Scheduling*. Department of Electronic Systems, Aalborg University.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## Mapping Framework for Heterogeneous Reconfigurable Architectures

## Combining Temporal Partitioning and Multiprocessor Scheduling

PhD Dissertation

Andreas Popp

Mapping Framework for Heterogeneous Reconfigurable Architectures - Combining Temporal Partitioning and Multiprocessor Scheduling

PhD Dissertation

ISBN: 978-87-92328-44-1

August 2010

Copyright 2010 © Andreas Popp (except where stated otherwise) Technology Platforms Section Department of Electronic Systems, Aalborg University Niels Jernes Vej 12 9220 Aalborg Øst

### **Preface**

This dissertation is submitted to the Faculty of Engineering, Science and Medicine at Aalborg University in partial fulfillment of the requirements for the degree of Doctor of Philosophy. The work was conducted from April 2007 to August 2010 as a project funded by the Center for Software Defined Radio at Aalborg University in cooperation with Rohde & Schwarz Technology Center A/S in Aalborg.

#### Acknowledgements

I would like to thank my supervisors Yannick Le Moullec and Peter Koch for their inspiration, contributions, and support during the whole process from initiation to finish of the work. I also thank Rohde & Schwarz Technology Center A/S in Aalborg for their time for good discussions, pleasant working environment, and support for the project. A special thank goes to my colleagues at OFFIS, Institute for Information Technology in Oldenburg, Germany during my stay from Feb. 2009 to June 2009. Especially thanks to Kim Grüttner for his willingness to organize the stay, and to both him and Andreas Herrholz for their cooperation and contribution during my stay in Germany. I also thank Christophe Jégo from Telecom Bretagne for his hospitality in September 2009 as well as our cooperation. Furthermore, I would like the thank my colleagues at Aalborg University, Jesper Michael Kristensen, Mehmood Ur Rehman Awan, and Rasmus Abildgren for doing your best in making every workday an enjoyable time. The same goes for the rest of my colleagues in the Technology Platforms Section.

Last but not least I thank my family and friends for your encouragement, company, and support - I know that your company has given me the energy to work. A final thank goes to Helle for withstanding my lack of presence during the lasts months of work - your company and support has been of great value to me.

Aalborg, Denmark, August 2010

Andreas Popp

#### List of Abbreviations

The following abbreviations are used throughout the thesis:

ASIC Application-Specific Integrated Circuit

CAD Computer Aided Design

CLB Configurable Logic Block

CDFG Control Data Flow Graph

**CORDIC** COordinate Rotation DIgital Computer

DAG Directed Acyclic Graph

DFG Data Flow Graph

**DLS** Dynamic Level Scheduling

**DPR** Dynamic Partial Reconfiguration

**DSP** Digital Signal Processor

**EDA** Electronic Design Automation

EDLS Extended Dynamic Level Scheduling

**FFT** Fast Fourier Transform

**FPGA** Field-Programmable Gate Array

**GPP** General-Purpose Processor

**HW** Hardware

**ICAP** Internal Configuration Access Port

**ICD** Inter-processor Communication Delay

**ILP** Integer Linear Programming

ISE (Xilinx) Integrated System Environment

EDK (Xilinx) Embedded Developer's Kit

MMSE Minimum Mean Square Error

MIMO Multiple-Input Multiple-Output

**RTR** Run-Time Reconfiguration

SDF Synchronous Data Flow

**SDR** Software Defined Radio

SW Software

VHDL Very-High-Speed-Integrated-Circuit (VHSIC) Hardware Description Language

## Contents

| Co | ntent                           | s                                                                   | V                          |

|----|---------------------------------|---------------------------------------------------------------------|----------------------------|

| Ab | strac                           | t                                                                   | VII                        |

| Re | sumé                            |                                                                     | IX                         |

| 1  | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Motivation                                                          | 1<br>6<br>10<br>12<br>13   |

| 2  | Met l<br>2.1<br>2.2             | Modeling                                                            | 15<br>15<br>18             |

| 3  | <b>Sum</b> 3.1 3.2              | mary of Contributions Feasibility of Reconfigurable Implementations | 23<br>23<br>24             |

| 4  | <b>Con</b> 4.1                  | clusion Future Work                                                 | <b>27</b> 29               |

| 5  | List                            | of Publications                                                     | 31                         |

| Re | feren                           | ces                                                                 | 33                         |

| Co | ntril                           | outions                                                             | 39                         |

| Pa | per A  1  2  3  4               | Introduction                                                        | 41<br>43<br>45<br>50<br>52 |

#### **CONTENTS**

| 5              |                                                                     | 52 |

|----------------|---------------------------------------------------------------------|----|

| 6              |                                                                     | 54 |

| Re             | ferences                                                            | 54 |

| Paper          | B: Scheduling Temporal Partitions in a Multiprocessing Paradigm for |    |

| _              |                                                                     | 57 |

| 1              | Introduction                                                        | 59 |

| 2              | Mapping Methodology                                                 | 60 |

| 3              | Mapping Experiments                                                 | 64 |

| 4              |                                                                     | 67 |

| 5              | Discussion                                                          | 67 |

| 6              | Conclusion                                                          | 69 |

| Re             | ferences                                                            | 70 |

| Paper          | C: SystemC-AMS SDF Model Synthesis for Exploration of Heteroge-     |    |

| -              | • • •                                                               | 71 |

| 1              | Introduction                                                        | 73 |

| 2              |                                                                     | 74 |

| 3              | Methodology                                                         | 75 |

| 4              | Experiments                                                         | 81 |

| 5              |                                                                     | 83 |

| Re             | ferences                                                            | 84 |

| Paper          | D: A Mapping Framework for Heterogeneous Reconfigurable Archi-      |    |

| _              |                                                                     | 87 |

| 1              |                                                                     | 89 |

| 2              |                                                                     | 90 |

| 3              |                                                                     | 91 |

| 4              |                                                                     | 93 |

| 5              | Simulations                                                         |    |

| 6              | Case Study: Iterative Receiver for MIMO Systems                     |    |

| 7              | Discussion                                                          |    |

| 8              | Conclusion and Outlook                                              |    |

| D <sub>o</sub> | farances 1                                                          |    |

#### **Abstract**

The topic of this PhD dissertation is the development of a mapping framework to assist the designers and developers when developing hardware (HW) and software (SW) for reconfigurable systems.

The dissertation focuses on the combination and modification of existing temporal partitioning algorithms for reconfigurable architectures with existing multiprocessor scheduling algorithms. The result is the mapping framework that utilizes these algorithms. Temporal partitioning is used in order to generate HW supernodes, which are clusters of operations performed in HW. The proposed heterogeneous multiprocessor scheduling algorithm treats HW supernodes and tasks performed in SW similarly. The mapping framework provides the designer with a possible schedule for implementation, derived based on input from the designer. This input is composed of three elements: an application model describing the tasks to be performed, an architecture model describing the processing units and their interconnection, and a cost library describing the cost of the implementation of each task on the processing units. In addition to the mapping framework, a cost-model for reconfigurable implementations is proposed. The model is used to conduct a study in order to determine when it is beneficial (in terms of area and execution time costs) to perform a reconfigurable implementation as opposed to a static implementation.

The dissertation is composed of four parts: first, the related challenges and state-of-the-art in relation to reconfigurable architectures is provided. Focus is on design methods and the need for a framework which can handle the mapping of applications onto reconfigurable architectures. Second, the background, considerations, and assumptions of the proposed methodology are given with regard to the utilized models as well as the developed mapping framework. Third, a summary of the contributions is provided related to the published papers. Finally, a conclusion and outlook are given.

The main body of the dissertation is composed of three peer-reviewed papers and one paper submitted for peer-review and presents the contributions. The results show that the cost of a reconfigurable implementation is largely dependent on the reconfiguration time, and thereby dynamic partial reconfiguration has lower cost than dynamic full reconfiguration. The reconfiguration time is relatively high for current Field-Programmable Gate Arrays (FPGAs), but can be accepted for applications with large execution time or massively parallel applications, e.g. multimedia processing.

The developed framework is able to handle binding and scheduling for heterogeneous reconfigurable architectures based on provided application and architecture models, and cost library. Results show that our mapping framework provide feasible schedules that it is possible to implement. Level-based temporal partitioning has the best performance in combination with Extended Dynamic Level Scheduling.

#### Resumé

Emnet for denne ph.d. afhandling er udviklingen af et mappingværktøj, som kan assistere designere og udviklere under udvikling af hardware (HW) og software (SW) til rekonfigurerbare systemer.

Afhandlingen fokuserer på kombination og modificering af eksisterende algoritmer til "temporal partitioning" til rekonfigurerbare arkitekturer med eksisterende multiprocessor scheduleringsalgoritmer. Resultatet heraf er mappingværktøjet som anvender disse algoritmer. "Temporal partitioning" anvendes til at generere HW super-knuder, der er klynger af hardwareoperationer. Den foreslåede heterogene multiprocessor-scheduleringsalgoritme behandler HW super-knuder og operationer eksekveret i SW ens. Mappingværktøjet tilvejebringer designeren en mulig køreplan, "schedule", til implementering, afledt baseret på designerens input. Dette input består af tre elementer: en model for applikationen, som beskriver de operationer, som skal udføres, en arkitekturmodel, som beskriver processeringsenhederne, og hvordan de er forbundne samt et "cost"-bibliotek, som indeholder "cost" af implementeringen af hver operation i processeringsenhederne. I tillæg til mappingværktøjet er foreslået en model for "cost" af rekonfigurerbare implementeringer. Modellen er blevet anvendt i et studium til bestemmelse af, hvornår det er fordelagtigt (målt på "cost") at foretage en rekonfigurerbar implementering i modsætning til en statisk implementering.

Afhandlingen består af fire dele: Først gives udfordringer og state-of-the-art i forbindelse med rekonfigurerbare arkitekturer. Der fokuseres på design metoder samt behovet for et værktøj som kan håndtere mapping til rekonfigurbare arkitekturer. Dernæst gives baggrund, overvejelser og antagelser anvendt i mapping værktøjet med hensyn til de anvendte modeller af det udviklede mappingværktøj. Derefter gives et overblik over bidrag til området med relation til de publicerede artikler. Sidst gives en konklusion og perspektivering.

Hoveddelen af afhandlingen består af tre peer-reviewede artikler samt en artikel indsendt til peer-review og beskriver bidrag til emnet mapping metoder til heterogene rekonfigurerbare arkitekturer. Resultaterne viser at cost ved en rekonfigurerbar implementering er overvejende afhængig af rekonfigurationstiden, og derfor har dynamisk partiel rekonfiguration lavere cost end dynamisk fuld rekonfiguration. Rekonfigurationstiden er relativt høj for tidssvarende Field-Programmable Gate Arrays (FPGA'er), men kan accepteres for en applikation som har høj eksekveringstid eller en høj grad af parallellitet i applikationen, f.eks. multimedia-processering.

Det udviklede værktøj kan håndtere binding og schedulering til heterogene, rekonfigurerbare arkitekturer forudsat applikations- og arkitekturmodel samt "cost"-bibliotek. Resultaterne viser, at mapping-værktøjet tilvejebringer schedules, som det er muligt at implementere. "Level-based temporal partitioning" yder bedst i kombinationen med "extended dynamic level scheduling".

#### 1 Introduction

This chapter contains a motivation of reconfigurable computing architectures, highlighting the research challenges of reconfigurable computing. This is followed by an overview of state-of-the-art in mapping of applications to heterogeneous reconfigurable architectures. Finally, the thesis is formulated and an outline of the dissertation is given.

#### 1.1 Motivation

Implementation of signal processing algorithms in e.g. telecommunication and multimedia applications require processing architectures that provide enough computational power and are, at the same time, subject to constraints in terms of chip area or power consumption. Furthermore, telecommunication devices are required to provide multiple functionalities, some simultaneously, other only at some time-instants.

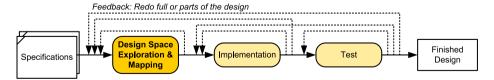

The aforementioned telecommunication and multimedia applications require more and more advanced functionalities, e.g. for improved spectrum usage or higher video quality. This causes an increase in the performance requirements and complexity of the reconfigurable architecture. When designing such a system, a designer may often follow the design trajectory, shown in Figure 1.1, which starts from a set of specifications and requirements. This is followed by design space exploration and mapping to evaluate implementation alternatives and find the best mapping for the application. The best mapping means fulfilling the requirements and constraints as well as minimizing the cost function

Figure 1.1: Overall design trajectory: The outset is a set of specifications describing the requirements to the application (behavior, physical factor, cost etc.) Then design space exploration and mapping are performed in order to evaluate various implementation alternatives and find the mapping that is the optimum for the application. This is then implemented and tested in order to obtain the final design. At any step of the design, it may be necessary to do an extra iteration or go one or more steps back in order to fulfill the requirements.

(see below). This mapping is then implemented and tested. The design may include several iterations, which in turn, cost money to the company developing the application due to the caused extension of development time.

Finding the correct final design is often a matter of trade-off between costs and performance, with a large design space covering the possible architectures and mappings. Mapping is composed of two design challenges: binding, where it is decided onto which processing unit a task should be implemented, and scheduling, where it is decided when tasks should be executed. We define scheduling to be relative in time, i.e. tasks are scheduled in relation to each other. Design space exploration is the evaluation of possible solutions with regard to a cost function, (1.1), where some of the parameters (e.g. area or execution time) may be constrained by the requirements. Searching the full design space is an extensive task, where obtaining a minimal cost solution within constraints of e.g. execution time or hardware resources is known to be NP-hard [3], and may thus be impossible for designers to complete in reasonable time. Therefore, there is a need for methodologies and tools that can help the designers to prune the design space in a reasonable time and thereby be compatible with the company's time schedule. We believe that a tool that can aid the designer during the design space exploration process is necessary in order to shorten the product development process and thereby meet the time-to-market requirements.

The cost, C, of an implementation may be measured by a cost function,

$$C = f(T, A, P, N) \quad , \tag{1.1}$$

where T is execution time, A is area or resource consumption, P is power consumption, and N is the numerical noise. Each of the parameters are assigned weight factors that define their importance, giving a cost function such as  $C = \alpha T + \beta A + \gamma P + \dots$  A cost function could also include other parameters such as price and development time.

Typical architectures for signal processing equipment consist of either (or a combination of) Application-Specific Integrated Circuits (ASIC) and Digital Signal Processors (DSPs). However, these components can generally be considered as fixed and efficient, or flexible and less efficient, respectively. In order to obtain a reasonable trade-off between these two end-points, the trend goes towards reconfigurable architectures [1], which offers this trade-off between ASICs and DSPs. The comparison between various architectures, as proposed in [2], is shown in Table 1.1 and illustrates that reconfigurable hardware can potentially offer the best trade-off by providing medium-high performance and high flexibility.

Reconfigurable hardware is motivated due to several advantages compared to ASIC or SW architectures. First, it is possible to increase the functionality of the same hardware by time-sharing of resources and thus obtain a reduction in chip area. Area-reduction also reduces the static power of the circuit, which is becoming a larger and larger part of the power consumption [4]. As a side effect of area reduction as well as the possibility of using reconfiguration to deactivate circuits, reconfiguration can also reduce the energy consumption. Finally, the flexibility of a reconfigurable hardware platform is of great use for e.g. Software Defined Radio (SDR) [5], where there is a large requirement for flexibility of the architecture. Further motivations and more precise examples of application of reconfigurable hardware are given in Section 1.2.

| Technology           | Performance | System      | Cost/Chip   | Power       | Flexibility |

|----------------------|-------------|-------------|-------------|-------------|-------------|

|                      |             | Design Cost |             |             |             |

| General-Purpose      | Low         | Low         | Low-Medium  | High        | High        |

| Processor (GPP)      |             |             |             |             |             |

| Digital Signal       | Medium      | Medium      | Low-Medium  | Medium      | Medium      |

| Processor (DSP)      |             |             |             |             |             |

| Reconfigurable       | Medium-High | Medium      | Medium-High | Medium-High | High        |

| Hardware             |             |             |             |             |             |

| Application-Specific | High        | High        | Low         | Low         | Low         |

| Integrated Circuit   |             |             |             |             |             |

| (ASIC)               |             |             |             |             |             |

Table 1.1: Qualitative comparison of implementation technologies, excerpt from Gokhale and Graham [2, Table 5.1]. Performance is a measure of execution time and throughput. System Design Cost is the total cost of design, i.e. the expenses for tools and engineering.

Even though we have introduced and briefly motivated reconfigurable hardware, it has not yet been defined. We use the definition inspired by Compton and Hauck [6] and define the following terms in Definition 1 and 2.

**Definition 1.** Reconfigurable hardware is hardware incorporating some form of hardware programmability, by which we mean the ability to change the behavior of the logic residing in the hardware.

**Definition 2.** *Reconfigurable architectures* are processing architectures consisting of one or more reconfigurable hardware units.

Reconfigurable hardware is characterized by its granularity, i.e. the smallest amount of logic that can be reconfigured. We generally distinguish between fine- and coarse-grained reconfigurable logic [7]. *Fine-grained logic* can be reconfigured down to 1 or 2 bit, both in function logic blocks as well as routing between the blocks. An example of fine-grained logic is Field-Programmable Gate Arrays (FPGAs). *Coarse-grained logic* is reconfigurable in quantities of 8-32 bit, and has a structure similar to microprocessors with configurable logic or computation units. The differences between fine- and coarse-grained reconfigurable HW, as proposed in [7], are highlighted in Table 1.2.

| Parameter               | Fine         | Coarse      |

|-------------------------|--------------|-------------|

| Configurable logic size | 1-2 bit      | 8-32 bit    |

| Design approach         | Logic design | SW design   |

| Performance             | Less High    | High        |

| Flexibility             | High         | High-medium |

Table 1.2: Qualitative comparison of fine and coarse-grained reconfigurable hardware, excerpt from Hartenstein et al. [7]. Design approach describes the similarity of the design to other technologies.

In parallel with the granularity, reconfiguration is also divided into three categories depending on the frequency and fraction of the device that is reconfigured. These terms are technology independent.

**Static configuration** is the configuration of the full device at only one single time during operation. This may be either before starting the system, or during the start-up sequence. The functionality of the HW is fixed during the runtime of the system.

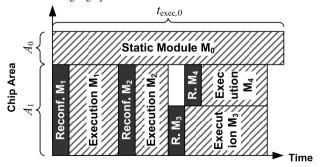

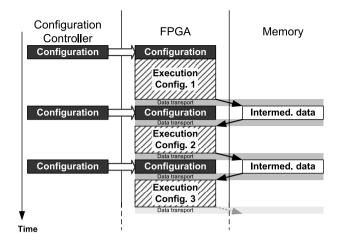

**Dynamic full reconfiguration** is dynamic in the sense that the functionality of the hardware can be reconfigured during the run-time of the system. However, reconfiguration is performed for the full hardware, thus interrupting execution and overwriting internal signals in the hardware. Therefore, it may be necessary to store the internal signals in external memory, as illustrated in Figure 1.2a.

**Dynamic Partial Reconfiguration (DPR)** or Run-Time Reconfiguration (RTR) is the most flexible type of reconfiguration. Similar to dynamic full reconfiguration the functionality can be changed during runtime. However, it is possible to reconfigure only part of the hardware, while the other parts are performing execution, as illustrated in Figure 1.2b. Those parts performing execution can be either static parts, that are constant during the full runtime, or parts that will be (or have been) reconfigured at other times.

(a) Dynamic full reconfiguration: The full chip area is reconfigured during runtime. Internal signals that must be used later need to be saved to/loaded from external memory. Thus data transport is marked in light gray.

(b) Dynamic partial reconfiguration: Parts of the chip area  $(A_1)$  are reconfigured during runtime while other parts  $(A_0)$  are still executing.

Figure 1.2: Illustration of dynamic full and partial reconfiguration. Reconfiguration is marked by dark gray whereas execution is marked by the diagonal line pattern.

To the best of our knowledge, the earliest work on reconfigurable architectures started by Estrin et al. in 1959 with the proposed "Fixed-plus-Variable (F+V) Structure Computer" consisting of a fixed computer plus a board with problem-specific optimized logic

blocks that could be replaced according to the application [8]. However, our definition of reconfigurable hardware is different as we rely on programmability and not the physical replacement of modules. Other reconfigurable architectures have been investigated, coarse-grain architectures mainly in the research domain [9, 10]. For further historic architectures, we refer to the surveys referenced later in this section.

Among the reconfigurable hardware devices, we believe that FPGAs are the most used at time of writing. Therefore, the remainder of this work considers reconfigurable architectures based on FPGAs. A recent study among embedded system developers showed that 42% of all current embedded designs contain an FPGA [11]. The most frequently used FPGA vendor was Xilinx. FPGAs contain three layers, where the first layer contains arrays of logic blocks and the second layer the routing between them. The actual configuration of the FPGA is determined by a third layer of memory, determining the functionality of the logic and routing in the first two layers.

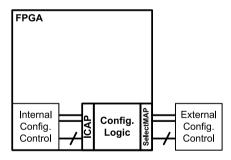

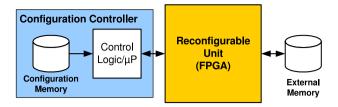

At the time of writing, Xilinx is the main company offering a commercially available solution for DPR. Xilinx FPGAs have several interfaces to the configuration memory [12]. For dynamic reconfiguration, the most useful ones are the SelectMAP and Internal Configuration Access Port (ICAP) interfaces with a throughput of 32 bit at 100 MHz. The selectMAP interface can be accessed from outside the FPGA (requiring an external controller) as illustrated in Figure 1.3. Furthermore, the configuration interface can also be accessed by internal signals inside the FPGA, after the FPGA has initially been configured from an external interface [12]. The internal interface is the Internal Configuration Access Port and provides the same throughput as the SelectMAP interface. The ICAP interface can be used from inside an FPGA in order to perform internally controlled partial reconfiguration via a controlling soft-core processor in the static part of the logic.

Figure 1.3: Illustration of SelectMAP and ICAP configuration interfaces for configuring Xilinx FPGAs. "Config." is short for *configuration*.

The FPGA can only allow one active reconfiguration interface at a time. Therefore, parallelized modules cannot be reconfigured in parallel and have to be scheduled sequentially on the configuration logic. This is illustrated in Figure 1.2b for the reconfiguration of module  $M_3$  and  $M_4$ , where the reconfiguration of module  $M_4$  has to wait for the reconfiguration of  $M_3$  to finish.

Surveys of the area of reconfigurable computing have been given by Compton and Hauck [6], Todman et al. [13], Shoa and Shirani [14] and several others, e.g. [15]. It is clear that reconfigurable hardware is not the sole component of a system, but does often form part of an architecture that both consists of several processing units, and is

heterogeneous in its composition in order to meet the constraints of the application. By a *heterogeneous architecture* we mean an architecture consisting of more than one processing unit and that there are at least two different units in the architecture, e.g. a HW/SW architecture.

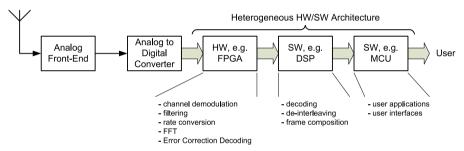

The cost function in (1.1) reflects that the cost of implementation is dependent on factors such as execution time, area, and power consumption. Signal processing applications typically consist of different blocks of algorithms with different characteristics as illustrated in Figure 1.4. Some may be massively parallel with high throughput and execution time requirements, while other may be sequential in structure with lower requirements to execution time. In order to maintain a low cost (defined by the cost function), a heterogeneous architecture often yields the lowest cost by e.g. performing time-critical parallel parts in HW and more sequential parts in SW. Other solutions may be a multi-processing solution with parallel processors to execute the parallel parts of the algorithm.

It is commonly accepted that there exist many challenges in the design of a system containing heterogeneous reconfigurable architectures. In the next section, we present our view on these challenges.

Figure 1.4: Example of a heterogeneous architecture in a radio receiver. After digitization in the analog-to-digital converter, the signal is processed in HW and SW. Some tasks (proposed below the blocks) are most suitable for HW, whereas some are more suitable for SW.

# 1.2 Challenges in the Design of Heterogeneous Reconfigurable Architectures

The design of applications implemented in heterogeneous reconfigurable architectures is a challenge within several areas. Based on surveys of reconfigurable computing, we see the challenges in three main groups, outlined in the sections below.

#### **Applications**

In order to justify the advantages of reconfigurable architectures over ASIC and DSP architectures, we provide a short survey of some applications implemented in reconfigurable hardware. The survey is a necessary part of the justification, as a quantification of the difference between ASIC and FPGA have shown that FPGA is a factor of 119x

larger in area compared to ASIC for a range of benchmarks ranging from Finite Impulse Response (FIR) filters to Reed-Solomon encoders/decoders [16].

A survey by Todman et al. [13] has shown a 500x speedup and 70% energy savings when using FPGAs instead of microprocessors for some applications. Helmschmidt et al. have presented an implementation of a Rake receiver for a Universal Mobile Telecommunications System (UMTS) and Wireless Local Area Network (WLAN) system in a heterogeneous reconfigurable architecture instead of parallel implementation of the two functionalities [17]. The architecture was a multiprocessor architecture with a controlling microprocessor, a digital signal processor, and a coarse-grain reconfigurable array.

In the field of Software Defined Radio, a reconfigurable Global System for Mobile communication (GSM) and Enhanced Data for GSM Evolution (EDGE) transmitter was implemented on a DSP/FPGA platform by Delahaye et al. [18]. The considered implementation consisted of a Gaussian filter and a Minimum-Shift Keying (MSK) and 8-Phase Shift Keying (8PSK) encoder. The authors investigated and compared full reconfiguration and partial reconfiguration to a static implementation. Results showed a 50% reduction in FPGA utilization due to the sharing of functionalities using both full and partial reconfiguration. The reconfigured parts had significant commonalities between them, so partial reconfiguration reduced the reconfiguration time from 130 ms to 11 ms.

Similarly, Tumeo et al. investigated the use of reconfigurable hardware instead of software for accelerating JPEG encoding [19]. Results showed a speedup for HW execution time of 3.02 compared to SW execution time. Furthermore, area savings of 30% were achieved.

Wang et al. [20] considered an FPGA-implementation of a Multiple-Input Multiple-Output (MIMO) square-root-decoder utilizing COordinate Rotation DIgital Computer (CORDIC) elements. The execution consisted of several stages utilizing the same CORDIC elements, but with changing CORDIC element registers and routing between the stages. Therefore, the reconfigurable area was relatively small leading to relatively low reconfiguration times. The results showed 30% area-savings due to the sharing of resources in the FPGA.

Implementations in reconfigurable hardware are illustrated by these examples to provide opportunities in terms of area and power consumption savings. Furthermore, reconfigurable architectures provide flexibility and adaptability that may be useful in Over-The-Air upgrade scenarios of radio terminals within Software Defined Radio. Other scenarios are that reconfigurable architectures provide redundancy and fault correction for flight and space missions [21].

An implementation in a reconfigurable FPGA provides the opportunity of power savings due to the fact that the accelerator can be more power efficient than a generic implementation as it is customized for the currently running task. However, energy must be considered as the power reduction may easily be nullified by the power consumed during reconfiguration [22]. Recent publications have also shown power and energy gains for FIR filters by Becker et al. [4] who have also presented the GroundHog benchmark [23] for power consumption evaluation for reconfigurable architectures. Power dissipation reduction in embedded controlling applications for the automotive industry have also been demonstrated by [24].

Although many applications have been proposed, we find it an open question to decide what and when to consider a reconfigurable implementation for static applications without the flexibility requirements that are present for SDR applications. We define

static applications as applications where the operations and flow of the algorithms are known at compile-time. In order to be able to determine under which conditions reconfigurable implementations prove more efficient than static HW or SW architectures, we find it necessary to evaluate models of implementations in reconfigurable hardware in order to qualitatively determine the feasibility of reconfigurable architectures. We define *feasibility* based on a cost function. If the costs are lower (or equal) for a reconfigurable than for a static implementation, we define it as feasible. This is further discussion in [A] and Section 2.1.

#### **Architectures and Technologies**

Many challenges lie in the reconfigurable architecture, which was also identified as a main challenge in the survey by Todman et al. [13]. The authors emphasized structure of the reconfigurable hardware as well as the interfaces between the elements of the architecture: hardware part, processor, and memory.

Similar conclusions have been made by Hartenstein [25], who identifies one of the main challenges as finding the right trade-off between fine- and coarse-grained architectures, also investigated by [26].

We have already outlined some successful applications of reconfigurable hardware. However, the efficiency of these applications proved to be very dependent on the reconfiguration time of the reconfigurable hardware. In reconfigurable hardware, e.g. FPGAs, the behavior of the reconfigurable hardware is described by a configuration file or bitstream. The bitstream is loaded through a configuration interface, thus the reconfiguration time is dependent on the throughput of the configuration interface. Furthermore, the size of the bitstream is proportional to the configured area [12].

The reduction of reconfiguration time is a challenge that has been covered in many research papers, with some approaches outlined here. These works use the strategy of adding extra hardware resources to provide faster reconfiguration.

Configuration caching has been investigated by Li et al. [27] and consists of adding a cache inside the chip in order to reduce the amount of data to transfer across the chip boundary. Similarly, a multi-context FPGA approach consisting of several layers (contexts) of configuration data in the overlaying configuration memory has been suggested in [28]. The switch between configurations is then performed by a multiplexer. This reduces the configuration time between pre-loaded configurations, but the configuration interface will still be a bottleneck if the number of configurations exceed the number of contexts. This approach (developed by Xilinx), is not integrated in the Virtex family of FPGAs [12], but recently the company, Tabula Inc., has marketed a time-multiplexed FPGA along with necessary development tools [29].

Another technique for reducing the communication across the chip boundary is the compression of configuration data, suggested by the same research group [30], [31]. This has been further investigated by Dandalis and Prasanna [32] proposing an improvement of the area and speed efficiency of the compression technique.

While the mentioned approaches require extra hardware area for the configuration controller and caching memory, another approach is *prefetch* [33], that hides configuration delay by performing reconfiguration and execution in parallel. This has been further developed by Qu et al. [34] where multiple configuration interfaces have been utilized for a single device. The motivation was that when reconfiguration delay is longer than one

execution, more reconfigurations must be performed in parallel, thus a single configuration interface may become a bottleneck.

#### **Design Methods for Reconfigurable Architectures**

The lack of design methods for heterogeneous reconfigurable architectures has been emphasized by among other Hartenstein [25] with the lack of Electronic Design Automation (EDA) for increasing and maintaining designer productivity. Furthermore, Todman et al. [13] consider Computer Aided Design (CAD) and compilation tools as significant research challenges.

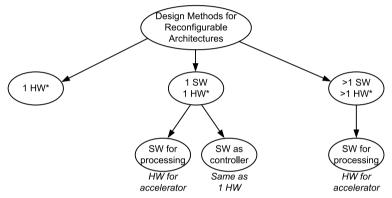

Design challenges and methods for coping with these have many facets and directions. We see the design problem as a tree, illustrated in Figure 1.5 and outlined in Section 1.3.

Figure 1.5: Suggested overview of the design cases in reconfigurable computing. HW\* denotes that HW may be utilized for either either full reconfiguration or partial reconfiguration. 1 HW is the case when the architecture consists of only one single reconfigurable unit. 1 SW/1 HW is the case of an architecture with a single software and a single reconfigurable hardware unit. This case is again split; if the SW is used for processing, the HW is considered a reconfigurable accelerator for the SW. However, if SW is used only for control of the reconfigurable HW, the case is similar to the 1 HW scenario. If there is more than one of either SW processor or reconfigurable HW unit, the architecture is a heterogeneous reconfigurable architecture. All cases are discussed in Section 1.3.

In the next section, we provide a state-of-the art of the existing work in design methods for reconfigurable computing in general, followed by heterogeneous reconfigurable architectures.

# 1.3 Mapping of Applications onto Heterogeneous Reconfigurable Architectures

In the following, we describe the state-of-the-art, related and grouped to the overview in Figure 1.5.

**Single Reconfigurable Unit** As we have described, FPGA execution can be performed in parallel, but the reconfiguration of regions must be scheduled sequentially. A scheduling algorithm for handling this problem for a single FPGA based on single-processor scheduling is proposed by Dittman and Götz [35]. The algorithm assumes equally sized reconfigurable slots on the FPGA. The task model is based on aperiodic tasks, starting at arbitrary times, independent of each other.

Bobda [36] has investigated methods for scheduling data flow graphs onto a reconfigurable device. The work includes both full reconfiguration and partial reconfiguration. For full reconfiguration, the tasks need to be partitioned into clusters of tasks. Each cluster corresponds to a configuration, and the activity of dividing a set of tasks into sequentially executable clusters of tasks is called *temporal partitioning*. Bobda investigates a list-scheduling algorithm for temporal partitioning, followed by an optimization step to reduce the communication across clusters or configurations.

Other approaches to temporal partitioning are the purely list-based approaches by Purna and Bhatia [37]. Purna and Bhatia suggest two temporal partitioning algorithms (level- and clustering-based), each for one of two optimization goals, execution time or communication interface, respectively.

For partially reconfigurable architectures, Bobda [36] has suggested an approach for *temporal placement* which is the task of dealing with both temporal and spatial partitioning of the application. The approach consists of: firstly a decision as to how to cluster components to be placed on the same device, and secondly a placement of the components on the reconfigurable device. For the clustering approach, Bobda used a list-based clustering algorithm followed by spectral-based optimization with higher computational complexity. The partitioning task set is input to a temporal placement algorithm based on a list-based schedule.

Another scheme suggested for utilization of reconfigurable architectures is based on configuration prefetch, and it thus hides the reconfiguration delay if the application allows the parallelization of reconfiguration and execution. Kim et al. [38] have proposed a temporal partitioning algorithm based on an extension of the work by Ganesan and Vemuri [39]. The work by Ganesan and Vemuri was based on a simple division of the hardware area into two equally sized parts, and then a partitioning of the tasks into equally sized blocks. Kim et al. suggest a method that divides a Control Data Flow Graph (CDFG) into sub-CDFGs that fit inside the area-constraints. The algorithm seeks to perform partitioning to maximize speedup of each loop iteration. Another approach for real-time scheduling has been performed by Clemente et al. [40, 41], where a task scheduler was implemented for multiple reconfigurable units.

While the mentioned approaches are developed for architectures with a single reconfigurable HW unit, they cannot handle HW/SW architectures and the required partitioning of the task-set into HW and SW.

**Single SW, Single Reconfigurable Unit** For HW/SW systems, one design challenge is partitioning of the task graph into HW and SW tasks. Chatha and Vemuri have investigated an iterative algorithm for architectures consisting of one SW unit and one reconfigurable HW unit using full reconfiguration [42]. The approach uses a list-scheduler to obtain the makespan of a partitioning, and uses an iterative partitioner to evaluate the design space until no further minimization of the makespan is achieved.

Similarly to Chatha and Vemuri, Galanis et al. [43] perform early HW/SW partitioning based on execution time, followed by temporal partitioning of the HW tasks. Further on, HW tasks are partitioned into coarse- and fine-grained HW. However, [43] does not describe the combined scheduling of HW and SW tasks, as well as the handling of heterogeneous architecture with more than one SW and one HW unit.

Banerjee et al. have investigated HW/SW partitioning for similar architectures consisting of one SW and one HW unit [44]. The HW is partially reconfigurable and the partitioning scheme takes into account the exclusiveness of the reconfiguration interface as well as a requirement for physically placing tasks in adjacent columns on the FPGA. The approach starts by a dependency graph describing tasks. The optimization problem is formulated as an Integer Linear Programming (ILP) problem, solved by a Kernighan-Lin/Fiduccia-Matheyes heuristic. The results showed that it is necessary to consider partitioning and scheduling simultaneously.

Inspired by Banerjee et al., Redaelli et al. have utilized the same ILP approach to schedule tasks and their reconfiguration on a partially reconfigurable FPGA [45]. Redaelli et al. obtain better results (in terms of lower makespan) than Banerjee, due to the consideration of configuration prefetch, module reuse, and anti-fragmentation strategies. However, they consider only HW execution and not SW. Furthermore, the exploration time for finding a solution was found to be prohibitively long [45]. As an extension to this work, the same research group has developed a methodology for performing partitioning of a task graph into cores with the aim to reuse the same cores for several nodes in the task graph [46].

Miramond and Delosme [47] have investigated HW/SW partitioning, temporal partitioning, and SW scheduling for a HW/SW system with fully flexible partial reconfiguration. The solution space was explored based on a simulated annealing algorithm initiated by a random partition.

Stitt et al. [48] have introduced guidelines for mapping the time-critical parts to HW. Criticality is based on the execution time of that part in relation to the total execution time. One decision parameter was speed-up based on Amdahl's law, but no formalized method was considered. Noguera and Badia [49] considered movement of SW to HW to minimize the overall execution time. Prefetch of configurations was considered to hide reconfiguration overhead by overlaying HW reconfiguration with SW execution.

Commonly, all the mentioned approaches cover the mapping and/or implementation process for architectures consisting of one SW unit and one HW unit. However, they do not handle the scheduling and communication overhead for heterogeneous reconfigurable architectures consisting of several SW and several reconfigurable HW units.

**Several SW and Several Reconfigurable HW Units** As an extension to Banerjee et al., Dittmann et al. [50] have proposed a method for mapping and design of heterogeneous reconfigurable systems consisting of several HW units. The outset is again a dependency

graph describing the tasks to implement. An architecture graph describes the architecture model that consists of several FPGAs and their interconnection. The FPGAs have predetermined (similarly sized) area slots that can be reconfigured, a fixed communication bus, and is constrained by a single configuration interface. The solutions are explored by a genetic algorithm and the outcome is a binding and schedule that can be implemented on the architecture. The quality of the solutions is dependent on a cost library containing the cost of implementation of each task.

Solid work in the field of mapping methods for reconfigurable architectures is available. However, the investigated approaches are either not adapted for heterogeneous, reconfigurable architectures with several SW and HW units, or they have a high computational complexity like those based on genetic algorithms. Therefore, we propose to investigate less complex methodologies for mapping applications onto heterogeneous, reconfigurable architectures. Our proposal consists of an extension and modification of existing low-complexity approaches such that they cover heterogeneous, reconfigurable architectures with several SW and HW units. The goal is to obtain a methodology that does not necessarily give the optimum solution - but provides a possible solution without the risk of the prohibitively long exploration times given by high computational complexity.

#### 1.4 Thesis Formulation

The thesis is formulated based on the questions formulated in Section 1.2. These can be summarized into two questions:

- What are the characteristics to be fulfilled in order for a reconfigurable implementation to be more feasible in terms of execution time and resource consumption than static implementation?

- Is it possible to extend and combine existing mapping methodologies to support heterogeneous architectures composed of several SW and HW units.

Based on these questions, we formulate the following theses and sub-clauses:

- It is possible to investigate the feasibility of implementations in reconfigurable architectures based on a model describing reconfiguration and execution in coarse terms.

- 2. Multiprocessor scheduling algorithms for SW architectures can be extended and combined with temporal partitioning algorithms for reconfigurable architectures.

- a) Temporal partitioning can generate clusters of HW task

- b) The HW clusters and their reconfiguration can be scheduled by a multiprocessing scheduler for SW architectures, taking into account the structure and delay of communication.

We believe that in case both theses can be supported, this work is a useful tool for the designer in the design space exploration process and can shorten development time by providing the designer with feasible bindings and schedules for implementation.

#### 1.5 Outline of the Dissertation

The remainder of this dissertation is organized as follows: First, the considerations behind the used methodology is described in Chapter 2. In Chapter 3 the summary of our contributions is given. This is followed by the conclusion and outlook in Chapter 4. Papers A-D (overview given in Chapter 5) are the contributions to the dissertation, and we refer to these papers by giving the letter in brackets, e.g. [A]. References to other resources are numbers in brackets, e.g. [1], referring to the list on page page 33.

## 2 Methodology

This chapter describes the considerations made during the development of the methodology used by the mapping framework. The chapter starts with the modeling of reconfigurable architectures, followed by the considerations of the mapping framework. Results are summarized in Chapter 3 and papers [A]-[D].

#### 2.1 Modeling

The modeling performed in the work is split in two parts. The approach of the modeling is formulated such that application and architecture are orthogonalized, as suggested for several methodologies [51, 52]. This allows the independent modeling of the application and of the architecture, thereby enabling the use of the same application model for several architectures, and vice versa. The application and architecture model are related via a cost-estimate library, describing each alternative of implementation of a task or operation. The cost-estimate library is described in Section 2.2.

#### **Application Modeling**

The applications of concern are signal processing and communication processing applications. We have decided to consider static applications, where the operations and flow of the algorithms are known at compile-time. This limits the number of applications, however, it suits many algorithms inside the concerned domain of applications.

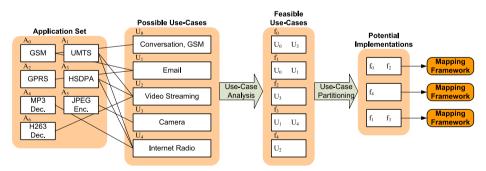

In order to handle adaptive applications (e.g. changing of modes in multi-mode and multi-standard radios), a consideration of the multiple use-cases analysis by Kumar et al. [53] could be considered. Use-cases are all uses of the application or product. These are analyzed to generate sets of functionalities resulting in a set of application graphs that should be implemented. Each application graph represents an implementation of one or more use-cases, and the switch between implementations may be performed by full reconfiguration of the system.

Our application model, as outlined in [D], models tasks as nodes and their dependencies as edges in a Directed Acyclic Graph (DAG), describing the precedence-relations between the tasks. Furthermore, we have added properties to the model to describe the amount of data transferred between nodes, so that communication delay can be modeled. Our application model allows the description of parallelism and dependencies, and can thereby describe a variety of signal processing applications. The nodes may have varying

granularity, which allows them to capture both fine-grain (down to bit-level) and coarse-grain (up to large chunks of functionality like FFT etc) tasks.

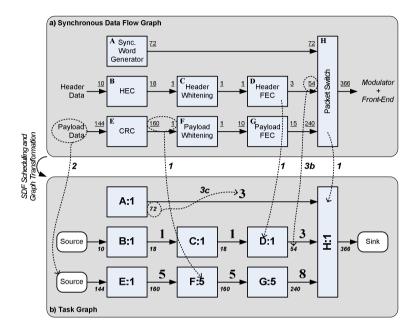

The precedence graphs are a subset of Synchronous Data Flow (SDF) graphs, describing precedence-relations and rate-specifications. The data-flow description is considered to be a natural selection as signal processing applications mostly consist of data-flow oriented algorithms. SDF allows the modeling of pipelined streaming and cyclic dependencies [54]. The cyclic dependencies allow modeling of digital Infinite Impulse Response (IIR) filters, but we assume that the full filter can be modeled as one node in the DAG. In [C] we have introduced a methodology to convert an application described as SDF into a directed acyclic precedence graph corresponding to our application model.

Some mapping approaches [55] have specified systems by Control Data Flow Graphs (CDFG) that allow the modeling of control path structures of the applications. However, we find that the DAG limitation is acceptable since the flexible granularity allows us to hide the control structure inside the node.

#### **Architecture Modeling**

Section 1.1 described how a heterogeneous, reconfigurable architecture is composed of one or more reconfigurable hardware units in connection with one or more SW processors. Therefore, the requirements to the architecture model is that it must be able to capture heterogeneity, granularity, and reconfiguration capabilities.

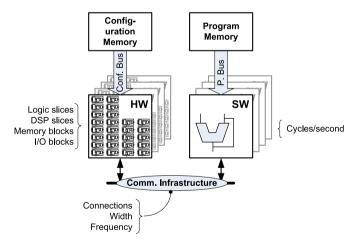

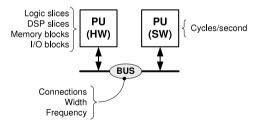

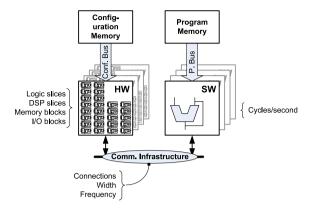

This resulted in the general architecture model which is shown in Figure 2.1. The architecture consists of a number of hardware and software units, connected via dedicated or shared buses.

Figure 2.1: General architecture model for a heterogeneous reconfigurable architecture. The properties that are included in the model for each unit type are marked by {-brackets.

The model is based on the assumption that each hardware and software unit can execute in parallel. Inherent parallelism as such inside the SW units is not reflected in the general model. Communication between units is performed before the initiation and after the start of executions.

Execution in SW is assumed to be performed sequentially, requiring a certain execution time to perform the task. The execution of a task may not be interrupted by other tasks. The SW units may have external memory, which is not included in our abstract model. This means that estimated execution times may vary due to the fact that the data may be saved either in internal registers, cache, or external memory. However, this limitation is chosen since it reduces the complexity of the model. The simple architecture model allows the modeling of multiple SW processors as well as multiple cores. However, the abstraction level does not cover multiple datapaths inside a single core (like e.g. the Texas Instruments C6000 series DSP [56]). The use of the multiple datapaths is assumed to be reflected in the cost estimates as described in [D].

Execution in HW is assumed to be performed both in parallel and possibly sequentially in time, i.e. the reconfigurable HW can have parallel processing cores implemented, but reconfiguration does also allow those to be reconfigured during run-time. However, the input and output data of an executed context must be transported before and after execution as described in Figure 1.2a. The reconfiguration of the reconfigurable hardware is performed and controlled from an external reconfiguration controller with external memory. This controller is assumed to be inherent of the architecture and is abstracted away to be represented only by the reconfiguration delay. The effect of this abstract model is that the reconfiguration delay is independent of the availability of the configuration interface. However, this is not an issue for full reconfiguration or partial reconfiguration with only one reconfigurable region.

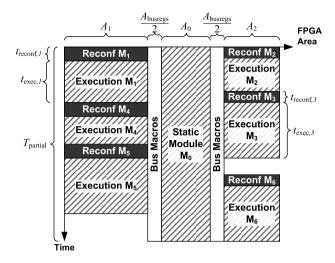

Our architecture model in Figure 2.1 does not include partial reconfiguration as such. Therefore, it can be argued that our model does not capture partial reconfigurability. However, the synthesis flow for generation of bitstreams for partial reconfiguration of Xilinx FPGAs does require an early decision on the placement and size of the reconfigurable region [57, 58], which is also illustrated in Figure 2.2. The modules that are reconfigured into these regions may have more parallel functionalities, and can be considered as fully reconfigurable partitions of the partially reconfigurable hardware. Thus our architecture model for heterogeneous, reconfigurable architectures does cover a design in partially reconfigurable FPGAs like the Xilinx Virtex series.

#### **Feasibility Modeling**

The feasibility of a reconfigurable implementation was defined based on a cost function. If the cost of a reconfigurable implementation is equal to or lower than a static implementation - the reconfigurable implementation is said to be *feasible*. The feasibility study is explained in [A].

In order to evaluate the feasibility, a cost function has been defined based on the product of area and time,  $C = A \times T$ . The area-time product has been selected as we consider these the main resources that are consumed during an implementation. The area, A is a measure of the resources in an architecture (for static and full dynamic reconfiguration), whereas, for partial dynamic reconfiguration, A is a measure of the resources consumed by a task. Time, T, is the execution time of the full application for a static implementation; execution and reconfiguration times for the dynamic reconfigurations.

Our model compared the full execution time, so that the same deadline was maintained for both a static and a (fully and partially) reconfigurable implementation. The approach was not similar to [59] which considers the maintaining of throughput and does

Figure 2.2: Illustration of the design flow of partial reconfiguration for Xilinx FPGAs based on [57], [58]. The design starts with a partitioning of the application into static and reconfigurable parts. The top-level contains the clock signals as well as relation (in terms of signals) between static and reconfigurable parts. Then each part is synthesized to obtain netlists for each module, using the Xilinx Integrated System Environment (ISE) synthesis tool and possibly the Embedded Developer's Kit (EDK). Then the size and placement of static and reconfigurable parts are decided (by the designer), and the top and static modules are implemented, followed by the implementation of each reconfigurable module. Finally, the full bitstream of the static module is generated, followed by the partial bitstreams.

not consider dynamic partial reconfiguration. Our cost function does not contain power consumption. However, a recent study by Becker et at. [4] concluded that feasibility in terms of energy consumption is related (not linearly) to the area consumption.

### 2.2 Mapping Framework

The framework was developed and is described in detail in [B] and [D]. The framework was developed for mapping static applications onto heterogeneous, reconfigurable architectures as described in Section 2.1. The outcome of the framework is the generation of a schedule that can then be implemented in the architecture. The schedule describes which tasks to perform in which unit - and when to execute them.

Mapping and scheduling for HW/SW architectures is a constrained optimization problem [3]. The constraints and costs are typically described by a cost function (as in (1.1)), which can be dependent on parameters such as execution time, area or resources (Configurable Logic Block (CLB), DSP blocks etc), power consumption, numerical accuracy etc. We formulate our constraints as minimization of overall execution time (makespan) while satisfying the resource-constraints of the reconfigurable hardware.

Another approach to the optimization problem could be to have a constraint on the execution time, and thus minimize the resource usage. However, we find that the first approach is the most useful since it suits the Xilinx development flow in Figure 2.2.

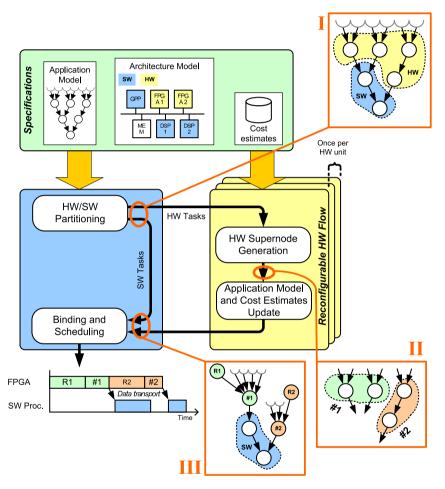

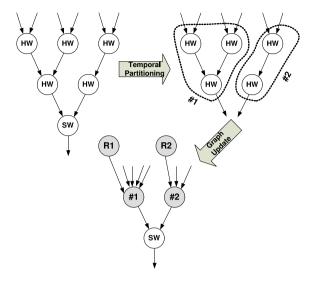

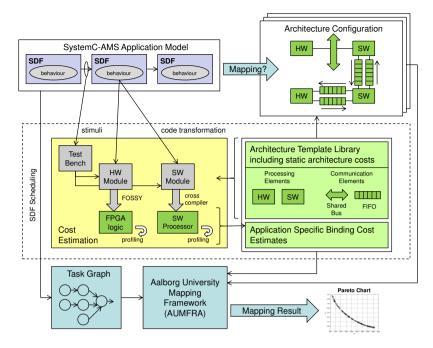

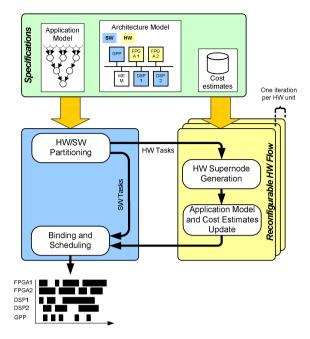

The outline of the mapping framework is given in Figure 2.3. For details and formalization, please consult [D]. The mapping framework takes as input the specification of the application, architecture, and their interrelation via a library of cost estimates as

Figure 2.3: Outline of our developed mapping framework. The orange marked circles and boxes (I-III) are an example of task-graph transformations, utilizing only one SW and one HW processing unit.

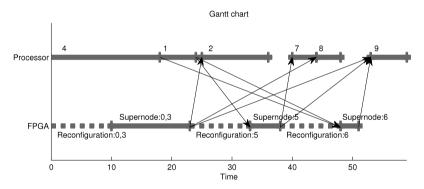

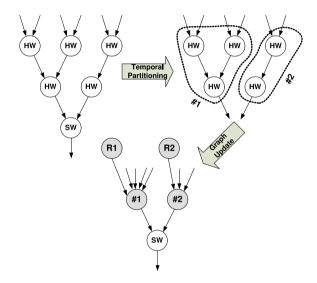

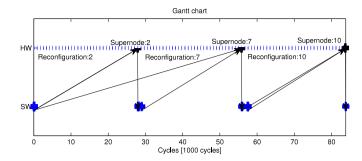

briefly outlined in Section 2.1 and more detailed in [D]. First, the tasks are split into HW and SW tasks in the HW/SW Partitioning step, resulting in a partitioning as indicated in box I. The HW tasks for each HW-unit are treated in the Reconfigurable HW Flow where super-nodes of HW tasks are created in HW Supernode Generation by temporal partitioning. Each super-node corresponds to a full configuration of the reconfigurable area (as illustrated in box II), and these are updated in the application graph and cost-table. The Reconfigurable HW Flow is performed once for each reconfigurable HW unit. The HW Supernode Generation can be performed in parallel, but the Application Model and Cost Estimates Update have to be performed sequentially in order to maintain a graph with updated edges. The resulting updated application graph is illustrated in box III. The binding and scheduling is performed by a multiprocessor scheduling algorithm for heterogeneous architectures. The scheduling algorithm treats the HW super-nodes similar to SW tasks, but only for the reconfigurable unit. Furthermore, the algorithm must ensure that reconfiguration for one task is followed by that task, and not another task or reconfiguration. The final output of the framework is a schedule that describes which tasks should be packed into one configuration, and which unit should perform which tasks (and at which time).

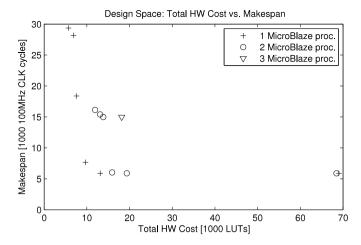

The orthogonalization of application and architecture allows the evaluation of several architecture models for the same application, and thus we can explore several points in the design space. This was also performed in papers [C] and [D].

The cost-estimate library contains costs of binding alternatives for each task, which can also be noted "design point". Each task may have more design points, e.g. on different processing units. A design point for a HW implementation is a tuple of costs, including execution time, logic resource consumption, plus possibly embedded DSP and embedded memory consumption. Our modeling allows the HW implementation to have several design points for a single HW unit. This reflects the area-time trade-off that FPGA designers can make when performing their implementation.

The modeling and our mapping methodology are highly dependent on the ability of the designer to provide realistic cost-estimates for the tasks. This requires the designer to have some knowledge about the implementation before starting the actual implementation. It can be argued that exactly this requires the designer to have performed the implementation before starting the exploration using the proposed framework. However, we argue that most designs are based on previous designs or IP blocks - mainly utilizing the same architecture. This is also supported by the Embedded Market Study [11] which show that 57% of all projects are an update or improvement of earlier projects, with 86% code reuse. Furthermore, 48% of the projects reuse the same SW processor. Very often the designer does not need to synthesize everything, but only the building blocks that are not available from previous designs/IPs. Therefore, we believe that the requirement for cost-estimates is an acceptable workload for the designer.

In the following, we point to specific points in the mapping framework, related to Figure 2.3.

#### **HW/SW Partitioning**

The HW/SW partitioning decides (based on the implementation alternatives), whether tasks should be executed in SW or HW. The decision can be made from one of several schemes. 1) The simplest is the comparison of execution speed in HW and SW; if HW is fastest, the task is executed in HW. 2) Other factors could be resource consumption. If a task would take up a large portion of the resources in HW, it may be beneficial to place it in SW. 3) HW/SW communication is also known to take time, so it may be beneficial to execute predecessors and successors of a task in the same unit or processor. 4) Analyzing the inherent parallelism of the applications is also an option, as SW is typically considered sequential whereas HW is considered parallel.

However, even though the sole consideration based on execution time may lead to lower performance, it has been selected since it has been shown that considering execution time in the partitioning and even only implement a few of the tasks in HW lead to a significant speedup [48].

Banerjee et al. [44] showed that the best performance of the scheduling algorithm was obtained by considering partitioning and scheduling simultaneously. However, one of the goals of the methodology was to reduce the overall complexity, which is achieved by separation of partitioning and scheduling.

#### **Reconfigurable HW Flow**

The reconfigurable HW flow creates super-nodes of tasks based on temporal partitioning algorithms. These algorithms partition the tasks into clusters that each correspond to a full reconfiguration of the device. The temporal partitioning algorithms are generally list-based or the more computationally complex refinement based (like the ones described by Bobda [36]). We selected to extend the list-based algorithms by Purna and Bhatia [37] which had a low computational complexity. The algorithms were based on either level-or clustering-based temporal partitioning, which had different performance in terms of overall execution time and communication delay.

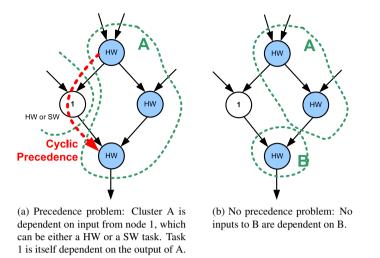

Our extension to the work is rooted in the fact that we have split HW and SW. Thus the temporal partitioning algorithm does not handle all tasks, which gives the risk of cyclic dependencies. We added a path search to the algorithms that ensured no precedence problems. For further details, see [D].

#### **Binding and Scheduling**

The binding and scheduling algorithm was subject to the requirement of being able to handle the following:

- 1. Heterogeneous architecture, consisting of

- a) Several SW processors

- b) Several reconfigurable HW units

- 2. Schedule reconfiguration for HW units correctly

- 3. Communication delay and the occupation of the communication resources

Our work is based on the Extended Dynamic Level Scheduling (EDLS) algorithm [60] that has a relatively low computational complexity while still taking into account the cost (in terms of time) of inter-processor communication. EDLS is an extension for heterogeneous architectures of the Dynamic Level Scheduling (DLS) algorithm.

The algorithm is further detailed in [60] and [D]. The algorithm computes a Dynamic Level (DL) value for each node-processor combination, and schedules the combination with the highest DL value. The algorithm has been modified such that in case a HW processor is configured for a specific task, the DL level is adjusted to a value such that only the combination with the corresponding execution will be chosen.

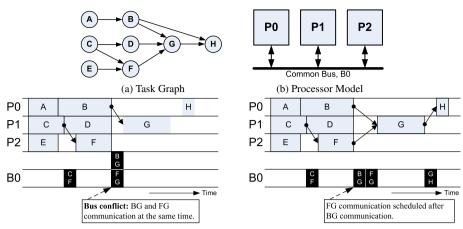

Since the modified EDLS algorithm maintains reconfiguration-execution relations, it is suitable for models where the usage of the configuration memory and interface is transparent. However, if more reconfigurable areas reside inside an FPGA, they share the same configuration port as illustrated in Figure 1.3. However, this can be modeled in our system by inserting the ICAP interface as a processing element, with corresponding reconfiguration nodes for this element.

The used methods in the developed framework allow us to handle static applications and map them onto heterogeneous reconfigurable architectures. Our approach has been to seek a computationally simple solution, and thereby keep the exploration time low. Thereby, we have implicitly accepted that our resulting schedule may not be the most optimal in terms of execution time and resource usage. However, we believe that the obtained schedule and the combination with several architecture models form a sufficient outset for the design space exploration of a heterogeneous reconfigurable implementation and thus allows rapid design space pruning. Furthermore, we assume that the solutions found by the mapping framework can actually be implemented in a heterogeneous reconfigurable architecture.

The used models for application and architecture modeling are general and allows flexible modeling that we believe is technology independent. The level of detail in the models is relatively low, which on the other hand eases the fitting of the model to the application and architecture by the designer.

### 3 Summary of Contributions

This chapter provides a summary of the contributions of this work. The summary is related to the papers A-D.

The body of this dissertation is formed by the papers A-D. First, an overview of the papers is given:

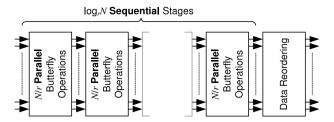

- **Paper A:** In this paper we investigate the feasibility of reconfigurable architectures in order to evaluate whether reconfigurable architectures are more feasible than static architectures for signal processing applications. Case studies were performed for a Fast Fourier Transform (FFT) and a Digital Audio Broadcasting (DAB) receiver.

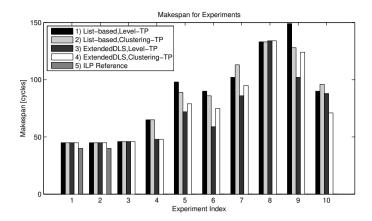

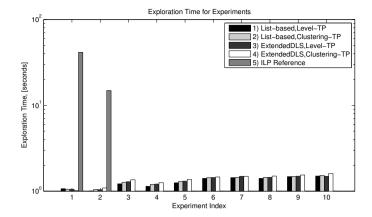

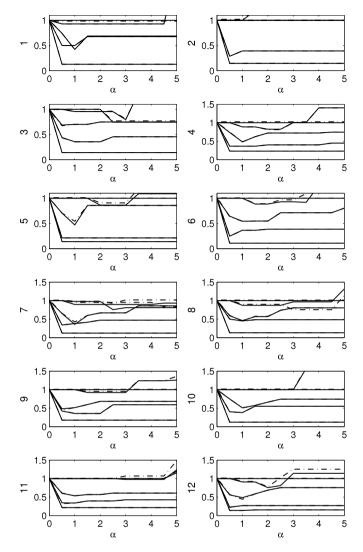

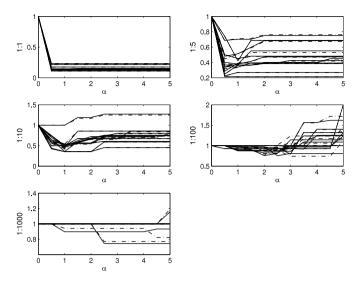

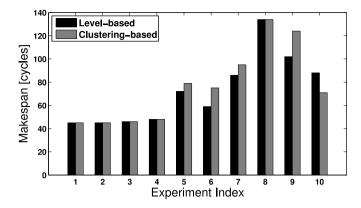

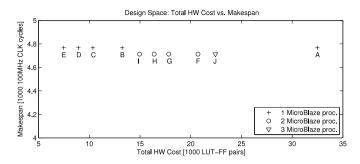

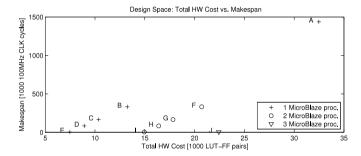

- **Paper B:** Here, we have presented the idea of our mapping methodology alongside with evaluations of two partitioning algorithms and two multiprocessor scheduling algorithms by simulations on abstract application models and cost-entries.

- **Paper C:** In this paper we have presented a method to obtain application graphs and cost-estimates for the mapping framework, based on a SystemC-AMS model of the application. The methodology is illustrated by a case study of a static implementation of a Bluetooth baseband unit in a Xilinx Virtex-5 FPGA.

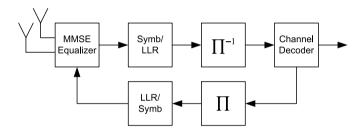

- **Paper D:** This paper contains a formalized description of the algorithms used by the mapping framework. We outline the simulations of using the mapping framework and perform a case-study based on the implementation of a Minimum Mean Square Error (MMSE) equalizer for a MIMO-system.

The papers treat the two topics from our thesis in Section 1.4, which are further described in the following sections:

### 3.1 Feasibility of Reconfigurable Implementations

In order to evaluate whether a static application could benefit from a reconfigurable implementation as opposed to a fully static FPGA implementation, we propose a model and cost function of the execution of applications in both static and reconfigurable FPGA implementations. Our work in this field is described in paper A.

The model is based on a split of execution into reconfiguration and execution, possibly with data-communication as described in Section 2.1 of the dissertation. Our contribution

is the proposed model based on execution time instead of throughput as performed by Wirthlin and Hutchings [59]. Thereby, our model allows the evaluation of time-sharing of the same area resources, as well as partial reconfiguration. Our cost function is based on an area-time product.

Our results (based on a case-study of an FFT core and a DAB receiver) show that the reconfiguration time for reconfiguring the full area is too high to make a reconfigurable implementation feasible. However, for applications where timing constraints are less stringent, a reconfigurable implementation may be beneficial. In the case of partial reconfiguration, the reconfiguration time is low enough to make the partially reconfigurable implementation feasible as compared to a static implementation.

In the paper we propose a similar feasibility study of the energy consumption aspects of full and partial reconfiguration. Since publication of our work, new contributions have been made by Becker et al. [4]. Although their study is related to energy aspects of reconfiguration, their model is also based on a split between execution and reconfiguration, and the conclusion about feasibility is similar to ours, i.e. it can be concluded that reconfiguration time is the limiting factor of the feasibility of reconfigurable implementation. They also conclude that in order to reduce the reconfiguration time as much as possible, the area should obviously be as small as possible.

#### 3.2 Mapping Framework

The mapping framework is described in paper B and D. Paper B are the preliminary results of the mapping framework, indicating which temporal partitioning algorithm yields the lowest makespan. We also formulate a light version of the Integer-Linear-Programming (ILP) formulation of placement-aware scheduling in partially reconfigurable FPGAs [44] for comparison purpose. Our contribution in this connection is a placement-unaware model, as we only consider area and not placement for contemporary FPGA design. The results are based on an abstract application and cost model, and was evaluated for uniprocessor solutions.

Paper D contains the formal description of our developed framework. Furthermore, a case-study of an MMSE equalizer for a MIMO system [61, 62] is included to compare the resulting schedule of the framework with an actual implementation in a Xilinx Virtex-5 FPGA [63]. Our contribution is the formal description of the algorithms in the framework, especially the additions to the temporal partitioning algorithms [37] and their interplay with the Extended Dynamic Level Scheduling (EDLS) algorithm by Sih and Lee [60]. Our overall algorithm has a complexity of  $O(P\ M\ N^3)$  for high M and N. This is lower than the iterative algorithm by Chatha and Vemuri [42] which has a relatively high complexity  $O(N^4\ B+N^3\ B^2+N^3\ B\ M)$  where N is the number of nodes in the task graph, M is the number of edges, and B is the maximum number of design points for each task.

Both the works in [B] and [D] are dependent on input from the designer in terms of application and architecture models, as well as a cost estimates library describing the cost of implementing each task. Paper C contains the description of a methodology to obtain the cost-estimates by the use of a VHDL synthesis tool. Furthermore, the resulting schedules of the framework are used in design-space exploration in order to select the most suitable architecture.

In paper C, we investigate a methodology to derive a directed acyclic application graph and corresponding cost-estimates from an executable description of an application. The executable description is a SystemC-AMS model describing the application by a synchronous data flow graph. The methodology is evaluated on a case-study of a Bluetooth baseband transmitter. The resulting graph and cost-estimates are fed to the mapping framework for a static architecture. Results show that by using the methodology in combination with the mapping framework, we are able to perform design space exploration and evaluate various architecture designs.

All contributions are targeted for use as parts of a tool for designers of an application implemented on a heterogeneous reconfigurable architecture, for which we assume the design trajectory in Figure 1.1. Both the feasibility estimation methodology and the mapping framework are tools for use in the *Design Space Exploration & Mapping* phase of the design, before the designer performs the actual implementation and test.

# 4 Conclusion

This chapter gives the conclusion of the work, supporting the theses. Furthermore, suggestions for future work are provided.

In this dissertation we investigate feasibility, modeling, and mapping methodologies for heterogeneous reconfigurable architectures. Our model of reconfigurable architectures allows us to describe the capabilities of a reconfigurable architecture, and is composed of 1) a pure model of the reconfigurable hardware for feasibility investigation, and 2) a model of a heterogeneous, reconfigurable architecture consisting of several reconfigurable hardware (in the form of FPGA) and software processing units. The model is input to a mapping framework for such architectures, together with an application model and a cost-library integrating the two. The mapping framework generates schedules for implementation of algorithms onto heterogeneous, reconfigurable architectures. The framework is a tool that may aid the designers in the *Design Space Exploration & Mapping* phase in the design trajectory illustrated in Figure 1.1.

In the following, we provide answers to the questions that lead to the formulated theses in Section 1.4.

It is possible to investigate the feasibility of implementations in reconfigurable architectures based on a model describing reconfiguration and execution in coarse terms.