Aalborg Universitet

## **Advanced Converter-level Condition Monitoring for Power Electronics Components**

peng, yingzhou

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): peng, Y. (2020). Advanced Converter-level Condition Monitoring for Power Electronics Components. Aalborg Universitetsforlag.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## ADVANCED CONVERTER-LEVEL CONDITION MONITORING FOR POWER ELECTRONICS COMPONENTS

BY YINGZHOU PENG

DISSERTATION SUBMITTED 2020

AALBORG UNIVERSITY DENMARK

# Advanced Converter-level Condition Monitoring for Power Electronics Components

Ph.D. Dissertation Yingzhou Peng

Dissertation submitted Oct., 2020

| Dissertation submitted:  | October 2020                                                               |

|--------------------------|----------------------------------------------------------------------------|

| PhD supervisor:          | Professor Huai Wang<br>Aalborg University                                  |

| PhD committee:           | Associate Professor Amjad Anvari-Moghaddam (chair.)<br>Aalborg University  |

|                          | Associate Professor Sanjib Kumar Panda<br>National University of Singapore |

|                          | Senior Lecturer Suresh Perinpanayagam<br>Cranfield University              |

| PhD Series:              | Faculty of Engineering and Science, Aalborg University                     |

| Department:              | Department of Energy Technology                                            |

| ISSN (online): 2446-1636 |                                                                            |

ISSN (online): 2446-1636 ISBN (online): 978-87-7210-820-9

Published by: Aalborg University Press Kroghstræde 3 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Yingzhou Peng

Printed in Denmark by Rosendahls, 2020

## Abstract

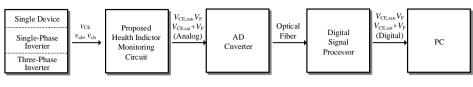

Applications, such as traction and offshore wind, demand cost-effective and robust condition monitoring solutions for operation optimization and predictive maintenance. There is still a gap between academic research and industrial applications in condition and health monitoring in power electronic converters from the signal extraction, calibration, and data processing perspectives. This Ph.D. study proposes two converter-level condition monitoring methods that have promising features to bridge the gap.

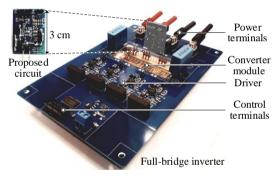

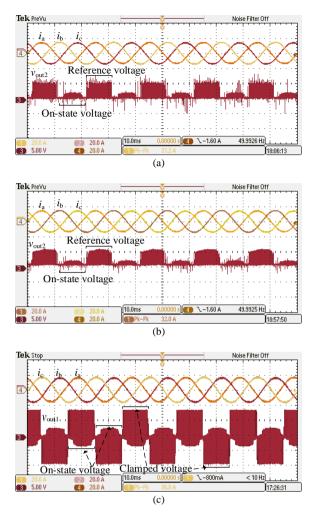

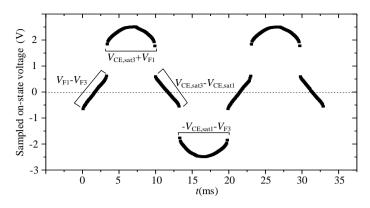

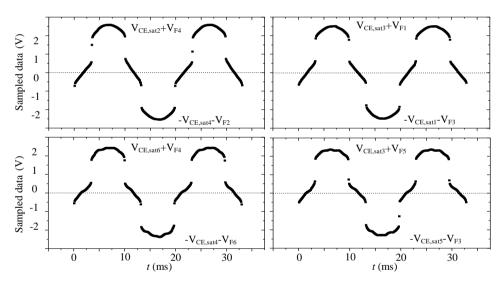

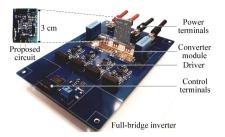

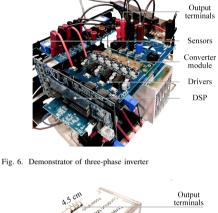

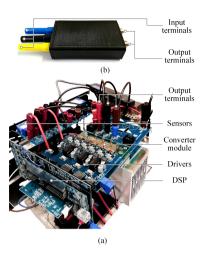

The first method is based on a converter-level on-state voltage measurement approach. The on-state voltage, such as saturation voltage of IGBTs and forward voltage of diodes, is a widely used electrical parameter for junction and health condition estimation of power semiconductor switches. Conventional methods are mainly at the component-level by adding a measurement circuit for each switch in its gate driver circuit. It suffers from two challenges: 1) gate driver is not always accessible, especially for power converters with design freeze, and 2) it has a relatively high cost and complexity. This study proposes a single measurement circuit connected in the middlepoints of the phase legs of a single-phase inverter or three-phase inverter. It can measure on-state voltages of all the power switches, including diodes. Three variants of the circuits have been proposed as well: 1) with external power supply as existing component-level methods do; 2) with a self-power scheme to exclude the power supply which is the most expensive component in the measurement circuit, and 3) simple passive solution without the need of both power supply and self-power circuit. The passive solution reduces the implementation cost to 10% of the widely used component-level on-state voltage measurement circuit for a three-phase inverter application. It provides a plug-and-play solution with better accessibility to both existing and new designs of power electronic converters. Based on the obtained on-state voltage information, the junction temperature and health status estimation are demonstrated on the case study of single-phase inverter.

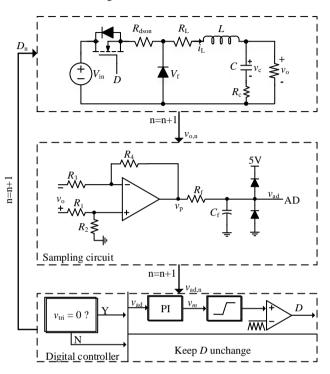

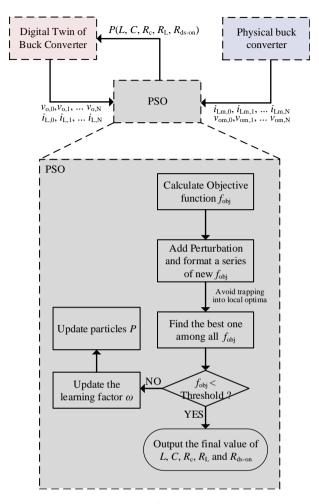

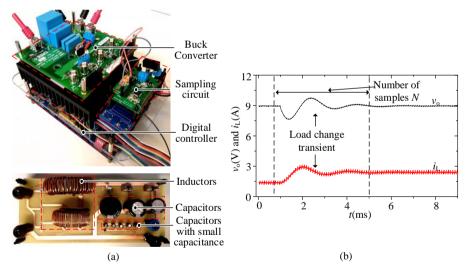

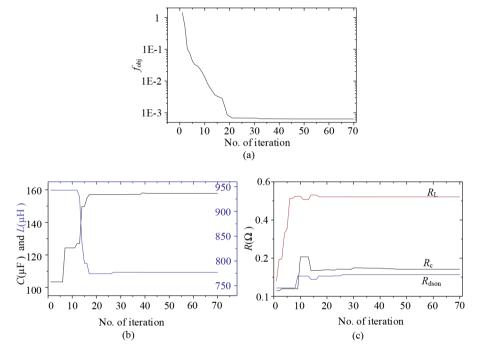

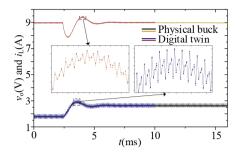

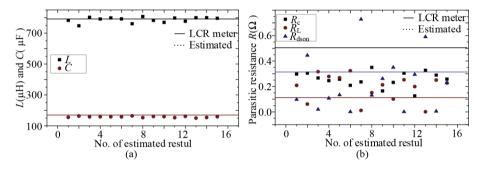

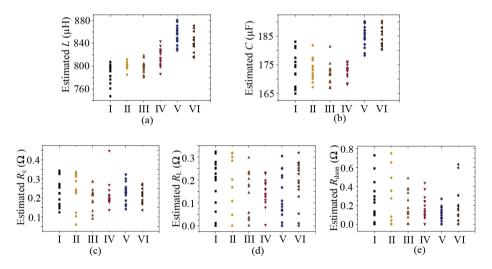

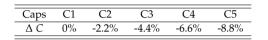

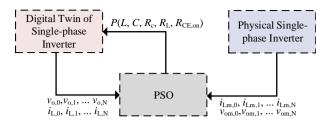

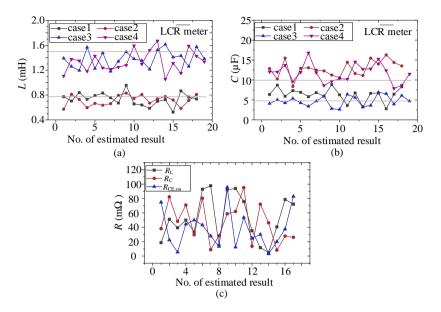

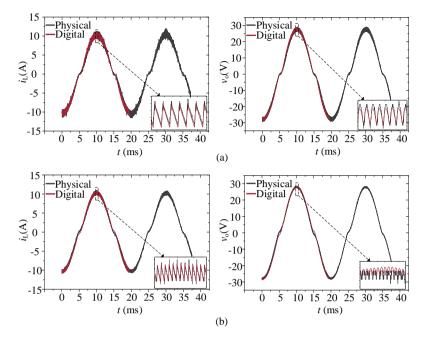

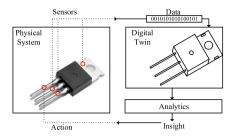

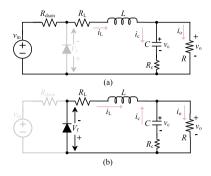

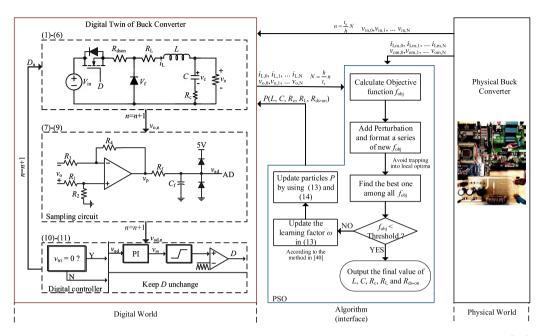

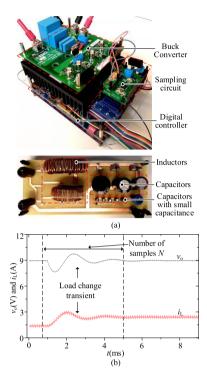

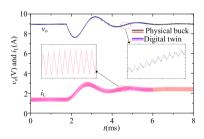

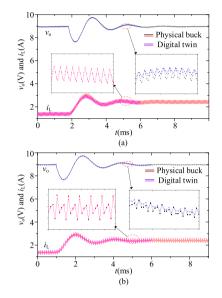

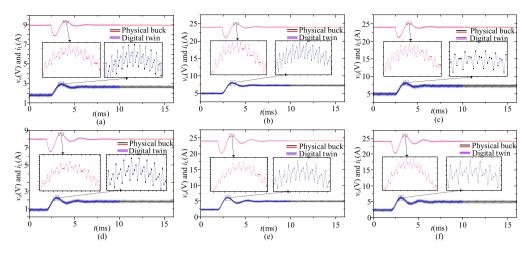

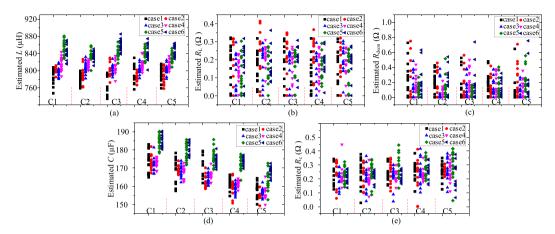

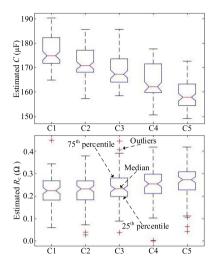

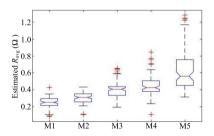

The second method is based on the digital twin concept without any additional hardware circuitry. This study chooses a Buck converter as the case study to prove the concept by using its digital twin for the degradation status monitoring of MOSFETs and capacitors. The analytical models of the power stage and controllers are built up for the Buck converter. The in-situ component parameters, such as the on-state voltage of MOSFETs, capacitance, and equivalent series resistance, are estimated based on the existing feedback signals from the physical prototype and the corresponding calculated values from the digital twin. A data cluster method is proposed, which eliminates the calibration requirement for excluding the impact of other factors on the estimated component parameters, such as load level and temperature. The proposed method enables the degradation monitoring of MOSFETs and capacitors in the Buck converter without calibration and additional sensor. The application of the concept has been extended to a single-phase inverter.

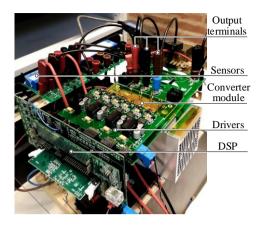

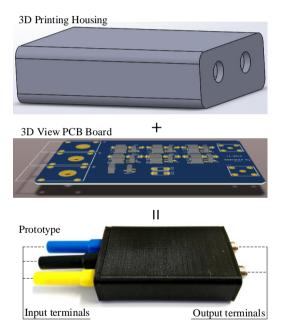

The above methods have been experimentally verified, besides the theoretical analyses. An industry-oriented prototype has been designed for the converter-level on-state voltage measurement. The results of the Ph.D. research have been presented in 1 patent, 5 journal papers, and a few other conference publications.

# Resumé

Anvendelser, såsom trækkraft og havvind, kræver omkostningseffektive og robuste tilstandsovervågningsløsninger til driftsoptimering og forudsigelig vedligeholdelse. Der er stadig en kløft mellem akademisk forskning og industrielle applikationer i tilstand og sundhedsovervågning i elektriske elektroniske omformere fra signaludvindings-, kalibrerings- og databehandling sperspektiver. Denne ph.d. undersøgelse foreslår to konverter-niveau tilstand overvågningsmetoder, der har lovende funktioner til at bygge bro over.

Den første metode er baseret på en konverterniveau på- spændingsmå -lingstilgang. On-state spænding, såsom mætningsspænding for IGBT'er og fremadspænding af dioder, er en meget brugt elektrisk parameter til kryds og helbredstilstand estimering af effekt halvlederleder switches. Konventionelle metoder er hovedsageligt på komponentniveauet ved at tilføje et målekredsløb for hver switch i dens gate driver-kredsløb. Det lider af to udfordringer: 1) portdriver er ikke altid tilgængelig, især for strømkonvertere med designfrysning, og 2) det har en relativt høj pris og kompleksitet. Denne undersøgelse foreslår et enkelt målekredsløb, der er tilsluttet midtpunkterne af fasebenene på en enfaset inverter eller trefaset inverter. Det kan måle on-state spændinger for alle strømafbrydere, inklusive dioder. Der er også foreslået tre varianter af kredsløbene: 1) med ekstern strømforsyning, som eksisterende metoder på komponentniveau gør; 2) med en selvkraftsplan for at udelukke strømforsyningen, der er den dyreste komponent i målekredsløbet, og 3) enkel passiv løsning uden behov for både strømforsyning og selvkraftkredsløb. Den passive løsning reducerer implementeringsomkostningerne til 10 % af det vidt anvendte komponentniveau på-spændingsmålingskredsløb til en trefaset inverterapplikation. Det giver en plug-and-play-løsning med bedre tilgængelighed til både eksisterende og nye design af elektriske elektroniske omformere. Baseret på den opnåede onstate spændingsinformation, demonstreres forbindelsestemperatur og sundhedsstatusestimering i case study af enfaset inverter.

Den anden metode er baseret på det digitale tvillingekoncept uden yder ligere hardwarekredsløb. Denne undersøgelse vælger en Buck-konverter som casestudie til at bevise konceptet ved at bruge dets digitale tvilling til nedbrydningstatusovervågning af MOSFETs og kondensatorer. De analytiske modeller for strømtrinet og controllere er opbygget til Buck-konverteren. Komponentparametrene in situ, såsom on-state spænding af MOSFETs, kapacitans og ækvivalent seriemodstand, estimeres baseret på de udgående feedbacksignaler fra den fysiske prototype og de tilsvarende beregnede værdier fra den digitale tvilling. Der foreslås en dataklyngemetode, der eliminerer kalibreringsbehovet for at udelukke påvirkningen af andre faktorer på de estimerede komponentparametre, såsom belastningsniveau og temperatur. Den foreslåede metode muliggør nedbrydningsovervågning af MOSFET'er og kondensatorer i Buck-konverteren uden yderligere sensor og kalibrering. Anvendelsen af konceptet er blevet udvidet til en enfaset inverter.

Ovenstående metoder er blevet eksperimentelt verificeret ud over de teoretiske analyser. En brancheorienteret prototype er designet til konverterniveau ved spændingsmåling. Resultaterne af ph.d. forskning er præsenteret i 1 patent, 5 tidsskriftsartikler og et par andre konferencepublikationer.

# Preface

This PhD thesis is a summary of the PhD project "Advanced Converter-Level Condition Monitoring for Power Electronics Components". This PhD project is supported by Department of Energy Technology, Aalborg University, Denmark.

Firstly, I would like to express my deepest gratefulness to my supervisor, Professor Huai Wang, for his professional, patient, and earnest guidance. Especially, he gave me a chance to pursuit my PhD degree. He is one of the most inspiring, insightful, and kind persons I have ever met. He provides a lot of instructive advices and valuable opportunities for both my research and career. It is my great honor to be one of his PhD students.

I am also grateful to Dr. Yanfeng Shen and Dr. Haoran Wang for their selfless help and effective discussion during my PhD study.

I would also like to thank Dr. Teng Long for inviting me as a visiting student in his group. I benefit a lot from this study abroad in University of Cambridge.

Many thanks to all my colleagues at the Department of Energy Technology, Aalborg University, for their valuable discussion and kind help. Especially, the FBL group, for organizing regular group meeting and various social events.

Finally, I want to thank my family for their consistent support. Last but most importantly, I would like to give my sincerest gratitude to my wife, for her boundless love and more than I can express in words. Without her support and understanding, I wouldn't manage this PhD study. Everything seems possible with she by my side.

> Yingzhou Peng Aalborg University, October 7, 2020

Preface

| Absti  | ract      |                                                                | iii |

|--------|-----------|----------------------------------------------------------------|-----|

| Resu   | mé        |                                                                | v   |

| Prefa  | ce        |                                                                | vii |

| Re     | eport     |                                                                | 1   |

| Part I | [. Pream] | ble                                                            | 3   |

| 1      | Intro     | duction                                                        | 4   |

|        | 1.1       | Background and motivation                                      | 4   |

|        | 1.2       | Literature study on condition monitoring methods for           |     |

|        |           | power electronic components                                    | 8   |

|        | 1.3       | Project motivation                                             | 15  |

|        | 1.4       | Project objectives and limitations                             | 16  |

|        | 1.5       | Thesis outline                                                 | 18  |

|        | 1.6       | List of disseminations                                         | 18  |

| Part 1 | II. Hardv | ware Based Non-invasive Converter-level Condition Mon-         |     |

| ite    | oring for | r Power Semiconductor Devices                                  | 21  |

| 2      | Desig     | gn of the converter-level on-state voltage monitoring circuits | 22  |

|        | 2.1       | Existing component-level on-state voltage monitoring           |     |

|        |           | circuits                                                       | 22  |

|        | 2.2       | Proposed circuits for converter-level on-state voltage mon-    |     |

|        |           | itoring                                                        | 28  |

|        | 2.3       | Selection of components                                        | 34  |

|        | 2.4       | Performance testing                                            | 35  |

|        | 2.5       | Summary                                                        | 40  |

| 3      | Appl      | ication of the converter-level on-state voltage measure-       |     |

|        | ment      | circuits                                                       | 43  |

|        | 3.1       | Implementation in a single-phase inverter                      | 43  |

|     |        | 3.2      | Implementation in a three-phase inverter                    | 50  |

|-----|--------|----------|-------------------------------------------------------------|-----|

|     |        | 3.3      | Implementation in other power converters                    | 55  |

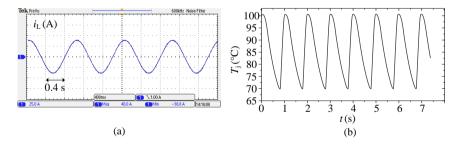

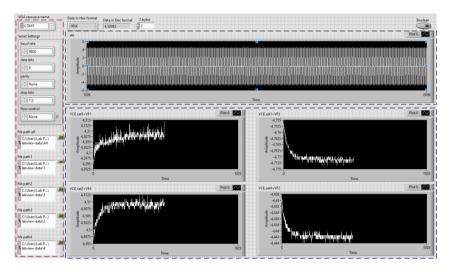

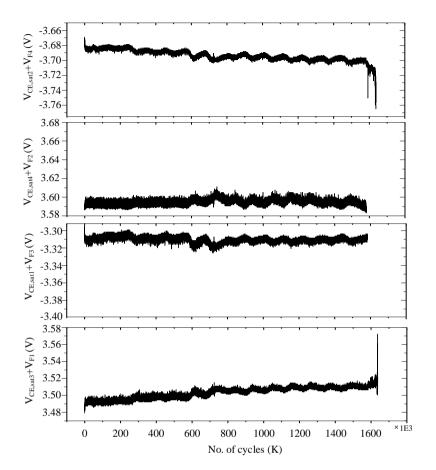

|     |        | 3.4      | Verification of the proposed circuits with power cycling    |     |

|     |        |          | testing                                                     | 58  |

|     |        | 3.5      | Verification of the proposed circuits with junction tem-    |     |

|     |        |          | perature estimation                                         | 61  |

|     |        | 3.6      | Summary                                                     | 63  |

| Da  | + III  | Diait    | al Twin Based System-level Condition Monitoring for         | 4   |

| 1 a |        | er Con   |                                                             | 65  |

|     | 4      |          | mentation of digital twin based condition monitoring in     | 05  |

|     | т      | -        | C converters                                                | 66  |

|     |        | 4.1      | Digital twin concept                                        | 66  |

|     |        | 4.1      | Digital twin of Buck converter case study: operation        | 00  |

|     |        | 4.2      | ° .                                                         | 67  |

|     |        | 4.3      | principle                                                   | 07  |

|     |        | 4.5      | Digital twin of the Buck converter case study: experi-      | 73  |

|     |        | 4.4      | mental testing for health indicators identification         | 13  |

|     |        | 4.4      | Digital twin of buck converter case study: Experimental     |     |

|     |        | 4 5      | testing for degradation monitoring                          | 77  |

|     | -      | 4.5      | Summary                                                     | 83  |

|     | 5      |          | ility study on the digital twin for single-phase inverter . | 85  |

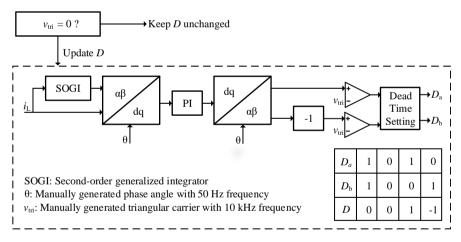

|     |        | 5.1      | Establishment of the digital twin for single-phase inverter |     |

|     |        | 5.2      | Experimental verification                                   | 87  |

|     |        | 5.3      | Summary                                                     | 89  |

| Pa  | rt IV. | Conclu   | usions                                                      | 91  |

|     | 6      |          | ary and outlook                                             | 92  |

|     |        | 6.1      | Summary and main contributions                              | 92  |

|     |        | 6.2      | Research perspectives                                       | 93  |

|     |        |          | 1 1                                                         |     |

| Bi  | bliog  | raphy    |                                                             | 95  |

|     | Refe   | rences   |                                                             | 95  |

|     |        |          |                                                             |     |

|     | Sala   | atad I   | Publications                                                | 107 |

|     | Sele   |          | ublications                                                 | 107 |

| Ι   | A D    | igital 🗆 | Twin Based Estimation Method for Health Indicators of       | E   |

|     | DC-    | -DC Co   | onverters                                                   | 109 |

| Π   | Con    | verter-1 | level On-state Voltage Measurement Method for Power         | r   |

| 11  |        |          | ictor Devices                                               | 125 |

|     |        |          |                                                             |     |

| II  |        |          | ver Solution for the On-State Voltage Monitoring Circuit    | t   |

|     | of P   | ower S   | emiconductors                                               | 133 |

|     |        |          |                                                             |     |

- IV An On-line Calibration Method for TSEP-based Junction Temperature Estimation 145

- V A Passive Circuit for On-State Voltage Measurement of Power Semiconductor Devices 155

# Report

# Part I. Preamble

This part is the preamble of the PhD project, which includes one chapter-**Chapter 1**. Introduction.

This chapter discusses the background and motivation of the PhD project. The research questions and objectives are discussed. Then, the outline of the PhD thesis is presented to show the flow of this research work.

### 1.1 Background and motivation

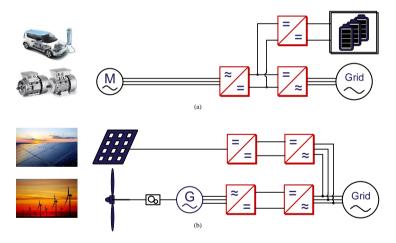

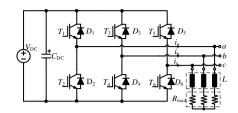

Power electronic converters serve as a key role in power generation, transmission, distribution, and consumption by providing sustainable, flexible, and stable power [1]. It is usually used to achieve the voltage and power conversion between direct current (DC) and alternate current (AC), frequency conversion, and phase conversion in many industrial applications, such as renewable power generation including Photovoltaic (PV) and Wind Turbine (WT), Electric Vehicle (EV) and aircraft, train traction, and Adjustable Speed Drives (ASD) [2–6]. For example, Fig.1 shows the examples of power converter applications. To provide different powers concerning various applications, the type of power converter differs from DC-DC, DC-AC, to AC-DC converters.

Fig. 1: Typical applications of power converters in: (a) electric vehicle and motor drives; (b) photovoltaic and wind turbine.

Conventionally, the principle design objective of power electronic converter is to improve the competitiveness in terms of economy and performance, which can be achieved by considering the following four factors [7]:

• Cost: it is usually the essential consideration for most applications since maximizing profit is the main target of converter producers.

- Efficiency: Customers prefer to the converters with higher efficiency due to lower energy lost;

- Power density: In some space-critical applications, such as electric vehicle, aircraft, and aerospace, the space for power converter is very limited;

- Manufacturability: Due to the increasing cost of labor and logistics, power converters are expected to be conveniently and economically produced and installed.

In recent decades, power converters are increasingly implemented at harsh and stressful conditions and bear the stresses coming from the temperature variation, mechanical vibration, humidity, and salinity penetration. After a long-term operation, the power converter may become vulnerable and unable to withstand those stresses. Consequently, the unexpected failure of power converter is becoming an issue. For example, field experiences in renewable applications show the critical role of power converters in terms of failure rate and maintenance cost [8]. Moreover, a survey from industry perspective reported that 93 % of respondents regarded reliability as the main issue for power electronic converters. More than 50 % emphasized the importance of improving the condition monitoring tools [9];

Therefore, to optimize the design of power converter, besides the four factors mentioned above, reliability is considered as an additional performance factor since it has significant impact on availability, safety, and operation cost.

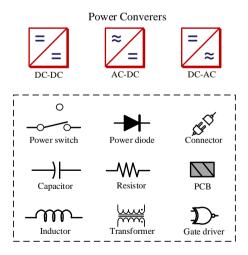

Fig. 2: Basic compositions of power electric converter.

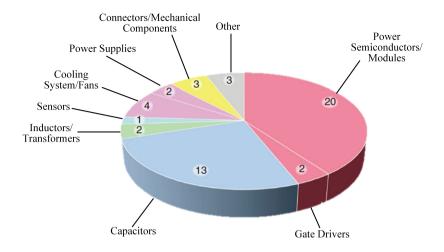

Fig. 3: The importance distribution of components in terms of reliability improvement in power electronics converter systems, from industry experts perspective [10].

The reliability of a power converter is dependent on each composed components, mainly including the power semiconductors/modules (power switches and diodes), capacitor, inductor, resistor, gate drive, and transformer as shown in Fig.2. Among them, power devices and capacitors are considered as the most crucial components that need future research to improve their reliability compared to other components according to the industry experts' answers in an industry survey as shown in Fig.3 [10], accounting for 20% and 13% of the power electronics systems, respectively.

Power device and capacitor are frequently considered as the most vulnerable components among the power converter based on the above information. Besides, they are also essential in terms of function, volume, and cost [7]. Therefore, currently, the reliability-related research mainly focuses on these two components [11].

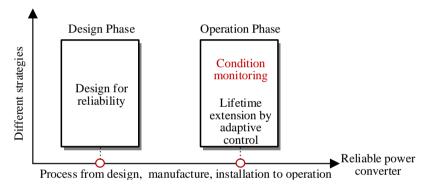

To mitigate the risk of unexpected failures, researchers are endeavoring to make the power converter more reliable and available by using different strategies over the design and operation phases of power converter as shown in Fig.4, which are detailed below:

• Design phase: reliability should be considered along with efficiency and cost at the very beginning of power converter hardware design. For example, increasing the design margin is one option to improve reliability [9], so that it can meet the reliability requirement under a specific operating condition. Moreover, the distribution of capacitor-bank can be well-designed to improve its lifetime [12, 13]. Also, in some applications, multi-converters are required. A proper uniformity design between these converters can improve the lifetime of the entire multi-

converters system [14]. Additionally, temperature control strategies are used to reduce the junction temperature swing of power devices, resulting in longer lifetime of power devices [15–19]. However, introducing temperature control needs to modify the original controller, which is not preferable. Finally, once the hardware and control strategy of power converter are decided, the lifetime models can be established and used to predict the life cycle of power devices and capacitors [20–22].

• Operation phase: firstly, condition monitoring technology can be used to monitor the health condition of power devices and capacitors in realtime, so that the degradation process and potential failures can be predicted, and the operators can schedule the maintenance to secure the availability of power converters [9, 23–26]. Or, the derating operation can be applied through adaptive control to achieve longer lifetime.

Fig. 4: Strategies of reliability design for power converter at different stages.

With the strategies mentioned above, the reliability and availability of power converter can be improved throughout its whole lifetime. At the hardware design stage, because increasing design margin and guaranteeing uniformity design lead to that the selected components have higher rated power than the required, which means the reliability is increased by sacrificing cost and efficiency in some degrees. At the control design stage, reducing the junction temperature swing needs to modify the conventional mature control algorithms, which may not be readily accepted by converter producers. Establishing lifetime models highly relies on the accuracy of physic and material knowledge of components, which are even different among a population of components with the same product part number. Also, operational and environmental conditions can affect the lifetime model parameters significantly. Thus, it is challenge to predict the real end-of-life of power converters in field applications through lifetime model.

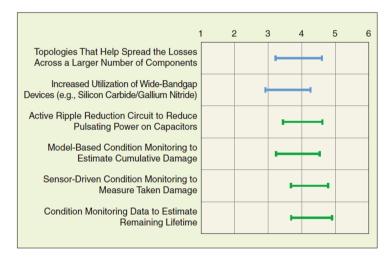

Condition monitoring technology is adopted when the converter is in operation with the ability of online assessing the health condition of the key components. It is reported that the cost of wind farm mainly comes from both in terms of installation cost and operating cost. Particularly, 50 % of the O&M is due to unscheduled maintenance costs [27]. Also, the economic benefits attained through 1 % efficiency improvement for PV manufactures can be easily negated by a few-days downtime due to failures [9]. With the condition monitoring technology: 1) the predictive maintenance can be realized, which improves the availability and reduces the life-cycle cost; 2) the design margin of power converter can be reduced since the health condition becomes accessible, leading to the reduction of design cost further. Most importantly, from the industry perspective, it is reported in [10] that condition monitoring is one of the most important approaches to address the reliability issue of power electronic converter as shown in Fig.5, presenting that the last three listed topics are related to condition monitoring and given high beneficial score by experts.

**Fig. 5:** The possible methods that will address the reliability of power electronics converters in the future, from industry experts' perspective. The scale is from one (not beneficial) to six (very beneficial). [10].

# **1.2** Literature study on condition monitoring methods for power electronic components

#### 1.2.1 Power switches

Condition monitoring technology for power switches has been developed for decades, starting from failure mechanisms research to laboratory test

[9, 23, 24]. Usually, power switches are well packaged and sealed to achieve electrical, mechanical, and chemical protection. Therefore, the operators are blind to their internal degradation and cannot directly predict potential failures. However, the degraded power switches present abnormal electrical, thermal behaviors, and even acoustic and optic signals, which are taken to research the condition monitoring technologies indirectly. The detailed process of condition monitoring development is shown below:

- Degradation mechanism (Step 1): the failures of power switch are mainly occurred in chip-level and packaging-level. Most of the chip-related failures are due to the overstress caused transient breakdown. Another chip-related failure occurring in the gate oxide-layer of silicon-carbon power switches is reported as well [28, 29], which is due to wear-out. The traditional packaging techniques include wire-bond and press-pack. Among them, the wire-bond is the dominant one due to its well-established and low cost wire-bonding technology. Therefore, the research in this project is based on wire-bond based power switches. It has been unveiled that the degradation of wire-bonding power switches is mainly contributed by the bond-wires lift-off and solder layer degradation for both silicon and silicon-carbon devices [30–33]. It is due to the repeatable stress-strain cycle caused by long-term electrical and thermal cycle [34–37].

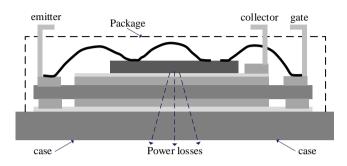

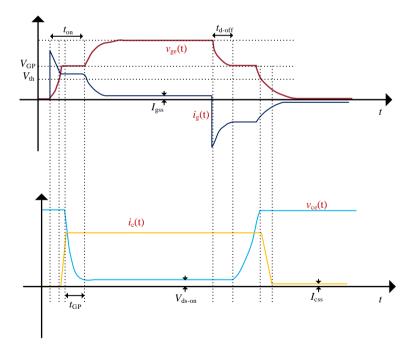

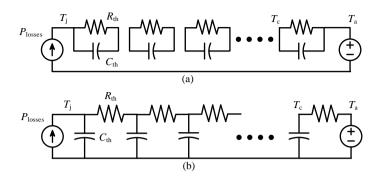

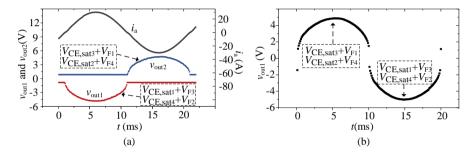

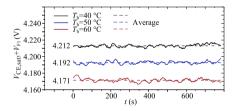

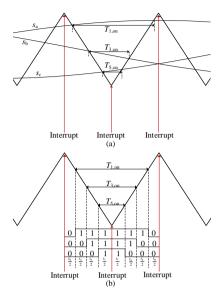

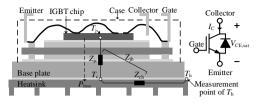

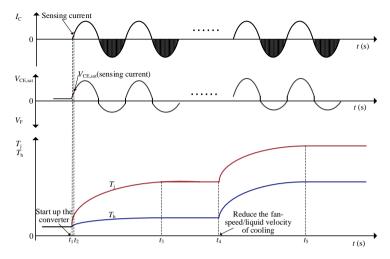

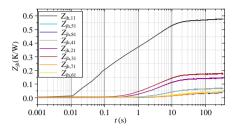

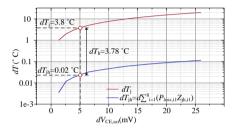

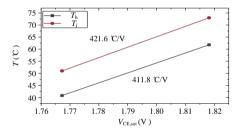

- Health indicators (Step 2): The degradation mechanisms described in step 1 can be related to various health indicators, including electrical, thermal, and even acoustic parameters. Among them, the electrical indicators can be extracted from those electrical waveforms as marked in Fig.7 [38–47].  $V_{GP}$  is the miller plateau in the gate turn-on voltage,  $t_{GP}$  is the duration time of the miller plateau,  $V_{th}$  is the threshold voltage,  $t_{on}$  is the turn-on time,  $t_{d-off}$  is the turn-off delay time,  $I_{gss}$  is the gate leakage current,  $I_{css}$  is the collector leakage current,  $V_{CE,sat}$  is the on-state voltage. The thermal behavior of power module as shown in Fig.6 can be expressed by the thermal networks as shown in Fig.8. The degradation of solder layer can weaken the capability of power losses dissipation, leading to the increase of thermal parameters  $R_{th}$  and  $C_{th}$ . Then,  $T_c$  is affected indirectly [48, 49]. Additionally, the optic and acoustic indicators were also presented in [50, 51]. Once the indicators are selected, they can be extracted from the electrical terminals (e.g., collector/drain, emitter/source, and gate) [52-60], thermal terminals (e.g., case), and by the optical and acoustic sensing equipment directly.

- Measurement and estimation of health indicator (Step 3): it is verified that all of the health indicators described in step 2 can reflect the degradation of power devices in some degree with laboratory testing. How-

ever, some are hardly measured in real-time, such as the collector and gate leakage current. For those measurable indicators, the corresponding on-line monitoring circuits are designed and tested in the laboratory [61–81]. Moreover, the model based estimation methods can also obtain the health indicators, but are rarely investigated. For example, the capacitance of capacitor was estimated in [82, 83].

• Data processing (Step 4): after the health indicators are obtained through the measurement circuits, data analysis and calibration are required to eliminate the data noise, operational and environmental impacts, consequently, to represent the health level of power devices [39].

To implement condition monitoring in field applications, the selection of indicators can be achieved by following some major considerations: 1) sensitivity to the dominant degradation mechanism of interest; 2) measurement complexity and cost, such as sampling frequency; 3) noise-immune ability, i.e., robustness. For the optical and acoustic indicators, the additional equipment with strong noise-immune ability is required to sense the faint change of optical and acoustic signals. For the thermal indicators, because the change of  $T_{\rm c}$  caused by the degradation of power devices can be easily negated by other neighboring heat sources, leading to lower degradation sensitivity or false detection. Moreover, installing multiple  $T_c$  sensors on the case of the module can degrade the capability of the power devices to remove power losses from the semiconductor onto the heatsink. Therefore, it is shown that the majority of condition monitoring researches for power switches focus on electrical indicators that can be extracted from the electrical terminals. Among them, the indicators relative to the switching transient appear to be attractive since the switching properties generally exist while the device is in operation. However, the measuring circuits for these indicators are connected to the gate of devices. Consequently, it is hard to distinguish if the parameter shifts of these indicators is due to the degradation of semiconductor or the gate driver. Meanwhile, integrating monitoring circuits with gate drivers may risk its regular operation, which is critical to a functioning converter. Moreover, the switching indicators are thought to be high frequency and sensitive to voltage, current, temperature, and parasitic parameters of connecting wire, which requires complex measurement circuit.

Alternatively, the on-state voltage of power switches is thought to be the most promising and practical health indicator so far, as it shows higher sensitivity to the degradation of power devices, non-invasive measurement due to the connection with power terminals, and simple measuring circuit due to the relative low frequency feature compared to the switching transient related indicators. Nevertheless, all of these existing on-state voltage measuring methods are designed to monitor a single power switch, calling component-level measurement [78], which causes practical issues while applying to a

converter: 1) The circuit complexity and cost are multiplied to monitor the all power switches in a converter; 2) It is connected to the power terminals of individual switching devices, which may introduce more connecting terminals; and 3) it has one reference ground for each phase-leg, which requires more isolation stages while sampling the data of all devices.

Fig. 6: A standard power module.

Fig. 7: Typical switching waveforms of power devices.

Fig. 8: Typical thermal network of power devices: (a) Foster network; (b) Cauer network.

#### 1.2.2 Capacitors

Capacitors are one of the reliability-critical components in power converters and many efforts have been made to the condition monitoring of capacitors, so as to obtain their on-line health information and predict the potential failure [25, 26].

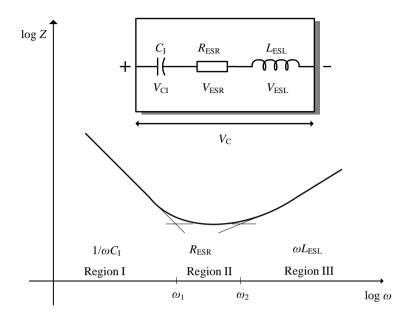

The simplified equivalent circuit of a capacitor is presented in Fig.9, including a capacitor ( $C_{\rm I}$ ), an equivalent series resistor ( $R_{\rm ESR}$ ), and an equivalent series inductor ( $L_{\rm ESL}$ ). It is unveiled that the degradation of the capacitor can shift these three parameters [25]. Consequently, the condition monitoring of capacitor can be achieved by monitoring these three parameters based on its impedance in response to frequency as shown in Fig.9. The impedance versus frequency plot of a capacitor can be divided into three regions based on  $\omega_1$  and  $\omega_2$  (typically 5-10 kHz) [84, 85], showing dominated capacitive impedance in region I, resistant impedance in region II, and inductive impedance in region III. Generally,  $L_{\rm ESL}$  can be neglected due to low inductance (nH level) and negligible impedance in region I and II. Therefore,  $C_{\rm I}$  and  $R_{\rm ESR}$  are the two leading health indicators for capacitor.

Fig. 9: Equivalent circuit and impedance characteristics of capacitors.

Based on the operational frequency region I and II, there are two main methods to estimate  $C_{\rm I}$  and  $R_{\rm ESR}$ : 1) in region I, the capacitance is the dominated value. Usually, the capacitor operates at some special conditions (frequency is less than  $\omega_1$ ), such as off-line discharge and charge transient, converter start-up and shut-down transient. During these particular conditions, the capacitance can be estimated through the charge/discharge curve; 2) in region II, capacitor operates at normal condition (frequency is within  $\omega_1$  and  $\omega_2$ ), and the capacitor voltage ripple and current ripple can be used to estimate the  $R_{\rm ESR}$ .

**Charge/discharge transient based condition monitoring method [86–89]** The start-up and shut-down transients are existed in many applications, which can be took to estimate  $C_{I}$ . For example, the discharge process of the DC-link capacitor in a converter can be recorded with the help of a discharge resistor  $R_{d}$ . Then, the discharge process during the shut-down can be expressed by:

$$u_{\rm C} = U_0 \times e^{-\frac{t}{(R_{\rm ESR} + R_{\rm d})C_{\rm I}}} \tag{1}$$

where  $u_{\rm C}$  is the capacitor voltage during discharge,  $U_0$  is the initial value of  $u_{\rm C}$ . Then,  $(R_{\rm ESR} + R_{\rm d})C_{\rm I}$  can be easily obtained through data fitting. Among them,  $R_{\rm d}$  is already known and far larger than  $R_{\rm ESR}$ , resulting in negligible  $R_{\rm ESR}$ . Finally,  $C_{\rm I}$  can be calculated.

This method is very simple and effective, and can obtain the accurate results without adding any external hardwares. However, it is kind of quasi on-line method due to the requirement on dis/charge event.

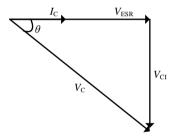

**Ripple based condition monitoring method [90–98]** According to Fig.9, the phase voltage across  $C_{\rm I}$  and  $R_{\rm ESR}$  at the frequency between  $\omega_1$  and  $\omega_2$  are depicted in Fig.10 based on the polarity of capacitor voltage  $V_{\rm C}$  and current  $I_{\rm C}$  (assuming  $V_{\rm ESL}$  is negligible). Then, based on the Pythagorean trigonometric, the phase difference between  $V_{\rm C}$  and  $I_{\rm C}$  can be expressed by:

$$\cos\theta = \frac{V_{ESR}}{V_C} \tag{2}$$

then,  $R_{\rm ESR}$  can be calculated by:

$$R_{\rm ESR} = \frac{V_{ESR}}{I_C} = \frac{V_C \times \cos\theta}{I_C}$$

(3)

Fig. 10: Phase direction of the equivalent circuit of capacitor by neglecting  $L_{ESL}$ .

$V_{\rm C}$  and  $I_{\rm C}$  at the frequency between  $\omega_1$  and  $\omega_2$  can be obtained by using a bandpass filter,  $\theta$  can be obtained by using a phase detector. It can be seen that the key steps of this method is to extract the ripple values of capacitor voltage and current, which is usually realized by adding the bandpass filters. In practice, capacitor voltage is measured for control or protection. The capacitor current be obtained: 1) by measuring the output currents of power converter and combining the on-off information of each power device; 2) embedding the current sensor inside the capacitor. Overall, the ripplebased method is an on-line condition monitoring and suitable for different applications. However, firstly, the indirect measurement of capacitor current can cause transfer errors and requires the PWM information. Moreover, the ripple extraction needs the bandpass filter and phase detector.

#### 1.2.3 Converter-level methods

Converter-level methods are proposed to realize the condition monitoring from the converter-level terminals, instead of the individual terminals of a single component. To our best knowledge, several converter-level methods have been proposed so far: 1) the harmonic spectrum of the output current of converter, for example, are proposed for monitoring the degradation of power switches [99, 100]. A reduction of fifth harmonic due to the increase of temperature is discovered; 2) another example is the overall efficiency of the converter [101]. The power loss generated among the converter is increased with the degradation of power switches and capacitors, leading to the reduction of overall efficiency. Nevertheless, the issues with the above converter-level methods are: a) both efficiency and harmonic are obtained by measuring the converter-level signals (e.g., DC-link voltage/current, output voltage/current) that are hardly affected by the degradation of power switches and capacitors. Thus, it is difficult to measure these indicators with enough accuracy for degradation monitoring; b) both the degradations of capacitor and power switch can affect these indicators and can not be distinguished; 3) moreover, due to the development of advanced computers and algorithms, the neural-network is recommended to do condition monitoring as well [102, 103]. This method can estimate the health status of the converter components by training an effective neural model that covers the full operation and degradation conditions of converter. However, firstly, the change of converter-level signals caused by component degradation is less than 0.1 % and could be covered by the measurement noise. Secondly, it is a challenge to obtain the training data that covers all possible operation and degradation conditions in field applications. Overall, these existing converter-level methods have low sensitivity in indicating the degradation of converters.

### 1.3 Project motivation

Existing condition monitoring with component-level methods require complex measurement circuits. For the converter-level methods, they rely on the measurement of converter-level signals. Thus, their degradation sensitivity is much lower than the measurement circuit based component-level methods and the change of converter-level indicators due to degradation could be lower than noise in field applications. Therefore, as the increasing demand for condition monitoring from field power converter applications, the movement toward practical and advanced condition monitoring methods meets new challenges.

• Due to the accessibility to existing or even next generation power electronics converters, the converter-level condition monitoring solutions with less or even without additional hardware are expected;

- Practical applications of condition monitoring face challenges in reducing the measuring circuit complexity, size, and cost. Moreover, a plugand-play solution with less connecting terminals is desired;

- Health indicators are also dependent on operational and environmental conditions, such as voltage, current, and temperature. Thus, a method capable of excluding these impactors beside degradation is required, which can be achieved by either calibration and data analytics-based methods.

- Software-based methods are relatively preferred from application perspective due to reduced cost and implementation complexity, compared to hardware-based methods.

Therefore, the embodiment of condition monitoring technologies with high performance in terms of complexity, cost, degradation sensitivity, and even hardware-free are still needed.

### 1.4 Project objectives and limitations

### 1.4.1 Research questions and objectives

Based on the discussion of the trend for the practical and advanced condition monitoring technologies and the review of the existing methods, the question about how to develop converter-level measurement/estimation methods of health indicators of power electronic components with reduced complexity and cost will be answered in this project. Specifically, the following research questions are to be addressed:

- Is it possible to measure the on-state voltage of power semiconductor devices without accessing its gate or power terminals?

- Is it possible to achieve software based health indicator estimation without the need for training data?

- Is it possible to achieve the condition monitoring of power electronic components without the need of calibration?

With the questions listed above, the overall objective of this PhD project is to research the advanced converter-level condition monitoring methods for power electronics components. The objectives of this project are detailed as follow:

• Circuit design methodology of the converter-level condition monitoring: the on-state voltage of power devices is the most widely reported health indicator so far. Although different measuring circuits have been

proposed in recent decades, they are limited in component-level measurement and hardly used in practical applications. Based on this, a converter-level on-state voltage measuring circuit is designed and developed with the considerations of circuit complexity, size, cost, and practical implementation;

- Implementation of the proposed converter-level condition monitoring circuit: In order to achieve the health assessment of power devices by using the proposed circuit, the practical implementations of the proposed circuit in different applications are investigated. Moreover, the proposed circuit is also capable of estimating the junction temperature of power devices through the monitored on-state voltage;

- Digital twin based condition monitoring for power converters: From the view of industry applications, it would be better if the condition monitoring can be achieved with existing sensors and without additional circuit. The possibility and feasibility of using digital twin to achieve condition monitoring are investigated. The experimental validation is also carried out. Meanwhile, the merits and shortcomings are discussed.

### 1.4.2 Project limitations

The PhD project studies the design and implementation of converter-level on-state voltage measurement and digital twin based health indicator estimation to achieve the condition monitoring for the key components of power converters with reduced complexity and cost. However, several limitations exist in this project:

- The failure mechanisms of power devices and capacitors considered in the condition monitoring are thermal and electrical stresses related degradation. Humidity, salinity, and other uncertain factors are not included;

- The verification of the proposed methods are limited to the laboratory testing at the time when this thesis is submitted. Field testing is to be performed in the future with industry partners;

- The degradation testing and verification of the proposed digital twin based method for condition monitoring is mainly conducted with Buck converter. The realization of single-phase inverter digital twin is investigated. It is possible to extend the study on the applications for three-phase converters.

| Chapter No. | <b>Relevant Publications</b> |

|-------------|------------------------------|

| 1           | -                            |

| 2           | J2, J3, J5, P1               |

| 3           | J2, J3, J4, J5               |

| 4           | J1                           |

| 5           | -                            |

| 6           | -                            |

Table 1: The related publications for each chapter.

#### 1.5 Thesis outline

The outcome of this project is documented by a PhD thesis, which includes two parts: a report and related disseminations (publications, patents, and tutorial).

The first part is Chapter 1. Introduction, which is the preamble of the report.

The second part is entitled "Hardware based non-invasive converter-level condition monitoring for power semiconductor devices", including two chapters. Chapter 2. Design of the converter-level on-state voltage monitoring circuits. Chapter 3. Applications of the converter-level on-state voltage monitoring circuits.

The third part is entitled "Digital twin concept based system-level condition monitoring for power converters", covering two chapters. Chapter 4. Implementation of digital twin for condition monitoring in DC-DC converters. Chapter 5. Feasibility study on the digital twin for single-phase inverter.

Last chapter of the report is Chapter 6. Summary and Outlook. It includes the summary of the contributions in this project, new research perspective and challenges for future study.

#### 1.6 List of disseminations

The invention and publications from this PhD project are shown below. In order to show the contributions for each chapter, the relationship between the chapters of the PhD thesis and the patent/publications are shown in Table. 1.

#### Patents

P1. Y. Peng, H. Wang, "Non-invasive front-end for power electronic monitoring", filed, P71138DK01, 2020.

#### Journal Papers

J1. Y. Peng, Shuai. Zhao, and H. Wang "A Digital Twin based Estimation Method for Health Indicators of DC-DC Converters" *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 1220-1224, Feb. 2021.

- J2. Y. Peng, Yanfeng. Shen, and H. Wang "A Converter-level On-state Voltage Measurement Method for Power Semiconductor Devices" *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 2105-2118, Feb. 2021.

- J3. Y. Peng, H. Wang "A Self-Power Method for A Converter-level On-state Voltage Measurement Concept" *IEEE Trans. Power Electron.*, Under review, 2020.

- J4. Y. Peng, H. Wang "An On-line Calibration Method for TSEP-based Junction Temperature Estimation" *IEEE Trans. Power Electron.*, Under review, 2020.

- J5. Y. Peng, H. Wang "A Passive Circuit for On-State Voltage Measurement of Power Semiconductor Devices" *IEEE Trans. Power Electron.*, Under review, 2020.

**Conference** Papers

- C1. Y. Peng, Yanfeng. Shen, and H. Wang, "A Condition Monitoring Method for Three Phase Inverter Based on System-Level Signal" in *Proc. IEEE PEAC*, pp. 228-233, 2018.

- C2. Y. Peng, H. Wang, "Parameters Identification of Buck Converter Based on Dynamic Characteristics" in *Proc. IEEE ECCE Asia*, pp. 228-233, 2019.

- C3. Y. Peng, H. Wang, "Application of Digital Twin Concept in Condition Monitoring for DC-DC Converters" in *Proc. IEEE ECCE*, pp. 228-233, 2019.

#### Project

P1. H. Wang and Y. Peng, "A Power Device On-State Voltage Monitoring Apparatus for Three-Phase Power Electronic Converters", Aalborg University proof-ofconcept grant. Feb.01, 2020 - Oct.31, 2020.

# Part II. Hardware Based Non-invasive Converter-level Condition Monitoring for Power Semiconductor Devices

In this part, the development of existing component-level on-state voltage monitoring circuits are discussed firstly. Then, the circuit design methodology of proposed converter-level on-state voltage monitoring is introduced. Finally, it's implementations in different applications are illustrated as well. There are two chapters in this part: **Chapter 2**. Design of the converter-level on-state voltage monitoring circuits and **Chapter 3**. Application of the converter-level on-state voltage monitoring circuits.

This chapter studies the existing component-level on-state voltage monitoring circuits with considering circuit complexity, cost, and practical implementation. Then, the circuit design methodology for a series of converter-level on-state voltage monitoring circuits is proposed and introduced. For the view of practical application, the restrictions in component selection for the proposed circuits are fully discussed. Performance testing for each proposed circuit is characterized finally.

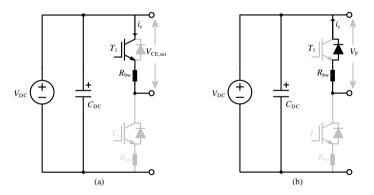

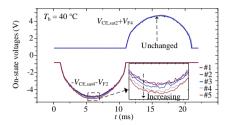

## 2.1 Existing component-level on-state voltage monitoring circuits

On-state voltage refers to the voltage across power device when it is in on-state or it is in current-freewheeling state as shown in Fig.11.  $V_{CE,sat}$  is the on-state voltage of power semiconductor devices (e.g, IGBT or MOSFET) and  $V_F$  is the forward voltage of freewheeling diode (FWD). Both  $V_{CE,sat}$  and  $V_F$  have similar features in indicating the health condition of power devices. Therefore, only  $V_{CE,sat}$  is used as a representative to analyze the failure mechanism.

Fig. 11: On-state voltage of power devices showing in a half-bridge.

As mentioned in Chapter 1, the most frequent failure mechanisms that occur in silicon devices are related to package and are primarily attributed to the different coefficients of thermal expansion (CTE) over the materials of chip, solder, and structure layers, and the temperature fluctuation they experience [9]. Specifically, along with repeated thermal cycling, the mismatch in CTE between chip (silicon) and bond-wire (aluminum) causes stress that leads to the cracks and lift-off in bond-wires. Then, the equivalent resistance of bond-wires  $R_{bw}$  is increased as well as  $V_{CE,sat}$ . Another common mismatch of CTE happens between chip (silicon), solder layer (SAC305), and DBC substrate (Al<sub>2</sub>O<sub>3</sub>), which causes cracks and voids inside the solder layer and weakens the capability of dissipating power losses from the chip onto heatsink. Consequently, the junction temperature of power device is increased, which causes

the increase of  $V_{CE,sat}$  as well. For silicon carbon devices, the dominant failure mechanism is the degradation of gate oxide layer [28, 29, 40], which causes the increase of threshold voltage. Then, the device operating in saturation mode exhibits increased on-state voltage [75].

Overall, the on-state voltage is generally sensitive to all of those dominant failure mechanisms. In addition, considering the advantages discussed in Chapter 1, on-state voltage is the most widely used health indicators for power devices. Thereafter, various on-state voltage monitoring circuits have been proposed.

The main concern for on-state voltage measuring is the capability to block the high DC-Link voltage at kV level when power device is in off-state and to precisely measure the on-state voltage up to few V at mV resolution when power device is in on-state. To achieve this, researchers have been struggling to design different circuits for decades. Those circuits have different features in respect to different applications and are discussed as below.

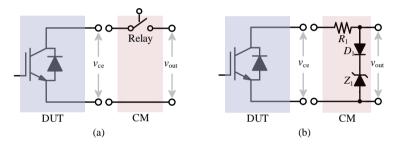

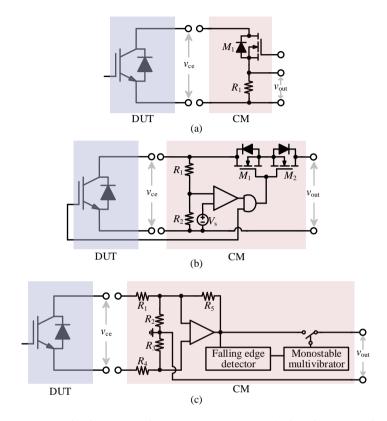

Fig. 12: Component-level on-state voltage monitoring circuits: (a) based on relay [73, 104]; (b) based on zener diode [62, 74].

The first one utilize the relay switch to block the high-voltage and pass the lowvoltage as shown in Fig.12(a) [73, 104]. The main concern is the response time for relay switch, which is 3 ms in [104] and 10 ms in [73]. Therefore, the application of relay based circuit is limited. The accuracy is determined by the voltage across relay. Therefore, the input impedance of the sampling circuit in the later stage should be high enough to make sure the current flowing through the relay can be negligible. In addition, the volume of high-voltage relay should be considered and an additional control signal is needed, which makes the circuit more complex.

In addition, Zener diode can be used to replace the relay [62, 74]. In Fig.12(b), the zener voltage of Zener diode  $V_Z$  should be larger than the maximum on-state voltage and it works like this: when the input voltage  $v_{ce}$  is lower than  $V_Z$ , only very small leakage current  $I_1$  can go through  $R_1$  and  $v_{out}$  can be expressed as:

$$v_{\rm out} = v_{\rm ce} - I_1 R_1 \tag{4}$$

when  $v_{ce}$  is higher than  $V_Z$ , the voltage across  $Z_1$  is claimed to  $V_Z$  and the voltage higher than  $V_Z$  is withstood by  $R_1$ . Then,  $v_{out}$  can be expressed as:

$$v_{\rm out} = V_{\rm Z} + V_{\rm D1} \tag{5}$$

Based on the above analysis,  $Z_1$  should be selected with low leakage current so the measurement error can be reduced.  $R_1$  should be high-voltage resistor and its

resistance should be decided by considering the rated power of  $R_1$ ,  $D_1$ , and  $Z_1$ , and the error caused by  $R_1$ . In addition, the Zener diode shows better performance than relay in response time. For example, the circuit in [74] presents 100  $\mu$ s response time.

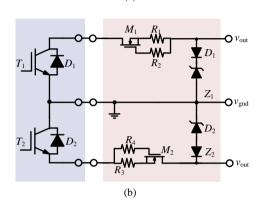

**Fig. 13:** Component-level on-state voltage monitoring circuits: (a) based on external controlled switch [105]; (b) based on gate driver controlled switch [81]; (c) based on collector signal controlled switch [61].

To reduce the response time, more faster switch devices are selected to block high-voltage as shown in Fig.13 [61, 77, 81, 105]. In Fig.13(a), the MOSFET is turned off when the input voltage  $v_{ce}$  is high-voltage and conducted when  $v_{ce}$  is low-voltage. Then,  $v_{out}$  can be expressed as:

$$v_{\rm out} = v_{\rm ce} \frac{R_1}{R_1 + R_{\rm ds,on}} \tag{6}$$

where  $R_{ds,on}$  is the on-state resistance of MOSFET and should be far smaller than  $R_1$  so as the voltage across MOSFET can be neglected.

In Fig.13(b), the MOSFET is connected in series with the device under test (DUT).  $R_1$  and  $R_2$  are used to divide  $v_{ce}$ , and the voltage across  $R_2$  is compared with the reference voltage  $V_s$  to determine if the  $v_{ce}$  is high-voltage or low-voltage. Then the

compared result is sent into an AND gate along with the gate drive signal of the DUT. Then, the output of the AND gate is used as the gate drive signal of  $M_1$  and  $M_2$ . It can be seen that the on-off state of MOSFETs is same with that of DUT, so that the high-voltage can be bearded by  $M_1$  and  $M_2$  when the DUT is in off-state. When the DUT is in on-state,  $v_{out}$  can be expressed as:

$$v_{\rm out} = v_{\rm ce} - V_{\rm M1} - V_{\rm M2}$$

(7)

where  $V_{M1}$  and  $V_{M2}$  are the on-state voltage of  $M_1$  and  $M_2$ , respectively.

Fig.13(c) uses four resistors  $R_1 - R_4$  to divide  $v_{ce}$  firstly. Then, the  $v_{out}$  is obtained through a monostable multivibrator. It is controlled by a falling edge detector. Once the  $v_{ce}$  is changed from high-voltage to low-voltage, the monostable multivibrator is turned on and  $v_{out}$  can be expressed as:

$$v_{\rm out} = v_{\rm ce} \frac{R_2 + R_5}{R_1 + R_2 + R_3 + R_4} \tag{8}$$

after a short pre-setting time, the multivibrator will back to off-state itself.

Overall, this group of circuits has very short response time. Their accuracy is determined by the selection of components as shown in (6)-(8). Especially for Fig.13(c), the temperature sensitivity and accuracy of those resistors could impact the accuracy of  $v_{out}$  significantly. The introduction of driving signal for the switches makes those circuits a little bit complex. More importantly, introducing driving signal from the gate or collector of the DUT may risk the normal operation of DUT or the monitoring circuit itself.

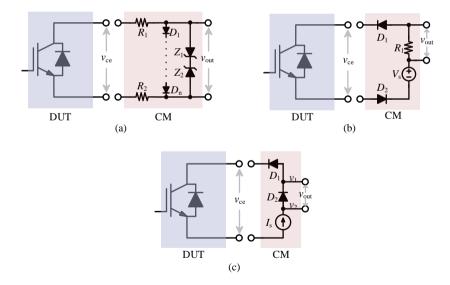

Fig. 14: Component-level on-state voltage monitoring circuits: (a) based on series connected diodes [69]; (b) based on diodes and external reference voltage source [69]; (c) based on diodes and external reference current source [72, 75].

To fix the issue caused by introducing additional gate driving signal. Diodes are used as it is able to block high-voltage and show passive characteristic [69, 72, 75]. In

Fig.14(a), multi diodes are connected in series along with two high-voltage resistors. When  $v_{ce}$  is high-voltage, those diodes are conducted and the output voltage  $v_{out}$  is claimed to:

$$v_{\rm out} = V_{\rm D1} + V_{\rm D1} + \dots + V_{\rm Dn} \tag{9}$$

where  $V_{\text{Dn}}$  is the forward voltage of  $D_n$ . The high-voltage is withstood by those two resistors.

When  $v_{ce}$  is lower than the sum of the forward voltages of all diodes, those diodes are blocked and  $v_{out}$  is:

$$v_{\rm out} = v_{\rm ce} - V_{\rm R1} - V_{\rm R2} \tag{10}$$

where  $V_{R1}$  and  $V_{R2}$  are the voltage across  $R_1$  and  $R_2$ , respectively.  $Z_1$  and  $Z_2$  are used as protection.

In Fig.14(b), two diodes are used to prohibit the high-voltage from reaching at the output terminal. While  $D_1$  and  $D_2$  are conducted by the reference voltage source  $V_s$  if  $v_{ce}$  is lower than  $V_s$ . Consequently, the output voltage can be obtained as:

$$v_{\rm out} = V_{\rm s} - V_{\rm D1} - V_{\rm D2} - v_{\rm ce} \tag{11}$$

where  $V_{D1}$  and  $V_{D2}$  are the forward voltages of  $D_1$  and  $D_2$ , respectively. For this circuit, the error is mainly caused by  $V_{D1}$  and  $V_{D2}$ . To reduce the error, Fig.14(b) is updated as shown in Fig.14(c).

In Fig.14(c),  $D_1$  and  $D_2$  are conducted by the current source when  $v_{ce}$  is low-voltage. Then,  $v_{ce}$  is:

$$v_{\rm ce} = 2v_1 - v_2 + 2V_{\rm D2} - 2V_{\rm D1} \tag{12}$$

where  $V_{D1}$  and  $V_{D2}$  are the forward voltages of  $D_1$  and  $D_2$  respectively. If  $V_{D1}$  is assumed to equal with  $V_{D2}$ ,  $v_{ce}$  can be accurately measured through  $v_1$  and  $v_2$ . Therefore, the accuracy of this circuit is determined by the difference between  $V_{D1}$  and  $V_{D2}$  while measuring.

**Fig. 15:** Component-level on-state voltage monitoring circuits: (a) based on enforced MOSFET [71]; (b) based on depletion MOSFET [76].

To increase the accuracy further, self-controlled switches are used as shown in Fig.15 [71, 76, 106]. In Fig.15(a), the on-off state of enforced MOSFET is controlled by a gate connected voltage source and a source connected resistor. Based on this circuit, the voltage across  $R_1$  can be expressed as:

$$V_{\rm R1} = V_{\rm s} - v_{\rm gs} = v_{\rm ce} - v_{\rm M1} \tag{13}$$

then, the gate-source voltage of  $M_1$  is:

$$v_{\rm gs} = V_{\rm s} - v_{\rm ce} + v_{\rm M1}$$

(14)

where  $v_{M1}$  is the on-state voltage of  $M_1$ . When  $v_{ce}$  is low-voltage,  $v_{gs}$  can be higher than the threshold voltage of  $M_1$ , which conducts  $M_1$ . Then,  $v_{out}$  is expressed as:

$$v_{\rm out} = v_{\rm ce} \frac{R_1}{R_1 + R_{\rm ds,on}} \tag{15}$$

$R_{ds,on}$  is the on-state resistance of  $M_1$ . Therefore, if  $R_1$  is far larger than  $R_{ds,on}$ ,  $v_{ce}$  can be measured accurately. However, if  $v_{ce}$  is high-voltage,  $v_{gs}$  can be lower than the threshold voltage of  $M_1$ , which makes  $M_1$  works at liner mode and withstands high-voltage.

In Fig.15(b), a depletion MOSFET is used and it works like this: if there is no current,  $M_1$  is in on-state. While, the current going through  $M_1$  and  $R_1$  can forms a negative voltage between the gate and source of  $M_1$ , which makes  $M_1$  operates at liner mode and exhibits high impedance. Based on this, if  $v_{ce}$  is lower than the reference voltage  $V_s$ , there is no current going through  $M_1$ , thus,  $v_{out}$  is:

$$v_{\rm out} = v_{\rm ce} \tag{16}$$

if  $v_{ce}$  is higher than  $V_s$ ,  $v_{out}$  is:

$$v_{\rm out} = V_{\rm s} + V_{\rm D1} \tag{17}$$

where  $V_{D1}$  is the forward voltage of  $D_1$ .

Tab 2 summarizes the ten typical component-level on-state voltage monitoring circuits in literature. They are discussed and analyzed in terms of circuit design, operation principle, and applicability to different applications. They are classified into five groups based on the key components to block the high-voltage and pass the low-voltage: relay, zener diode, the MOSFET with complex additional driver, general diode, and the MOSFET with simple self-driver. All of these circuits have different pros and cons in terms of response time, accuracy, and practical application.

Although the on-state voltage monitoring circuits have been developed for decades, they are still not mature enough to be implemented in practical applications. The main challenges are that all of those existing on-state voltage monitoring circuits are component-level solutions and active measurement with the requirement of external power supply, which can induce more practical issues when a power converter needs to be monitored. For example, applying those circuits in a three-phase converter: 1) It has high circuit complexity and cost to monitor six power switches; 2) It is connected to the power terminals of individual switching devices, which requires more connecting terminals; and 3) it has one reference ground for each phase-leg, which introduces isolation issue while sampling data of all devices; 4) it requires the additional power supply for each phase-leg. Overall, a converter-level on-state voltage monitoring circuit is still missing at present.

|                   | -              | 0 1                              | on-state voltage monitoring circuits     |

|-------------------|----------------|----------------------------------|------------------------------------------|

| Circuits          | Response       | Accuracy                         | Implementation                           |

|                   | time           |                                  |                                          |

| Fig.12(a)         | at ms level    | depends on the                   | the volume of relay and its              |

| [104]             |                | equivalent resistance of         | controller can increase the size and     |

|                   |                | relay                            | complexity of this circuit; limited      |

|                   |                |                                  | applications due to response time        |

| Fig.12(b)         | at 100 µs      | depends on the leakage           | the volume and power of $R_1$ should     |

| [74]              | level          | current of zener diode           | be considered since it needs to          |

|                   |                | and $R_1$                        | withstand high-voltage; limited          |

|                   |                | -                                | applications due to response time        |

| Fig.13(a)         | (1-10) µs      | accuracy is high since           | additional driver for $M_1$ is needed;   |

| [105]             | (              | $R_1$ can be far larger          | , i i i i i i i i i i i i i i i i i i i  |

| [100]             |                | than $R_{ds,on}$ in (6)          |                                          |

| Fig.13(b)         | (1-10) µs      | depends on the on-state          | $R_1$ and $R_2$ need to withstand        |

| [81]              | (1 10) 110     | voltages of $M_1$ and $M_2$      | high-voltage; complex circuit with       |

| [*-]              |                |                                  | internal driver for $M_1$ and $M_2$ and  |

|                   |                |                                  | external power supply; the gate          |

|                   |                |                                  | driver of DUT may be impacted            |

| Fig.13(c)         | (1-10) µs      | depends on the                   | $R_1$ - $R_4$ need to withstand          |

| [61]              | (1 10) µ3      | characteristics of $R_1$ - $R_5$ | high-voltage; complex circuit with       |

| [01]              |                | characteristics of K1-K5         | $v_{ce}$ divider, falling edge detector, |

|                   |                |                                  | and monostable multivibrator             |

| Fig 14(z)         | (1-10) µs      | depends on the voltage           | $R_1$ and $R_2$ need to withstand        |

| Fig.14(a)<br>[69] | (1-10) µs      |                                  | high-voltage; the sum of the             |

| [09]              |                | across $R_1$ and $R_2$           |                                          |

|                   |                |                                  | forward voltages of $D_1$ - $D_n$ should |

|                   |                |                                  | be higher than the maximum               |

| T: 44/1           | (1.10)         | 1 1 1                            | on-state voltage of DUT;                 |

| Fig.14(b)         | (1-10) µs      | depends on the                   | external power supply is needed;         |

| [69]              |                | forward voltages of $D_1$        | measurement error caused the             |

|                   |                | and $D_2$ and the                | forward voltage of diode is an issue     |

|                   |                | reference voltage Vs             |                                          |

| Fig.14(c)         | (1-10) $\mu s$ | depends on the                   | measurement error can be reduced         |

| [72]              |                | forward voltages of $D_1$        | significantly if $V_{D1}$ is same with   |

|                   |                | and $D_2$                        | $V_{D1}$ as much as possible; external   |

|                   |                |                                  | power supply is needed                   |

| Fig.15(a)         | (1-10) µs      | accuracy is high since           | external power supply is needed;         |

| [71]              |                | $R_1$ can be far larger          |                                          |

|                   |                | than $R_{ds,on}$ in (15)         |                                          |

| Fig.15(b)         | (1-10) µs      | high accuracy                    | external power supply is needed          |

| [76]              | · •            | - •                              |                                          |

|                   |                |                                  |                                          |

Table 2: Comparison of existing component-level on-state voltage monitoring circuits

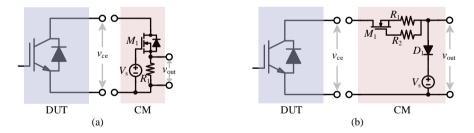

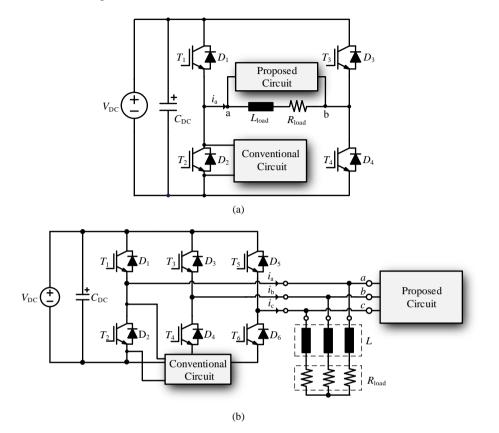

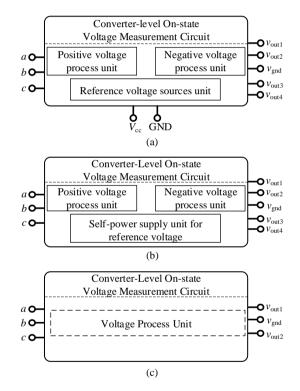

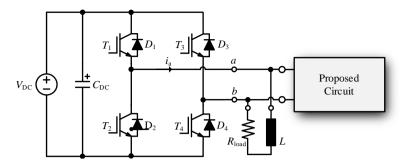

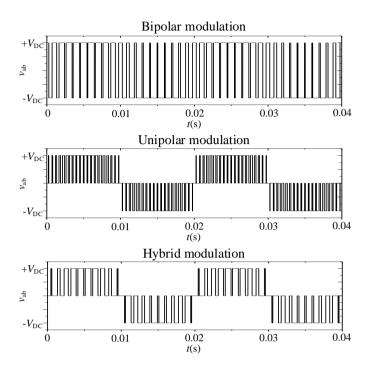

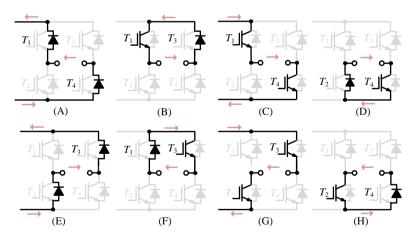

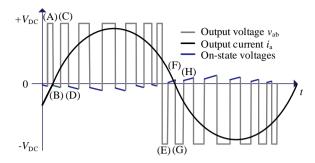

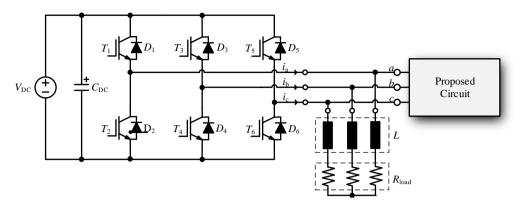

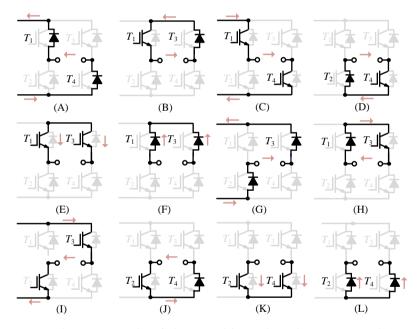

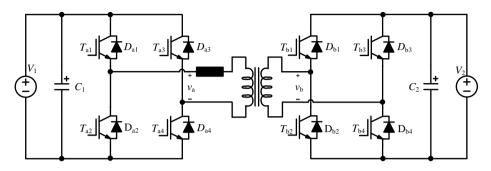

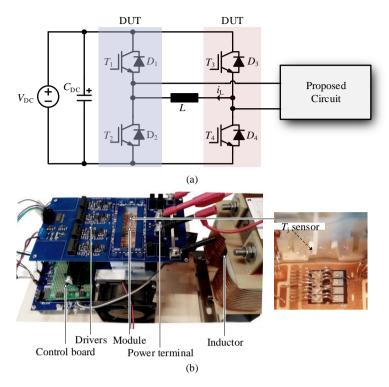

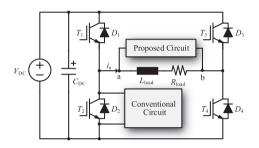

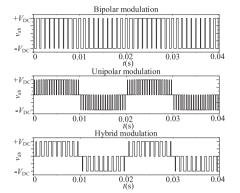

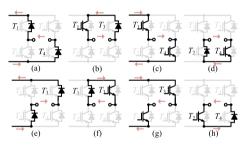

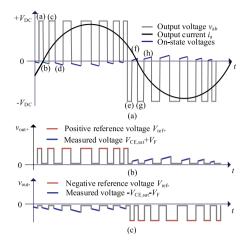

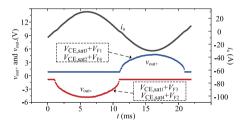

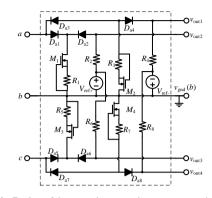

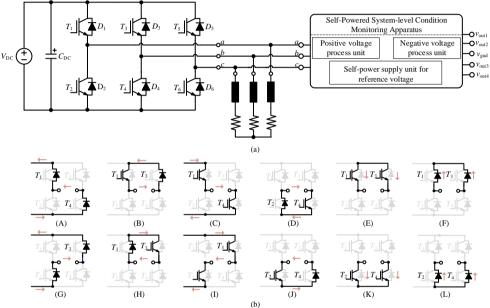

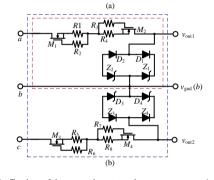

## 2.2 Proposed circuits for converter-level on-state voltage monitoring

In this thesis, three converter-level on-state voltage monitoring circuits are proposed and discussed in this Section, which achieves the unique feature by connecting to the output terminals of converters, instead of the two power terminals of individual power switch as the conventional methods do as shown in Fig.16. Due to the rich operation modes of converter, the voltages across the inverter output terminals is constructed by the on-stage voltages of all power switches and diodes, and the positive/negative DC-link voltages, which enables the converter-level measurement

of on-state voltage.

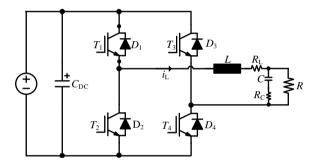

**Fig. 16**: Comparison of connection to power converter between conventional methods and proposed methods: (a) in single-phase inverter; (b) in three-phase inverter.

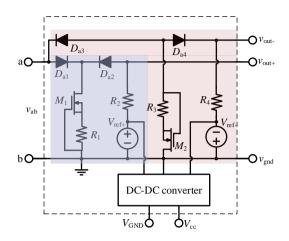

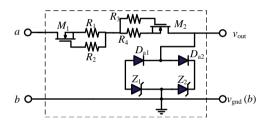

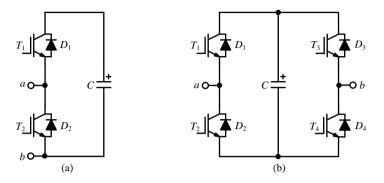

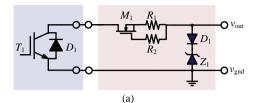

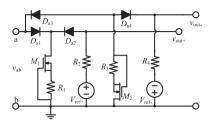

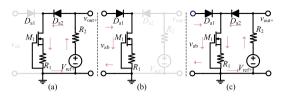

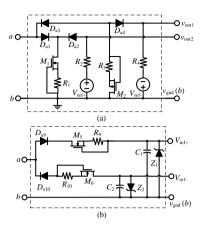

#### 2.2.1 Proposed measurement circuit with an external power supply

To block the DC-link voltage and obtain the low on-state voltage, a measurement circuit with an external power supply is proposed as shown in Fig.17, which is composed of two symmetric parts with the function of extracting the on-state voltages from the bipolar output voltage of single-phase inverter  $v_{ab}$ . The first part is marked with blue rectangle and is composed of one signal MOSFET  $M_1$ , two diodes  $D_{a1}$  and  $D_{a2}$ , two resistors  $R_1$  and  $R_2$ , and one positive reference voltage  $V_{ref+}$ . This part is used to prevent any negative voltage and positive voltage higher than  $V_{ref+}$  from reaching at the output terminal of this circuit, and to pass the positive voltage lower than  $V_{ref+}$  only. The second part is marked with red rectangle, including  $M_2$ ,  $D_{a3}$ ,  $D_{a4}$ ,  $R_3$ ,  $R_4$ , and  $V_{ref-}$ . It has opposite function with the first part, blocking any positive voltage higher than  $V_{ref-}$ . The bidirectional reference voltage is provided with an

external isolation DC-DC converter, which means this circuit is active.

**Fig. 17:** Proposed converter-level on-state voltage monitoring circuit with external power supply for single-phase converter application [J2].

Fig. 18: Operation modes of blue part in Fig.17 [J2].

Among those devices,  $M_1$  and  $M_2$  are N-channel depletion MOSFET and they works like this: when there is no current flowing through  $M_1$ , for example, the gatesource voltage is zero and  $M_1$  is in on-state; If there is current flowing through  $M_1$ , the gate-source voltage will be negative due to the positive voltage across  $R_1$ , which makes  $M_1$  operates at liner mode and exhibits high-impedance. To simplify the analysis process, only the operation modes of blue part in Fig.17 are given as shown in Fig.18. The operation modes of red part circuit can be derived similarly.

• Model a (Fig.18(a)): when  $v_{ab}$  is negative,  $D_{a1}$  is in reverse-blocked state and  $D_{a2}$  is in conducted state, the positive output  $v_{out+}$  is:

$$v_{\text{out}+} = \frac{R_1}{R_1 + R_2} \left( V_{\text{ref}+} - V_{\text{Da}2} - V_{\text{M}1} \right) + V_{\text{Da}2} + V_{\text{M}1}$$

(18)

$R_1$  has much smaller resistance than  $R_2$ , leading to a small  $v_{out+}$  (e.g., 1 V).  $V_{Da1}$  and  $V_{Da2}$  are the forward voltage of  $D_{a1}$  and  $D_{a2}$ , respectively.  $V_{M1}$  is the voltage across  $M_1$ .

- 2. Design of the converter-level on-state voltage monitoring circuits

- Model b (Fig.18(b)): when v<sub>ab</sub> is positively higher than V<sub>ref+</sub>, D<sub>a1</sub> is conducted and D<sub>a2</sub> is blocked. Then, v<sub>out+</sub> equals to the reference voltage V<sub>ref+</sub>.

$$v_{\rm out+} = V_{\rm ref+} \tag{19}$$

• Model c (Fig.18(c)): when  $v_{ab}$  is in the range of 0 and  $V_{ref+}$ ,  $D_{a1}$  and  $D_{a2}$  are conducted as shown in Fig.3(c). Thus,  $v_{out+}$  can be described as:

$$v_{out+} = v_{ab} - V_{Da1} + V_{Da2}$$

(20)

In practice,  $V_{Da1}$  and  $V_{Da2}$  can cancel each other out substantially if  $D_{a1}$  and  $D_{a2}$  are selected with same characteristics as much as possible and are mounted together. Thus, it is reasonable to assume that  $v_{out+}$  is equal to  $v_{ab}$ . Overall, with the blue and red parts in Fig.17 together, any input voltages out of the range between  $V_{ref-}$  and  $V_{ref+}$  are clipped to the preset reference voltages, while the input voltage within that range can be measured directly. The functions of the proposed circuit are summarized in Table 3.

Table 3: Overall functions of the proposed circuit.

| Modes | $v_{ab}$                     | $v_{out+}$     | v <sub>out-</sub> |

|-------|------------------------------|----------------|-------------------|

| Ι     | $[V_{\text{ref}+}, +\infty]$ | $V_{\rm ref+}$ | -1 V              |

| II    | $[0, V_{ref+}]$              | $v_{ab}$       | -1 V              |

| III   | $[V_{\rm ref-}, 0]$          | +1 V           | $v_{ab}$          |

| IV    | $[-\infty, V_{\text{ref}-}]$ | +1 V           | $V_{\rm ref-}$    |

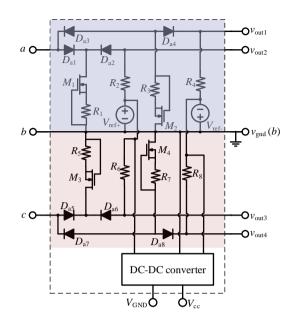

To apply the proposed converter-level on-state voltage monitoring circuit to threephase converters, the circuit presented in Fig.17 is partially replicated as shown in Fig.19. The sub-circuits marked with blue and red can share one external power supply due to the common reference ground b.

Fig. 19: Proposed converter-level on-state voltage monitoring circuit with external power supply for three-phase converter application [J3].

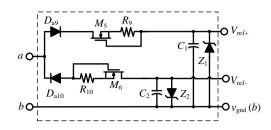

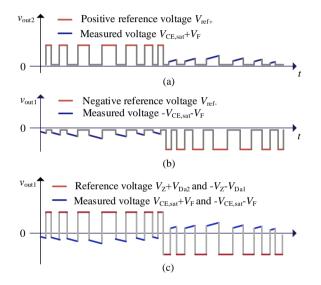

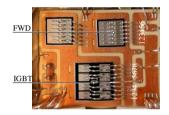

#### 2.2.2 Proposed measurement circuit with self-power supply

The external power supply is existed in both the conventional methods and the proposed circuits presented in Fig.19. It usually accounts for the total cost and size of the measurement circuit for at least 90% and 30%, respectively. Moreover, two additional connecting terminals are needed for this power supply. Therefore, from the view of practical application, it would be much better if the external power supply can be removed. To address this problem, a self-power supply capable of extracting a stable bidirectional reference voltages from the input voltage is designed in this thesis, as shown in Fig.20.

$D_{a9}$  and  $D_{a10}$  are normal diode,  $Z_1$  and  $Z_2$  are Zener diode and their Zener voltage is  $V_z$ ,  $M_5$  and  $M_6$  are signal N-channel depletion MOSFET. Based on this, when the input voltage of the self-power supply is positive,  $D_{a9}$  is conducted and  $D_{a10}$  is blocked.  $C_1$  is charged until its voltage reaches at  $V_z$ . When the input voltage is negative,  $D_{a9}$  is blocked and  $D_{a10}$  is conducted.  $C_2$  start to charge until its voltage reaches at  $-V_z$ . According to this, the bidirectional reference voltages can be obtained by using the proposed self-power circuit and is the Zener voltage  $\pm V_z$ . Moreover, the proposed on-state voltage measurement circuit and self-power circuit can share a same ground, which means the isolation is unnecessary. Thus, the external power supply used in conventional methods and Fig.19 can be replaced with the proposed self-power supply.

Fig. 20: Proposed self-power supply circuit [J3].

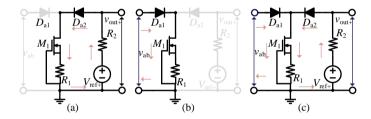

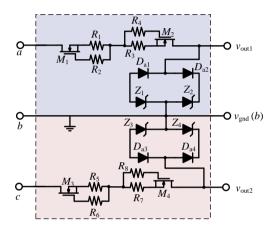

#### 2.2.3 Proposed measurement circuit without power supply

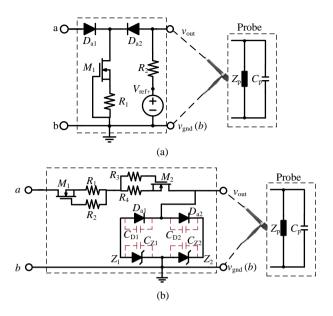

The proposed converter-level measurement circuit with external or self-power supply outperforms conventional component-level methods in many ways. However, the circuit is still a little bit complex. To address this problem, a much simplified measurement circuit is proposed in this thesis as shown in Fig.21, which is able to achieve converter-level monitoring without external or internal (self-power) power supply.

Fig. 21: Proposed converter-level on-state voltage monitoring circuit without power supply for single-phase converter application [J5].

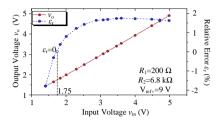

The circuit in Fig.21 enables sampling the change of on-state voltage at mV precision. It consists of few common signal devices without power supply, making it possible to be designed as a compact circuit or a even chip.  $M_1$  and  $M_2$  are signal depletion MOSFET, exhibiting different impedance by controlling the source resistor ( $R_1$  or  $R_4$ ) and the gate resistor ( $R_2$  or  $R_3$ ).  $Z_1$  and  $Z_2$  are common Zener diodes, and its Zener voltage  $V_Z$  should be higher than the maximum value of the input signal to be measured.

If the input voltage  $v_{ab}$  is higher than  $V_Z$ , a negative voltage drop across  $R_2$  makes  $M_1$  exhibits high impedance, so that only a very low current (few mA) is allowed to flow. While the anti-parallel body diode of  $M_2$  and  $D_{a2}$  are conducted, and thereby the voltage across  $Z_2$  is clamped at  $V_Z$ . Accordingly,  $v_{out}$  can be expressed as:

$$v_{\rm out} = V_{\rm Z} + V_{\rm Da2} \tag{21}$$

where  $V_{\text{Da2}}$  is the forward voltage of  $D_{a2}$ .

When  $v_{ab}$  is lower than  $-V_Z$ , similarly, the anti-parallel body diode of  $M_1$  and  $D_{a1}$  are conducted.  $M_2$  exhibits high impedance and  $v_{out}$  can be expressed as:

$$v_{\rm out} = -V_Z - V_{\rm Da1} \tag{22}$$

where  $V_{\text{Da1}}$  is the forward voltage of  $D_{a1}$ .

When  $v_{ab}$  is within the range between  $-V_Z$  and  $V_Z$ , diode  $D_{a1}$ ,  $D_{a2}$ ,  $Z_1$  and  $Z_2$  are all blocked and the voltages across  $R_1$  and  $R_4$  are zero, which means  $M_1$  and  $M_2$  are in on-state. Therefore,  $v_{out}$  equals to  $v_{ab}$  at this situation as shown below:

$$v_{\rm out} = v_{\rm ab} \tag{23}$$

In conclusion, the function of the proposed circuit is to block the voltage higher than  $V_Z$  and lower than  $-V_Z$ , while pass the voltage within  $-V_Z$  and  $V_Z$  without error.

To apply the proposed converter-level on-state voltage monitoring circuit to threephase converters, the circuit presented in Fig.21 is replicated as shown in Fig.22.

Fig. 22: Proposed converter-level on-state voltage monitoring circuit for three-phase converter application [J5].

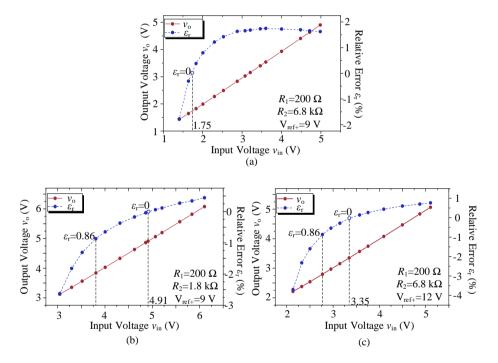

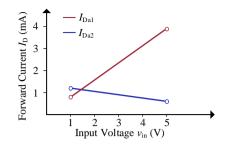

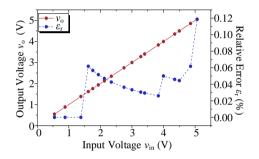

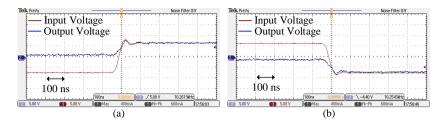

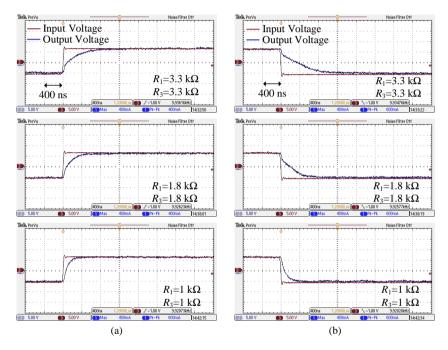

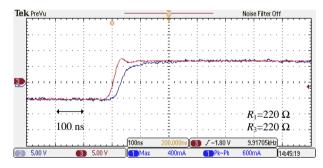

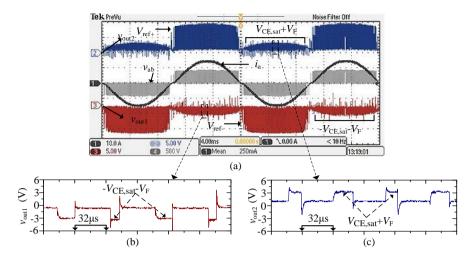

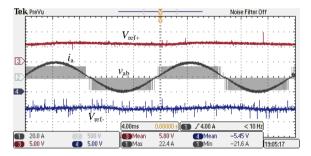

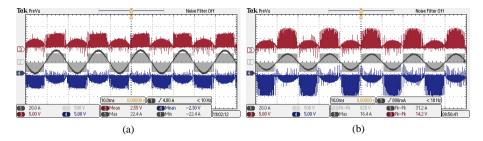

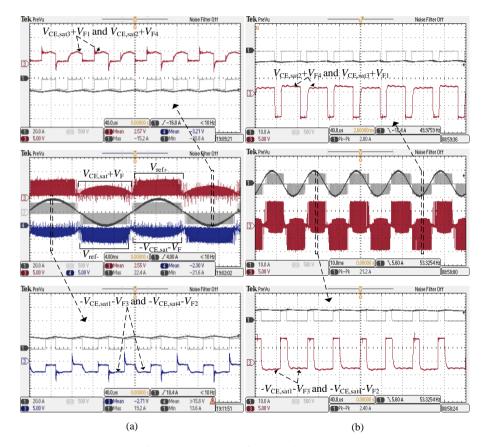

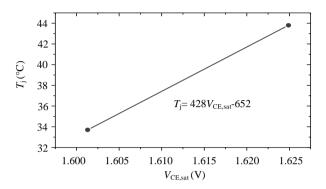

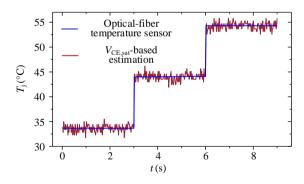

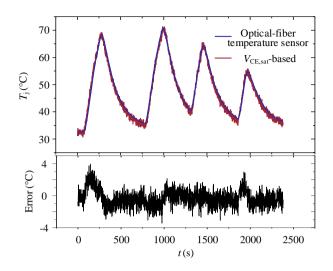

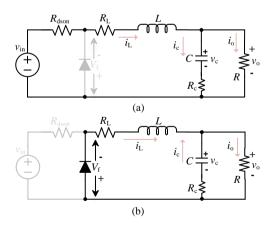

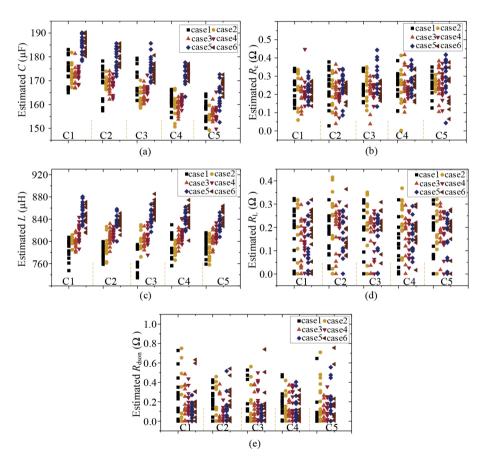

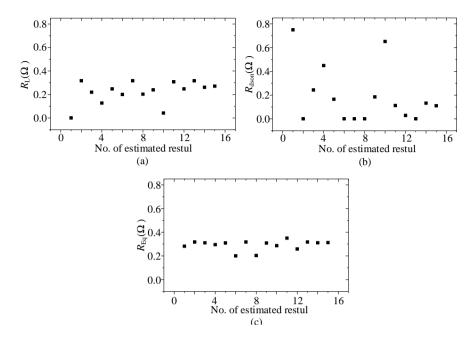

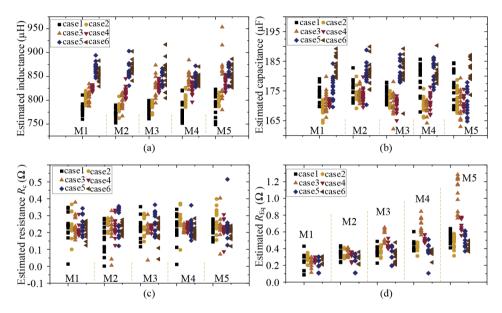

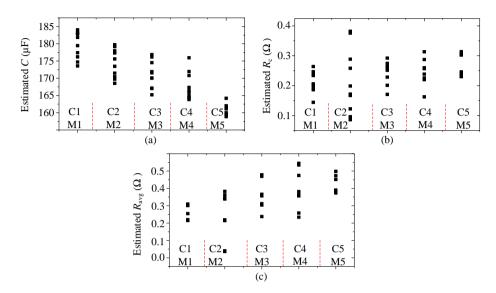

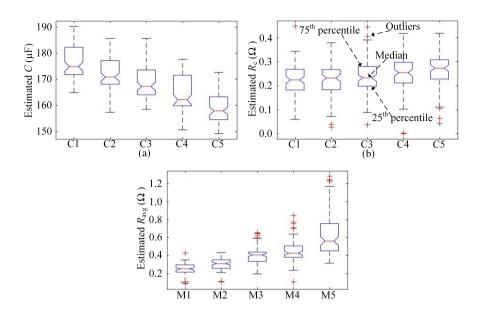

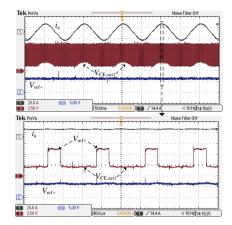

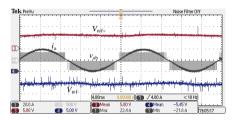

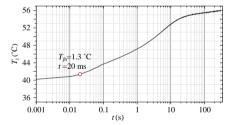

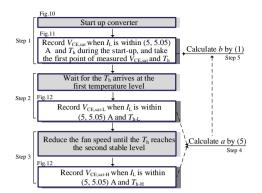

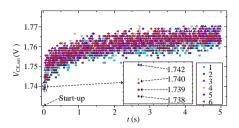

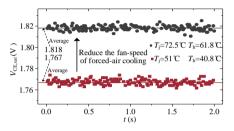

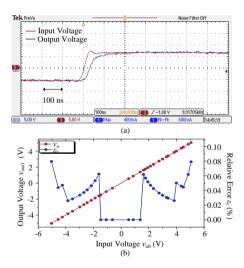

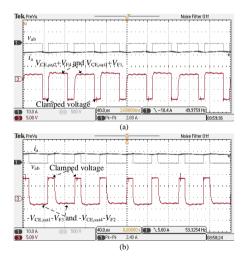

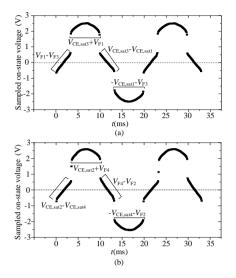

## 2.3 Selection of components