#### **Aalborg Universitet**

| Mitigation Strategy                                               |

|-------------------------------------------------------------------|

| Du, He                                                            |

|                                                                   |

|                                                                   |

|                                                                   |

| Publication date:<br>020                                          |

| Pocument Version Publisher's PDF, also known as Version of record |

Link to publication from Aalborg University

Citation for published version (APA): Du, H. (2020). Impact of Short-Circuit Events on the Remaining Useful Life of SiC MOSFETs and Mitigation Strategy. Aalborg Universitetsforlag.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

### IMPACT OF SHORT-CIRCUIT EVENTS ON THE REMAINING USEFUL LIFE OF SIC MOSFETS AND MITIGATION STRATEGY

BY HE DU

**DISSERTATION SUBMITTED 2020**

# Impact of Short-Circuit Events on the Remaining Useful Life of SiC MOSFETs and Mitigation Strategy

By

He Du

A Dissertation Submitted to the Faculty of Engineering and Science at Aalborg University in Partial Fulfilment for the Degree of Doctor of Philosophy in Electrical Engineering

November 2020 Aalborg, Denmark Dissertation submitted: November 2020

PhD supervisor: Prof. Francesco Iannuzzo

Aalborg University, Denmark

Assistant PhD supervisor: Dr. Paula Diaz Reigosa

University of Applied Sciences Northwestern

Switzerland (FHNW), Switzerland

PhD committee: Associate Professor Pooya Davari (chairman)

Aalborg University

Associate Professor Marina Antoniou

The University of Warwick

Head of Research Stefan Mollov

Mitsubishi Electric R&D Centre Europe

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: Department of Energy Technology

ISSN (online): 2446-1636

ISBN (online): 978-87-7210-841-4

Published by:

Aalborg University Press

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk

forlag.aau.dk

© Copyright: He Du

Printed in Denmark by Rosendahls, 2021

"Real generosity toward the future lies in giving all to the present." Albert Camus

### **Preface**

This Ph.D. thesis is a summary of the Ph.D. project "Impact of Short-Circuit Events on the Remaining Useful Life of SiC MOSFETs and Mitigation Strategy" conducted in Center of Reliable Power Electronics (CORPE), Department of Energy Technology, Aalborg University, Denmark.

First of all, I would like to express my deepest gratitude to my supervisor, Prof. Francesco Iannuzzo, who provided me with the opportunity to start this academic journey and offered plenty of helpful guidance and relentless encouragement throughout the Ph.D. period. I greatly appreciate his kindness, patience, and open-mindedness. His broad knowledge in the field of power semiconductor devices was an important source of inspiration. I would also like to thank my co-supervisor, Dr. Paula Díaz Reigosa for her enthusiastic support and insightful advice all the times. It was a great experience to work under her supervision.

My appreciation goes to all my colleagues at the Department of Energy Technology, Aalborg University, especially to Dr. Lorenzo Ceccarelli, Dr. Nick Baker, Mr. Yingzhou Peng, and Mr. Keting Hu for their kind help and fruitful discussions. I am also thankful to all the involved staffs at Aalborg University for a friendly environment as well as administrative and technical support.

I would like to extend special thanks to Mr. Andreas Schletz for inviting me for a six-month research visit at Fraunhofer IISB in Germany and his kindness during my stay. With this occasion, I would also like to thank all my colleagues at Fraunhofer IISB, especially to Dr. Sebastian Letz, Mr. Jonas Buettner, and Mr. Thomas Goetz, who helped me with the failure analysis and device simulation of SiC MOSFETs.

I would like to express my gratitude to the assessment committee for this doctoral defence: Assoc. Prof. Pooya Davari from Aalborg University, Assoc. Prof. Marina Antoniou from University of Warwick, and Dr. Stefan Mollov from Mitsubishi Electric R&D Centre Europe.

Finally, yet importantly, I am thankful to my friends, who I met in Aalborg, especially Mr. Mathias Fredslund and Mr. Akihiro Hino, as well as my best friends from my hometown for their help and support. I would like to thank, from the deepest of my heart, my family for their unconditional love, support and understanding all the times. They always have been my rock-solid foundation, who encourage me to find my own path in life and make me who I am today.

He Du

October 31, 2020 Aalborg, Denmark

#### **Abstract**

Power semiconductor devices are critical components in power electronic systems. Thanks to the unprecedented performance compared with silicon-based devices, silicon carbide (SiC) devices are desirable for high-efficiency and high-power-density power converters. However, the proliferating demand for SiC MOSFETs raises concerns for long-term reliability and short circuit is one of the critical aspects as the devices withstand both high voltage and high current at the same time.

With the development of faster fault detection and short-circuit protection, the risk of catastrophic failure can be reduced, which allows the device to withstand many non-destructive short-circuit events during its life. Typically, the remaining useful life (RUL) of the devices can be estimated based on the condition monitoring parameters, i.e. the ageing indicators and it only considers the wear-out failures under normal operating conditions. Therefore, this Ph.D. thesis aims at investigating the impact of short-circuit events on the RUL of SiC MOSFETs.

The thesis starts with an analysis of the degradation indicators under short-circuit conditions to identify the one which can best reflect the short-circuit degradation process and two test approaches were performed. Then, static and dynamic characteristics measurements were performed during repetitive short-circuit tests, respectively and the purpose is to investigate the impact of short-circuit degradation on the normal operating performance of SiC MOSFETs. As the case temperature is subjected to real application conditions, its influence is also considered by performing the repetitive short-circuit tests at different case temperatures.

Thereafter, power cycling tests were used to evaluate the wear-out ageing and lifetime of the devices. Mixed power-cycling/short-circuit tests were performed to assess the impact of short-circuit degradation on the power-cycling conditions, and further on, the RUL by applying different short-circuit stress. To deeply analyse the degradation mechanisms, failure analysis tools (lock-in thermography, focused ion beam, and scanning electron microscope) were used on both failed and functional device. Besides, a transient thermo-mechanical simulation based on finite-element-analysis software was achieved to verify the degradation mechanisms. Finally, a mitigation strategy comprising a top-side thermal mass is studied.

The main contribution of this thesis is the strong implication of short-circuit events on the RUL of SiC MOSFETs. With a larger number of events, the higher gate leakage current results in higher junction temperature swing and less number of cycles to failure. The root cause of gate leakage current is the mismatch of coefficient of thermal expansion between Al and SiO<sub>2</sub>, which forms the SiO<sub>2</sub> interlayer crack, and the molten Al flowing through the crack, which builds a conductive path between gate- and source terminals. Moreover, sintered Cu foil on the top side could be an effective approach to mitigate this short-circuit degradation.

### Dansk Résumé

Effektelektronikke enheder er vigtige komponenter i kraftelektroniske systemer. På grund af den hidtil usete ydeevne sammenlignet med silicium-baserede enheder er siliciumcarbid (SiC) enheder højt ønsket til mere effektive og effekttæthed omformere. Imidlertid rejser den voksende demand efter SiC MOSFET bekymringer over langsigtet pålidelighed, og kortslutning er et af de kritiske aspekter, da enhederne samtidigt modstår både høj spænding og strøm.

Med udviklingen af hurtigere fejldetektion og kortslutningsbeskyttelse, kan risikoen for katastrofale fejl reduceres, hvilket gør det muligt for enheden at modstå mange ikke-destruktive kortslutningshændelser i sin levetid. Typisk kan den resterende livstid (remaining useful life, RUL) estimeres baseret på condition monitoring parametre, dvs. aldringsindikatorer, men denne inkluderer kun slitage under almindelig driftsforhold.

Denne ph.d. afhandling er målrettet mod at undersøge påvirkningen af kortslutningshændelser på RUL af SiC MOSFETs. Afhandlingen starter med en analyse af nedbrydnings indikatorer under kortslutnings forhold for at kunne identificere hvilke ene ud af alle, der bedst kan monitorere kortslutnings-nedbrydningsprocessen. Her er to test fremgangsmåder udført. Derefter blev der målinger udført af statiske og dynamiske egenskaber under gentagende kortslutningstest målrettet at undersøge påvirkningen af kortslutnings nedbrydnings processen på SiC MOSFETs normale driftsydeevne. Da skal udsættes for reelle applikationsbetingelser, er indflydelsen af temperaturen også overvejet ved at udføre gentagende kortslutnings tests ved forskellige temperature af enhedscase.

Derefter blev der udført power cycling tests, for at vurdere slitage og enhedernes resterende livtid. Blandet power-cycling- og kortslutningstests var udført også, for at anslå indvirkningen af kortslutningsnedbrydning på power cycling, og relateret RUL ved at give forskellige kortslutnings stress. For ordentligt at kunne analysere nedbrydnings mekanismer, er fejlanalyse værktøjer (lock-in-termografi, fokuseret ionstråle og scanning-elektronmikroskop) brugt på både nedbrudte- og virkende enheder. Derudover, blev der udført en forbigående termo-mekanisk simulation med finite-element software, for at validere nedbrydningsmekanismerne. Endeligt, er en afbødende strategi foreslået, der omfatter en termisk masse på chip toppen.

Hovedbidraget for denne afhandling er studien af de implikationer af kortslutningshændelser på RUL af SiC MOSFETs. Med stigende antal hændelser, vil den større og større lækstrøm fra gaten resultere i større og større temperatursvingninger og mindre og mindre antal cykler til fejl. Årsagen for gate lækstrøm er mismatchet af koefficienterne for termisk ekspansion mellem Al og SiO2. Dette former mellemlags revner i SiO2, hvor aluminum kan smeltes og flyde gennem revnerne og opbygge en ledende sti mellem gate- og source terminaler. Til sidst, der foreslås at en sinteret Cu-folie på chip toppen kan være en effektiv tilgang til at afbøde kortslutningsnedbrydning.

## **Contents**

| Preface                                                       | iv   |

|---------------------------------------------------------------|------|

| Abstract                                                      | v    |

| Dansk Résumé                                                  | vi   |

| Contents                                                      | vii  |

| List of Figures                                               | ix   |

| List of Tables                                                | xiii |

| 1 Introduction                                                | 1    |

| 1.1 Background                                                | 1    |

| 1.1.1 Silicon Carbide: From Material to Devices               | 2    |

| 1.1.2 Reliability Challenges: Normal and Abnormal Conditions  | 7    |

| 1.2 Research Motivation                                       | 12   |

| 1.3 Scientific Questions                                      | 12   |

| 1.4 Thesis Objectives                                         | 13   |

| 1.5 Limitations                                               | 13   |

| 1.6 Thesis Outline                                            | 14   |

| 1.7 List of Publications                                      | 14   |

| 2 Degradation Indicators under Short-Circuit Conditions       | 17   |

| 2.1 Short-Circuit Performance and Failure Modes               | 17   |

| 2.2 Short-Circuit Test Bench                                  | 20   |

| 2.3 Short-Circuit Degradation Indicators                      | 22   |

| 2.4 Summary                                                   | 27   |

| 3 Impact of Short-Circuit Degradation on the Normal Operation | 29   |

| 3.1 Selected Conditions for Repetitive Short-Circuit Tests    | 29   |

| 3.2 Impact on the Static and Dynamic Characteristics          | 31   |

| 3.3 Case Temperature Influence Consideration                  | 37   |

| 3.4 Summary                                                   | 41   |

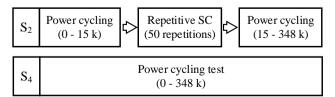

| 4 | Impact of Short-Circuit Degradation on the Remaining Useful Life | 43 |

|---|------------------------------------------------------------------|----|

|   | 4.1 Introduction of Power Cycling Test                           | 43 |

|   | 4.2 Mixed Power-Cycling/Repetitive Short-Circuit Test            | 47 |

|   | 4.3 Impact of Short Circuit on the RUL                           | 53 |

|   | 4.4 Summary                                                      | 58 |

| 5 | Short-Circuit Degradation Analysis and Mitigation Strategy       | 59 |

|   | 5.1 Failure Analysis                                             | 59 |

|   | 5.2 Thermo-Mechanical Simulation of Short-Circuit Condition      | 63 |

|   | 5.3 Mitigation Strategy: Top-Side Thermal Mass                   | 67 |

|   | 5.4 Summary                                                      | 72 |

| 6 | Conclusions and Future Work                                      | 73 |

|   | 6.1 Summary                                                      | 73 |

|   | 6.2 Research Highlights                                          | 74 |

|   | 6.3 Proposals for Future Work                                    | 75 |

| R | eferences                                                        | 77 |

# List of Figures

| Fig. 1.1. Stability diagram of SiC polytypes                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2. SiC devices' development milestones                                                                                                                                       |

| $Fig.\ 1.3.\ Typical\ SiC\ MOSFET\ cell\ structures:\ (a)\ planar\ type;\ (b)\ trench\ type.\ \dots\dots\dots 5$                                                                    |

| Fig. 1.4. Conventional SiC MOSFET package structures: (a) discrete device with TO-247-3 package; (b) power module                                                                   |

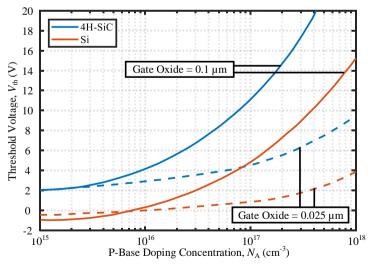

| Fig. 1.5. Threshold voltage of SiC MOSFET compared to Si MOSFET (including the impact of N+ polysilicon gate and an oxide fixed charge of $2\times10^{11}$ cm <sup>-2</sup> )8      |

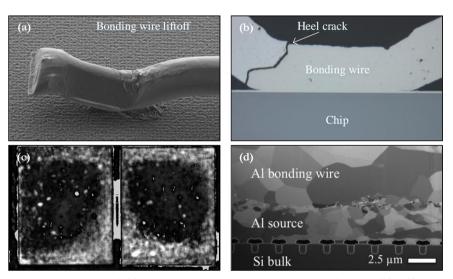

| Fig. 1.6. Package-level failure modes in power module: (a) bonding wire lift-off; (b) bonding wire fracture; (c) chip solder edge delamination; (d) Al metallization reconstruction |

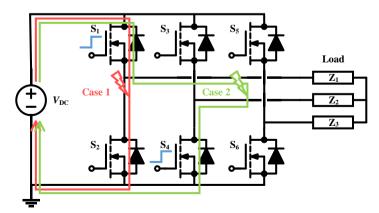

| Fig. 1.7. Short-circuit cases in a three-phase voltage source converter11                                                                                                           |

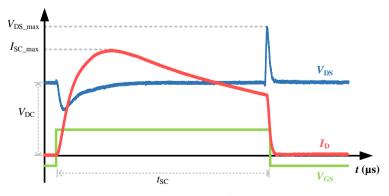

| Fig. 2.1. Typical short-circuit (type I) behaviour in SiC MOSFETs17                                                                                                                 |

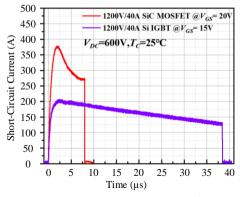

| Fig. 2.2. Short-circuit current comparison of the 1.2 kV/40 A SiC MOSFET and Si IGBT ( $V_{\rm DC}$ = 600 V, $T_{\rm C}$ = 25 °C)                                                   |

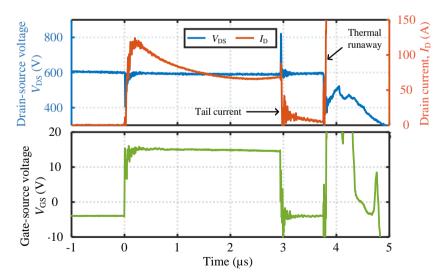

| Fig. 2.3. Short-circuit waveforms of a 1000 V/22 A SiC MOSFET exhibiting thermal runaway failure mode                                                                               |

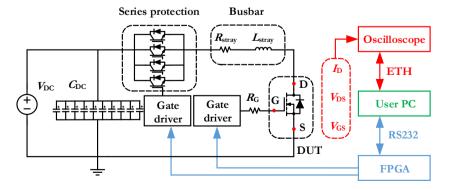

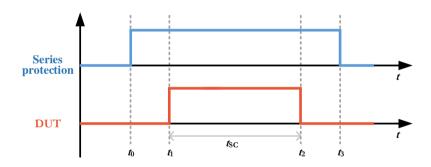

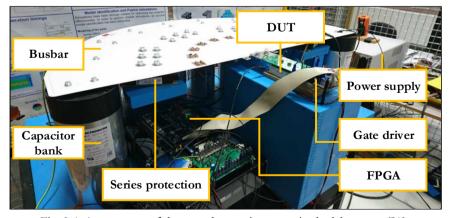

| Fig. 2.4. Schematic of the non-destructive tester                                                                                                                                   |

| Fig. 2.5. Control signals for the gate drivers of series protection and DUT21                                                                                                       |

| Fig. 2.6. Appearance of the non-destructive tester in the laboratory21                                                                                                              |

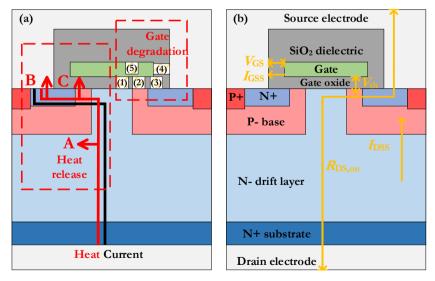

| Fig. 2.7. (a) Degradation mechanisms and (b) degradation indicators under short-circuit conditions (different gate damages marked as type (1) - (5))22                              |

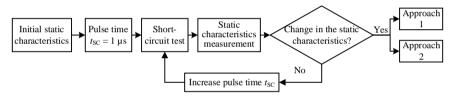

| Fig. 2.8. Flowchart of two short-circuit test approaches for the degradation indicators.                                                                                            |

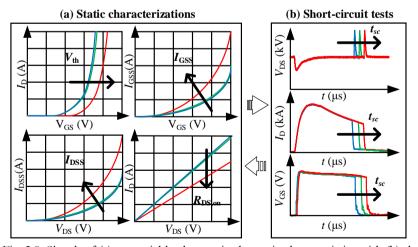

| Fig. 2.9. Sketch of (a) appreciable changes in the static characteristics with (b) the short-circuit pulse time increase                                                            |

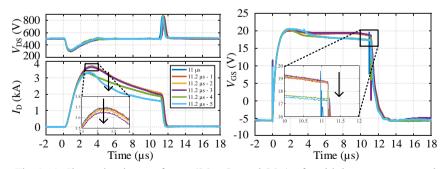

| Fig. 2.10. Short-circuit waveforms ( $V_{DS}$ , $I_{D}$ , and $V_{GS}$ ) of multiple tests at $t_{SC}$ equal to 11.2 $\mu s$ (approach 1)                                           |

| Fig. 2.11. Gate current waveforms of multiple 11.2 $\mu s$ short-circuit tests (1st - 5th repetition)                                                                               |

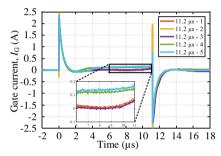

| Fig. 2.12. Static characteristics variation after repetitive short-circuit tests at $t_{SC}=11.2~\mu s$ : (a) $V_{th}$ , (b) $I_{GSS}$ , (c) $I_{DSS}$ , and (d) $R_{DS,on}$        |

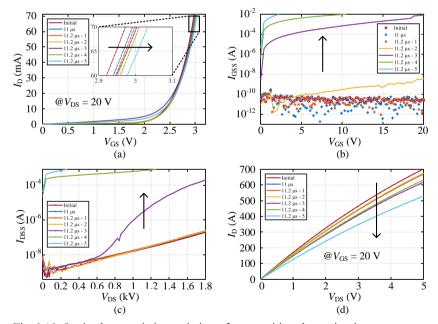

| Fig. 2.13. Short-circuit tests with the pulse time increase: (a) $V_{DS}$ , $I_{D}$ , and (b) $V_{GS}$ (approach 2)                                                                 |

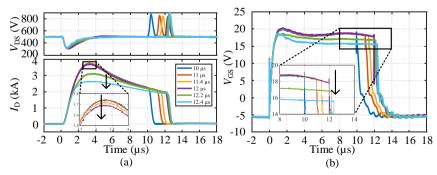

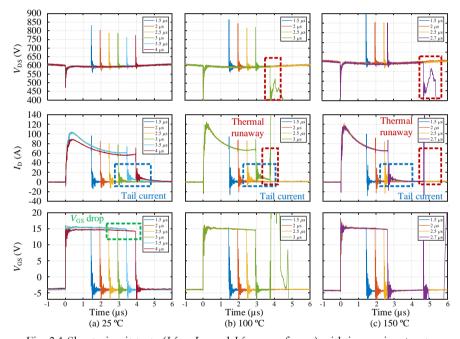

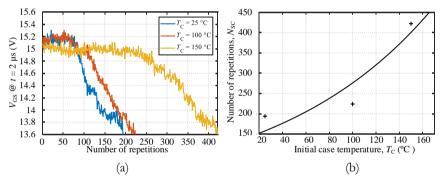

| Fig. 3.1 Short-circuit tests ( $V_{DS}$ , $I_{D}$ , and $V_{GS}$ waveforms) with increasing $t_{SC}$ at different initial case temperature (a) 25 °C, (b) 100 °C, and (c) 150 °C                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

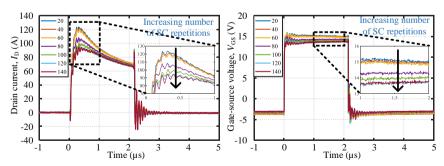

| Fig. 3.2. Drain-source voltage ( $V_{\rm DS}$ ) and drain current ( $I_{\rm D}$ ) waveforms during repetitive short-circuit tests ( $20^{\rm th}$ - $140^{\rm th}$ repetition at 25 °C)                                            |

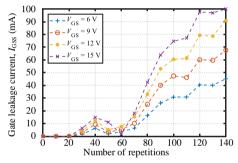

| Fig. 3.3. Gate leakage current (from static characteristics measurement) versus the number of short-circuit repetitions                                                                                                            |

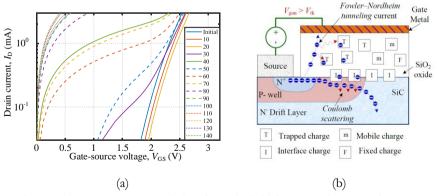

| Fig. 3.4. (a) $I_D$ - $V_{GS}$ curves variation from the initial state to the state after 140 short-circuit repetitions; (b) Multiple types of charges in the gate oxide layer and the schematic of Fowler-Nordheim tunnelling     |

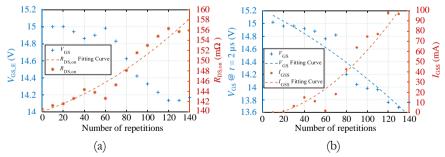

| Fig. 3.5. (a) Increased $R_{\rm DS,on}$ with the number of short-circuit repetitions; (b) correlation between the $V_{\rm GS}$ at $t=2~\mu s$ during short-circuit tests and the $I_{\rm GSS}$ measured with power device analyser |

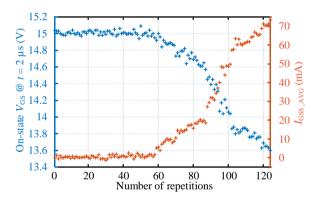

| Fig. 3.6. Correlation between the $V_{\rm GS}$ at $t=2~\mu \rm s$ and the $I_{\rm GSS\_AVG}$ during repetitive short-circuit tests                                                                                                 |

| Fig. 3.7. Schematic of double pulse test                                                                                                                                                                                           |

| Fig. 3.8. Experimental waveforms of double pulse test ( $V_{DS}$ , $I_{D}$ , and $V_{GS}$ )                                                                                                                                        |

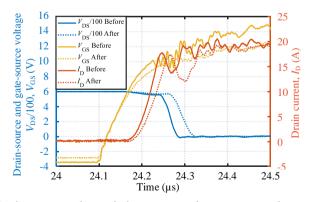

| Fig. 3.9. Drain-source voltage, drain current and gate-source voltage waveforms during turn-on transient before and after 110 repetitions                                                                                          |

| Fig. 3.10. Drain-source voltage, drain current and gate-source voltage waveforms during turn-off transient before and after 110 repetitions                                                                                        |

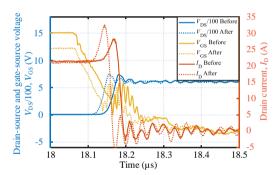

| Fig. 3.11. Variation of switching loss and gate-source voltage reduction with the number of repetitions                                                                                                                            |

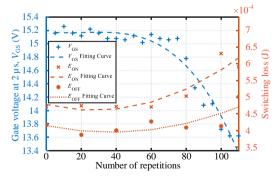

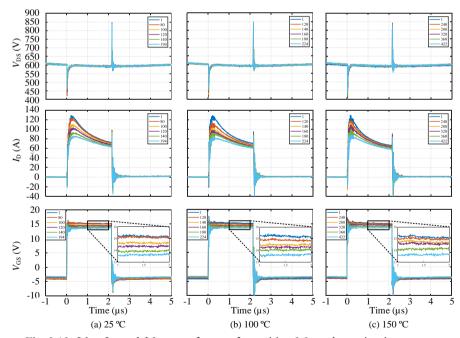

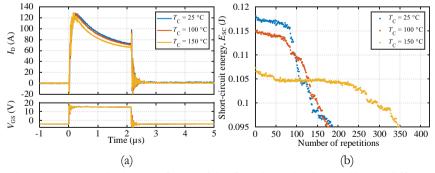

| Fig. 3.12. $V_{DS}$ , $I_{D}$ , and $V_{GS}$ waveforms of repetitive 2.2 $\mu$ s short-circuit tests at different initial case temperatures: (a) 25 °C, (b) 100 °C, and (c) 150 °C                                                 |

| Fig. 3.13. (a) $V_{\rm GS}$ reduction with the number of repetitions at $T_{\rm C}$ = 25 °C, 100 °C, and 150 °C; (b) the relationship between the number of repetitions and $T_{\rm C}$                                            |

| Fig. 3.14. (a) $I_D$ and $V_{GS}$ waveforms of the first short-circuit repetition at different $T_C$ ; (b) short-circuit energy reduction with the number of short-circuit repetitions at different $T_C$                          |

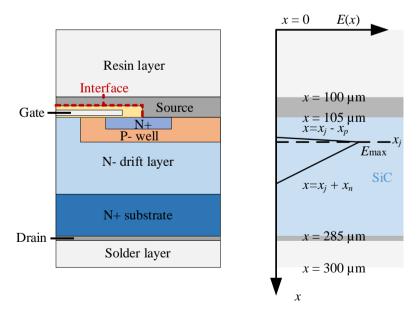

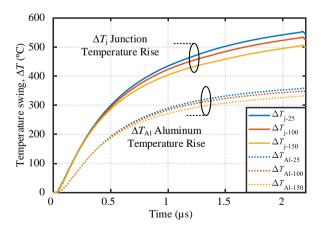

| Fig. 3.15. 1-D heat propagation thermal model of the SiC MOSFET39                                                                                                                                                                  |

| Fig. 3.16. Junction temperature and aluminium temperature rise at initial $T_{\rm C}$ = 25 °C, 100 °C, and 150 °C                                                                                                                  |

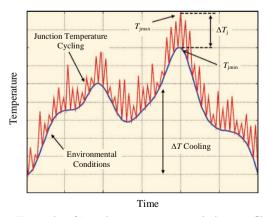

| Fig. 4.1. Example of junction temperature mission profile                                                                                                                                                                          |

| Fig. 4.2. Typical junction temperature evolution of the power-cycling test44                                                                                                                                                       |

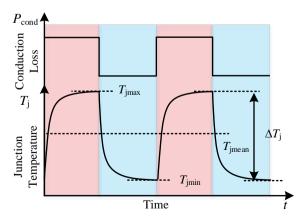

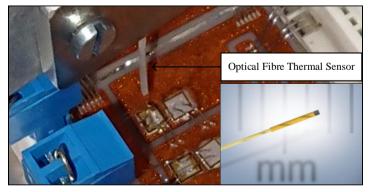

| Fig. 4.3. DC-based power-cycling test with the optical fibre $T_j$ measurement45                                                                                                                                                   |

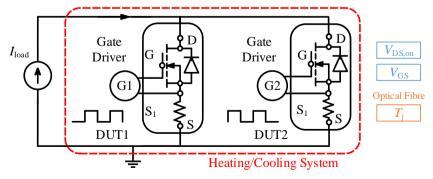

| Fig. 4.4. DC-based power-cycling test with $T_{\rm j}$ measurement through body diode voltage drop ( $V_{\rm SD}$ )                                                                                                                |

| Fig. 4.5. An example of junction temperature measurement using optical fibre thermal sensor                                                                                                                                        |

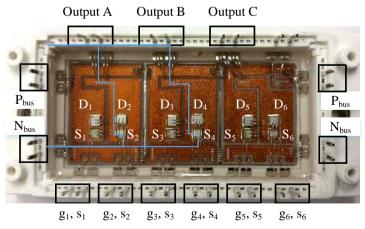

| Fig. 4.6. Layout of the three-phase SiC module (1.2 kV/20 A) 47                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

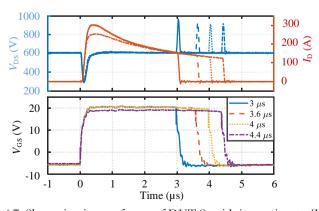

| Fig. 4.7. Short-circuit waveforms of DUT $S_5$ with increasing $t_{SC}$                                                                                                                                                                                                                                        |

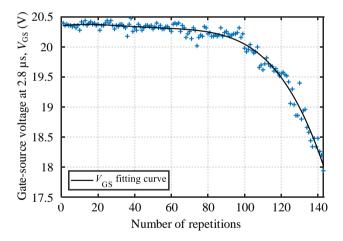

| Fig. 4.8. Reduction of gate-source voltage at $t = 2.8 \mu s$ (DUT S <sub>6</sub> ) with the number of repetitions increase                                                                                                                                                                                    |

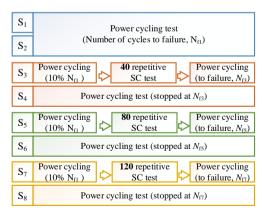

| Fig. 4.9. The approach of mixed power-cycling/repetitive short-circuit test                                                                                                                                                                                                                                    |

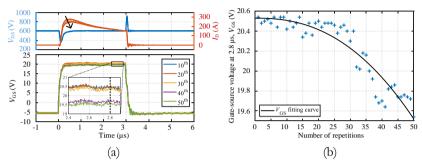

| Fig. 4.10. (a) Short-circuit waveforms of DUT $S_2$ from the $10^{th}$ to the $50^{th}$ repetition; (b) gate-source voltage at $t=2.8~\mu s$ versus the number of repetitions50                                                                                                                                |

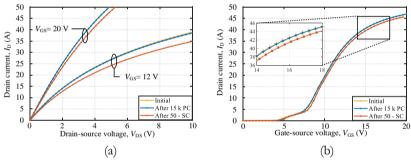

| Fig. 4.11. (a) $I_D$ - $V_{DS}$ and (b) $I_D$ - $V_{GS}$ curves of DUT $S_2$ before the test, after 15 k power cycles, and after 50 short-circuit repetitions                                                                                                                                                  |

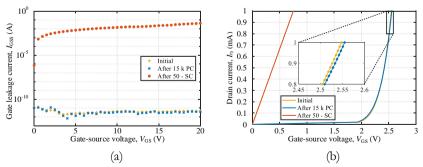

| Fig. 4.12. (a) Gate leakage current and (b) threshold voltage of DUT $S_2$ before the test, after 15 k power cycles, and after 50 short-circuit repetitions                                                                                                                                                    |

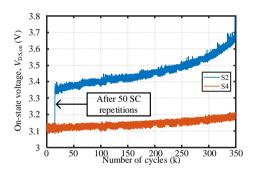

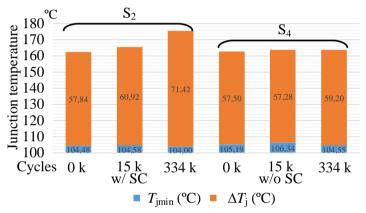

| Fig. 4.13. Evolution of $V_{\rm DS,on}$ throughout the mixed power-cycling test with/without 50 short-circuit repetitions performed at 15 k cycles                                                                                                                                                             |

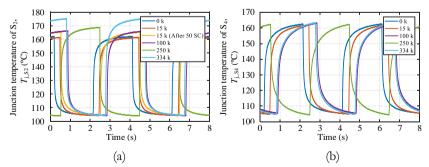

| Fig. 4.14. $T_j$ waveforms of power-cycling test at 0 k, 15 k, 100 k, 250 k, and 334 k: (a) DUT $S_2$ and (b) DUT $S_4$                                                                                                                                                                                        |

| Fig. 4.15. Comparison of junction temperature ( $T_{\rm jmax}$ , $T_{\rm jmin}$ , and $\Delta T_{\rm j}$ ) variation between DUT S <sub>2</sub> and S <sub>4</sub> (with/without 50 short-circuit repetitions)                                                                                                 |

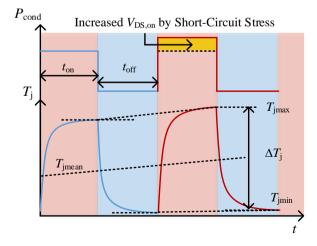

| Fig. 4.16. Effect of short-circuit degradation on the power-cycling conditions                                                                                                                                                                                                                                 |

| Fig. 4.17. Test approach of mixed power-cycling/repetitive short-circuit test with a different number of short-circuit repetitions (the devices paired with the same colours have been tested until the same number of cycles)                                                                                 |

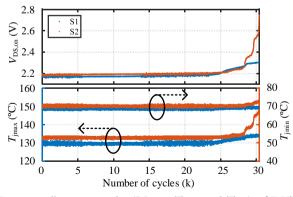

| Fig. 4.18. Power cycling test results ( $V_{DS,on}$ , $T_{jmax}$ , and $T_{jmin}$ ) of DUT $S_1$ and $S_2$ without any short-circuit stress.                                                                                                                                                                   |

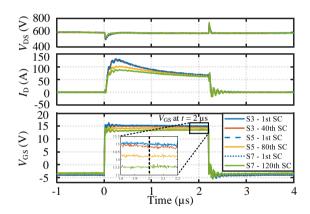

| Fig. 4.19. Repetitive short-circuit test results of DUT S <sub>3</sub> , S <sub>5</sub> , and S <sub>7</sub> (only the first and last repetition)                                                                                                                                                              |

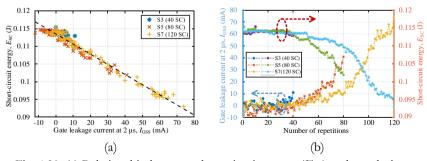

| Fig. 4.20. (a) Relationship between short-circuit energy ( $E_{SC}$ ) and gate leakage current at 2 $\mu$ s $I_{GSS}$ ; (b) $I_{GSS}$ and $E_{SC}$ versus number of repetitions.                                                                                                                               |

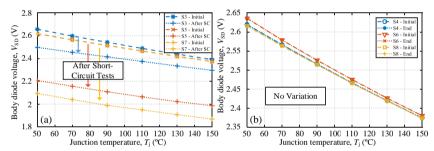

| Fig. 4.21. (a) $V_{\text{SD}}$ - $T_{\text{j}}$ curve of DUT S <sub>3</sub> , S <sub>5</sub> , and S <sub>7</sub> before test and after short-circuit repetitions; (b) $V_{\text{SD}}$ - $T_{\text{j}}$ curve of DUT S <sub>4</sub> , S <sub>6</sub> , and S <sub>8</sub> before and after power-cycling test. |

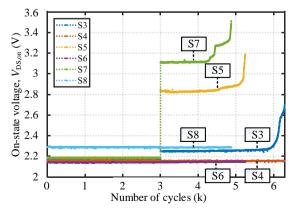

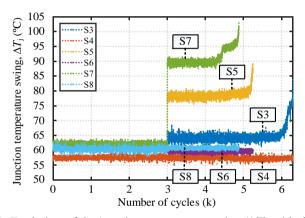

| Fig. 4.22. $V_{DS,on}$ evolution of DUT $S_3$ - $S_8$ with the number of power cycles56                                                                                                                                                                                                                        |

| Fig. 4.23. Evolution of the junction temperature swing $(\Delta T_j)$ with the number of power cycles on DUT $S_3$ - $S_8$                                                                                                                                                                                     |

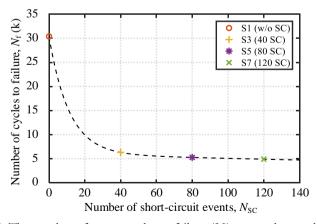

| Fig. 4.24. The number of power cycles to failure $(N_{\rm f})$ versus the number of short-circuit repetitions $(N_{\rm SC})$                                                                                                                                                                                   |

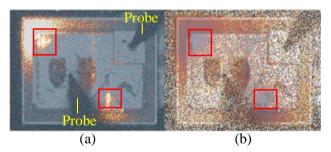

| Fig. 5.1. Lock-in thermography results of DUT S <sub>5</sub> : (a) amplitude image; (b) phase image                                                                                                                                                                                                            |

| Fig. 5.2. Lock-in thermography results of DUT S <sub>6</sub> : (a) amplitude image; (b) phase image                                                                                                                                                                                                            |

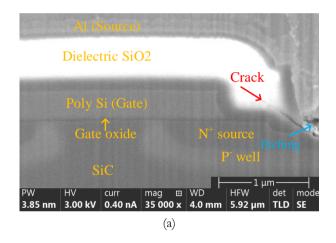

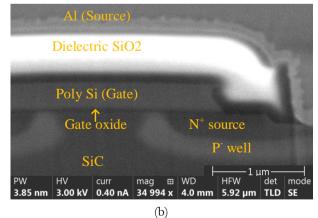

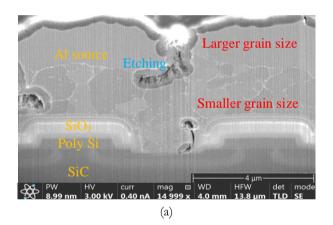

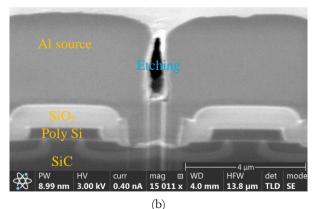

| Fig. 5.3. Cross-sectional SEM images: (a) DUT $S_5$ (the damaged cell and the $SiO_2$ crack marked with the red arrow); (b) DUT $S_6$ (the intact cell)61                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 5.4. Cross-sectional SEM images: (a) DUT $S_5$ (different grain sizes in the Al metallization layer); (b) DUT $S_6$ (no observable grain boundaries)                                                 |

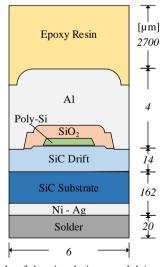

| Fig. 5.5. Sketch of the simulation model (not to scale)                                                                                                                                                   |

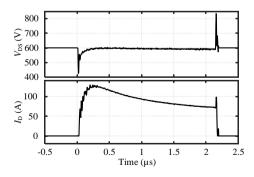

| Fig. 5.6. Short-circuit waveforms derived from experimental test ( $V_{DC}$ = 600 V, $t_{SC}$ = 2.2 $\mu s$ , and $T_{C}$ = 25 °C)64                                                                      |

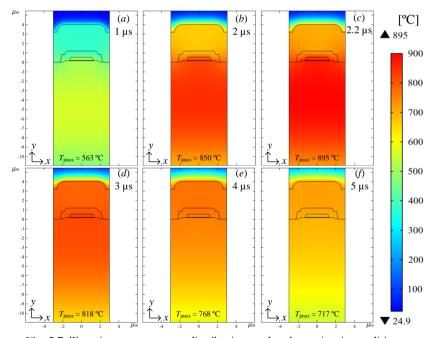

| Fig. 5.7. Transient temperature distribution under short-circuit condition at different time point: (a) 1 $\mu$ s; (b) 2 $\mu$ s; (c) 2.2 $\mu$ s; (d) 3 $\mu$ s; (e) 4 $\mu$ s; (f) 5 $\mu$ s            |

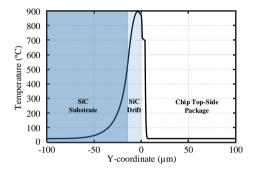

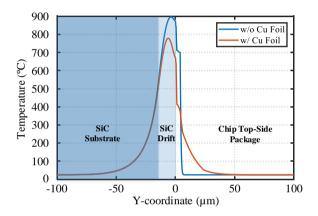

| Fig. 5.8. Temperature distribution along the Y-coordinate (X = $0 \mu m$ ) at the end of pulse time ( $t$ = $2.2 \mu s$ )                                                                                 |

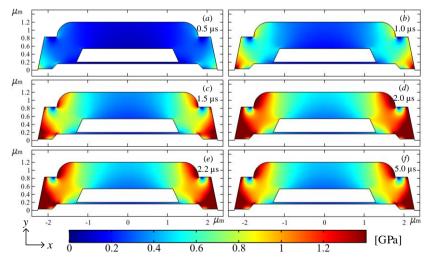

| Fig. 5.9. Von Mises stress distribution under short-circuit condition at different time point: (a) $0.5~\mu s$ ; (b) $1.0~\mu s$ ; (c) $1.5~\mu s$ ; (d) $2.0~\mu s$ ; (e) $2.2~\mu s$ ; (f) $5~\mu s$ 66 |

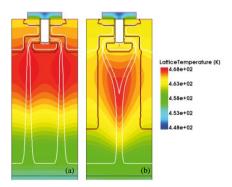

| Fig. 5.10. Lattice temperature distribution during the short-circuit condition at 0.2 $\mu s$ : (a) conventional MOSFET; (b) semi-SJ MOSFET67                                                             |

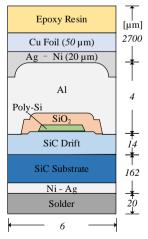

| Fig. 5.11. Sketch of the simulation model with Cu foil sintered on the top surface of the Al metallization layer (not to scale).                                                                          |

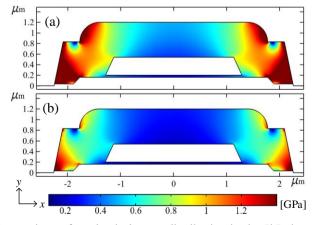

| Fig. 5.12. Temperature distribution comparison of two models at $t = 2.2 \mu s$ (a) the model without Cu foil (b) the model with Cu foil                                                                  |

| Fig. 5.13. Temperature distribution along with the vertical direction Y-coordinate (X = 0) at $t$ = 2.2 $\mu$ s in the model without and with Cu foil70                                                   |

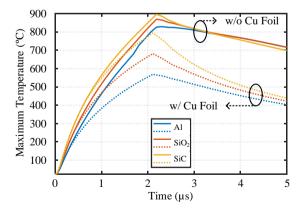

| Fig. 5.14. Evolution of maximum temperature with the time inside the Al, $SiO_2$ , and $SiC$ drift region in the model without and with Cu foil70                                                         |

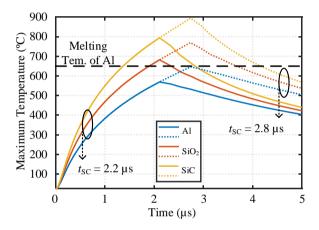

| Fig. 5.15. Evolution of maximum temperature inside the Al, SiO <sub>2</sub> , and SiC drift region in the model with Cu foil (increased pulse time from 2.2 $\mu$ s to 2.8 $\mu$ s)71                     |

| Fig. 5.16. Comparison of mechanical stress distribution in the $SiO_2$ interlayer region in the model (a) without Cu foil; (b) with Cu foil71                                                             |

## List of Tables

| Table 1.1 - Physical Properties of Si and 4H-SiC                                 | 2  |

|----------------------------------------------------------------------------------|----|

| Table 1.2 - Common Failures and Root Causes of Power Devices                     | 7  |

| Table 1.3 - Failure Locations and Causes of SiC MOSFETs                          | 10 |

| Table 1.4 - Accelerated Life Tests for SiC MOSFETs                               | 10 |

| Table 1.5 - Related Publications to the Chapters                                 | 15 |

| Table 2.1 - Main Testing and Measurement Equipment (Accessories)                 | 22 |

| Table 2.2 - Calculation of the Peak Drain Current Reduction                      | 27 |

| Table 3.1 - Summary of Short-Circuit Capability with Different Case Temperatures | 30 |

| Table 3.2 - Thermal Simulation Settings                                          | 41 |

| Table 4.1 - Test Condition for the Power Cycling Test                            | 48 |

| Table 4.2 - Test Condition for the Repetitive Short Circuit Test                 | 48 |

| Table 4.3 - Test Conditions for the Power Cycling Test                           | 54 |

| Table 4.4 - Test Conditions for the Repetitive Short Circuit Test                | 54 |

| Table 5.1 - Thermal Properties of the Materials                                  | 64 |

| Table 5.2 - Mechanical Properties of the Materials                               | 64 |

| Table 5.3 - Physical Properties of the Other Materials                           | 69 |

## Chapter 1

### Introduction

This chapter presents the background and motivation of this thesis, followed by the scientific questions, thesis objectives, and limitations. The outline of the thesis is provided, along with a list of publications at the end.

#### 1.1 Background

With the proliferation demand for electric vehicles and renewable energy systems, power electronic technology with the function of power conversion and energy process plays a more and more critical role [1]. The expected production of electric vehicles in Europe may grow to more than 4 million units in the next five years [2] and the total installed capacity of wind power in Europe will be more than 256 gigawatts by 2023 [3].

Modern power electronic systems mainly include three kinds of components: active components (i.e. the power semiconductor devices), passive components (e.g. transformers, capacitors, and inductors), and control units. Among these, power semiconductor devices are the key components to turn on or turn off the current flow. To meet the increasing requirements toward high efficiency, high power density, and highly-integrated systems, especially for the electric vehicle applications, power semiconductor devices need to have lower and lower power loss, higher switching speed, and blocking voltage capability [4].

Power electronic circuits mainly consist of active switches and diodes, where silicon (Si) is the dominant material. Typical active switches are metal-oxide-semiconductor field-effect transistors (MOSFET) and insulated gate bipolar transistor (IGBT). Among these, the former is a unipolar device, whereas the other one is a bipolar device, which uses majority as well as minority carriers (i.e. electrons and holes) at the same time.

Due to the absence of minority carriers, Si-based power MOSFETs have inherently fast switching capability and low switching losses. However, the blocking voltage capability is related to the thickness and doping concentration of the drift region. To enable a greater blocking voltage capability, its on-state resistance and conduction losses will increase. This factor results in a limited on-state current in high-voltage applications. Therefore, it is usually the choice for low operating voltage applications (below 600 V).

For bipolar devices, when the devices are in the on-state, minority carriers are injected into the high-resistance drift region, which causes a reduction in the resistivity. Thanks to this so-call conductivity modulation, they exhibit the advantages of high-current capability with low on-state resistance in high-voltage applications (from 600 V to 6.5 kV). Nevertheless, the switching frequency is limited.

Despite these advancements, the performance of Si-based power devices is now approaching the fundamental material limits for some high-power,

high-switching-frequency, and high-temperature applications. The maximum rating voltage of commercial Si-based IGBTs is 6.5 kV with a relatively slow switching speed and its practical operating temperature lower than 175 °C, which doesn't meet the requirement for industrial and automotive applications [5]. The aforementioned factors also hinder the efficiency improvement of the power converters and result in bulky cooling systems at the same time. Although future development in Si-based power devices will not stop, the introduction of wide-bandgap materials brings a significant revolution to the power electronics technology and market. As a wide bandgap material, silicon carbide (SiC) has become a hot topic of interest and been the focus of many studies over the last two decades [6].

#### 1.1.1 Silicon Carbide: From Material to Devices

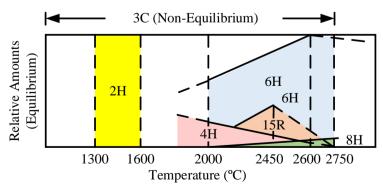

SiC material exists in more than 250 different crystalline structures (i.e. polytypes) depending on the different stacking ways of identical two-dimensional layers, such as 3C-SiC, 4H-SiC, and 6H-SiC [7]. At present, 4H-SiC polytype is generally favoured by power device manufacturers for its wider bandgap, less ionization energy and higher carrier mobility [8] [9]. A comparison of physical properties between Si and 4H-SiC material with 10<sup>16</sup> cm<sup>-3</sup> doping density at room temperature is listed in Table 1.1[10] [11].

Since the critical electric field strength of 4H-SiC is significantly higher than that of Si, SiC devices can be made with much thinner drift layer and higher doping concentrations. Compared to Si, SiC devices such as MOSFETs can have very high blocking voltage capability and very low on-state resistance at the same time. In this case, the lower on-state resistance makes it possible to have a smaller chip size, resulting in lower parasitic capacitance and faster switching speed.

The switching speed of power devices is also related to the saturated drift velocity. With the influence of the high electric field, the drift velocity of carriers is no longer proportional to the electric field strength and it gradually becomes saturated due to the scattering phenomenon. During the turn-off transient, carriers are swept out of the

| Material                                     | Si        | 4H-SiC    |

|----------------------------------------------|-----------|-----------|

| Energy Bandgap (eV)                          | 1.12      | 3.26      |

| Electron Mobility (cm <sup>2</sup> /V·s)     | 1200      | 850       |

| Hole Mobility (cm <sup>2</sup> /V·s)         | 420       | 115       |

| Electron Saturated Drift Velocity (107 cm/s) | 1         | 2.2       |

| Critical Electric Field Strength (106 V/cm)  | 0.4       | 2.5       |

| Relative Dielectric Constant                 | 11.8      | 9.8       |

| Thermal Conductivity (W/cm·K)                | 1.4 - 1.5 | 3.3 - 4.9 |

| Melting Point (K)                            | 1690      | ~3100     |

| Young's Modulus (GPa)                        | 160       | 390 - 690 |

| Fracture Strength (GPa)                      | 7         | 21        |

Table 1.1 - Physical Properties of SI and 4H-SiC [10] [11]

depletion region at the saturated drift velocity [12]. Since the saturated drift velocity of 4H-SiC is twice the value of Si, SiC devices reach higher switching speeds.

The much wider bandgap of 4H-SiC means that it can operate at extremely high temperatures beyond 600 °C without suffering from intrinsic conduction effects. On the other hand, it has approximately three times higher thermal conductivity compared to Si material; this property enables to dissipate a larger amount of generated heat, which opens for applications requiring high cooling temperatures. Presently, the operating temperature of SiC devices remains from 150 °C to 200 °C due to the issues related to oxide quality [8] [13]. It is believed to operate at the temperature higher than 200 °C with coming improvements [14].

All of the advantages mentioned above make SiC devices a most attractive candidate for high-power, fast-switching, and high-temperature power electronics applications. However, the cost still hinders their extensive diffusion into the market and a large proportion of the cost is from the 4H-SiC substrate. Nowadays, the physical vapor transport (PVT), also known as modified Lely method, is typically used for 4H-SiC crystal growth. The stability of different SiC polytypes is shown in Fig. 1.1 as a function of temperature and 4H-SiC growth only remains stable in the harsh temperature range, mainly from 1800 °C to 2600 °C [15]. Although the growth rate depends on many parameters (e.g. pressure and temperature), it is in the range of 0.2 – 2 mm/h, which is much lower than the value for Si crystal pulling [16]. Besides, a high-quality SiC crystal with a large diameter still faces challenges due to crystallographic defects such as stacking faults and threading dislocations.

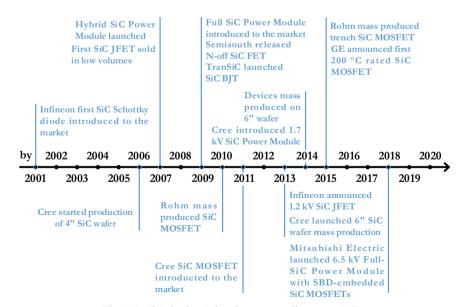

With the improvement of SiC wafer quality and process technology, the SiC devices' market is booming. Some significant SiC development milestones have been reported in [17] and they are shown in Fig. 1.2 together with latest achievements.

Since Infineon launched the first commercial SiC Schottky diode in 2001, the SiC diodes have shown a continuous increase in the blocking voltage and conduction current rate. There are mainly three types of SiC diodes: Schottky barrier diode (SBD), junction barrier Schottky (JBS) diode, and PiN diode. With a combination of Schottky diode structure and SiC material, the SBDs show fast switching behaviour and no reverse recovery current thanks to the majority carrier conduction. However, as a result of

Fig. 1.1. Stability diagram of SiC polytypes [15].

Schottky barrier lowering effect, the leakage current of the SBDs increases fast at high temperatures, which limits its available blocking voltage. Benefiting from the effect of the P+ region, the JBS diodes keep lower leakage current even at high temperature. At present, most commercial SiC diodes in the market are JBS structures in the range from 600 V to 1.7 kV. Some 3.3 kV devices are also available in the market, but with lower current rating due to the thick drift layer. Besides, a 15 kV JBS diode has been designed for high-frequency application [18] and a trench structure has been proposed in [19]. As for the SiC PiN diode, it has much lower leakage current and its drift resistance is reduced with conductivity modulation, which makes it a possible candidate for high-temperature operations and ultra-high voltage ratings (such as 10 - 20 kV) [20]. On the other hand, the influence of minority carrier causes the disadvantage of a non-zero reverse recovery effect.

Regarding SiC active switches, the SiC junction field effect transistors (JFETs) became the focus at the early stage of development as can be seen in Fig. 1.2. Nevertheless, the JFET is inherently a normally-on device, which limits its usage in power electronic circuits. Normally-off trench JFETs have been proposed thanks to a higher built-in voltage of their P-N junctions, but the high channel resistance and low threshold voltage still needed to be improved [21]. Thanks to the double-side high-level injection and no channel region, the SiC BJT has the advantages of lower on-resistance, which enables high current ratings. However, it requires a large control current through the base-emitter junction, which causes a substantial power loss due to the built-in potential. Several high-voltage SiC IGBTs have also been developed over the past decade, showing much higher voltage ratings than their Si counterparts. Due to the much higher mobility of electrons than holes, the N-type SiC IGBTs have a faster switching speed than the

Fig. 1.2. SiC devices' development milestones [17].

P-type ones. However, the P+ substrate shows high resistivity and defect density, which impedes the development of the N-type IGBT until the free-standing technology proposed in 2010 [22] [23]. At present, the N-type and P-type SiC IGBT have reached 27 kV and 15 kV blocking voltage, respectively [24] [25]. In addition, the gate turn-off thyristor (GTO) and the emitter turn-off thyristor (ETO) based on SiC are also promising devices for high voltage applications [26] [27].

Among SiC switches, SiC power MOSFET is well suited for the voltage rating requirement from 600 V to 3.3 kV, especially the 1.2 kV – 1.7 kV range. Some high-voltage SiC MOSFETs have also been designed from 3.3 kV to 15 kV [28] [29] [30]. Compared to the Si IGBT, it has a lower switching loss because of majority carrier conduction mechanism. Besides, benefiting from SiC material, it shows a lower conduction loss than Si MOSFET. Apart from these, the body diode of SiC MOSFET is a P-N junction diode with short minority carrier lifetime and its recovery performance is similar to the one of SiC SBD, which enables an extremely low recovery loss [8]. However, bipolar degradation may occur when current flows through the body diode [31]. In this case, there remains a need to use external anti-parallel SiC SBD to suppress current flowing through the body diode. Since the chip size of an SBD could be larger for the higher blocking voltage, Mitsubishi Electric first launched the 6.5 kV full-SiC power module with SBD-embedded SiC MOSFETs in 2018 [32] [33].

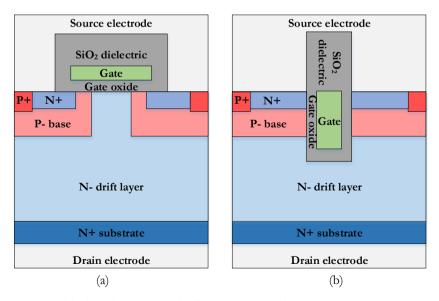

Owing to the higher mobility of electrons in respect to holes, the SiC MOSFET is typically designed with N-channel. Nowadays, there are mainly two types of SiC MOSFET structures, named as planar and trench technology and Fig. 1.3 shows their typical cell structures.

Fig. 1.3. Typical SiC MOSFET cell structures: (a) planar type; (b) trench type.

Rohm and Cree first launched the commercial SiC MOSFET in 2010 and 2011, respectively. General Electric (GE) released a SiC MOSFET with 200 °C junction temperature in 2014 [34]. In 2015, Rohm first mass-produced trench-type SiC MOSFET.

Based on the conduction current path, the on-state resistance of planar SiC MOSFET mainly consists of channel resistance, JFET region resistance, drift resistance and substrate resistance. In trench- MOSFETs, by eliminating the JFET region, the current density in the trench cell improves, which enables lower on-state resistance.

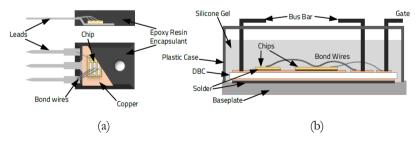

To ensure chip operation and meet application requirements, a suitable package is needed, which typically concerns three aspects: good thermal conductivity to dissipate the heat losses to an external cooling system; compact layout to achieve low parasitics (especially for high switching frequency applications); good protection against environmental influences (such as electrical insulations). In general, the package type depends on the power range of the chips. Nowadays, there are two conventional package types for SiC MOSFET chips, namely discrete devices and power modules, which mainly continue to use previous packaging technology for Si chips.

Discrete packages are generally used in the range of small power below 1.7 kV blocking voltage and 120 A rating current. A common through-hole design of this package in the market is transistor outline (TO) package. Fig. 1.4 (a) presents a single-chip discrete device with TO-247 (3-pin) package [35]. The drain of the SiC MOSFET chip is soldered on a lead frame, which is connected to the middle lead. The source and gate pads of the SiC MOSFET chip are connected to the other two leads through metal (such as Al and Cu) bond wires. For the purpose of protection and insulation, it is encapsulated with transfer mould compound such as epoxy resin. The backside of the device is normally metal and electrically-connected to the drain. The hole enables to mount the device on a heat sink, which allows dissipating more heat.

Power module, on the other hand, can provide a higher heat dissipation capability and make it possible multi-chip electrical connection internally, such as half-bridge and three-phase circuits, etc. Fig. 1.4 (b) exhibits a classical structure cross-section of the power module [35]. The drain of the SiC MOSFET chips is soldered on the direct bonded copper (DBC) substrate by means of a solder layer, which has an insulated ceramic substrate sandwiched with two copper layers and the multiple chips electrical connection are archived through the copper tracks and the bond wires. The backside of the DBC

Fig. 1.4. Conventional SiC MOSFET package structures: (a) discrete device with TO-247-3 package; (b) power module [35].

substrate is also soldered on a base plate, which can be mounted on a cooling system with a thermal grease, such as a heat sink and provides mechanical support at the same time. To ensure the chips insulation and prevent environmental contamination/vibration, the silicone gel is poured into the module case and only the terminals, which connect to the copper tracks, are kept outside of it for power and control.

Apart from these, some advanced packaging structures for SiC MOSFET power modules have been investigated to meet the specific requirement for high switching frequency and high-temperature operations. Due to the influence of fast switching speed (dV/dt) and di/dt, the parasitic properties need to be minimized and thereby, various wireless and novel structures have been proposed, such as flexible printed circuit board (PCB) with Ag sintering [36], press-pack structure [37] and chip-on-chip structure [38]. On the other hand, as SiC devices provide the potential to achieve operating temperature higher than 200 °C, new packaging materials and techniques are drawing more and more attention [14] [39].

With the superior SiC material properties, improved chip design and packaging technology mentioned above, SiC devices are believed to play an important role for many specific power electronic applications. According to the report from Yole, the SiC devices market's value is expected to approach two billion USD by 2024 [40]. However, at the same time, the reliability and robustness challenges rise to the surface.

#### 1.1.2 Reliability Challenges: Normal and Abnormal Conditions

To meet the long-term operation requirement and reduce the cost, the reliability prediction of Si-based power electronic system have been investigated extensively in the past, mainly from two aspects: the design for reliability and remaining useful life (RUL) prediction. However, due to the implementation of the SiC MOSFETs and its promising capability for high power density and harsh applications, the reliability and lifetime model of SiC MOSFETs itself needs to be investigated at first.

Failures can be divided into three categories: early failures, catastrophic failures, and ageing failures as listed in Table 1.2. Most early failures come from the defects and quality issues from the manufacturing process and supply chain. Catastrophic failures, in most case, are induced by abnormal events, which means that the SiC MOSFET exceeds its nominal conditions (i.e. safe operating area) for a short period and there are various types of abnormal events, such as overvoltage, overcurrent, short circuit, unclamped inductive switching (UIS), over-temperature. According to different root causes, catastrophic failures can also be divided into two subgroups, i.e. severe overstress and instabilities.

TABLE 1.2 - COMMON FAILURES AND ROOT CAUSES OF POWER DEVICES

| Failures              | Root Causes                        |                       |  |

|-----------------------|------------------------------------|-----------------------|--|

| Early Failures        | Manufacturing Defects              |                       |  |

| Catastrophic Failures | Severe Overstress<br>Instabilities | (Abnormal Conditions) |  |

| Ageing Failures       | Wear Out                           | (Normal Conditions)   |  |

#### 1.1. Background

The former is directly related to external conditions (e.g. system level) with higher stress than nominal value, whereas the latter is characterized by a loss of control internally (device level), leading to destruction. Despite instabilities can also be triggered by external conditions, they are strongly related to the chip technology, manufacturing process, and wire bonding quality [41]. As a result of wear-out under normal operating conditions, ageing failures typically take years to occur and a degradation process prior to failure can be observed.

From the perspective of device structures, failure modes of SiC MOSFETs can be classified into chip-level and package-level failure modes. Gate oxide and body diode are two common failure locations at the chip level. Due to increased scattering at the oxide/semiconductor interface, the electrons mobility in the inversion layer is lower than that in the bulk semiconductor. In SiC MOSFETs, the inversion layer mobility is only 5-10% of the bulk mobility, and this proportion is much lower than the one in Si MOSFETs, which is around 50% [10]. This factor results in larger channel resistance in SiC MOSFETs. In order to reduce channel resistance, a relatively low gate threshold voltage (V<sub>th</sub>) is desired. However, as can be seen in Fig. 1.5, if the P-base doping concentration ( $N_A$ ) is  $1\times10^{17}$  cm<sup>-3</sup> and the gate oxide thickness is 0.1 µm, its  $V_{th}$  will reach as high as 11 V [42]. Thus, the gate oxide thickness tends to be thinner than Si MOSFETs and this raises reliability issues. Typically, the gate oxide thickness for SiC MOSFETs is designed only about 50 nm. Reducing the spacing between P-base regions of planar SiC MOSFETs can be an approach to shield the gate oxide region from the high electric field under forward blocking condition, but meanwhile, it results in an increased on-state resistance since the drain current flow is limited by the narrower IFET region. Therefore, a trade-off between on-state resistance and gate oxide reliability needs

Fig. 1.5. Threshold voltage of SiC MOSFET compared to Si MOSFET (including the impact of N+ polysilicon gate and an oxide fixed charge of  $2 \times 10^{11}$  cm<sup>-2</sup>) [42].

to be considered. In addition, locally-enhanced electric field provided by a relative thinner gate oxide, existing defects in gate oxide layer, and interface traps could cause time-dependent dielectric breakdown issues [43] [44] [45].

The body diode of the SiC MOSFETs is formed by the N- drift and P-base/P+ region and its reliability is also an important issue. When a surge stress is applied to the body diode, the overheating may cause the expansion of stacking faults from basal plane dislocation in the epitaxial layers, leading to a permanent forward voltage drop ( $V_F$ ) increase [31] [46].

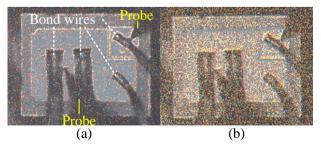

Since commercial SiC MOSFET devices are still packaged with a similar structure as Si-based devices and they show similar failure locations in the package level, i.e. bonding wire and solder layers. Fig. 1.6 shows package-level failure modes, including bond wire lift-off [47], bond wire fracture [48], solder layer fatigue [49] and Al metallization reconstruction [50].

Bonding wires mainly have two types of failure modes: bond wires fracture and bond wires lift-off. For power modules, the former occurs slowly at the interface with copper tracks of the DBC and this is caused by repetitive expansion and contraction due to alternative heat and cooling [51]. The latter generally happens at the interface with SiC die, induced by the mismatch of the coefficients of thermal expansion (CTE) between bond wires and SiC. Thermo-mechanical stress contributes to the metallization reconstruction and cracks near the interface, which gradually leads to a bond wire lift-off [52] and it is also observed in the discrete SiC MOSFETs after failure analysis [53].

Typically, solder layers in SiC power modules are used to attach the SiC die on the DBC substrate and connect the substrate with the baseplate. Also due to CTE mismatch between SiC and DBC, shear stress could gradually cause the cracks and voids in the

Fig. 1.6. Package-level failure modes in power module: (a) bonding wire lift-off [47];(b) bonding wire fracture [48]; (c) chip solder edge delamination [49]; (d) Al metallization reconstruction [50].

#### 1.1. Background

solder layer, which increases the thermal resistance, resulting in temperature rise and further solder delamination [54].

Compared with Si devices, the package-level reliability of SiC MOSFETs is still facing some new challenges. The higher current density of the SiC chips may lead to more voids inside bond wires and solder layers under the influence of electromigration, which induces a more severe degradation [52] [55]. Since the SiC material has much larger Young's modulus than Si, as listed in Table 1.1, the interface between SiC die attached solder and the DBC substrate need to endure higher stress and accumulated creep strain [56]. Another factor is the thermal conductivity. Although the higher thermal conductivity of SiC material makes it possible for dissipating more heat, at the same time, it may cause a larger temperature variation in SiC devices than in Si, increasing the thermo-mechanical stress at the interfaces [57]. To summarize, the common failure locations of SiC MOSFETs and their main causes are listed in Table 1.3.

To ensure the reliable operation within expected service life and enable a reliability prediction under field stress conditions, many laboratory accelerated life tests (ALTs) have been developed and Table 1.4 lists the main ALTs for SiC MOSFETs.

Among these ALTs, the power cycling (PC) tests are designed to detect ageing failures induced by long-term wear-out under normal operating conditions (e.g. bond wires lift-off) since SiC MOSFET chips are actively heated by their generated losses and

TABLE 1.3 - FAILURE LOCATIONS AND CAUSES OF SIC MOSFETS

| Level   | Failure Location | Main Cause                                         |  |

|---------|------------------|----------------------------------------------------|--|

| Chip    | Gate Oxide       | High Electric Field/High Temperature               |  |

|         | Body Diode       | Surge Current                                      |  |

| Package | Bond Wires       | High Current Density                               |  |

|         | Solder Layers    | High Temperature Swing and High<br>Young's Modulus |  |

TABLE 1.4 - ACCELERATED LIFE TESTS FOR SIC MOSFETS

| Test | Brief Description                  | Test Condition                    |  |

|------|------------------------------------|-----------------------------------|--|

| HTGB | High Temperature Gate Bias Test    | Maximum $V_{GS}$ and $T_j$ Stress |  |

| HTRB | High Temperature Reverse Bias Test | Maximum $V_{DS}$ and $T_j$ stress |  |

| PC   | Power Cycling Test                 | Internal Heating by Losses        |  |

| TC   | Temperature Cycling Test           | Low External Heating Rate         |  |

| TS   | Thermal Shock Test                 | High External Heating Rate        |  |

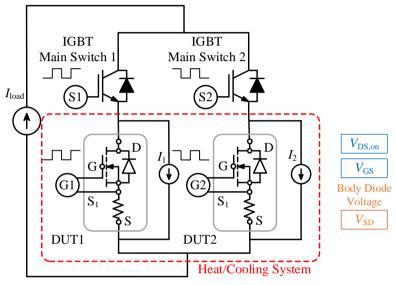

this test approach is often used for reliability prediction and lifetime estimation. At present, a power cycling test protocol for SiC MOSFETs at high temperature has been proposed [58]. Different measurement and power cycling methods have been evaluated and the method of measuring the voltage drop of the body diode with negative gate voltage is found most suitable for SiC MOSFETs [59] [60]. In [61], a modified estimation model for the bond wire resistance increase is proposed based on chip degradation. In addition, several electrical parameters can be compared before and after the power-cycling tests showing that the threshold voltage, output characteristic and transfer characteristic are affected significantly [62].

Apart from these ALTs aiming at normal operating conditions, catastrophic failures of SiC MOSFETs, induced by abnormal conditions, also attracted extensive attention. To meet the requirements for power electronic applications, the SiC MOSFETs are expected to withstand short circuits and a short-circuit event can occur in different ways. For instance, Fig. 1.7 presents a conventional three-phase voltage source converter mainly used for motor drive applications, together with two possible short-circuit cases. 1) When the devices S<sub>1</sub> and S<sub>4</sub> start to work in the on-state, the short-circuit case 1 is caused by the unexpected conduction of the device S<sub>2</sub>. In this case, the devices S<sub>1</sub> and S<sub>2</sub> withstand short-circuit stress. 2) Due to the degradation of phase-to-phase insulation, the short-circuit case 2 could occur and it leads to the short-circuit condition on the devices S<sub>1</sub> and S<sub>4</sub>.

In fact, short circuit conditions can also be classified into different types [63]:

1) Type I (hard switching fault): A short circuit that already exists when the device is turned on. 2) Type II (fault under load): Short circuit occurs when the device is in the conducting state. 3) Type III: Short circuit occurs across the load during the conducting mode of the body diode. Recently, the SiC MOSFETs have been evaluated under various types of short circuits as well as stresses [64] [65] [66]. A short-circuit safe operation area (SCSOA) has been proposed for SiC MOSFET power devices [67].

Based on the experimental data obtained from ALTs, the lifetime model of SiC MOSFETs can be built and the approaches for lifetime estimation can be mainly divided

Fig. 1.7. Short-circuit cases in a three-phase voltage source converter.

into two groups: empirical lifetime models and physics-based lifetime models. The empirical models are statistical and cannot distinguish between different failure mechanisms. The latter, in contrast, is time-consuming but considers the physical interactions of the observed failure mechanisms taking into account the packaging geometric structure and materials [68]. In other words, the lifetime can be estimated based on the failure mechanism root cause. Besides, the RUL estimation also needs matched lifetime model and suitable ageing indicators. Therefore, it is critical to fully understand the ageing and failure mechanisms of SiC MOSFETs by taking into account various operating conditions.

#### 1.2 Research Motivation

At present, many efforts have been devoted to investigate the reliability and robustness of SiC MOSFETs by performing either ALTs or short circuit tests, separately. As mentioned above, through different stresses of ALTs (especially power cycling tests), an accurate lifetime model of SiC MOSFETs can be worked out. Thereafter, when the SiC MOSFETs is used in a power electronic system, the remaining useful life (RUL) of SiC MOSFETs can be estimated based on the condition monitoring parameters, i.e. the ageing indicators. Notably, this approach only considers the ageing failures, in other words, the wear-out issues under normal operating conditions. On the other hand, the catastrophic failures of SiC MOSFETs, coming from abnormal operating conditions are investigated by performing UIS tests or short-circuit tests, which aim to evaluate its robustness (e.g. short-circuit capability) and failure mechanisms.

With the development of faster short circuit protection and desaturation fault detection for SiC MOSFETs, the device destruction can be avoided to some extents, allowing the SiC MOSFETs to withstand many non-destructive short-circuit events within its expected service lifetime. Since the impact of short-circuit events was used to be neglected before, this situation brings a new scientific question for the lifetime estimation of SiC MOSFETs. Therefore, the motivation of this thesis is to investigate the reliability of SiC MOSFETs by taking into account the short-circuit events.

#### 1.3 Scientific Questions

Based on the background and research motivations regarding the above reliability issues of SiC MOSFETs, the overall question of this Ph.D. thesis is listed here:

What is the impact of short-circuit events on the Remaining Useful Life of SiC MOSFETs?

To be more specific, more detailed scientific questions are to be explored:

- How can the short-circuit conditions affect the electrical parameters of SiC MOSFETs? How to identify a suitable degradation indicator?

- How do the short-circuit conditions affect the normal operation of SiC MOSFETs? Assuming the device is utilized in applications at different temperatures, how to consider the influence of case temperature?

- How can short-circuit events affect the accelerated ageing tests and, further, the Remaining Useful Life of SiC MOSFETs?

• What is the short-circuit degradation mechanism? How can the impact of short circuit events be mitigated at the package-level?

#### 1.4 Thesis Objectives

This Ph.D. thesis aims to investigate the impact of short-circuit conditions on the remaining useful life (RUL) of SiC MOSFETs. In order to answer the aforementioned scientific questions, the main objectives are described in this section as following:

- Study of degradation indicators under short-circuit conditions

A suitable degradation indicator should be able to reflect the key degradation process under short-circuit conditions. Degradation indicators will be explored with two experimental approaches.

- Investigation on the impact of short-circuit degradation on the normal operation

To meet the repeatability requirement, the short-circuit condition will be

evaluated for a specific type of SiC MOSFET. By means of curve tracer and

double pulse tests, the variation of static and dynamic characteristics will be

explored extensively. The influence of case temperature will also be considered.

- Investigation on the impact of short-circuit degradation on the RUL

Based on the mixed power-cycling/repetitive short-circuit tests, the quantitative

impact of short-circuit events on the power-cycling conditions and further RUL

will be explored. A deeper analysis of the failed and still functional device will

be performed to better understand the degradation mechanisms.

- Simulation of the short-circuit degradation and mitigation strategy

This study aims to simulate the thermal and mechanical behaviour of SiC MOSFETs under short-circuit conditions to explain the degradation observed in experimental test and failure analysis. Based on the degradation mechanisms, a package-level strategy will be explored to mitigate the impact of short-circuit events.

#### 1.5 Limitations

With the improvement of higher quality SiC process technology and design evolution, many power semiconductor manufacturers are introducing new commercial SiC devices into the PE market. The various chip- and package level designs of SiC MOSFETs from 650 V to 1.7 kV may bring a deviation for reliability analysis. This thesis focuses on the planar-type SiC MOSFETs with the blocking voltage in the range of  $1.0~\rm kV - 1.2~\rm kV$ , which is now to be regarded as mature, and is gradually replacing its Si counterparts in many applications.

Furthermore, the short-circuit tests done in this thesis have been performed with a low-inductance laboratory non-destructive tester. Since the short-circuit performance is affected by the stray inductances, the short-circuit events in the real case may result in a higher voltage overshoot, exceeding the maximum rated voltage. This factor is not taken into account in this thesis either.

Finally, the mixed power-cycling/short-circuit tests have been carried out with a restricted number of samples. Although the SiC MOSFET samples were well-selected

with matched electrical characteristics to mitigate the influence of characteristic variation, there has been a non-negligible dispersion in some cases.

#### 1.6 Thesis Outline

The Ph.D. dissertation takes the form of a collection of papers and sums up the outcomes from a number of publications which are listed in Section 1.7. This thesis consists of two main parts: 1) a Report, which is organized with six chapters and 2) Selected Publications.

Chapter 1 has given an introduction to this thesis, mainly the research background and motivation. Following the scientific questions, the thesis objectives have been discussed as well as the limitations. Chapter 2 shows the short-circuit performance in SiC MOSFETs and the degradation indicators were analysed based on two experimental approaches. As the affecting main factors for the SiC MOSFETs operation, the variation of static and dynamic characteristics induced by the short circuits were assessed in Chapter 3. Since case temperature strongly depends on the field application, temperature-dependent degradation was also considered. Chapter 4 describes the investigation on the impact of short-circuit events on the power-cycling conditions, and furthermore, the RUL by applying different degrees of short-circuit stress. A revised lifetime model taking into account the short-circuit events is proposed. Chapter 5 gives a further insight into the short-circuit degradation by the achievement of thermo-mechanical simulation and failure analysis. Based on the degradation mechanisms, a package-level strategy is proposed to mitigate the impact of short-circuit conditions on the RUL. Finally, the conclusions are drawn in Chapter 6 together with the prospect of future research on this topic.

#### 1.7 List of Publications

The publications related to this Ph.D. thesis are shown below and their relevant contribution to each chapter are listed in Table 1.5.

#### **Journal Articles**

- [J1] H. Du, P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Investigation on the degradation indicators of short-circuit tests in 1.2 kV SiC MOSFET power modules," *Microelectronics Reliability*, vol. 88-90, pp. 661-665, 2018.

- [J2] H. Du, L. Ceccarelli, F. Iannuzzo, and P. D. Reigosa, "Implications of short-circuit events on power cycling of 1.2-kV/20-A SiC MOSFET power modules," *Microelectronics Reliability*, vol. 100-101, pp. 113373, 2019.

- [J3] H. Du, P. D. Reigosa, L. Ceccarelli, and F. Iannuzzo, "Impact of repetitive short-circuit tests on the normal operation of SiC MOSFETs considering case temperature influence," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 195-205, 2020.

[J4] H. Du, S. Letz, N. Baker, T. Goetz, F. Iannuzzo, and A. Schletz, "Effect of short-circuit degradation on the remaining useful lifetime of SiC MOSFETs and its failure analysis," *Microelectronics Reliability*, pp. 113784, 2020.

#### **Publications in Conference Proceedings**

- [C1] H. Du, P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Impact of the case temperature on the reliability of SiC MOSFETs under repetitive short circuit tests," in *Proc. of 2019 IEEE Applied Power Electronics Conference and Exposition* (APEC), 2019, pp. 332-337.

- [C2] H. Du, N. Baker, and F. Iannuzzo, "Implications of short-circuit degradation on the aging process in accelerated cycling tests of SiC MOSFETs," in Proc. of the 32nd IEEE International Symposium on Power Semi-conductor Devices and ICs (ISPSD), 2020, pp. 202-205.

- [C3] **H. Du** and F. Iannuzzo, "A mitigation strategy for the short-circuit degradation in SiC MOSFETs," in *Proc. of IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia 2020 (WiPDA-Asia)*, 2020 (in press).

TABLE 1.5 - RELATED PUBLICATIONS TO THE CHAPTERS

| Chapter No. | Relevant Publications |  |

|-------------|-----------------------|--|

| 2           | J1 and J3             |  |

| 3           | J3 and C1             |  |

| 4           | J2, J4, and C2        |  |

| 5           | J4 and C3             |  |

### Chapter 2

## **Degradation Indicators under**

### **Short-Circuit Conditions**

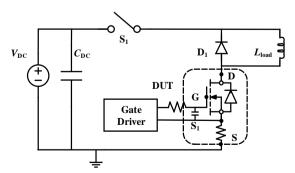

In this chapter, the short-circuit performance in SiC MOSFETs considering several key factors is presented and two common failure modes under short-circuit conditions are introduced. Then an experimental short-circuit test bench is described in detail and the degradation indicators in terms of short-circuit tests are investigated with two experimental approaches. This chapter is mainly contributed by [11] and [13].

#### 2.1 Short-Circuit Performance and Failure Modes

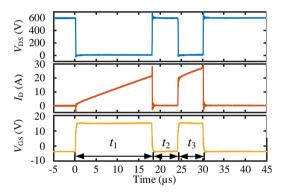

As mentioned above in Section 1.1.2, there are mainly three types of short-circuit conditions, and this thesis focuses on the type I, also termed hard switch fault. Fig. 2.1 shows a typical short-circuit behaviour of SiC MOSFETs including drain-source voltage ( $V_{\rm DS}$ ), gate-source voltage ( $V_{\rm GS}$ ), and drain current ( $I_{\rm D}$ ). Before turning on the SiC MOSFETs, a negative voltage is applied to  $V_{\rm GS}$  and the  $V_{\rm DS}$  keeps at rated high voltage with the value of  $V_{\rm DC}$ . When the device turns on with short-circuit condition, the  $I_{\rm D}$  starts to increase and settles at saturation current ( $I_{\rm SC\_max}$ ) corresponding to specific  $V_{\rm GS}$ . At the same time, the  $V_{\rm DS}$  decreases for a short time due to the  $I_{\rm D}$  gradient, i.e. di/dt. Then the device is subjected to both high voltage and high current simultaneously for several or up to 10-20 microseconds, and the  $I_{\rm SC}$  decreases with time due to the

Fig. 2.1. Typical short-circuit (type I) behaviour in SiC MOSFETs.

self-heating. Thereafter, the short-circuit protection triggers and the device turns off with a negative  $V_{\rm GS}$  to avoid catastrophic failures. During the turn-off period, an inductive voltage peak ( $V_{\rm DS\_max}$ ) appears, which is also caused by the di/dt, similarly to turn-on transient. To ensure a lower  $V_{\rm DS\_max}$  than the rated blocking voltage of the device, the stray inductance in the power loop needs to be minimized and the di/dt must be limited by a higher gate resistance.

Meanwhile, the dissipated energy during short-circuit pulse ( $E_{SC}$ ) can be calculated by integration and the critical value without any degradation or failure is regarded as the critical energy ( $E_{C}$ ).

$$E_{SC} = \int_0^{t_{SC}} V_{DS}(t) \cdot I_D(t) dt$$

(2.1)

Therefore, the short-circuit capability for a specific SiC MOSFET can be evaluated by increasing the drain bias voltage ( $V_{\rm DC}$ ) or short-circuit pulse duration ( $t_{\rm SC}$ ), and the maximum value of  $t_{\rm SC}$  is typically known as the maximum short-circuit withstanding time (SCWT). Apart from these, the short-circuit energy is also determined by many other parameters, such as gate driver voltage ( $V_{\rm GS}$ ) [69], gate resistance ( $R_{\rm G}$ ) [70] and case temperature ( $T_{\rm C}$ ) [71]. Among these, the  $V_{\rm GS}$  is a key factor to the  $E_{\rm SC}$ . When the applied positive  $V_{\rm GS}$  decreases, the MOS channel might not be fully turned on and this can lead to a lower saturation current ( $I_{\rm SC}$ ), which reduces the  $E_{\rm SC}$  and enables a larger short-circuit capability.

It is worth noting that the short-circuit capability of SiC MOSFETs is much worse than Si IGBTs. Fig. 2.2 shows an example of the short-circuit  $I_{\rm D}$  comparison between SiC MOSFET and Si IGBT with the same rated current and same test settings (except the  $V_{\rm GS}$  is set based on the rating values) [72]. The 1.2 kV/40 A SiC MOSFET (C2M0040120D) has only 8  $\mu$ s SCWT and the  $I_{\rm SC\_max}$  of 375 A (which is typically more than 6 times the rated current). In contrast, the Si IGBT (IKW40T120) has the SCWT of 38  $\mu$ s and it only shows around 200 A  $I_{\rm SC\_max}$ .

One main reason for weaker short-circuit capability in SiC MOSFETs is the much smaller chip size, which leads to a higher power density in short-circuit condition. The

Fig. 2.2. Short-circuit current comparison of the 1.2 kV/40 A SiC MOSFET and Si IGBT ( $V_{DC}$  = 600 V,  $T_C$  = 25 °C) [72].