Aalborg Universitet

#### Short-Circuit Instabilities in Silicon IGBTs and Silicon Carbide Power MOSFETs

Reigosa, Paula Diaz

DOI (link to publication from Publisher): 10.5278/vbn.phd.eng.00033

Publication date: 2017

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Reigosa, P. D. (2017). Short-Circuit Instabilities in Silicon IGBTs and Silicon Carbide Power MOSFETs. Aalborg Universitetsforlag. https://doi.org/10.5278/vbn.phd.eng.00033

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

### SHORT-CIRCUIT INSTABILITIES IN SILICON IGBTS AND SILICON CARBIDE POWER MOSFETS

BY PAULA DÍAZ REIGOSA

**DISSERTATION SUBMITTED 2017**

AALBORG UNIVERSITY DENMARK

### Short-Circuit Instabilities in Silicon IGBTs and Silicon Carbide Power MOSFETs

by

Paula Díaz Reigosa

A Dissertation Submitted to the Faculty of Engineering and Science at Aalborg University in Partial Fulfilment for the Degree of Doctor of Philosophy in Electrical Engineering

July 2017 Aalborg, Denmark

| Dissertation submitted:                               | July, 2017                                                     |

|-------------------------------------------------------|----------------------------------------------------------------|

| PhD supervisor:                                       | Prof. Francesco Iannuzzo<br>Aalborg University, Denmark        |

| Assistant PhD supervisor:                             | Prof. Frede Blaabjerg<br>Aalborg University, Denmark           |

| PhD committee:                                        | Prof. Kjeld Pedersen (Chairman)<br>Aalborg University, Denmark |

|                                                       | Prof. Ichiro Omura<br>Kyushu Institute of Technology, Japan    |

|                                                       | Dr. Caroline Andersson<br>ABB Corporate Research, Switzerland  |

| PhD Series:                                           | Faculty of Engineering and Science, Aalborg University         |

| Department:                                           | Department of Energy Technology                                |

| ISSN (online): 2446-1636<br>ISBN (online): 978-87-711 | 2-996-0                                                        |

Published by: Aalborg University Press Skjernvej 4A, 2nd floor DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Paula Díaz Reigosa

Printed in Denmark by Rosendahls, 2017

## Preface

This PhD thesis has been supported by the Center of Reliable Power Electronics (CORPE) and the Department of Energy Technology at Aalborg University. The center is supported by the *Danish Strategic Research Council* and *Det Obelske Familiefond*, especially the latter one receives my greatest gratitude. Acknowledgments are given to the Otto Mønsteds Fond, which provided me with financial support to participate in several conferences abroad.

This project has been supervised by Professor Francesco Iannuzzo and Professor Frede Blaabjerg from the Department of Energy Technology at Aalborg University. I would like to thank Professor Francesco Iannuzzo for his guidance and supervision during this work. His great knowledge in the field of power semiconductor devices was a very important source of information and inspiration during this thesis. I greatly appreciate our technical discussions, which contributed to the outcome of this PhD thesis. I would like to thank Professor Frede Blaabjerg for kindly accepting to be the co-supervisor of this thesis, giving me very valuable inputs as well as support and encouragement.

I would like to sincerely acknowledge Dr. Munaf Rahimo, who lead me in the activities that I have carried out during my Ph.D. study abroad, at ABB Switzerland Ltd. Semiconductors. His inspired suggestions and invaluable help, not only for the research part but also at career level, have led me to complete my thesis. With this occasion, I would also like to thank the entire R&D BiMOS team at ABB, that helped me with the understanding of the short-circuit oscillations in IGBTs - especial thanks to Arnost Kopta, Chiara Corvasce, Luca De Michielis and Samuel Hartmann.

I would like to express my gratitude to the examiners of this doctoral dissertation, Professor Kjeld Pedersen from Aalborg University, Professor Ichiro Omura from Kyushu Institute of Technology and Dr. Caroline Andersson from ABB.

I appreciate the fruitful collaborations with Dr. Rui Wu, Mr. Lorenzo Ceccarelli, Dr. Huai Wang, Dr. Haoze Luo, Professor Stig-Munk Nielsen, as well as all the group members in CORPE. I also want to thank my colleagues from the Department of Energy Technology for the friendly environment and enthusiastic help. I am thankful to all the staff at the Department of Energy Technology for their administrative support in aspects related to my study. Especially, John K. Pedersen, Tina Larsen, Corina Busk Gregersen, Casper Jørgensen and Bonnie Steffensen. For the assistance in the laboratory, Walter Neumayr, Mads Lund and Jan Krogh Christiansen.

I want to thank my closest friends, who I met in Aalborg during my Ph.D, for making my life easier, even during the difficult times: Alba Parareda, Jessica de Miguel, Nuria Fleta, Jaime Gómez, Asdro de la Torre, Sergio Fernández, Pau Mercadé, Paul Burlacu, Ignacio Rodríguez, Eloy Moldes and Laura García. Also, I want to thank my best friends from my home town, Marta Robla, Inmaculada Rubiera and Cristina Solar for encouraging me, not only during my Ph.D journey but also during my whole life. My deepest gratitude to my family and in particular to my parents, who have taught me to work hard for the things that I aspire to achieve.

At last but not least, I am truly thankful to Enrique Rodríguez, for being always beside me during the happy and hard moments, encouraging me in finishing this Ph.D thesis even when I had doubts. He has also helped me with technical discussions, being a valuable source with inputs from different angles but also helping me to disconnect from the working daily basis.

"Life is a constant oscillation between the sharp horns of a dilemma."

by H.L. Mencken

Paula Díaz Reigosa

July 5, 2017 Aalborg Øst, Denmark

# Abstract

Power semiconductor devices are exposed to different type of stresses over their lifetime, which they need to overcome in order to guarantee long-term reliable operation up to 20 years or more. One of the most typical stresses that the device must withstand is related to short-circuit events, which occur randomly during the component's life. Silicon-based IGBTs are good candidates for limiting the external current in case of a short-circuit event, however their robustness is frequently limited due to instabilities. In this Ph.D. thesis, the short-circuit performance of silicon-based IGBTs has been extensively evaluated, but since Wide-Band Gap (WBG) devices, such as SiC MOSFETs, are rapidly growing as a potential substitute of silicon-based technologies, its robustness with respect to short circuit is also addressed.

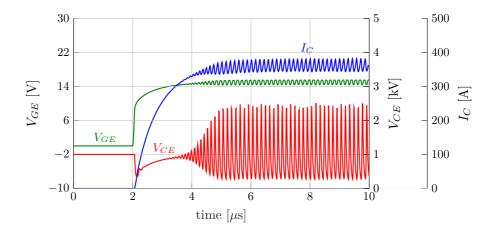

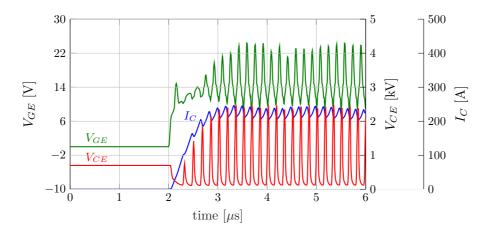

One of the most important experimental findings, and also the main motivation of this thesis, is that IGBTs exposed under specific operational conditions suffer from high frequency gate voltage oscillations (i.e., tens of MHz). Such oscillations are very critical in case that they become unstable, which will cause the catastrophic damage of the device. This failure type cannot be explained by any known short-circuit failure mechanism reported in the literature. Therefore, the aim was to investigate which factors could lead the IGBT into an unstable behaviour. This was achieved by using a combination of finite-element device simulations and experimental investigations of 1.2 kV, 1.7 kV, 3.3 kV, IGBTs with different cell technologies (i.e., planar, trench and BIGT).

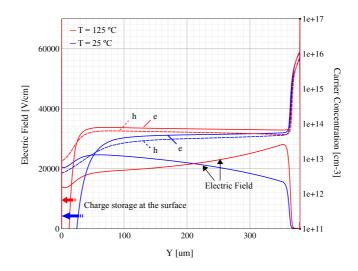

The experimental results demonstrate that the short-circuit ruggedness strongly depends on the applied DC-link voltage, this means that at low DC-link voltages the oscillations always occur, but at high DC-link voltages oscillations may not observed. A sensitivity analysis on the oscillating behavior's dependence revealed that there are some factors which help to minimize the oscillations: low gate-emitter voltage, high temperature and reduced stray inductance.

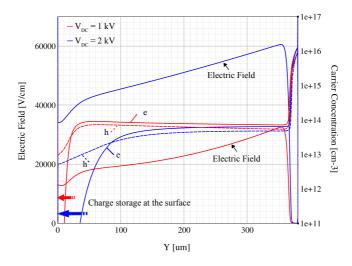

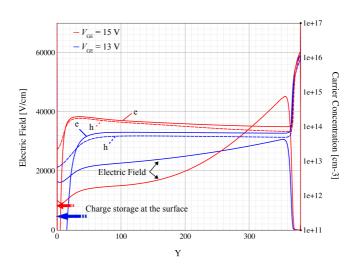

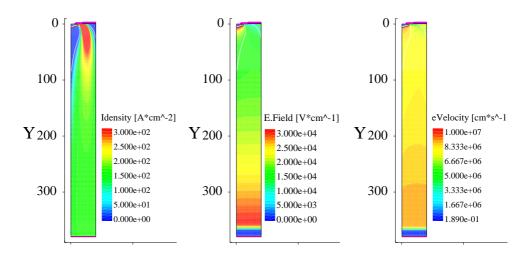

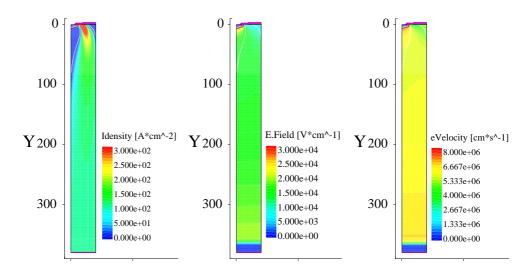

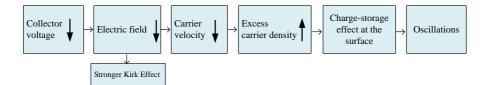

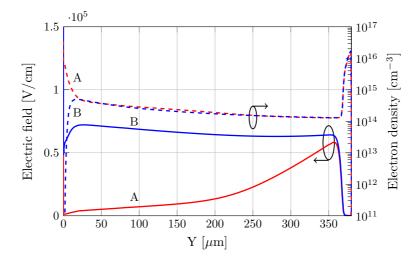

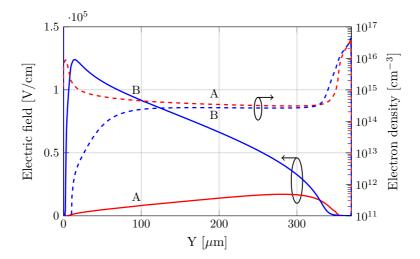

The root cause of the oscillation mechanism has been discovered to be as a consequence of a parametric oscillation, whose time-varying element is the Miller capacitance, leading to an amplification mechanism involving the external circuit. As a major achievement of this work, it has been possible to correlate the electric field distortions to gate capacitance variations, and thus, associate the capacitance variation with chargestorage effects occurring at the surface of the IGBT. The analysis has demonstrated that the primary cause for the excess electron density at the surface of the IGBT is the weak electric field in this region, driven by the Kirk Effect. The carrier drift velocities have a strong impact on the charge balance of the IGBT, especially at low DC-link voltages. Therefore, the low drift velocities will cause electron accumulation effects due to the weak electric field. On the other hand, at high DC-link voltages, the carrier drift velocities become saturated across the whole n-base, which means that the charge-storage effect is no longer present and the input capacitance becomes fixed.

# Dansk Abstrakt

Effektelektroniske komponenter anvendt i elektriske energisystemer udsættes for forskellige typer af stress igennem deres levetid og det er stress, som de skal modstå for at sikre en langsigtet pålidelig drift. Levetiden skal være op til 20 år og endda længere. En af de hyppigste belastninger, som komponenterne skal tåle er relateret til kortslutninger, som forekommer tilfældigt igennem komponenternes liv og som stresser dem. Silicium-baserede IGBT'ere er fremragende komponenter, som evner at begrænse strømmen i tilfælde af en kortslutning, men det er observeret at deres robusthed kan være begrænset på grund af ustabilitet. I denne Ph.D. afhandling er silicium-baserede IGBT'er primært blevet evalueret med hensyn til denne ustabilitet, men Wide Band Gap (WBG) baserede komponenter, såsom Silicium Carbide (SiC) MOSFET's er også studeret med hensyn til deres robusthed for kortslutninger, da disse komponenter vokser hurtigt på markedet som en potentiel erstatning for de silicium-baserede komponenter.

Et af de vigtigste eksperimentelle opdagelser, og som også er hovedmotivationen for denne afhandling er, at IGBT'er, når de udsættes for specifikke driftsbetingelser, oplever højfrekvente gate-spændings oscillationer (i 10-30 MHz området). Sådanne svingninger er meget kritiske, hvis de er ustabile, og de kan forårsage katastrofal skade på IGBT'ernr. Denne fejltype kan ikke forklares ved allerede kendte kortslutningsfejlmekanismer, som er rapporteret i litteraturen. Derfor har målet været at forstå fænomenet, der vil umiddelbart vil begrænse de undersøgte IGBT'eres kortslutningsevne i praksis. En bedre forståelse er blevet opnået ved at anvende en kombination af finite-element simuleringer af komponenternes strukturer og foretage eksperimentelle undersøgelser af 1.2 kV, 1.7 kV, 3.3 kV IGBT'ere, som har forskellige interne strukturer i deres opbygning.

De eksperimentelle resultater viser, at robustheden for kortslutningerne stærkt afhænger af den anvendte DC-spænding over IGBT'erne når de testes. Ved lave DC-spændinger forekommer svingningerne altid, mens ved høje DC-spændinger kan oscillationerne i mange tilfælde ikke observeres. En følsomhedsanalyse af oscillationernes afhængighed har vist, at der er nogle faktorer, der hjælper med at minimere oscillationerne såsom lav gate-emitter spænding, høj temperatur og lav spredningsinduktans i kredsen.

Hovedårsagen til oscillationerne har vist sig at være på grund af indgangs-kapacitansen i komponenten, der opfører sig stærkt ulineært og som giver en forstærkningsmekanisme, der også involverer det eksterne kredsløb. Som et vigtigt bidrag i dette arbejde har det været muligt at korrelere de elektriske felt fordelinger i komponenten med variationer i komponentens kapaciteter og relatere kapacitans-variationen med ladningerne i komponenten, der forekommer på overfladen af selve IGBT'en. Analysen har vist, at den primære årsag til de overskydende elektroner på overfladen af IGBT'en er det svage elektriske felt i denne region, som er drevet af Kirk Effekten. Ladningernes hastighed har en stærk indvirkning på IGBT'ens ladningsbalance, især ved lave DC-spændinger. Derfor vil lave ladnings hastigheder forårsage akkumuleringseffekter af elektronerne på overfladen af IGBT'erne på grund af det svage elektriske felt i denne region. På den anden side bliver ladningernes drifts-hastigheder ved høje DC-koblingsspændinger begrænset på tværs af hele n-basen i IGBT'en, hvilket betyder, at lagringseffekten ikke længere er til stede, og input-kapaciteten bliver konstant og den samlede kreds dermed bliver stabil.

# Contents

| Pref            | face  |                                            |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | iii                                                                                                                                                            |

|-----------------|-------|--------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{Abs}$  | tract |                                            |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\mathbf{v}$                                                                                                                                                   |

| Dan             | sk A  | bstrak                                     | t                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | vii                                                                                                                                                            |

| $\mathbf{List}$ | of F  | igures                                     |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xiii                                                                                                                                                           |

| $\mathbf{List}$ | of T  | ables                                      |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xxi                                                                                                                                                            |

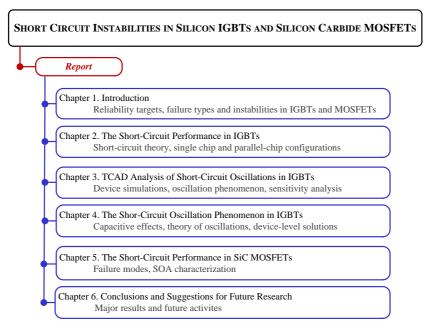

| 1               | Intr  | oducti                                     | on                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                              |

|                 | 1.1   | Backg:<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4 | Reliabilit<br>The shor<br>Overview<br>1.1.3.1<br>1.1.3.2<br>1.1.3.3<br>1.1.3.4 | I Motivation       Image: Structure         ty needs for power electronic devices       Image: Structure         t-circuit performance in IGBTs       Image: Structure         v of short-circuit instabilities in Si-IGBTs       Image: Structure         Latch-up       Image: Structure         Negative Differential Resistance (NDR)       Image: Structure         Current filamentation       Image: Structure         Short-circuit oscillations       Image: Structure         V of short-circuit instabilities in SiC MOSFETs       Image: Structure         Thermal runaway       Image: Structure | $     \begin{array}{c}       1 \\       4 \\       5 \\       5 \\       6 \\       7 \\       7 \\       7 \\       8 \\       9 \\       9     \end{array} $ |

|                 | 1.2   | Proble                                     | m Definit                                                                      | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10                                                                                                                                                             |

|                 | 1.3   | Thesis                                     | Objective                                                                      | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                                                                                                             |

|                 | 1.4   | Projec                                     | t Limitati                                                                     | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                                                                                                             |

|                 | 1.5   | Outlin                                     | e of the T                                                                     | 'hesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                                                                                                                             |

|                 | 1.6   | List of                                    | Publicati                                                                      | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                                                                                                                             |

| <b>2</b>        | The   | Short                                      | -Circuit                                                                       | Performance in IGBTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                                             |

|                 | 2.1   | Descri<br>2.1.1                            | -                                                                              | he Experimental Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\begin{array}{c} 17 \\ 17 \end{array}$                                                                                                                        |

|   |     | 2.1.2   | Description of the 2.4-kV/ 10-kA Non Destructive Tester (NDT) at CORPE | 18              |

|---|-----|---------|------------------------------------------------------------------------|-----------------|

|   |     | 2.1.3   |                                                                        | 10<br>21        |

|   | 2.2 | Short-0 | - •                                                                    | 22              |

|   |     | 2.2.1   | 1 0 1                                                                  | <br>23          |

|   |     | 2.2.2   |                                                                        | 25              |

|   |     | 2.2.3   |                                                                        | 26              |

|   |     | 2.2.4   | 1                                                                      | 27              |

|   |     | 2.2.5   | 0                                                                      | 29              |

|   |     |         | 1                                                                      | 29              |

|   |     |         |                                                                        | 30              |

|   |     |         | 0                                                                      | 31              |

|   | 2.3 |         | 1 1                                                                    | 32              |

|   |     | 2.3.1   | 1 0                                                                    | 32              |

|   |     | 2.3.2   | 0                                                                      | $\frac{33}{34}$ |

|   |     |         | 1                                                                      | 34<br>36        |

|   |     |         |                                                                        | 30<br>37        |

|   |     | 2.3.3   | 0                                                                      | 38              |

|   |     | 2.0.0   | 2.3.3.1 Short-circuit assessment of a modified version of the          | 00              |

|   |     |         |                                                                        | 38              |

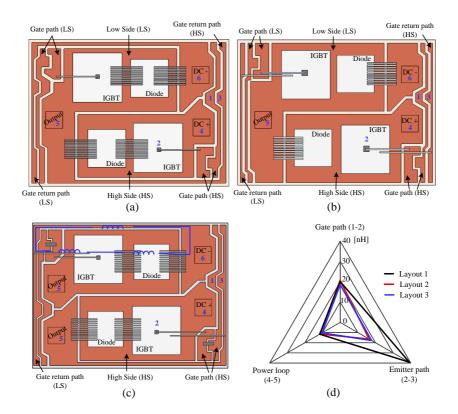

|   |     |         | 2.3.3.2 DCB substrate layout variations                                | 40              |

|   | 2.4 | Conclu  | sion of this chapter                                                   | 43              |

| 3 | TC  | AD Ser  | nsitivity Study of Short Circuit Oscillations in IGBTs                 | <b>45</b>       |

|   | 3.1 | IGBT    | Designs for 2-D Device Simulations                                     | 45              |

|   | 3.2 | The C   | urrent-Voltage Characteristic of the IGBT                              | 46              |

|   | 3.3 |         | 0                                                                      | 49              |

|   | 3.4 | Simula  | tion of the Short Circuit Oscillations                                 | 53              |

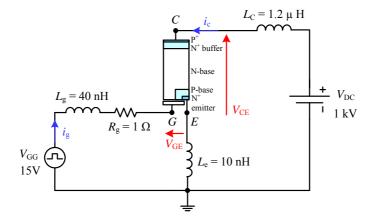

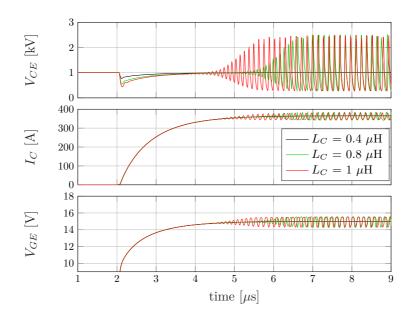

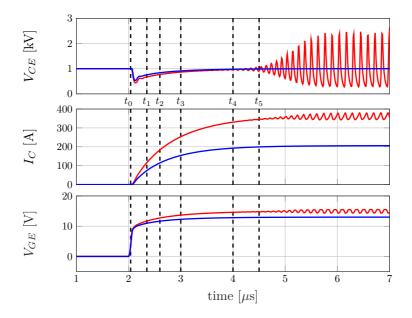

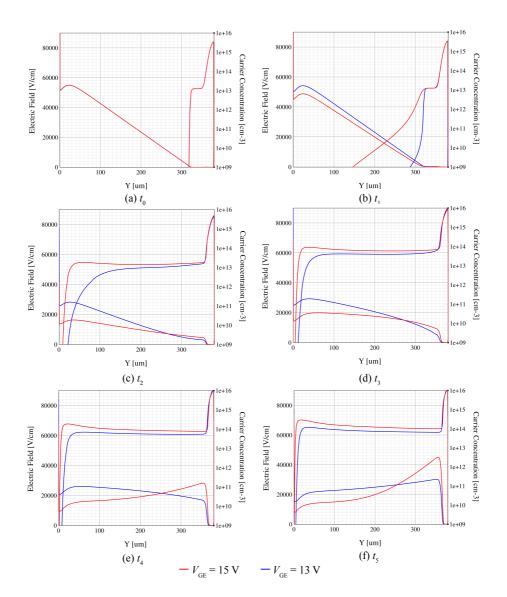

|   |     | 3.4.1   |                                                                        | 55              |

|   |     | 3.4.2   |                                                                        | 58              |

|   |     | 3.4.3   |                                                                        | 59              |

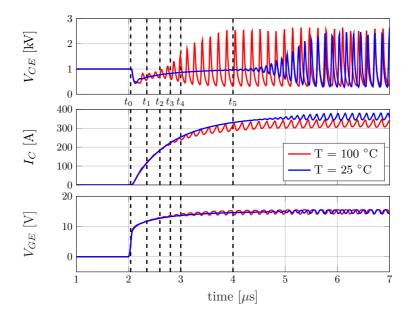

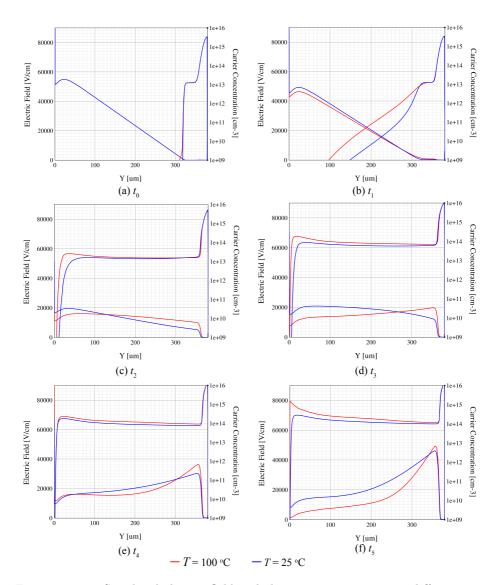

|   |     | 3.4.4   | Temperature effect                                                     | 63              |

|   | 3.5 | Discus  | sion of the Physical Mechanisms Leading to Oscillations                | 65              |

|   | 3.6 | Conclu  | sion of this Chapter                                                   | 71              |

| 4 | The | Short   | Circuit Oscillation Phenomenon in IGBTs                                | 73              |

|   | 4.1 | Introdu | uction                                                                 | 73              |

|   | 4.2 | Physic  | al Mechanisms during Short Circuit                                     | 74              |

|   |     |         |                                                                        |                 |

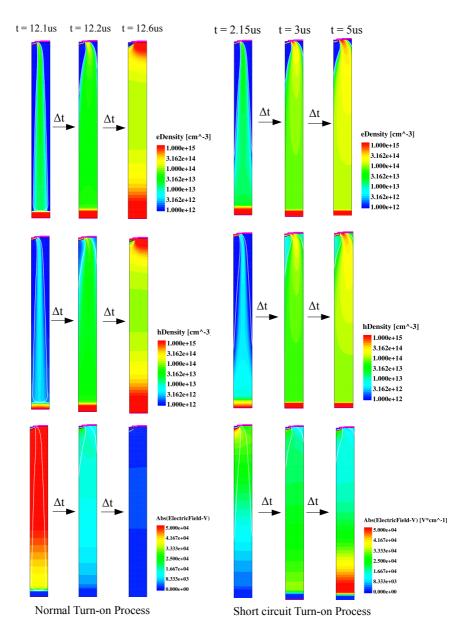

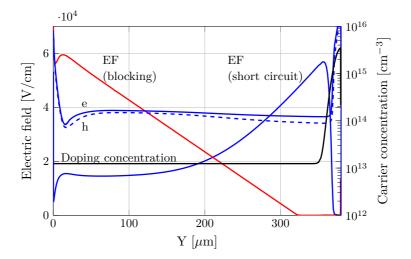

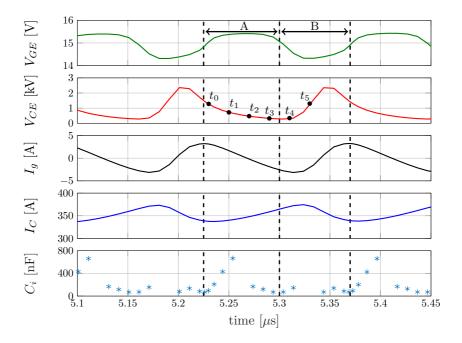

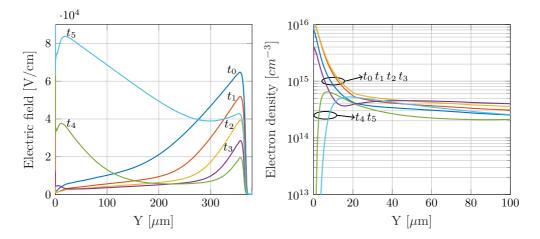

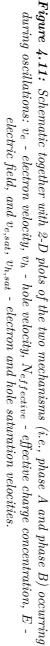

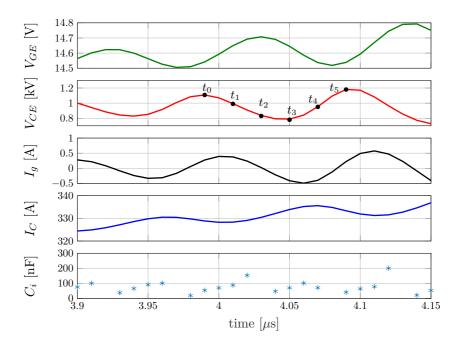

|          |       | 4.2.1            |              | ns during the oscilations                                              | 75         |

|----------|-------|------------------|--------------|------------------------------------------------------------------------|------------|

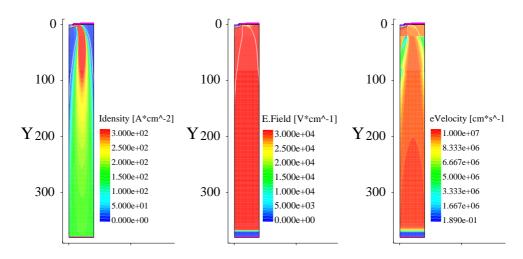

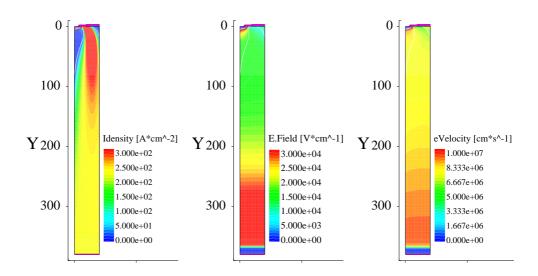

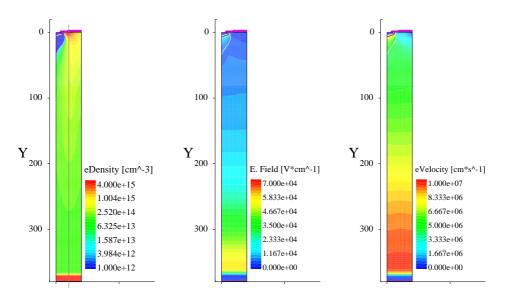

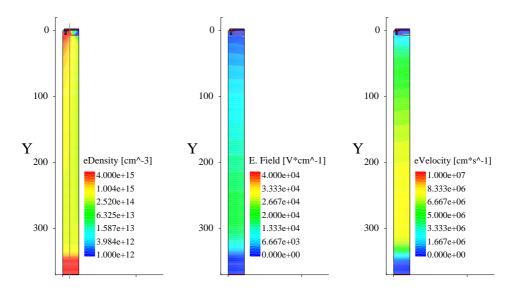

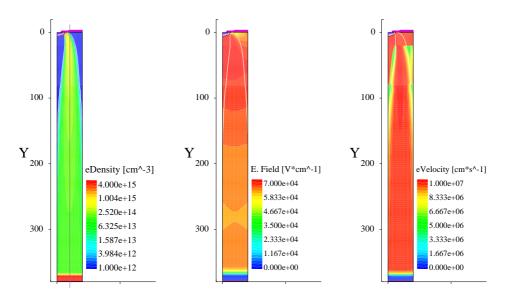

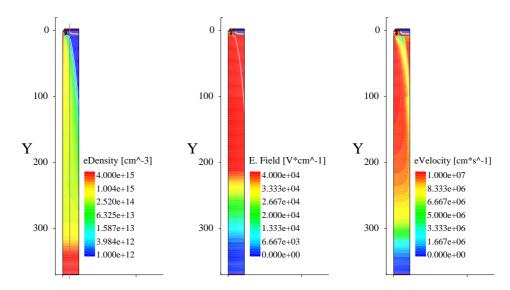

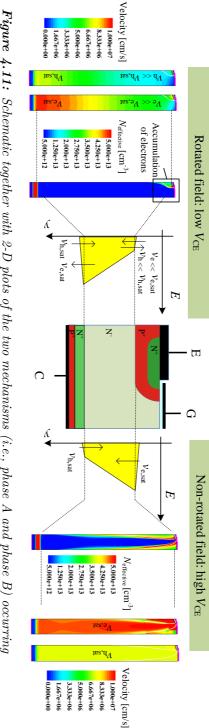

|          |       |                  |              | Phase A: charge-storage phase                                          | 76<br>79   |

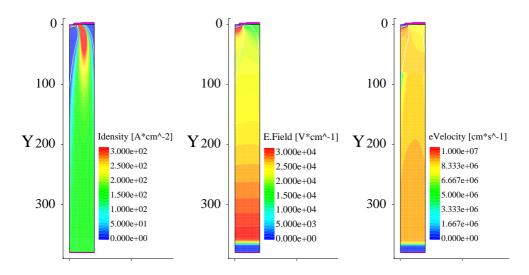

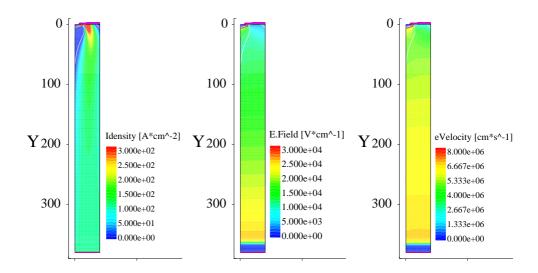

|          |       |                  |              | Comparison between phase A and phase B                                 | 79         |

|          |       | 4.2.2            |              | ns at the beginning of the oscillations                                | 83         |

|          | 4.3   | Param            | etric Oscil  | lations in IGBTs                                                       | 85         |

|          | 4.4   | Design           |              | for Improved Short Circuit Robustness                                  | 88         |

|          |       | 4.4.1            |              | dependence                                                             | 89         |

|          |       | 4.4.2            |              | On-state and turn-off losses                                           | 90<br>90   |

|          |       | 1. 1.2           |              | The electric field and charge balance during short circui              |            |

|          |       |                  | 4.4.2.2      | Blocking capability                                                    | 97         |

|          |       |                  |              | On-state and turn-off losses                                           | 97         |

|          | 4.5   | Conclu           | usion of thi | is Chapter                                                             | 99         |

| <b>5</b> | The   | Short            | -Circuit I   | Performance in SiC Power MOSFETs                                       | 101        |

|          | 5.1   |                  |              |                                                                        | 101        |

|          | 5.2   |                  |              | eration of Single-Chip SiC MOSFETs                                     | 102        |

|          |       | $5.2.1 \\ 5.2.2$ |              | wit assessment of 1.2 kV/ 36 A SiC MOSFET                              | 102        |

|          | 5.3   |                  |              | wit assessment of the $1.2 \text{ kV} / 90 \text{ A SiC MOSFET}$       | $105\\108$ |

|          | 0.5   | 5.3.1            | 1            | cuit assessment of the $1.2 \text{ kV}/300 \text{ A SiC power module}$ |            |

|          |       | 5.3.2            |              | cuit assessment of the $1.2 \text{ kV}/180 \text{ A SiC}$ power module |            |

|          | 5.4   | Short-           | Circuit Saf  | fe Operation Area Identification Criterion                             | 113        |

|          |       | 5.4.1            |              | cuit current-based criterion                                           | 113        |

|          |       | $5.4.2 \\ 5.4.3$ |              | age-based criterion                                                    | 115        |

|          | 5.5   |                  |              | cuit safe operation area                                               | 115        |

|          |       |                  |              | his Chapter                                                            | 117        |

| 6        |       |                  |              | aggestions for Future Research                                         | 119        |

|          | 6.1   |                  | •            |                                                                        | 119        |

|          | 6.2   |                  |              | Dns                                                                    | 121        |

|          | 6.3   | Propos           | sals for Fut | ture Work                                                              | 122        |

| 7        | App   | endix            |              |                                                                        | 125        |

| Refe     | erenc | es               |              |                                                                        | 133        |

|          |       |                  |              |                                                                        |            |

# List of Figures

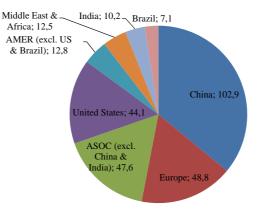

| 1.1          | Global trends in renewable energy investment 2015 (\$ billion). Source: FS-UNEP [7]                                                                                                                                          | 2       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

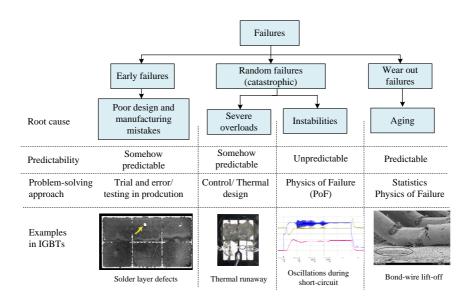

| 1.2          | Classification of failures in Power Electronics.                                                                                                                                                                             | 3       |

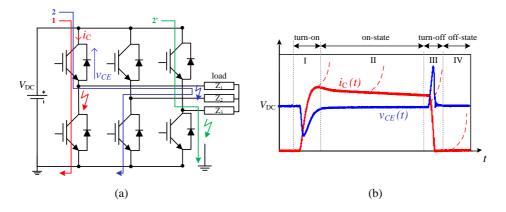

| 1.3          | The short-circuit condition applied to IGBTs: (a) short-circuit paths in a three-phase voltage source converter, and (b) types of failures during a short-                                                                   | -       |

|              | circuit event.                                                                                                                                                                                                               | 4       |

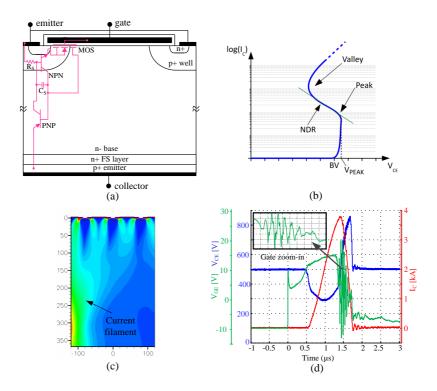

| 1.4          | Short-circuit instabilities in IGBTs: (a) IGBT structure highlighting the parasitic thyristor as main cause of latch-up, (b) the NDR region in the I-V curve [10], (c) a device simulation showing the current filamentation | т       |

|              | mechanism [12], and (d) oscillation phenomena during short-circuit events [13].                                                                                                                                              | 6       |

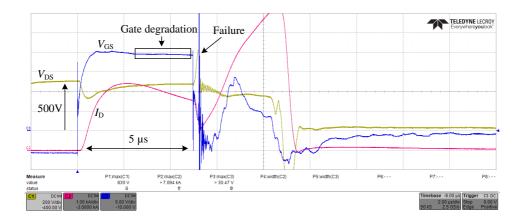

| 1.5          | Example of a gate-oxide breakdown failure of a 1.2 kV/ 300 A SiC MOSFET                                                                                                                                                      |         |

|              | power module performed at 500 V of drain-source voltage                                                                                                                                                                      | 8       |

| 1.6          | Example of a thermal runaway failure of a $1.2~\mathrm{kV}/$ 300 A SiC MOSFET                                                                                                                                                |         |

|              | power module performed at 600 V of drain-source voltage                                                                                                                                                                      | 9       |

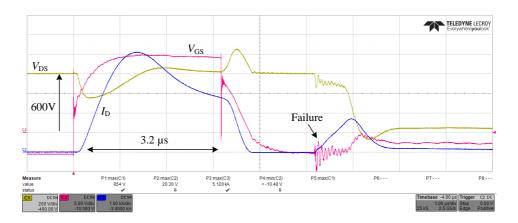

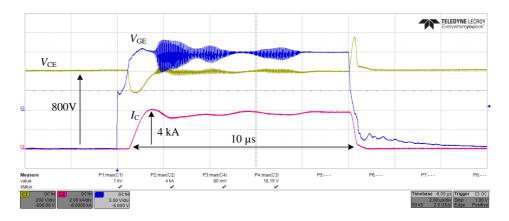

| 1.7          | Oscillations during a short circuit test of a $1.7 \text{ kV} / 1 \text{ kA IGBT}$ power module                                                                                                                              |         |

|              | performed at 800 V of collector voltage. Time scale: $2 \ \mu s/div$ ; gate voltage: 5 V/div; collector voltage: 200 V/div; collector current: 2 kA/div [13]                                                                 | 11      |

| 1.8          | Thesis structure and highlights of each part                                                                                                                                                                                 | 11 $14$ |

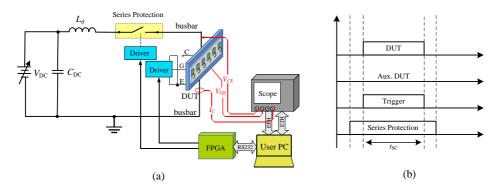

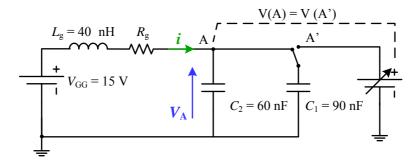

| 2.1          | The principle of the Non-Destructive Testing (NDT) system for short-circuit operation: (a) circuit schematic, and (b) time settings for short-circuit type                                                                   |         |

|              | $1 \ [46]. \ \ldots \ $                                                                                                                              | 18      |

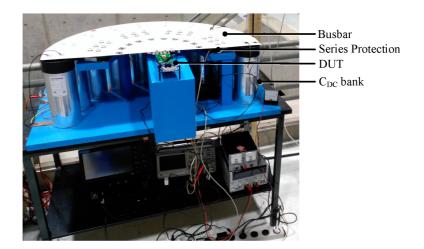

| 2.2          | A picture of the 2.4-kV/ 10-kA Non-Destructive Testing (NDT) test bench                                                                                                                                                      |         |

|              | for repetitive short-circuit tests [36]                                                                                                                                                                                      | 19      |

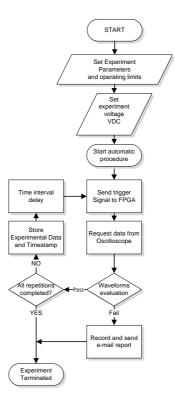

| 2.3          | A screen-shot of the Graphical User Interface to perform the repetitive short-                                                                                                                                               |         |

| ~ .          |                                                                                                                                                                                                                              | 20      |

| $2.4 \\ 2.5$ | Flowchart of the implemented repetitive short-circuit sequence [47]<br>Picture of the dynamic substrate test bench at ABB for performing short-                                                                              | 20      |

|              | circuit tests.                                                                                                                                                                                                               | 22      |

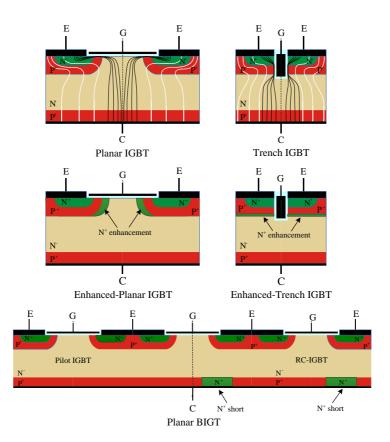

| 2.6          | Evolution of the IGBT cell design technology.                                                                                                                                                                                | 23      |

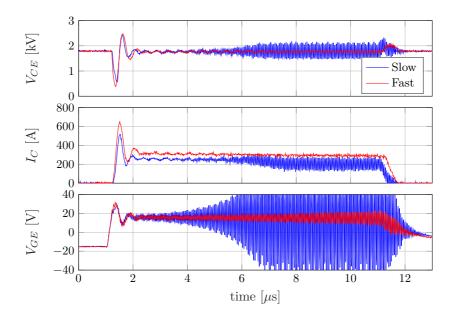

| 2.7  | Short-circuit of 3.3-kV SPT <sup>+</sup> planar IGBTs having different switching speeds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $R_{q,on} = 2.2 \ \Omega, L_{\sigma} = 530 \text{ nH} \text{ and } T_{case} = 25 \text{ °C.} \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24  |

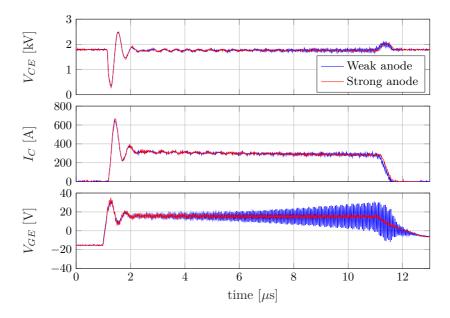

| 2.8  | Short-circuit of 3.3-kV SPT <sup>+</sup> planar IGBTs with different anode doses. $R_{q,on}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | = 2.2 $\Omega$ , L <sub><math>\sigma</math></sub> = 530 nH and T <sub>case</sub> = 25 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25  |

| 2.9  | Short-circuit capability of a 3.3-kV SPT <sup>+</sup> trench IGBT. $R_{g,on} = 2.2 \ \Omega, L_{\sigma}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | = 530 nH and $T_{case} = 25$ °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26  |

| 2.10 | Short-circuit capability of a 3.3-kV SPT <sup>+</sup> planar BIGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28  |

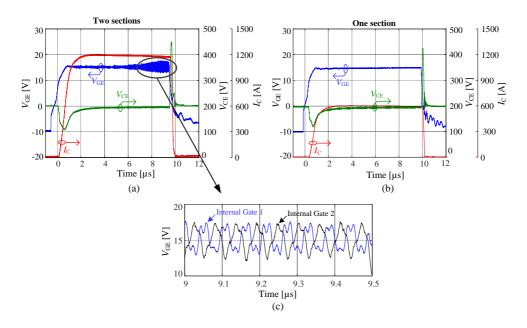

|      | Short-circuit capability of a 3.3-kV SPT <sup>+</sup> trench BIGT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28  |

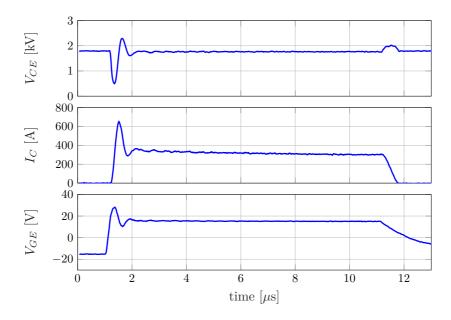

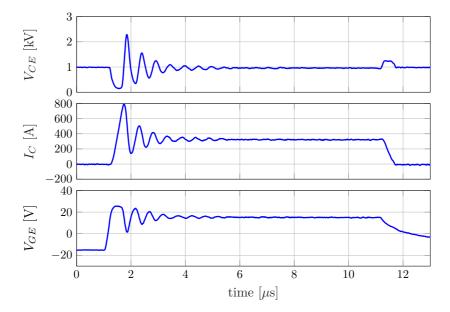

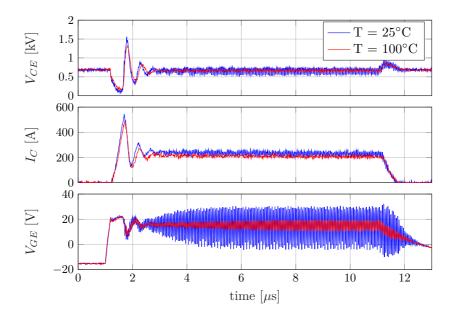

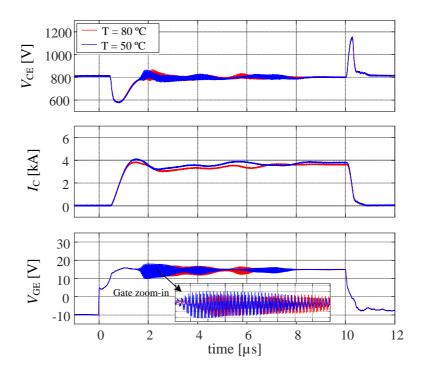

| 2.12 | Temperature effect on the short-circuit oscillations of a 3.3-kV SPT <sup>+</sup> planar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | IGBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29  |

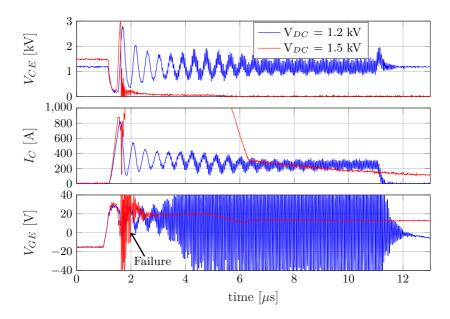

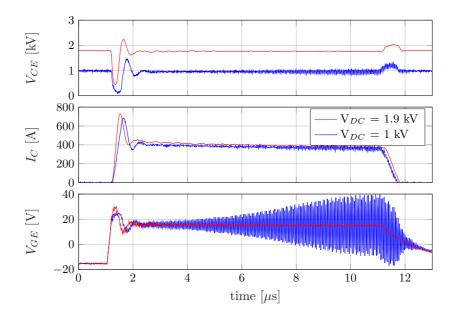

| 2.13 | DC-link voltage effect on the short-circuit oscillations of a 3.3-kV SPT <sup>+</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | planar IGBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30  |

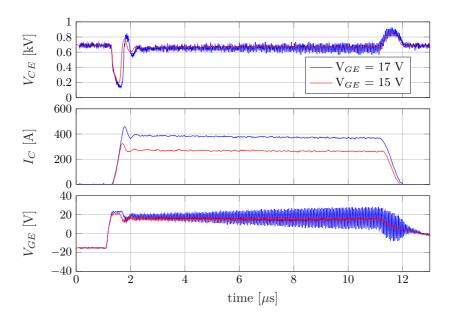

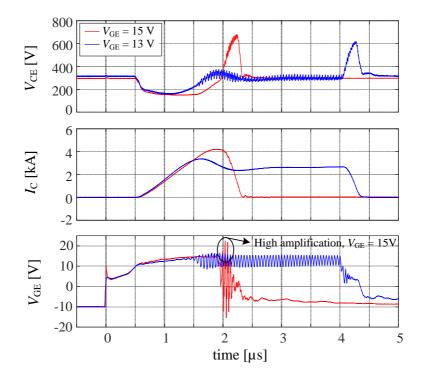

| 2.14 | Gate voltage effect on the short-circuit oscillations of a $3.3$ -kV SPT <sup>+</sup> planar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | IGBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31  |

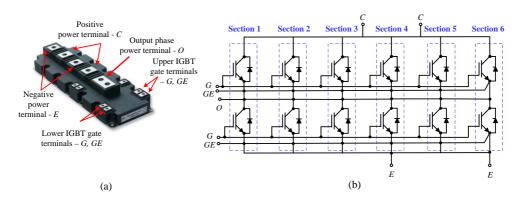

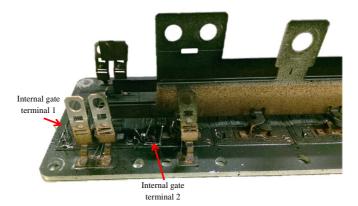

| 2.15 | The 1.7-kV/ 1-kA IGBT power module investigated to compare different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | manufacturer's short-circuit performance: (a) packaging geometry and ter-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|      | minals, (b) the half-bridge internal structure [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33  |

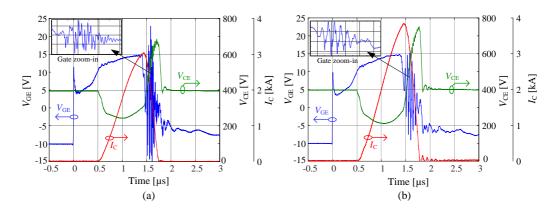

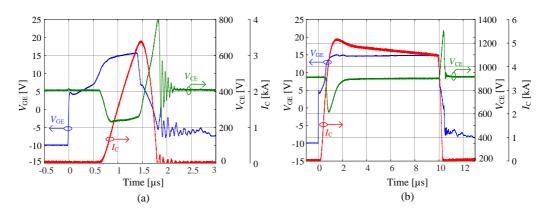

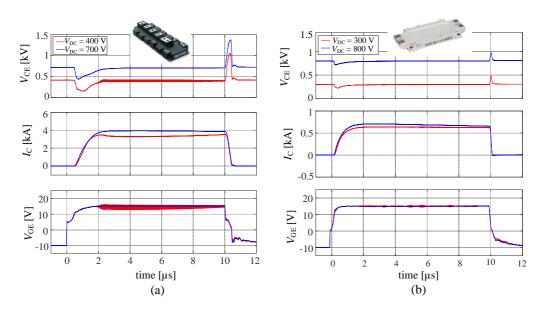

| 2.16 | Short-circuit oscillation phenomena observed in the 1.7-kV/ 1-kA IGBT $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

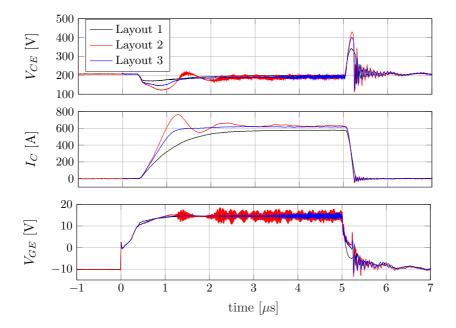

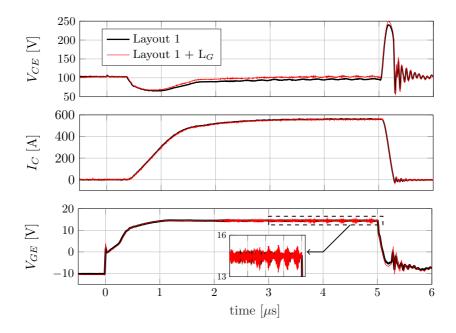

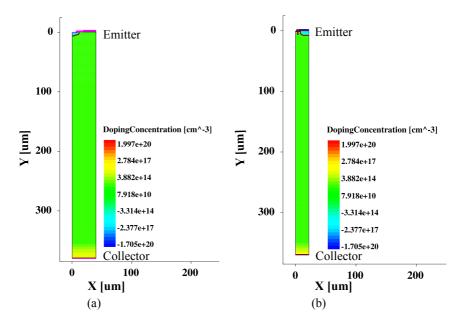

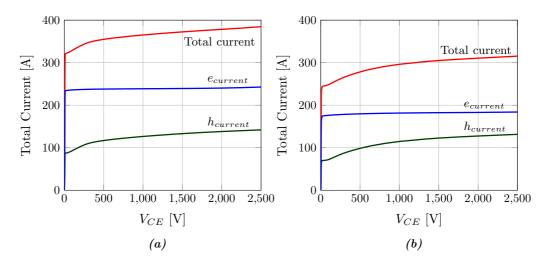

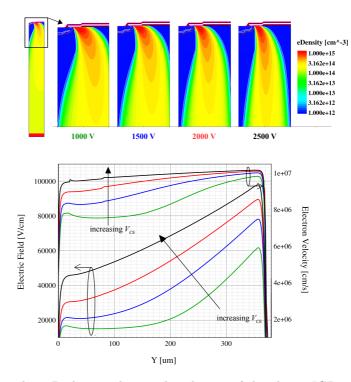

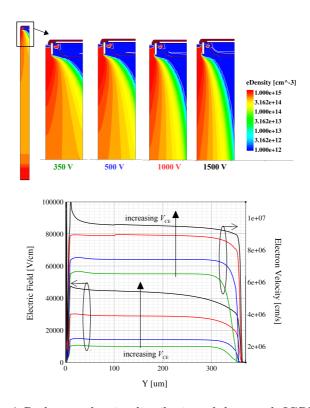

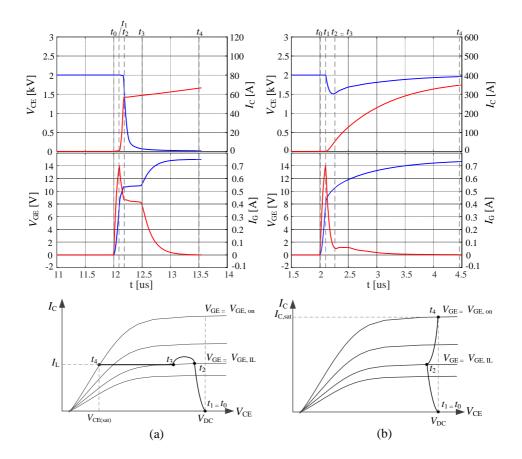

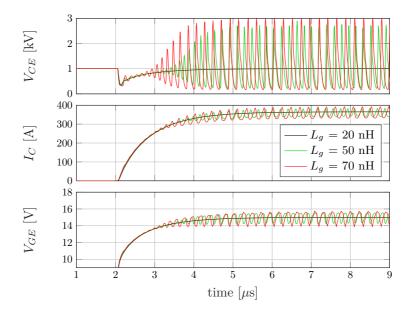

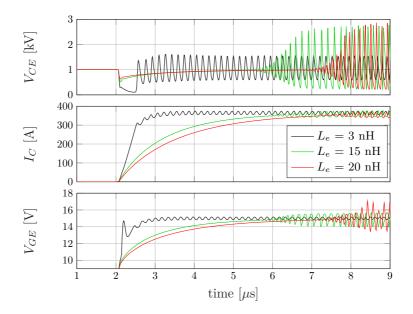

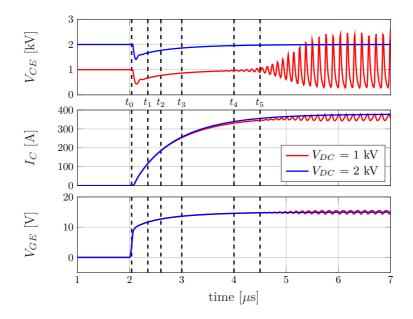

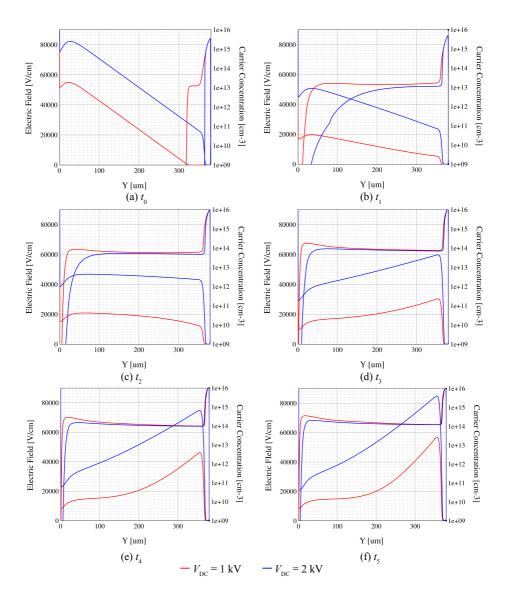

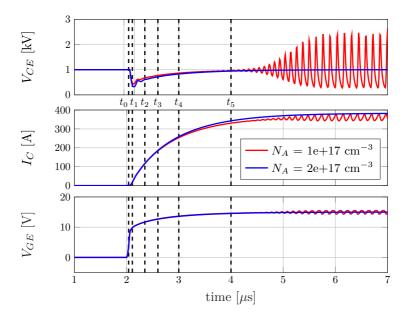

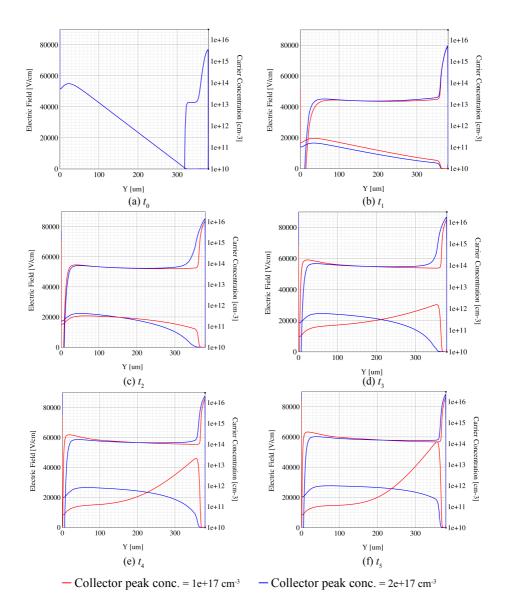

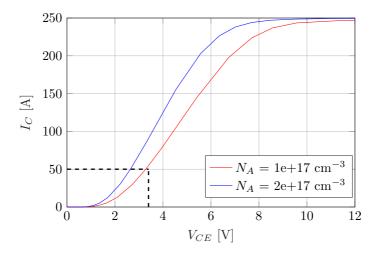

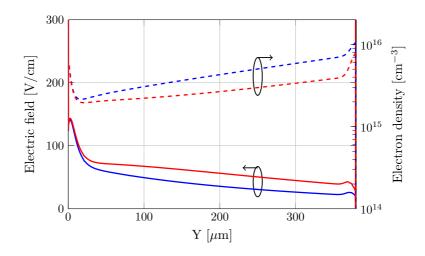

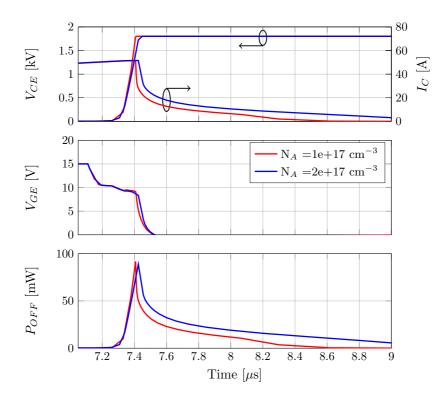

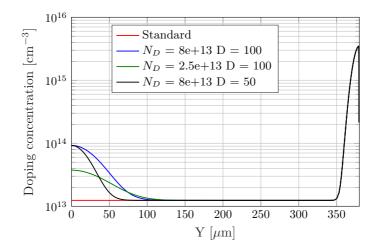

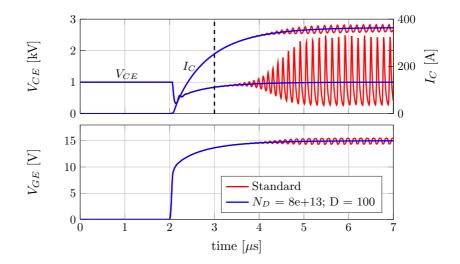

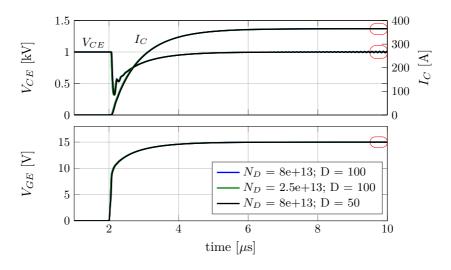

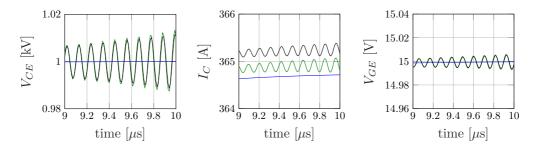

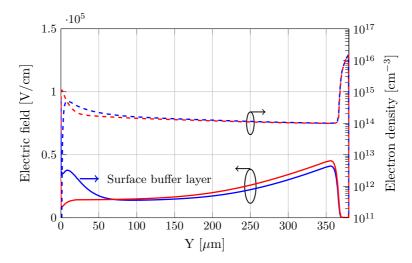

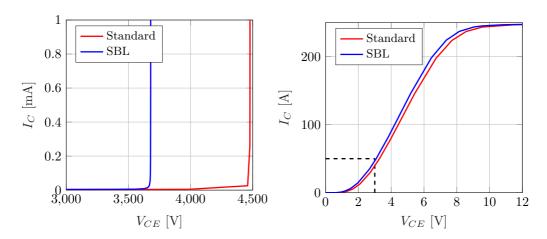

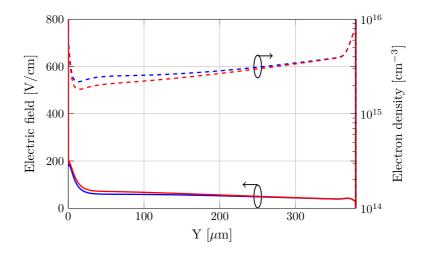

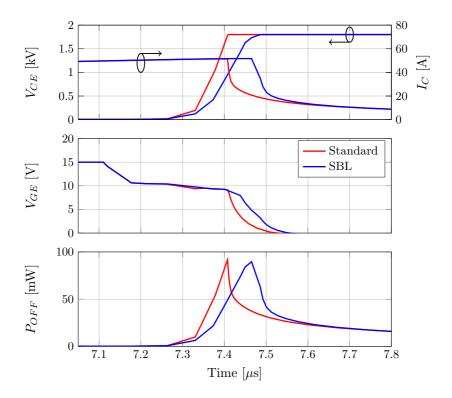

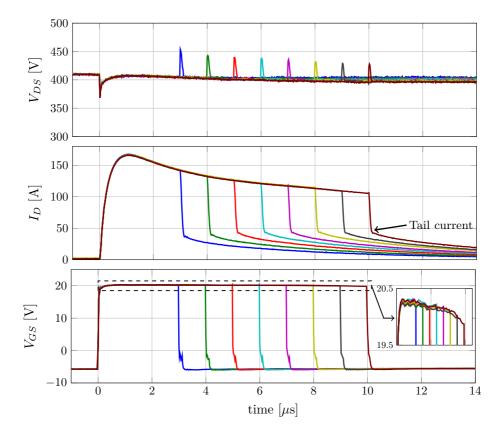

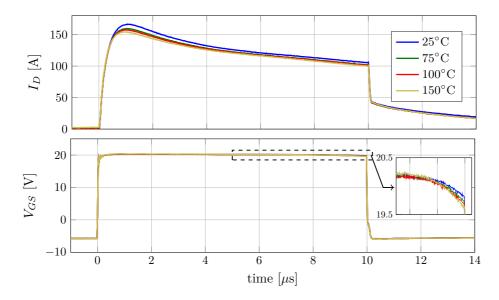

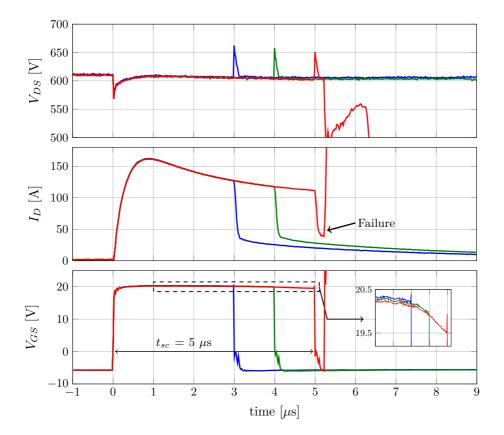

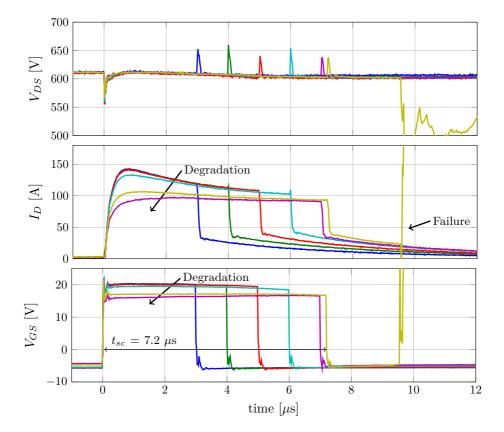

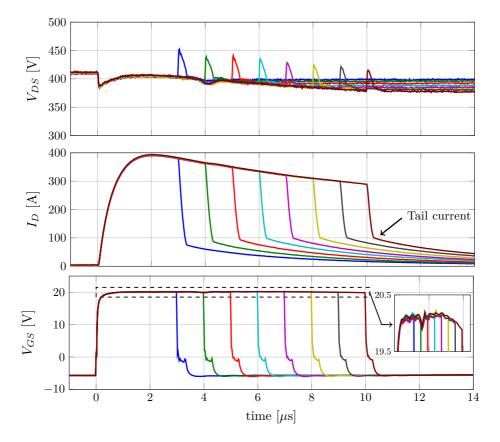

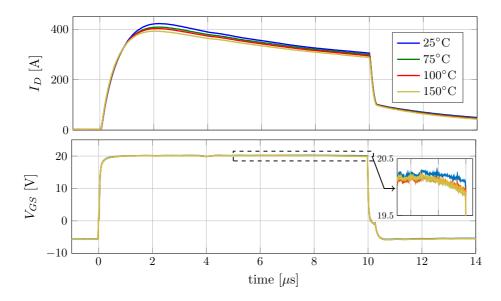

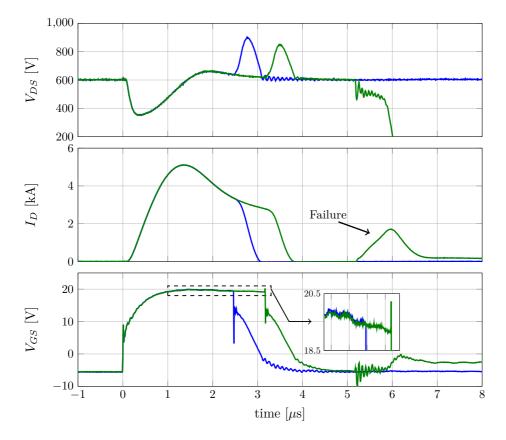

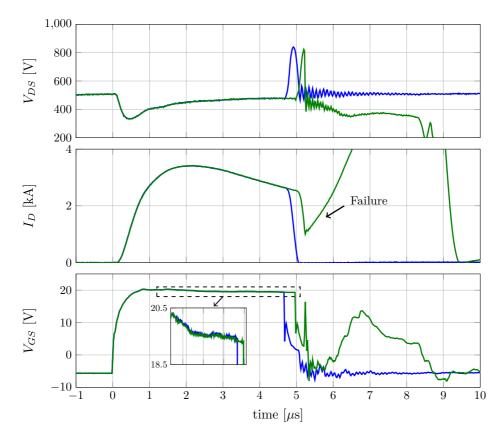

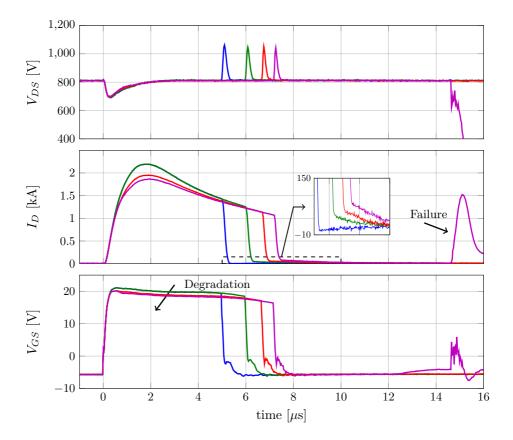

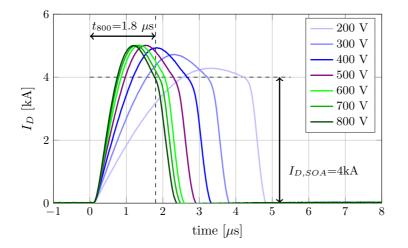

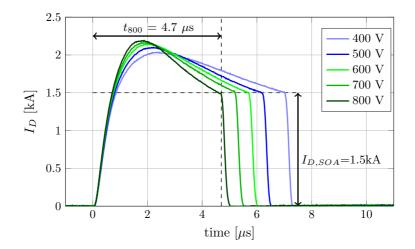

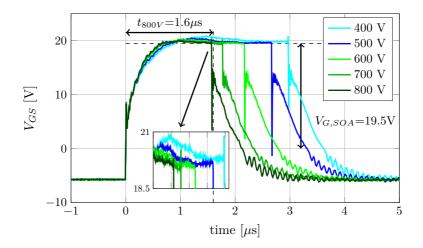

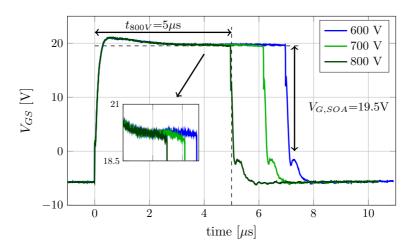

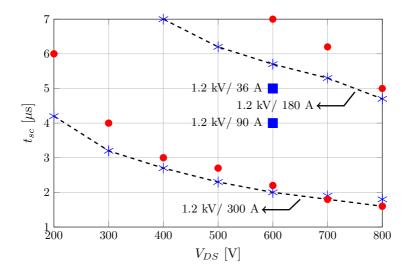

|      | power module: (a) manufacturer A, and (b) manufacturer B. Testing condi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |