Aalborg Universitet

### Control and Optimization of Modular Multilevel Cascaded Statcom Converters for Offshore Wind Application

Tanaka, Takaaki

Publication date: 2018

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Tanaka, T. (2018). Control and Optimization of Modular Multilevel Cascaded Statcom Converters for Offshore Wind Application. Aalborg Universitetsforlag.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## CONTROL AND OPTIMIZATION OF MODULAR MULTILEVEL CASCADED STATCOM CONVERTERS FOR OFFSHORE WIND APPLICATION

BY TAKAAKI TANAKA

**DISSERTATION SUBMITTED 2018**

AALBORG UNIVERSITY Denmark

### CONTROL AND OPTIMIZATION OF MODULAR MULTILEVEL CASCADED STATCOM CONVERTERS FOR OFFSHORE WIND APPLICATION

by

Takaaki Tanaka

Dissertation submitted to Faculty of Engineering and science

at Aalborg University in 2018

•

| Dissertation submitted:   | December 2018                                           |

|---------------------------|---------------------------------------------------------|

| PhD supervisor:           | Prof. Frede Blaabjerg,<br>Aalborg University            |

| Assistant PhD supervisor: | Associate Prof. Huai Wang,<br>Aalborg University        |

| PhD committee:            | Professor Zhe Chen (chairman)<br>Aalborg University     |

|                           | Professor Hirofumi Akagi<br>Tokyo Tech                  |

|                           | Professor Leonids Ribickis<br>Riga Technical University |

| PhD Series:               | Faculty of Engineering and Science, Aalborg University  |

| Department:               | Department of Energy Technology                         |

| ISSN (online): 2446-1636  | 0.363-1                                                 |

ISBN (online): 978-87-7210-363-1

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Takaaki Tanaka

Printed in Denmark by Rosendahls, 2018

# CV

Takaaki Tanaka was born in Kyoto, Japan in 1987. He received the B.E. degree in electrical engineering from National Institute of Technology, Maizuru College, Kyoto, Japan, in 2010 and the M.E. degree in electrical engineering from Nagaoka University of Technology, Niigata, Japan, in 2012. From 2012, he is a researcher at the Corporate R&D Headquarters, Fuji Electric, Co., Ltd., Tokyo, Japan.

Mr. Tanaka was a visiting researcher with the Center of Reliable Power Electronics (CORPE) at Aalborg University, Aalborg, Denmark from December 2015 to November 2017. His research interests include power electronics and its applications such as in renewable energies, transportation, reliability, power density, WBG devices and circuit architecture. He is a member of the Institute of Electrical and Electronics Engineers (IEEE) and the Institute of Electrical Engineers of Japan (IEEJ).

# ENGLISH SUMMARY

The capacity for renewable energy generation has continued to grow in the last decade, and it is expected to become 2.5 TW in 2020. In accordance with constructions of large-scale renewable energy generation systems such as solar photovoltaic and wind power plants, stricter grid codes under both normal operation and grid fault conditions are demanded by Transmission System Operators (TSO) in most countries.

Large-scale offshore wind power generation is significantly growing and becoming one of the major renewable energy sources in Europe with strong wind and shallow sea areas, because of the advantages such as constant and high wind velocity as well as extensive offshore sites, which reduces the generation cost. However, the generated electrical power has to be transmitted to the Point of Common Coupling (PCC) onshore by long-distance submarine cables, which arise a large amount of reactive power if a Medium to High Voltage Alternating Current (MVAC-HVAC) transmission system is selected. In order to compensate enough reactive power and to satisfy the grid codes, SVC or STATCOMs have to be installed on the onshore side of the wind power plant.

The Modular Multilevel Cascade Converters (MMCC) family are promising solutions in the case of high-voltage and high-power STATCOM applications. They have significant advantages, compared to the conventional two-level or three-level voltage source converters, such as lower harmonic distortions, transformer-less configuration at medium voltage level, and modular/ redundant design. Nevertheless, voltage-balancing for a large number of DC-link capacitors in converter cells are still challenging to be achieved for MMCCs, especially under asymmetrical grid faults. In addition, the principal dc-link capacitor voltage ripple with second-order at grid frequency in each converter cell makes the required capacitor size large compared to the conventional converters.

Many authors have proposed useful control schemes and design methods for each type of MMCC solutions until now. However, the optimum MMCC solution for the STATCOM application is still an open question because a comprehensive comparison between each type of MMCC solution has not been done. In addition to the total cost and volume of the MMCC solutions, the asymmetrical reactive power delivering capability under grid faults becomes more and more important for the STATCOM application. Furthermore, it seems that capacitor voltage ripple reduction methods for the MMCC solutions have not been considered enough yet.

This thesis clarifies the performances of potentially used four configurations of the MMCC family with SSBC, SDBC, DSCC, and DSBC for the STATCOM in large-scale offshore wind power plants, with special focus on asymmetrical Low Voltage

Ride Through (LVRT) capability under grid faults. Then, a capacitor voltage ripple reduction method by using a third harmonic zero-sequence current for one type of MMCC-SDBC is proposed and the benefits have been verified.

All achievements in this thesis have been validated by a practical designed 80 MVar/ 33 kV MMCC based STATCOM simulation result. These contributions have also been published in 2 journal papers and 4 conference papers.

# DANSK RESUME

Den installerede kapacitet af den vedvarende energi-systemer er fortsat voksende og den forventes at blive 2,5 TW i 2020. I lyset af den stigen kapacitet af store vedvarende energiproduktionssystemer såsom solcelle- og vind-kraftværker bliver der specificeret stadig strengere tilslutnings-krav af Transmission System Operators (TSO) i de fleste lande både under normal drift og ved net-fejl.

Storskala vindkraftproduktion til havs vokser markant og bliver en af de største vedvarende energikilder i Europa, der har glimrende vindforhold og samtidig lavvands havområder, hvilket giver fordele såsom konstant og høj vindhastighed, hvilket reducerer prisen for den producerede energi. Den genererede elektriske energi skal dog overføres til land via lange kabler i havet, og typisk er det baseret på vekselspændings-teknologien (AC). For at kompensere tilstrækkelig for den reaktive effekt, der opstår på grund af kablerne og for at tilfredsstille net-kravene, skal SVC'ere eller STATCOMs installeres på onshore side af vindkraftværkerne.

Den Modulære Multi-level Cascaded Converter (MMCC) omformer familie er en lovende løsning i tilfælde af høj-spænding og høj-effekt STATCOM applikationer. Konverterne i denne familie har betydelige fordele i forhold til de konventionelle effekt-omformere, som er baseret på to eller tre niveau omformer-systetmer, idet de har lavere harmonisk forvrængning, er en transformer fri konfiguration på mellemspændingsniveau og har samtidig et modulært / redundant design. Ikke desto mindre er spændingsbalanceringen i sådanne konvertere med et stort antal DCkondensatorer i konverter-cellerne stadig en udfordring for MMCC'erne, især under asymmetriske net-fejl. Hertil kommer at kondensatorerne har en spændingsvariation af anden harmonisk, som gør den nødvendige kondensator-størrelse relativ stor i forhold til de konventionelle omformere.

Mange har indtil nu foreslået forskellige kontrol systemer og design-metoder for hver type of MMCC-løsningerne. Den optimale MMCC-løsning til STATCOMapplikationen er dog stadig et åbent spørgsmål, idet en detaljeret sammenligning mellem hver type MMCC-løsning endnu ikke er blevet udført. Ud over de samlede omkostninger og volumen af MMCC-løsningerne bliver den asymmetriske reaktive strømafgivelsesevne under net-fejl en mere og mere vigtig parameter for STATCOM-applikationerne. Endvidere ser det ud til, at kondensator spændingsvariationen i MMCC løsningerne ikke er blevet studeret nok endnu.

Denne PhD afhandling sammenligner fire potentielt anvendelige konfigurationer af MMCC-familien, som er SSBC, SDBC, DSCC og DSBC, som skal agere som STATCOM i store offshore vindkraftværker med særlig fokus på drift under asymmetriske lave spændinger (LVRT), som typisk opstår under net-fejl. Der foreslås også en kondensator spændings-variations reduktionsmetode, der kan i

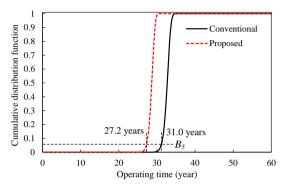

praksis reducere kondensator størrelsen med 20 % og dette realiseres ved at anvende en harmoniske nul-sekvensstrøm og dette princip er specielt velegnet i typen MMCC-SDBC. En detaljeret design er udført i afhandlingen, såvel som utallige simuleringer er udført til at underbygge den foreslåede metode.

Alle resultater i denne afhandling er blevet afprøvet på en praktisk designet 80 MVar / 33 kV MMCC baseret STATCOM model. Resultaterne er udover i PhD-afhandlingen blevet offentliggjort i 2 tidsskriftsartikler (IEEE) og 4 konferenceartikler.

# ACKNOWLEDGEMENTS

This thesis is a summary of the collaboration research project entitled "Control and Optimization of Modular Multilevel Cascade STATCOM Converters for Offshore Wind Application". The research work is supported by the 2-year study abroad program of Fuji Electric Co., Ltd., Japan. Acknowledgements are given to the company as well as Aalborg University, who provided me a research environment in Denmark.

This research project was carried out under the supervision of Prof. Frede Blaabjerg and Prof. Huai Wang from the Department of Energy Technology, Aalborg University, Denmark, and Prof. Ke Ma from the Department of Electrical Engineering, Shanghai Jiao Tong University, China. I would like to show my deepest gratitude to them, for their professional and precise advice with their openmindedness and earnestness during the collaboration research. Their supervision affects my research style, which I do believe will continuously support me in my future career.

I would like to say thank you to all my colleagues from the Department of Energy Technology for the warm environment. Best wishes to my friend - Changwoo Yoon, Yu-Hsing Chen, Yanfeng Shen, Haoran Wang, Uimin Choi, Hammam Soliman, Zhongxu Wang, Hamid Soltani, and all the other friends. The life hence became more interesting and colorful. My appreciations are extended to John K. Pedersen, Tina Larsen, Corina Busk Gregersen, Eva Janik and Casper Jørgensen for their assistance in different ways.

I would also like to acknowledge with much appreciation to Prof. Toshihisa Shimizu, Tokyo Metropolitan University, Japan, Prof. Jun-ichi Itoh, Nagaoka University of Technology, Japan, and Dr. Yasushi Matsumoto, Fuji Electric Co., Ltd, for introducing me to my supervisors, and Dr. Akio Toba, Fuji Electric Co., Ltd, for kind understanding of my Ph.D. study.

Last but not least, I am deeply thankful to my parents and my sister for their endless love and support.

Takaaki Tanaka

September, 2018

Tokyo, Japan

# TABLE OF CONTENTS

| Chapter 1. Introduction                                                                        | 1 |

|------------------------------------------------------------------------------------------------|---|

| 1.1. Background and motivation1                                                                |   |

| 1.1.1. Market – Offshore wind power generation 1                                               |   |

| 1.1.2. Modern large-scale offshore wind power plants 2                                         |   |

| 1.1.3. STATCOM technology for offshore wind power plants                                       |   |

| 1.1.4. Fault Ride Through requirements                                                         |   |

| 1.2. Research questions and objectives                                                         |   |

| 1.3. Limitations on this study                                                                 |   |

| 1.4. Outline of the thesis 10                                                                  |   |

| 1.5. List of publications                                                                      |   |

| Chapter 2. Modeling and control of the MMCC solutions for offshore wind<br>STATCOM Application |   |

| 2.1. Typical offshore wind power plant and system fault scenarios [J1] 13                      |   |

| 2.1.1. System configuration [19]13                                                             |   |

| 2.1.2. Reactive curret requirement                                                             |   |

| 2.1.3. Grid fault scenarios [19]14                                                             |   |

| 2.2. Comparison of key devices for each type of the MMCC-based STATCOM [J1]                    |   |

| 2.2.1. Basic structure and power semiconductor devices [19] 20                                 |   |

| 2.2.2. Modulation type and frequencies for PWM [19]                                            |   |

| 2.2.3. Interconnection inductance [19]                                                         |   |

| 2.2.4. DC-link capacitance [19] 22                                                             |   |

| 2.3. Control strategy for the MMCC-based STATCOMs                                              |   |

| 2.3.1. Output current control block                                                            |   |

| 2.3.2. Phase Locked Loop (PLL) block                                                           |   |

| 2.3.3. Overall voltage control block                                                           |   |

| 2.3.4. DC-link capacitor voltage balancing control block                                       |   |

| 2.4. Thermal modeling for the power devices [19]                                               |   |

| 2.5. Summary                                                                                   |   |

| Chapter 3. Theoretical operation of MMCC family under asymmetrical reactive power compensation [J1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1. Definition of the grid fault voltage and current on Bus C [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.2. MMCC-SSBC with zero-sequence ac voltage [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 3.3. MMCC-SDBC with zero-sequence ac current [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 3.4. MMCC-DSCC with circulating dc current [19] 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.5. MMCC-DSBC with circulating dc current [19]43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 3.6. Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Chapter 4. Performance benchmark of the MMCC solutions [J1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

| 4.1. Electrical and thermal simulation modeling [19] 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

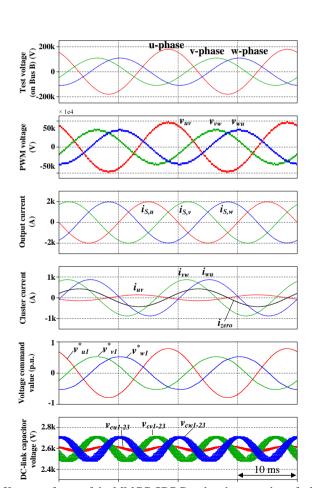

| 4.2. Electrical and thermal simulations of the MMCC-SSBC [19] 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

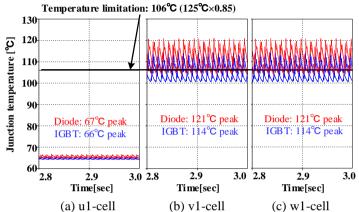

| 4.3. Electrical and thermal simulations of the MMCC-SDBC [19] 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

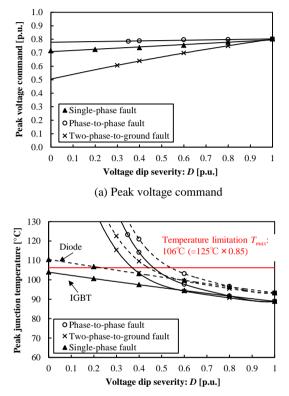

| 4.4. Electrical and thermal simulations of the MMCC-DSCC [19] 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

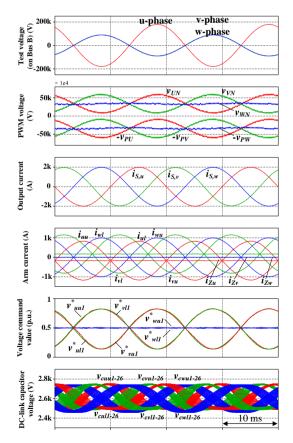

| 4.5. Electrical and thermal simulations of the MMCC-DSBC [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4.6. Performance comparison between the MMCC family [19] 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 4.7. Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Chapter 5. A dc-link capacitor voltage ripple reduction method for an MMCC-<br>SDBC [J2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63 |

| SDBC [J2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63 |

| <b>SDBC [J2]</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63 |

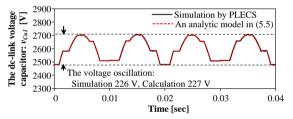

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63 |

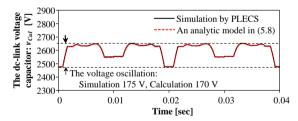

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65         5.2.2. Proposed capacitor voltage ripple reduction method [43]       68                                                                                                                                                                                                                                                                                                                                                       | 63 |

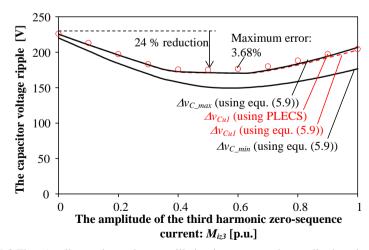

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65         5.2.2. Proposed capacitor voltage ripple reduction method [43]       68         5.2.3. DC-link capacitor voltage ripple [43]       69                                                                                                                                                                                                                                                                                         | 63 |

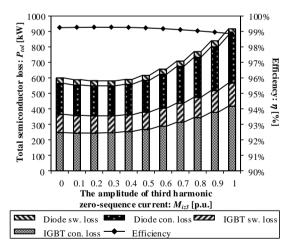

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65         5.2.2. Proposed capacitor voltage ripple reduction method [43]       68         5.2.3. DC-link capacitor voltage ripple [43]       69         5.3. Power semiconductor losses and junction temperatures [43]       70                                                                                                                                                                                                         | 63 |

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65         5.2.2. Proposed capacitor voltage ripple reduction method [43]       68         5.2.3. DC-link capacitor voltage ripple [43]       69         5.3. Power semiconductor losses and junction temperatures [43]       70         5.4. Capacitor bank design [43]       74                                                                                                                                                        | 63 |

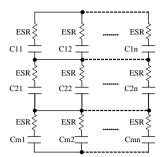

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65         5.2.2. Proposed capacitor voltage ripple reduction method [43]       68         5.2.3. DC-link capacitor voltage ripple [43]       69         5.3. Power semiconductor losses and junction temperatures [43]       70         5.4. Capacitor bank design [43]       74         5.4.1. Capacitor bank structure [43]       74                                                                                                  | 63 |

| SDBC [J2]       63         5.1. Introduction [43]       63         5.2. The theoretical behavior of the dc-link capacitor voltage [43]       64         5.2.1. Conventional operation [43]       65         5.2.2. Proposed capacitor voltage ripple reduction method [43]       68         5.2.3. DC-link capacitor voltage ripple [43]       69         5.3. Power semiconductor losses and junction temperatures [43]       70         5.4. Capacitor bank design [43]       74         5.4.1. Capacitor bank structure [43]       74         5.4.2. Thermal stress of each MPPF-Cap. [43]       75                                    | 63 |

| <ul> <li>SDBC [J2]</li> <li>5.1. Introduction [43]</li> <li>5.2. The theoretical behavior of the dc-link capacitor voltage [43]</li> <li>64</li> <li>5.2.1. Conventional operation [43]</li> <li>65</li> <li>5.2.2. Proposed capacitor voltage ripple reduction method [43]</li> <li>68</li> <li>5.2.3. DC-link capacitor voltage ripple [43]</li> <li>69</li> <li>5.3. Power semiconductor losses and junction temperatures [43]</li> <li>70</li> <li>5.4. Capacitor bank design [43]</li> <li>74</li> <li>5.4.1. Capacitor bank structure [43]</li> <li>74</li> <li>5.4.2. Thermal stress of each MPPF-Cap. [43]</li> <li>78</li> </ul> |    |

| SDBC [J2]635.1. Introduction [43]635.2. The theoretical behavior of the dc-link capacitor voltage [43]645.2.1. Conventional operation [43]655.2.2. Proposed capacitor voltage ripple reduction method [43]685.2.3. DC-link capacitor voltage ripple [43]695.3. Power semiconductor losses and junction temperatures [43]705.4. Capacitor bank design [43]745.4.1. Capacitor bank structure [43]745.4.2. Thermal stress of each MPPF-Cap. [43]785.5. Summary79                                                                                                                                                                             | 63 |

| 3. Future work |

|----------------|

|----------------|

# **TABLE OF FIGURES**

| Figure 1-1 World renewable electricity capacity and forecast                       |

|------------------------------------------------------------------------------------|

| Figure 1-2 Offshore wind power capacity and forecast by region                     |

| Figure 1-3 Offshore wind power plants constructed from 2010 to 2015 with different |

| transmission systems                                                               |

| Figure 1-4 System configurations of typical offshore wind power plants             |

| Figure 1-5 Reactive power compensators. (a) Shunt reactor/Static condenser. (b)    |

| Static Var Compensator (SVC). (c) Static Synchronous Compensator (STATCOM).        |

|                                                                                    |

| 5<br>E 160 E 11 E 11 E                                                             |

| Figure 1-6 Candidates for high voltage and high power STATCOM configuration        |

| for offshore wind power plant (Per-phase circuit is depicted)                      |

| Figure 1-7 Reactive power requirements of large-scale generating plants under grid |

| fault (low voltage ride through) [19]                                              |

| Figure 2-1 A typical offshore wind power plant with an MMCC-STATCOM and            |

| shunt reactor [19] 14                                                              |

| Figure 2-2 Circuit configurations of the MMCC family for a STATCOM application     |

| [19]                                                                               |

| Figure 2-3 Overall control block for the MMCC STATCOM solutions                    |

| Figure 2-4 Output current control block diagram for the STATCOMs used in the       |

| thesis                                                                             |

| Figure 2-5 Overall voltage control block diagram for dc-capacitors                 |

| Figure 2-6 Power flow of the dc-link capacitor voltage control for the MMCC        |

| solutions                                                                          |

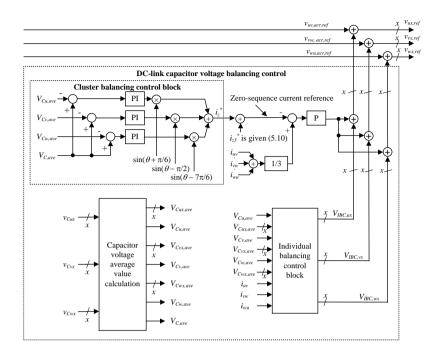

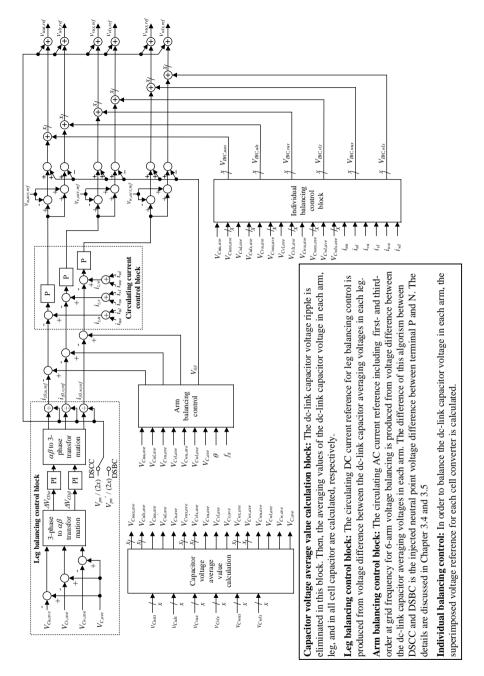

| Figure 2-7 DC-link capacitor voltage balancing control block for MMCC-SSBC [36].   |

| 27                                                                                 |

| Figure 2-8 DC-link capacitor voltage balancing control block for MMCC-SDBC         |

| [26]                                                                               |

| Figure 2-9 DC-link capacitor voltage balancing control block for MMCC-DSCC and     |

| DSBC [39]                                                                          |

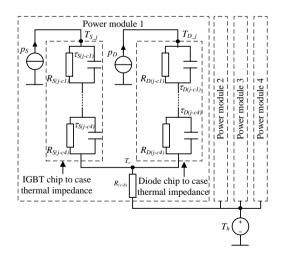

| Figure 2-10 Thermal network model between power semiconductor chip and heat        |

| sink on each cell converter [19]                                                   |

|                                                                                    |

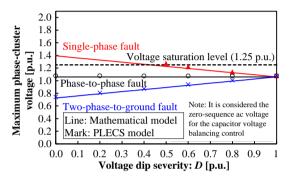

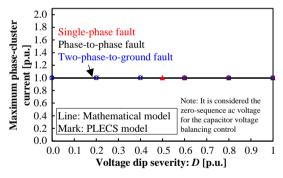

| Figure 3-1 Maximum-phase-cluster output of the MMCC-SSBC corresponding to          |

| various grid fault scenarios [19]                                                  |

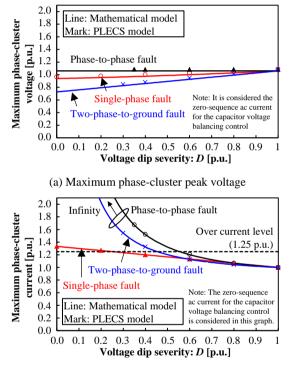

| Figure 3-2 The Maximum-phase-cluster output of the MMCC-SDBC corresponding         |

| to various grid fault scenarios [19]                                               |

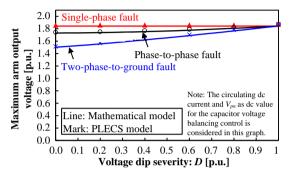

| Figure 3-3 Maximum arm output of the MMCC-DSCC corresponding to various            |

| grid fault scenario [19]                                                           |

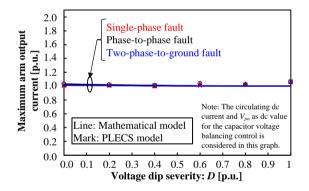

| Figure 3-4 Maximum arm output of the MMCC-DSBC corresponding to various            |

| grid fault scenario [19] 44                                                        |

| Figure 4-1 Key waveforms of the MMCC-SSBC under single-phase fault with a dip      |

| severity <i>D</i> of 0.5 p.u [19]                                                  |

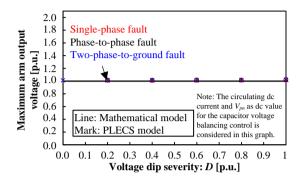

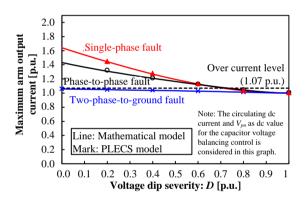

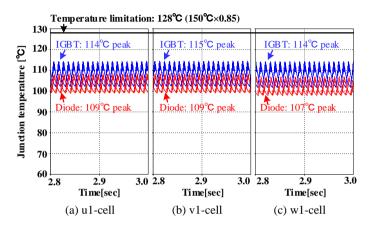

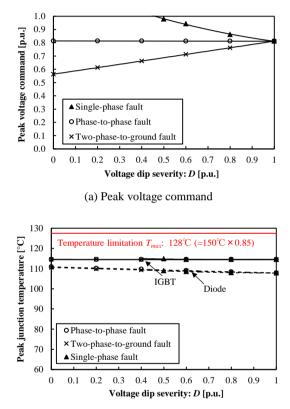

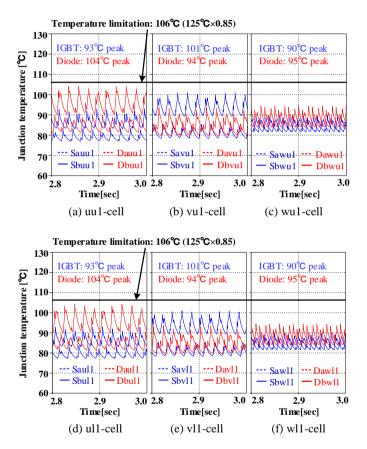

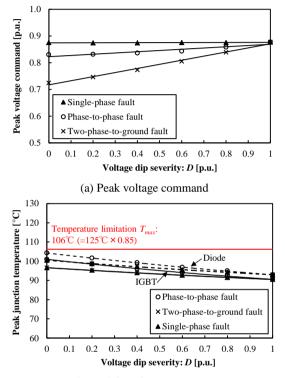

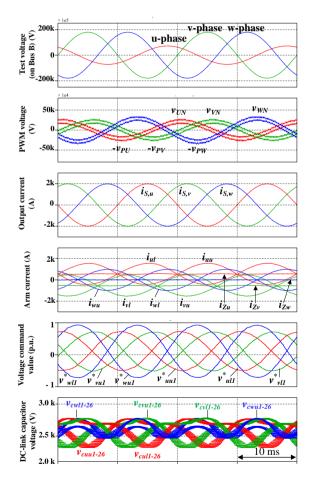

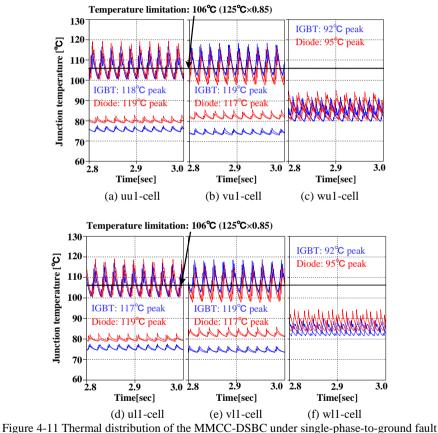

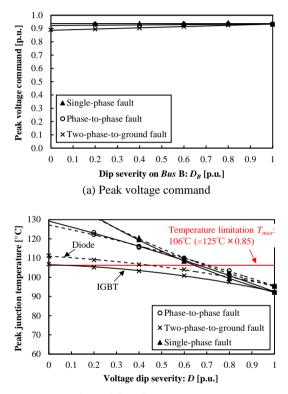

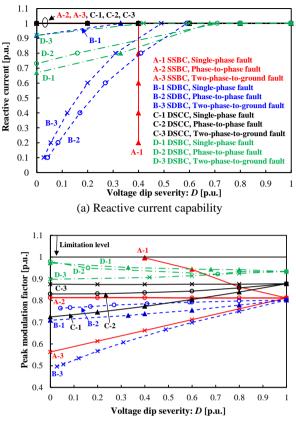

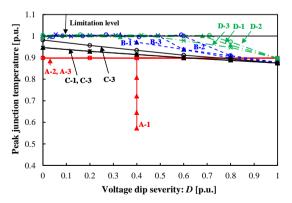

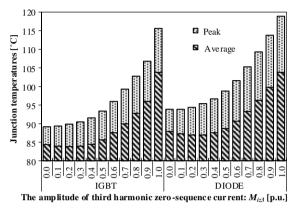

| Figure 4-2 Thermal distribution of the MMCC-SSBC under single-phase fault with<br>dip severity D of 0.5 p.u. [19]48Figure 4-3 Electrical-thermal simulations of the MMCC-SSBC at different dip<br>severities [19]49Figure 4-4 Key waveforms of the MMCC-SDBC under phase-to-phase fault with a<br>dip severity D of 0.4 p.u. [19]50Figure 4-5 Thermal distribution of the MMCC-SDBC under phase-to-phase fault<br>with a dip severity D of 0.4 p.u [19]51Figure 4-6 Electrical-thermal simulations of the MMCC-SDBC at different dip<br>severities [19]52Figure 4-7 Key waveforms of the MMCC-DSCC under phase-to-phase fault with a<br>dip severity D of 0 p.u. [19]53Figure 4-8 Thermal distribution of the MMCC-DSCC under phase-to-phase fault<br>with a dip severity D of 0 p.u. [19]54Figure 4-9 Electrical-thermal simulations of the MMCC-DSCC at different dip<br>severities [19]54Figure 4-10 Key waveforms of the MMCC-DSBC under single-phase-to-ground<br>fault with a dip severity D of 0.4 p.u [19]56Figure 4-11 Thermal distribution of the MMCC-DSBC under single-phase-to-<br>ground fault with a dip severity D of 0.4 p.u [19]57Figure 4-12 Electrical-thermal simulations of the MMCC-DSBC under single-phase-to-<br>ground fault with a dip severity D of 0.4 p.u [19]57Figure 4-12 Electrical-thermal simulations of the MMCC-DSBC at different dip<br>severities [19]58Figure 4-13 Reactive current compensation capability of the MMCCs for different<br>dip severities [19]58 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

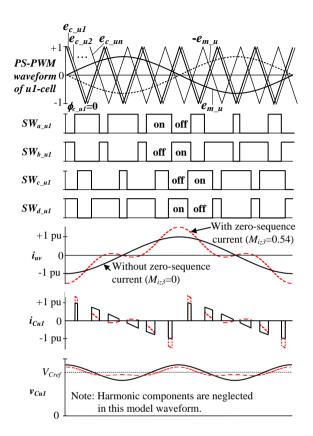

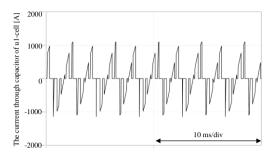

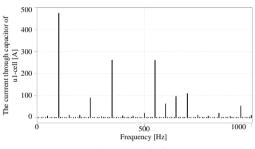

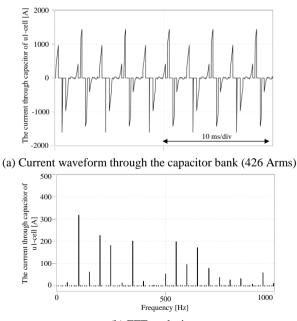

| Figure 5-1 The PWM waveforms and current in the u1-cell for the MMCC-SDBC circuit [43]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

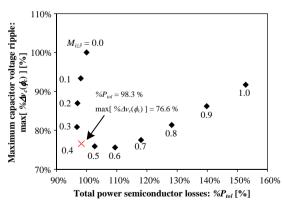

| $M_{iz3}$ [43]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# **CHAPTER 1. INTRODUCTION**

### **1.1. BACKGROUND AND MOTIVATION**

### 1.1.1. MARKET - OFFSHORE WIND POWER GENERATION

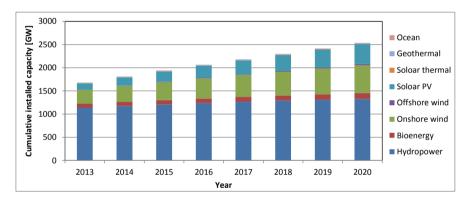

Globally, renewables are the largest electrical power source of net additions to power capacity over the medium term. They account for 62% of the expansion by 2020 and grow faster than fossil fuels and nuclear. Second to the hydropower, the wind power generation has the largest share in renewable energy source, and has continued to grow in the last decade, with a 532 GW installed capacity, including 20 GW from offshore wind turbines, by the end of 2018 as shown in Figure 1-1 [1].

Figure 1-1 World renewable electricity capacity and forecast.

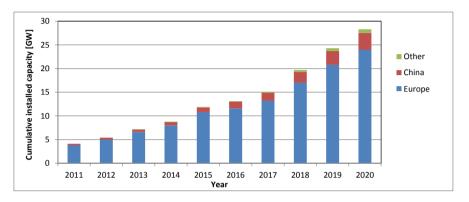

Large-scale offshore wind power generation is significantly growing (see Figure 1-2) and become one of the major renewable energy sources in Europe, which is having strong wind and shallow sea areas and giving the advantages of constant and high wind velocity as well as Europe also has extensive offshore areas. All together will reduce the generation cost of wind energy [1], [2].

Figure 1-2 Offshore wind power capacity and forecast by region.

#### 1.1.2. MODERN LARGE-SCALE OFFSHORE WIND POWER PLANTS

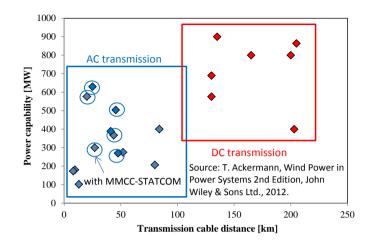

Offshore wind turbine plants can be placed close to and in long distance to shore. Figure 1-3 plots large-scale offshore wind power plants constructed between 2010 and 2015, depending on the power capacity and electrical transmission distance [3]. The power capacity range of each offshore wind power plant seems to be between a hundred and up to a thousand MW and even more in some areas. The electrical transmission distance from the offshore wind farm to Point of Common Coupling (PCC) located at the onshore side seems to be in the range from a few km to 200 km. It is noted that two types of electrical transmission system exist, which are Alternating Current (AC) transmission system, and Direct Current (DC) transmission system. It highly depends on the transmission distance and other site conditions such as water depth and also transmission system voltage. The breakeven distance seems to be around 100 km as far as the recent existing projects. The system configurations of the two types offshore wind power plants are described as follows.

Figure 1-3 Offshore wind power plants constructed from 2010 to 2015 with different transmission systems.

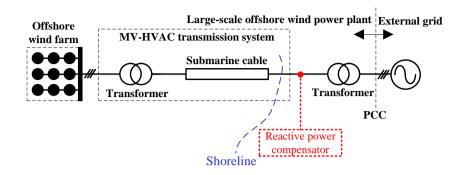

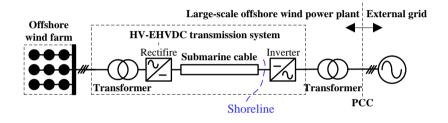

Figure 1-4 (a) shows the system configuration of a typical offshore wind power plant with AC transmission system, which voltage range typically becomes Medium Voltage to High Voltage (MV-HV). The generated active power in offshore wind turbines are transmitted to the PCC by MV-HVAC transmission system with submarine cables. In order to obtain as high voltage as possible between one side and another side, transformers are installed in the offshore wind power plant. It is noted that, where the submarine cable has a long distance, reactive power compensation is required.

Figure 1-4 (b) shows the system configuration of a typical offshore wind power plant with a DC transmission system, which voltage range typically becomes High Voltage to Extra High Voltage (HV-EHV). The generated active power in the offshore wind farm is transmitted to the PCC by HV-EHVDC transmission system with long distance submarine cables, which does not cause reactive power. Therefore, when the distance of the transmission system is longer, the DC transmission system has been selected although it requires expensive AC/DC converter (Rectifier) and DC/AC converter (Inverter).

(a) Offshore wind power plant with AC transmission system

(b) Offshore wind power plant with DC transmission system

Figure 1-4 System configurations of typical offshore wind power plants.

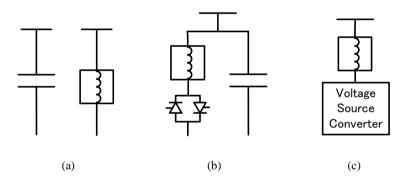

In this thesis, the offshore wind power plant with long distance HVAC transmission system is in focus. Lot of cases exist of this plant type, and typically the reactive power compensator is installed to compensate a large amount of reactive power arisen by the impedance from long distance submarine cables, and also in order to satisfy the grid code. Figure 1-5 shows various types of reactive power compensators for offshore wind power plant. A brief explanation of each type is introduced as follows [2], [4]:

(a) Shunt reactor/Static condenser: The inductor or capacitor is connected in parallel to the grid, which can compensate lead/lag reactive power, respectively. In case of offshore wind power plant, the shunt reactor may be connected to compensate the reactive power arisen by large amount of parasitic capacitance in the long distance submarine cables. It is obviously that it cannot change the compensation amount of the reactive power, although the compensating reactive power to be required changes with each moment.

(b) Static Var Compensator (SVC): SVC can compensate both lead/lag reactive power variably by control of the switching timing of the Thyristor. However, the SVC gives a lot of low-order harmonic currents to the grid by the switching operation of the thyristor, which requires a large amount of passive filters. In addition, when the grid voltage drop by short-circuit grid fault, the reactive power compensation capability of the SVC is significantly reduced, although the reactive power delivering capability under grid fault should according to recent grid codes for large scale offshore wind power plant.

(c) Static Synchronous Compensator (STATCOM): STATCOM could have the highest performance, but it is a more expensive reactive power compensator compared to the three types, which is constructed by Voltage Source Converter (VSC). It can also induce both lead/lag reactive power variably with very fast response and with very small low-order harmonic currents. Then, the reactive power compensation capability does not decrease even if grid voltage drops by a short-circuit grid fault. It is noted that, when the asymmetrical grid fault happens, one type of VSC has a limitation to deliver the reactive current, but it is much better than the SVC.

Figure 1-5 Reactive power compensators. (a) Shunt reactor/Static condenser. (b) Static Var Compensator (SVC). (c) Static Synchronous Compensator (STATCOM).

The STATCOM has become the preferable solution for the offshore wind power plant with long distance HVAC transmission system, and it has been selected in some existing offshore wind power plants as shown in Figure 1-3.

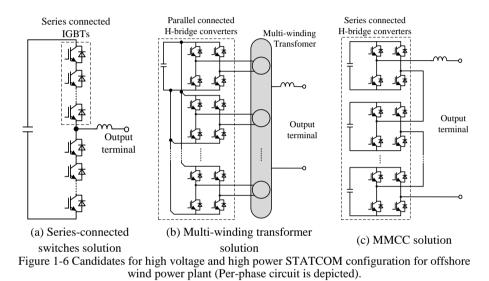

### 1.1.3. STATCOM TECHNOLOGY FOR OFFSHORE WIND POWER PLANTS

Figure 1-6 shows three types of potentially used high voltage and high power STATCOMs for offshore wind power application. It is noted that the circuit configuration is depicted as a per phase circuit configuration in the figure for simple explanations, but it is a three-phase system in the actual systems. The rated power and voltage for the STATCOM application become several tens of MVar and several tens of kV, respectively. Self-turn-off power devices such as Insulated Gate Bipolar Transistor (IGBT) and Integrated Gate Commutated Turn-off thyristor (IGCT) have been used for the STATCOMs [5]. The symbol of the power device is depicted as an IGBTs. Table 1-1 summarizes the characteristics of each circuit configuration. The details of each circuit configuration are explained as follows.

*The circuit configuration (a):* The reactive power is controlled by a traditional voltage source using two-level (or neutral point clamped three-level [6]) converter. In order to increase the rated voltage of the converter, the IGBT devices are connected in series. It seems that this solution is the cheapest solution. However, depending on the required rated voltage, the series connection counts of the number of IGBT increases. When only one IGBT device in an arm is broken, the STATCOM cannot operate anymore. This may practically be a problem.

The circuit configuration (b) [7]: The ac sides of the single-phase converters such as H-bridge converter having common dc-link terminals are connected to each winding of the input side of the multiplex transformer, where the transformer multiplexes each converter voltage in series. In this result, the output voltage of the multiplex transformer can obtain a high voltage with multi-level waveforms, which will reduce the amount of necessary harmonic filter. However, the multiplex transformer is very expensive and heavy. It is noted that, by redundantly designing the number of the single phase converters, this configuration can continue its operation even if one of the single phase converters is broken.

The circuit configuration (c) [8, 9, 10, 11, 12]: Single-phase converters such as Hbridge converters are directly connected in series in order to increase the system rated voltage. This circuit configuration also gains multi-level voltage waveforms, and also redundant operation. However, as only this circuit configuration becomes galvanic isolated of each dc-link terminal of the single-phase converter, each dc-link capacitor voltage has the double frequency voltage ripple at the source frequency, which increases the dc-link capacitor size. In addition, this circuit configuration has a limitation for asymmetrical Fault Ride Through operation, which performance is highly required in recent grid codes as described in the next section.

Nowadays, the circuit configuration in (c) becomes the mainstream solution for the STATCOM, because of significant advantages compared to the conventional

configuration (a) and (b) as it is mentioned above, like lower harmonic distortions, multiplex transformer-less configuration, and modular/ redundant design. Nevertheless, in addition to the capacitor size, voltage-balancing for a large number of DC-link capacitors in the converter cells are still challenging to be achieved for MMCCs, especially under asymmetrical grid faults [4], [13], [14], [15].

Based on this comparison, the MMCC solutions are selected for further study.

| Table 1-1 Characteristics | of each circuit configur | ation in Figure 1-6 for the | STATCOM application. |

|---------------------------|--------------------------|-----------------------------|----------------------|

|                           |                          |                             |                      |

|                         | (a) Series-connected switches solution | (b) Multi-winding<br>transformer solution | (c) MMCC solution            |

|-------------------------|----------------------------------------|-------------------------------------------|------------------------------|

| Cost                    | +++                                    | +                                         | ++                           |

| - Harmonic filter       | Medium                                 | Small                                     | Small                        |

| - Harmonic Inter        | Wiedium                                | ( multi-level voltage)                    | ( multi-level voltage )      |

| - Multiplex transformer | No                                     | Yes                                       | No                           |

|                         |                                        |                                           | Large                        |

| - DC-link capacitor     | Small                                  | Small                                     | (low frequency voltage       |

|                         |                                        |                                           | ripple by identical DC-link) |

| Redundancy operation    | No                                     | Yes                                       | Yes                          |

| Asymmetrical Fault Ride |                                        |                                           |                              |

| Through operation       | +++                                    | +++                                       | ++                           |

#### **1.1.4. FAULT RIDE THROUGH REQUIREMENTS**

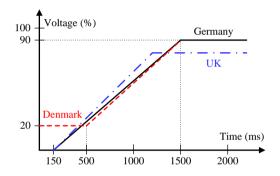

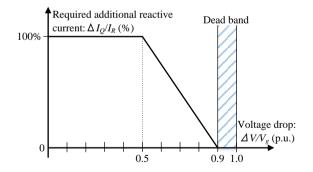

Besides the normal operation, the Transmission System Operators (TSOs) in different countries have issued strict grid supporting requirement for the growing large-scale renewable power plants under grid fault, which is specified in Figure 1-7 [16], [17]. According to the grid codes, the offshore wind power plant has to keep the operation regarding the voltage sag under grid fault as shown in Figure 1-7 (a), and in the case of German and Danish grid codes, it should be able to inject additional reactive current to support the recovery of grid voltage sag which is also shown in Figure 1-7 (b). It is noted that recent grid codes are not requiring negative-sequence reactive current injection, which contributes to recover asymmetrical grid fault voltages. The detail of the negative-sequence current injection can only be found only in Germany grid code as an option for the moment [18]. Therefore, Fault Ride Through capability of the STATCOM becomes more and more important.

(a) LVRT requirement by different countries.

(b) Additional reactive current requirements during LVRT

Figure 1-7 Reactive power requirements of large-scale generating plants under grid fault (low voltage ride through) [19].

### **1.2. RESEARCH QUESTIONS AND OBJECTIVES**

This thesis focuses on the promising MMCC-based STATCOM solution for the rapidly growing offshore wind application. The following issues are qualified in this thesis, which has become open questions.

- 1. Which type of MMCC solutions is the best to be in the offshore wind power plants operating as STATCOM? This question gives the following objectives in the thesis.

- ✓ Specifications and the component sizing of potentially four types of MMCC solutions for the STATCOM application are compared. The total cost and volume are of interest based on the total power semiconductor chip area and total energy stored in the passive components.

- ✓ Mathematical formulation of the STATCOM based on the MMCC solutions under asymmetrical compensation operation is developed, which contributes to the quantitative understanding of the performance limitation and circuit behavior for the Fault Ride Through (FRT) operation.

- ✓ The FRT capacity focusing on the MMCC solutions need to be compared under different grid faults scenarios with the consideration of actual device limitations.

- ✓ The most attractive MMCC solution for the STATCOM application should be suggested based on the obtained results.

- 2. Exist there any dc-link capacitor reduction method for the MMCC solutions?

- ✓ A dc-link capacitor voltage ripple reduction method for MMCC-based STATCOM should be proposed.

- ✓ Also dc-link capacitor volume reduction effect by applying the developed method should be estimated.

### **1.3. LIMITATIONS ON THIS STUDY**

Due to the large efforts to prepare the MMCC systems in practice, experimental setups are not developed in this thesis. However, this thesis proposes mathematical models and computer simulation models of the four types of the MMCC-based STATCOMs. The simulation models are carefully designed and they are based on a practical 80 MVar/33 kV STATCOM model. The realistic cell counts, power modules, and control strategies are taken as much as possible into account in order to clarify the research objectives.

### 1.4. OUTLINE OF THE THESIS

The Ph. D. dissertation consists of six chapters, which are introduced as follows:

### Chapter 1: Introduction

The background and motivation for the research are first presented. Then, the objective of the research is described as well. Finally, the outline of this dissertation is described.

# Chapter 2: Modeling and control of the MMCC solutions for offshore wind STATCOM Application

As preparatory for the study, the system configuration of the typical offshore wind power plant, grid fault scenarios, and also the fundamental control scheme of the potentially used configurations of the MMCC solutions for the STATCOM application are summarized. Then, specifications and the component sizing of each type of practical 80 MVar / 33 kV scaled MMCC-STATCOM are carefully designed and compared.

# Chapter 3: Theoretical operation of MMCC family under asymmetrical reactive power compensation

The mathematical formulation for the STATCOM based on the MMCC solutions under asymmetrical compensation operation is developed, which contributes to the quantitative understanding of the performance limitation and also the circuit behavior under asymmetrical grid fault operation.

### **Chapter 4: Performance benchmark of the MMCC solutions**

The electro-thermal stresses of the actual power modules used in each type of the MMCC with practical controls are analyzed in detail. The asymmetrical reactive power capacity focusing on the MMCC solutions is compared under different scenarios of grid faults, with the consideration of device temperature limits and voltage saturation. The most attractive MMCC solution for the STATCOM application is suggested based on the obtained results.

# Chapter 5: DC-link Capacitor Voltage Ripple Reduction Method for an MMCC-SDBC

This chapter proposes a capacitor voltage ripple reduction method by using a third harmonic zero-sequence current for Modular Multilevel Cascade Converter (MMCC) with Single Delta Bridge Cells (SDBC). A practical case study on an 80 MVar/ 33 kV MMCC-SDBC based STATCOM is used to demonstrate the method. The impact of the third harmonic zero-sequence current level of the capacitor oscillation reduction and the electro-thermal stresses on the IGBT modules are investigated. An optimal parameter of the current level is obtained by compromising the above two performance factors. The capacitor bank volume is also estimated and compared.

### **Chapter 6: Conclusions**

This chapter gives a summary, the main findings, and conclusion of this study. Topics for future research are also listed.

At the end of the thesis, the published papers during the Ph.D. study period are attached.

### **1.5. LIST OF PUBLICATIONS**

A list of journal papers related to the thesis, which have been published or submitted until now, is given as follows:

- **[J1] T. Tanaka**, H. Wang, K. Ma, and F. Blaabjerg, "Asymmetrical Fault Ride Through Capability of a STATCOM based on Modular Multilevel Cascade Converters," *IEEE Trans. Power Electron.* (in press)

- [J2] T. Tanaka, H. Wang, and F. Blaabjerg, "DC-link Capacitor Voltage Ripple Reduction Method of an MMCC-SDBC by Third Harmonic Zero-sequence Current Injection," *IEEE Trans. Ind. Appl.* (under review)

- A list of conference papers related to this thesis is given as follows.

- [C1] T. Tanaka, H. Wang, K. Ma, F. Blaabjerg, "Reactive Power Compensation Capability of a STATCOM based on Two Types of Modular Multilevel Cascade Converters for Offshore Wind Application," in *Proc. IEEE ECCE Asia*, pp.326 - 331, Jun. 2017.

- [C2] T. Tanaka, H. Wang, K. Ma, F. Blaabjerg, "Low Voltage Ride Through Performance of a STATCOM based on Modular Multilevel Cascade Converter Family for Offshore Wind Application," in *Proc. IEEE ECCE*, pp. 4879 - 4886, Oct. 2017.

- [C3] T. Tanaka, H. Wang, K. Ma, F. Blaabjerg, " Low Voltage Ride Through Capability of a STATCOM based on Modular Multilevel Cascade Converters for Offshore Wind Application," *IEEE eT&D workshop*, Nov. 2017.

- [C4] T. Tanaka, H. Wang, F. Blaabjerg, " A DC-link Capacitor Voltage Oscillation Reduction Method for a Modular Multilevel Cascade Converter with Single Delta Bridge Cells (MMCC-SDBC)," in *Proc. IEEE ECCE Asia*, pp. 2604 – 2610, May 2018.

# CHAPTER 2. MODELING AND CONTROL OF THE MMCC SOLUTIONS FOR OFFSHORE WIND STATCOM APPLICATION

As preparatory for the study, this chapter summarizes the system configuration of a typical offshore wind power plant including reactive power requirements, grid fault scenarios, and fundamental control scheme of the potentially used configurations of the MMCC solutions for the STATCOM application. Then, specifications and the component sizing of each type of practical 80 MVar / 33 kV scaled MMCC-STATCOM are carefully designed. The total cost and volume are compared based on the total amount of power semiconductor chip area and total energy stored in the passive components.

### 2.1. TYPICAL OFFSHORE WIND POWER PLANT AND SYSTEM FAULT SCENARIOS [J1]

### 2.1.1. SYSTEM CONFIGURATION [19]

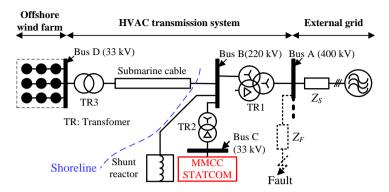

Figure 2-1 shows the system configuration of a typical offshore wind power plant and an MMCC-based STATCOM. The generated active power from the offshore wind farm needs to be provided to the Point of Common Coupling (PCC) as *Bus* A (400 kV in this case) by an HVAC transmission system (220 kV in this case) with long distance submarine cables. Reactive power induced by the submarine cable is typically compensated by the full-scale converters of wind turbines, the shunt reactor, and the STATCOM connected to *Bus* B via a delta-star transformer. Other power generators and loads besides the wind power plant may also be connected to *Bus* A.

Figure 2-1 A typical offshore wind power plant with an MMCC-STATCOM and shunt reactor [19].

### 2.1.2. REACTIVE CURRET REQUIREMENT

In order to compensate reactive power arisen by long-distance submarine cable and satisfy the grid codes, a STATCOM may be installed in offshore wind power plant. In addition, as mentioned in section 1.1.4, the offshore wind power plant has to keep the operation regarding the voltage sag under grid fault, and in the case of some countries it should be able to inject additional reactive current to support the recovery of the grid voltage sag. The reactive current reference is only defined as positive-sequence component because today's grid codes do not require negative-sequence current to compensate for the asymmetrical grid fault voltage recovery.

#### 2.1.3. GRID FAULT SCENARIOS [19]

Table 2-1 shows the representative grid fault voltage phasors and vectors corresponding to the three-phase-to-ground fault, single-phase-to-ground fault, phase-to-phase short-circuit fault and two-phase-to-ground fault [20], [21]. Here,  $V_{Su_pu}$ ,  $V_{Sv_pu}$ , and  $V_{Sw_pu}$  are each phase voltage standardized on *Bus* A by the rated voltage. It is assumed that the short-circuit faults happen somewhere on a feeder with the line impedance  $Z_F$  to *Bus* A (PCC) in Figure 2-1. The line impedance from the PCC to the grid with a higher voltage level is  $Z_s$ . A voltage dip severity *D* is determined by the ratio of the  $Z_s$  and  $Z_F$  with positive-, negative- and zero-sequence impedances. In order to simplify the grid fault scenarios, the dip severity *D* is considered as a real part only. More details are explained and classified in [22], [23].

| Fault types                                       | Phasor diagram definitions                                     | Vector definitions                                                                                                                                |

|---------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| (a)<br>Three-phase-<br>to-ground<br>fault         | $V_{Sw,pu}$ $V_{Su,pu}$ $V_{Su,pu}$                            | $\dot{V}_{Su_pu} = D$ $\dot{V}_{Sv_pu} = -\frac{1}{2}D - j\frac{\sqrt{3}}{2}D$ $\dot{V}_{Sw_pu} = -\frac{1}{2}D + j\frac{\sqrt{3}}{2}D$           |

| (b)<br>Single-phase-<br>to-ground<br>fault        | V <sub>Sw_pw</sub><br>V <sub>Sw_pw</sub><br>V <sub>Sv_pw</sub> | $\dot{V}_{Su_{pu}} = D$<br>$\dot{V}_{Sv_{pu}} = -\frac{1}{2} - j\frac{\sqrt{3}}{2}$<br>$\dot{V}_{Sw_{pu}} = -\frac{1}{2} + j\frac{\sqrt{3}}{2}$   |

| (c)<br>Phase-to-<br>phase short-<br>circuit fault | V <sub>Siv_pu</sub><br>V <sub>Siv_pu</sub>                     | $\dot{V}_{Su_{pu}} = 1$<br>$\dot{V}_{Sv_{pu}} = -\frac{1}{2} - j\frac{\sqrt{3}}{2}D$<br>$\dot{V}_{Sw_{pu}} = -\frac{1}{2} + j\frac{\sqrt{3}}{2}D$ |

| (d)<br>Two-phase-<br>to-ground<br>fault           | V <sub>Sw_pu</sub><br>V <sub>Sv_pu</sub>                       | $\dot{V}_{Su_pu} = 1$ $\dot{V}_{Sv_pu} = -\frac{1}{2}D - j\frac{\sqrt{3}}{2}D$ $\dot{V}_{Sw_pu} = -\frac{1}{2}D + j\frac{\sqrt{3}}{2}D$           |

Table 2-1 Phasor diagram and vector definitions of different grid fault scenarios on PCC (*BUS* A) [19]

In this thesis, three asymmetrical grid-fault scenarios are chosen to be studied as shown in Table 2-1 (b), (c) and (d), where the asymmetrical grid fault voltage on *Bus* A propagated to *Bus* B, the *Bus* A and *Bus* B voltages do not appear significant different due to the used neutral point grounded wye-wye-delta transformer TR1. However, the voltage on *Bus* B shows different characteristics, when it is propagated to *Bus* C, which is seen by the STATCOM due to the used delta-wye transformer TR2. Table 2-2 shows the asymmetrical grid fault scenarios on *Bus* C corresponding to each grid fault. The  $V_{dq}^+$ ,  $V_{dq}^-$  and  $V^0$  are positive-, negative and zero-sequence component of the voltage on dq domain, respectively, which are defined as scenarios used in this thesis.

| Fault types                                       | Each sequence voltage vector                                                                                                                                                                                                     |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (b)<br>Single-phase-<br>to-ground<br>fault        | $\begin{bmatrix} V_{dq}^{+} \\ V_{dq}^{-} \\ V^{0} \end{bmatrix} = V_{S} \begin{bmatrix} \frac{D}{3} + \frac{2}{3} \\ \frac{D}{6} - \frac{1}{6} + j \left( \frac{D}{2\sqrt{3}} - \frac{1}{2\sqrt{3}} \right) \\ 0 \end{bmatrix}$ |

| (c)<br>Phase-to-<br>phase short-<br>circuit fault | $\begin{bmatrix} V_{dq}^{+} \\ V_{dq}^{-} \\ V^{0} \end{bmatrix} = V_{S} \begin{bmatrix} \frac{D}{2} + \frac{1}{2} \\ -\frac{D}{4} + \frac{1}{4} + j\left(-\frac{\sqrt{3}D}{4} - \frac{\sqrt{3}}{4}\right) \\ 0 \end{bmatrix}$   |

| (d)<br>Two-phase-<br>to-ground<br>fault           | $\begin{bmatrix} V_{dq}^{+} \\ V_{dq}^{-} \\ V^{0} \end{bmatrix} = V_{S} \begin{bmatrix} \frac{2}{3}D + \frac{1}{3} \\ -\frac{D}{6} + \frac{1}{6} + j\left(-\frac{D}{2\sqrt{3}} + \frac{1}{2\sqrt{3}}\right) \\ 0 \end{bmatrix}$ |

Table 2-2 Sequence voltage amplitude definition of different grid fault scenarios on Bus C [19]. (The  $V_s$  is the rated voltage on Bus C.)

### 2.2. COMPARISON OF KEY DEVICES FOR EACH TYPE OF THE MMCC-BASED STATCOM [J1]

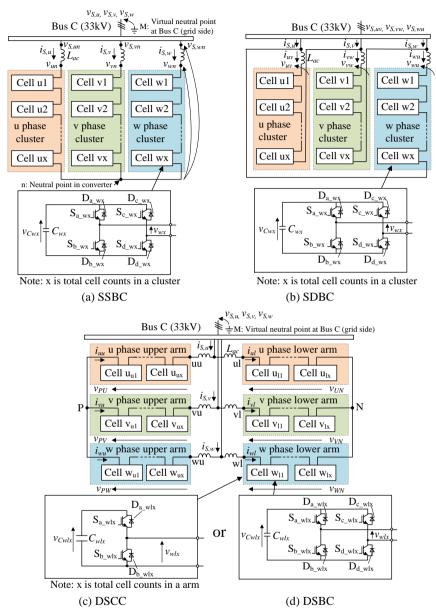

An 80 MVar / 33 kV case study for a practical STATCOM application is chosen in this thesis. Figure 2-2 shows the potentially used circuit configurations for the STATCOM based on MMCC. The MMCC with Single Star Bridge Cells (SSBC) has a star connection constructed by H-bridge converters. The MMCC with Single Delta Bridge Cells (SDBC) has a delta connection constructed by H-bridge converters. The MMCC with Double Star Chopper Cells (DSCC) and Double Star B ridge Cells have two star connections constructed by chopper converters and H-bridge converters, respectively. The difference of the connection type and cell configuration in the MMCC solutions show different cell counts and rated cell current when the output voltage and current of the MMCC solutions are designed to have the same value.

# CONTROL AND OPTIMIZATION OF MODULAR MULTILEVEL CASCADED STATCOM CONVERTERS FOR OFFSHORE WIND APPLICATION

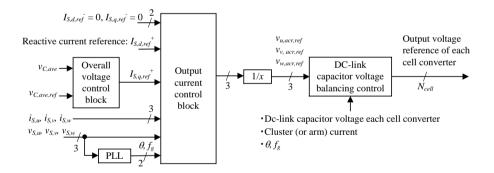

Figure 2-2 Circuit configurations of the MMCC family for a STATCOM application [19].

Table 2-3 shows the specifications, the cell numbers and key components for the specific application. The design procedure is given from next page.

| Circuit type of<br>MMCC                                        | SSBC                                                                    | SDBC                                        | DSCC                                    | DSBC                                    |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| Rated power $Q_r$                                              | ±80 MVA                                                                 |                                             |                                         |                                         |  |  |

| Rated line-to-line<br>voltage V <sub>s</sub>                   | 33 kVrms (Source angular frequency $\omega_s$ : $2\pi \times 50$ rad/s) |                                             |                                         |                                         |  |  |

| Rated DC-link<br>voltage each cell<br>$V_{C,dc}$               | 2600 Vdc                                                                |                                             |                                         |                                         |  |  |

| Nominal output                                                 | AC 1450 Vrms                                                            |                                             | AC 725 Vrms                             | AC 1450 Vrms                            |  |  |

| voltage each cell                                              | DC 0 Vdc                                                                |                                             | DC 1300 Vdc                             | DC 0 Vdc                                |  |  |

| Equivalent<br>switching<br>frequency f <sub>eq_sw</sub>        | 10 kHz (with Phase Shift PWM)                                           |                                             |                                         |                                         |  |  |

| Number of total                                                | 39                                                                      | 69                                          | 156                                     | 78                                      |  |  |

| cells N <sub>cell</sub>                                        | (13 cells/cluster)                                                      | (23 cells/cluster)                          | (26 series/arm)                         | (13 series/arm)                         |  |  |

| Number of total<br>switching devices<br>$N_{sw}$               | 156                                                                     | 276                                         | 312                                     | 312                                     |  |  |

| Rated output<br>current of each<br>cell $I_r$                  | 1400 Arms                                                               | 808 Arms                                    | 700 Arms                                | 700 Arms                                |  |  |

| Carrier frequency $f_c$                                        | 380 Hz                                                                  | 215 Hz                                      | 190 Hz                                  | 190 Hz                                  |  |  |

| Total energy<br>stored in<br>interconnection<br>inductor $E_L$ | 15  kJ<br>( $L_{ac} = 2.6 \text{ mH}$ )                                 | 15 kJ<br>( <i>L<sub>ac</sub></i> = 7.8 mH ) | 15  kJ<br>( $L_{ac} = 5.2 \text{ mH}$ ) | 15  kJ<br>( $L_{ac} = 5.2 \text{ mH}$ ) |  |  |

| Total energy<br>stored in<br>dc-link capacitor<br>$E_C$        | 1.6  MJ<br>( $C_x = 12 \text{ mF}$ )                                    | 1.6  MJ<br>( $C_x = 7.0 \text{ mF}$ )       | 6.3 MJ<br>( $C_x = 12 \text{ mF}$ )     | 1.6  MJ<br>( $C_x = 6.0 \text{ mF}$ )   |  |  |

| IGBT module                                                    | MBN1500FH45F<br>(4500V/1500A)                                           | MBN900D45A<br>(4500V/900A)                  | MBN800H45E2<br>(4500V/800A)             | MBN800H45E2<br>(4500V/800A)             |  |  |

Table 2-3 The MMCC specifications for the case study [19]

# 2.2.1. BASIC STRUCTURE AND POWER SEMICONDUCTOR DEVICES [19]

The rated DC-link voltage  $V_{C,dc}$  of each converter cell in the four types of MMCC solutions are designed to be the same at 2600 Vdc where the widely used 4.5 kV IGBT modules are selected for each converter cell in this thesis. The nominal output AC voltage of each converter cell in the SSBC, SDBC and DSBC is designed at 1450 Vrms with the nominal modulation factor  $\alpha_n = 0.8$ . The margin of the modulation factor (0.2) is determined by the voltage drop of the output impedance, current control dynamics, pulse width limitation due to dead time, and also in order to achieve modular redundancy. However, the circuit configuration of the converter cell for the DSCC is a chopper converter, which cannot output negative voltage. Because +/- output voltage is also required for the DSCC based STATCOM, the output voltage in each chopper converter cell is superimposed with the half value of the rated DC-voltage ( i.e. 1300 Vdc ). When the above design guideline is followed, the nominal output AC voltage of each converter cell in the DSCC becomes 725 Vrms AC with the nominal modulation factor for the AC component  $\alpha_n = 0.8$ .

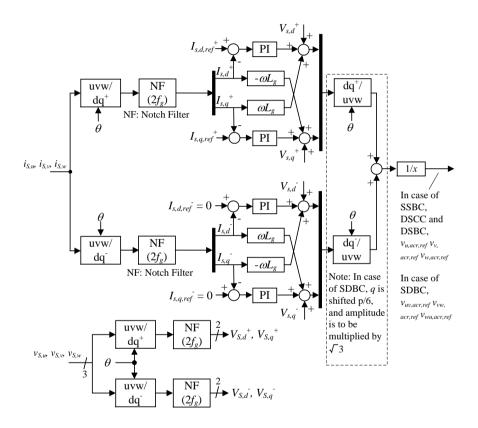

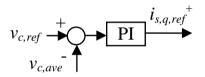

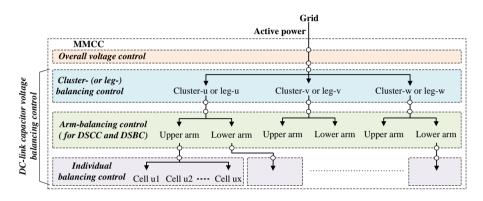

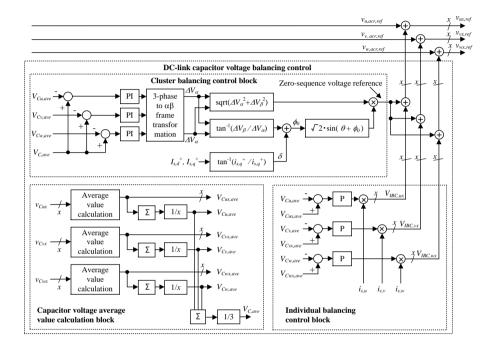

|                                                               | SSBC                                                                        | SDBC                                                                | DSCC                                                              | DSBC                                                                        |