Aalborg Universitet

# Advanced Modeling of SiC Power MOSFETs aimed to the Reliability Evaluation of **Power Modules**

Ceccarelli, Lorenzo

Publication date: 2019

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Ceccarelli, L. (2019). Advanced Módeling of SiC Power MOSFETs aimed to the Reliability Evaluation of Power Modules. Aalborg Universitetsforlag.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# ADVANCED MODELING OF SIC POWER MOSFETS AIMED TO THE RELIABILITY EVALUATION OF POWER MODULES

BY LORENZO CECCARELLI

**DISSERTATION SUBMITTED 2019**

AALBORG UNIVERSITY DENMARK

# Advanced Modeling of SiC Power MOSFETs aimed to the Reliability Evaluation of Power Modules

By

Lorenzo Ceccarelli

A Dissertation Submitted to the Faculty of Engineering and Science at Aalborg University in Partial Fulfilment for the Degree of Doctor of Philosophy in Electrical Engineering

May 2019 Aalborg, Denmark

| Dissertation submitted:  | June 2019                                                                      |

|--------------------------|--------------------------------------------------------------------------------|

| PhD supervisor:          | Prof. Francesco Iannuzzo, Ph.D.<br>Aalborg University                          |

| PhD committee:           | Associate Professor Tamas Kerekes (chairman)<br>Aalborg University             |

|                          | Professor Ulrike Grossner<br>ETH Zurich                                        |

|                          | Grainger Endowed Chair Professor John Shen<br>Illinois Institute of Technology |

| PhD Series:              | Faculty of Engineering and Science, Aalborg University                         |

| Department:              | Department of Energy Technology                                                |

| ISSN (online): 2446-1636 |                                                                                |

ISBN (online): 978-87-7210-450-8

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Lorenzo Ceccarelli

Printed in Denmark by Rosendahls, 2019

"Look up at the stars and not down at your feet. Try to make sense of what you see, and wonder about what makes the universe exist. Be curious."

Stephen W. Hawking

# Preface

I would like to acknowledge the Centre of Reliable Power Electronics (CORPE), the Advanced Power Electronic Technology and Tools (APETT) project and the Department of Energy Technology at Aalborg University for making possible and supporting this Ph.D. project. I am also grateful for the funding received by Det Obelske Familiefond and Otto Mønsted Fond, which allowed me to attend several conferences and purchase laboratory equipment for my experimental setups.

My deepest gratitude goes to my supervisor Prof. Francesco Iannuzzo, who offered me the opportunity of starting this academic journey and has been relentlessly stimulating and supportive during the past three years. I especially appreciate his availability, kindness and friendliness, which have always fostered a great professional and human relationship. His thoughtful guidance and broad knowledge of power semiconductor devices have been a constant reference and source of inspiration. Moreover, I thank Prof. Frede Blaabjerg and Assoc. Prof. Huai Wang for involving me in the APETT project and for their valuable aid.

My appreciation also goes to my colleagues and fellow members of CORPE, especially to Assist. Prof. Dr. Amir Bahman and Dr. Paula Díaz Reigosa, for their invaluable help, enthusiasm and fruitful co-authorship. The same goes for my other colleagues and the staff at the Department of Energy Technology, especially to John K. Pedersen, Tina Larsen, Corina Busk Gregersen, Bonnie Steffensen and Walter Neumayr for their highly professional assistance in administrative and technical matters. They all contribute to a vividly diverse and dynamic research environment.

At the same time, I want to extend special thanks to Prof. Dr. Alan Mantooth and the MSCAD team at the University of Arkansas, in Fayetteville, where I spent my five-month study abroad period. There I found a lively research group in the field of device modeling, which keeps yielding prolific collaboration and discussion.

I would like to thank the assessment committee for this doctoral defense: Assoc. Prof. Tamas Kerekes from Aalborg University, Prof. Dr. John Shen from Technology Institute of Illinois, and Prof. Dr. Ulrike Grossner from ETH Zurich.

Finally yet importantly, I would like to thank, from the deepest of my heart, my family, for being the rock-solid foundation and sustenance of my curious and openminded outlook, and my girlfriend Shawna, for sharing the journey on the road through this great life adventure.

Lorenzo Ceccarelli May 12, 2019 Aalborg, Denmark

# Abstract

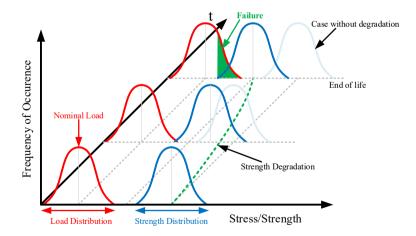

Power semiconductor devices are the core element in every electronic power conversion system. During the typical 20-year lifespan of a power electronic (PE) application, the devices undergo a significant amount of stress from operating in normal and abnormal conditions. The temperature fluctuations generated by the device power losses are the most significant stressors, eventually leading to thermomechanical degradation and failure.

A new range of wide bandgap (WBG) power semiconductor devices, especially those based on Silicon Carbide (SiC) and Gallium Nitride (GaN), are rapidly evolving to replace Silicon-based components. SiC power MOSFETs are already widely manufactured and are becoming the device of choice in the design of many low-tomedium power (<1 megawatt) PE applications. These devices are especially promising for their high power density, high-voltage blocking capability and very fast switching. Nevertheless, the widespread diffusion of such devices is slowed down by their significantly higher cost and the lack of solid reliability data and accurate models to support optimized circuit design. Moreover, high power density comes at the cost of increased thermal stress, especially during short circuit events, which may lead to instabilities and degradation phenomena at a chip and package level.

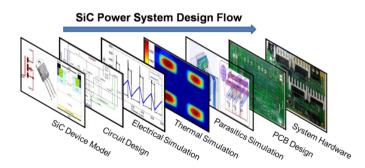

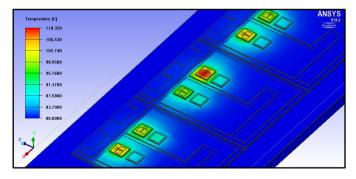

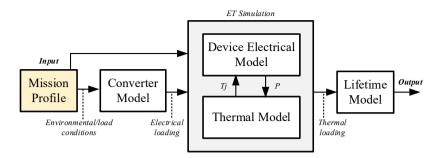

It is important to bear in mind that advanced models and simulation tools for WBG devices, can support the reliable and optimized design of next-generation power converters. Therefore, this Ph.D. project aimed at developing compact electrothermal models to explore the normal and abnormal behavior of commercial SiC MOSFETs. The research activity started with the implementation and identification of a physical device model, based on earlier work and expanded with additional features, such as self-heating and short circuit behavior. Several SiC discrete devices and power modules have been characterized experimentally in a wide range of operating conditions, providing data to validate the device model. Besides, realistic package models have been created using Finite-Element Analysis (FEA) software, in order to extract lumped circuit elements to couple with the device model, obtaining fast and accurate electrothermal simulations. The combined use of different software environments (e.g. PSpice, MATLAB/Simulink and ANSYS) allowed the optimization of computation time and co-simulation of different timescales. The main outcome of the project has been the implementation of advanced models for commercial SiC MOSFET devices and power modules. Moreover, the simulation results have provided a better understanding of the short circuit behavior and thermal instabilities in SiC power modules, the estimation of the device thermal loading during real mission profiles for DC-AC converter applications, and the impact of aging conditions on the device performance.

# Dansk Résumé

Effektelektroniske komponenter er kerneelementet i alle elektroniske strømkonverteringssystemer. I mellem den typiske 20-årige kraftelektronisk applikations levetid, undergår komponenterne en betydeligt beløb af stress fra drift i normale og unormale tilstand. Temperaturfluktuationerne, der genereres af komponents effekttab, er de vigtigste stress-faktorer, som endelig fører til termomekanisk nedbrydning og nederlag.

En ny serie af "wide bandgap" (WBG) komponenter, især dem, der er baseret på siliciumcarbid (SiC) og galliumnitrid (GaN), udvikler sig hurtigt for at erstatte siliciumbaserede komponenter. SiC power MOSFET'er er allerede bredt fremstillet og bliver de præfererede komponenter i designet af mange lav-til-medium strøm (<1 megawatt) kraftelektronisk applikationer. Disse komponenter er især lovende for deres højeffektdensitet, højspændingsblokerende kapacitet og meget hurtig kommutation. Alligevel forsinker den udbredte diffusion af SiC MOSFET's deres højere omkostninger og manglen på solide pålidelighedsdata og præcise modeller til understøttelse af optimeret design af effektomformere. Desuden skaber høj effektæthed øget termisk stress, især i tilfælde af en kortslutning, som kan føre til ustabilitet og nedbrydning fænomener på en chip og indkapsling niveau.

Det er vigtig at huske, at udviklingen af avancerede modellerings- og simuleringsværktøjer til WBG-komponenter kan understøtte det pålidelige og optimerede design af næste generations kraftomformere.Formålet med dette Ph.D. projekt er at udvikle kompakte elektrotermiske modeller for at undersøge den normale og unormale opførsel af kommercielle SiC MOSFET'er. Forskningsaktiviteten startede med implementering og identifikation af en fysisk enhedsmodel baseret på tidligere arbejde og udvidet med vderligere funktioner, såsom selvopvarmning og kortslutningsadfærd. Flere SiC diskrete komponenter og strømmoduler er blevet karakteriseret i laboratoriet i en bred udvalg af driftsbetingelser, der giver data til validering af modellen. Fokus har været på skabelsen af realistiske indkapsling modeller ved hjælp af Finite-Element Analysis (FEA) software og udvindingen af klumpede elementer, som giver hurtige og præcise elektrotermiske simuleringer. Den kombinerede brug af forskellige softwaremiljøer (fx PSpice, MATLAB / Simulink og ANSYS) tillod optimering af beregningstid og co-simulering af forskellige tidsskalaer. Hovedresultatet af projektet var implementeringen af avancerede modeller til kommercielle SiC MOSFET-enheder og strømmoduler. Resultater af simuleringerne har bl.a. givet en bedre forståelse af kortslutningsadfærd og termiske ustabiliteten i SiC-effektmoduler, estimeringen af termiske stress under ægte mission-profiler til DC-AC kraftomformere og virkningen af aldringsbetingelser på komponent vdeevne.

# Contents

| Preface                                                                              |                                                                                                                                                                                                                     | iv                                           |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Abstract                                                                             |                                                                                                                                                                                                                     | v                                            |

| Dansk Res                                                                            | umé                                                                                                                                                                                                                 | vi                                           |

| Contents                                                                             |                                                                                                                                                                                                                     | vii                                          |

| Chapter 1                                                                            | Introduction                                                                                                                                                                                                        | 1                                            |

| 1.1<br>1.1.1<br>1.2<br>1.3<br>1.4<br>1.5                                             | Background<br>Wide bandgap semiconductors: a new era<br>Reliability of modern power semiconductor devices<br>Aim of the Project<br>Scientific Questions<br>Objectives<br>Limitations                                |                                              |

| 1.6<br>1.7                                                                           | Thesis Outline<br>List of Publications                                                                                                                                                                              |                                              |

| Chapter 2                                                                            | Operation and Modeling of SiC Power MOSFETs                                                                                                                                                                         | 13                                           |

| 2.1<br>2.1.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.4                         | State-of-the-art SiC MOSFET Compact Modeling<br>Model Description and Implementation<br>Including Self Heating<br>A MATLAB-based GUI for parameter extraction<br>Experimental Setup for Model Validation<br>Summary | 14<br>18<br>20<br>22<br>24<br>25<br>28       |

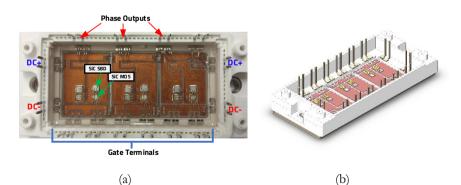

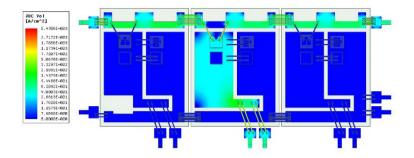

| Chapter 3<br>3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3 | Switching Validation<br>Case Study II: SPICE Simulation of a SiC MOSFET power module<br>Model Validation<br>Extraction of parasitic elements<br>Extraction of the thermal model                                     | 29<br>29<br>32<br>34<br>35<br>37<br>38<br>38 |

|                                                                                      | Fast and Accurate Electrothermal Simulation Strategy                                                                                                                                                                |                                              |

| 4.1                                                                                  | Multi-domain and multi-timescale simulation at a glance                                                                                                                                                             | 43                                           |

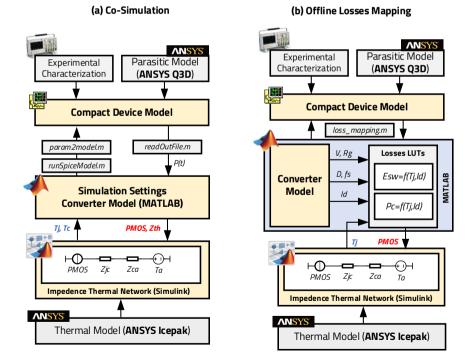

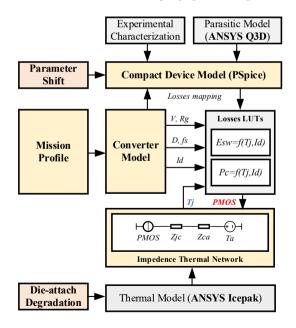

| 4.1.1     | Integrating a compact device model in an electrothermal model | . 44 |

|-----------|---------------------------------------------------------------|------|

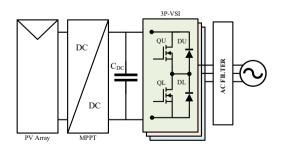

| 4.2       | Case study III: ET modeling of a 3P 1.2-kV SiC power module   | . 46 |

| 4.2.1     | Electrical Model                                              | . 47 |

| 4.2.2     | Converter Model                                               | . 48 |

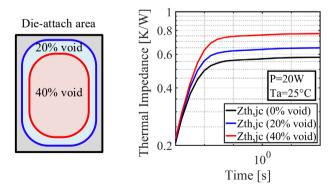

| 4.2.3     | Thermal Model                                                 | . 49 |

| 4.2.4     | Electrothermal Simulation Results                             | . 52 |

| 4.3       | Summary                                                       | . 54 |

| Chapter 5 | Lifetime Prediction and Aging Effects in SiC Power MOSFETs    | . 55 |

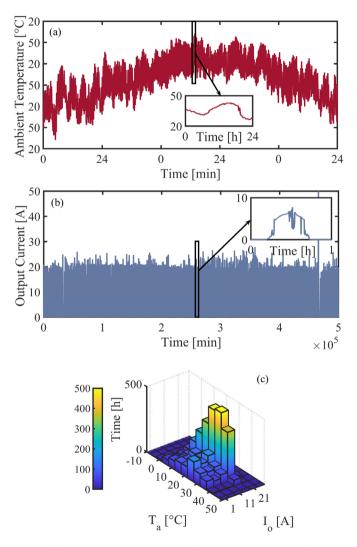

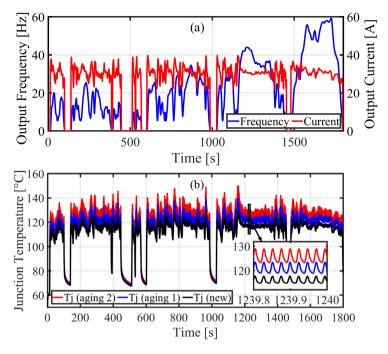

| 5.1       | Mission-profile-based Lifetime Estimation                     | . 55 |

| 5.1.1     | Characterization of a Mission Profile                         | . 57 |

| 5.1.2     | Lifetime Modeling and Damage Accumulation                     | . 60 |

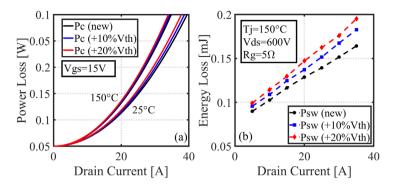

| 5.2       | Including Aging Impact                                        | . 63 |

| 5.3       | Summary                                                       | . 65 |

| Chapter 6 | Conclusions and Future Work                                   | . 67 |

| 6.1       | Summary                                                       | . 67 |

| 6.2       | A Side Topic: Using SiC Photoemission as a TSOP               | . 68 |

| 6.3       | Research highlights                                           | .70  |

| 6.4       | Proposals for future research topics                          | .71  |

|           |                                                               |      |

| Appendix  |                                                               | 73   |

| 11                    |    |

|-----------------------|----|

| References            | 80 |

| Selected Publications | 89 |

# Chapter 1 Introduction

# 1.1 Background

Power electronics (PE) can be defined as the application of solid-state electronics to the conditioning, control and conversion of electric power. As the demand for electricity and the concern for environmental protection grow worldwide, PE is playing an increasingly important role in modern society. Most of the electrical power used nowadays flows through power conversion systems, ranging from household appliances and automotive to high-power, grid-connected applications. It is especially required in the booming market of renewable energy sources, which is estimated to triplicate in size in the next few decades [1]. The PE market was valued at USD 36.93 Billion in 2017 and is expected to reach USD 51.01 Billion by 2023, at a compound annual growth rate (CAGR) of 5.5% [2]. Power conversion includes both voltage conversion (AC-DC, DC-AC, DC-DC, AC-AC) and frequency conversion (AC-AC). The energy conversion efficiency of such systems is typically 85-95%, whit the remaining 5-15% lost as heat. Power semiconductor devices are the core component of all power electronic systems and in most cases the responsible for the largest share of losses in the system [3]. With the wide spread use of electronics in the industrial, consumer and transportation sectors, the study and development of power semiconductor devices has a major impact on the evolution of PE systems, their efficiency and their reliability.

The research for more powerful and efficient electronic devices travels along two parallel paths. On the one hand, the requirement for high power and reduced size/weight has increased in many applications, which has led to the design of compact power modules, embedding multiple devices in a relatively small package [4], [5]. On the other hand, the study and manufacturing of wide bandgap semiconductors, among which Silicon Carbide (SiC) and Gallium Nitride (GaN), moves towards the development of a new generation of devices [6]–[8]. Some of these devices have already reached a quite advanced stage and are now commercialized by many manufacturers. They are capable of withstanding hightemperature and high-voltage operations with great efficiency and enhanced power density.

The development of such new technologies has introduced a number of new

challenges. First, the cost reduction to enable their diffusion in the market. Second, but equally important, the study of the reliability of both single-chip - or discrete - devices and multi-chip modules, specifically by means of advanced simulation tools, is a crucial aspect for the diffusion of these new technologies in the application field, where a guaranteed lifetime and ruggedness to abnormal conditions are always a requirement.

### 1.1.1 Wide bandgap semiconductors: a new era

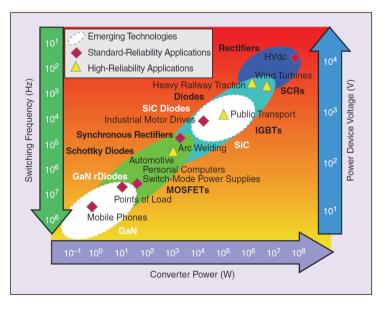

The world of PE devices has been dominated by silicon (Si) based technology for over 50 years. The development of power metal-oxide-semiconductor field-effect transistors (MOSFETs) and insulated gate bipolar transistors (IGBTs), together with the improvement of computer-aided device simulation, has greatly improved the performance of power switching devices over the last three decades. Despite that, though, Si technology exhibits some relevant limitations, especially concerning voltage blocking capability vs. conduction power loss, switching performance and high temperature operation, which are intrinsically limited by its material properties. At present, the highest blocking voltage rating for commercial devices is 6.5 kV [9], while the current rating for multi-chip power modules goes as far as 3 kA. The use of Si-based devices beyond such power rating is hindered by the aforementioned limitations and affects the overall efficiency of the power converter, requiring, at the same time, expensive, bulky and complex cooling systems and passive components. Figure. 1.1 [10], from Iannuzzo et al. in 2014, shows the use of different types of PE

Figure. 1.1. Power semiconductor device application map [10].

switches in applications, related to the power output rating and the switching frequency, as well as their blocking voltage. One can clearly observe how the panorama for Si-based devices is in the range of 10 MW output power at low switching frequencies (<1 kV) and to 100 kHz for low power applications (<10 kW). Nevertheless, increased switching frequency is always desired in power converter applications, since it allows reducing the size of passive components such as transformers and capacitors, as well as the bulk of cases and PCBs. Additionally, a number of industrial, automotive and aerospace applications require power converters to operate at temperatures significantly larger than 200°C, way beyond Si limitations.

Over the past 20 years, a new class of power devices, based on the so-called wide bandgap (WBG) semiconductors, has emerged, demonstrating a number of extremely promising properties. At present, SiC and GaN are by far the ones showing the best tradeoff between material characteristics and maturity of their manufacturing technology [11]. It is worth to note, that the SiC lattice polytipe referred to in this work is 4H-SiC, which, at present, is yielding the best manufacturing outcome for power devices. A comparison of several significant material properties of Si, SiC and GaN is provided in Table 1.1. The larger bandgap of these materials results in a higher critical electric field, enabling the design of power devices with thinner and highly doped drift regions, meaning lower conduction energy loss. Although GaN offers better high frequency and high voltage capability, the manufacturing of good-quality substrates, suitable for HV vertical devices, is still hard to achieve and its thermal conductivity is lower compared to SiC. Looking at Figure. 1.1, currently off-the-shelf WBG devices occupy an area of influence that partly overlaps the ones of Si MOSFETs and IGBTs, but has a perspective margin of improvement towards higher switching frequency and power rating. It is important to notice that the scenario for GaN devices has evolved in recent years, reaching up to 650 V.

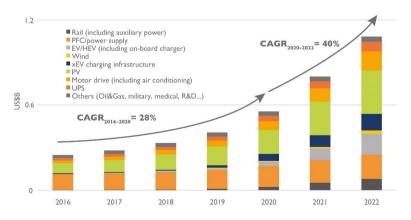

At present, SiC is widely acknowledged as a potential replacement to its Si counterparts in the HV, medium-power department. Figure 1.2 shows the development of the SiC power device market in several application fields from 2016,

| Property                                               | Silicon | 4H-SiC   | GaN  |

|--------------------------------------------------------|---------|----------|------|

| Bandgap (eV)                                           | 1.1     | 3.26     | 3.45 |

| Breakdown (x10 <sup>6</sup> Vcm <sup>-1</sup> )        | 0.3     | 3        | >1   |

| Carrier Mobility (cm <sup>2</sup> /V s <sup>-1</sup> ) |         |          |      |

| Electron                                               | 1500    | 1140     | 1250 |

| Hole                                                   | 600     | 50       | 850  |

| Thermal Conductivity (W/cm K <sup>-1</sup> )           | 1.5     | 4.9      | 1.3  |

| Melting Point (K)                                      | 1693    | 3103     | 2773 |

| Thermal Expansion (x10 <sup>6</sup> K <sup>-1</sup> )  | 2.6     | 4.2÷4.68 | 5.6  |

TABLE 1.1 – SEMICONDUCTOR MATERIAL PROPERTIES

projected until 2022, in the analysis carried out in [12]. The market CAGR will soon reach 40%, with a significant expansion in the PV and EV sectors. The research and development activity on this field has already yielded devices with voltage ratings up to 15 kV [13], [14] and power modules with current ratings up to 600 A, and demonstrated their improved efficiency in applications ranging from low-voltage battery chargers to plug-in electric vehicles powertrains and grid-connected PV inverters [15]. SiC material properties make it an excellent choice for the construction of unipolar switching devices, such as MOSFETs or JFETs, and Schottky Barrier Diodes (SBD), based on a metal-semiconductor interface. In particular, the SiC MOSFET has reached an advanced state of maturity and many manufacturers worldwide (among which Wolfspeed, Rohm, Infineon, STMicro, and others) have reached the 3rd generation for their devices. As a unipolar switch, the SiC MOSFET features all the advantages of the traditional Si MOSFET (fast switching, excellent controllability, reverse conduction capability) and of the Si IGBT (high power density with low conduction losses). On the other hand, it does not exhibit some of the IGBT's main disadvantages (bipolar charge recombination, high conduction losses) [16].

These characteristics have a big potential for the optimized design of more power-dense converters where higher switching frequency, reduced volume or higher efficiency are required and can pay off the additional cost for SiC components. In fact, SiC power devices (and in general WBG devices) are sold at roughly 2÷5 times the cost of Si components, which significantly hinders their diffusion in many fields where cost constrains matter. This is mostly due to a still inefficient supply chain, with scarce availability of SiC epi-wafers in large scale and low price, as argued in [17]. The growing volume and demand in the market will allow chip manufacturers to implement an economy-of-scale, obtain wafers at lower prices, or rearrange Si facilities for SiC devices, which might significantly reduce the cost.

Figure 1.2. SiC device market size split by application (Source: Power SiC: Materials, Devices, Modules, and applications report, Yole Développement, August 2017)

The other great question is whether SiC (and GaN) devices could ever match and exceed Si state-of-the-art reliability and robustness level in relationship to the specific applications.

### 1.1.2 Reliability of modern power semiconductor devices

As PE systems complexity evolves to reach greater efficiency and power density, the requirement for reliability have become stricter in many application, especially within automotive and aerospace industries. At the same time, the energy sector is following this path and especially focusing on cost-effective and sustainable solutions for improved reliability [18].

Substantial efforts have been invested in the reliability assessment of gridconnected converters, especially for photovoltaic (PV) energy generation [19]. A five-year operation field report conducted in 2008 from a 3.5 MW PV plant, ascribes to the inverter as much as the 34% of the unscheduled maintenance events and 59% of the unscheduled maintenance costs [20]. These shares are much bigger than the

|                                       | Failure Modes                |                               |                       |  |

|---------------------------------------|------------------------------|-------------------------------|-----------------------|--|

| Devic                                 | Device Level                 |                               | Level                 |  |

| Catastrophic                          | Wear-out                     | Catastrophic                  | Wear-out              |  |

| Thermal<br>Instability                | Oxide<br>Degradation         | Over-temperature<br>(melting) | Bond-wire<br>Fatigue  |  |

| Overvoltage                           | Voltage<br>Threshold Drift   | Partial<br>Discharge          | Solder<br>Fatigue     |  |

| Overcurrent                           | Epitaxial<br>Dislocations    |                               | Substrate<br>Creeping |  |

| Cosmic Ray<br>Failures                | Metallization<br>Degradation |                               |                       |  |

| Activation of<br>Parasitic<br>Devices | Passivation<br>Degradation   |                               |                       |  |

TABLE 1.2. COMMON FAILURE MODES IN POWER DEVICES

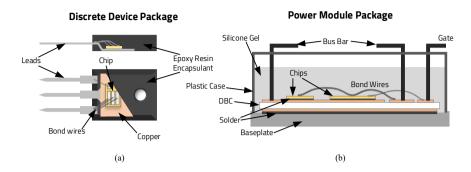

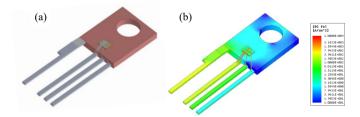

Figure 1.3 Packaging technologies: single-chip discrete device TO-247 package (a); cross section of a multi-chip power module (b).

single contributions from other subsystems like PV panels, data acquisition system, etc. Another survey on reliability in PE converters [21], carried out in 2011, reports that the most frangible components in a converter are, in fact, the power switching devices (34%), followed by capacitors (20%). Therefore, when approaching the system-level reliability prediction, a deeper insight on the component-level reliability and lifetime modeling has to be sought.

Table 1.2 reports the most common failure modes on device (chip) and package level. These can be divided into two subcategories: catastrophic failures and wearout failures. The former are those failures occurring in the time range of micro- to milliseconds, often unpreceded by any indicator, whereas the latter are related to the device ageing over its operational life, and are always characterized by a slow and detectable degradation process. Many catastrophic failure modes in devices, such as overvoltage, overcurrent and cosmic ray failures, are due to external events - i.e. occurring outside the device packaging- and evolve into self-sustaining internal phenomena [10]. Other chip failures are related to internal instabilities, like thermal unbalances between the device elementary cells or activation of intrinsic parasitic devices (e.g. IGBT's thyristor latch-up or MOSFET's BJT turn-on). Device wear-out failure include oxide-semiconductor or oxide-metal interface degradation; charge migration to/from the oxide resulting in threshold voltage shift; lattice dislocations in the epitaxial layer or the substrate due to poor wafer quality; damage to the top metallization and passivation. So far, WBG devices have most of their device-level failure modes in common with their Si counterparts. In some cases, though, since their manufacturing technology has not reached an advanced stage yet, some of these failure modes tend to occur more frequently and have not been solved or mitigated. For example, the short circuit (SC) ruggedness of SiC power MOSFETs is still a critical issue, with SC withstanding time at nominal voltage much lower than the 10 microseconds required in many applications [22].

The package also heavily influences the reliability of power semiconductor devices [23]. It has to fulfill a series of purposes, all vital for the device operation, such as ensuring electrical connection/insulation between one or more

semiconductor chips and the external circuit; dissipating the heat generated during chip operation to a cooling system; protecting the chip from harmful ambient conditions. Figure 1.3 depicts two of the most common packaging technology used nowadays for power semiconductor chips and the ones studied in this project. The so-called *discrete device* package pictured in Figure 1.3.a, in this case a TO-247 type, is commonly used for components rated below 100 A and 1.2 kV. In this kind of packages, the chips are soldered on a copper lead frame and connected to the other leads via wire bonding. A molded plastic encapsulant, such as epoxy resin, is used to protect and isolate the chip. The *multi-chip power module* technology, whose cross section is depicted in Figure 1.3.b, is adopted for higher power ratings or in order to achieve specific circuit layouts. Here, the chips are soldered on an electrically insulated copper trace. The traces and chips are interconnected via bond wires (commonly made of Al) and the main power and control leads protrude from the module plastic case. The modules are filled with insulating and protecting silicone gel. The direct-bonded copper (DBC), consisting in a ceramic substrate sandwiched between two copper layers, allows the insulation, while at the same time providing a good thermal conductive path towards the baseplate. The module is mounted on a heat dissipation system, most likely a heat sink, via the baseplate, with a thermal interface material, in between, e.g. thermal grease. For current ratings above 5 kA, mostly for grid-connected PE applications, the power module is sometimes replaced by press-pack components, where the semiconductor is mounted between two metal discs and thermal and electrical contacts are ensured by pressing them instead of use solder. In addition, many new packaging technologies are emerging, such as flip-chip, press-fit, double-sided cooling or DBC substrate-based molded power modules.

Package-level catastrophic failures are mostly connected to excessive temperature stress, originating from the ambient or produced by the chips within the package, and leading to melting or vaporization of the internal metallic structures or the plastic casing. Moreover, overvoltage or poor design, i.e. not respecting a proper creepage distance between components at different electric potential, can determine a destructive breakdown in the dielectric, e.g. arcing or partial discharge.

The main wear-out failure mechanisms of power semiconductor packaging are induced by thermal stress. The mismatch in coefficient of thermal expansion (CTE) between the different material stacked up in the package determines stress and strain during the intermittent operation of the power switches. Bond wires lift-off, heel cracking, solder joint fatigue and substrate/baseplate cracking are some of the most common failure modes observed in power modules [24]. In particular, bond wires and chip solder are the most critical areas of degradation, being exposed to the full temperature swing caused by the chip self-heating [25]. The degradation process has been extensively studied in the case of Si IGBT modules and several lifetime modeling techniques have been introduced, both physical [26] and empirical [27].

Nowadays, the packaging technology for commercial SiC MOSFET power modules is, in fact, mostly identical to the one widely used for Si IGBT modules. This solution has been adopted by most of the manufacturers to guarantee the compatibility of their modules with already-existing PE system designs and have better acceptance by the end users. This brings a huge limitation to the exploitation of the full potential of SiC technology due to larger electrical parasitic elements e.g. stray inductances and capacitive coupling - that worsen the switching performance and, thus, the overall efficiency. However, this also means that the same degradation and failure mechanisms have been observed in SiC modules [28], and bond wire damage and solder degradation are still the predominant causes of thermally-induced failure and ageing. Despite this fact, the operational conditions that make SiC devices a better choice over Si ones, i.e. high temperatures and harsh environments, present a much bigger reliability challenge, since the stress on the package is higher. Thus, it is crucial to carry out a proper lifetime estimation for these new components, in order to assess whether or not they offer acceptable long-term performance. This can be investigated experimentally by performing a series of reliability tests, i.e. power cycling, temperature cycling, SC testing, high-temperature reverse/gate bias (HTRB/HTGB), and others [4]. At the same time, the evolution of advanced modeling and simulation tool can significantly aid the researchers in studying the device performance. A large effort has already been dedicated to the creation and validation of compact WBG device models within circuit-based simulation environment (e.g. PSpice, LTspice, Saber, Plecs, etc.), as well as more detailed finite element method (FEM) models meant for TCAD software. However, a deeper understanding of the device's physics and intrinsic limitations, as well as their mission profile, is most needed in order to obtain meaningful simulation results and

### 1.2 Aim of the Project

The aim of this Ph.D. project is to investigate the reliability and ruggedness of PE devices and modules through the modeling of SiC power MOSFETs. The project methodologies are specifically oriented towards compact circuit-based modeling, finite-element method (FEM) simulation techniques, an corroborated with extensive experimental characterization and testing of commercially available devices, performed in the laboratory under a wide range of operating conditions. The knowledge acquired from the characterization activity will be employed in the development of new and more complete models, accounting for detailed electrothermal behavior, abnormal and degradation phenomena, as well as the implementation of a method for the fast and accurate reliability prediction of SiC MOSFET power modules.

### 1.3 Scientific Questions

The Ph.D. project aims to investigate what the current reliability and robustness challenges are in the emerging market of SiC power MOSFETs and how electrothermal modeling and simulation can actually boost their optimized and reliable design. Accordingly, the project's research questions are listed as follows:

- How can the electro-thermal behavior of SiC MOSFETs be described by means of compact physics-based device models under normal and abnormal operation? Are such models equally suitable for multi-chip power modules? How can the model parameters be properly identified?

- What is the state-of-the-art short-circuit robustness of commercial SiC power MOSFETs? Can simulation help estimating the junction temperature and identifying the failure modes? Additionally, how can the short-circuit capability be enhanced?

- How can we enable the fast system-level simulation of SiC-based power converters? How can we perform mission-profile based analysis and lifetime prediction on a very large timescale, preserving the accuracy of the devicelevel model?

# 1.4 Objectives

In order to answer the aforementioned scientific questions, the presented Ph.D. project focuses on:

- The study and development of advanced modeling approaches for SiC power MOSFETs, ranging from the single device to high power modules, oriented to the reliability prediction and evaluation. The focus is specifically on the implementation, identification and experimental validation of compact electro-thermal models.

- The study of SiC MOSFETs short-circuit behavior and better understanding of their failure modes. Additionally, the device model should feature short-circuit behavior and be able to describe the abnormal condition (with specific focus on the junction temperature) in both discrete devices and power modules. A parametric study of the device internal structure may offer an insight on how to mitigate or suppress the failure modes.

- Assess the accuracy and performance of the models by means of multiphysics FEM simulations, extensive experimental characterization and testing of commercially available devices, performed in the laboratory under a wide range of normal and abnormal operating conditions.

- The implementation of a fast and accurate converter-level electro-thermal model, suitable for the simulation of long or very-long timescales. More specifically, a mission-profile based lifetime estimation algorithm, oriented to the reliability evaluation of SiC power modules, needs to be developed.

# 1.5 Limitations

SiC technology is rapidly evolving and penetrating the PE market. Many manufacturers and research facilities worldwide achieve new device structures and module layouts almost on a monthly basis. Devices technology evolution advances in parallel with the availability of better and better quality semiconductor wafers and doping implantation techniques. Many manufacturers have now reached their 3<sup>rd</sup> generation SiC devices and started adopting trench [29] and super-junction technologies [30], which are soon to be commercialized. Different device structures may result in different electric behavior and require dedicated models and characterization.

On the other hand, very compact packaging solutions, such as flip-chip, presspack, molded modules or double-sided cooling, optimized for WBG devices, are emerging - although the packaging for off-the-shelf part numbers is roughly the same as for Si technology. Such an ever-changing scenario poses the biggest challenge for reliability evaluation. An extensive power cycling campaign may last for several months or years, which might rapidly make the devices under test obsolete. Therefore, reliability documentation about SiC devices is still scarce, which hinders the development and validation of accurate lifetime models.

This goes in addition to all the limitations normally connected to reliability analysis and lifetime prediction. Although thermo-mechanical wear-out failure modes have been considered here, these are not the only stressors the component undergoes during its lifetime. An extensive study of multi-stressors failure mechanisms – such as voltage, humidity, vibrations etc. – is out of the scope of this project. Moreover, the lifetime and damage accumulation models are taken from the available literature and applied to the presented electro-thermal simulation strategy.

In conclusion, the purpose of this work is to provide general-purpose modeling and simulation tools for the reliability and robustness study of SiC power MOSFETs rather than focusing on a specific technology, while necessarily relying on a series of assumptions and trying to quantify the resulting inaccuracies.

### 1.6 Thesis Outline

This Ph.D. thesis sums up the outcome of the Ph.D. project, in the form of "collection of papers". Therefore, the document is structured in two parts: Report and Selected Publications. The report is organized into six chapters. Chapter 1 has provided the introduction of the Ph.D. thesis, stating the background and the scientific questions connected to the project, as well as the research objectives and the list of publications. The device-level modeling and simulation of SiC power MOSFETs are described in Chapter 2. The device physical normal and abnormal behavior is briefly introduced and thus followed by the model description and implementation. A special attention is given to the characterization short-circuit operation. Additionally, the parameter extraction method and experimental validation process are reported. In Chapter 3, the model implementation and validation for both discrete devices and multi-chip power modules is addressed using two Case Studies (I and II) involving commercial devices. The effect of package parasitics on normal and abnormal switching operation is also considered. Once the full device modeling procedure has been presented, the development of a fast and accurate simulation strategy for SiC-based switching applications is addressed in

Chapter 4. The chapter focuses on Case Study III, where a full-SiC module is chosen for the converter-level simulation of a three-phase inverter. Chapter 5 moves towards the mission-profile based reliability prediction for SiC power MOSFET modules, demonstrating that the fast simulation strategy can be suitable for large timescales and support the reliable design of power converters featuring this technology. Finally, a discussion of the project outcomes and concluding remarks are summarized in Chapter 6 together with the perspective future research on this topic. Additionally, a subsection of this last chapter deals with a side topic, which the candidate has encountered during the study period, yielding interesting findings worth to be mentioned briefly.

### 1.7 List of Publications

The research outcomes of this Ph.D. project have been disseminated in the form of journal articles, articles in conference proceedings and book chapters. Together with the publication in which the candidate figures as first author, other works containing his relevant contribution are reported in this Ph.D. thesis. The publications are listed below.

#### **Publications in Conference Proceedings**

**[C1]** L. Ceccarelli, F. Iannuzzo, and M. Nawaz, "PSpice Modeling Platform for SiC power MOSFET Modules with Extensive Experimental Validation," in *Proc. of* 2016 IEEE Energy Conversion Congress and Exposition (ECCE), 2016.

**[C2]** M. M. Hossain, L. Ceccarelli, A. U. Rashid, R. M. Kotecha, and H. A. Mantooth, "An Improved Physics-based LTSpice Compact Electro-Thermal Model for a SiC Power MOSFET with Experimental Validation," in *IECON 2018 - 44th Annual Conference of the IEEE Industrial Electronics Society*, pp. 1011–1016, 2018.

**[C3]** L. Ceccarelli, P. D. Reigosa, A. S. Bahman, F. Iannuzzo, and F. Blaabjerg, "Compact electro-thermal modeling of a SiC MOSFET power module under shortcircuit conditions," in *Proc. of IECON 2017 - 43rd Annual Conference of the IEEE Industrial Electronics Society*, pp. 4879–4884, 2017.

**[C4]** L. Ceccarelli, A. S. Bahman, F. Iannuzzo, and F. Blaabjerg, "A Fast Electro-Thermal Co-Simulation Modeling Approach for SiC Power MOSFETs," in *Proc. of the 32nd IEEE Applied Power Electronics Conference and Exposition*, Tampa, USA, pp. 966–973, 2017.

**[C5]** L. Ceccarelli, R. Kotecha, F. Iannuzzo, and A. Mantooth, "Fast Electrothermal Simulation Strategy for SiC MOSFETs Based on Power Loss Mapping," in *Proc. of 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC)*, 2018.

#### Journal Articles

[J1] L. Ceccarelli, P. D. Reigosa, F. Iannuzzo, and F. Blaabjerg, "A survey of SiC power MOSFETs short-circuit robustness and failure mode analysis," *Microelectronics* Reliability, v. 76–77, pp. 272-276, Sep. 2017.

[J2] L. Ceccarelli, R. Kotecha, F. Iannuzzo, "Impact of Device Aging in the Compact Electrothermal Modeling of SiC Power MOSFETs," *Microelectronics Reliability*, accepted for publication, Apr. 2019.

**[J3]** L. Ceccarelli, R. Kotecha, F. Iannuzzo, and A. Mantooth, "Mission-profilebased lifetime prediction for a SiC MOSFET power module using a multi-step condition-mapping simulation strategy", in *IEEE Transactions on Power Electronics*, Jan. 2019.

[J4] L. Ceccarelli, H. Luo, and F. Iannuzzo, "Investigating SiC MOSFET body diode's light emission as temperature-sensitive electrical parameter," *Microelectronics Reliability*, v. 88-90, pp. 627-630, Sep. 2018.

# Chapter 2 Operation and Modeling of SiC Power MOSFETs

### 2.1 Power MOSFET Structure and Operation

The earliest Field-Effect Transistor (FET) was patented back in 1925 by J. E. Lilienfeld. Later on, in 1959, the first *Metal-Oxide-Semiconductor Field Effect Transistor* (MOSFET) was theorized and invented at Bell Labs [31]. Nowadays, the power MOSFET is the most commonly used power semiconductor controllable switch for low and medium power applications, up to several kilowatts [32]. It is widely spread in household appliances, power supplies and automotive power electronics. Its operation as power switch does not essentially differ from the low voltage MOSFETs, which are used in digital integrated circuits. Their structure, though, in order to achieve high voltage blocking capability, has evolved into the so-called vertically double-diffused MOSFET (VD-MOSFET) layout. The maximum blocking voltage capability for Si-based MOSFETs available off-the-shelf nowadays is limited to approximately 600 V, because of the significant on-state power loss introduced by thicker epitaxial (EPI) layers.

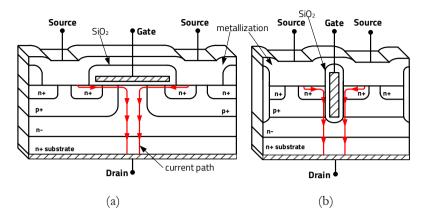

The vertical cross-section of a state-of-art power MOSFET's cell is depicted in Figure 2.1.a. This structure is defined *enhancement mode*, planar *n-channel* VD-MOSFET. The *gate* and *oxide* structures are placed on top of the semiconductor epilayers. The power terminals are the top metallization or *source*, and the bottom surface of the heavily n-doped *substrate*, named *drain*. When the gate terminal is protruding into the semiconductor material, like in Figure 2.1.b, the structure is called *trench* or vertical n-channel U-MOSFET (because of the U-shaped gate structure), with a number of advantages in the achievable power density (the cell width is reduced) and reduced losses. Several thousands of these elementary cells (few µm wide) are paralleled into a chip to increase the current capability of the device.

When a negative voltage is applied across drain and source the p+/n-/n+ structure becomes forward biased and the device starts behaving like a diode. It is important to take into account the presence of this intrinsic or *body diode* when designing circuits with power MOSFETs. The diode structure is often optimized by the manufacturer to avoid the use of external diodes – for example as freewheeling

Figure 2.1. Cross-section of a horizontal, n-channel power MOSFET's cell (a), cross-section of a trench power MOSFET structure (b).

current paths in power converters – although its conduction and switching performance is always well below that of a state-of-the-art power diode because of its peculiar geometry.

The structure and operation of SiC power MOSFETs does not differ much from that of their Si counterparts. The wide energy bandgap of SiC, though, as mentioned in Chapter 1, allows for a much thinner and narrower cell structure with both planar and trench technology [33]. Therefore, although the normal on-state, reverse conduction and switching behavior, resembles closely that of a Si power MOSFET, the instabilities and failure modes occurring outside the device Safe Operating Area (SOA), are yet to be fully understood and mitigated.

#### 2.1.1 Short Circuit Operation and Failure Modes

SiC devices come with significantly smaller die size and higher current density in comparison to traditional Si devices. For example, a commercial 2<sup>nd</sup>-generation 1.2 kV / 36 A SiC MOSFET chip [34] measures 10.4 mm<sup>2</sup> against the 41.4 mm<sup>2</sup> of a Si IGBT with equivalent rating [35], with an almost four times higher current density. The design of power semiconductor chips aims to miniaturization, in order to maximize production, optimize costs and fully exploit the material properties. With SiC, this is possible thanks to the aforementioned physical characteristics, but inevitably leads to a higher thermal stress on the device during both normal and abnormal operations. When abnormal conditions like *short circuit* (SC) or *unclamped inductive switching* (UIS) occur, the smaller die size turns out to be a major downside for the robustness of such devices. The extremely high heat generation density in microsecond-scale time intervals determines a significant temperature increase within the die, which can permanently damage the semiconductor/oxide interface and top metallization and lead to different failure mechanisms. The characterization

and modeling of SC operating conditions is, therefore, of great interest in the robustness evaluation of SiC MOSFETs.

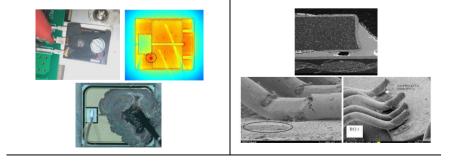

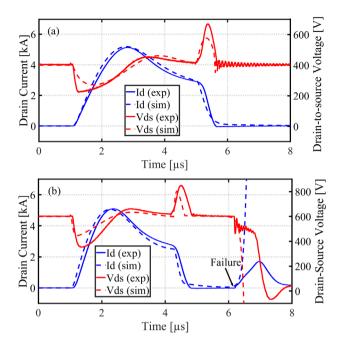

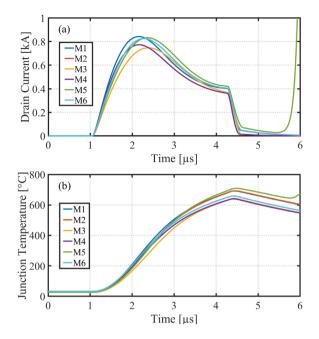

The withstanding time and failure modes observed during the SC testing of discrete SiC MOSFETs in the last few years – about 40 reported failures in total – were surveyed in [J1]. Based on several literature contributions [16], [22], [37]–[41], only part of the tested 1.2 kV-rated discrete devices and none of the multichip modules (from different manufacturers) could withstand more than 10  $\mu$ s SC time with a drain-to-source voltage of 600 V. These results were further confirmed by the experiments carried out using the non-destructive test (NDT) facility at Aalborg University, several power modules and discrete components were tested to determine their SC withstanding capability.

According to the studies in [42]–[44], it became clear that the root cause of all the SC failure modes is the steep junction temperature increment, reaching rates of about  $300-400^{\circ}C/\mu s$  when the nominal drain-to-source voltage is applied. So far, two major instabilities have been observed in the literature:

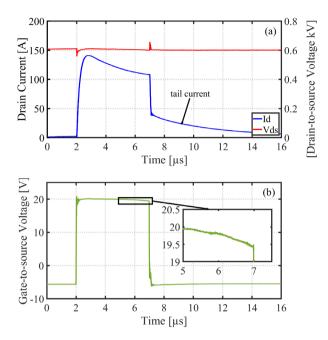

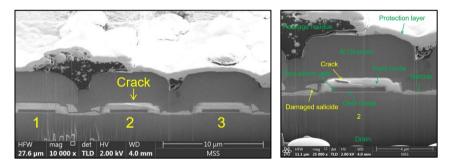

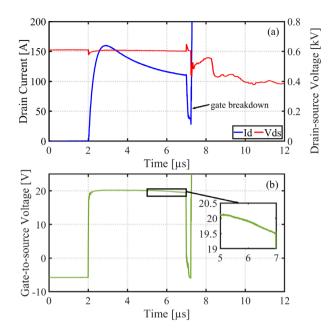

Gate oxide breakdown: the intrinsic reliability of SiC MOSFETs' gate oxide has been object of several studies, such as [45]-[47], in the latest years. In particular, reducing the SiO<sub>2</sub> thickness in order to keep the gate voltage threshold at reasonable values, together with the intrinsic roughness of the SiO<sub>2</sub>/SiC interface, makes the gate structure significantly prone to high-voltage and hightemperature related failure and degradation phenomena. In the test results reported in Figure 2.2, one can clearly see a device (part number C2M0080120D [34]) catastrophic failure due to gate oxide breakdown after a 5.2 µs short-circuit pulse at 600 V drain-to-source voltage and 150°C case temperature. The postfailure analysis of this device was made impossible by the complete destruction of the chip and epoxy resin encapsulant. Before the device catastrophic failure though, a permanent degradation of the oxide structure was observed. The precursor of this mechanism is the on-state gate voltage drop, which can be seen in Figure 2.2, and the increase of the gate leakage current. An in-depth investigation of a degraded device was carried on in [48], where a Focused Ion Beam (FIB) cut of the device was performed to expose a cross-section view of the damaged cell, as shown in Figure 2.3. Cell number 2 exhibits a crack in the SiO<sub>2</sub>, spanning from the polysilicon gate finger to the source contact Al metallization. Additionally, a structural modification in the metallization and salicide occurs, suggesting an excessive thermal stress focused in the semiconductor-oxide interface. Similar results, with more severe material alterations, were observed in [49]. The root cause of the oxide crack is yet to be discovered, though it is clear that an extreme temperature increase rate is contributing to this failure mode.

Figure 2.2. Catastrophic gate failure of a 1.2 kV/36 A SiC MOSFET [J1]. Drain current and drain-to-source voltage waveforms (a); gate-to-source voltage (b).

Figure 2.3. Focused Ion Beam (FIB) cut of a damaged device after SC displaying oxide crack on cell number 2 [22].

If the temperature increases enough to reach the Al melting point (660°C) the metal can fill the crack and create a low-resistance conductive path between gate and source contacts, which makes the device no longer controllable and leads to catastrophic failure.

Figure 2.4. SC waveforms of a 1.2 kV/36 A SiC MOSFET exhibiting a large tail current [J1]. Drain current and drain-to-source voltage waveforms (a); gate-to-source voltage (b).

Thermal runaway: the behavior reported in Figure 2.4 has also been observed during experiments. Here, after a 5 µs SC pulse at 600 V, the device [34] displays a current tail of significant amplitude, which is rather atypical in unipolar devices. The studies in [42], [44] have successfully correlated this mechanism to the increasing thermal generation of minority carriers (holes) across the body/drift junction due to the high heat energy released during the SC event. These carriers are pushed towards the source terminal by the high electric field creating a leakage current. The voltage drop caused by the current through the body resistive path may cause the activation of the intrinsic bipolar-junction transistor (BJT) and lead to a self-sustaining feedback mechanism that eventually results to the device destruction via gate breakdown. In fact, the activation may occur in one cell or few adjacent ones, and create an hot spot or current filament, which focuses most of the SC current in a very limited area of the chip [50], [51]. This kind of failure, as reported in [[1], can occur several  $\mu$ s after the device turns off. Moreover, it is not excluded that the threshold voltage drift due to extreme high temperature may accelerate this failure mode by preventing a complete channel shutdown [52].

# 2.2 State-of-the-art SiC MOSFET Compact Modeling

The main aim of compact device modeling is to obtain a description of the onstate characteristics and the switching behavior as a function of the applied voltage and currents, the temperature conditions and intrinsic physical characteristics – such as material, geometry and doping level. The model always requires a necessary tradeoff between mathematical complexity and computational speed. The criteria a designer can apply when making such tradeoff are the desired accuracy and the simulation time, together with the intended application for the model. Usually, very simple models provide fast simulations but lack an insight into the device physic and, consequently, accuracy. On the other hand, a complex physics-based model provides accurate estimation of the device behavior but also require longer simulation time.

Power semiconductor device models usually do not have the need for the detailed small-signal behavior required in analog electronic circuit simulation. They are rather used as switches in power electronic applications. This means that the most critical features which should be captured in a device model are: the conduction properties of the various semiconductor layers, influencing the on-state power loss; and the internal capacitances defining the switching speed and charge effects. It is also important to model the variation of these parameters with temperature, accounting for the device self-heating using lumped static or dynamic thermal models. Additionally, if the abnormal conditions are meant to be simulated, the model should include proper elements, such as breakdown and avalanche mechanisms, extreme temperature conditions, activation of parasitic devices, etc.

Compact physics-based or partially physics-based (semi-physics) models are the main focus of this work, since they provide the desired tradeoff between accuracy

Figure 2.5. Typical equivalent lumped circuit of a power MOSFET.

and simulation time for the circuit-level evaluation of SiC MOSFETs and power modules, both in normal and abnormal operation. Additionally, they are easy to identify using parameter extraction sequences based on static and switching tests or datasheet curves, and do not require a detailed knowledge of the device internal geometry, which is almost never provided by the manufacturer.

A good classification of the available models for SiC power MOSFETs can be found in [53]. Table 2.1 offers an overview of the noteworthy physics- and semiphysics based compact models proposed in the literature during the last decade.

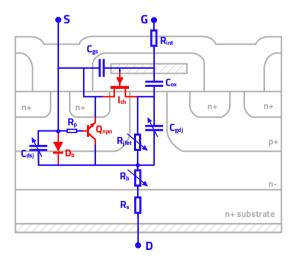

Figure 2.5 shows a general equivalent circuit, which highlights the main Si/SiC power MOSFET features traditionally modeled in the literature. The circuit elements are overlapped to a single MOSFET cell for explanatory purpose, but their parameters are lumped and scaled up to describe the whole chip architecture, made up of several thousand of elementary cells in parallel. It is worth nothing that not all the models reported in Table 2.1 feature the whole circuit and different analytical formulations may appear for each of the elements.

The model originally developed by McNutt and others in 2007 [54] represents one of the first steps in the compact physics-based modeling of SiC MOSFETs and some of its feature have inspired later works, including the presented project. This model is based on the channel current  $I_{ch}$  expression provided in the well-established Hefner IGBT model [55].

| First Author       | Year | Main Contributions                                                                     | Implementation |

|--------------------|------|----------------------------------------------------------------------------------------|----------------|

| Mc Nutt [56], [54] | 2007 | Improved channel current<br>description and simple<br>parameter extraction<br>sequence | IMPACT, MAST   |

| Potbhare [57]      | 2008 | Detailed interface trap<br>modeling                                                    | Not indicated  |

| Fu [58]            | 2012 | Non-uniform current<br>distribution in the JFET<br>region                              | PSpice         |

| Cui [59]           | 2012 | <i>n-th</i> power law MOSFET model                                                     | PSpice         |

| Mudholkar [60]     | 2014 | Based on McNutt with<br>datasheet-driven parameter<br>extraction                       | SABER          |

| Sun [61]           | 2014 | Wide temperature range                                                                 | PSpice         |

| Peng [62]          | 2016 | Body diode model                                                                       | Not indicated  |

| Riccio [63]        | 2017 | Suitable for simulations outside SOA                                                   | SPICE          |

| He [64]            | 2017 | Scalability to different<br>device layouts and non-<br>linear features                 | SPICE          |

TABLE 2.1. SIC MOSFET COMPACT MODELS IN LITERATURE

The expression was refined by introducing temperature-dependency and two separate current components with different gate threshold voltage, which reproduce the gradual transition from linear to saturation region observed in the 1<sup>st</sup> generation of SiC MOSFETs, now less common. The parasitic MOSFET capacitors  $C_{gs}$  and  $C_{ox}$ are assumed constant, whereas the  $C_{dsj}$  and  $C_{gdj}$  are determined by the depletion region thickness. Body diode, intrinsic BJT and JFET region are not described, and the only contributions to the on-state resistance are  $R_b$  and  $R_s$ . More noticeably, the paper proposed an intuitive parameter extraction sequence that offers the possibility to be implemented and automated in many software environments – the original was coded in IMPACT while the model was developed in MAST. In 2014, another work [60] presented a new simplified parameter extraction sequence for the same model, which only requires data and curves available in the datasheet of commercial devices.

At the early stages of SiC MOSFET manufacturing, the performance and reliability limitation were mostly connected to the large number of defects found at the SiC/SiO2 interface. This is why models like [57] in 2008, filled the gap in the physics-based modeling of charge trapping and Coulomb scattering at the rough semiconductor-oxide interface.

The modeling activity evolved mostly towards the inclusion of additional features, like non-uniform current distribution in the JFET region in [58] and wide temperature range operation [61]. Moreover, a model for the body diode was introduced in [62], featuring a rather detailed description of the charge storage effects and reverse recovery, using a Fourier series solution of the ambipolar diffusion equation (ADE). The parasitic BJT has only been included in recent models, like [63], to describe the device behavior under abnormal (off-SOA) operation.

Additionally, semi-physical models, i.e. partly behavioral, models are sometimes provided by the manufacturers, such as [65]. Their performance has also been explored and compared to that of a physics-based model in this work.

### 2.3 Model Description and Implementation

The SiC MOSFET device model used for the circuit simulations in this project collects many of the features contained in the aforementioned physics-based model, aiming to provide a compact implementation and an intuitive parameter extraction sequence. The model formulation and complexity has changed throughout the project, depending on the degree of accuracy required in the specific case study. Table 2.2 contains the complete list of equations and parameters enclosed in the model for both normal and abnormal device behavior.

The channel current expressions are divided into two regions, namely *linear* region and *saturation* region. the temperature-dependent gate threshold voltage  $V_T(T_j)$  and the pinch-off voltage factor  $P_{vf}$  determine the boundary between the two regions. Two lumped transconductance factors,  $K_f$  and  $K_p(T_j)$ , define the current intensity for the chip. The lumped on-state resistance is divided into three contributions: the JFET region resistance  $R_{jfet}$ , drift region resistance  $R_b$  and substrate resistance  $R_s$ .

| Channel Current                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{MOS} = \frac{K_f K_p \left[ (V_{gs} - V_T) V_{ds} - \frac{P_{vf}^{y-1} V_{ds}^y (V_{gs} - V_T)^{2-y}}{y} \right]}{1 + \theta (V_{gs} - V_T)}  for  V_{ds} \le \frac{V_{gs} - V_T}{P_{vf}}  (1)$ |

| $I_{MOS} = \frac{K_p (V_{gs} - V_T)^2}{1 + \theta (V_{gs} - V_T)}  for  V_{ds} > \frac{V_{gs} - V_T}{P_{vf}}  (2)$                                                                                  |

| $y = \frac{K_f}{K_f - \frac{P_{vf}}{2}} $ (3)                                                                                                                                                       |

| MOSFET On-State Behavior                                                                                                                                                                            |

| $R_b = \frac{W_b - W_{dsj}}{qAN_d \mu_n}  (4) \qquad R_{jfet} = \frac{W_{jfet}}{qA_{jfet}N_d \mu_n}  (5) \qquad R_s = \frac{W_s}{qAN_s \mu_n}  (6)$                                                 |

| $\mu_n(T_j) = \frac{947}{1 + \left(\frac{N_b}{1.94 \cdot 10^{17}}\right)^{0.61}} \cdot \left(\frac{T_j}{300 \text{ K}}\right)^{k_{\mu}} $ (7)                                                       |

| Intrinsic Capacitances                                                                                                                                                                              |

| $n_i(T_j) = 4 \cdot 10^{16} T_j^{1.5} e^{-\frac{19115.8}{T_j}}  (8) \qquad V_{bi}(T_j) = \frac{kT_j}{q} \ln\left(\frac{1 \cdot 10^{16} N_d}{n_i^2}\right)  (9)$                                     |

| $W_{dsj} = \sqrt{\frac{2\varepsilon_{sic}(V_{ds} - V_{bi})}{qN_d}}  (10) \qquad C_{dsj} = \frac{A_{ds}\varepsilon_{sic}}{W_{dsj}}  (11)$                                                            |

| $W_{gdj} = \sqrt{\frac{2\varepsilon_{SiC}(V_{dg} - V_{bi})}{qN_d}}  (11) \qquad C_{gdj} = \frac{A_{gd}\varepsilon_{SiC}}{W_{gdj}}  (12)$                                                            |

| $C_{gd} = \begin{cases} C_{ox} & for \ V_{ds} \le V_{gs} - V_{Td} \\ C_{ox} \parallel C_{gdj} & for \ V_{ds} > V_{gs} - V_{Td} \end{cases} $ (13)                                                   |

| Body Diode Current                                                                                                                                                                                  |

| $I_{bd} = i_s \left( e^{-\frac{V_{ds}}{nV_{bl}}} - 1 \right) \cdot e^{-\frac{V_{gs}}{k_{bd}}}  (14)$                                                                                                |

| Short Circuit Behavior                                                                                                                                                                              |

| $I_{g,th} = \frac{q A n_i}{\tau_g} \sqrt{\frac{2\varepsilon_{SiC}}{q} \left(\frac{N_d + N_p}{N_d N_p}\right) V_{ds}}  (15) \qquad R_p = \frac{W_p}{q N_p \mu_p (A - A_{jfet})}  (16)$               |

| $I_{npn} \cong \beta \cdot I_{g,th}  (17)$                                                                                                                                                          |

| Temperature Scaling                                                                                                                                                                                 |

| $V_T(T_j) = V_{T0} - V_{T1}(T_j - 300 \text{ K})  (18)  K_p(T_j) = K_{p0} \cdot \left(\frac{T_j}{300 \text{ K}}\right)^{K_{p1}} (19)$                                                               |

# TABLE 2.2. SIC MOSFET MODEL EQUATIONS

These values are calculated based only on the chip geometry and SiC material properties. This also applies to the voltage dependent capacitances  $C_{gd}$  and  $C_{ds}$ , determined by the respective depletion region thickness ( $W_{dsj}$  and  $W_{gdj}$ ). A rather simple expression, contained into the standard SPICE diode model, is used to model the body diode. The thermally generated current  $I_{g,th}$  expression derives from the Shockley-Read-Hall semiconductor theory. The parasitic BJT's current amplification is approximated using a gain factor  $\beta$ .

The model has been implemented in SPICE code and can be interpreted by both PSpice and LTspice simulation environments [C1, C2]. The reason for the use of this software lies in the good tradeoff between simulation speed, coding complexity and popularity. Creating a SPICE platform for the compact physical modeling of SiC devices and power modules can provide a useful framework for the prospective designers of WBG-based converters. Moreover, it is relatively easy to interface SPICE models with other software environments, such as MATLAB or ANSYS Simplorer, which ensures great flexibility for multi-physics co-simulation at a system level. The full SPICE code for a discrete component is reported in the Appendix.

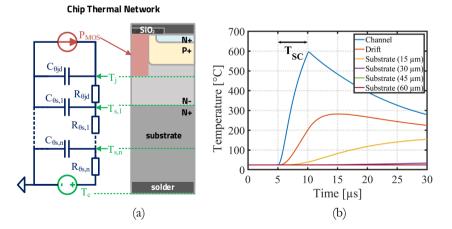

#### 2.3.1 Including Self Heating

The heat conduction in an isotropic homogeneous material can be described by (20). The equation models the temperature T evolution, when a one-dimensional heat flow along the x-axis is assumed for simplicity.  $\lambda$ ,  $\rho$  and c respectively stand for the material's thermal conductivity, its density and its specific heat.

$$\frac{\partial^2 T}{\partial x^2} = \frac{c \cdot \rho}{\lambda} \cdot \frac{\partial T}{\partial t}$$

(20)

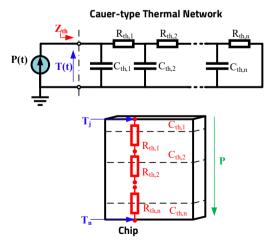

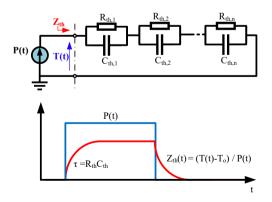

Figure 2.6. Cauer-type impedance thermal network

Assuming that the heat conduction can be compared to an electrical transmission line (without inductance) where a RC network defines the system time constant [66], the equation becomes (21). The equivalent thermal resistance  $R_{\text{th}}$  and capacitance  $C_{\text{th}}$  account for the thermal properties of the material.

$$\frac{\partial^2 T}{\partial x^2} = R_{th} C_{th} \cdot \frac{\partial T}{\partial t} \frac{\partial T}{\partial t}$$

(21)

Lumped impedance thermal networks have been used for a long time to model the thermal response of power electronic systems in compact circuit simulations [67], [68]. Two classic representations for a thermal network have become the standard nowadays: the *Cauer*-type and the *Foster*-type.

The *Cauer*-type thermal network in Figure 2.6 reflects the physical geometry of the material (or stack of layers of different materials) through which the heat spreading occurs. Its elements can be directly calculated by dividing the considered geometry in an arbitrary number of layers with finite volume along the heat propagation path. The *i-th* element's thermal time constant ( $R_{th,i}$ · $C_{th,i}$ ) depends exclusively on its thermal and geometrical properties and can be calculated as in (22) and (23),

$$R_{th,i} = \frac{d}{\lambda \cdot A} \quad (22) \qquad \qquad C_{th,i} = c \cdot \rho \cdot d \cdot A \quad (23)$$

Where d is the thickness of the *i-th* element and A is the heat conducting cross section. This thermal impedance model offers better results when studying simple geometries and heat flow condition, such as a single homogeneous chip with the junction located in proximity to the top surface. Moreover, being a physical equivalent of the system structure, this network provides correct information about the temperature in each of the internal nodes. Compact one-dimensional Cauer networks can only roughly estimated the temperature when several layers with different material properties, geometries and multiple heat sources coexist, such as

Figure 2.7. Foster-type impedance thermal network

in a multichip power module package.

Another way to obtain a thermal equivalent circuit is to fit the transient temperature step response of a system to a defined power source with an analytical function. This approach is very useful when the system is already available as a prototype and its detailed geometry and materials are not fully known. The usual procedure consists in measuring the temperature evolution T(t) when a constant power dissipation P is generated in the chip until the thermal equilibrium is reached ("heating curve") or when the power is turned off and the system cools down to the ambient temperature  $T_0$  ("cooling curve"). Both these transients can be described by means of the analytical step response function in (24), whose electrical equivalent is a chain of parallel RC elements, as the one depicted in Figure 2.7.

$$Z_{th}(t) = \frac{T(t) - T_0}{P} = \sum_{i=1}^{n} R_{th,i} \left( 1 - e^{-\frac{t}{R_{th,i}C_{th,i}}} \right)$$

(24)

This "transfer-function" representation of the system's thermal behavior does not provide any information about the temperature evolution within the structure, which is modeled as a black box with a defined transfer function. Segmenting the network to access the voltage (temperature) in one of the internal nodes would require measuring the thermal response of the system in that point and reiterate the fitting. Besides, the number of RC elements for each segment and their order is arbitrary and dependent on the fitting accuracy. The Foster-type thermal network is suitable for complex systems and, most importantly, can be extracted by running transient FEM simulations, as proven in [69], including thermal cross coupling effects between different heat sources [70].

Since the material thermal properties change with temperature, the accuracy of these representations is limited to a defined range of injected power. Device operation outside this range requires new RC element values, as demonstrated in [71]. Nevertheless, thermal networks represent a very versatile and useful tool when implementing fast and compact electrothermal models.

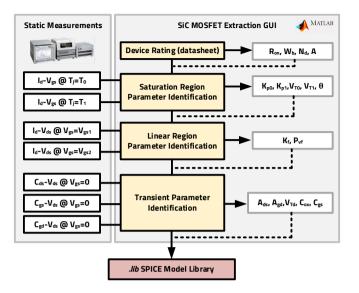

#### 2.3.2 A MATLAB-based GUI for parameter extraction

A graphic-user interface (GUI) was developed in MATLAB for the parameter identification of the presented model based exclusively on static I-V and C-V measurements and information available from the device datasheet [C1]. The steps used for the extraction sequence are similar to those reported in [54], [60] and are depicted in the flowchart in Figure 2.8. The device breakdown voltage, on-state voltage and current ratings are first used to extract the device active area and drift-region properties. Thus, it is possible to identify the MOSFET forward conduction characteristics in the saturation and linear region, by uploading I-V curves at different temperature and gate bias levels. Finally, the C-V characteristics are used to extract the capacitance parameters defining the device's switching transient. All the parameters are found by rearranging the model equations. The GUI shows the

Figure 2.8. Parameter extraction sequence flowchart.

measured characteristics against the simulated ones, allowing the user to manually tune the parameters for a better fitting. Eventually, when the sequence is complete, the GUI allows the user to save the full parametrized SPICE model library (*.lib* file) of the device. The main concept in this work was to provide a complete and userfriendly MATLAB tool to create a turn-key PSpice/LTspice compatible model without necessarily needing SPICE coding skills.

### 2.3.3 Experimental Setup for Model Validation

Static I–V and C–V measurements are carried out in order to extract the model parameters and verify the accuracy of the model over the defined range of operation. The static measurements are pulsed, to avoid self-heating, and are generally performed by using a curve tracer / device analyzer. A Keysight B1506A fixture has been used for most of the static testing during the project, allowing full static characterization of the device up to 10 kV/1.5 kA and 150°C, by using a controlled airflow heater.

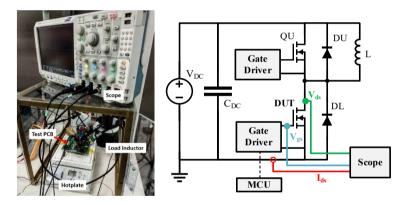

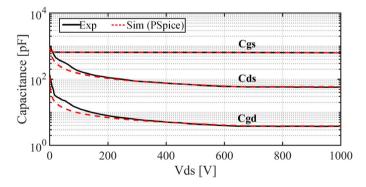

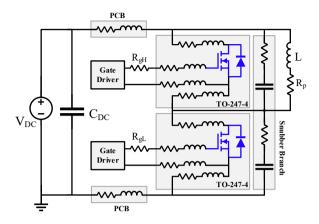

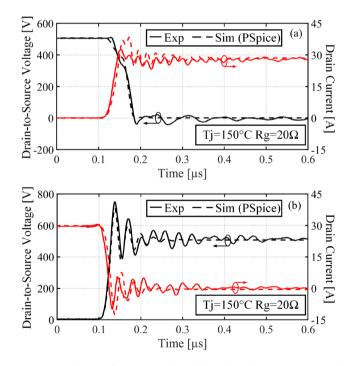

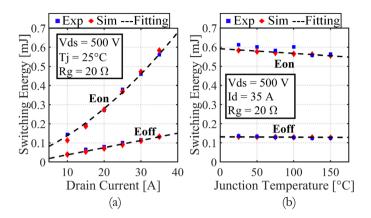

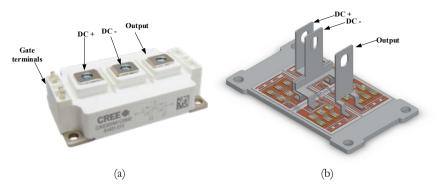

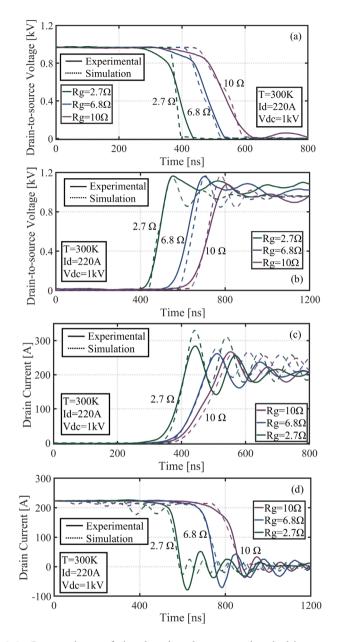

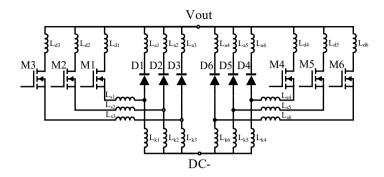

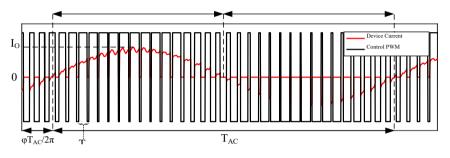

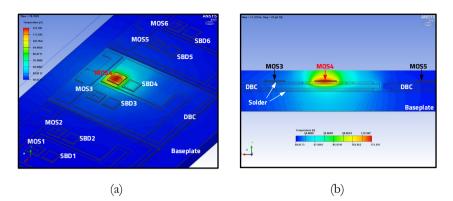

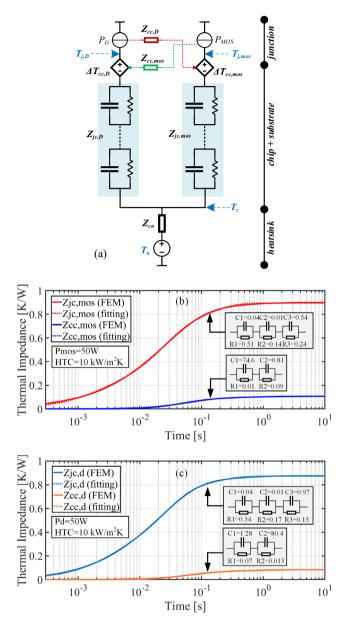

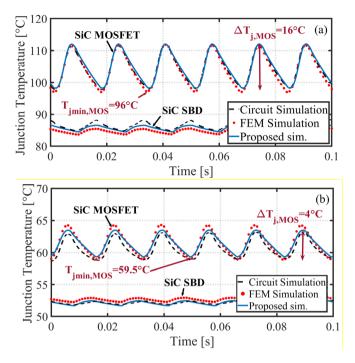

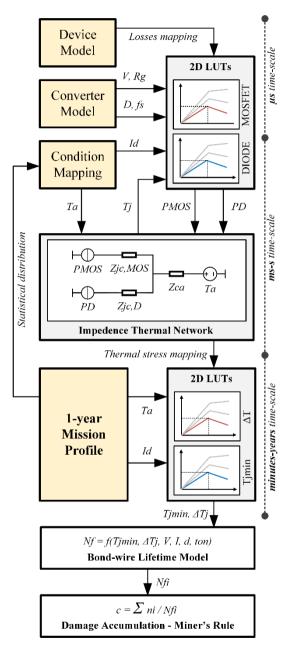

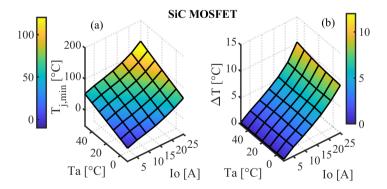

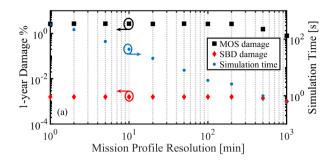

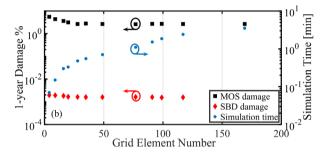

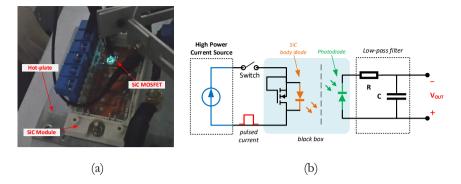

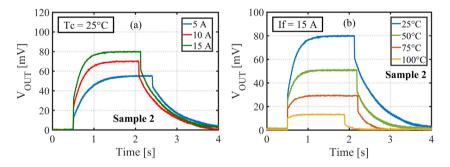

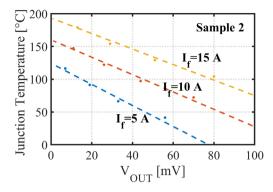

A double-pulse test (DPT) setup, like the one shown in Figure 2.9 [C5] is usually built to validate the simulated switching behavior of the device against experimental waveforms. The design and measurements methods used in a DPT are crucial for obtaining clear waveforms and calculating the device switching energy loss correctly. Especially when dealing with WBG devices, the presence of significant parasitic inductance and capacitance in the power and gate current loops and the very high switching dV/dt and dI/dt, will provoke undesired oscillations and couplings [72].