Aalborg Universitet

# System and Circuit Design Aspects for CMOS Wireless Handset Receivers

Mikkelsen, Jan H.

Publication date: 2005

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Mikkelsen, J. H. (2005). System and Circuit Design Aspects for CMOS Wireless Handset Receivers. Department of Electronic Systems, Aalborg University.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

PhD Dissertation ISSN 0908-1224

# System and Circuit Design Aspects for CMOS Wireless Handset Receivers

Jan Hvolgaard Mikkelsen, M.Sc.E.E.,

E-mail: jhm@es.aau.dk

**RF Integrated Systems & Circuits (RISC) Division,** Department of Electronic Systems, Aalborg University, Niels Jernes Vej 12, DK-9220 Aalborg, Denmark.

# TITLE

System and Circuit Design Aspects for CMOS Wireless Handset Receivers

# AUTHOR

Jan Hvolgaard Mikkelsen,

RF Integrated Systems & Circuits (RISC) Division, Aalborg University, Niels Jernes Vej 12, DK–9220 Aalborg East, Denmark

### **ADJUDICATORS**

Professor, Dr. Techn. Erik Bruun, Technical University of Denmark, Lyngby, Denmark Technology Manager, Jens Christian Lindof, Texas Instruments, Aalborg, Denmark Associate Professor, Ph.D., Peter Koch, Aalborg University, Denmark

### **SUPERVISOR**

Professor, Dr. Techn. Torben Larsen, Aalborg University, Denmark

# ABSTRACT

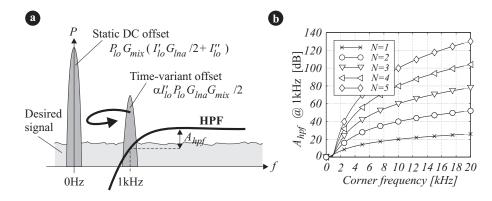

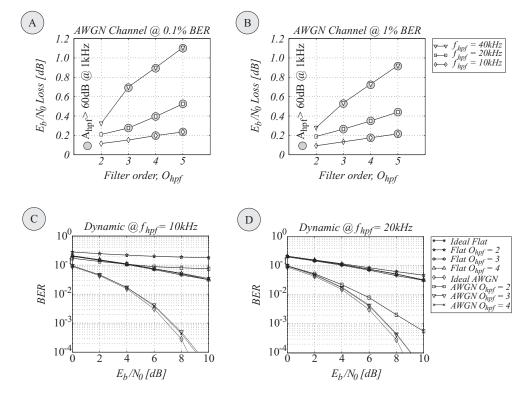

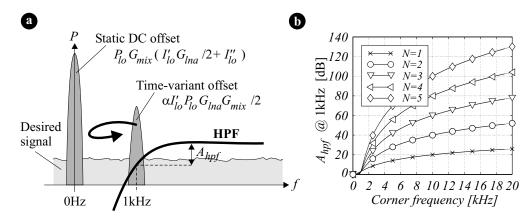

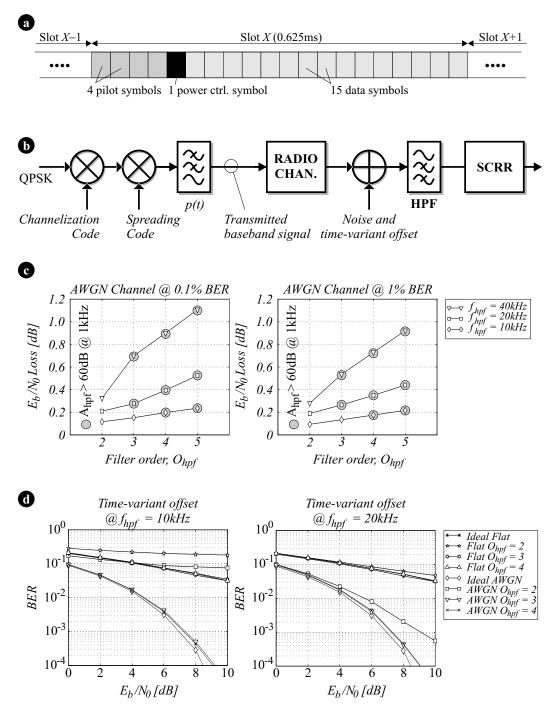

The work documented in this dissertation deals with system and circuit design aspects for Complementary Metal Oxide Semiconductor (CMOS) implementations of wireless handset receivers. The work has been divided into three parts: Part I of the dissertation is concerning CMOS as an RF technology, Part II deals with receiver architectures on a system level, and Part III considers RF circuit and device implementations in CMOS. Through comparison a historic background to the use of CMOS in cellular applications is provided. The tremendous developments in CMOS technology are considered and the analog short-comings are evaluated. The lack of high quality passive devices, inductors in particular, is found to be one of the major obstacles in achieving a fully integrated RF design based on CMOS. Part II starts with an overview of different receiver architectures and a discussion of some fundamental problems in relation to CMOS integration. Based on the standards provided for Universal Mobile Telephone System (UMTS) requirements are derived for a UTRA/FDD (UMTS Terrestial Radio Access - Frequency Division Duplex) direct-conversion receiver. The direct-conversion receiver is chosen in spite of the well-known problem with DC-offset. The wideband nature of the UMTS signal opens up for simple DC-offset cancellation schemes. In line of this the effect of highpass filtering as a means to reduce the DC-offset is pursued. Based on link-simulations a correlation between DC-offset cancellation and Bit Error Ratio (BER) is established. To

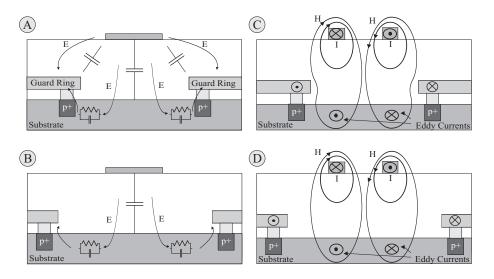

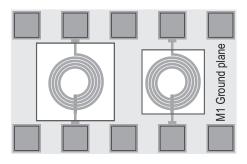

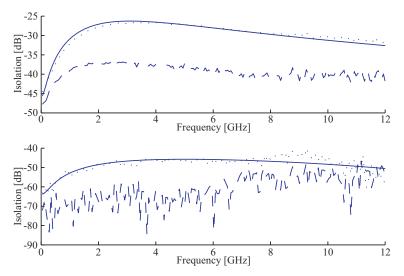

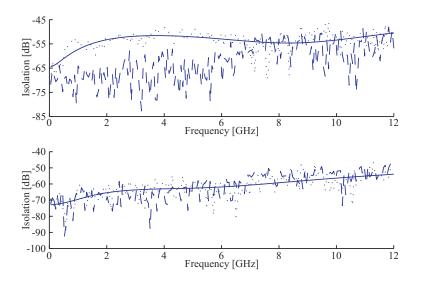

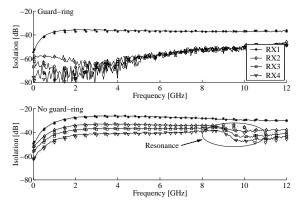

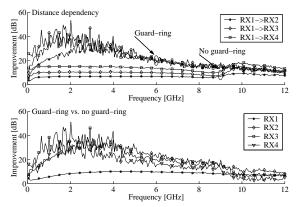

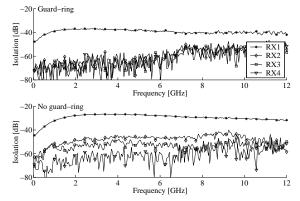

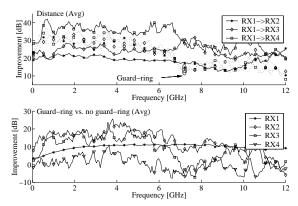

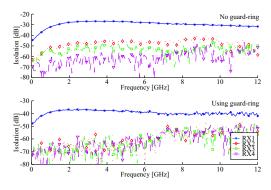

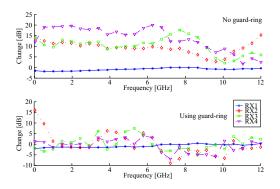

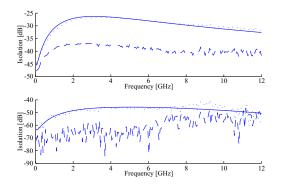

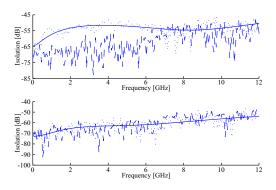

be used in the receiver planning it is found that a third to fourth order Butterworth filter provides sufficient DC-offset cancellation while degrading  $E_b/N_0$  only by 0.2 – 0.3dB. When an implementation performance surplus is available it is common practice to simplify receiver planning and employ a full separation of different distortion mechanisms. This approach is not an option when a low-cost silicon technology is the target. For a UTRA/FDD receiver the disturbance scenario is complicated as a consequence of continuos transmission and reception. To manage this a simple voltage domain approach to receiver planning is presented. The method allows all interferring components to be considered simultaneously whereby a more optimum receiver design results in comparison with traditional calculations based on manual distribution of distortion effects. Aiming for CMOS implementation the UTRA/FDD requirements are used to specify requirements for all receiver stages in the direct-conversion receiver. Having requirements for both low noise and especially high linearity the mixer stands out as one of the more challenging blocks and has therefore been selected for CMOS implementation in Part III. A modified Gilbert cell mixer topology forms the basis for the quadrature mixer design. The modification is shown to have a 3dB noise advantage over traditional quadrature mixers. As a drawback the mixer is sensitive towards imbalance in the LO voltage levels and for that matter it is necessary to have an accurate LO feed. For direct-downconversion mixers LO leakage represents a significant source to performance degradation. Due to antennalike characteristics and typically large areas the inductor is especially prone to crosstalk. To minimize the coupling to and from inductors the traditional approach is to surround these by guard-ring structures. While guard-rings improve isolation they also form a trade-off between device area and performance. The relation between guard-ring area and inductor performance is evaluated and it is shown that, depending on the size of the guard-ring, the Q-value reduction may be as high as 16% at 2GHz. In continuation of this, various coupling effects for CMOS onchip co-planar spiral inductors are presented. Simple guard-rings are shown to improve isolation between closely spaced adjacent inductors by approximately 10-15dB. At larger distances the gain of having a guard-ring reduces and is eventually found to be zero at a distance of  $1000\mu$ m. For modeling purposes an extended lumped element model is proposed and found to fit very well with measurements.

# TITEL

System- og Kredsløbs-designaspekter vedrørende CMOS Håndsæt til Trådløs Kommunikation

## FORFATTER

Jan Hvolgaard Mikkelsen,

RF Integrated Systems & Circuits (RISC) Divisionen, Aalborg Universitet, Niels Jernes Vej 12, DK–9220 Aalborg Øst, Danmark

### **OPPONENTER**

Professor, Dr. Techn. Erik Bruun, Danmarks Tekniske Universitet, Lyngby, Danmark Technology Manager, Jens Christian Lindof, Texas Instruments, Aalborg, Danmark Lektor, Ph.D., Peter Koch, Aalborg Universitet, Danmark

# VEJLEDER

Professor, Dr. Techn. Torben Larsen, Aalborg Universitet, Danmark

# RESUMÉ

Arbejdet dokumenteret i denne afhandling omhandler aspekter af system og kredsløbsdesign for trådløse modtagere og implementering af disse i Complementary Metal Oxide Semiconductor (CMOS) teknologi. Arbejdet er delt op i tre dele, hvoraf del I omhandler RF egenskaberne for CMOS teknologi, del II omhandler radio-modtagere på arkitekturnivau, og del III omhandler implementation af RF kredsløb og komponenter i CMOS teknologi. Gennem sammenligninger præsenteres et historisk forløb, hvor anvendelsen af CMOS til implementering af trådløse applikation er i fokus. Den intense udvikling CMOS har gennemgået beskrives, og begrænsningerne i forhold til analog kredsløbsdesign vurderes. Her viser det sig at, manglen på spoler med tilstrækkelig høj Q-faktor er en af de væsentligste problemer i forhold til at kunne realisere fuldt integrerede RF kredsløb i CMOS. Del II starter med en gennemgang af forskellige modtager-arkitekturer og en diskussion af deres fundamentale problemer i relation til en integration i CMOS. Ud fra standarderne for Universal Mobile Telephone System (UMTS) udledes kravene til en direct-conversion-modtager til UTRA/FDD (UMTS Terrestial Radio Access - Frequency Division Duplex) systemet. Direct-conversion-modtageren vælges til trods for det velkendte problem med DC-offset. Den store båndbredde anvendt i UMTS gør det muligt at anvende simple teknikker til reduktion af DC-offset. I forlængelse af dette undersøges det om højpas-filtrering er en farbar vej til reduktion af DC-offsettet. Baseret på linksimulering etableres en sammenhæng mellem DC-offset-reduktion og bitfejl-sandsynlighed (BER). Til brug i den efterfølgende modtager-designfase afdækkes, at et tredie- eller fjerdeordens Butterworth filter giver tilstrækkelig reduktion af DC-offsettet samtidig med at  $E_b/N_0$ kun reduceres med 0.2 – 0.3dB. Forudsat at den anvendte implementeringsteknologi kan levere et performanceoverskud, er det normal praksis at simplificere modtager designet ved at betragte de forskellige forstyrrende mekanismer seperat. Denne praksis er ikke mulig når en low-cost Silicium-implementering er målsætningen. I UTRA/FDD-systemet foregår signaltransmission og modtagelse samtidigt hvilket øger kompleksiteten af modtager-designopgaven. Til håndtering af dette benyttes en fremgangsmetode, der bygger på spændingsdomænebeskrivelser. Metoden gør det muligt at betragte samtlige forstyrrende signaler samtidigt, hvorved et mere optimalt modtagerdesign kan opnås til sammenligning med traditionelle teknikker baseret på en manuel fordeling af de forstyrrende effekter. Med en implementering i CMOS for øje specificeres kravene til alle modtagerblokke i en direct-conversion-modtager ud fra UTRA/FDD-kravene. Med krav om både lav støj og høj linearitet skiller mixeren sig ud som en udfordrende blok, hvorfor denne vælges til implementering i del III. Her danner en modificeret Gilbert-cell-mixer basis for et quadratur-mixerdesign. Modifikationen vises at have en støjfordel på 3dB i sammenligning med mere traditionelle implementeringer. En ulempe ved den valgte topologi er, at den er følsom overfor ubalance i LO-signalet. For en directconversion-modtager er LO-overhør en væsentlig kilde til performancereduktion. På grund af dens antennelignende udformning og relativt store størrelse er spolen særdeles tilbøjelig til skabe overhør. For at minimere overhør til og fra spoler benyttes normalt guard-ringstrukture. Udover at reducere overhør medfører guard-rings også et trade-off mellem komponent-areal og performance. Sammenhængen mellem guard-ringareal og spole-performance analyseres og det vises, at afhængig af størrelsen på guard-ringen, kan reduktionen i Q-faktor være helt op til 16% ved 2GHz. I forlængelse af dette gennemgås forskellige kilder til overhør og det vises, at simple guard-rings kan reducere overhør mellem tætplacerede spoler med omkring 10 - 15dB. Ved større afstande reduceres effekten af guard-ringen og for en afstand på 1000µm ses ikke længere nogen effekt. Til anvendelse i simuleringer foreslås en model baseret på passive komponenter, og modellen viser sig at stemme særdeles godt overens med målinger.

# Preface

This dissertation is submitted to the Faculty of Technology and Science at Aalborg University in partial fulfillment of the requirements for the PhD degree. The work has been carried out in the Department of Communication Technology, at Institute of Electronic Systems, at Aalborg University.

The work presented in the dissertation is part of a larger research project running within the *RF Integrated Systems & Circuits* (RISC) Division, also Aalborg University. The overall goal is here to exploit the characteristics of state-of-the-art CMOS processes for RF applications. To accomplish this the RISC Division conducts research on all levels of RF integrated circuit design, i.e. system, circuit, and device level. The basis of the work presented in this dissertation falls within all three research areas, a fact also reflected by the structure of the dissertation. The dissertation is divided into an introductory part and subsequently two parts that each provides an extended summary of the work done within the system level as well as the circuit and device areas.

- The first part, the introduction, presents the concept of CMOS integrated circuit design by a short historical introduction followed by an example of the current state-of-theart for commercially available RF CMOS design. CMOS as a vehicle for digital and analog integrated circuit design is considered and a few considerations related to the much debated single-chip vision is presented. This is followed by an evaluation of the RF potential of CMOS by considering its characteristics in relation to traditional radio design metrics.

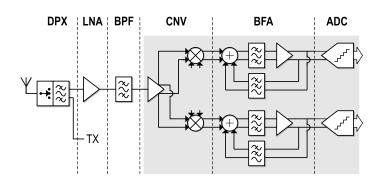

- The second part addresses the system level aspect of IC design. In particular, the system level design of receiver architectures for modern cellular system handsets. The available receiver architectures are considered. A system level design for a direct-downconversion receiver for WCDMA (UTRA/FDD) is conducted. As part of this the DC-offset problem related to the direct-downconversion receiver is addressed. A DC-offset model is presented and using this the robustness of a WCDMA signal is evaluated using link-simulations. This leads to a set of filter requirements that form a compromise between overload protection of baseband circuits and signal degradation.

- The third part of the dissertation focuses on the implementation level of RF IC design. The mixer is an essential circuit block in any direct-downconversion receiver and as a natural extension of part two, the design of a direct-downconversion mixer is the target of part three. In addition to the actual circuit design of a mixer it is essential

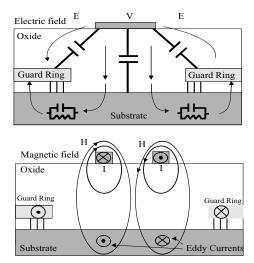

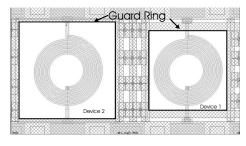

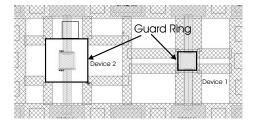

that any unwanted signal leakage is minimized. Therefore, this part of the dissertation also considers crosstalk and minimization of this. To increase isolation between devices and circuits guard rings are often used. The use of guard rings results in either an inductor performance penalty or an additional area requirement. Using simulations and experimental set-ups the effectiveness of guard rings is evaluated. The device degradation is analyzed and different coupling mechanisms are evaluated to form a lumped element crosstalk model for the inductor-to-inductor coupling.

Including this preface the three parts form a 58 page extended summary of the work. Each part is completed with a summary and the overall achievement summary of the dissertation is provided at the end of this preface. The dissertation is based on a total of 14 selected publications, of which seven are first-authored and the remaining seven are co-authored. All 14 publications are included as part of this dissertation. The included papers span a total of six years and for that reason it should be expected that in some cases the background for certain assumptions and motivations may have changed over time.

### **Publications**

- 1. J.H. Mikkelsen, "Evaluation of CMOS Front-End Receiver Architectures for GSM Handset Applications," in *IEEE International Symposium on Communication Systems and Digital Signal Processing (CSDSP)*, (Sheffield Hallam University, Sheffield, England), pp. 164–167, April 1998.

- 2. T.E. Kolding, J.H. Mikkelsen, and T. Larsen, "CMOS Technology Adjusts to RF Applications," *Microwaves and RF*, vol. 37, pp. 79–88, June 1998.

- 3. J.H. Mikkelsen, T.E. Kolding, and T. Larsen, "RF CMOS Circuits Target IMT-2000 Applications," *Microwaves and RF*, vol. 37, pp. 99–107, July 1998.

- 4. <u>J.H. Mikkelsen</u>, "CMOS Low-Noise Asymmetric Poly-Phase Filter for GSM Low-IF Radio Receivers," in *European Conference on Circuit Theory and Design (ECCTD)*, (Stresa, Italy), pp. 221–224, August–September 1999.

- J.H. Mikkelsen, T.E. Kolding, T. Larsen, T. Klingenbrunn, K.I. Pedersen, and P. Mogensen, "Feasibility Study of DC Offset Filtering for UTRA-FDD/WCDMA Direct-Conversion Receiver," in *17th IEEE NORCHIP Conference*, (Oslo, Norway), pp. 34–39, November 1999.

- O.K. Jensen, T.E. Kolding, C.R. Iversen, S. Laursen, R.V. Reynisson, <u>J.H. Mikkelsen</u>, E. Pedersen, M.B. Jenner, and T. Larsen, "RF Receiver Requirements for 3G WCDMA Mobile Equipment," *Microwave Journal*, vol. 43, pp. 22–46, February 2000.

- P. Madsen, O.K. Jensen, T. Amtoft, R.V. Reynisson, <u>J.H. Mikkelsen</u>, S. Laursen, C.R. Iversen, T.E. Kolding, T. Larsen, and M.B. Jenner, "RF Requirements for UTRA/FDD Transceivers," in *Conference Proceedings for Wireless Personal Multimedia Communications (WPMC)*, vol. 1, (Aalborg, Denmark), pp. 197–202, , September 2001.

- 8. J.H. Mikkelsen and T.E. Kolding, "Accurate Computer-Assisted Planning of Integrated Radio Receivers," in *19th IEEE NORCHIP Conference*, (Kista, Sweden), pp. 167–172, November 2001.

- P. Madsen, O.K. Jensen, T. Amtoft, R.V. Reynisson, <u>J.H. Mikkelsen</u>, S. Laursen, T.E. Kolding, T. Larsen, and M.B. Jenner, "UTRA/FDD RF Transceiver Requirements," in *Wireless Personal Communications*, vol. 23, no. 1, pp. 55–66, Kluwer Academic Publishers, October, 2002.

- J. Bøjer, M.B. Gentsch, O.K. Jensen, <u>J.H. Mikkelsen</u>, K.Aa. Pedersen, and S. Lindfors, "An UTRA/FDD Direct-Downconversion Mixer in 0.25µm CMOS," in 20th IEEE NORCHIP Conference, (Copenhagen, Denmark), pp. 259–264, November 2002.

- N. Sainz, O.K. Jensen, and <u>J.H. Mikkelsen</u>, "Evaluation and Modeling of Guard Ring Related Device Performance Degradation," in *21st IEEE NORCHIP Conference*, (Riga, Latvia), pp. 228–231, November 2003.

- J. Bøjer, M.B. Gentsch, O.K. Jensen, <u>J.H. Mikkelsen</u>, K.Aa. Pedersen, and S. Lindfors, "An UTRA/FDD Direct-Downconversion Mixer in 0.25µm CMOS", in *Analog Integrated Circuits and Signal Processing*, vol. 38, pp. 27–33, Kluwer Academic Publishers, January, 2004.

- J.H. Mikkelsen, O.K. Jensen, and T. Larsen, "Measurement and Modeling of Coupling Effects of CMOS On-Chip Co-Planar Inductors," in *IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF)*, (Atlanta, Georgia, USA), pp. 37– 40, September 2004.

- J.H. Mikkelsen, O.K. Jensen, and T. Larsen, "Crosstalk Coupling Effects of CMOS Co-Planar Spiral Inductors," in *IEEE Custom Integrated Circuits Conference (CICC)*, (Orlando, Florida, USA), pp. 371–374, October 2004.

#### Summary of Publications

The included papers all have CMOS implementations as a common focal point. Apart from that, the contributions aim at both system, circuit, and device levels. In the following, summaries of the papers are presented to provide an overview of the scientific contributions combined in this dissertation. The order of the paper summaries is according to the list of publications as just mentioned above.

# 1. Evaluation of CMOS Front-End Receiver Architectures for GSM Handset Applications

The paper presents the first direct evaluation of the potential of RF-CMOS for implementing highly integrated receivers for the Global System for Mobilecommunication (GSM). Also, the paper is the first to report results of RF-CMOS receiver evaluations where the performance of the data receiver is included. The two most promising architectural candidates for implementing highly integrable receivers are identified to be the direct-downconversion receiver (DCR) and the low intermediate frequency (Low-IF) receiver. Both receiver architectures are analyzed and link simulations are conducted based on contemporary CMOS performance. The simulations show that an all CMOS Low-IF receiver solution for GSM is realistic. The DCR is shown to suffer from low-frequency noise problems that lead to de-sensitization causing it to fail to meet specifications. The paper concludes that when using contemporary CMOS performance an all-CMOS Low-IF receiver is potential while the DCR presents problems that still need to be solved.

# 2. CMOS Technology Adjusts to RF Applications

This paper is the first part of a two-part feature that takes a first look at RF CMOS technologies and circuits aiming for IMT-2000. This, the first part, provides an overview of advances in CMOS technologies and their importance in relation to analog circuit design. Normally the minimum feature size of a given technology is used as a technology performance indicator. For digital designs this is an appropriate measure as a number of important parameters is positively affected by the continuous downscaling. Traditional analog RF performance metrics, such as gain, noise and linearity are not necessarily improved in the same way. Instead the paper argues that analog improvements come from other digital improvements than downscaling. For instance, as CPU speeds enter the 1 - 2GHz range, design techniques previously considered to be exotic analog techniques are finding way into digital designs. As an example, to reduce interconnect resistivity the use of copper is considered as a replacement of alumina and to ease interconnectivity in extremely dense digital designs several metal layers are needed. Both of these, in principle, digital improvements have direct effect on analog circuit performance as the potential inductor performance is significantly improved. Despite such improvements the paper argues that the major limitation is related to the low-resistivity substrate. An overview of the achievable RF performance for CMOS passive devices is provided to illustrate the limitations in device performance. The paper concludes that all the technological innovations are only useful as long as they maintain the low cost advantage of CMOS.

# 3. RF CMOS Circuits Target IMT-2000 Applications

This paper is the second part of the feature looking at RF CMOS technologies and circuits aiming for IMT-2000. The paper is the first to consider the requirements for the coming 3G systems (IMT-2000) while drawing relations to the achievable RF performance of CMOS. Since IMT-2000 requirements are not yet finalized GSM-like RF requirements are expected. In that sense the step from 2G towards 3G should only be a minor

one. However, the increased bandwidth and the air interface flexibility (4MHz, 6MHz, 12MHz) impose big challenges. The paper points at the increased bandwidth as being the major challenge as the present  $f_T$  and  $g_m/I_D$  characteristics of MOS devices are more suited for narrow-band design. Some of the limitations of CMOS are that the CMOS devices introduce significant noise and distortion into the signal path. The paper identifies two very different design approaches that aim to solve this; simplicity in design and advanced signal processing. Simplicity in design implies that the number of devices used in the signal path is to be minimized – the philosophy being that fewer non-ideal components are going to provide a minimum of degradation of signal quality. In direct contrast to this, advanced signal processing may be used to mitigate the short-comings of CMOS. Here, circuit complexity is added to implement complex signal processing in the analog domain. The important point is made, that for a majority of the CMOS designs reported, the performance has been obtained in controlled environments. Stabledesign innovations are required to mature CMOS to a state where packaging effects and process variations become manageable. The paper concludes that issues besides pure circuit performance must be considered to close the gab between current TDMA systems and the coming IMT-2000 system.

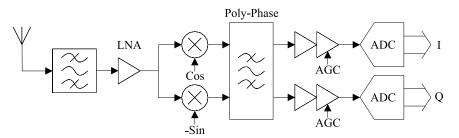

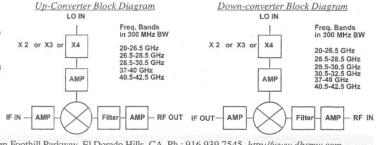

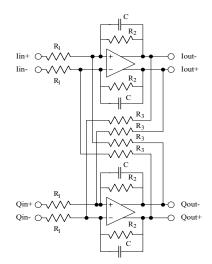

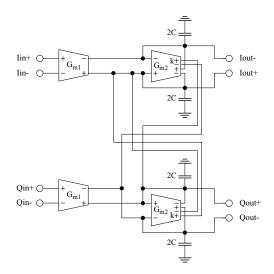

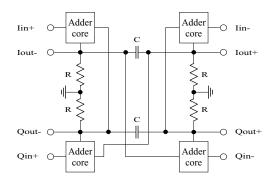

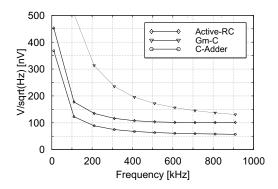

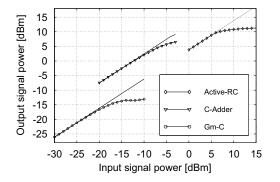

- 4. CMOS Low-Noise Asymmetric Poly-Phase Filter for GSM Low-IF Radio Receivers The key component in any low-IF receiver is the poly-phase filter. This paper provides the first comparison of different implementations of active poly-phase filters. To achieve high levels of image-rejection using traditional poly-phase filtering a high filter-order is needed. High-order filtering normally comes at the expense of increased noise levels and for that reason the paper looks at low-noise implementations. The traditional active-RC implementation is compared with two new current-mode topologies, a  $G_m - C$  based implementation and a current-adder topology. For the Active-RC implementation only moderate gain may be implemented while low noise performance is preserved. Further, low noise performance and low frequency operation imply large capacitors which require a large area. For the  $G_m - C$  approach the paper proposes an enhanced  $G_m$  cell with dual output whereby matching performance is improved. Based on the principle of simplicity in design the paper also proposes a poly-phase filter topology based on differential current adding. This topology improves noise performance significantly but suffers from the fact that the cut-off frequency depends on transistor matching. The paper concludes that the active-RC topology has the best signal handling performance of the three implementations. In its current implementation the  $G_m - C$  topology has inferior performance compared to the two other implementations. The current-adder topology has the best noise performance and offers potential for implementing low-noise poly-phase filters even at high frequency.

- 5. Feasibility Study of DC-Offset Filtering for UTRA-FDD/WCDMA Direct-Conversion Receiver

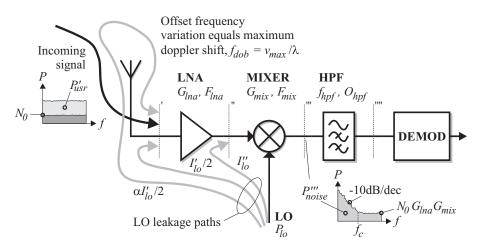

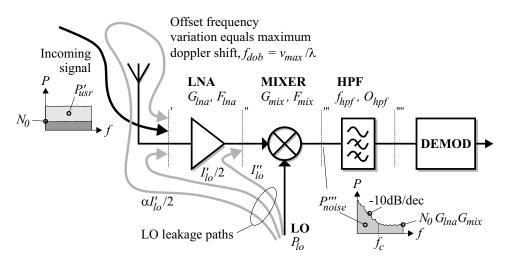

One of the strongest contenders for a completely integrable receiver architecture has long been the DCR. The DCR has a number of inherent short-comings with DC-offset being one of the more severe issues. This paper is the first to present a study of the DC-offset

problem for UTRA-FDD/WCDMA DCRs. The paper takes a look at the root of the DC-offset problem and provides the first reported model for DC-offset. The causes of DC-offset are characterized as being either largely time-invariant or time-variant. The largely time-invariant contributions may be mitigated in production-line calibration or through power-up calibration. For that reason the DC-offset model only considers the time-variant parts. The DC-offset model is specified in a manner that provides for a worst-case scenario with the maximum frequency content determined by the maximum Dopler shift. To prevent saturation of receiver stages following the mixer the paper shows that 60 - 80dB attenuation at 1kHz is required. Based on extensive link-simulations the paper is the first to provide an evaluation of the robustness of the WCDMA signal against removal of low frequency signal content. The paper concludes that a third to fourth order Butterworth filter with a cut-off frequency around 10kHz provides for a good compromise between BER degradation and saturation protection.

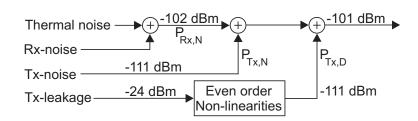

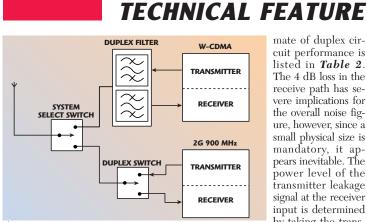

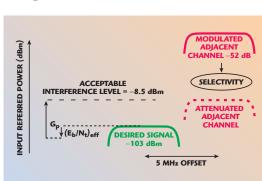

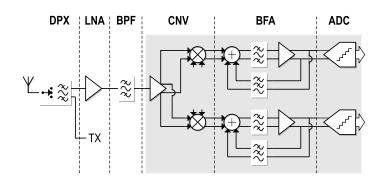

#### 6. RF Receiver Requirements for 3G WCDMA Mobile Equipment

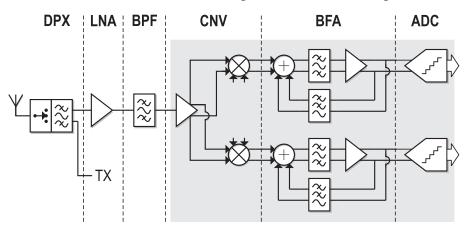

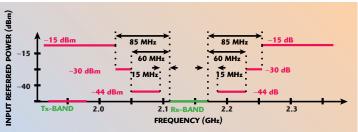

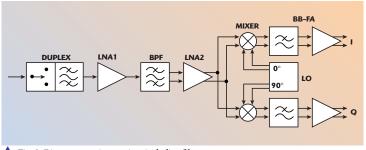

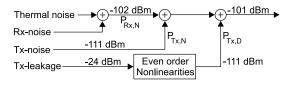

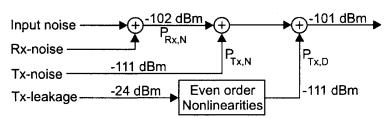

The paper provides the first reported analysis of the RF receiver requirements for 3G WCDMA mobile equipment. Two very important considerations affect the analysis presented in the paper. First, unlike the traditional TDMA systems, the considered WCDMA system employs simultaneous transmission and reception which requires a duplex filter. Secondly, it is expected that WCDMA mobile equipment must be able to operate using the already existing 2G network. This requires a transceiver configuration capable of supporting both the TDMA and the WCDMA systems. The paper concludes that noise figure and adjacent-channel rejection requirements are not directly affected by the presence of the TX leakage signal. Considering second-order non-linearities two sources of interferers are identified; unwanted channels in the receive band and the TX leakage signal and it turns out that the TX leakage signal by far represents the worst case. In addition to the intermodulation test prescribed, the presence of the TX leakage forms and additional requirement. Any CW signal to arrive at the receiver at an offset of 67.4MHz is going to mix with the TX leakage which at an offset of 135MHz is to give third order intermodulation. This adds to the list of specifications. In conclusion, the continuing presence of a TX leakage signal complicates the task of receiver specification. However, the paper shows that a DCR with reasonable requirements is capable of meeting derived specifications when an interstage bandpass filter is used to attenuate the TX leakage signal.

#### 7. RF Requirements for UTRA/FDD Transceivers

This paper provides an extension to the work presented in publication 6. The receiver analysis is refined and a transmitter analysis is added to provide the first published requirements for a complete UTRA/FDD handset. The receiver calculations are some of the first to be published and the transmitter calculations are the first published. Based on a realistic duplex arrangement all receiver requirements are derived for the interface between the RX output of the duplexer and the input to the actual receive path. Furthermore, it is assumed that all disturbing signals that are not located at the channel frequency of the wanted signal are removed by filtering in the digital baseband part. This

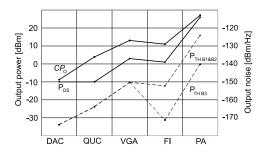

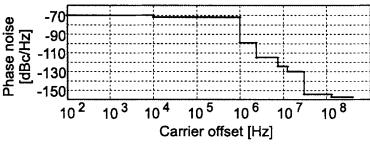

implies that any distortion resulting from second order non-linearities is significantly reduced. Also, using highpass filtering to attenuate any DC-offset also improves the performance. For the transmitter analysis the standard dictates the overall requirements to EVM, ACLR and spurious emission. In addition to this, the receiver analysis adds an additional requirement by specifying the maximum amount of transmitter noise that can be tolerated in the receive band. These specifications form an overall budget for the transmitter which is used to derive requirements for the different receiver blocks. The requirements are given in terms of I/Q-imbalance, in-band ripple, LO phase noise and leakage, and compression points. It is found that a baseband filter is needed before the PA in order to meet the requirement for transmitter noise in the receive band.

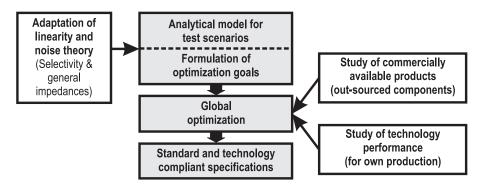

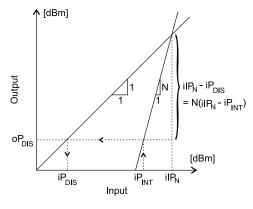

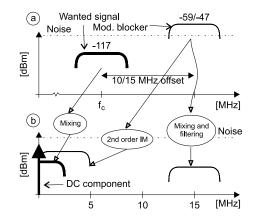

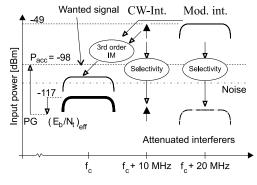

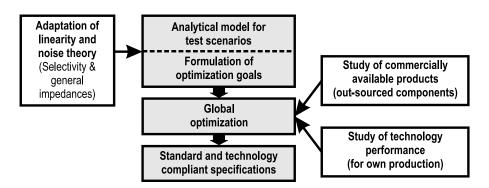

### 8. Accurate Computer-Assisted Planning of Integrated Radio Receivers

In this paper a general methodology for accurate and fast planning of integrated lowcost receivers is presented. The proposed method is based on a loop-form voltage domain extension of traditional microwave theory and the method is the first to include general selectivity and non-50 $\Omega$  interface transitions in a simple and manageable way. The presented approach allows the designer to consider all interferring components simultaneously thereby optimizing the receiver planning to minimize the effect of implementation impairments. To exemplify the approach, the paper makes use of a CMOS-based UTRA/FDD RF/baseband receiver case study. The receiver is required to operate at a BER of less than  $10^{-3}$ . To simplify the receiver planning this BER requirement is mapped into a 7dB SIR requirement. A simulation model is built for each of the different test scenarios. It is emphasized that it is important to ensure that the model includes all simultaneously active disturbance effects that contribute to the overall performance degradation. The case study shows that it is not possible to have all test scenarios exactly match the 7dB requirement but using the proposed method a close-to optimum receiver specification results where over-specification is avoided.

# 9. UTRA/FDD RF Transceiver Requirements

This paper is a reprint of publication 7. The original paper was selected for a reprint in a special issue of Kluwer Academic Publishers *Journal of Wireless Personal Communication*. The reprint is shorter than the original paper and a major revision was therefore needed. Compared to the original paper a few changes are made; the compression point requirements are replaced with ACLR requirements and it is described how ACLR requirements for cascaded blocks may be used to calculate a resulting ACLR measure.

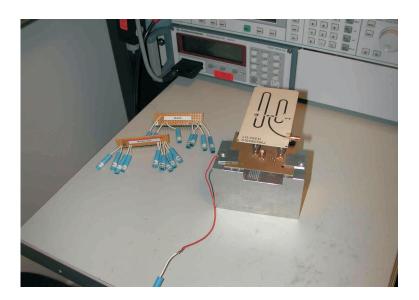

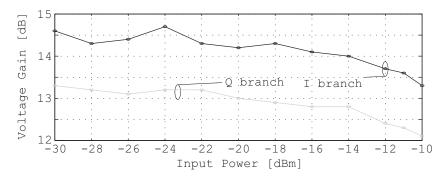

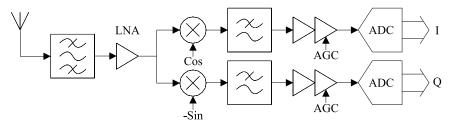

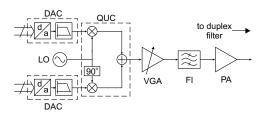

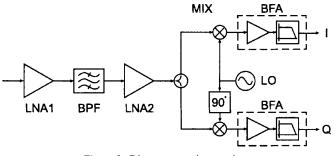

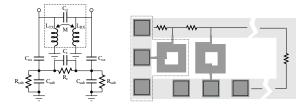

# 10. An UTRA/FDD Direct-Downconversion Mixer in 0.25μm CMOS

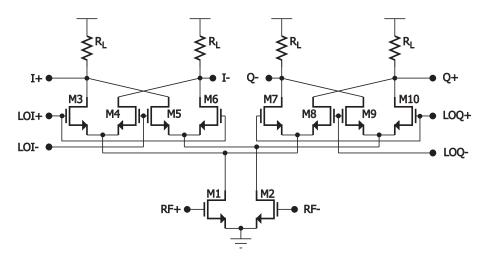

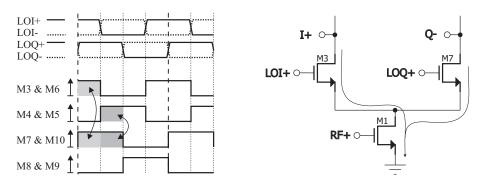

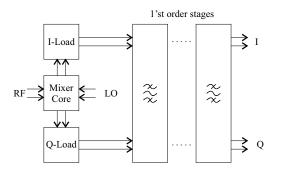

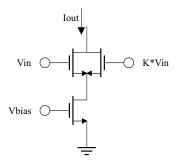

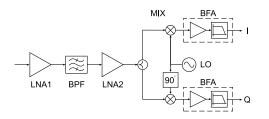

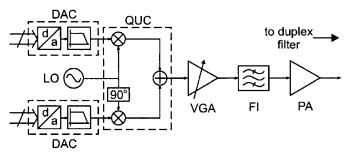

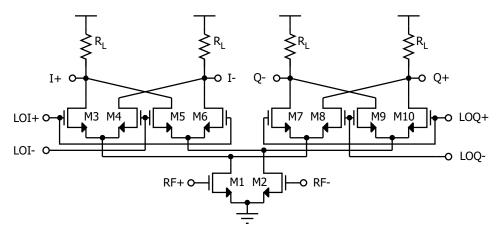

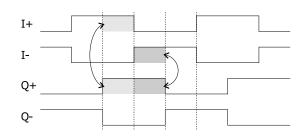

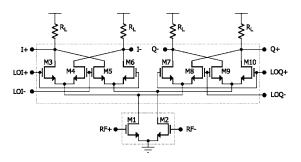

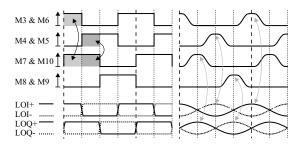

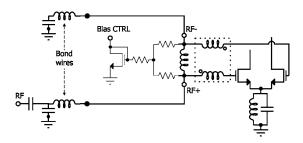

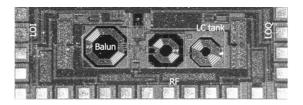

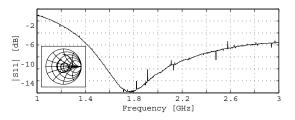

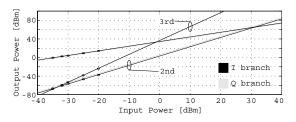

This paper presents the design of a 2GHz direct-downconversion mixer for a UTRA/FDD receiver. The mixer is implemented using a standard low-cost  $0.25\mu$ m, single-poly, sixmetal CMOS process. The implemented topology is a modification of the well-known Gilbert cell mixer. To provide for a quadrature output, as required in a DCR, the mixer uses a shared differential transconductance stage as input. This approach implies that only the switching core mismatch add to imbalance in the mixer output. Compared

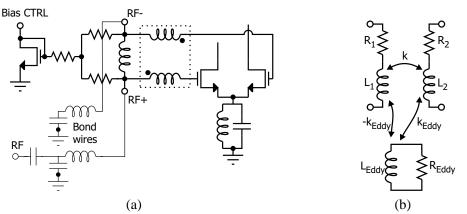

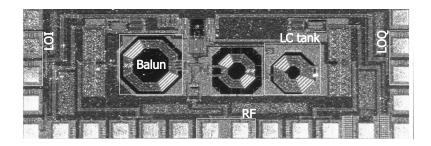

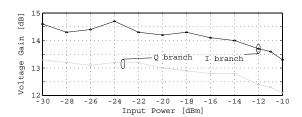

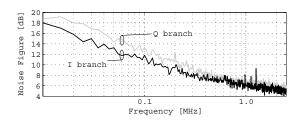

to a single Gilbert cell mixer, the noise performance of the proposed mixer topology is inferior when instantaneous switching is assumed. However, for non-switching LO signals the proposed topology holds a noise advantage over the Gilbert cell mixer. The usual current-source bias approach is abandoned in favor of a LC resonator. With the input stage based on a LC resonator, common-mode rejection is provided without the loss of voltage headroom. The input also includes an on-chip balun to provide a singleended to differential transformation of the input signal. Based on measurements the mixer is found to offer a voltage gain of 15dB, a state-of-the-art noise figure of 8dB, and an iIP3 of around -1dBm.

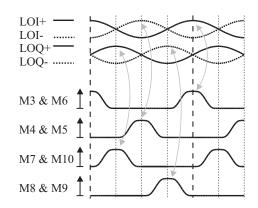

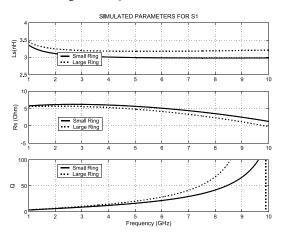

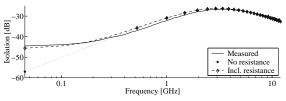

#### 11. Evaluation and Modeling of Guard Ring Related Device Performance Degradation

In this paper the importance of distance between guard ring and device is evaluated. This is done by quantifying the variations in inductor and capacitor performance for different guard ring distances. For this purpose several test structures are implemented using a  $0.25\mu$ m, single-poly, five-metal layer, CMOS technology. To explain the relation between guard ring and device performance both the magnetic and the electrical fields are considered. Based on this it is argued that the guard ring is of insignificant importance for capacitor performance. This argument is supported by measurements. For inductors the situation is more complicated and 2.5D simulations are used to support and help understand measurements. The distance between inductor and guard ring is found to be of significant importance and as expected, the inductance values are found to decrease when the distance to the guard ring is reduced. Consequently, the Q-value of the device also degrades. At 5GHz it is found that a 35% reduction in component area due to reduced guard ring distance may cause a reduction of approximately 16% in Q-value.

#### 12. An UTRA/FDD Direct-Downconversion Mixer in 0.25μm CMOS

This paper is a reprint of publication 10. The original paper was selected for a reprint in a special issue of Kluwer Academic Publishers *Journal of Analog Integrated Circuits and Signal Processing*. The reprint is longer than the original paper and offers the opportunity of further explanations. The receiver set-up and mixer requirements are explained in more detail and, more importantly, the mixer topology is explained in greater detail. The nature of the mixer in switching versus non-switching LO scenarios is given more attention. In a switching scenario it is explained how the proposed topology has an increased sensitivity towards LO amplitude mismatch in comparison with two separate mixers. For a sinusoidal LO input this impairment is significantly reduced. It is also explained how the quadrature topology holds a noise advantage over two separate mixers for sinusoidal LO inputs. Because of the shared input stage, noise in I- and Q-branches is correlated and consequently there is a 3dB noise advantage.

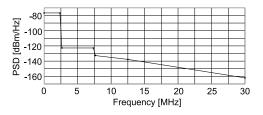

# 13. Measurement and Modeling of Coupling Effects of CMOS On-Chip Co-Planar Inductors

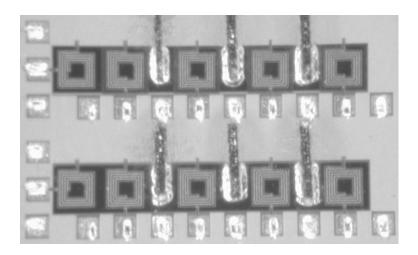

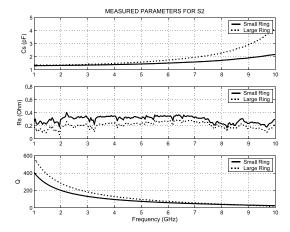

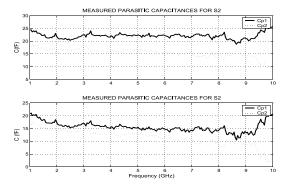

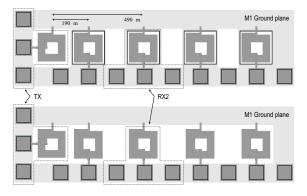

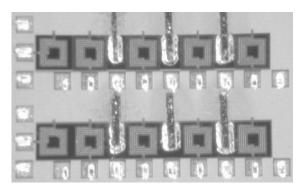

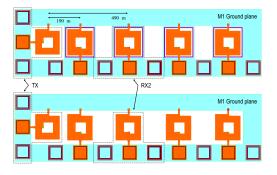

This paper evaluates the coupling effects between two planar inductor structures. The evaluation considers the effect of different distances between the structures and also the effect of having a guard ring or not. For this purpose an experimental set-up is

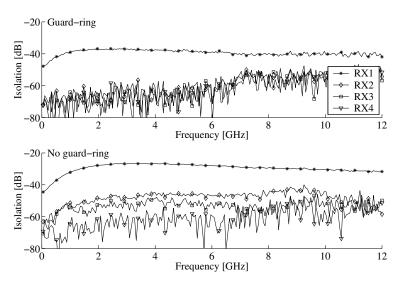

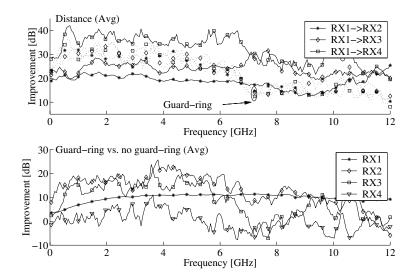

implemented using a  $0.25\mu$ m, single-poly, five-metal layer, CMOS process. The test structures are also evaluated using 2.5D simulation to support measurements. The test fixtures are found to affect measurements significantly and to solve this, laser cutting is used to break an unintended coupling path. With the test fixture problem solved it is found that the coupling depends significantly on the distance between inductors. The nature of the correlation between coupling and distance is highly dependent on whether a guard ring is used or not. When using guard rings the resulting isolation is found to be independent of distance unless the inductors are placed at a very short distance to one another. For all the tested distances an isolation of approximately 30dB results. The same trend is not seen when no guard ring is used. For an increase in distance from 190 $\mu$ m to 290 $\mu$ m around 20dB of reduction is provided while an increase from 190 $\mu$ m to 1090 $\mu$ m results in approximately 35dB additional isolation.

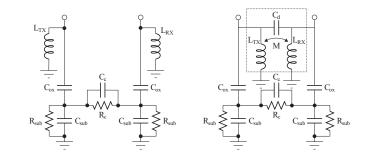

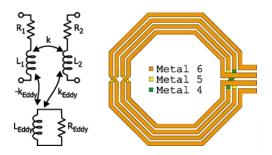

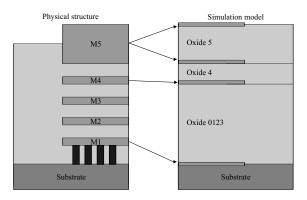

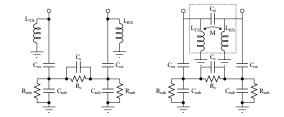

# 14. Crosstalk Coupling Effects of CMOS Co-Planar Spiral Inductors

This paper may be considered to be an extension of publication 13. This paper builds on the same measurement set-up as publication 13 but the focus here is on the modeling of the crosstalk coupling between two planar inductors. Often crosstalk is assumed to result only from substrate carried effects. In this paper an extended model including magnetic as well as direct capacitive coupling is used to evaluate the crosstalk effects when no guard ring is used. The extended lumped model is shown to provide a very good fit to measured data for all four different distances. In contrast to previous reports the substrate-related coupling is found to have only minor effect at all. The majority of the crosstalk coupling is found to be a result of inductive coupling between the two inductors.

# Achievement Summary

As part of the work documented in this dissertation a number of contributions has been made. Some of these findings and achievements are as followingly summarized:

# Part I:

- A survey of CMOS technology and its performance and shortcomings in relation to RF design requirements is provided.

- Trends and technology developments for digital IC design are put into an analog perspective.

# Part II:

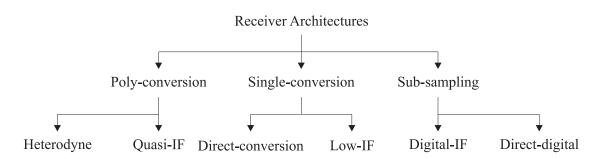

• A survey of receiver architectures and their characteristics from an IC implementation point of view is given.

- The direct-conversion receiver is shown to be an interesting architecture for implementing UTRA/FDD receivers, allowing for high integration and holds potential for multi-mode operation.

- A DC-offset model is developed and used to set requirements to DC-offset cancellation schemes.

- Link-level simulations are used to show that the UTRA/FDD signal may be subject to highpass filtering without significant signal-quality degradation. It is found that a third to fourth order Butterworth filter with a 3dB cut-off frequency of 10kHz provides a good compromise between DC-offset cancellation and signal degradation.

- Based on voltage domain expressions, allowing for non-50Ω impedances and receiver stage selectivity, a simple method for receiver planning is proposed. The method allows all noise and distortion components to be considered simultaneously whereby a close-to-optimum receiver planning is possible.

- An UTRA/FDD direct-conversion receiver is proposed. It is shown that the receiver is able to meet the UTRA/FDD requirements when based on block performance that seems to be within reach of CMOS.

# Part III:

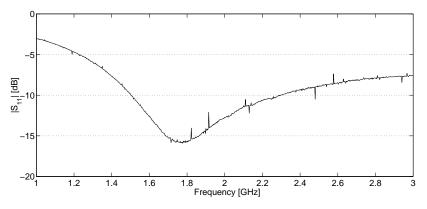

- A CMOS 2GHz quadrature down-conversion mixer is designed, implemented, and tested. Measured results are: 13.8dB voltage gain, 8dB noise figure, 25dBm input second order intercept point at 15MHz offset, and -3.1dBm input third order intercept point at 10/20MHz offset. These data are obtained for a supply voltage of 2.5V and a current consumption of 6mA.

- The effect of guard ring area is analyzed and shown to have significant impact on inductor performance.

- It is shown that reducing the distance between coil and guard ring from  $32\mu m$  to  $10\mu m$  (corresponding to an area reduction of 32%) results in 5.8% reduction in inductance values and 16% reduction in quality factor at 2GHz. At 5GHz the inductor value is found to be reduced by 8.1% and the quality factor by 15.8%.

- To determine if the use of guard rings is justified, experiments on inductor isolation are conducted to determine the degree of inductor cross-talk.

- It is shown that the test set-up for doing isolation measurements is very important. Specific problems and how to solve these are described.

- It is shown that guard rings provide around 10 15dB improvement in isolation for closely spaced inductors. At larger distances the improvement is shown to reduce to zero. It is found that a doubling of distance provides an additional 20dB of isolation.

PAGE xiv

• An extended lumped-component model is proposed to model the crosstalk between inductors. Mutual coupling is found to be the most significant source of crosstalk. The model provides very good fit to measurements.

### **Acknowledgments**

First of all, I would like to express my gratitude to my supervisor Professor, Dr. Techn. Torben Larsen who during the many times of slow progress somehow managed to summon enough belief. I would also like to thank Professor Christian Christensen for initiating the work in the first place. In continuation of this, a few people deserve special recognition for providing their voluntary support. Peter Boie Jensen for his assistance with the manufacturing of various test boards; always of impeccable quality, and Ole Kiel Jensen for readily providing feedback and input on almost any topic. A special recognition goes to Troels Emil Kolding for being who he is – pushy, suggestive, and always of a positive attitude. I would also like to thank colleagues at RISC for providing a generally constructive atmosphere. Finally, I would like to thank my family and girlfriend Eva for their love and support.

# **Contents**

#### Ι **CMOS Technology RF IC Design for Wireless Applications** 1 A World gone Wireless 3 1.1 1.2 Integrated Circuit Design for Cellular Applications – State-of-the-art . . . . 4 1.3 Complementary Metal Oxide Semiconductor 6 1.3-1 CMOS – a Digital IC Technology 6 1.3-2 7 CMOS – an Analog IC Technology 1.4 8 1.4-1 10 1.5 CMOS as an RF Technology – Performance vs. Requirements . . . . . . . 11 12 1.5-1 1.5-213 Low Noise 1.5-3 14 High Linearity 1.5-4 Low Power 15 1.5-5 16 Low Voltage 1.5-6 17 1.6 Summary 19

# II CMOS Aware Receiver Planning Receiver Architectures and DC-Offset Cancellation

| 2.1 | Receiver Architectures and General Considerations |                                       |    |  |  |  |  |

|-----|---------------------------------------------------|---------------------------------------|----|--|--|--|--|

|     | 2.1-1                                             | Poly-Conversion Receivers             | 24 |  |  |  |  |

|     | 2.1-2                                             | Single-Conversion Receivers           | 26 |  |  |  |  |

|     | 2.1-3                                             | Subsampling Receivers                 | 29 |  |  |  |  |

|     | 2.1-4                                             | Choosing the Appropriate Architecture | 31 |  |  |  |  |

| 2.2 | 2 Receiver Structure for UTRA-FDD                 |                                       |    |  |  |  |  |

| 2.3 | 3 DC-Offset Filtering of W-CDMA Signals           |                                       |    |  |  |  |  |

|     | 2.3-1                                             | DC-Offset Model and Cancellation      | 35 |  |  |  |  |

| 2.4 | Receiver Planning                                 |                                       |    |  |  |  |  |

|     | 2.4-1                                             | Test Scenarios and Work-Flow          | 39 |  |  |  |  |

| 2.5 | Summa                                             | ury                                   | 40 |  |  |  |  |

Page xvii

21

|      | MOS Circuit and Device Design                              | 12 |

|------|------------------------------------------------------------|----|

| UIKA | -FDD Mixer Design and Inductor Crosstalk Issues            | 43 |

| 3.1  | Mixer Design for a UTRA-FDD Direct-Downconversion Receiver | 45 |

|      | 3.1-1 Switching Core                                       | 46 |

|      | 3.1-2 Input Stage                                          | 46 |

|      | 3.1-3 Measurement Results                                  | 47 |

| 3.2  | Circuit Isolation and Inductor Design Trade-off            | 49 |

|      | 3.2-1 Inductor Performance and Guard-Rings                 | 50 |

|      | 3.2-2 Inductor Crosstalk                                   | 53 |

| 3.3  | Summary                                                    | 57 |

# Part I

# **CMOS Technology**

**RF IC Design for Wireless Applications**

"In modern wireless communication systems a given performance at a low cost is almost always preferred to improved performance at a greater cost".

L.M. Burns

Communication technology as a general concept has evolved immensely over the last couple of decades. New system concepts have been engineered and the implementation technologies have seen an almost explosive development. This part of the dissertation takes a look at the "Wireless World" concept followed by an example of state-of-the-art in RF-CMOS design today. The development of CMOS as both a digital and an analog technology is considered and the RF characteristics of CMOS are evaluated.

# 1.1 A World gone Wireless

There is little question that the world is going wireless. Since the mobile communication revolution started in the early 80s through the introduction of the *Nordic Mobile Telephone* (NMT) system, a wide range of systems and applications based on wireless communication has emerged. Intended as a digital replacement for NMT, the *Global System for Mobile communication* (GSM) was introduced in the early 90s as a first real attempt at a truly global communication standard [1, 2]. GSM did not succeed in becoming a global standard but it saw a significant penetration in Europe and with its 72% share of the world's wireless market it is today by far the most wide-spread cellular system [3]. Almost simultaneously with the introduction of GSM the first *Digital European Cordless Telephony* (DECT) system saw operation.

To provide for better services and especially to offer higher data rates, a second generation of GSM, the *Enhanced Data rate for GSM Evolution* (EDGE) system, was developed. With EDGE a maximum bandwidth of 384Kb is possible which is a significant improvement over GSM. With GSM being labeled as a second generation (2G) cellular system, EDGE is considered to be a 2.5G system. Even before mobile operators had started to offer EDGE based services, a third generation (3G) system was being drafted. The new system, *Universal Mobile Telephone System* (UMTS), is the second attempt for a global standard [4]. Once again political and commercial interests prevented UMTS from being a unified global standard. Instead several sub-standards have been formed and these have then been incorporated as options within the UMTS standard. There is a lot of dispute regarding the 3G system and a majority of the mobile operators has disregarded 3G and instead focuses on GSM and EDGE. In Denmark, a single operator has only recently started to offer 3G services and this with a very limited success as public interest has been very scarce. Despite the limited interest in 3G, industry and academia are already highly focused on forming and developing the next mobile communication system, the 4G system [5].

In parallel with the expansions within the area of mobile telephone communication a number of wireless computing applications has been developed. This includes applications such as *Wireless Local Area Network* (WLAN), Bluetooth, and ZigBee [6–8]. All three standards are basically intended as cable replacements offering very different bandwidths, data rates, and power consumption levels. Location applications such as the *Global Positioning System* (GPS) have been matured and fairly cheap handheld terminals have been commercially available for some years. As a further note, GPS is currently being incorporated into a number of other

applications. As an example, in the United States the *Federal Communications Commission* (FCC) has an ongoing initiative (E911) to provide positioning information to for instance rescuers in emergency situations. The intention is that a positioning service with an accuracy in the order of 50m - 150m should be a required and integrated part in all new cellular phone handsets by the end of year 2005. To meet this, GPS and *Assisted-GPS* (A-GPS) in particular, is suggested [9]. This is a clear advocate for increased functionality and complexity in handheld wireless communication.

More recently the concept of a *Personal Area Network* (PAN) is being accepted as a potential scenario for a future wireless world [10]. Based on user-centricity, such PANs are to support user activities by enabling seamless and possible ad-hoc based communication to (and between) all of a user's devices capable of network connection whether at home, at the office, or in the wireless vicinity of the user. In such a scenario a vast number of wireless communication devices is to co-exist. This covers both ends of the bandwidth-scale including very low data-rate sensory nodes to very high data-rate 4G systems. For full user-centricity, a single device should enable transparent communication to and from all user devices. This calls for an unprecedented level of flexibility in the handset design.

# 1.2 Integrated Circuit Design for Cellular Applications – State-of-the-art

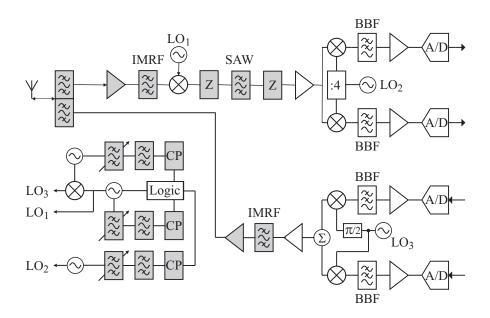

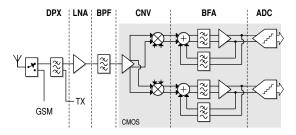

As a whole, the development in integrated circuit design has found good use in wireless applications, hand-portable communication equipment in particular. In fact, for the last 5-10 years applications based on wireless communication technology have represented the fastest growing market segment within the electronic industry [11]. During this time cellular handsets have gone from being mainly discrete implementations using hundreds of components to highly compact solutions based on three to four chips [12]. To illustrate this significant increase in system and circuit integration, an early single-chip GSM transceiver example is shown in Figure 1.1.

The design makes use of a heterodyne receiver architecture where a single intermediate frequency of 71MHz is used before the signal is downconverted to baseband. The transmitter is based on the direct-upconversion architecture where offset-LOs are used to prevent injection pulling. The extensive use of off-chip components results in a bulky and expensive implementation. Considering that even a \$2 external component may be objectionable by manufactureres, the solution in Figure 1.1 is hardly desirable. However, at the time of its introduction the implementation of Figure 1.1 took cellular handset design integration to a new level.

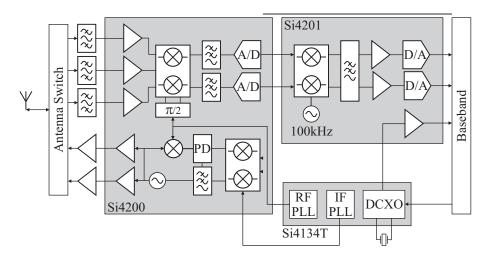

With cost, form factor, and a reduced *Bill of Material* (BoM) being driving factors, a majority of the high-cost components had to be eliminated. In this sense the most successful product to date is the GSM transceiver, *Aero<sup>TM</sup>*, offered by Silicon Laboratories. The transceiver, illustrated in Figure 1.2 consists of three CMOS chips; a Low-IF receiver and offset-PLL transmitter (Si4200), a digital downconverter and channel select chip (Si4201), and a separate frequency

*Figure 1.1: Example of an early GSM transceiver based on a 1.5µm silicon bipolar technology. Shaded blocks represent off-chip components [13].*

synthesizer chip. Despite its increased complexity, a direct result of its multi-mode capability, the chip-set offers a significantly higher degree of integration compared to the early attempt in Figure 1.1 as it only occupies  $2.4cm^2$  and requires only 20 external components. By mid 2003 this GSM transceiver, Silicon Laboratories' first generation design, had been sold in over 30 million samples leaving little doubt about the commercial capabilities and success of RF CMOS design [14].

Figure 1.2: Silicon Laboratories' CMOS chip-set with support for GSM, DCS, and PCS [15].

On June 7, 2004, Silicon Laboratories announced the third generation of their  $Aero^{TM}$  chipset. By combining the functionality of the earlier three-chip solution in a single chip, the resulting highly integrated solution takes up only  $1cm^2$  and requires only 19 external components to form a complete quad-band GSM transceiver [15]. With its  $Aero^{TM}$  chipsets Silicon Laboratories have managed to transform CMOS from initially being largely an academic oddity to its new-found status as a commercially proved technology for cellular applications.

# 1.3 Complementary Metal Oxide Semiconductor

For a large number of years CMOS has been the preferred technology for implementing digital designs. During this time CMOS as a technology has been developed significantly, a development fueled by digital design requirements. In the early 90s analog designers started to present results that have eventually caused CMOS to develop into an analog IC technology [16, 17].

# 1.3-1 CMOS – a Digital IC Technology

The appearance of the *bipolar junction transistor* (BJT) in the 40s and the *monolithic integrated* circuits (MICs) during the 50s and 60s, more or less formed the foundation for integrated circuit design [18, 19]. Despite initially emerging as an analog design invention, semiconductor developments have been driven largely by digital design requirements. As a result Very Large Scale Integration (VLSI) circuits, containing hundreds of thousands of transistors, have become standard in most digital designs. The transition from VLSI to Ultra Large Scale Integration (ULSI), containing more than half a billion transistors per chip, has long since been achieved. As an illustration the first microprocessor, the Intel 4004 introduced in 1971, contained 2300 transistors occupying 12mm<sup>2</sup> in a 10µmP-channel Metal Oxide Semiconductor (PMOS) technology [19]. The original Intel 8086 processor had some 29,000 transistors while the Pentium and the Pentium Pro have around 1 million and some 5.5 million transistors onchip [20, 21]. By 1992, high-end microprocessors, such as the 21164 Alpha chip, contained 9.3 million transistors occupying 209mm<sup>2</sup> in a  $0.35\mu$ m CMOS technology [22]. The number of transistors per area obviously differs significantly for the Alpha chip and the Intel 4004. The density is in fact improved by a factor of approximately 230 when the two designs are compared. This is partly due to technology improvements such as scaling where a shift from a minimum feature size of  $10\mu m$  to  $0.35\mu m$ , alone, provides for a significant reduction in area.

At the time of writing, state-of-the-art microprocessors are breaking the 3GHz boundary [23]. One of the more recent processors on the market to do so is the Intel Pentium 4 - *Prescott*. As seen from Table 1.1 the number of transistors has increased by more than a magnitude when comparing the P4 to the Alpha. Despite this growth in complexity the overall chip area has in fact been reduced as a result of the continued aggressive technology scaling.

The high packing density has helped CMOS become today's preferred technology in terms of digital circuit designs. The high packing density leads to reduced volume costs which is a primary design parameter today. Also, zero static power consumption and high yield characterize CMOS [25, 26]. These characteristics make CMOS an extremely valuable

| Table 1.1: Performance comparison of the early Intel 4004, the 21164 Alpha microprocessor, |

|--------------------------------------------------------------------------------------------|

| and the newer Intel Pentium 4 - Prescott processor [24]. NoT = Number of Transistors.      |

| Design     | Year | Technology  | Area               | NoT                | Clock    |

|------------|------|-------------|--------------------|--------------------|----------|

| Intel 4004 | 1971 | 10µm PMOS   | 12mm <sup>2</sup>  | 2300               | 0.108MHz |

| DEC Alpha  | 1992 | 0.35µm CMOS | 209mm <sup>2</sup> | $9.3 \cdot 10^{6}$ | 500MHz   |

| Intel P4   | 2004 | 0.09µm CMOS | 112mm <sup>2</sup> | $125 \cdot 10^{6}$ | 3.2GHz   |

technology. By completely dominating the world of digital designs, CMOS is currently the most widespread semiconductor technology [27,28].

Looking at processor road-maps from major microprocessor suppliers such as Intel and *Advanced Micro Devices* (AMD), a change of technology is forseen [29]. Using conventional transistor technology the power consumptions of future processors could increase exponentially to reach as much as 100W/cm [30]. Because of this manufacturers of high performance microprocessors are turning towards *Silicon on Insulator* (SOI) as their new technology platform. It would appear that due to power dissipation issues, standard CMOS has outplayed its role as the vehicle for high performance microprocessor design.

# 1.3-2 CMOS – an Analog IC Technology

The BJT was the first transistor to be successfully integrated and a long experience with bipolar based analog circuit designs exists. One reason for the success of the bipolar technologies is that the BJT has a number of nice analog features. For instance, the BJT displays a high transconductance value per DC bias current,  $g_m/I_c$ , which makes it an attractive technology for high gain amplifier implementations [25]. Further, BJT technologies also provide low flicker noise corner frequencies, typically in the order of 1 - 10kHz [31].

Due to the semi-conducting nature of silicon technologies these generally experience higher losses than the more sophisticated technologies, such as GaAs. This is a serious impairment, especially at high frequencies where the substrate effects are more pronounced. The actual resistivity level of silicon is, however, highly dependent on the particular technology. For CMOS the resistivity is around 5–20 $\Omega$ cm, with 10 $\Omega$ cm as a typical level [32]. The low substrate resistivity for CMOS is a legacy from its digital heritage where latch-up issues are important. For analog purposes the disadvantages connected to the low resistivities come two-fold. First, the low-resistivity substrate causes loading of high frequency signals, and secondly, it offers a significant electrical coupling path for both signals and noise. While such characteristics speak

against CMOS for analog designs its low cost potential is of great interest to the industry. For that matter substrate-related coupling issues have been, and continue to be, an ongoing research topic where the aim is to mature CMOS for analog high frequency applications [33–41].

Compared to the high frequency performance of bipolar technologies CMOS leaves much to be desired. This lack in high frequency performance of CMOS is caused by a number of factors. For instance, the analog performance of CMOS is limited by the low transconductance of PMOS devices [42]. In general the low  $g_m/I_D$  is of concern in CMOS designs. A general impediment of analog CMOS is the reduced device-to-device matching compared to bipolar technologies [43]. In addition, both resistive and capacitive parasitics, related to the aforementioned substrate effects, limit the attainable bandwidths of CMOS designs. Further, while the high frequency noise of the MOSFET is slightly lower than that of the BJT, the flicker noise performance is inferior to that of bipolar technologies [44]. Typical corner frequencies for CMOS are 0.1 - 1MHz [45]. Technology improvements in terms of down-scaling do not affect the BJT in a degree even comparable to the effect it has on a MOSFET device. For the MOSFET, down scaling, while preserving the current consumption level, results in an increased gate overdrive voltage,  $V_{od}$ , which in turn results in increased linearity of the device [45].

Over the last decade a third technology, *bipolar CMOS* (BiCMOS), has evolved. BiCMOS is a result of merging processing steps from bipolar and CMOS technologies. This merger combines advantages from both processes in terms of speed and power handling [42]. In a BiCMOS technology the disadvantages of MOSFETs may consequently be alleviated by using BJTs whenever these outperform MOSFET performance. However, combining bipolar and CMOS technologies involves some compromises and as a result, transistors found in state-of-the-art BiCMOS processes have reduced performance compared to their counterparts manufactured in their pure technologies [46]. This is partly due to the fact that state-of-the-art BiCMOS processes are typically lagging state-of-the-art CMOS processes by a technology node or two. Still, having both BJTs and MOSFETs available often eases some design tasks. This approach provides for optimum circuit implementation and from a circuit designer point of view, BiCMOS appears to be the better choice [47,48]. Manufacturing of BiCMOS circuits requires more processing steps than regular CMOS thus adding to production costs. Furthermore, digital circuit implementations in BiCMOS need larger areas than equivalent CMOS implementations. Some of the short-comings of BiCMOS are illustrated by two Bluetooth transceiver design examples from the public literature [49, 50]. Reaching comparable performance levels the 0.18µm CMOS implementation provides a 40% area reduction compared to the BiCMOS implementation. Therefore, despite claims that aggressive scaling of CMOS adds to processing costs and that the cost advantage is weakening, CMOS still remains the most cost effective technology [46, 51-53].

# 1.4 Choosing the Appropriate Technology

It has been claimed that for modern wireless communication systems a given performance at a low cost is preferred over improved performance at a greater cost [43]. That is, if a functionality is implemented using any number of technologies, at sufficient performance, the cheaper solution always wins. In today's practical cellular networks the scenario is not quite as simple as that. To increase their market shares network operators have been engaging in costly discount campaigns for the last five to ten years. The result is that operators sell selected handsets at prices that are significantly lower than the cost price of the handset. Customers often tend to blame the network operators if they experience performance reductions and with this in mind the operators are of course interested in promoting only handsets with good performance. As a consequence, low cost on its own is not a sufficient performance parameter. Low cost has to come together with good performance, a low form factor, and low power operation if the product is to become successful.

Independently of technology, integrated design has potential for meeting all these requirements. Still, as already stated, clearly there is a number of tradeoffs involved in choosing the right technology for any given application. Only within the last decade CMOS has seriously been considered an analog high frequency technology option [54–56]. Through enginuitive designs, limitations have been negotiated to make the available CMOS performance sufficient for many applications [51]. Still, depending on a particular application either technology, bipolar or CMOS, may be favored. If, for instance, low current consumption is required, MOS has a switching speed advantage over the BJT. The opposite is the case if instead low voltage is of prime concern [57]. When cost is considered the raw technology expense is unfortunately not a sufficient parameter. If this was indeed the case, every IC design would then be implemented in a standard digital CMOS process.

While academia can afford to look at the cheapest as well as the most expensive and exotic technologies, industry must ensure competitiveness. Consequently, industry has time-to-market as one of its major design factors. For that matter the net cost of a product may in fact be optimized short term by selecting the more superior technology despite its excess cost. Here, the additional design effort required with using a cheaper technology may exceed its cost advantage. Another approach to cost reduction is through system level design optimization. In an attempt to mitigate some of the expensive external components, architectures have been revised over time. This is also apparent when Figures 1.1 and 1.2 are considered. Here, not only a change in implementation technology makes the difference, the system architectures of the two transceivers also differ.

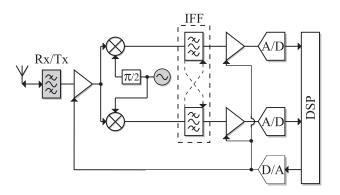

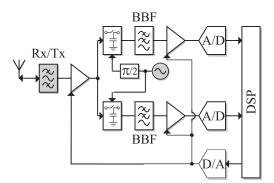

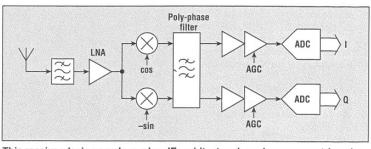

Two of the more popular outcomes of the research on receiver and transmitter architectures are the reintroduced *Direct-Conversion Receiver* (DCR) topology and also the *Low Intermediate Frequency* (Low-IF) topology. The transceiver in Figure 1.2 makes use of the latter topology. When an optimum receiver topology is considered, the DCR stands out as being the most obvious choice. By converting the incoming RF signal down to baseband in a single step, high frequency signal processing is minimized, the image-reject filter at RF is mitigated and the same goes for the IF filter. However, the DCR concept suffers from a number of inherent disadvantages such as sensitivity towards DC-offset and low frequency noise. When both these issues are considered bipolar devices are favored over CMOS. Due to its inferior matching performance, CMOS designs result in higher DC-offset levels and due to flicker noise performance CMOS also produces more low frequency noise.

This lack in performance combined with the picture of the DCR as the optimum topology did not favor CMOS for RF-IC design. Based on a principle of concurrency in design the Low-IF is found to favor CMOS [58]. This is especially the case for narrow-band systems where signal modulations with a significant DC and/or low frequency content are used. This is also reflected by the success of the design in Figure 1.2. For narrowband systems the disadvantages of the DCR are outspoken and generally favors a bipolar implementation. If instead a Low-IF topology is used the main limitations of the DCR are mitigated and a CMOS solution becomes feasible. One reason for this is the use of poly-phase filtering which allows for image-signal rejection using analog signal processing in the complex domain [59–61]. When considering wideband systems the DCR offers better performance. One reason for this is that the wideband nature of the signals makes these more robust towards removal of low frequency content. In such cases it is possible to compensate for the short-comings of CMOS which makes this the favored technology. This fact is clearly reflected by the many WLAN [62–65] and WCDMA [66–70] designs presented in the public literature over the last couple of years. A majority of these utilize the direct-downconversion principle.

# 1.4-1 The Single-Chip Vision

There is a great tendency towards single-chip transceiver integration in the published RF-CMOS work. The basic philosophy being that the full potential of CMOS is unleashed only when analog RF and digital baseband are integrated on a single die. Such a design would in principle only require the addition of a display and a keypad to form a complete handset solution. While the single-chip vision represents a common goal for a majority of researchers, the viability of the single-chip idea remains a much debated issue. At least two important issues fuel the debate; i) design yield and ii) processing yield.

One of the major concerns related to design yield is the isolation properties of the substrate. With requirements for higher digital operating frequencies and increased analog accuracy, precise modeling of the substrate and all coupling effects is mandatory for the single-chip ever to become realistic. Processing yield is another limiting factor for the single-chip vision. In any IC fabrication process a number of error spots is going to exist on the wafers. Despite the significant improvements in feature-size the number of error spots per wafer has not seen the same improvement. For a typical CMOS process the defect density is around one per  $cm^{-2}$  [71]. For a 12" wafer this would imply that approximately 730 error spots would be spread across the wafer. Assuming a die area of 5mm x 5mm a total number of 2920 dies would be on the wafer. With 730 error spots this would result in a 75% yield. Such error spots set a limit on the resulting yield according to [72]

$$Yield = \frac{\text{Number of functional chips}}{\text{Total number of chips}} \approx \exp(-l \cdot A), \qquad (1.1)$$

PAGE **10**

where A is the chip area and l is a function of the defect density for the given fabrication process. According to Equation (1.1), for a 95% yield design a doubling of the area would result in a yield of 86%. In high volume productions a 9% drop in yield represents a significant loss.

As a result of such practical problems single-chip design for wireless communications is still not a cost effective solution [73]. The standing question is then whether or not a single-chip solution is ever to become cost effective.

# 1.5 CMOS as an RF Technology – Performance vs. Requirements

From being mostly a low and medium frequency technology, CMOS is already targeting a number of RF applications. One of the driving factors behind this is the on-going development in semiconductor technology. This has resulted in the RF potential of CMOS processes becoming more evident than ever. The major achievement here being the continuous decrease in minimum feature size. Only a few years ago did the *Semiconductor Industries Association* (SIA) start to define CMOS processes in terms of nanometer rather than micrometers and already the  $0.1\mu$ m milestone has been reached. This illustrates the swift evolution in CMOS technology. In contrast to digital design requirements, the technical requirements for analog transceiver functions are considerably more complicated [57]. Where speed, yield, and power dissipation are the major performance metrics for digital designs, analog designs face additional metrics such as noise, accuracy, linearity, selectivity, and high frequency gain. If CMOS can adjust to those RF needs, it has the potential of dominating analog RF design as well as digital design.

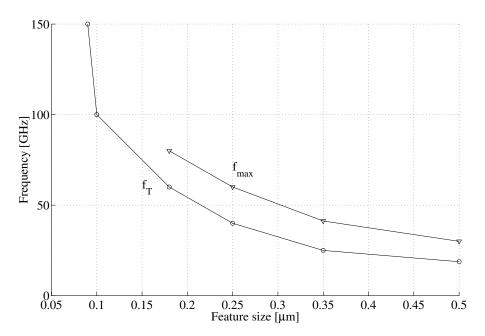

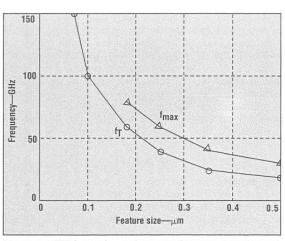

To indicate the analog performance of a given technology two parameters,  $f_T$  and  $f_{max}$ , are particularly popular. The first,  $f_T$ , represents the frequency at which the extrapolated current gain of the MOSFET reaches unity. The second one,  $f_{max}$ , represents the frequency at which the power gain falls to unity. Simplified expressions for the aforementioned  $f_T$  and  $f_{max}$  are given as [74]

$$f_T = \frac{g_m}{2\pi \left(C_{gs} + [1+g_m]C_{gd}\right)}$$

[Hz] (1.2)

$$f_{max} \approx \frac{1}{4\pi} \sqrt{\frac{2\pi f_T}{r_g \cdot C_{gd}}} = \frac{1}{4\pi} \sqrt{\frac{g_m}{r_g (C_{gd} \cdot C_{gs} + [1 + g_m] C_{gd}^2)}}$$

[Hz], (1.3)

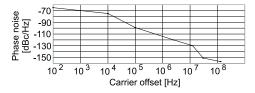

where  $C_{gs}$  is the gate-to-source capacitance,  $C_{gd}$  is the gate-to-drain capacitance,  $r_g$  is the gate resistance, and  $g_m$  is the transconductance of the device. The down-scaling into deep submicron leads to  $f_T$  and  $f_{max}$  values in excess of requirements which, as a conservative measure, is ten times the operating frequency of the circuit. As Figure 1.3 illustrates, 5GHz operation is well within the capabilities of modern CMOS processes.

Figure 1.3: Measured CMOS  $f_T$  and  $f_{max}$  values versus feature size [75].

### 1.5-1 High frequency gain

To provide for high frequency operation sufficient gain is crucial. This is particularly the case when implementing active circuits as the gain has to come at low current levels to save power. With  $f_T$  values of silicon processes, sub-micron CMOS processes in particular, reaching levels comparable to GaAs devices, sufficient high frequency gain is provided. However, the  $f_T$  measure ignores any effects the gate resistance,  $r_g$ , and drain-to-source junction capacitance,  $C_{ds}$ , have on high frequency performance. In that sense, the  $f_{max}$  measure is a more appropriate measure as this includes the gate resistance and thereby takes layout effects into account. In fact, the high  $f_{max}$  values reported for CMOS result primarily from lowered gate resistances due to fingered transistor layout [57]. From the first-order approximation in Equation (1.3) it is clear that  $f_{max}$  is increased either by reducing the gate resistance, the gate-drain or gate-source capacitances, or by increasing  $g_m$ .

In providing RF gain, sufficient transistor performance is not always enough. As many RF circuits, such as LNAs and oscillators, are tuned to some narrow frequency band using an LC resonator type load, the performance of these reactive components also plays an important part in ensuring ample RF gain. Take for instance a single-FET LNA where the parasitic capacitances are used in conjunction with a load inductor to implement the LC tank. The resulting peak voltage gain for this circuit may be expressed as  $g_m$  times  $Z_0$  where  $Z_0$  is the impedance of the tank at resonance. The attainable impedance is here often limited by the quality factor, Q, of the inductor. The resonance impedance may be written as

$$Z_0 = Q \cdot \omega_0 \cdot L = \frac{Q}{\omega_0 \cdot C} \qquad [\Omega], \tag{1.4}$$

where *L* is the resonator inductance, *C* is the resonator capacitance, and  $\omega_0$  is the resonance frequency. Based on this the voltage gain may be expressed as

$$A_V = g_m \cdot Z_0 = \frac{g_m \cdot Q}{\omega_0 \cdot C} \qquad [-] \tag{1.5}$$

From this it appears that a high RF gain requires low loss passive devices and tight control of parasitic capacitances if power consumption is to remain reasonable. However, increasing the Q-value is also governed by a compromise. Circuits based on large loaded Q-values are highly susceptible to de-tuning due to either component spread or simply from insufficient estimation and modeling of parasitics [76]. As an example, for any given circuit with a gain tolerance specification there is a technology dependency as component spread sets a limit on how high the Q is allowed to go. In turn this means that there is also a limit to how low the power consumption may go.

#### 1.5-2 Low Noise

Apart from amplification of the wanted signal RF front-ends also need to display lownoise performance in order to meet sensitivity requirements. Typical front-end noise figure requirements range from 5–10dB when measured at the antenna terminals [77, 78]. As the LNA has significant influence on the overall noise performance this is a key circuit element in meeting noise figure requirements. Typically LNAs must display noise figures of less than 3dB for the overall receiver to meet specifications [57]. Eventually at some point the incoming signal is translated to baseband in the receiver chain. Depending on the nature of the receiver architecture, input-referred noise from baseband circuits may drown the weak input signals. At the expense of increased power consumption a high gain LNA may help overcome this. However, to prevent the need for very high gain in RF stages baseband circuits must also be low noise. This relation is an often neglected issue in the public literature.

Considering the noise performance of the MOSFET, a simplified expression for the minimum noise figure is given as [57]

$$NF_{min} \approx 1 + k \cdot g_m \cdot r_g \cdot \left(\frac{f}{f_T}\right)^2 \quad [-],$$

(1.6)

where  $r_g$  is the gate resistance of the device, k is a unitless technology dependent constant, and  $g_m$  is the device transconductance. Equation (1.6) illustrates the importance of having both a low gate resistance and a high  $f_T$ . While technology scaling has a significant positive effect on  $f_T$  the reduced feature sizes increase  $r_g$  to form a trade-off in noise performance. The minimum noise figures for MOS devices are in the order of 0.6 - 0.8dB which is slightly lower than for bipolar devices [45]. That CMOS is capable of producing low noise LNAs is evident from various reported works where noise figures around 1.2dB – 3dB have been reported [79–82]. In fact, CMOS is gradually approaching the sub-1dB NF range [45, 83, 84].

A low  $NF_{min}$  for a circuit does not on its own guarantee a resulting low noise figure. It is also crucial to know the optimum source impedance,  $Z_{SOF}$ , for the device as well as the spacings of

the noise circles as these determine how easy optimum noise matching may be attained. The performance gap between reported  $NF_{min}$  values and actual circuit noise figures relates to the fact that low noise input matching to 50 $\Omega$  is hard for MOS devices. This is partly due to the inherent capacitive nature of the MOSFET and partly due to the large component variations. This implies that a degradation of noise or power dissipation performance results from moving the input impedance closer to 50 $\Omega$ . So once again a tradeoff is the result. To understand these trade-offs consider the thermal noise for a MOS device given as [85]

$$v_t = \sqrt{\frac{\langle |\boldsymbol{e}_{tn}|^2 \rangle}{\Delta f}} = \sqrt{\frac{4kT \cdot \boldsymbol{\gamma} \cdot \boldsymbol{g}_{d0}}{\boldsymbol{g}_m^2}} = \frac{2\sqrt{kT \cdot \boldsymbol{\gamma} \cdot \boldsymbol{g}_{d0}}}{\boldsymbol{g}_m} \qquad \left[\frac{\mathrm{V}}{\sqrt{\mathrm{Hz}}}\right],\tag{1.7}$$

where k is Boltzmann's constant and  $g_{d0}$  is the drain-source conductance at zero  $V_{DS}$  voltage. The parameter  $\gamma$  equals unity at zero  $V_{DS}$  and, for long-channel devices, decreases to approximately 2/3 in saturation. For short-channel devices  $\gamma$  takes on a value of two to three or even larger [74]. According to Equation (1.7) a large  $g_m$  value helps to reduce thermal noise. Another important noise source results from the generation of flicker noise. The flicker noise adds a noise current to the drain-source current of the MOSFET. The spectral characteristics of flicker noise follow a 1/f characteristic that, when reflected back to the gate, is described as [85]

$$v_f = \frac{i_f}{g_m} = \frac{1}{g_m \cdot L} \sqrt{\frac{KF \cdot I_D^{AF}}{f \cdot C'_{ox}}} \qquad \left[\frac{V}{\sqrt{Hz}}\right],\tag{1.8}$$

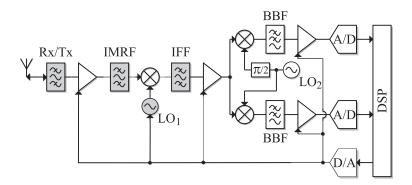

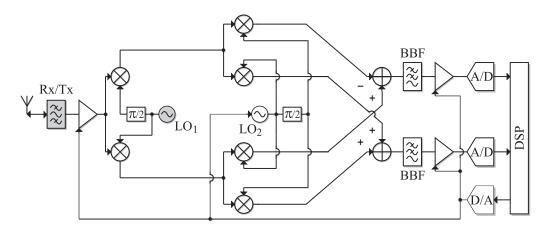

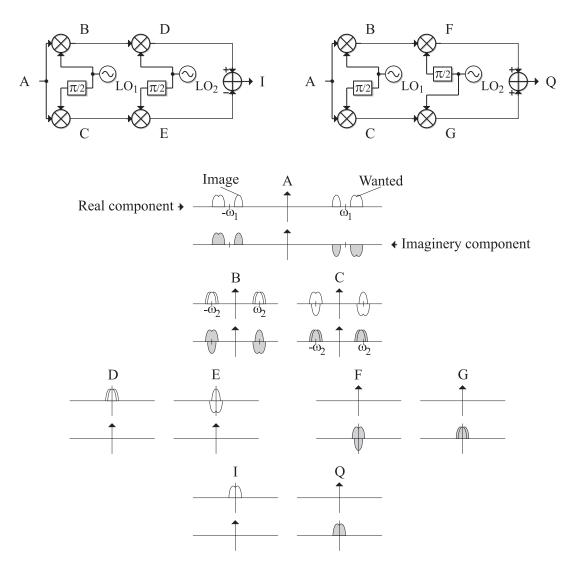

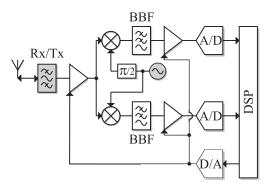

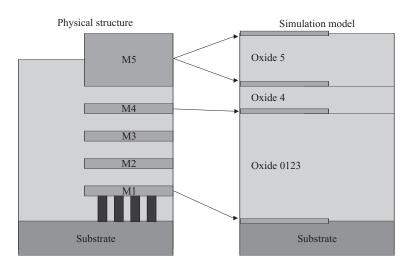

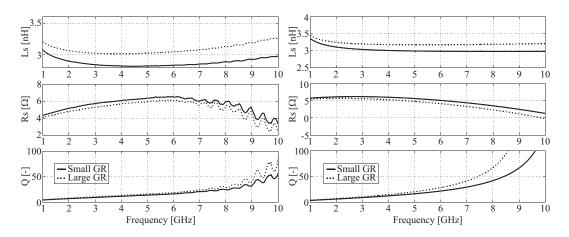

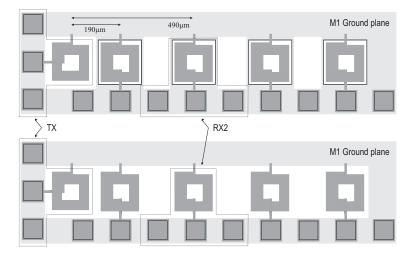

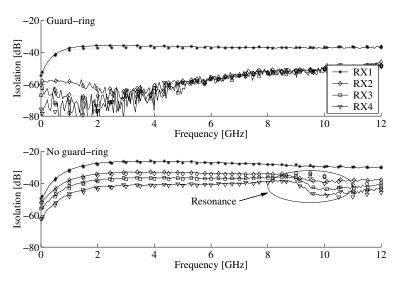

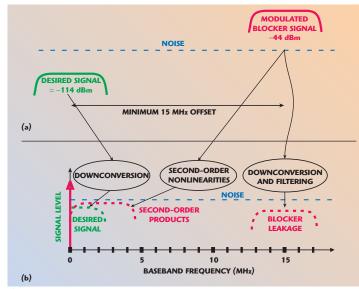

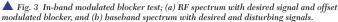

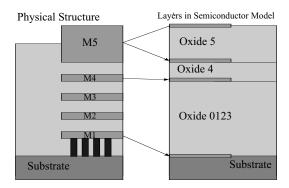

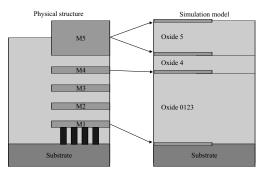

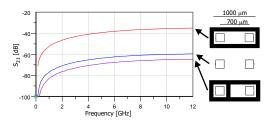

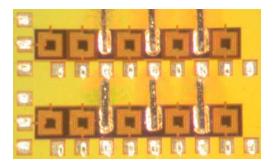

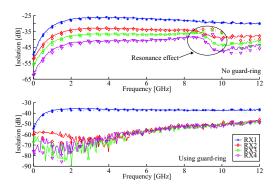

where the flicker noise coefficient, KF, typically is in the order of  $10^{-25}V^2F$ , the flicker noise exponent, AF, is around 0.5 to 2,  $C'_{ox}$  is the gate oxide capacitance, and  $I_D$  is the DC drain current. Hence, in reducing the flicker noise contribution long devices with large transconductances are needed. Comparing Equations (1.6) and (1.8) reveals that the overall noise performance may be improved only through the use of long devices or by a combination of large  $g_m$  and large  $f_T$ .