#### **Aalborg Universitet**

| Grid Converters for Stationary Battery Energy Storage Systems                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trintis, Ionut                                                                                                                                                                |

| minus, ionat                                                                                                                                                                  |

|                                                                                                                                                                               |

|                                                                                                                                                                               |

|                                                                                                                                                                               |

| Publication date: 2011                                                                                                                                                        |

| Document Version Accepted author manuscript, peer reviewed version                                                                                                            |

| Link to publication from Aalborg University                                                                                                                                   |

|                                                                                                                                                                               |

| Citation for published version (APA): Trintis, I. (2011). Grid Converters for Stationary Battery Energy Storage Systems. Department of Energy Technology, Aalborg University. |

| Citation for published version (APA): Trintis, I. (2011). Grid Converters for Stationary Battery Energy Storage Systems. Department of Energy                                 |

**General rights**Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# GRID CONVERTERS FOR STATIONARY BATTERY ENERGY STORAGE SYSTEMS

IONUT TRINTIS

DISSERTATION SUBMITTED TO THE

FACULTY OF ENGINEERING & SCIENCE AT

AALBORG UNIVERSITY

IN CANDIDACY FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY IN ELECTRICAL ENGINEERING

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF ENERGY TECHNOLOGY

SUPERVISOR: STIG MUNK-NIELSEN

Co-Supervisor: Remus Teodorescu

September 2011

© Copyright by Ionut Trintis, 2011. All rights reserved.

Department of Energy Technology Alborg University Pontoppidantraede 101 DK-9220 Alborg East

Printed in Denmark by UniPrint ISBN: 978-87-89179-83-4

#### Abstract

The integration of renewable energy sources in the power system, with high percentage, is a well known challenge nowadays. Power sources like wind and solar are highly volatile, with fluctuations on various time scales. One long term solution is to build a continentwide or worldwide supergrid. Another solution is to use distributed energy storage units, and create virtual power plants. Stationary energy storage is a complementary solution, which can postpone the network expansion and can be optimized for different kind of grid services. As an energy storage solution with timing for few seconds to hours, rated at MW and MWh, battery energy storage systems are suitable and efficient solutions.

Grid connection of the storage system can be done at different voltage levels, depending on the location and application scenario. For high power and energy ratings, increase in the battery and converter voltage ratings can enhance the overall system efficiency.

This work is divided in two parts, "Control of DC-AC Grid Converters" and "Medium Voltage Grid Converters for Energy Storage". The first part starts with a brief review of control strategies applied to grid connected DC-AC converters. A control implementation was realized for a 100 kW active rectifier to be used in a 6 kV battery energy storage test bench. In the second part, different solutions for power converters to interface energy storage units to medium voltage grid are given. A new modular multilevel converter concept is introduced, where the energy storage units are integrated in each converter cell.

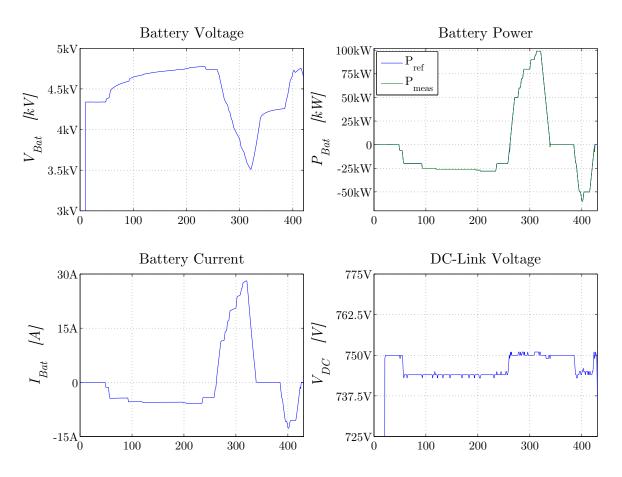

The control of DC-AC grid converters has been a research subject for more than a century, and there is still place for improvements. A review of the main control principles is given in the first part. The stationary frame control was implemented for a low-voltage 100 kW bidirectional grid converter, to be used in a high voltage battery energy storage test bench. The control structure proved to be stable without damping. The converter was tested in the test bench and the experimental results are presented.

Multilevel converters are replacing the classical two-level converters more and more, on a large variety of applications. For medium voltage applications, multilevel converters are a necessity. The second part presents a review of hard-switched and soft-switched multilevel converter topologies for medium voltage. Four converter topologies were chosen as potential solutions for direct connection of battery energy storage systems to the grid. An evaluation is done, in terms of semiconductors requirements and losses, output voltage quality and common mode voltage.

The main advantage of batteries direct connection to the grid is the high efficiency potential. However, this solution is suitable only for battery technologies with low voltage variation. It is also necessary to build a battery system with high amount of serial connected cells, and the knowledge in this field is still limited nowadays. Therefore, two-stage converters solutions were introduced to overcome these disadvantages. Modular multilevel converters can make use of battery voltage technologies where the maturity and reliability is well proven in industry.

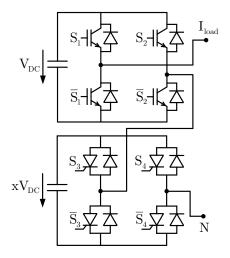

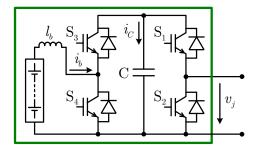

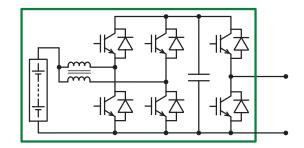

Cascaded H-bridge topology with bidirectional boost converters is proposed to interface low voltage batteries to the medium voltage grid. A control structure based on single phase control is proposed. It balances the capacitor voltages and the state of charge of batteries from different cells. A semiconductor loss analysis is performed and it shows the loss distribution in the converter cell and the efficiency over a wide battery voltage variation.

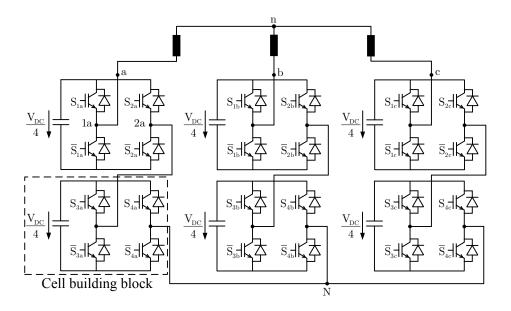

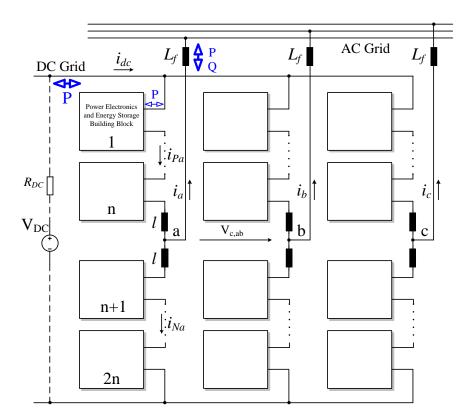

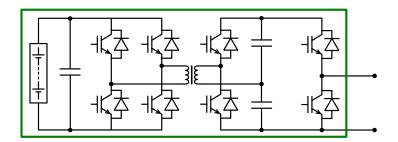

A new modular multilevel converter structure with integrated energy storage is introduced. This converter structure is suitable to interface low and medium voltage energy storage units to medium and high voltage grids. It can also interconnect a DC and AC grid with bidirectional power flow, were both can be backed-up for the distributed energy storage units installed in each converter cell. The converter operation and control methods are presented, and the energy storage system construction concept and challenges are addressed.

#### Acknowledgements

I will firstly like to express my gratitude to my supervisor, Prof. Stig Munk-Nielsen, for all his time and patience invested in this project. The endless interesting discussions we had during the PhD period created ideas, ground and shape for this work. Many thanks to my co-supervisor Prof. Remus Teodorescu for all this technical support based on straight-forward approaches. Discussions along the project helped to clarify to myself many of the technical issues in grid connected converters and power systems that integrate power converters.

I would like to acknowledge the financial support from the E.ON AG, under the E.ON Research Initiative, the call on Energy Storage with the project 2007/B4-Highly Efficient and Reliable Modular Battery Energy Storage Systems (HERMES). I would also like to acknowledge the supervisors from E.ON UK for the good cooperation and good understanding they had during the project, and in particular to Matthew Knight and Stuart Norman. I acknowledge the financial support also from Aalborg University.

I would like to thank to our Prof. Frede Blaabjerg for making this project happen. Without his good cooperation with Aachen University, and his expertise in power electronics, this work would never be in place. Many thanks to Prof. Rik W. De Doncker, which was at the ground of the HERMES project and responsible with the good coordination. His active participation, interesting discussions and feedback during the meetings was very important to all the project partners.

I want to thank to all the colleagues from Aachen University, for their professionalism and their kind help during my stay in the study abroad at ISEA and IFHT. In particular, I thank to Stephan Thomas for the interesting discussions we had and all the help during the project.

Many thanks to all my colleagues from the Department of Energy Technology, Aalborg University (AAU) - very nice people that created a pleasant research environment where kind help at all levels is provided by default. The interesting discussions with them can always generate new ideas, and can clarify technical issues on a large variety of topics.

Many thanks to the PhD assessment committee - Sergio Busquets-Monge (UPC), Paul Thoegersen (KK Electronic A/S), and Dezso Sera (chairman, AAU) - for all the effort they have done to review and assess the present work. Special thanks to Sergio, who made an in-depth review and provided valuable feedback and corrections.

I would like to acknowledge Prof. Dan Floricau, "Politehnica" University of Bucharest (UPB), for his initiation in the field of power electronics. He was the teacher that cultivated at first, my passion for multilevel converters.

I would also like to thank to Prof. Pedro Rodriguez for teaching me the basics of PLL, to Prof. Vassilios Agelidis for the interesting discussions and valuable feedback during his visit at AAU, to Prof. Marco Liserre for teaching the basics of grid connection control and to Prof. Joseph Guerrero for teaching the basics of microgrids.

Last but not least, I would like to thank to my wife Ancuta Gabriela for her continuous support at all levels, and to our parents which were close to our hearts the whole time.

I would like to apologise and thank also to the people that had a contribution to this work and I probably forgot to mention.

IONUT TRINTIS,

Aalborg, September 2012

$To \ Ancuta$   $To \ our \ Families$

# Contents

|    |         | e Page                                                                                                       | j            |

|----|---------|--------------------------------------------------------------------------------------------------------------|--------------|

|    |         | $\operatorname{nowledgements}$                                                                               | iii          |

|    |         | tents                                                                                                        | vi           |

|    |         | nenclature                                                                                                   | xii          |

|    | 11011   | reneration                                                                                                   | 711          |

| 1. |         | oduction                                                                                                     | 1            |

|    |         | Background and motivation                                                                                    | 1            |

|    | 1.2.    | Objectives                                                                                                   | 3            |

|    | 1.3.    | Methodology                                                                                                  | 4            |

|    | 1.4.    | Limitations                                                                                                  | 4            |

|    | 1.5.    |                                                                                                              | 5            |

|    |         | 1.5.1. List of Publications                                                                                  | 6            |

|    | 1.6.    | Outline                                                                                                      | 6            |

|    |         |                                                                                                              |              |

| 1  | Ca      | ontrol of DC-AC Grid Converters                                                                              | 9            |

| Ι. | CC      | ontrol of DC-AC Grid Converters                                                                              | 9            |

| 2. | Stat    | e-of-the-Art on Control for DC-AC Grid Converters                                                            | 11           |

|    | 2.1.    | Introduction to Grid Control Structures                                                                      | 11           |

|    | 2.2.    | Synchronization Methods                                                                                      | 12           |

|    |         | 2.2.1. Three-phase methods                                                                                   | 13           |

|    |         | 2.2.2. Single-phase methods                                                                                  | 16           |

|    | 2.3.    | Current Control Methods                                                                                      | 17           |

|    |         | 2.3.1. Natural frame                                                                                         | 17           |

|    |         | 2.3.2. Stationary frame                                                                                      | 18           |

|    |         | 2.3.3. Rotating frame                                                                                        | 19           |

|    |         | 2.3.4. Hysteresis                                                                                            | 20           |

|    |         | 2.3.5. Direct power control                                                                                  | 22           |

|    |         | 2.3.6. Predictive                                                                                            | 23           |

|    |         | 2.3.7. Passivity based control                                                                               | 24           |

|    | 2.4.    | DC Voltage Control                                                                                           | 26           |

|    | 2.5.    | Summary                                                                                                      | 28           |

| 2  | ۸ - ۰ ' | us Dostifica Implementation for a IIV France Character Test D                                                | 21           |

| ა. |         | ve Rectifier Implementation for a HV Energy Storage Test Bench Introduction to the Energy Storage Test Bench | <b>31</b> 31 |

|    | o.t.    | introduction to the Energy Storage Test Dench                                                                | $^{01}$      |

#### Contents

|     |              | Control of the DC-AC grid converter                         |      |

|-----|--------------|-------------------------------------------------------------|------|

|     | 3.5.         | Experimental results                                        |      |

|     | 3.6.         | Summary                                                     | . 42 |

| 11. | . M          | edium Voltage Grid Converters for Energy Storage            | 45   |

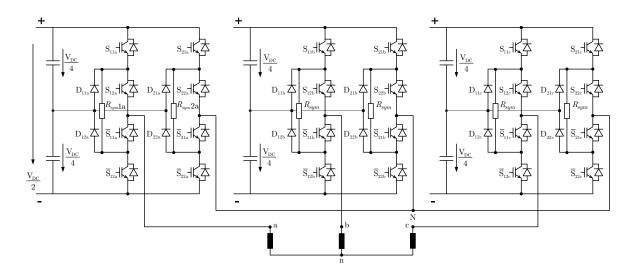

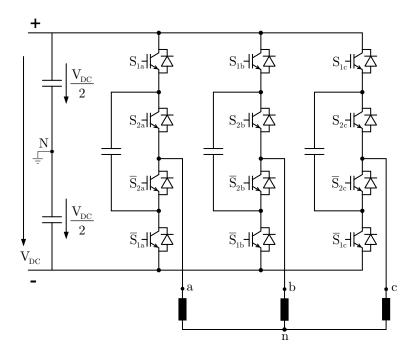

| 4.  |              | te-of-the-Art on Medium Voltage Multilevel Converters       | 47   |

|     |              | Introduction                                                |      |

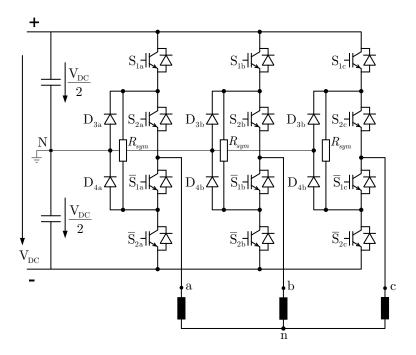

|     |              | Cascaded H-bridge Converter                                 |      |

|     |              | Neutral Point Clamped Converter                             |      |

|     | 4.4.         | H-bridge Neutral Point Clamped Converter                    |      |

|     | 4.5.<br>4.6. | Flying Capacitor Converter                                  |      |

|     |              | Cascaded half-bridge Converter                              |      |

|     |              | Summary                                                     |      |

|     | 4.0.         | Summary                                                     | . 02 |

| 5.  | Sing         | gle-Stage Medium Voltage Grid Converters for Energy Storage | 65   |

|     | 5.1.         | Introduction                                                | . 65 |

|     | 5.2.         | Converter specifications                                    |      |

|     | 5.3.         | Semiconductors requirements                                 |      |

|     | 5.4.         | Design of passive components                                |      |

|     |              | 5.4.1. Output filter design                                 |      |

|     |              | 5.4.2. Design of flying capacitors                          |      |

|     |              | 5.4.3. DC-link capacitors size                              |      |

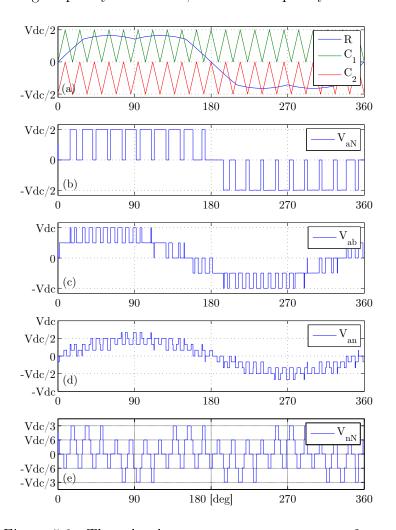

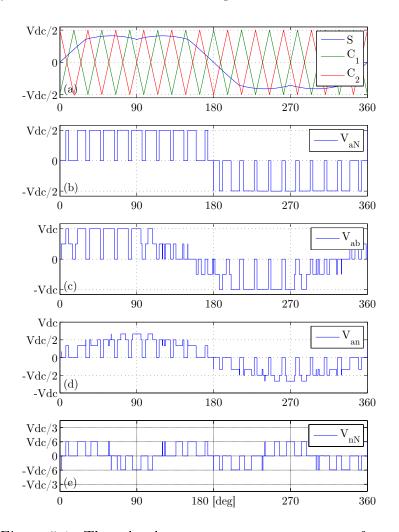

|     | 5.5.         | Simulation results                                          |      |

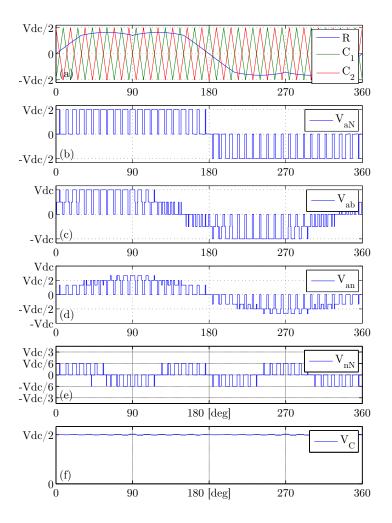

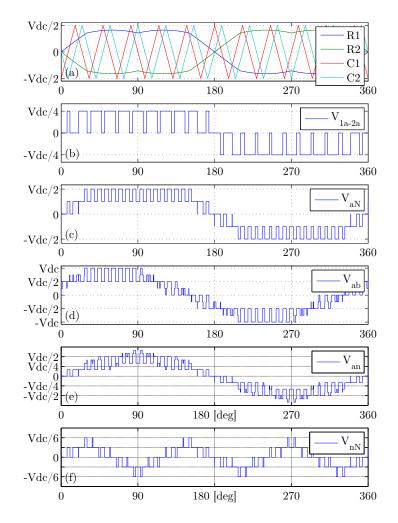

|     |              | 5.5.1. Converters output voltages                           |      |

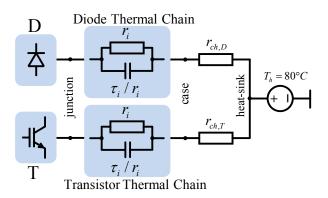

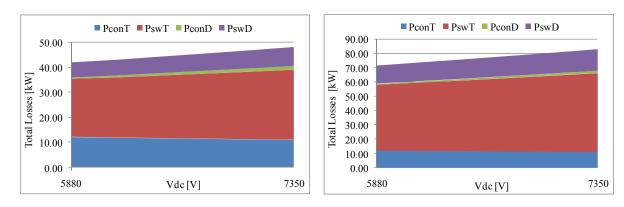

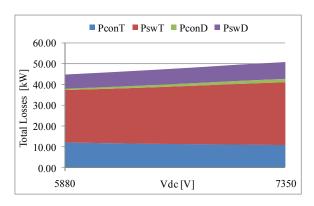

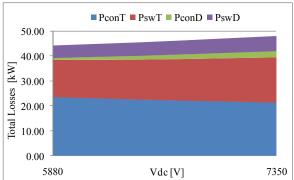

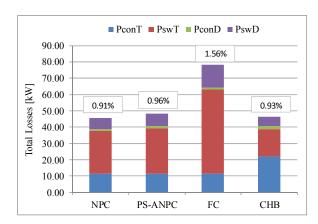

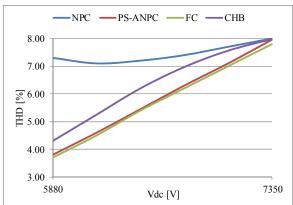

|     | 5.6          | 5.5.2. Converters semiconductor loss analysis               |      |

|     | 5.0.         | Summary                                                     | . 10 |

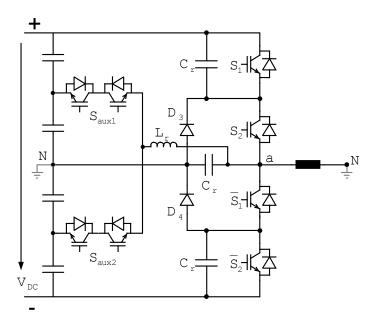

| 6.  | Two          | o-Stage Cascaded H-bridge Grid Converter for Energy Storage | 79   |

|     | 6.1.         | Introduction                                                | . 79 |

|     | 6.2.         | Overview of CHB active rectifier control structures         | . 82 |

|     | 6.3.         | Proposed CHB control structure                              | . 82 |

|     | 6.4.         | Converter model                                             | . 84 |

|     | 6.5.         | Simulation results                                          | . 85 |

|     |              | 6.5.1. Performance of the proposed control strategy         |      |

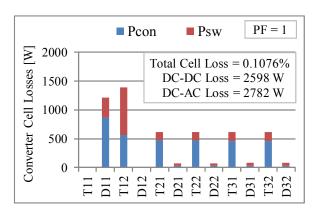

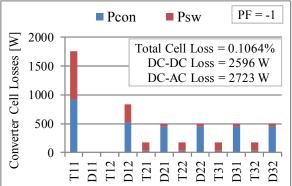

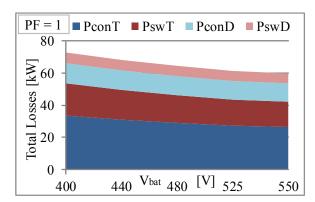

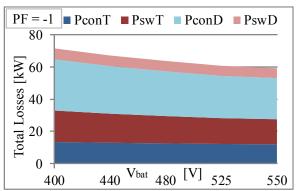

|     |              | 6.5.2. Power semiconductor loss analysis                    |      |

|     | 6.6.         | Summary                                                     | . 92 |

| 7.  | New          | Modular Multilevel Converter with Integrated Energy Storage | 93   |

|     | 7.1.         | Introduction                                                | . 93 |

| $\sim$ | 1 |          | 1  |

|--------|---|----------|----|

| Con    | Ť | $\rho n$ | TC |

| -      | U | -11      | UD |

| 7           | .2.   | New Modular Multilevel Converter Concept   | . 94  |

|-------------|-------|--------------------------------------------|-------|

| 7           | .3.   | Converter Operation and Control Methods    | . 97  |

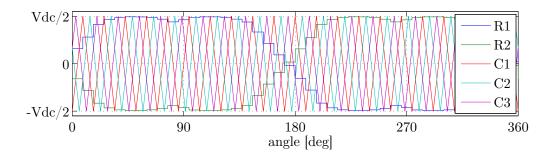

|             |       | 7.3.1. Modulation Strategies               | . 97  |

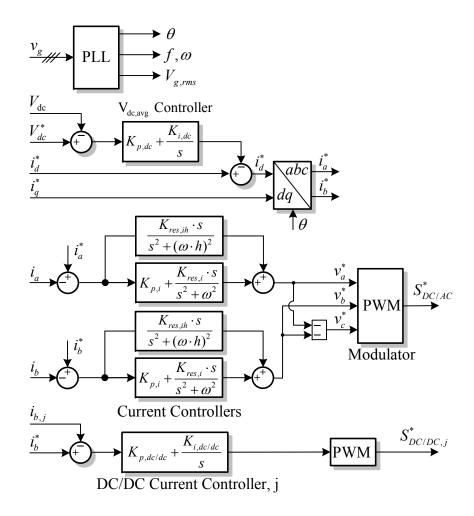

|             |       | 7.3.2. Current Control                     | . 99  |

|             |       | 7.3.3. DC Voltage Control                  | . 99  |

|             |       | 7.3.4. DC-DC Converters Control            | . 100 |

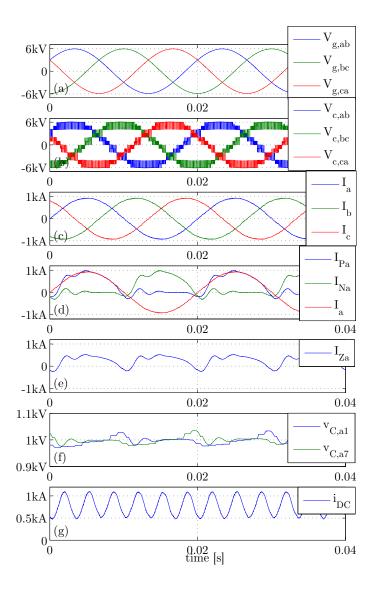

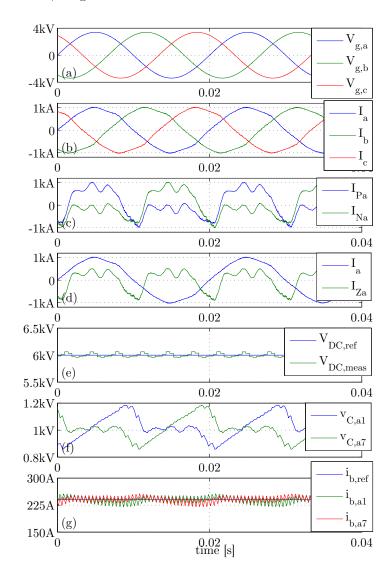

| 7           | .4.   | Operation Modes and Their Performance      | . 101 |

| 7           | .5.   | Energy Storage System Construction Concept | . 106 |

| 7           | .6.   | Storage System Design Considerations       | . 107 |

| 7           | .7.   | Summary                                    |       |

| 111         | $C_0$ | nclusions                                  | 111   |

|             |       | inclusions                                 |       |

| 8. C        | Con   | clusions and Future Work                   | 113   |

| 8           | .1.   | Summary and Conclusions                    | . 113 |

| 8           | .2.   | Future Work                                | . 115 |

| Bibli       | iogı  | raphy                                      | 117   |

| <b>A</b> 1. | Spa   | ace Vector Transformations                 | 131   |

| 1           | -     | Clarke Transformation                      | . 131 |

| 2           |       | Park Transformation                        |       |

| 3           |       | Unbalanced signals decomposition           |       |

| A2.         | Ins   | tantaneous Powers Calculation              | 133   |

### Nomenclature

#### Abbreviations

AC alternating current

DC direct current

DC-DC DC to DC converter DC-AC DC to AC converter

HV high voltage LV low voltage

IGBT insulated gate bipolar transistor integrated gate commutated thyristor

VSC voltage source converter

CHB cascaded H-bridge

ChB cascaded half-bridge

ANPC active neutral point clamped NPC neutral point clamped

ARCP auxiliary resonant commutated pole

FC flying capacitor

DAB dual active bridge

FIT failure in time

BESS battery energy storage system

SOC state of charge

DOD depth of discharge

PLL phase-locked-loop

QSG quadrature signal generator

second order generalized integrator

SRF synchronous reference frame

PNSC positive negative sequence calculator

I integrator

PI proportional integrator

PR proportional resonant

DPC direct power control

PWM pulse width modulation

SVM space vector modulation

#### Contents

| PS | phase shift |

|----|-------------|

| LS | level shift |

selective harmonic elimination SHE

total harmonic distortion THD

PFpower factor

#### **Symbols**

ttime ffrequency angular frequency  $\omega$ voltage vicurrent  $\theta$ angle Linductance Ccapacitance Rresistance Qelectric charge complex number sactive power preactive power q $f_p$ active power slope reactive power slope  $f_q$  $\psi$ error  $k_p$ proportional gain  $k_i$ integral gain  $S^*$ switching function / duty cycle Spower electronic switch

#### **Subscripts**

grid side gconverter side

DC side DC

stationary frame  $\alpha,\beta$ rotating frame dqresonant

res

harmonic order h

#### Superscripts

+positive sequence negative sequence imposed / reference

# Chapter 1.

## Introduction

#### 1.1. Background and motivation

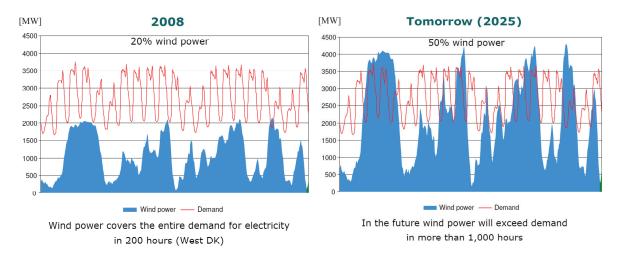

The necessity to reduce the harmful emissions from the conventional power plants, leads to a transition of the power systems towards dispersed generation production based on renewable energy sources. Wind power and photovoltaic installations are the most important renewables with significant worldwide installed capacities and high annual growth rate. The drawback of this renewable energy sources is the high fluctuation on daily and seasonal basis. This fact makes their integration with high percentage into the grid a well-known challenge, since the security of supply is a high priority [1]. This can be deducted from Fig. 1.1 which shows the wind power production and demand in Denmark West for 20% wind in 2008 and the scaling to 50% for 2025 [2].

Figure 1.1.: Wind power production and demand for Denmark West [2]

One way to overcome this drawback is to strengthen the electrical network. However, this implies high expenses and the overall efficiency drops when the energy is transported over long distances [3]. Moreover, the grid codes for different interconnected countries must be unified and this is a long time task [4]. Another way is to install distributed energy

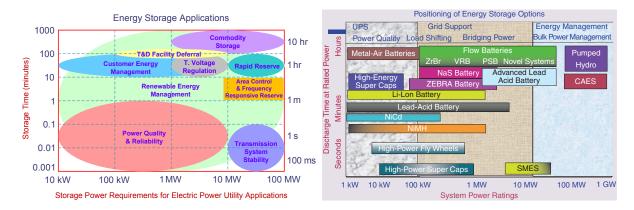

storage units. Using communication between generators, loads and storage systems, the high level control can define groups that can operate independent or together with the main electrical grid and can behave similar to a conventional power plant [5, 6]. The generation-consumption can then be optimized by using minimization criteria for the given priority (lowest price, highest efficiency, lowest CO<sub>2</sub>, etc.). Stationary energy storage is a complementary solution, which can be optimized for different kind of services provided. In Fig. 1.2 the potential applications for energy storage are shown, and the state-of-the-art storage technologies are presented in Fig. 1.3 [7].

Figure 1.2.: Storage Applications

Figure 1.3.: Storage Technologies [7]

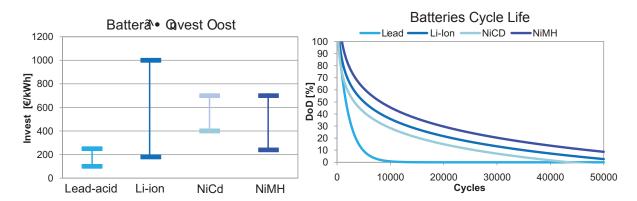

As an energy storage solution with timing for few seconds up to several hours, with capacities up to 100 MWh and fast response, batteries are a suitable and efficient solution [8, 9]. However, today's investment price in the battery system is high and is difficult to build storage systems that can be economically self sustained. In Fig. 1.5 the cost of Lead-acid, Li-ion, NiCd and NiMH battery technologies is shown [10]. Today's price is the high value on the given variation, and the expectancy of price drop being the low investment price [10, 11, 12, 13].

Figure 1.4.: Batteries investment cost

Figure 1.5.: Batteries lifetime as f(DOD)

The batteries lifetime dependency on depth of discharge (DOD) is shown in Fig. 1.5. Moreover, the calendrical lifetime must also be considered. This is around 5 years for

Lead-acid and NiCd, 10 years for NiMH and 15 years for Li-ion. Therefore, for the given operation scenario the planned cycling lifetime has to match the calendric life for the best system economical outcome.

Even if the energy storage in batteries is still an expensive solution nowadays, the outlook of the future vehicle-to-grid opens new perspectives for centralized storage systems such as enabling the reuse of electric cars batteries with reduced capacity before recycling. Thus, the development of centralized storage systems is needed for the future grids and will coexist with distributed energy storage systems.

The connection of storage systems can be done at different voltage levels, depending on the application scenario. For increased power and energy ratings, it is natural to increase also the connection point voltage and reduce battery and converter current ratings. It was shown that high efficiency can be achieved with increased nominal voltage of the battery system [14]. Medium voltage is an appropriate level where both transmission and distribution networks can take support from the storage system [15]. At this level, multilevel converters are employed as grid interface, making use of conventional and mature power electronic devices.

In the design of the power electronic converters for battery energy storage, it is critical that the charging and discharging procedures are implemented in such a way that it will enhance the battery lifetime. External stress factors are not desired, since already the battery system is the technology with the smallest lifetime and expensive.

#### 1.2. Objectives

The project this work is based on was financed by E.ON AG [16] under the E.ON Research Initiative under the call on Energy Storage with the project 2007/B4-HIGHLY EFFICIENT AND RELIABLE MODULAR BATTERY ENERGY STORAGE SYSTEMS (HERMES) in cooperation with RWTH Aachen University, Germany. The aim of the project was to design a modular battery energy storage system, taking into account the interaction between the electrochemical system and the power electronics. The project main objective was to identify the optimum battery building block for grid applications with large-scale potential having the rated power in the MW range and energy capacities from 1 second to 12 hours. To achieve this objective, a 6 kV battery energy storage test bench was to be realized to prove a potential large-scale battery concept.

The first objective of this work was to realize a custom grid connected DC-AC converter to be used in the HERMES test bench. The rated power is 100 kW and the control should be as active rectifier, to allow a connection with a current controlled DC-DC converter as battery charger/discharger.

To connect a 6 kV battery system to the power grid, a power electronic interface has to be designed. Therefore, another objective was to make a survey on suitable medium-voltage

multi-level converter topologies including soft-switching topologies for high efficiency. Converter topologies design and loss analysis was a following objective, to determine the amount of active and passive components required.

The knowledge of high voltage battery systems  $(V_n > 1 \ kV)$  is still limited nowadays. Their safety, efficiency, reliability and feasibility are not well known. Therefore, another objective of this work was to design power electronics that can allow a connection to the medium voltage grid using batteries with low voltage ratings which are at technological maturity to date.

#### 1.3. Methodology

In the realization of the DC-AC converter to be used in the HERMES test bench, the 110 kW Danfoss VLT FC 302 a low voltage two-level converter which is commercial product from Danfoss A/S [17] was modified and interfaced using the IPC2 interface and protection card developed at Aalborg University [18]. The control structures were simulated in MATLAB/Simulink [19], and the controllers were designed either via analytical calculations or using the Control System Toolbox from MATLAB.

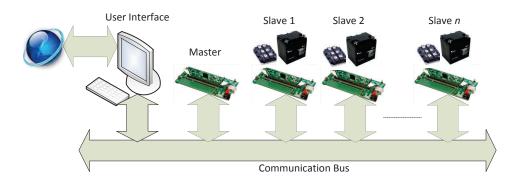

Control implementation for the HERMES grid converter was realized on a XCS 2000 AIX Control System, control platform comprising of a field programmable gate array (FPGA) and two digital signal processors (DSP) [20]. Additional interface printed circuits boards (PCB) were designed using Altium Designer [21]. Testing of the grid converter functionality has made use of a 30 kW, 1000 V power supply to emulate the batteries and DC-DC converter.

Control structures, multilevel converters switching models and power electronic devices loss models were implemented in MATLAB/Simulink using the PLECS blockset [22].

#### 1.4. Limitations

One of the limitation during the development of the low voltage DC-AC grid converter, was the DC power supply that was used to emulate the test bench batteries and DC-DC converter, which was limited in power up to around 22 kW for an output voltage of 750 V. Therefore initial tests were done only at light load. Another related limitation was the weak grid at the connection point during tests. The high impedance of the grid, and the light load operation, has created difficulties in the tuning of the harmonic compensation for the current control.

The definition of the optimal building block of the HERMES system was one of the main limitations of the project. Having undefined parameters of the battery systems has led to a more general approach considering the power electronics. The design of converter

topologies that can accommodate a large variety of battery technologies and for different battery voltage levels was necessary.

The laboratory implementation of the modular converters that were proposed during the project was not finalized. This was mainly because of the time frame of the project and also because of the chosen software implementation based on distributed processing units. Therefore, it was not possible to present experimental results for those converter topologies.

#### 1.5. Scientific Contributions

The main scientific contributions of this work, from the author's perspective, are outlined in the following:

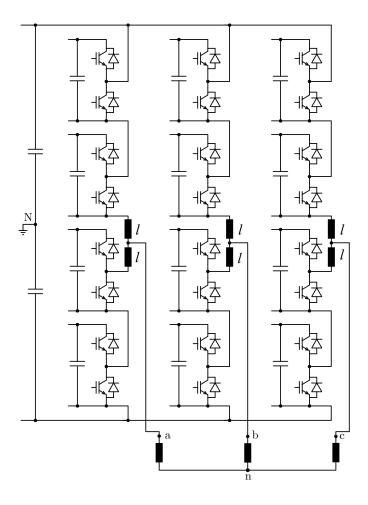

- A new modular multilevel converter with integrated energy storage.

- A two stage cascaded converter topology with construction based on half-bridge converter legs was introduced. This structure can interconnect a DC and AC grid with bidirectional power flow, where both can be backed-up with the distributed energy storage units installed in each converter cell. This converter topology has low dependency on the energy storage unit characteristic, and is suitable for medium and high voltage grids.

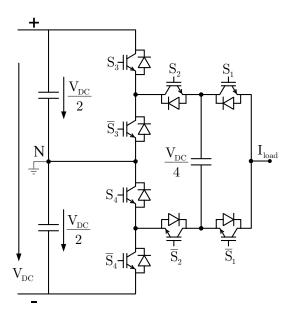

- Two-stage cascaded H-bridge converter for energy storage.

The connection of low voltage batteries to the 4.16 kV medium voltage AC grid was proposed to be realized with the cascaded H-bridge converter with bidirectional boost converters. This is also a modular concept, and the design and control was investigated. A novel control strategy was proposed to fit the requirements of this converter topology.

- Case study on single-stage medium voltage converters for storage.

The high efficiency can be achieved with a single stage conversion system. However, the converter operation is highly dependent on the energy storage characteristic, fact that is challenging in the converter design and control. An investigation has been done, for a design case scenario, where different converter topologies were compared.

- A survey on medium voltage multilevel converters.

This contribution can inspire further research on multilevel converters, for different applications that require highly efficient and reliable design. Hard-switched and soft-switched topologies were reviewed, identifying their advantages and disadvantages.

- A survey on control methods for grid connected converters.

A state-of-the-art in synchronization, current control and DC voltage control was

presented. This contribution can inspire further research on new and emerging control structures for grid converters.

#### 1.5.1. List of Publications

- Ionut Trintis, Stig Munk-Nielsen, Remus Teodorescu, "A new modular multilevel converter with integrated energy storage", 37th Annual Conference of the IEEE Industrial Electronics Society (IECON 2011), Melbourne, AU, 2011

- Ionut Trintis, Stig Munk-Nielsen, Remus Teodorescu, "Cascaded H-bridge with bidirectional boost converters for energy storage", 14th European Conference on Power Electronics and Applications (EPE 2011), Birmingham, UK, 2011

- Ionut Trintis, Stephan Thomas, Tobias Blank, Christoph Roggendorf, Stig Munk-Nielsen, Remus Teodorescu "Bidirectional converter interface for a battery energy storage test bench", 14th European Conference on Power Electronics and Applications (EPE 2011), Birmingham, UK, 2011

- Tobias Blank, Stephan Thomas, Christoph Roggendorf, Thomas Pollok, Ionut Trintis, Dirk Uwe Sauer, "Design and construction of a test bench to characterize efficiency and reliability of high voltage battery energy storage systems", *International Telecommunications Energy Conference (INTELEC 2010)*, 6-10 June, Orlando, US, 2010

- Ionut Trintis, Stig Munk-Nielsen, Remus Teodorescu, "Single stage grid converters for battery energy storage", 5th International Conference on Power Electronics, Machines and Drives (PEMD 2010), 19-21 April, Brighton, UK, 2010

- Christoph Roggendorf, Tobias Blank, Stephan Thomas, Ionut Trintis, "Design and Construction of a Test Bench to Characterize the Charging and Discharging Behaviour of Batteries in High Voltage Storage Systems", 4th International Renewable Energy Storage Conference (IRES 2009), 24-25 November, Berlin, DE, 2009

#### 1.6. Outline

The work is divided in two parts. The first part is on Control of DC-AC GRID Converters and contains two chapters (2 and 3). The second part is on Medium Voltage Grid Converters for Energy Storage and contains four chapters (4, 5, 6, 7). A summary, conclusions and future work is given in chapter 8. Two appendices are on Space Vector Transformations and Powers and Sequences Calculation.

CHAPTER 2 shows a review of the state-of-the-art control structures for grid converters. This includes phase-locked loop systems for single and three-phase, linear and nonlinear current control methods and DC voltage control.

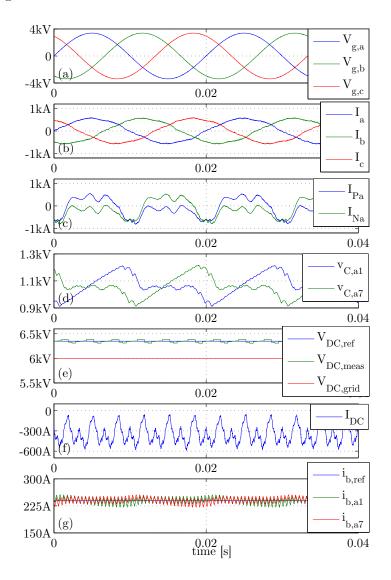

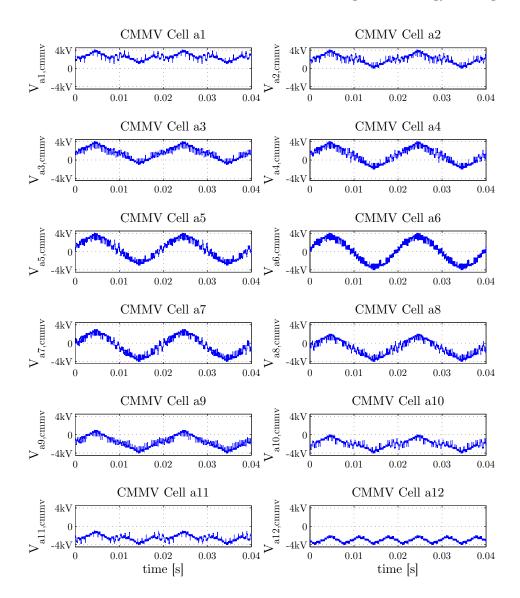

CHAPTER 3 shows the implementation of a low voltage two-level active rectifier to be used in a high voltage battery energy storage test bench. The interaction with the current controlled DC-DC converter is also simulated. Finally, the experimental results for the DC-AC grid converter and for the operation of the entire test bench are shown.

CHAPTER 4 presents the state-of-the-art on medium voltage multilevel converters. Hard-switched and soft-switched converter topologies are shown for the most promising configurations. Advantages and disadvantages are given for each converter topology and finally the component count is summarized.

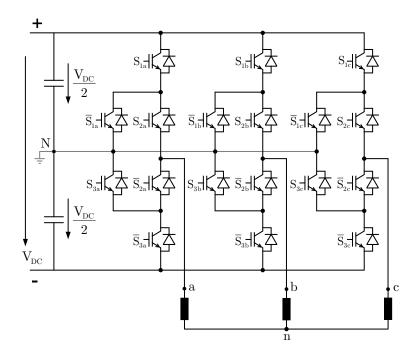

CHAPTER 5 analyses four multilevel converters to be used for direct connection of battery systems to the medium voltage AC grid. A comparison is realized over a 25% battery voltage variation considering the semiconductors requirements and losses, output voltages and harmonic distortion.

CHAPTER 6 presents the design and control of a two-stage cascaded H-bridge converter as interface for modular low voltage batteries to the medium voltage grid. The independent phase control for the DC voltages and AC currents is proposed and validated by simulation. In final, a loss analysis is performed over the entire battery voltage variation.

CHAPTER 7 introduces a new modular converter concept with integrated energy storage. Converter operation and control methods are presented, and the identified operation modes are simulated to validate the possible power flows. Finally, an implementation concept for a complete modular energy storage system is given together with some design considerations.

# Part I. Control of DC-AC Grid Converters

# Chapter 2.

# State-of-the-Art on Control for DC-AC Grid Converters

This chapter gives a brief description of the state of the art control methods for grid connection of DC-AC converters

#### 2.1. Introduction to Grid Control Structures

The control of DC-AC grid converters started its development almost a century ago, when the first power converters based on mercury arc devices were developed to interconnect two grids with different voltage and frequencies [23, 24]. From its early stage, it was possible to apply different control methods - constant power or variable power with respect to the grid frequency.

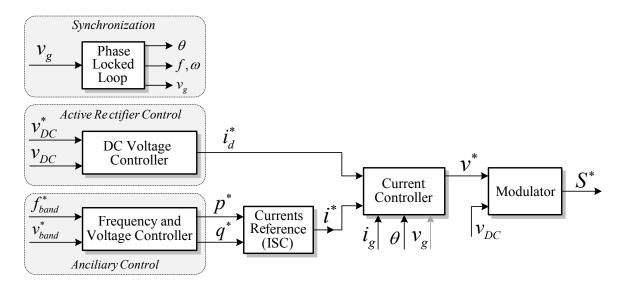

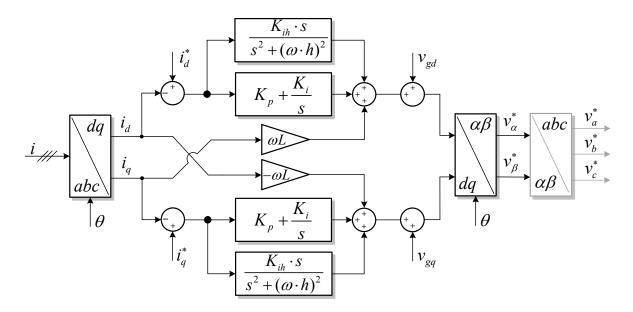

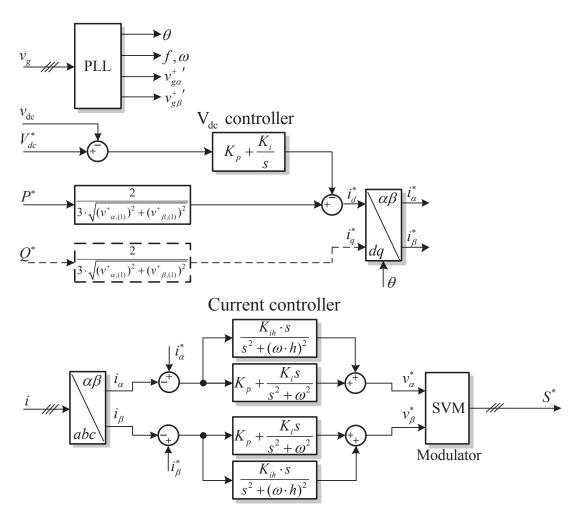

Nowadays with the development of power semiconductors devices, converter topologies and digital signal processors, the control structures enable the control of active and reactive powers and their sequence as well as the harmonic content of the transferred currents. Fig. 2.1 shows the block diagram of the grid control structure.

A synchronization method is used to detect the phase angle of the grid voltage, which can be used for coordinate transformations to and from the dq frame (Sec. 2.2). Frequency and voltage band controls are ancillarly services that the converter can provide, through the control of active and respectively the reactive currents, with limitations to its rated power. Whenever the converter is to be operated as active rectifier the DC-link voltage is controlled, reacting on the converter active current reference (Sec. 2.4). The current control is the core of the grid converter's control structure, its operation shaping the performance of the complete system [25, 4] (Sec. 2.3). This is the closed-loop with the highest bandwidth and it has to provide high dynamic response, reduce the output current harmonic distortion or it must control specific harmonic frequencies in case of active filtering [26]. Finally, the modulation strategy is the converter's topology dependent open-loop algorithm which converts the reference voltage into discrete steps to achieve the desired output voltage after filtering.

Figure 2.1.: General control structure of DC-AC grid converters

In the following, a review of the state of the art control structures is presented. The ancillary control strategies (f and v control) are not considered in this work, since it is a service dependent on the converter power ratings and dependent on the application. Modulation strategies are also not discussed in this chapter, these being dependent on the used converter topology and current controller. For linear current control methods however, a pulse width modulation (PWM) strategy is considered to generate the duty cycles based on the input voltage references.

#### 2.2. Synchronization Methods

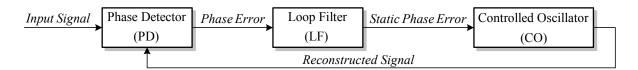

The grid converter's synchronization with the grid voltage is one of the key methods that are mandatory to be used. It is critical to detect the correct phase angle of the grid voltage, to allow a safe and smooth connection and to be able to inject/draw the desired currents. Phase-Locked-Loops (PLL) are the most popular methods used nowadays, introduced in 1923 [27] with the first patent from 1932 [28]. In Fig. 2.2 the general PLL structure is shown, consisting of a Phase Detector (PD), Loop Filter (LF) and a Controlled Oscillator (CO).

Figure 2.2.: Phase-Locked-Loop General Structure

The role of the PD is to generate the phase error between the actual input signal and the internal reconstructed signal. The phase error is then filtered by the LF, output used to reconstruct the signal with the CO. First implementations were realized with analog circuits, the PD being implemented with a multiplier, the LF with a RC low-pass filter and the CO with a variable capacitor to control its resonant frequency based on the input bias voltage. Nowadays, the PLL as well as the control implementation is discretized and implemented in digital signal processors (DSP), where the LF is a PI controller and the CO is an integrator usually with a feed-forward term in the input.

Depending on the input signal(s), adaptation of the PD module results in a classification of the PLL methods in three-phase (see Sec. 2.2.1) and single-phase (see Sec. 2.2.2) PLL's. With the development of methods for generating the virtual  $\beta$  component from a phase voltage [29], basically the single-phase PLL becomes a particular case of the three-phase PLL. This is used in single-phase systems or in particular three-phase systems with independent phase voltage synchronization and control, see application in Sec. 6.3.

#### 2.2.1. Three-phase methods

Three-phase synchronization methods can be classified in open-loop and closed-loop. One of the simplest synchronization technique is to transform the input three-phase voltages in  $\alpha\beta$  or dq frames (see A1), filter out the harmonics and calculate the angle from the  $\alpha\beta$  frame using the inverse tangent function [30]. However, the operation during voltage frequency deviations requires adaptation of the resonant filters and the behaviour during unbalanced input voltages is poor. Another proposed structure is based on Kalman filtering algorithms [31], structure which provides good accuracy under distorted and unbalanced input signals. The disadvantage is the high required processing power as well as selecting the optimal covariance matrices [32].

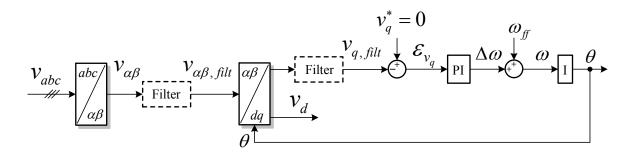

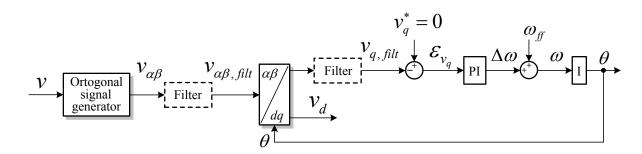

Figure 2.3.: Three-phase PLL general structure

The widely accepted and used synchronization method for three-phase systems is presented as a general structure in Fig. 2.3, the dq-PLL also known as the synchronous reference frame PLL (SRF-PLL). The three-phase quantities are transformed in the dq frame using the estimated phase angle, and the phase angle error is reflected in the alignment

on the q axis of the voltage vector. This phase angle error is regulated by the PI controller to zero, and the PI tuning (usually done with the *symmetrical optimum* [33]) defines the PLL dynamic performance.

The basic structure implemented without the filtering blocks, works well on balanced and light distorted grid voltages. However, in a case of a grid fault or transients of high power electronics, the grid voltages may be highly distorted and unbalanced and the SRF-PLL cannot detect the correct grid voltage phase angle.

To mitigate the distortion, filtering either on the  $\alpha\beta$  frame or on the dq frame can be implemented. Basically with the decrease of the bandwidth of the PI controller, a natural low-pass filtering can be achieved with the disadvantage of overall PLL slower dynamics.

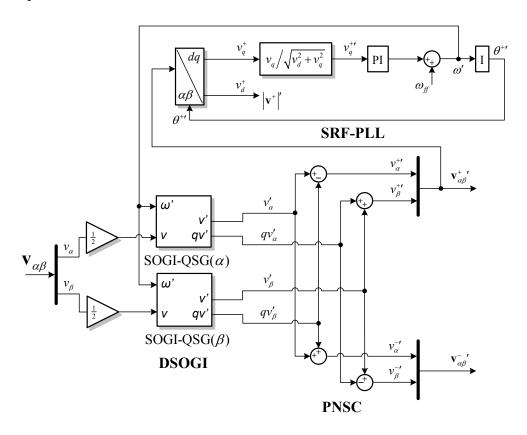

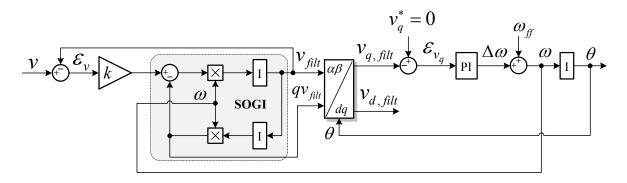

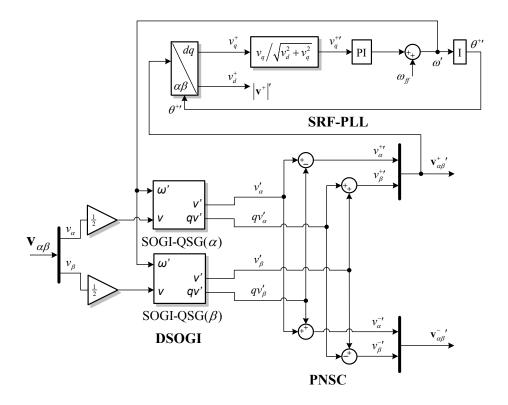

The grid voltages filtering on the  $\alpha\beta$  frame based on the Second Order Generalized Integrator (SOGI) is a solution with theoretical no delay. The Double SOGI PLL (DSOGI-PLL) structure was introduced in [34], presented in Fig. 2.4. For grid control structures where only the control of positive sequence currents is desired, distortion immunity is required, the DSOGI-PLL represents a reliable synchronization solution at a relatively small computation cost.

Figure 2.4.: Double SOGI Phase-Locked-Loop algorithm [34]

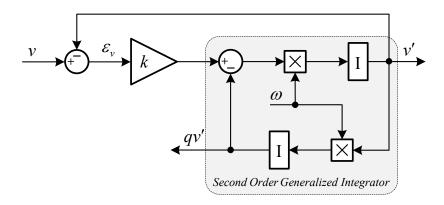

The core of the filtering algorithm on the  $\alpha\beta$  components of the grid voltage is the SOGI Quadrature Signal Generator (SOGI-QSG) [35], see Fig. 2.5. At a given input signal, this block has a theoretical infinite gain at the given angular frequency  $\omega$ . Therefore it is possible to extract from the input signal only the desired frequency components, like the fundamental component of the grid voltage. Moreover, the output of the second integrator is the filtered output signal with a 90° phase shift delay called in quadrature signal [36] or orthogonal signal [35]. Therefore, the output of the SOGI gives the filtered input signal which can be aligned on the  $\alpha$  axis on the stationary frame ( $\alpha\beta$ ) and the quadrature signal can be aligned on a virtual  $\beta$  axis. Having this, the grid voltage  $\alpha\beta$  components can be decoupled in positive and negative sequence by the Positive Negative Sequence Calculator (PNSC) shown in Fig. 2.4.

Figure 2.5.: Quadrature Signal Generator based on SOGI (SOGI-QSG) [35]

To be able to extract the correct grid voltage angle under unbalanced condition the decomposition of the positive and negative sequences of the grid voltage is required. This is achieved using the instantaneous symmetrical components (ISC) method [37]. Based on the ISC decomposition of the grid voltage it is possible to synchronize only with the positive sequence of the grid voltages, and the Decoupled Double Synchronous Reference Frame PLL (DDSRF-PLL) was introduced [38, 4]. Having also the magnitudes of the positive and negative sequences of the grid voltage, given by this structure, it is possible to inject/draw also unbalanced currents to reduce the power system oscillations [4]. However, the structure presented in [38] is not feasible under a highly distorted grid.

New synchronization methods were introduced recently, the locked-loop being realized on the grid frequency rather than on the grid phase angle, such as: Adaptive Notch Filter (ANF) [39], DSOGI Frequency Locked Loop (DSOGI-FLL) [40, 36]. This synchronization methods are claimed to present increased robustness [36], and may bring benefits in control structures based on  $\alpha\beta$  frame [4].

#### 2.2.2. Single-phase methods

First developed synchronization methods were designed for independent sinusoidal signals [27], used also nowadays with basically the same structural building blocks. Research and development has led to improvements in the synchronization performance, optimizing the performance for the specific application. Several methods are available to be used, in open-loop or closed loop. Synchronization in open-loop is usually based on filters, from which we can distinguish the following methods: discrete Fourier transform (DFT) [31], weighted-least-square-estimation (WLSE) [41], adaptive notch filter (ANF) [42], Kalman filtering [31] and artificial neural networks (ANN) [43]. Closed-loop synchronization methods are based on PLL from which various methods were proposed with particular PD implementations: Enhanced PLL (EPLL) [44], Adaptive PLL [45] and in quadrature signal generation (QSG) based PLL's. The QSG-PLL is in fact a particular implementation of the SRF-PLL adapted for single-phase systems, with the general structure shown in Fig. 2.6.

Figure 2.6.: Single-phase SRF-PLL general structure

Figure 2.7.: Single-phase SRF-PLL based on SOGI-QSG

Different solutions can be adopted for the quadrature signal generation on the voltage to be synchronized with, such as: T/4 Transport Delay, Hilbert Transform, Inverse Park Transform, Generalized Integrator (GI), Second Order Generalized Integrator [4], D-filters based [46] and Kalman filter based [47]. The first three methods do not ensure filtering and therefore in Fig. 2.6 a filter needs to be employed either on  $\alpha\beta$  or dq frames.

The Kalman filter-based method requires variable sampling time to correct the errors due to frequency deviations, fact that may not be allowed by the digital implementation platform. The GI, SOGI and D-filter based methods however, apart from generating the in quadrature signal provides also filtering at the tuned frequency and are frequency adaptive. Therefore, implementing one of these structures the optional blocks from Fig. 2.6 can be disregarded. Fig. 2.7 shows the structure of the single-phase SRF-PLL based on SOGI-QSG, structure which is applied in Sec. 6.3.

#### 2.3. Current Control Methods

The grid converter's current control method is the core of the control structure, its performance being critical for the dynamic response, operation during grid faults and output current distortion to comply with the grid connection requirements [4]. The basic function is to control the current in the output filter (L or LCL) to the desired reference, by modulating the available DC-link voltage. Many current control concepts were proposed over the time, linear and non-linear, with advantages and disadvantages which are selected and applied for different applications. Linear controllers are based on PWM modulation using proportional resonant (PR) controllers or deadbeat controllers in the natural abc frame or the stationary  $\alpha\beta$  frame, or PI controllers in the dq rotating frame. Non-linear controllers are based on PWM such as passivity based control (PBC), or on ON-OFF control such as hysteresis and predictive control with minimization criteria.

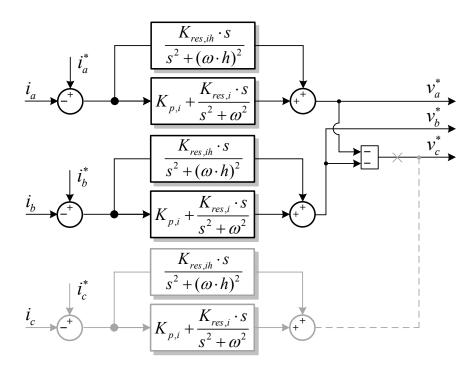

#### 2.3.1. Natural frame

The current control in the natural abc frame requires controllers that can compensate effectively the error of sinusoidal signals, and adapt with the frequency change [48, 49, 50, 51]. The structure using PR controllers to regulate the error on the fundamental frequency, introduced in [48], is shown in Fig. 2.8. To eliminate the harmonic content of low order harmonics, resonant integrators are tuned at the required frequencies [50].

Two controllers are normally required in a three-phase system, when regulation of the currents is done symmetrically. Whenever it is desired to control the currents independently, a third controller can be employed [52]. It was shown that it is possible to control the active and reactive power without the use of any transformation from the dq frame, using the structure from Fig. 2.8 in combination with the single phase PLL structure from Fig. 2.7. However, the plant of the three-phase load/source is not decoupled in single phase systems and therefore the control of the three phases must be done coordinated with respect to phase shifts and injected/drawn currents sequence [4].

Current control implementation using PI controllers in abc frame was one of the first used methods [53]. Because of the steady state error, implementations were done in dq frame. However, it was shown that the PI current controller can be used in the

Figure 2.8.: Natural frame abc current control with PR controllers

abc frame with very good transient and steady state performance, if it is enhanced with PWM transport delay compensation [54]. The steady state error is not removed, but the reference tracking is accurate and with improved transient response.

Another type of controller which can be used in the abc frame is the deadbeat (DB) controller. It is a linear predictive controller introduced in 1973 [55] and firstly used in power electronics in 1985 [56], also called  $One\ Sample\ Ahead\ Controller$ . It predicts the current error on the next sample based on current and previous measurement, and generates the duty cycle to eliminate the error at the end of the next switching period. The prediction however, is based on the plant model and therefore is highly sensitive to parameters change. To overcome this drawback, the artificial decrease of the controller constant term in its transfer function leads to an increased damping [57] and therefore allowing the operation over a wide parameter change in the plant (L or LCL filter).

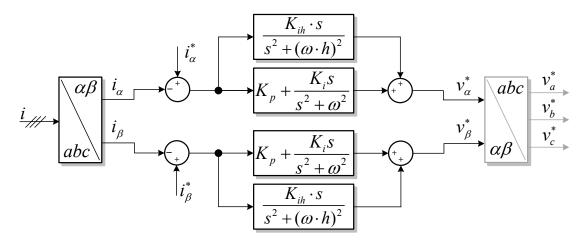

#### 2.3.2. Stationary frame

Transforming the feedback currents from the natural abc frame to the stationary  $\alpha\beta$  frame, using the Clarke transformation (see A1 $\rightarrow$ Eq. 1), regulation of the three-phase currents can be done using two sets of controllers. Compared with the natural abc frame, the same computation burden is required when indirect control of the third phase is done. It must be noted that in the  $\alpha\beta$  frame the controllers of the two in quadrature  $\alpha$  and  $\beta$ , have both a direct influence on all three phases. The control structure using PR

controllers for fundamental and harmonics compensation is shown in Fig. 2.9. The zero sequence component is not considered, because normally there are no zero sequence produced currents in the three-phase system with isolated neutral [58].

Figure 2.9.: Stationary frame  $\alpha\beta$  current control

Under unbalanced grid condition, the control of the positive and negative sequence currents with this structure can be achieved [50], only by having the two sets of controllers from Fig. 2.9. Generation of current references has a major influence on the current control performance [59]. Whenever the current references are given in d and q components and transformed in  $\alpha\beta$  frame, rotated with the PLL angle of the positive sequence, only the positive sequence error is compensated.

#### 2.3.3. Rotating frame

One of the most used control techniques in control of electrical machines and grid connected converters is the rotating dq frame control, also called voltage oriented control. The use of PI controllers to control three-phase AC currents cancelling the error of two in quadrature DC currents (dq) is made possible by using the Park transformation (see A1 $\rightarrow$ Eq. 3). The steady state error is brought to zero [60] since the classical integrator has infinite gain at zero frequency, and the performance is similar to a resonant control in stationary frame [49]. The particularity of the dq frame control is that due to the rotation with the angular frequency  $\omega$ , the resulting d and q components are coupled in the converter model [61]. Therefore a decoupling network is necessary to be implemented, see Fig. 2.10, to decouple the two PI controllers actions on the two axis. However, the decoupling is not ideal since the plant inductance is not known precisely.

Feedforward of the dq components of the grid voltages is required to minimize the effort in the PI controllers, as shown in Fig. 2.10. When the grid voltages are distorted, filtering is necessary to deliver a clean reference for the PWM modulator.

Figure 2.10.: dq current control

Regarding harmonic compensation in dq frame, it can be implemented using resonant integrators tuned between two compensating frequencies  $(h + \omega \text{ and } h - \omega)$  [62, 63, 64] (eg.  $6^{th}$ ,  $12^{th}$ ,  $18^{th}$ ). This is valid in the case of compensating the harmonics generated by diode rectifiers, having for instance in stationary frame negative sequence  $5^{th}$  harmonic and positive sequence  $7^{th}$  harmonic which rotated with  $\omega$  in dq frame results in negative and positive  $6^{th}$  harmonic. This results in a reduced number of used resonant integrators for harmonic compensation.

The compensation for the fundamental frequency is done only for the sequence that is used to rotate the *abc* components, which usually is the positive sequence. For control of the negative sequence currents, if necessary in case of faults, another set of controllers is required with two more transformations. Moreover, the second harmonic filtering is necessary due to the power oscillations given in this case (see  $A2 \rightarrow Eq. 10,11$ ).

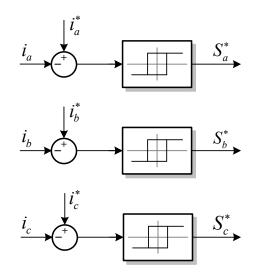

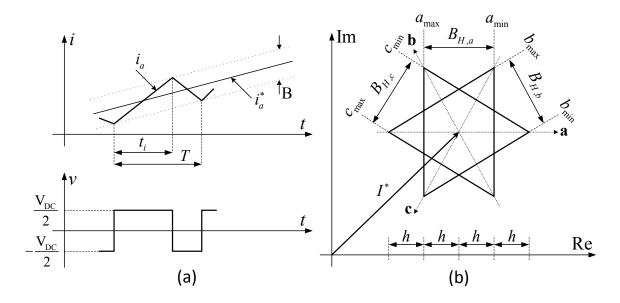

#### 2.3.4. Hysteresis

Hysteresis control is a type of nonlinear control based on ON-OFF controllers for each phase, structure shown in Fig. 2.11. Each controller reacts to the measured current, and keeps the error in the hysteresis band as shown in Fig. 2.12 [65]. Thus, the maximum phase current error is equal to half the hysteresis band h, the maximum line current error is 2h and maximum current vector error is 4h [53].

The operation of hysteresis current control is inferior to PWM based control at low modulation index due to the required high switching frequency. However, grid connected converters operate at high modulation indices all the time. The advantages in the basic

Figure 2.11.: Hysteresis current control

Figure 2.12.: (a) Phase a current regulation; (b) Hysteresis bands for phases abc

implementation are: high dynamic performance, control and implementation simplicity, and independence of the load parameters give robustness. One of the disadvantage is the stringent requirements on the current sensing, which directly influences the controller performance. The current measurement must be noisefree, and if the control is implemented in a processor the sampling frequency and resolution of the analog to digital converter must be high.

The main concern of the hysteresis control technique is the variable switching frequency. The operating switching frequency is also influenced by the coupling between phases,

where the error of the three-phase current vector is high (see Fig. 2.12.(b)). Operating the converter at variable switching is not desired, especially for high power, because of the spread harmonic spectrum. Therefore, work has been done to reduce the interaction between phases by using adaptive hysteresis bands in order to achieve constant switching frequency [66, 67]. This however increases the control complexity, but the dynamic response and robustness is not affected.

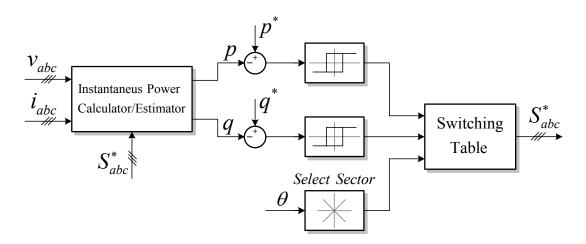

#### 2.3.5. Direct power control

The principle of controlling indirectly the grid currents by controlling the instantaneous active and reactive powers was introduced in 1991 [68], with the basic control structure shown in Fig. 2.13. Two hysteresis controllers are used to control the active and reactive power, and the switching table selects the appropriate voltage vector with the sector given by the grid voltage angle. Advantages like no coordinate transformation, no required decoupling in the control of active and reactive powers, and the fast response makes this control strategy very attractive.

Figure 2.13.: Direct power control structure

Based on the same principle, control structures were introduced to implement the control with reduced number of sensors, by using estimators [69, 70]. Measuring only the converter's output currents, the direct power control (DPC) can be implemented by estimating the grid voltages and the instantaneous output/input powers [69]. Looking at the power grid as to a virtual generator, another DPC method was developed based on the estimation of the virtual flux, this being used to calculate the instantaneous powers [70]. However, the disadvantages of the hysteresis controller such as requirement of high sampling frequency and variable switching frequency and are still present. To compensate for this drawbacks, the direct power control using space vector modulation (DPC-SVM) was introduced in [71], shown in Fig. 2.14.

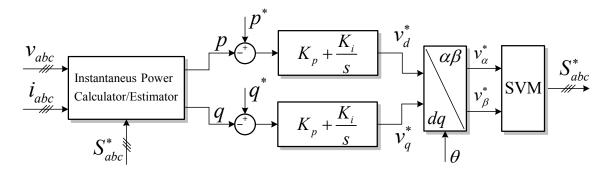

Figure 2.14.: Direct power control based on SVM

In the DPC-SVM, the active and reactive powers are regulated using PI controllers which give the voltage references in the dq frame. Therefore, an additional dq to  $\alpha\beta$  transformation is necessary and the control has to rely on a correct estimation of the grid phase angle.

#### 2.3.6 Predictive

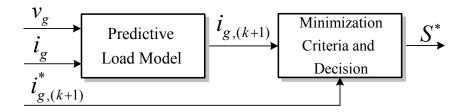

The predictive control theory was started in 1960's by Kalman [72], and the first patent on a predictive control system for aircraft positioning system was published in 1965 [73]. The application to AC machines control was introduced by Holtz in 1983 [74], minimizing the spatial current vector error in the complex plane. The basic structure of the predictive current control is shown in Fig. 2.15.

Figure 2.15.: Basic structure of the predictive current control

Based on the load model, the actual and previous measurements, the value of the next sample of the grid current is estimated. Based on the given prediction  $(i_{g,(k+1)})$  and the reference current for the next sample  $(i_{g,(k+1)}^*)$  a switching vector will be selected which must minimize the current error. Next, the selection of the switching vector can be done depending on the predefined minimization criteria which can minimize the switching frequency, minimize the response time or reduce the current distortion.

Based on the described control principle, a new concept for decision on which switching vector sequence will be applied at the next state was introduced in [75]. This method

defines a weighting function which incorporates the minimization criteria. Calculating the weighting function for all the possible vectors that can be applied, the vector with the smallest weighting function is chosen.

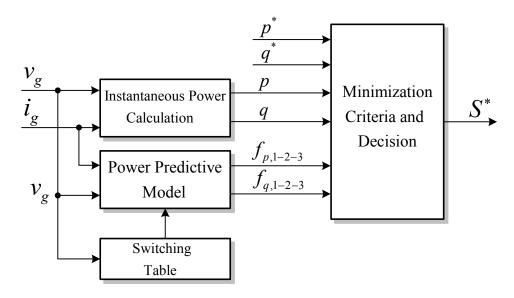

The combination of the DPC structure with the predictive selection of the switching vectors sequence was introduced in [76], control structure shown in Fig. 2.16.

Figure 2.16.: Predictive Direct Power Control

Using the instantaneous power theory the active and reactive powers are calculated. Based on the load model, the active and reactive power slopes  $(f_{p,1-2-3}, f_{q,1-2-3})$  are estimated for the given switching sequences from the switching table. Having the power slopes and the measured powers at the current sampling, the active and reactive power in for the next sample can be predicted. Therefore, having also the active and reactive power references, based on the imposed minimization criteria the next switching sequence and application time can be computed. One of the selection criteria can be the achievement of constant switching frequency [76].

# 2.3.7. Passivity based control

Passivity based control (PBC) introduced in 1988 by Ortega [77] is a nonliniar control approach, which uses the energy to describe the state of the system. The system passivity is given by describing the energy flow to/from the ambience, and it was successfully applied in many applications [78, 79, 80, 81, 82]. An energy-based controller shapes the energy of the system in such a way to reach the desired state. The control is achieved by an energy reshaping, injecting damping to modify the dissipation of the system.

The first formulation was based on the Euler-Lagrange equations for energy shaping, mainly suitable for the control of electrical machines [78]. However, for electrical systems,

other formulations were described in the literature: Port-Hamiltonian [83] or Mixed-Potential [84].

#### Port-Controlled Hamiltonian Systems with Dissipation

The port-controlled Hamiltonian system with dissipation is described by the Eq. 2.1 [85]:

$$\frac{dx}{dt} = [J(x) - R(x)] \cdot \frac{\partial H(x)}{\partial x} + g(x) \cdot u$$

$$y = g^{T}(x) \cdot \frac{\partial H(x)}{\partial x} \tag{2.1}$$

Here, x is a vector of n dimension, H(x) is the function that represents the total stored energy, J(x) and g(x) are the interconnection matrices, and R(x) is the matrix that represents the dissipation. The interconnection matrices must respect the conditions from Eq. 2.2:

$$J(x) = -J^{T}(x)$$

$$R(x) = R^{T}(x) \ge 0$$

(2.2)

The energy-balance then is given by Eq. 2.3:

$$\frac{dH(x(t))}{dt} = u^{T}(t) \cdot y(t) - \frac{\partial^{T} H(x(t))}{\partial x} \cdot R(x(t)) \cdot \frac{\partial H(x(t))}{\partial x} \le u^{T}(t) \cdot y(t) \tag{2.3}$$

Based on the above formulation, two control concepts were defined: Control by Interconnection, and Passivity-Based Control of port-controlled Hamiltonian systems with dissipation [85, 81].

In the Control by Interconnection, a desired port-controlled Hamiltonian system with dissipation is imposed in the closed loop, with the matching equation given by Eq. 2.4:

$$[J(x) - R(x)] \cdot \frac{\partial H(x)}{\partial x} + g(x) \cdot u_C(x) = [J_C(x) - R_C(x)] \cdot \frac{\partial H_C(x)}{\partial x}$$

(2.4)

Here, the imposed port-controlled Hamiltonian system with dissipation  $(J_C, R_C, H_C$  - "controller") must match the plant and the control function is  $u_C(x)$  [85, 82]. The controller is given by the state feedback interconnection from Eq. 2.5, where e,  $e_C$  are external signals inserted in the feedback.

$$u = -y_C + e$$

$$u_C = y + e_C$$

(2.5)

The Passivity-Based Control of port-controlled Hamiltonian systems is basically a particular case of the Control by Interconnection, where the passivity-based control low is

taken from the state feedback  $u = \alpha(x)$ :

$$g(x) \cdot \alpha(x) = [J(x) - R(x)] \frac{\partial H_C(G(x) + c)}{\partial x}$$

(2.6)

Here the state feedback  $u = \alpha(x)$  can be derived from the interconnection of the two systems considered in Eq. 2.4.

#### Mixed-Potential Function

The Mixed-Potential formulation is based on the following defined function [84]:

$$P(i_L, v_C) = \underbrace{[P_R(i_L) + P_E(i_L)]}_{Current\ Potential} - \underbrace{[P_G(v_C) + P_J(v_C)]}_{V\ oltage\ Potential} + \underbrace{[P_T(i_L, v_C)]}_{Circulating\ Power}$$

(2.7)

Here, the first term is defined as a current potential which is related with the current-controlled resistors and voltage sources, the second therm is a voltage potential which is related with voltage-controlled resistors and current sources and the last therm is related to the internal circulating power across the dynamic elements (see Eq. 2.8).

$$P_R(i_L) = \int_0^{i_L} v_R(i'_L) \cdot di'_L$$

$$P_G(v_C) = \int_0^{v_C} i_G(v'_C) \cdot dv'_C$$

$$P_T(i_L, v_C) = i_L^T \cdot \psi \cdot v_C$$

$$(2.8)$$

Here,  $\psi$  is the interconnection matrix which is determined by Kirchhoff's voltage and current laws.

Based on the Mixed-Potential formulation, the current and DC voltages controls of the cascaded H-bridge converter was developed in [79, 80].

# 2.4. DC Voltage Control

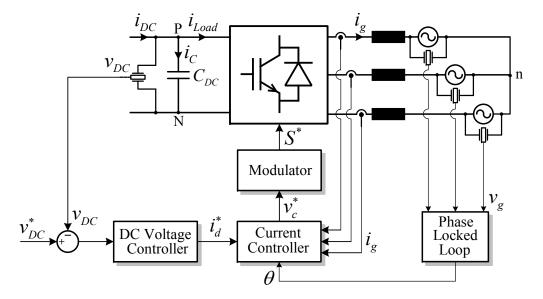

The grid converter's DC voltage control is activated whenever the supplied/drawn power on the DC side is current controlled. This functionality is also called ACTIVE RECTIFIER OPERATION, and is very common for wind turbines, photovoltaic systems, fuel cells and battery energy storage systems [5]. The general control schematic is shown in Fig. 2.17.

Figure 2.17.: Active rectifier general control structure

The DC-link dynamics is described in Eq. 2.9:

$$C_{DC}\frac{dv_{DC}}{dt} = i_{DC} - i_{Load} - i_{C}$$

(2.9)

Here,  $i_{DC}$  is the current supplied/drawn to/from the DC-link capacitor,  $i_{Load}$  is the current supplied/drawn to/from the AC grid and  $i_C$  is the current supplied/drawn to/from the DC-link capacitor. Thus, the higher the installed capacitance the higher the difference between the supplied and drawn current can be, for a given voltage variation. In complementary, when the load current matches very accurately the supplied current, the installed DC-link capacitance can be reduced to a minimum.

The tuning of the DC control loop is strictly dependent on the installed capacitance. A general approach to chose the minimum DC-link capacitor value, is given in Eq. 2.10 [86]:

$$C_{\min} = \frac{\Delta Q_{C,\max}}{\Delta V_{DC,\max}} = \frac{\max\left(\int (i_C - i_{C,avg})dt\right)}{\Delta V_{DC,\max}}$$

(2.10)

Here,  $\Delta Q_{C,\text{max}}$  is the maximum capacitor charge variation, which is given by the capacitor current ripple apart from the current drawn by the capacitor itself.

The DC voltage controller from Fig. 2.17 is normally implemented with a PI controller, which is designed using the *symmetrical optimum* principle [87, 4]. The bandwidth of this PI controller must be lower compared with the current controller bandwidth, to ensure decoupling between the two control loops. This leads to slower dynamics in the DC voltage regulation. To improve the DC-link dynamics, feed-forward on the current reference should be used. This can either be implemented by having a measurement of the load current or designing an observer [88].

An important issue in the DC control loop is the situation when there is a second harmonic voltage ripple due an unbalance in the grid voltage, or when using converter topologies based on H-bridge (see Ch. 6). The usage of an additional resonant controller tuned at the  $2^{nd}$  harmonic frequency was proposed to be used in this situation [89]. However, this solution leads to a distortion of the grid current with a  $3^{rd}$  harmonic. When this situation is not desired, just the feedback filtering of the DC-link voltage should be implemented either by averaging on the  $2^{nd}$  harmonic period or using a notch filter.

# 2.5. Summary

A brief description of the main control principles used for grid converters was given in this chapter, such as: phase-locked-loop (PLL) methods, linear and some non-linear current control methods and DC-link voltage control.

A review of the PLL methods was given, with implementations for three-phase and single-phase. This is a very important building block in the grid converter control development. Three-phase PLL methods are widely used in three-phase converter due to a simplified implementation and reduced computational burden. Single-phase PLL methods can be used in special cases for three-phase converters when the processing power is available and if the topology requires the independent phase control.

Intensive research on current control strategies over the past years led to the introduction of many different concepts. Linear controllers are widely used in the industry, where the dq frame control is the most spread at the moment. It is disadvantageous that the d and q components need to be decoupled, and this is not ideal. Moreover, the behaviour during unbalanced grid voltage is in question, due to the second harmonic oscillation on the normally DC signals on the d and q axes. Stationary  $\alpha\beta$  and natural abc frame controller making use of proportional resonant regulators are an alternative, to overcome this unpleasant situation. In the  $\alpha\beta$  control, the axes are naturally decoupled, and both the positive and negative sequences are controlled at the same time with the same controllers. However, the generation of reference signals is very important, and must be carefully implemented. Hysteresis and direct power control techniques are interesting alternatives, which are very robust and with excellent dynamic performance. However, implementations with constant switching frequency and well defined current spectrum must be considered. Predictive control is an emerging technique, where the minimizing criteria can bring important benefits for different applications. However, its dependency on the load parameters and high computational burden are the main disadvantages. Passivity based control is a nonlinear control concept, that uses the energy to describe the state of the system. It was shown that using control structures based on this concept gives robustness against load parameter variation and enhances the overall operation stability.

When operating the grid converter in active rectifier mode, which is in most of the cases, the second harmonic ripple on the DC-link must be taken into consideration when designing the control loop. Moreover, with the trend to reduce the installed capacity and therefore reduce the decoupling between the supply and load, the proper DC voltage control must be ensured.

# Chapter 3.

# Active Rectifier Implementation for a HV Energy Storage Test Bench

This chapter presents the design, control and experimental results of a LV two-level active rectifier, grid connected through an LCL filter, implemented for a HV battery energy storage test bench

# 3.1. Introduction to the Energy Storage Test Bench

The increase of power generation based on volatile sources as wind and solar requires special considerations for power management in electrical networks. The power management can be done using conventional power plants or energy storage systems. Conventional power plants are more efficient having a stationary or predictive load situation. Energy storage is the key technology to integrate renewable energy sources on large scale into the present power systems, without compromising its stability. Storage systems can partially compensate the fluctuations of the volatile power sources. Battery energy storage systems offer scalable solutions for high power and high energy demands of up to 100 MW and 100 MWh [90, 91]. When the installed power goes up to the highest levels, series connected batteries will be necessary to reduce the current levels and thus the overall system losses. The charging and discharging characteristics of series connected batteries up to several kV is unknown. To test the operating behaviour of 360 series connected 12 V lead-acid battery blocks, a test bench with 100 kW and 120 kWh was realized [92].

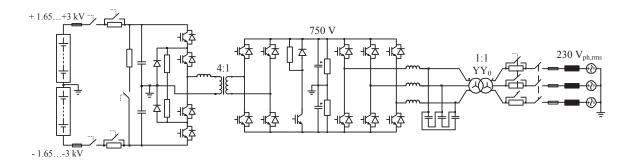

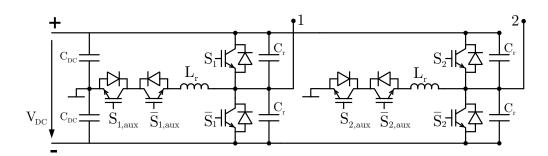

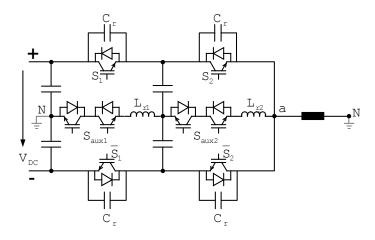

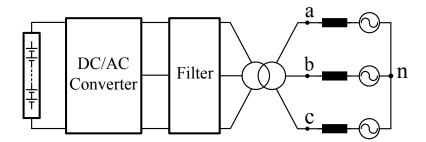

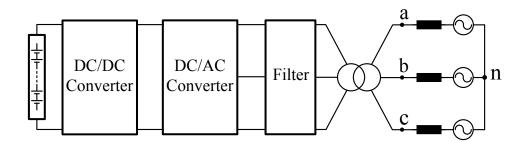

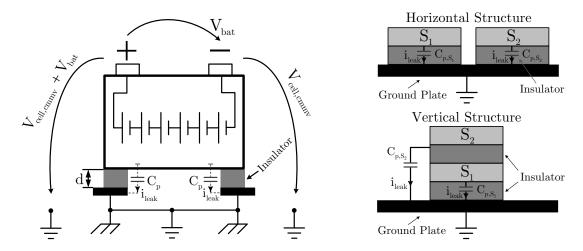

The test bench power electronic interface has a two stage conversion, consisting of a galvanic insulated 3-level/2-level dual-active bridge DC-DC converter and a 2-level DC-AC converter, for the 50 Hz, 400  $V_{LL}$  grid connection, see Fig. 3.1. The DC-DC converter has a maximum transformation ratio of 8 and acts as a charging/discharging unit, controlling the batteries' current. The power rating transfer is between 5 kW and 100 kW.

To fix the DC-DC converter's transformer potential on the high voltage side, the 3-level's neutral point and the battery stack midpoint are connected and grounded. On the low

Figure 3.1.: Test bench power electronic interface

voltage side, the DC-link midpoint is grounded. This will indirectly fix the potentials of both transformers. This is also the path for the inherent common mode currents of both low voltage converters.

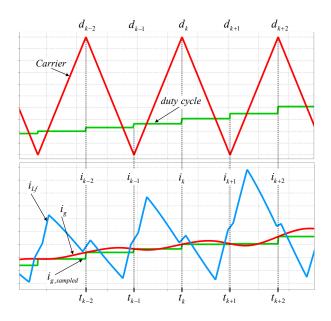

The installed DC-link capacitance between the DC-DC converter and the inverter is a trade-off between the capacitors price and maximum allowable voltage ripple. The DC-DC converter is switched with 1 kHz, producing a current ripple which is absorbed by the common low voltage DC-link. The DC-AC converter is switched with 3.15 kHz and controls the grid current with a power factor of  $\pm 1$ , with a DC voltage control as outer loop. Therefore, the dimensioning must take into account the achievable DC control bandwidth to keep the ripple at a level where the current loop is not affected.

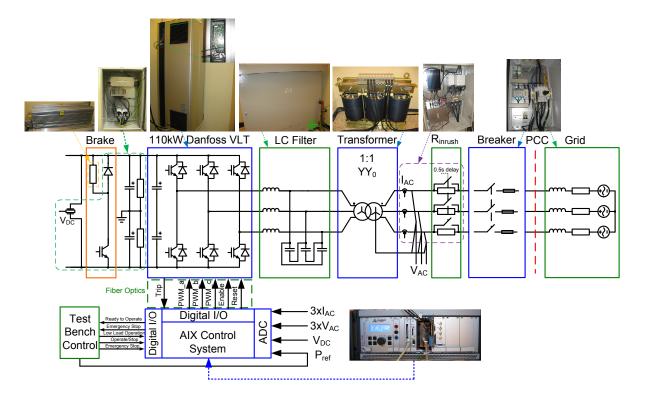

#### 3.2. Hardware breadboard of the DC-AC converter

The grid side converter uses the classical 2-level hard-switched topology with a LC filter having delta connected capacitors and a low frequency transformer for insulation, see Fig. 3.2. The transformer acts also as filter inductor on the grid side, considering its leakage inductance. The  $Yy_0$  winding connections allow the propagation of asymmetrical grid faults in all three phases in the transformer winding on the converter side [93]. This is an important advantage for the current control loop stability.

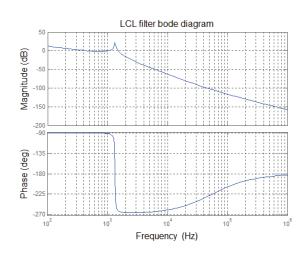

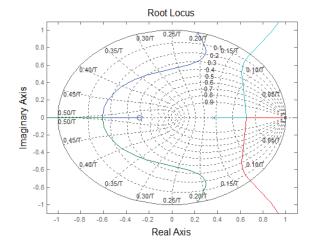

Inrush current limiting resistors are installed to reduce the DC-link capacitors charging current, the free-willing diodes current and the transformer magnetizing current. The grid converter's rated power is 110 kVA. Thus, it theoretically can provide or consume reactive power on demand while charging/discharging the batteries at rated current (145  $A_{rms}$ ). The chosen filter inductance is  $L_f = 0.2 \, \text{mH}$  at rated power and filter capacitor of  $C_f = 47 \, \mu \text{F}$ , resulting in an attenuation of around 30 dB at the switching frequency of 3.15 kHz. The filter capacitors' and inductors' parasitic resistances are in the range of m $\Omega$  and thus a small natural filter damping is achieved.

Measurement of the grid current for the inner control loop is done on the grid side of the equivalent LCL filter, using hall sensors for each phase to avoid the cumulative error when

Figure 3.2.: Grid converter test setup

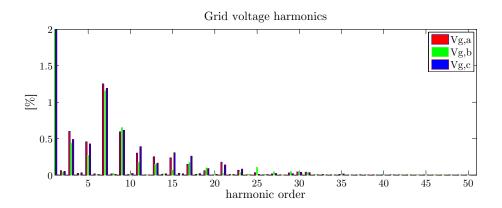

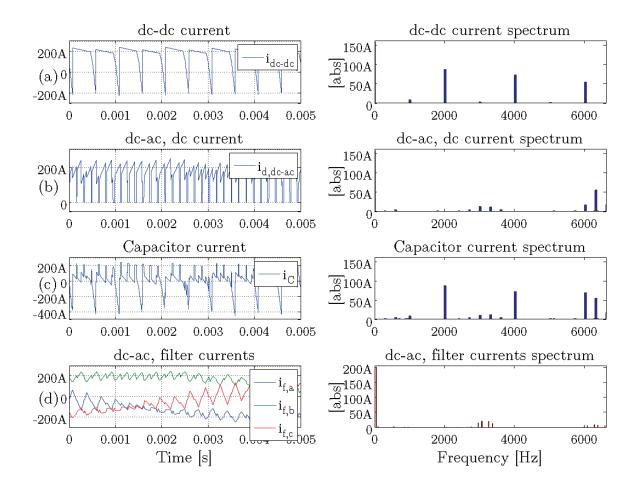

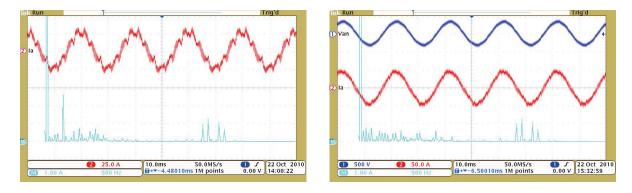

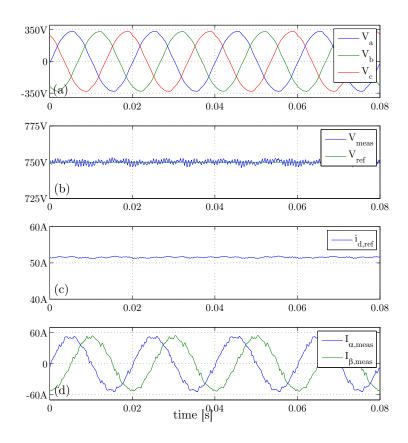

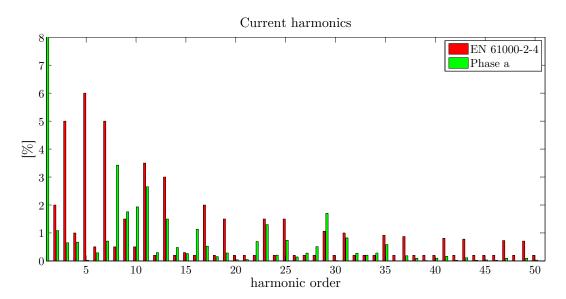

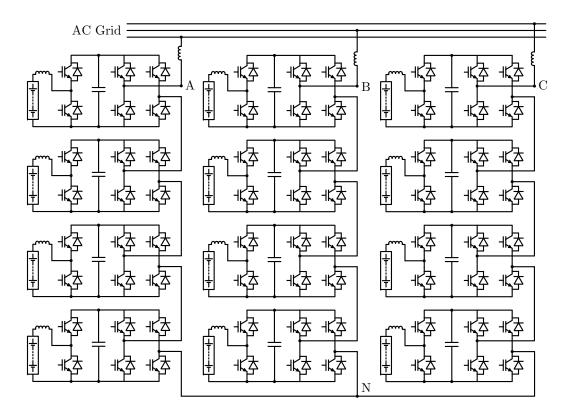

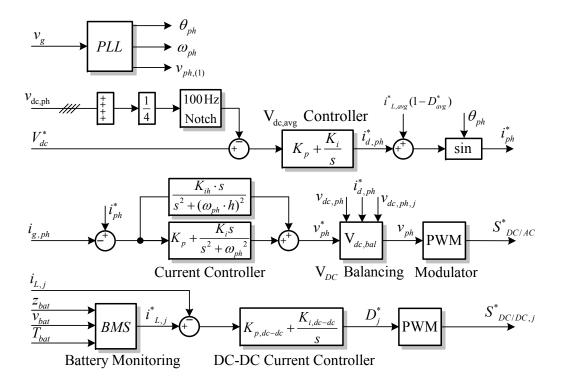

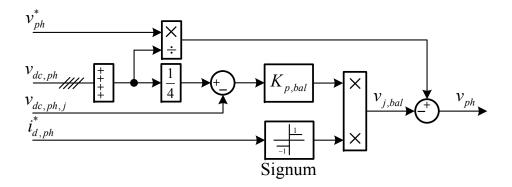

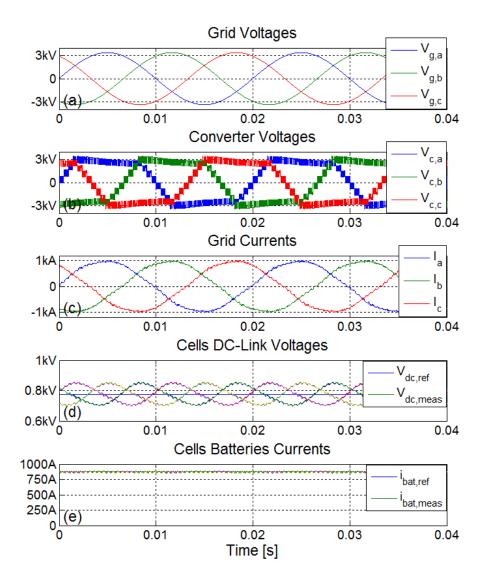

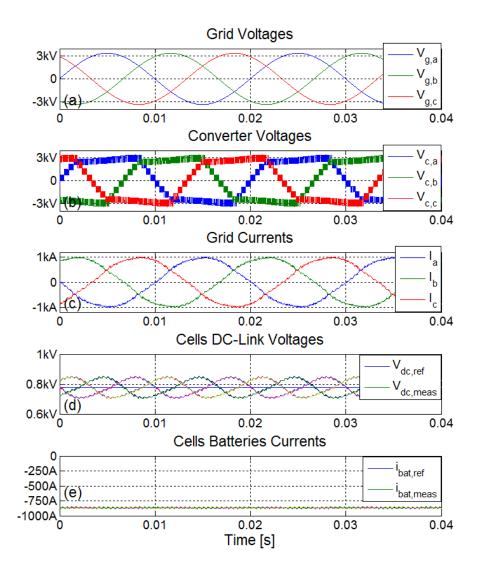

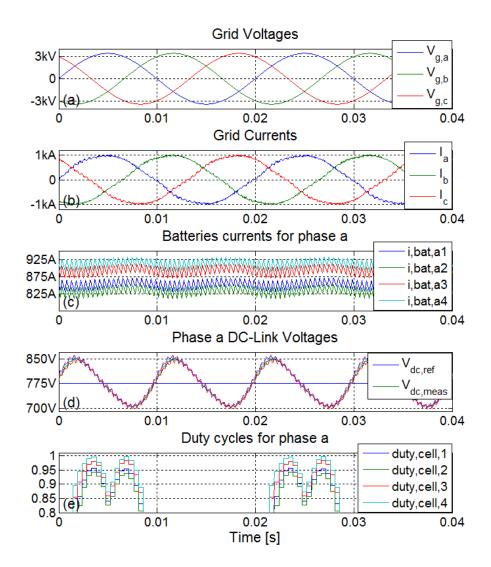

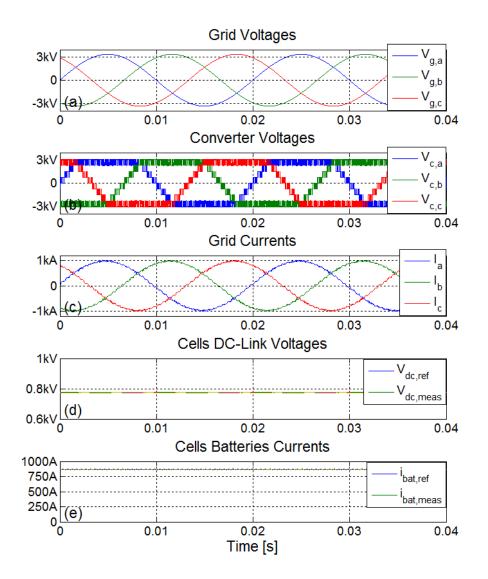

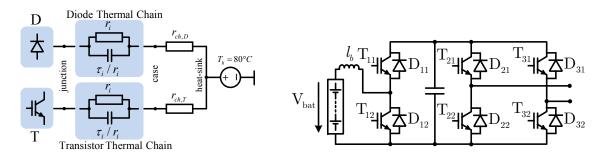

using two sensors only. This solution has the advantage of achieving stable operation without damping, and natural achievement of the unity power factor<sup>1</sup> operation of the current control when the reactive current reference is set to zero [94]. The grid voltages are sensed on each phase at the coupling point.