#### **Aalborg Universitet**

#### SiC-Based 1.5-kV Photovoltaic Inverter

Switching Behavior, Thermal Modeling, and Reliability Assessment Chen, Mengxing

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Chen, M. (2020). SiC-Based 1.5-kV Photovoltaic Inverter: Switching Behavior, Thermal Modeling, and Reliability Assessment. Aalborg Universitetsforlag.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# SIC-BASED 1.5-kV PHOTOVOLTAIC INVERTER: SWITCHING BEHAVIOR, THERMAL MODELING, AND RELIABILITY ASSESSMENT

BY MENGXING CHEN

**DISSERTATION SUBMITTED 2020**

# SiC-Based 1.5-kV Photovoltaic Inverter: Switching Behavior, Thermal Modeling, and Reliability Assessment

Ph.D. Dissertation Mengxing Chen

Dissertation submitted: Aug., 2020

PhD supervisors: Prof. Frede Blaabjerg

Aalborg University, Denmark

Prof. Huai Wang

Aalborg University, Denmark

Prof. Xiongfei Wang

Aalborg University, Denmark

PhD committee: Associate Professor Szymon Michal Beczkowski

Aalborg University (chairman)

Professor Hans-Peter Nee

KTH Royal Institute of Technology

Professor Maria Ines Valla

National University of La Plata (UNLP)

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: Department of Energy Technology

ISSN (online): 2446-1636

ISBN (online): 978-87-7210-696-0

Published by:

**Aalborg University Press**

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Mengxing Chen

Printed in Denmark by Rosendahls, 2020

# **Abstract**

Power electronic converter based on silicon carbide (SiC) devices is one of the most promising technologies for a breakthrough in renewable generation systems. Owing to its wide band-gap (WBG) characteristics, the SiC features several superiorities compared to its silicon (Si) counterpart, e.g., the increased electric field, the higher thermal conductivity, and the greater melting point. Among the application areas of SiC devices, the emerging 1.5-kV photovoltaic (PV) inverter is one of the most popular applications over the last five years. However, the broad adoption of SiC devices in emerging 1.5-kV PV inverters is still facing several reliability uncertainties. Although manufacturers have been working promptly to enhance the robustness of their SiC power devices, efforts from the application perspective are still highly demanded in several aspects.

First, owing to the high di/dt and dv/dt during the switching transient, the SiC metal-oxide-semiconductor field-effect-transistor (MOSFET) can suffer unfavorable switching behaviors, e.g., critical switching oscillations and voltage overshoots, which lead to a catastrophic breakdown in the early phase of operation. Moreover, this switching-behavior challenge becomes even more considerable in the emerging 1.5-kV PV inverter application, where three-level topologies are commonly adopted. Hence, it is highly demanded to have a switching-behavior investigation in 1.5-kV SiC-based inverters and identify the potential solution.

Secondly, the state-of-the-art thermal models fail to ensure an acceptable level of accuracy (especially in high operating temperatures), since the temperature effect on thermal performance is omitted. As the SiC device's thermal profile is closely related to several failure mechanisms, falsely predicting the junction temperature can lead to thermal runaway or accelerated degradation in both short-term and long-term operations. Therefore, a modified thermal model and its modeling methodology with improved accuracy will be needed to realize a highly reliable SiC-based PV inverter.

Thirdly, the long-term wear-out reliability of SiC MOSFETs is still threatened by the issue of die-solder fatigue inside the module, as the Young's modulus of SiC material is two times greater than Si. It has been reported that the thermal-mechanical lifetime of SiC device with standard solder is only 1/3 of Si. Nevertheless, this lifespan deduction has not been considered in state-of-art reliability assessments and design-for-reliability cases. In this perspective, a reliability assessment considering this solder fatigue effect for the 3L-ANPC 1.5-kV PV inverter is highly demanded to evaluate how much system-level lifetime deduction can be expected.

To address the reliability issues as mentioned above, this Ph.D. project works on the following three aspects of SiC-based 1.5-kV PV inverters – switching behaviors, thermal modeling, and wear-out assessment.

Subsequently, the switching behaviors of SiC MOSFETs in a 1.5-kV three-level active-neutral-point-clamped (3L-ANPC) PV inverter are studied in a comprehensive way to identify the unfavorable switching behaviors. The issues of multi-frequency switching oscillation and the induced drain-source voltage overshoot are investigated, and the reliability-critical SiC device and root-cause parasitic component are identified accordingly. Specific design considerations are concluded to aid the design for more reliable SiC-based PV inverters with 1.5-kV dc input.

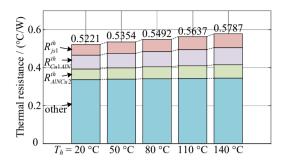

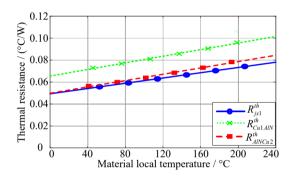

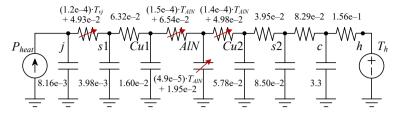

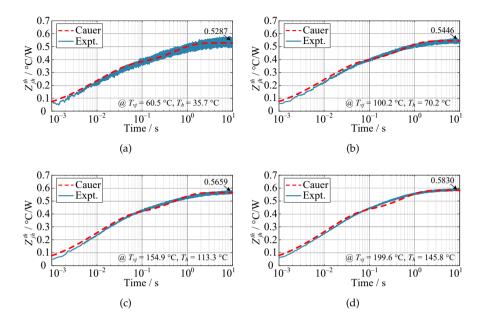

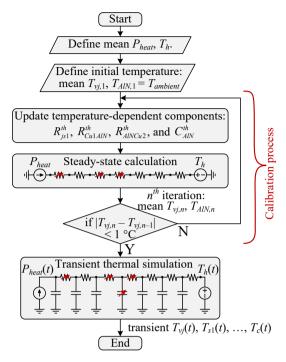

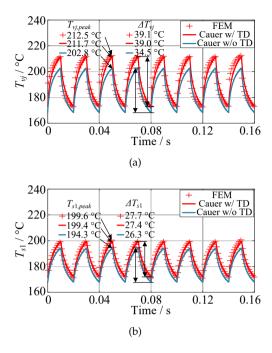

One critical point regarding an accuracy-level enhanced thermal model lies in taking the temperature effect into account. In this regard, the temperature-dependent thermal properties of several SiC power module package materials are integrated into a finite-element-method (FEM) based thermal simulation. On this basis, a temperature-dependent Cauer-type thermal model is extracted, where some of its thermal resistance and capacitance are characterized as temperature-dependent by linear polynomials. It can be concluded that the junction-heatsink thermal resistance is increased by over 10% under high junction temperatures (200  $^{\circ}\text{C})$  by taking the temperature effect in to account.

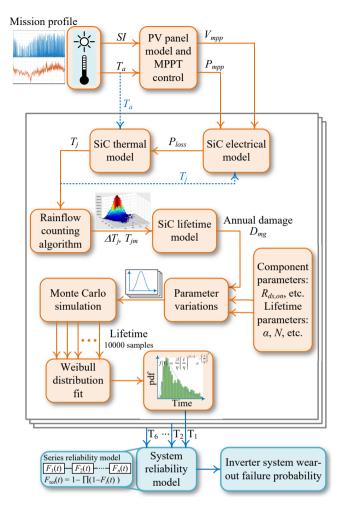

Regarding the wear-out assessment of SiC-based 1.5-kV PV inverter, special efforts are paid on identifying a convincing lifetime model for solder-joints in the SiC power module. Based on available power cycling data and simulation results, a die-solder lifetime model is extrapolated. With the electrical and thermal models already built and validated, a mission-profile-based wear-out assessment procedure is conducted to predict the accumulated failure rate due to the wear-our of SiC modules within a lifespan of thirty years. On this basis, the wear-out reliability performance considering the SiC solder-joint wear-out can be concluded.

# Dansk Resumé

Effektelektroniske omformere baseret på Silicium-Carbid (SiC) er en af de mest lovende teknologier i elektriske systemer til vedvarende energi. På grund af SiCs brede båndgapsegenskaber (WBG) har SiC flere fordele sammenlignet med det konventionelle anvendte silicium (Si). Eksempler på forbedringer er det forøget elektriske felt, en højere termisk ledeevne og et højere smeltepunkt. Blandt anvendelsesområderne af SiC-enheder er den nye 1,5 kV solcelle (PV) vekselretter en af de mest anvendte applikationer. Dog står den udbredte anvendelse af SiC-enheder i nye 1,5 kV PV-konvertere stadig over for flere pålidelighedsusikkerheder. Selvom producenterne arbejder med at forbedre robustheden af deres elektriske SiC-omformere, er pålideligheden fra applikationsperspektivet stadig meget ukendt i flere aspekter.

Som det første, grundet høje di/dt og dv/dt for SiC metal-oxid-halvlederfelt-effekt-transistor (MOSFET), opleves der ugunstige skifteadfærd under skiftende transienter af transistorerne. Dette medfører f.eks. kritiske oscillationer og uønskede spændingsoverskridelser, der kan føre til et katastrofalt nedbrud i den tidlige fase af komponentens livstid. Desuden bliver udfordringen omkring denne skifteadfærd endnu mere betydelig i den nye 1,5 kV PV-vekselretter, hvor tre-niveau typologier oftest anvendes. Det er derfor særdeles vigtigt, at der foretages en adfærdsundersøgelse af skiftende transistorer i 1,5-kV SiC-baserede vekselrettere, samt at potentielle løsninger på pålideligheds-problemet identificeres.

For det andet er moderne termiske modeller ikke i stand til at sikre et acceptabelt niveau af nøjagtighed (især ved høje driftstemperaturer), da temperatureffekten på den termiske ydeevne udelades. Da SiC-enhedens termiske profil er tæt relateret til flere fejlmekanismer, kan forkert forudsigelse af overgangs temperaturen føre til en termisk overophedning eller accelereret nedbrydelse af komponenten. Derfor vil en modificeret termisk model og dens modellerings-metodologi med forbedret nøjagtighed være nødvendig for at realisere en yderst pålidelig SiC-baseret PV-vekselretter.

Som et tredje element, trues den langsigtede pålidelighed af SiC MOSFETs af problemer med lodningstræthed inde i modulet, da Young's modulus af

SiC-materialet er to gange større end det for Si. Det er rapporteret, at den termisk-mekaniske levetid for SiC-enheder med standardlodning kun er 1/3 af det der kan forventes for Si. Ikke desto mindre er dette levetidsfradrag ikke taget i betragtning i avancerede pålidelighedsvurderinger og applikationer hvor der designes for høj pålidelighed. I dette perspektiv kræves der en pålidelighedsvurdering, hvor effekten af lodningen for en 3L-ANPC 1,5 kV PV-vekselretter undersøges, samt for at evaluere, hvor stort et levetidsfradrag der kan forventes på systemniveau.

For at tackle pålidelighedsproblemerne som nævnt ovenfor, arbejder dette ph.d. projektet med tre aspekter af SiC-baserede 1,5-kV PV-omformere, nemlig skifteadfærd, termisk modellering og slidvurdering.

Derefter foretages der et omfattende studie af skifte egenskaberne af SiC MOSFETs i en 1,5 kV 3L-ANPC PV-vekselretter for at identificere den ugunstige skifteadfærd. Spørgsmål vedrørende multi-frekvens oscillationer og den inducerede transistor overspænding er undersøgt, og den pålidelighedskritiske SiC-enhed er identificeret. Specifikke designovervejelser er givet for at forbedre designet af mere pålidelige SiC-baserede PV-vekselrettere med et 1,5 kV dc input.

Et vigtigt punkt vedrørende en forbedret termisk model med en høj nøjagtighed ligger i at tage temperatur effekten i betragtning. I dette henseende er de temperaturafhængige termiske egenskaber for flere SiC moduler integreret i en finit-element-metode (FEM) baseret termisk simulering. På dette grundlag forslåes en temperaturafhængig termisk model af Cauer-typen, hvor noget af dens termiske modstand og kapacitet er karakteriseret som temperaturafhængige lineære polynomier. Det kan konkluderes, at den overordnede termiske modstands fra modul-indre til kølelegeme kan hæves med mere end 10% under høje temperaturforhold (200 °C) ved at inkludere denne temperatureffekt.

Hvad angår slidvurderingen af SiC-baseret 1,5 kV PV-vekselrettere, gøres der en særlig indsats for at identificere en overbevisende levetidsmodel for loddeforbindelser i SiC-modulet. Baseret på tilgængelige data for effektcykler og simuleringsresultater, ekstrapoleres en levetidsmodel. Med de elektriske og termiske modeller foreslået i dette projekt, udføres en mission-profil baseret vurderingsprocedure for at forudsige den akkumulerede fejlhyppighed på grund af slid på SiC-moduler inden for en levetid på tredive år. På dette grundlag kan pålidelighedens præstation konkluderes med SiC-loddesamlinger taget i betragtning.

| A  | bstra | ct       |                                                      | iii  |

|----|-------|----------|------------------------------------------------------|------|

| D  | ansk  | Resum    | é                                                    | v    |

| Tl | nesis | Details  | 3                                                    | xi   |

| Pı | eface | <b>:</b> |                                                      | xiii |

|    | Rep   | ort      |                                                      | 1    |

| 1  | Intr  | oductio  | on                                                   | 3    |

|    | 1.1   | Backg    | round                                                | 3    |

|    |       | 1.1.1    | Topologies for PV Inverter with a 1.5-kV DC-Link     | 6    |

|    |       | 1.1.2    | Switching Behaviors of SiC MOSFETs in 1.5-kV 3L-ANPC |      |

|    |       |          | Inverter                                             | 8    |

|    |       | 1.1.3    | Thermal Characterization of SiC MOSFET Module        | 9    |

|    |       | 1.1.4    | Wear-out of SiC MOSFET Based Inverter                | 10   |

|    | 1.2   | Projec   | t Motivation                                         | 12   |

|    |       | 1.2.1    | Research Questions                                   | 12   |

|    |       | 1.2.2    | Research Objectives                                  | 13   |

|    | 1.3   | Projec   | et Limitations                                       | 13   |

|    | 1.4   | Thesis   | S Outline                                            | 14   |

|    | 1.5   | List o   | f Publications                                       | 16   |

| 2  |       | _        | Behavior Investigation of SiC MOSFETs in 1.5-kV 3L-  | -    |

|    | AN    | PC Inv   | erter                                                | 19   |

|    | 2.1   |          | Introduction                                         | 19   |

|    | 2.2   | Parasi   | tic Modeling of SiC-based 3L-ANPC Phase-Leg          | 20   |

|    |       | 2.2.1    | Half-bridge SiC MOSFET Module                        | 20   |

|    |       | 2.2.2    | 3L-ANPC Phase-Leg                                    | 21   |

|    | 2.3   | Analy    | rses of Commutation Modes                            | 22   |

|   |     | 2.3.1  | Switching States                                        | 22 |

|---|-----|--------|---------------------------------------------------------|----|

|   |     | 2.3.2  | Full-Mode Commutation                                   | 23 |

|   |     | 2.3.3  | Outer-Mode Commutation                                  | 26 |

|   |     | 2.3.4  | Inner-Mode Commutation                                  | 28 |

|   | 2.4 | Doubl  | e-Pulse Test (DPT) and Result Analysis                  | 31 |

|   |     | 2.4.1  | Test Setup Introduction                                 | 31 |

|   |     | 2.4.2  | Transient Switching Waveforms                           | 33 |

|   |     | 2.4.3  | Result Analysis – Multi-Frequency Switching Oscillation | 34 |

|   |     | 2.4.4  | Result Analysis - Voltage Overshoots, Current Over-     |    |

|   |     |        | shoots, and Capacitive Charge                           | 37 |

|   |     | 2.4.5  | Result Analysis – Switching Losses                      | 38 |

|   | 2.5 | Summ   | nary and Design Considerations                          | 40 |

| 3 | Tem | peratu | re-Dependent Thermal Modeling of SiC MOSFETs            | 43 |

|   | 3.1 |        | ntroduction                                             | 43 |

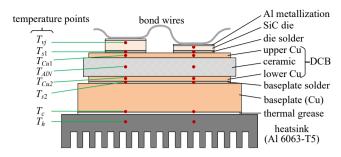

|   | 3.2 | Struct | ure and Thermal Properties of a Commercial SiC MOS-     |    |

|   |     | FET M  | Iodule                                                  | 44 |

|   |     | 3.2.1  | Structure of SiC MOSFET Module                          | 44 |

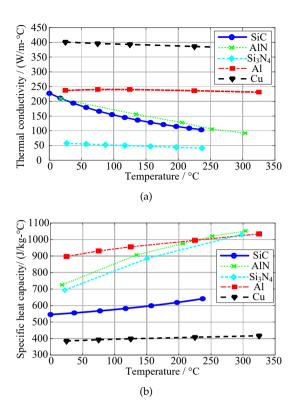

|   |     | 3.2.2  | Temperature-Dependent Thermal Properties                | 45 |

|   | 3.3 | Extrac | tion of the Temperature-Dependent Cauer Model           | 45 |

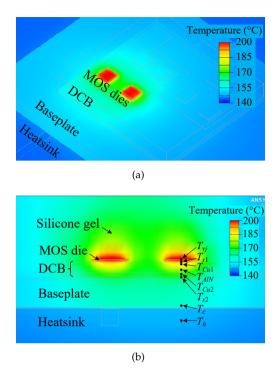

|   |     | 3.3.1  | FEM Simulations of SiC MOSFET Module                    | 46 |

|   |     | 3.3.2  | Extraction Methodology of Thermal Resistance and Ca-    |    |

|   |     |        | pacitance                                               | 48 |

|   |     | 3.3.3  | Temperature-Dependent Cauer Model                       | 49 |

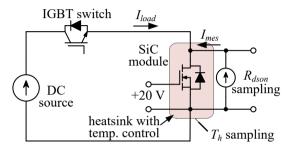

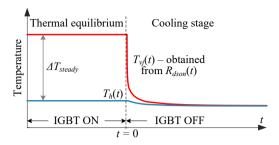

|   | 3.4 | -      | imental Characterization of Transient Thermal Impedance | 51 |

|   |     | 3.4.1  | Experiment Setup                                        | 51 |

|   |     | 3.4.2  | Measurement of Transient Thermal Impedance              | 52 |

|   |     | 3.4.3  | Experimental Results                                    | 53 |

|   | 3.5 |        | cation of Transient Thermal Simulation                  | 54 |

|   | 3.6 | Summ   | nary                                                    | 55 |

| 4 | Wea |        | Failure Assessment of SiC MOSFETs in 3L-ANPC Inverter   |    |

|   | 4.1 |        | ntroduction                                             | 59 |

|   |     | 4.1.1  | System Description                                      | 59 |

|   |     | 4.1.2  | Reliability Assessment Procedure                        | 60 |

|   | 4.2 |        | o-Thermal and Lifetime Modeling of SiC Devices          | 61 |

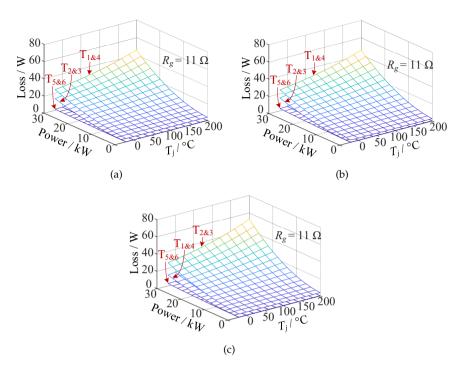

|   |     | 4.2.1  | Electrical Model of SiC MOSFETs – Switching Losses      | 61 |

|   |     | 4.2.2  | Electrical Model of SiC MOSFETs – Conduction Losses .   | 63 |

|   |     | 4.2.3  | Thermal Model of SiC MOSFETs                            | 63 |

|   |     | 4.2.4  | Lifetime Model of SiC MOSFETs                           | 67 |

|   | 4.3 | -      | ses of Wear-Out Failure Probability                     | 68 |

|   |     | 4.3.1  | Annual Damage of Devices                                | 68 |

|   |     | 4.3.2  | Monte-Carlo Simulation                                  | 68 |

|   |      | 1.3.3 Results Analyses | 2 |

|---|------|------------------------|---|

|   | 4.4  | Summary                | 3 |

| 5 | Con  | usions 75              | 5 |

|   | 5.1  | Summary                | 5 |

|   |      | Main Contributions     |   |

|   | 5.3  | Project Perspectives   | 7 |

| A | Bibl | ography 79             | 9 |

|   | Refe | ences                  | 9 |

# Thesis Details

**Thesis Title:** SiC-Based 1.5-kV Photovoltaic Inverter: Switching Behav-

ior, Thermal Modeling, and Reliability Assessment

Ph.D. Student: Mengxing Chen

**Supervisors:** Prof. Frede Blaabjerg, Aalborg University, Denmark

Prof. Huai Wang, Aalborg University, Denmark

Prof. Xiongfei Wang, Aalborg University, Denmark

The main body of this thesis consists of the following papers:

#### **Publications in Refereed Journals**

- **J1. M. Chen**, D. Pan, H. Wang, X. Wang, and F. Blaabjerg, "Investigation of Switching Oscillations for Silicon Carbide MOSFETs in Three-Level Active Neutral-Point-Clamped Inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. PP, no. 99, pp. 1-15, 2020, Early Access.

- J2. M. Chen, H. Wang, D. Pan, X. Wang, and F. Blaabjerg, "Thermal Characterization of Silicon Carbide MOSFET Module Suitable for High-Temperature Computationally-Efficient Thermal-Profile Prediction," IEEE J. Emerg. Sel. Topics Power Electron., vol. PP, no. 99, pp. 1-12, 2020, Early Access.

- J3. M. Chen, Z. Shen, H. Wang, X. Wang, and F. Blaabjerg, "Reliability Assessment of SiC MOSFETs in Three-Level Active Neutral-Point-Clamped Inverters Considering Die-Solder Degradation," IEEE Trans. Power Electron., 2020, Status: to be Submitted.

#### Publications in Refereed Conferences

- C1. M. Chen, D. Pan, H. Wang, X. Wang, F. Blaabjerg, and W. Wang, "Switching Characterization of SiC MOSFETs in Three-Level Active Neutral-Point-Clamped Inverter Application," in *Proc. 2019 10<sup>th</sup> Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia)*, May 2019, pp. 1793-1799.

- **C2. M. Chen**, H. Wang, F. Blaabjerg, X. Wang, and D. Pan, "A Temperature-Dependent Thermal Model of Silicon Carbide MOSFET Module for Long-Term Reliability Assessment," in *Proc. 2018 IEEE 4<sup>th</sup> Southern Power Electronics Conference (SPEC)*, Dec. 2018, pp. 1-7. (Best Paper Award)

- **C3. M. Chen**, T. Zhu, D. Pan, H. Wang, X. Wang, and F. Blaabjerg, "Loss Analysis of SiC-Based Three-Level Active Neutral-Point-Clamped Inverters under Different Modulation Schemes," in *Proc.* 2020 IEEE 9<sup>th</sup> International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Status: In Press.

This thesis has been submitted for assessment in partial fulfillment of the Ph.D. degree. The thesis is a summary of the outcome from the Ph.D. project, which is documented based on the above publications. Parts of the results are used directly or indirectly in the extended summary of the thesis. The co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science, Aalborg University.

# **Preface**

This Ph.D. thesis is a summary of the Ph.D. project "Highly Efficient and Reliable SiC-based Photovoltaic Inverters", which was conducted at the Department of Energy Technology, Aalborg University, Denmark. This Ph.D. project is sponsored by Innovation Fund Denmark under grant 5185-00006B (HER-SiC project). I would like to express my gratitude to both institutions for their enduring supports. Also, I would like to thank our project partners, Harbin Institute of Technology (HIT) and Global Energy Interconnection Research Institute (GEIRI), for their continued supports.

I would like to sincerely thank my supervisor Professor Frede Blaabjerg for his patient instruction and valuable suggestions during this Ph.D. project. He is such a generous mentor who always provides me with infinite guidance and support during my academic career in Aalborg. I would also like to express the deepest gratitude to my co-supervisor Professor Huai Wang, who always offers me professional and patient advice regarding theoretical analyzing, paper drafting, and experimental testing. Likewise, I would like to sincerely thank my co-supervisor Professor Xiongfei Wang. He always provides me with enthusiasm advising and warmth encouragement.

My special gratitude goes to Professor Eckart Hoene for his kidness and intriguing discussion during my study-abroad in Fraunhofer Institute for Reliability and Microintegration IZM, Berlin, Germany. Also, many thanks to the colleagues at Fraunhofer IZM for their hospitality during my stay in Berlin.

I would like to thank my colleagues at the Department of Energy Technology, Aalborg University for their kind support and interesting discussions. Special thanks go to Dr. Donghua Pan, Dr. Yipeng Song, Dr. Yanfeng Shen, Dr. Haoran Wang, Dr. Zhan Shen, Dr. Mads Graungaard Taul, Mr. Tianyu Zhu, and Mr. Yangwen Wang for their kind supports to this Ph.D. thesis.

Finally, my most sincere gratitude goes to my parents and my girl-friend Miss Yunfeng Li. Your endless love and encouragement keep me going forwards even in darkness.

Mengxing Chen Aalborg University, August 29, 2020

#### Preface

# Report

# Chapter 1

# Introduction

#### 1.1 Background

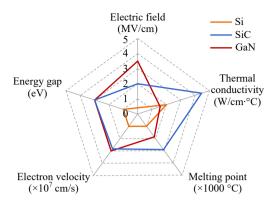

As a wide band-gap (WBG) material, the SiC exhibits several superiorities compared to its silicon (Si) counterpart, e.g., the enhanced electric field, the greater electron velocity, and the higher thermal conductivity and melting point, as exhibited in Fig. 1.1 [1]. The material properties of SiC enable practical power devices with blocking voltages an order of magnitude of the possibility in Si, improved dynamic behavior, extended operating temperature range, and significantly reduced energy losses [2, 3]. One of the most prevalent devices is the SiC metal-oxide-semiconductor field-effect-transistor (MOSFET) as it meets the requirement of 1.2–3.3 kV blocking voltage for several applications, e.g., photovoltaic (PV) converters [4], uninterruptible power supplies (UPS) [5, 6], locomotive power converters [7], and electric vehicles [8, 9].

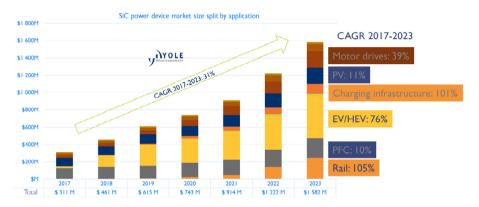

Among these application areas, the SiC-based photovoltaic (PV) inverter is one of the most interesting research topics in the last five years [3, 4, 10–13], where improvements in the conversion efficiency and power density have been reported. As the world demands more renewable and sustainable energies, the SiC power device market for PV applications keeps increasing over recent years, as it is exhibited in Fig. 1.2 [14]. The compound annual growth rate (CAGR) of SiC power devices in PV applications is anticipated to be 11% from the year 2017 to 2023, and its market size is expected to reach 100 million US Dollars upon the year 2023.

Despite the dramatic market demand, the broad adoption of SiC MOSFET in PV inverters is still facing reliability and robustness challenges, as summarized in Table 1.1. It is noted that the SiC MOSFET suffers various reliability issues, e.g., over-voltage breakdown [15], power-cycling capability [16–19], electro-thermal instability [20, 21], short-circuit robustness [22–25], GOX re-

#### Chapter 1. Introduction

Fig. 1.1: Benchmark of material properties among Si, SiC, and GaN. [1]

Fig. 1.2: SiC power device market share and compound annual growth rate (CAGR) split by applications. [14]

liability [18, 26, 27], threshold instability [28], and body-diode degradation [29]. In order to tackle these challenges, the device manufacturers have been working promptly to improve the robustness of their SiC power devices. For instance, the GOX of SiC MOSFET has exhibited a lifetime comparable with that of the Si insulated-gate bipolar transistor (IGBT), as it is reported in [18]. Also, novel interconnection technologies, e.g., aluminum-copper (AlCu) ribbon and silver (Ag) sintering, have seen applications in industrial prototypes to enhance their power cycling capabilities [19]. Even though, efforts from the application perspective are still highly demanded to improve the robustness and reliability of SiC-based power converters. To maximize the PV energy yields, it is generally required that the commercial PV inverters should achieve a useful lifetime of twenty years. A future lifetime target for reliable PV inverters shall be thirty years. It is still questionable if the SiC-based PV inverters are able to achieve an useful lifetime of twenty years.

#### 1.1. Background

Table 1.1: Reliability issues, failure mechanisms, and critical stressors of SiC MOSFET.

| Reliability issues                   | Critical failure mechanisms     | Stressors               |

|--------------------------------------|---------------------------------|-------------------------|

| Over-voltage breakdown [15]          | Thermal runaway, PD             | $V_{ds}$ , $T_{jm}$     |

| Power-cycling capability [16–19]     | Solder-joint wear-out           | $\Delta T_j$ , $T_{jm}$ |

| Electro-thermal instability [20, 21] | Thermal runaway                 | $T_{jm}$                |

| Short-circuit robustness [22–25]     | Thermal runaway, GOX damage     | $T_{im}$                |

| GOX reliability [18, 26, 27]         | Extrinsic failure, over-heat    | $V_{gs}$ , $T_{im}$     |

| Threshold instability [28]           | Trapped electrons               | $V_{gs}$                |

| Body-diode degradation [29]          | Crystal defect (stacking fault) | $I_f$                   |

GOX: gate oxide, PD: partial discharge,  $V_{ds}$ : drain-source voltage,  $T_{jm}$ : mean junction-temperature,  $\Delta T_j$ : junction-temperature swing,  $V_{gs}$ : gate-source voltage,  $I_f$ : diode forward current.

Several reliability challenges for SiC-based PV inverters still exist from the application perspective, as listed below:

#### • Challenge I – switching-behavior uncertainty:

Owing to the high di/dt and dv/dt during switching transients, the SiC device can suffer unfavorable switching behaviors. More critically, the emerging PV inverter commonly adopts a 1.5-kV dc-link with three-level (3L) inverters to diminish PV-power transmission losses. Integrating the fast-switching SiC MOSFETs into 3L inverters worsens their switching characteristics (e.g., critical voltage overshoots, excessive switching losses, and multiple switching-oscillation components) and may lead to immediate failure and performance degradation of the power semiconductor [30–32].

#### • Challenge II – thermal uncertainty:

The thermal performance of a power semiconductor device is closely related to its reliability. It is noted from Table 1.1 that the mean junction-temperature  $T_{jm}$  and the junction-temperature swing  $\Delta T_j$  are two of the most significant stressors to a variety of critical failure mechanisms. However, the state-of-art thermal models and their characterization methodologies fail to provide sufficient accuracy for SiC power devices, especially under high-temperature operating conditions.

#### • Challenge III – wear-out uncertainty:

Up till now, one of the most significant failure mechanisms limiting the long-term reliability of SiC power modules is the solder-joint wearout. As the Young's modulus of SiC is two times greater than that of Si (meaning that SiC is two times stiffer than Si), the SiC solder-joints suffer substantial mechanical stress during the long-term power cycling operations. It has been reported that the thermal-mechanical lifetime of the SiC device is only 1/3 of Si [17, 19]. However, this lifetime reduction

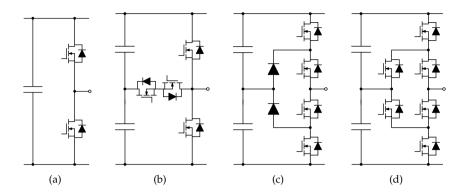

**Fig. 1.3:** Prevalent 3-phase PV inverter topologies for 1.5-kV dc-link voltage. (a) Two-level half-bridge (2L-HB). (b) Three-level T-type neutral-point-clamped (3L T-type NPC) [37]. (c) Three-level diode neutral-point-clamped (3L-DNPC) [38]. (d) Three-level active neutral-point-clamped (3L-ANPC) [39].

has not been addressed in the design and lifespan-expectation of SiC-based power converters.

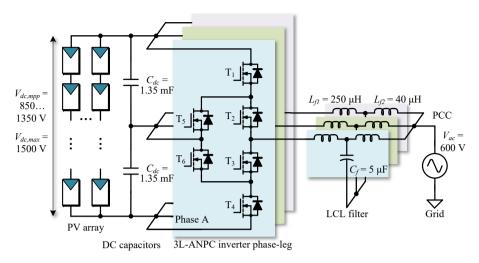

#### 1.1.1 Topologies for PV Inverter with a 1.5-kV DC-Link

As the PV panels with 1.5-kV insulation capability have been commercialized in recent years, one of the most significant trends in emerging commercial-and utility-scale PV plants is the extension of the maximum dc voltage to 1.5 kV [33]. It is reported in [34] that the increase of dc voltage to 1.5 kV leads to a reduction of 15–85% in conductor mass, as well as a reduction of 25–60% in combiner boxes, depending on PV array sizes and configurations. It is worth to note that the maximum input voltage of the PV inverter can reach 1.5 kV, which matches the maximum open-circuit voltage of the PV array. During operation, the maximum-power-point (MPP) voltage can operate from 880 V to 1450 V or 850 V to 1350 V, as defined by SMA Solar Technology AG [35] and ABB AG [36], respectively.

The prevalent PV inverter topologies are exhibited in Fig. 1.3. The two-level half-bridge [2L-HB, see Fig. 1.3(a)] and three-level T-type neutral-point clamped [3L T-type NPC, see Fig. 1.3(b)] topologies may only be applicable in 1-kV PV systems. Compared with the 2L-HB, the 3L architectures bring several merits. The volume and and cost of the ac-side filter can be designed to be much lower [40], and the system leakage current can be significantly reduced due to a lower dv/dt [40]. However, as each of the main switches in 2L-HB and 3L T-type NPC topologies bears the whole dc-link voltage during blocking state, the 1.5-kV inverter based on 2L-HB and 3L T-type NPC topologies can not guarantee a sufficient voltage margin for commercial 1.7-

#### 1.1. Background

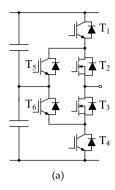

**Fig. 1.4:** Two types of hybrid 3L-ANPC inverter architectures using both Si IGBTs and SiC MOSFETs. (a) Type I: inner mode. (b) Type II: outer mode.

#### kV power devices.

On the other hand, the three-level diode neutral-point-clamped [3L-DNPC, see Fig. 1.3(c)] and three-level active neutral-point-clamped [3L-ANPC, see Fig. 1.3(d)] topologies can assure a sufficient voltage margin with commercial 1.2-kV Si IGBTs and SiC MOSFETs, making them competently qualified for PV inverters with the 1.5-kV dc-link voltage. Compared with the 3L-DNPC, the 3L-ANPC inverter is able to re-distribute the power-loss and heat stresses among different semiconductor devices [39].

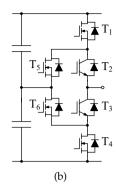

Over the recent years, the applications of SiC MOSFETs in 3L-ANPC inverters are presented in the literature with enhancement in efficiency and power-density [4, 41–44]. Except for fully utilizing SiC MOSFETs in a 3L-ANPC inverter phase-leg [as exhibited in Fig. 1.3(d)], implementing two types of hybrid 3L-ANPC architectures with both SiC MOSFETs and Si IGBTs [as demonstrated in Figs. 1.4(a) and 1.4(b)] reduces the cost while still maintains the superiority brought by SiC MOSFETs [4, 42–44]. In specific, the type I shown in Fig. 1.4(a) only implements inner switches T<sub>2</sub> and T<sub>3</sub> as SiC MOSFETs (high-frequency switching), while other switches are implemented using Si IGBTs (line-frequency switching). The type II [see Fig. 1.4(b)], on the other hand, uses SiC MOSFET with high-frequency-switching for devices T<sub>1</sub>, T<sub>4</sub>, T<sub>5</sub>, and T<sub>6</sub>, while the inner switches T<sub>2</sub> and T<sub>3</sub> are implemented using Si IGBTs with line-frequency-switching.

Considering the above-mentioned merits of SiC-based 3L-ANPC inverters in 1.5-kV PV applications, the world's leading PV-system manufacturer, SMA Solar Technology AG, has successfully launched a 1.5-kV, 150-kW PV inverter based on the hybrid 3L-ANPC topology shown in Fig. 1.4(a) [45]. It is expected that using the 3L-ANPC topology with SiC MOSFETs will be a significant trend in future 1.5-kV PV systems.

Fig. 1.5: Over-voltage failure samples of SiC MOSFET modules [20]. (a) Sample I. (b) Sample II.

# 1.1.2 Switching Behaviors of SiC MOSFETs in 1.5-kV 3L-ANPC Inverter

Although the SiC-based 3L-ANPC inverter exhibits a significant application potential in 1.5-kV PV systems, the switching behaviors of SiC MOSFETs in 3L-ANPC inverters still have not been fully revealed. The fast-switching SiC MOSFETs may suffer unfavorable switching behaviors in 3L-ANPC inverters, e.g., critical switching oscillations, voltage overshoots, and excessive switching losses, which may lead to an over-voltage breakdown of the SiC power device (by thermal runaway or partial discharge). Two failure samples of SiC MOSFET caused by transient over-voltage are exhibited in Fig. 1.5.

Differing from the switching characteristics in discrete-devices and 2L-HB configurations [46–53], the switching characteristics of SiC MOSFETs in 3L-ANPC inverters are more sophisticated, as they can be significantly affected by multiple commutation modes and line-frequency devices [31, 54, 55]. The three representative commutation modes, i.e., the full mode, outer mode, and inner mode, of the 3L-ANPC inverter were studied in [39]. The typical commutation loops and characteristics related with the three commutation types were investigated in [54, 55]. Most recently, the extra junction capacitance and the capacitive loop induced by low-frequency switches are illustrated in [31]. Owing to various commutation loops and high slew rates, the fast-switching of SiC MOSFET in 3L-ANPC inverters engenders unfavorable switching behaviors, e.g., critical voltage overshoots, excessive switching losses, and multiple switching-oscillation components.

In [30], the over-voltage issue of SiC MOSFET in 3L-ANPC inverters was introduced for the outer and inner modes. A model for the over-voltage issue was proposed in [32], which only studies the outer-mode mechanism. Despite the studies mentioned above, the comprehensive understanding regarding the switching oscillations with multiple frequency components closely related to the SiC-based 3L-ANPC inverter remains unexplained. A com-

#### 1.1. Background

**Fig. 1.6:** Failure samples of SiC MOSFET modules caused by high temperature. (a) Failure sample under single-event unclamped inductive switching (UIS) [59]. (b) Failure sample under long-term over temperature [20].

prehensive study of the switching behaviors (e.g., overshoots, oscillations, and switching losses) with these three typical ANPC commutation modes is highly demanded since the performance of the switching is dependent on commutation modes.

#### 1.1.3 Thermal Characterization of SiC MOSFET Module

As discussed in Table 1.1, the mean junction temperature  $T_{im}$  and junctiontemperature swing  $\Delta T_i$  are two of the most significant stressors to a variety of critical failure mechanisms of SiC MOSFET [56]. Compared with the Si IGBT, the SiC MOSFET can be more easily damaged by a single over-temperature event, e.g., the short-circuit and unclamped inductive switching (UIS), owing to its GOX weakness and compact die size. On the other hand, the solderjoint degradation of the SiC die can be two times faster than the Si IGBT during the long-term thermal cycling process, due to the high stiffness of SiC [16-19]. Moreover, other reliability issues, e.g., the time-dependent dielectric breakdown, inter-layer dielectric erosion, and electrode delamination, can be triggered under a long-term high-temperature operating condition [57]. To guarantee the reliability of the SiC MOSFET module during its lifespan, a high-precision thermal model and its characterization methodology for the temperature-profile prediction within a wide temperature range are strongly demanded. Thereafter, a reliability investigation methodology shall be used to transfer the temperature data to a variety of reliability characteristics [56, 58].

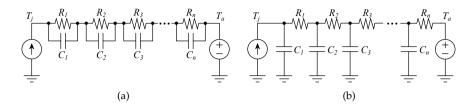

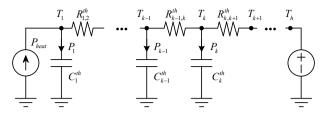

Nowadays, one of the most general methodologies regarding thermal estimations of power devices is to conduct the circuit-level thermal simulation using these resistor-capacitor (RC) lumped thermal models [60, 61], i.e., the Foster-type and Cauer-type. In specific, the Foster-type RC lumped thermal model [the Foster model, as illustrated in Fig. 1.7(a)] can usually be accessed

Fig. 1.7: Two types of prevailing RC lumped thermal models. (a) Foster model. (b) Cauer model.

from the datasheet of power semiconductor devices, which are obtained from the transient-thermal-impedance curve characterized by experiments. The Cauer-type thermal model [the Cauer model, as exhibited in Fig. 1.7(b)], on the other hand, can be built based on the knowledge of geometry and material properties of the power semiconductor device [62]. These two types of RC lumped thermal models have found their applications for long-term thermal-profile evaluations of SiC MOSFETs in several works [63–66].

However, the RC lumped thermal models are commonly characterized under a fixed temperature with constant thermal resistance and capacitance values. The precision under high-temperature circumstance is unwarranted. The thermal conductivities and heat capacities of the SiC die and peripheral materials can shift dramatically with local-temperature variations due to free electrons and lattice vibration. To address the aforementioned issue, a temperature-dependent thermal model for the Si IGBT module was proposed in [67]. It was also validated that omitting the temperature effect of Si IGBT's thermal model can lead to significant junction-temperature estimation errors. Nevertheless, the temperature effects of peripheral materials other than the Si IGBT die, especially the ceramic substrate, were not characterized [67]. A SiC MOSFET thermal model having a particular focus on the die area was studied in [68], and the temperature-dependent thermal properties of SiC were considered. Yet, the temperature-dependent thermal performance of the whole power module remains unexplored.

#### 1.1.4 Wear-out of SiC MOSFET Based Inverter

Regarding the long-term power cycling reliability of the SiC device, one of the most crucial failure mechanisms is the solder-joint wear-out. Due to contact of different packaging layers with different coefficients of thermal expansion (CTE), the solder material (e.g., Sn-Ag-Cu as die-solder or baseplate-solder) can suffer from dramatic thermo-mechanical stresses during the long-term power cycling. As the Young's modulus of SiC is two times greater than that of Si (meaning that SiC is two times stiffer than Si), the solder layer beneath the SiC die will degrade two times faster than that of Si. As it is

#### 1.1. Background

Fig. 1.8: Comparison of normalized thermal resistance degradation for SiC Schottky barrier diode (SBD) and Si IGBT measured during the power cycling test. [16]

Fig. 1.9: Scanning electron microscope image of a cracked SiC die-solder in cross-section view [19].

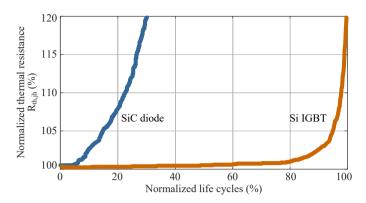

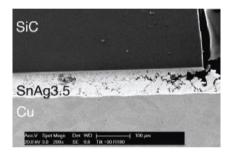

demonstrated in Fig. 1.8, the power cycling lifetime of a SiC diode is only 1/3 of Si IGBT, assuming the end-of-life criteria to be a 20 % increase of the thermal resistance  $R_{th,jh}$  [16]. A scanning electron microscope (SEM) image shows that the solder layer beneath a SiC die to crack from the die edge, where the strain energy during power cycling is concentrated [19].

Although the novel Ag sintering technology can solidify the die-attach reliability in SiC-based power modules, its application in practical power electronic converters is still constrained by high costs. For some cost-sensitive applications, e.g., PV inverters, the SiC MOSFET modules with standard solder materials (e.g., the Sn-Ag-Cu) still dominate the SiC market. However, this lifetime deduction caused by the solder degradation has not been addressed in the lifespan-evaluation of SiC-based power converters [65, 69]. Moreover, a useful power cycling lifetime model of the SiC module with standard soldering technology is still under research.

#### 1.2 Project Motivation

#### 1.2.1 Research Questions

As discussed in previous sub-chapters, the broad application of the SiC power device in 1.5-kV PV inverter systems is still restricted by its reliability uncertainties in different aspects (as listed in Table 1.1). Although the manufacturers have been working promptly to enhance the robustness of their SiC power devices, efforts from the application perspective are even more demanding to realize more reliable SiC-based power electronic converters. Concerning this point, the Ph.D. project works with the reliability challenges from a power electronic system's viewpoint.

Therefore, the overall research question for this Ph.D. project is defined as follows:

Q0: How to ensure twenty years of a useful lifetime for SiC-based 1.5kV PV inverters?

To answer this overall research question, we need to be aware that the SiC-based 1.5-kV PV inverter can face numerous reliability challenges during its whole lifespan. Three of the most critical ones are switching-behavior uncertainty, thermal uncertainty, and wear-out uncertainty, as discussed in Chapter 1.1. Based on the justifications mentioned above, the following research questions are considered in this Ph.D. project:

- Q1: Will the 3L-ANPC topology bring reliability challenges to SiC MOSFETs in terms of their potential unfavorable switching behaviors?

- **Q2:** How to improve the power-stage design to address the reliability challenge brought by switching behaviors?

- Q3: How to characterize the thermal behaviors of SiC power modules with an improved accuracy level throughout the full temperature range?

- Q4: Is there any power-cycling lifetime model available for SiC MOS-FET modules with standard the soldering and wire-bonding technology?

- Q5: What amount of lifetime expectation will be concluded if a twotimes faster solder-layer degradation process is considered for SiC MOS-FET modules.

#### 1.2.2 Research Objectives

Motivated by the research questions mentioned above, this Ph.D. project aims to achieve the following research objectives:

#### • O1 – Switching-behavior investigation:

To answer Q1 and Q2, a comprehensive investigation of switching behaviors for SiC MOSFETs in 3L-ANPC topologies shall be conducted in this dissertation. The reliability-critical components need to be found based on a parasitic model of the 3L-ANPC phase-leg. The switching behaviors of SiC MOSFETs need also to be tested under a 1.5-kV PV inverter prototype.

# • O2 – Temperature-dependent thermal model with computational efficiency:

To answer Q3, a temperature-dependent thermal model shall be developed in this Ph.D. project, which should consider the temperature effect and provide an enhanced accuracy level. Meanwhile, a high computational efficiency should be guaranteed to make the proposed thermal model suitable for long-term reliability assessment.

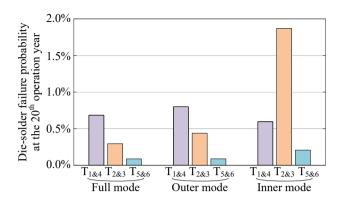

• O3 – Wear-out reliability assessment considering die-solder wear-out: To answer Q4 and Q5, a power cycling lifetime model considering die-solder degradation effects of SiC MOSFET need to be identified. Then a mission-profile-based reliability investigation should be conducted to assess the wear-out reliability of SiC-based 1.5-kV PV inverter. The wear-out failure probability of different SiC MOSFETs under three typical 3L-ANPC commutation modes are to be found and concluded accordingly.

These research objectives are achieved in the same order throughout this dissertation, based on the published journal and conference papers. The published papers are provided in the appendix of the dissertation.

#### 1.3 Project Limitations

Several scientific limitations of this Ph.D. project are listed as follows:

• L1: The overall reliability performance and assessment can be more complicated with multiple failure mechanisms and stressors involved (see Table 1.1). This Ph.D. project covers the packaging-related wearout failure mechanisms, while other reliability-limiting factors, e.g., the humidity and cosmic ray, are not considered.

- L2: The switching-behaviors of SiC MOSFETs are studied based on a 3L-ANPC inverter demonstrator, where the switching characteristics are specified. Different values of switching metrics, e.g., amplitudes of overshoots and oscillation frequencies, might be witnessed if a redesigned 3L-ANPC inverter prototype is tested.

- L3: To build the proposed temperature-dependent Cauer-type thermal model, the knowledge of temperature-dependent thermal property and power-module geometry is mandatory.

- L4: The lifetime model extrapolated in this Ph.D. project can only predict the lifetime of the SiC MOSFET module with conventional interconnection technologies, i.e., using the Sn-based solder and Al bond wires.

- L5: The reliability assessment of SiC MOSFETs is conducted based on the mission profile sampled in one specific location, i.e., Arizona, USA. The failure probability figures may not be applicable for SiC-based 3L-ANPC inverters operating at other installation sites.

#### 1.4 Thesis Outline

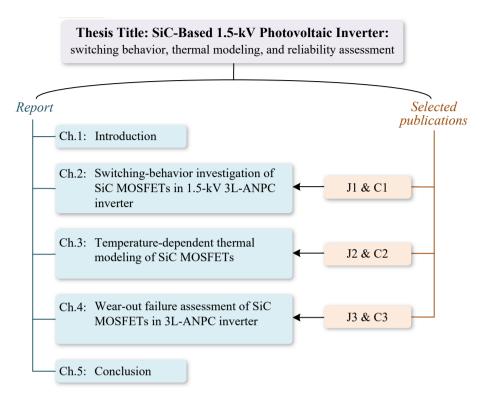

This Ph.D. dissertation consists of two parts: **Report** and **Selected Publications** (Journals: J, Conference: C), as illustrated in Fig. 1.10. The **Report** summarizes the research outcomes during the Ph.D. project, which is based on both journal and conference publications presented in the **Selected Publications** part. The **Report** is divided into five chapters, and the research objectives O1, O2, and O3 are discussed in Chapters 2, 3, and 4, respectively. A brief introduction of chapter contents and their corresponding publications are summarized as follows:

#### • Chapter 1 - Introduction

Chapter 1 reviews the background of the SiC device and its reliability challenges in several aspects for the 1.5-kV PV application. Then, the motivations (i.e., research questions and objectives) and limitations of this Ph.D. project are derived in Chapter 1.

#### Chapter 2 – Switching-behavior investigation of SiC MOSFETs in 1.5kV 3L-ANPC inverter

Aiming to identify and address the reliability challenges caused by unfavorable switching behaviors, a comprehensive investigation of switching performance for SiC MOSFET in 3L-ANPC inverters is conducted in Chapter 2. It is figured out that the inner SiC devices can suffer severe voltage overshoots, and multiple switching-oscillation components

**Fig. 1.10:** The outline of this Ph.D. thesis, and the relationship between the **Report** and **Selected Publications**. I: journal, C: conference.

are induced due to the 3L-ANPC topology. Then, the critical parasitic components are identified to achieve reliability improvements in SiC-based 1.5-kV 3L-ANPC inverters.

Based on publications: J1, C1

#### Chapter 3 – Temperature-dependent thermal modeling of SiC MOS-FET

This chapter focuses on improving the precision of the SiC MOSFET thermal model under the full temperature range. A temperature-dependent Cauer-type thermal model and its FEM based modeling methodology are proposed in Chapter 3. Moreover, a temperature-sensitive electrical parameter (TSEP) based transient-thermal-impedance characterization method is introduced to validate the proposed thermal model under the full temperature range of a SiC MOSFET module.

Based on publications: J2, C2

• Chapter 4 - Wear-out failure assessment of SiC MOSFETs in 3L-

#### **ANPC** inverter

In Chapter 4, a die-solder lifetime model for the SiC MOSFET module is extrapolated. A mission-profile-based wear-out assessment for the SiC-based 1.5-kV 3L-ANPC inverter is conducted based on the electrothermal model. The wear-out failure probabilities of different SiC MOSFETs are identified accordingly, and the reliability-critical devices under each commutation mode are identified.

Based on publications: J3, C3

#### • Chapter 5 - Conclusion

The contributions of this Ph.D. project are summarized, and future research perspectives are expected.

#### 1.5 List of Publications

The research dissemination during the Ph.D. study is shown below in the forms of journal papers and conference publications. Parts of them are used in the Ph.D. thesis, i.e., J1, J2, J3, C1, C2, and C3.

#### Journal Papers:

- J1. M. Chen, D. Pan, H. Wang, X. Wang, and F. Blaabjerg, "Investigation of Switching Oscillations for Silicon Carbide MOSFETs in Three-Level Active Neutral-Point-Clamped Inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. PP, no. 99, pp. 1-15, 2020, Early Access.

- J2. M. Chen, H. Wang, D. Pan, X. Wang, and F. Blaabjerg, "Thermal Characterization of Silicon Carbide MOSFET Module Suitable for High-Temperature Computationally-Efficient Thermal-Profile Prediction," IEEE J. Emerg. Sel. Topics Power Electron., vol. PP, no. 99, pp. 1-12, 2020, Early Access.

- J3. M. Chen, Z. Shen, H. Wang, X. Wang, and F. Blaabjerg, "Reliability Assessment of SiC MOSFETs in Three-Level Active Neutral-Point-Clamped Inverters Considering Die-Solder Degradation," *IEEE Trans. Power Electron.*, 2020, Status: to be Submitted.

#### **Conference Papers:**

- C1. M. Chen, D. Pan, H. Wang, X. Wang, F. Blaabjerg, and W. Wang, "Switching Characterization of SiC MOSFETs in Three-Level Active Neutral-Point-Clamped Inverter Application," in *Proc.* 2019 10<sup>th</sup> Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), May 2019, pp. 1793-1799.

- C2. M. Chen, H. Wang, F. Blaabjerg, X. Wang, and D. Pan, "A Temperature-Dependent Thermal Model of Silicon Carbide MOSFET Module for Long-Term Reliability Assessment," in *Proc. 2018 IEEE 4<sup>th</sup> Southern Power Electronics Conference (SPEC)*, Dec. 2018, pp. 1-7. (Best Paper Award)

#### 1.5. List of Publications

- C3. **M. Chen**, T. Zhu, D. Pan, H. Wang, X. Wang, and F. Blaabjerg, "Loss Analysis of SiC-Based Three-Level Active Neutral-Point-Clamped Inverters under Different Modulation Schemes," in *Proc.* 2020 IEEE 9<sup>th</sup> International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Status: In Press.

- M. Chen, H. Wang, H. Wang, F. Blaabjerg, X. Wang, and D. Pan, "Reliability Assessment of Hybrid Capacitor Bank Using Electrolytic- and Film-Capacitors in Three-Level Neutral-Point-Clamped Inverters," in *Proc.* 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2019, pp. 2826-2832.

- D. Pan, M. Chen, X. Wang, H. Wang, F. Blaabjerg, and W. Wang, "EMI Modeling of Three-Level Active Neutral-Point-Clamped SiC Inverter Under Different Modulation Schemes," in *Proc.* 2019 10<sup>th</sup> International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Busan, Korea (South), 2019, pp. 1-6.

- D. Pan, **M. Chen**, X. Wang, H. Wang, F. Blaabjerg, and W. Wang, "Precise Inductor Current Ripple Distribution of Three-Level Active Neutral-Point-Clamped Inverter," in *Proc.* 2019 10<sup>th</sup> International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Busan, Korea (South), 2019, pp. 1952-1959.

#### Chapter 1. Introduction

# **Chapter 2**

# Switching-Behavior Investigation of SiC MOSFETs in 1.5-kV 3L-ANPC Inverter

# 2.1 Brief Introduction

As discussed in Chapter 1.1.1, the 3L-ANPC topology exhibits a superior application potential in 1.5-kV PV systems compared to its counterparts, as a sufficient voltage margin and active loss and thermal distribution can be realized. Considering the merits of applying the 3L-ANPC topology and SiC devices, it is expected that using 3L-ANPC topology with SiC MOS-FETs will be a significant trend in future 1.5-kV PV systems [45]. However, fast-switching SiC MOSFETs in 3L-ANPC inverters can induce unfavorable switching behaviors, e.g., critical switching oscillations, voltage overshoots, and excessive switching losses, which engenders reliability challenges (i.e., over-voltage breakdown and partial discharge) to the SiC-based 3L-ANPC inverters.

Compared with the switching characteristics of SiC MOSFETs in discrete or half-bridge configurations [46–53], the switching behavior of SiC MOSFET in the 3L-ANPC inverter can be much more complicated, as line-frequency devices can induce a secondary switching loop. Furthermore, the 3L-ANPC inverter features three representative commutation types, i.e., the full mode, outer mode, and inner mode, and each mode exhibits distinguished switching behavior [J1].

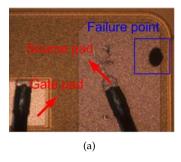

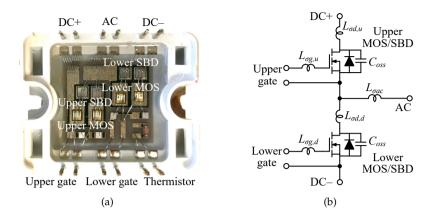

**Fig. 2.1:** SiC MOSFET module APTMC120AM55CT1AG (made by Microsemi). (a) Photograph from top-side. (b) Circuit diagram. Source: [J1].

Considering the aforementioned reliability challenges in terms of unfavorable switching behaviors, this chapter presents a comprehensive study of the switching characteristics of SiC MOSFETs in 1.5-kV 3L-ANPC inverters under the three representative commutation modes. The analyses are conducted based on a parasitic model extracted from finite-element-method (FEM) simulations. The theoretical findings are validated experimentally through double-pulse test (DPT) results.

# 2.2 Parasitic Modeling of SiC-based 3L-ANPC Phase-Leg

## 2.2.1 Half-bridge SiC MOSFET Module

The half-bridge SiC MOSFET module (APTMC120A-M55CT1AG made by Microsemi) is used as a forming element of the 3L-ANPC phase-leg. The device is rated at 1200 V and 42 A specified at the case temperature of 80 °C [70]. The top-side image and circuit diagram are depicted in Figs. 2.1(a) and 2.1(b), respectively. It is noted in Fig. 2.1(a) that two pairs of SiC MOSFET dies as well as their anti-parallel Schottky barrier diode (SBD) dies are packed in the half-bridge module, as noted to be the upper and lower MOS/SBDs in Fig. 2.1(b).

To connect SiC dies with module's electrical terminals, copper traces and bond wires are used in the module housing. This unavoidably introduces parasitic inductance and affects the commutation behaviors. Then, these parasitic-inductance components induced by copper traces and bond wires

| Category     |              | Symbol           | Inductance<br>(nH) | Resistance<br>(mΩ) |

|--------------|--------------|------------------|--------------------|--------------------|

| AC terminal  |              | $L_{\sigma ac}$  | 6.0                | 1.0                |

| Unnar davica | gate         | $L_{\sigma g,u}$ | 9.4                | 6.5                |

| Upper device | drain+source | $L_{\sigma d,u}$ | 10.0               | 3.7                |

| Lower device | gate         | $L_{\sigma g,d}$ | 12.0               | 8.7                |

| Lower device | drain+source | $L_{\sigma d,d}$ | 12.9               | 3.8                |

| PCB trace    |              | $L_{\sigma clp}$ | 5.2                | 1.0                |

|              |              | $L_{\sigma inv}$ | 34.1               | 5.6                |

| Busbar       |              | $L_{\sigma bus}$ | 3.6                | _                  |

**Table 2.1:** Values of parasitic components of the SiC MOSFET module (extracted at 1 MHz). Source: [J1].

are extracted using finite-element method (FEM) simulations (ANSYS/Q3D), as given in Fig. 2.1(b). The components  $L_{\sigma d,x}$  and  $L_{\sigma g,x}$  (x = u or d) represent the parasitic inductance located at the drain and gate terminals of the SiC MOSFET die, respectively. Moreover,  $L_{\sigma ac}$  is the parasitic inductance contributed by the module's AC terminal. These inductance values and their related series resistances are summarized in Table 2.1, and it can be seen that their values can vary (from 6.0 nH to 12.9 nH) due to geometry variations.

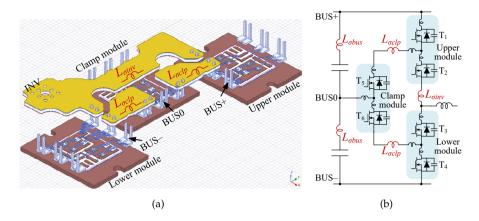

## 2.2.2 3L-ANPC Phase-Leg

Utilizing the aforementioned half-bridge SiC MOSFET module, a 3L-ANPC phase-leg is built, as illustrated in Fig. 2.2(a). Three half-bridge modules are used, which are denoted as the upper module, clamp module, and lower module. A four-layer PCB busbar is implemented to interconnect the three SiC MOSFET modules, and the parasitic circuit diagram demonstrating the layout is exhibited in Fig. 2.2(b). Accordingly, the 3L-ANPC phase-leg can withstand a dc-link voltage of 1.5 kV (with a sufficient voltage margin) using commercial 1.2-kV SiC MOSFETs.

Nevertheless, the PCB routing also brings excessive parasitic inductances to the ANPC phase-leg. More specifically, the components  $L_{\sigma clp}$  and  $L_{\sigma inv}$  denote the PCB inductance induced by the clamping branch and inversion branch, respectively, as they are marked in both Figs. 2.2(a) and 2.2(b). FEM simulations are also performed on the PCB busbar to extract the values of  $L_{\sigma clp}$  and  $L_{\sigma inv}$ , which are also exhibited in Table 2.1. It can be seen that the clamping branch features a low inductance value ( $L_{\sigma clp}$  = 5.2 nH). In contrast, the inversion branch features a relatively significant inductance value ( $L_{\sigma inv}$  = 34.1 nH) due to its longer geometry [as shown in Fig. 2.2(a)].

Moreover, another part of the parasitic inductance comes from the 1.5-kV capacitor bank. Both the capacitor's equivalent-series-inductance (ESL) and

**Fig. 2.2:** Layout and circuit diagram of the 3L-ANPC phase-leg. (a) Physical layout from top-side. (b) Simplified parasitic model–circuit diagram. Source: [J1].

| States | $T_1$ | <b>T</b> <sub>2</sub> | <b>T</b> <sub>3</sub> | $T_4$ | <b>T</b> <sub>5</sub> | <b>T</b> <sub>6</sub> |

|--------|-------|-----------------------|-----------------------|-------|-----------------------|-----------------------|

| _      | 0     | 0                     | 1                     | 1     | 1                     | 0                     |

| 0L2    | 0     | 0                     | 1                     | 0     | 0                     | 1                     |

| 0L1    | 1     | 0                     | 1                     | 0     | 0                     | 1                     |

| 0F     | 0     | 1                     | 1                     | 0     | 1                     | 1                     |

| 0U1    | 0     | 1                     | 0                     | 1     | 1                     | 0                     |

| 0U2    | 0     | 1                     | 0                     | 0     | 1                     | 0                     |

| +      | 1     | 1                     | 0                     | 0     | 0                     | 1                     |

|        |       |                       |                       |       |                       |                       |

**Table 2.2:** Switching states of the 3L-ANPC inverter [39].

the routing inductance of busbar should be considered in the loop. Hence, the PCB busbar is specifically designed to minimize the routing inductance [71]. To simplify, the capacitor's ESL and the busbar's routing inductance are unified as  $L_{\sigma bus}$  in Fig. 2.2(b), which is estimated as being 3.6 nH. Having the knowledge of parasitic components in the 3L-ANPC phase-leg, the three commutation modes and their corresponding switching circuits will be analyzed in the following sub-chapters.

# 2.3 Analyses of Commutation Modes

## 2.3.1 Switching States

The switching states will first be demonstrated before introducing the commutation modes of the 3L-ANPC inverter, as summarized in Table 2.2.

For the "-" state, switches T<sub>3</sub> and T<sub>4</sub> conduct the phase current to the neg-

ative bus-rail (i.e., BUS–). Meantime, the switch  $T_5$  also conducts to balance the voltage sharing between switches  $T_1$  and  $T_2$ . Similarly, switches  $T_1$ ,  $T_2$ , and  $T_6$  conduct during the "+" state to realize the positive bus-rail output. Moreover, by turning on switches  $T_3$  and  $T_6$ , the phase current can be conducted to the neutral point in both directions through the lower neutral path. The switch  $T_1$  can be in either ON or OFF state, leading to lower-clamping states "0L1" or "0L2", respectively. Analogously, the phase current can also be conducted via the upper neutral-path by turning on switches  $T_2$  and  $T_5$  simultaneously. The switch  $T_4$  can be in either ON or OFF state, leading to dual upper-clamping states, "0U1" or "0U2", respectively. Alternatively, the phase current can be conducted via both the upper and lower neutral paths by turning on switches  $T_2$ ,  $T_3$ ,  $T_5$ , and  $T_6$  simultaneously, which is known as the full state "0F".

Accordingly, different commutation options can take place between a single active state (either "+" or "-") and one clamping state ("0L1", "0L2", "0U1", "0U2", or "0F"). The three representative commutation modes (i.e., the full mode, outer mode, and inner mode) of the 3L-ANPC phase-leg will be analyzed as follows.

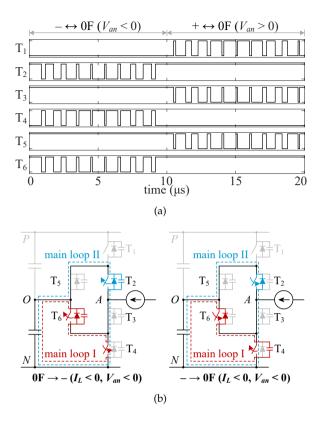

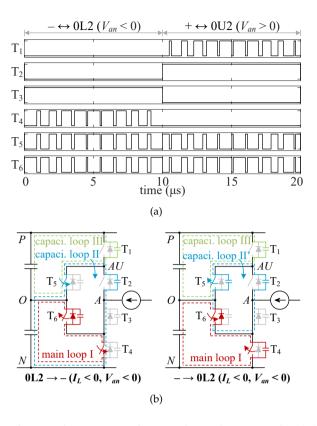

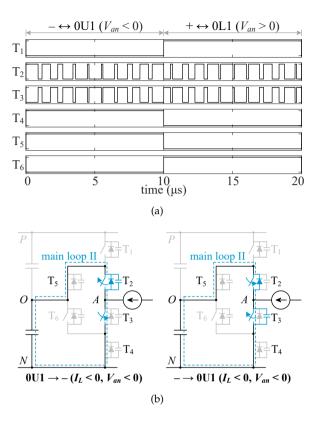

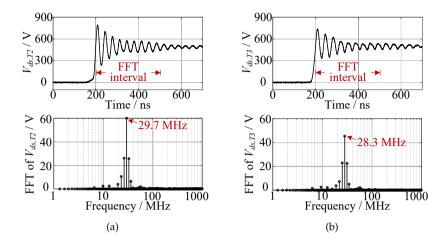

#### 2.3.2 Full-Mode Commutation

The full-mode commutation contains commutation transitions " $-\leftrightarrow 0$ F" and " $+\leftrightarrow 0$ F" for the negative and positive ac line-cycles, respectively. In short, the commutation transition for the negative line-cycle (i.e., " $-\leftrightarrow 0$ F") will be analyzed in this work. Figs. 2.3(a) and 2.3(b) present the gate signals and circuit diagrams during the full-mode commutation, respectively. During the negative line-cycle (i.e.,  $V_{an} < 0$ ), switch  $T_4$  is modulated to be sinusoidal, while switches  $T_2$  and  $T_6$  are switched complementarily. Accordingly, the phase current will commutate between the active phase-arm and both the upper and lower neutral paths, forming dual switching loops nominated as the main loops I and II in Fig. 2.3(b) [J1].

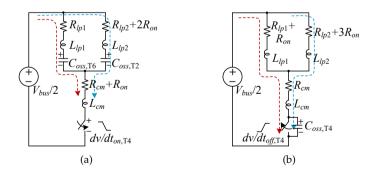

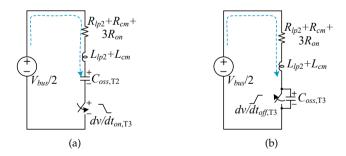

To reveal the commutation mechanisms, the equivalent switching circuits during full mode are investigated. Figs. 2.4(a) and 2.4(b) demonstrate the equivalent switching circuits during "0F  $\rightarrow$  -" and "-  $\rightarrow$  0F" (i.e., the turn-on and turn-off transients of T<sub>4</sub>), respectively. The components  $L_{lpx}$  and  $R_{lpx}$  represent the parasitic inductance and resistance of switching loops I and II (x = 1 and 2), respectively. The components  $L_{cm}$  and  $R_{cm}$  denote the common loop inductance and resistance enclosed by loops I and II. Besides,  $R_{on}$  and  $C_{oss,Tx}$  are the on-state resistance and output capacitance of SiC MOSFETs, respectively. The values of these parasitic components are summarized in Table 2.3, which are obtained based on the parasitic model.

During the transition "0F  $\rightarrow$  –" (i.e., the turn-on transient of T<sub>4</sub>), the output capacitance of T<sub>6</sub> and T<sub>2</sub> (i.e.,  $C_{oss,T6}$  and  $C_{oss,T2}$ ) are charged via main

Fig. 2.3: Gating voltages and commutation diagrams during the full mode. (a) Gating voltages. (b) Commutation diagrams for transitions "0F  $\rightarrow$  -" and "-  $\rightarrow$  0F". Source: [J1].

**Fig. 2.4:** Full-mode equivalent switching circuits. (a) Transition "0F  $\rightarrow$  -". (b) Transition " $\rightarrow$  0F". Source: [J1].

loops I and II, respectively. Multi-frequency switching oscillations will exist for the transition "0F  $\rightarrow$  -". Moreover, switch  $T_2$  is expected to experi-

#### 2.3. Analyses of Commutation Modes

| Symbol                | Inductance<br>(nH) | Resistance<br>(mΩ) | Capacitance<br>(pF) |

|-----------------------|--------------------|--------------------|---------------------|

| $L_{lp1}$ , $R_{lp1}$ | 24.1               | 5.8                | _                   |

| $L_{lp2}$ , $R_{lp2}$ | 78.2               | 18.8               | _                   |

| $L_{lp3}$ , $R_{lp3}$ | 40.8               | 10.4               | _                   |

| $L_{cm}$ , $R_{cm}$   | 22.5               | 4.8                | _                   |

| $R_{on}$              | _                  | 49                 | _                   |

| $C_{oss,Tx} \ (x=16)$ | -                  | -                  | 270 @ 500 V         |

Table 2.3: Switching-loop parasitic parameters. Source: [J1].

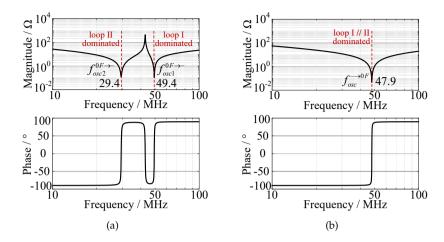

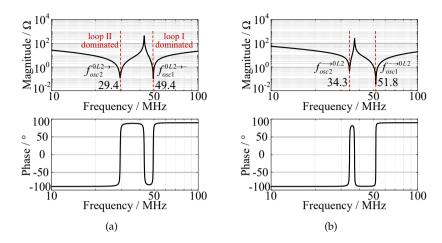

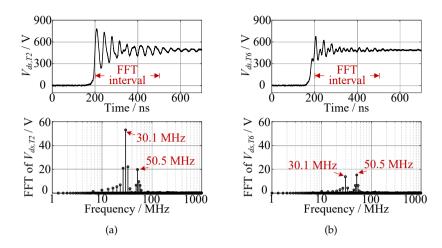

ence a more significant voltage overshoot than  $T_6$  as  $L_{lp2}$  is greater than  $L_{lp1}$ . Impedance characteristic of the equivalent switching circuit for "0F  $\rightarrow$  –" is depicted in Fig. 2.5(a). Dual switching-oscillation components with different frequencies are identified in Fig. 2.5(a) as  $f_{osc1}^{0F\rightarrow-}=49.4$  MHz and  $f_{osc2}^{0F\rightarrow-}=29.4$  MHz, which are dominated by loops I and II, respectively. The two oscillation frequencies can also be obtained by letting the imaginary part of the circuit impedance to be zero:

$$f_{osc1,osc2}^{0F\to -} = \frac{1}{2\pi} \cdot \sqrt{\frac{L_{lp1} + L_{lp2} + 2L_{cm} \pm \sqrt{\left(L_{lp1} - L_{lp2}\right)^{2} + 2L_{cm}^{2}}}{2C_{oss} \cdot \left(L_{lp1}L_{lp2} + L_{lp1}L_{cm} + L_{lp2}L_{cm}\right)}} . \tag{2.1}$$

During the transition " $-\to 0$ F" (i.e., when  $T_4$  is switched off), the output capacitance of  $T_4$  is charged by the load current. After  $T_4$ 's drain-source voltage reaches  $V_{bus}/2$ , the oscillation is triggered via the conduction path established by loops I and II, as shown in Fig. 2.4(b). It is expected that turning  $T_4$  off will not introduce severe switching-oscillation and voltage-overshoot issues since the total loop inductance is not significant considering the paralleling effect:

$$L_{tot}^{-\to 0F} = \frac{L_{lp1}L_{lp2}}{L_{lp1} + L_{lp2}} + L_{cm}$$

(2.2)

where,  $L_{tot}^{-\to 0F}$  is the equivalent loop inductance during "0F  $\to$  –", which is estimated to be 40.9 nH. Then, a single switching-oscillation component  $f_{osc}^{-\to 0F} = 47.9$  MHz is identified according to:

$$f_{osc}^{-\to 0F} = \frac{1}{2\pi \cdot \sqrt{L_{tot}^{-\to 0F} \cdot C_{oss}}} \,. \tag{2.3}$$

This is confirmed by the impedance analysis presented in Fig. 2.5(b).

**Fig. 2.5:** Impedance curves of equivalent switching circuits during the full-mode commutation. (a) Magnitude and phase characteristics for "0F  $\rightarrow$  -". (b) Magnitude and phase characteristics for " $-\rightarrow$  0F". Source: [J1].

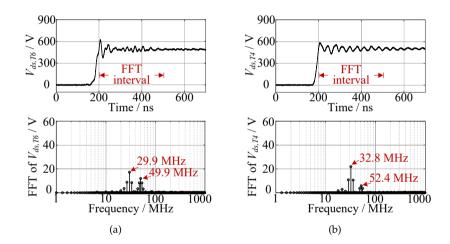

#### 2.3.3 Outer-Mode Commutation

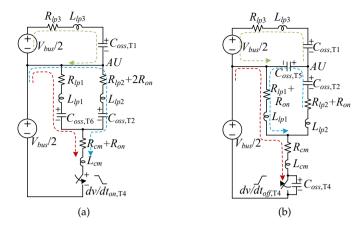

The outer mode is composed of commutations " $-\leftrightarrow 0L2$ " and " $+\leftrightarrow 0U2$ " for the negative and positive line periods, respectively. Figs. 2.6(a) and 2.6(b) illustrate the gate signals and commutation diagrams during the outer mode. During the negative line-cycle (i.e.,  $V_{an} < 0$ ), switch  $T_4$  is operated identically with its modulation pattern during the full-mode commutation, while only T<sub>6</sub> is switched complementary. Simultaneously, switch T<sub>5</sub> is modulated identically with T<sub>4</sub> to balance the voltage sharing between T<sub>1</sub> and T<sub>2</sub>. Accordingly, the phase current will commutate between the active phase-arm and its neighboring neutral path (e.g., the lower neutral path during  $V_{an} < 0$ ), and the loop I is found to be the major commutation loop [J1]. Furthermore, the switching operation of T<sub>5</sub> will charge and discharge the device output capacitance of T<sub>2</sub> and T<sub>1</sub>, which leads to double capacitive loops, i.e., the capacitive (capaci.) loop II (or II') and capaci. loop III in Fig. 2.6(b). Even though no actual phase current flows through these two capacitive loops, critical switching oscillations and voltage overshoots may be introduced in outer-mode switching circuits.

Figs. 2.6(a) and 2.6(b) illustrate the equivalent switching circuits of the outer transitions "0L2  $\rightarrow$  –" and "–  $\rightarrow$  0L2", respectively.  $R_{lp3}$  and  $L_{lp3}$  denote the parasitic resistance and inductance of the capacitive loop III, respectively. During the transition "0L2  $\rightarrow$  –", the output capacitances of  $C_{oss,T6}$  and  $C_{oss,T2}$  shall be charged via the main loop I and capacitive loop II, respectively. Additionally, the output capacitance of switch  $T_1$  (i.e.,  $C_{oss,T1}$ ) is

#### 2.3. Analyses of Commutation Modes

Fig. 2.6: Gating voltages and commutation diagrams during the outer mode. (a) Gating voltages. (b) Commutation diagrams for transitions " $0L2 \rightarrow -$ " and " $- \rightarrow 0L2$ ". Source: [J1].

also charged through the loop III owing to the conduction of switch  $T_5$ . Nevertheless, the capacitive loop III does not alter commutation behaviors of the main switches involved in the main loop I and capaci. loop II. Hence, the switching behavior of outer-mode commutation "0L2  $\rightarrow$  –" duplicates that of the transition "0F  $\rightarrow$  –", and the dual switching-oscillation components can be obtained by:

$$f_{osc1,osc2}^{0L2\to -} = f_{osc1,osc2}^{0F\to -}$$

$$\frac{1}{2\pi} \cdot \sqrt{\frac{L_{lp1} + L_{lp2} + 2L_{cm} \pm \sqrt{\left(L_{lp1} - L_{lp2}\right)^2 + 2L_{cm}^2}}{2C_{oss} \cdot \left(L_{lp1}L_{lp2} + L_{lp1}L_{cm} + L_{lp2}L_{cm}\right)}}$$

(2.4)

where,  $f_{osc1}^{0L2\to-}$  and  $f_{osc2}^{0L2\to-}$  are calculated to be 29.4 MHz and 49.4 MHz, respectively. This can also be validated through the impedance curve of the equivalent switching circuit exhibited in Fig. 2.8(a).

Fig. 2.7: Outer-mode equivalent switching circuits. (a) Transition "0L2  $\rightarrow$  -". (b) Transition " $\rightarrow$  0L2". Source: [J1].

The switching behavior for the transition " $-\to 0L2$ " is more complicated compared to others since the three loops, i.e., the main loop I, capacitive loops II', and III, all take effects. Even though, it is expected that there will not be significant switching oscillations and voltage overshoots on switch  $T_4$ , as the main loop I with relatively low inductance is actively involved. Fig. 2.8(b) shows the circuit impedance analysis of the transition " $-\to 0L2$ ", and dual oscillation components of  $f_{osc1}^{-\to 0L2}=34.3$  MHz and  $f_{osc2}^{-\to 0L2}=51.8$  MHz can be determined, which can also be obtained from the calculations:

$$f_{osc1,osc2}^{-\to 0L2} = \frac{1}{2\pi} \cdot \frac{1}{2} \cdot \sqrt{\frac{L_a^{-\to 0L2} \pm \sqrt{(L_a^{-\to 0L2})^2 - 24 \cdot (L_b^{-\to 0L2})^2}}{C_{oss} \cdot (L_b^{-\to 0L2})^2}}$$

(2.5)

where

$$L_a^{-\to 0L2} = 5L_{lv1} + 2L_{lv2} + 3L_{cm} \tag{2.6}$$

$$L_b^{-\to 0L2} = \sqrt{L_{lp1}L_{lp2} + L_{lp1}L_{cm} + L_{lp2}L_{cm}} . {(2.7)}$$

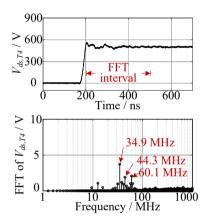

#### 2.3.4 Inner-Mode Commutation

The inner-mode commutation features commutation transitions " $-\leftrightarrow 0$ U1" and " $+\leftrightarrow 0$ L1" for the negative and positive line-cycles, respectively. Figs.

**Fig. 2.8:** Impedance curves of equivalent switching circuits during the outer-mode commutation. (a) Magnitude and phase characteristics for " $0L2 \rightarrow -$ ". (b) Magnitude and phase characteristics for " $- \rightarrow 0L2$ ". Source: [J1].

2.9(a) and 2.9(b) illustrate the gating voltages and commutation diagrams during the inner mode operation, respectively. It can be seen from Fig. 2.9(a) that only inner switches  $T_2$  and  $T_3$  are modulated to be sinusoidal, while the gating signals of other switches alter each half line-cycle. The phase current switches between  $T_2$  and  $T_3$ . Being different from the other two commutation modes, the inner mode involves a single switching loop, i.e., the main loop II shown in Fig. 2.9(b).

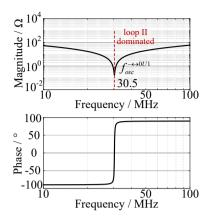

The equivalent switching circuits during inner-mode commutations "0U1  $\rightarrow$  –" and "–  $\rightarrow$  0U1" are demonstrated in Figs. 2.10(a) and 2.10(b), respectively, which resemble that of the two-level converter [50]. As a single switching loop is featured, only one switching-oscillation component with  $f_{osc}^{-\leftrightarrow 0U1}$  = 30.5 MHz can be identified for both inner transitions "0U1  $\rightarrow$  –" and "–  $\rightarrow$  0U1" in Fig. 2.11. This oscillation component can be identified by:

$$f_{osc}^{-\leftrightarrow 0U1} = \frac{1}{2\pi \cdot \sqrt{L_{tot}^{-\leftrightarrow 0U1} \cdot C_{oss}}}$$

(2.8)

$$L_{tot}^{-\leftrightarrow 0U1} = L_{lp2} + L_{cm} \tag{2.9}$$

where  $L_{tot}^{-\leftrightarrow 0U1}$  (= 100.7 nH) denotes the loop inductance in total for the innermode commutation. It can be expected that both the inner switches T<sub>2</sub> and T<sub>3</sub> will suffer dramatic switching oscillations and voltage overshoots since its switching loop is relatively long and contains four devices.

Fig. 2.9: Gating voltages and commutation diagrams during the inner mode. (a) Gating voltages. (b) Commutation diagrams for transitions "0U1  $\rightarrow$  -" and "-  $\rightarrow$  0U1". Source: [J1].

Fig. 2.10: Inner-mode equivalent switching circuits. (a) Transition "0U1  $\rightarrow$  -". (b) Transition " $\rightarrow$  0U1". Source: [J1].

A summary of the switching-loops involved and their corresponding oscillation frequencies for each commutation mode are presented in Table 2.4.

#### 2.4. Double-Pulse Test (DPT) and Result Analysis

Fig. 2.11: Impedance curves of equivalent switching circuits during the inner-mode commutation. Source: [11].

**Table 2.4:** Summary of commutation loops and associated frequencies of oscillations. Source: [J1].

| Commutation modes | Loops<br>involved | Symbols                                                                                                                        | Oscillation<br>frequencies     |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Full              | Main I II         | $f_{osc1}^{0F\rightarrow -}, f_{osc2}^{0F\rightarrow -}$                                                                       | 29.4 & 49.4 MHz                |

| Tun               | widht 1, 11       | $f_{osc}^{-	o 0F}$                                                                                                             | 47.9 MHz                       |

| Outer             | Main I and        | $f_{osc1}^{0L2 \rightarrow -}$ , $f_{osc2}^{0L2 \rightarrow -}$                                                                | 29.4 & 49.4 MHz                |

| Outer             | capaci. II, III   | $f_{osc1}^{- ightarrow 0L2}$ , $f_{osc2}^{- ightarrow 0L2}$                                                                    | 34.3 & 51.8 MHz                |

| Inner             | Main II           | $f_{osc}^{-\leftrightarrow 0U1}$                                                                                               | 30.5 MHz                       |

| Full Outer Inner  | capaci. II, III   | $f_{osc}^{OL2 \rightarrow OF}$ $f_{osc1}^{OL2 \rightarrow -}, f_{osc2}^{OL2 \rightarrow -}$ $f_{osc1}^{ODL2}, f_{osc2}^{ODL2}$ | 29.4 & 49.4 M<br>34.3 & 51.8 M |

Owing to the multiple loops, the full mode and outer mode are characterized by multiple switching-oscillation components. Nevertheless, the inner mode exhibits only one oscillation component owing to its single switching loop.

# 2.4 Double-Pulse Test (DPT) and Result Analysis

## 2.4.1 Test Setup Introduction

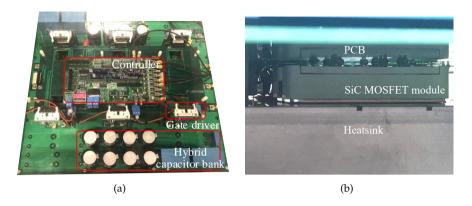

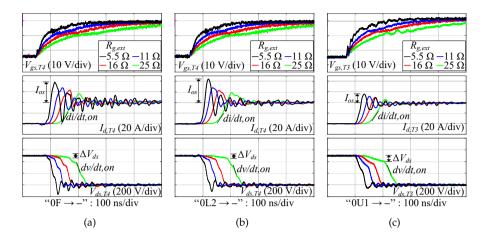

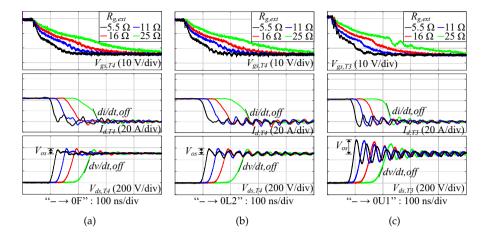

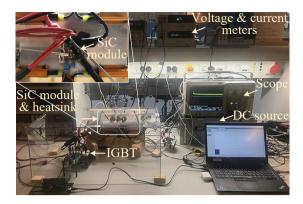

To validate the theoretical analyses presented in previous sub-chapters, DPTs are conducted on the 1.5-kV 3L-ANPC inverter prototype using SiC MOSFETs. The power stage is implemented according to the design demonstrated in Chapter 2.2. A top view of the 1.5-kV SiC-based 3L-ANPC inverter prototype is exhibited in Fig. 2.12.

The basic principle of the DPT is referred to [72]. In this work, the basic

Fig. 2.12: Photograph of the 1.5-kV SiC-based 3L-ANPC inverter protopype. (a) Top-view. (b) Lateral-view of the SiC MOSFET module. Source: [J1].

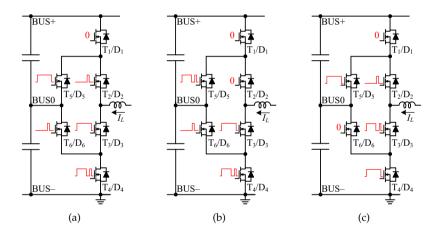

**Fig. 2.13:** DPT circuits of the 3L-ANPC phase-leg under the three representative commutation modes. (a) The full mode " $-\leftrightarrow 0$ F". (b) The outer mode " $-\leftrightarrow 0$ L". (c) The inner mode " $-\leftrightarrow 0$ U1".  $I_L$ : load current. Source: [J1].

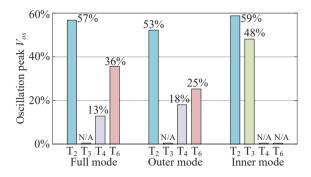

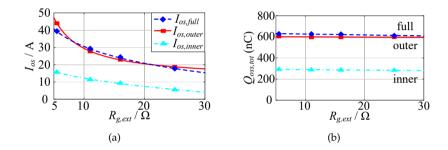

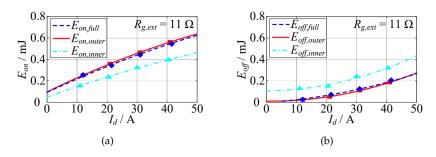

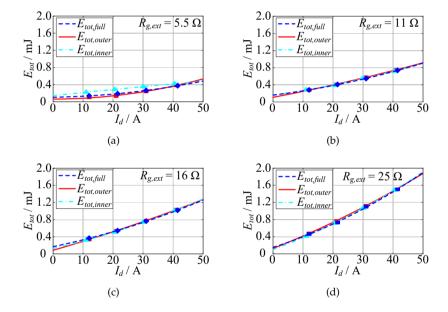

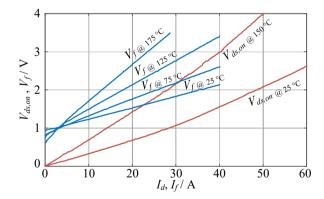

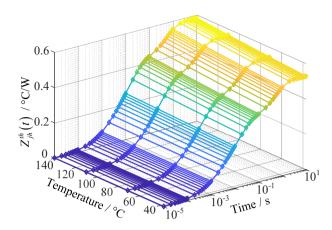

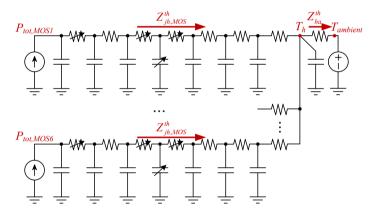

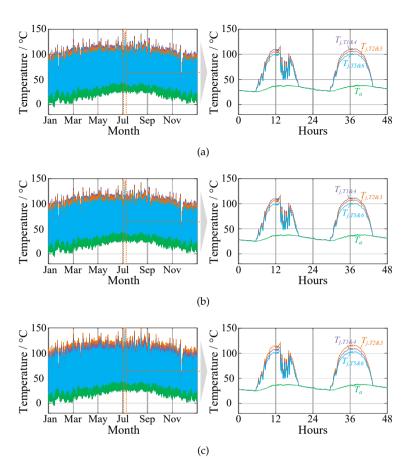

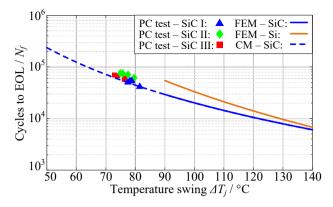

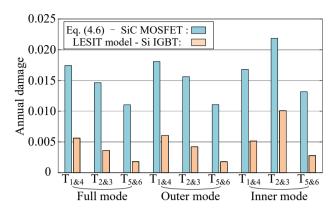

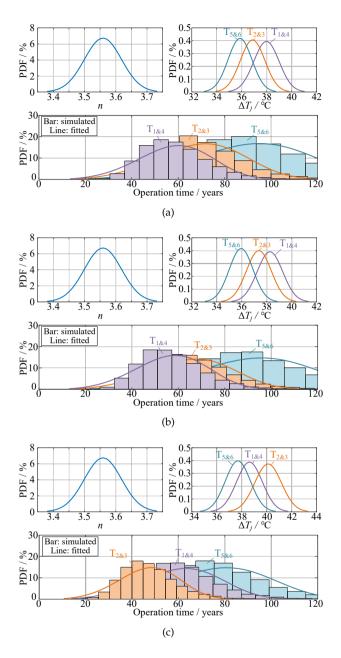

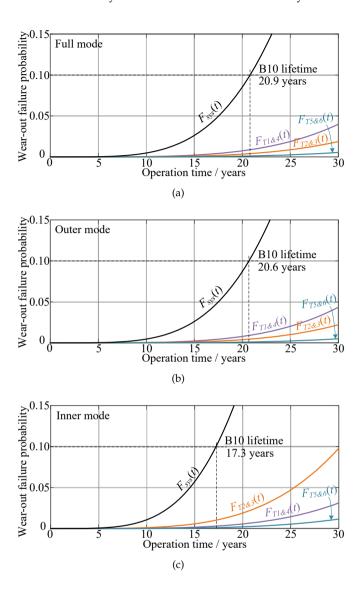

DPT principle is extended to 3L-ANPC inverters, where the gating signals are assigned to all six SiC MOSFETs of the 3L-ANPC phase-leg during the DPT. The configurations of gating pulses for full-mode, outer-mode, and inner-mode commutations during the tests are depicted in Figs. 2.13(a), 2.13(b), and 2.13(c), respectively [J1]. It is noted that the oscilloscope and the BUS-rail are grounded and commutation for negative cycles, i.e., "–  $\leftrightarrow$  0F", "–  $\leftrightarrow$  0L", and "–  $\leftrightarrow$  0U1" are studied.