### **Aalborg Universitet**

#### Parallel Connection of Silicon Carbide MOSFETs - Challenges, Mechanism, and Solutions

Li, Helong: Zhao, Shuang: Wang, Xiongfei: Ding, Lijian: Mantooth, Homer Alan

Published in:

**IEEE Transactions on Power Electronics**

DOI (link to publication from Publisher): 10.1109/TPEL.2023.3278270

Creative Commons License CC BY 4.0

Publication date: 2023

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Li, H., Zhao, S., Wang, X., Ding, L., & Mantooth, H. A. (2023). Parallel Connection of Silicon Carbide MOSFETs - Challenges, Mechanism, and Solutions. *IEEE Transactions on Power Electronics*, 38(8), 9731-9749. https://doi.org/10.1109/TPEL.2023.3278270

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Parallel Connection of Silicon Carbide MOSFETs—Challenges, Mechanism, and Solutions

Helong Li<sup>®</sup>, Senior Member, IEEE, Shuang Zhao<sup>®</sup>, Member, IEEE, Xiongfei Wang<sup>®</sup>, Fellow, IEEE, Lijian Ding<sup>®</sup>, Member, IEEE, and Homer Alan Mantooth<sup>®</sup>, Fellow, IEEE

Abstract-Power semiconductor devices are often connected in parallel to increase the current rating of the power conversion systems. However, due to mismatched circuit parameters or semiconductor fabrication discrepancies, the current of paralleled power semiconductor devices can be unbalanced, which potentially leads to accelerated aging and long-term reliability issues. The fast-switching speed of silicon carbide (SiC) devices aggravates this problem due to its higher sensitivity to parasitic parameters. Numerous efforts have been dedicated to analyzing and addressing the current imbalance issue of paralleling SiC devices. This article comprehensively summarizes and presents state-of-the-art research regarding the current imbalance in paralleled SiC devices. Degree of imbalance is proposed to comprehensively quantify the current mismatch. Starting with mechanism analysis, different types of current imbalance are categorized. Various device parameters and the package layout that impact the current distribution are investigated. The existing solutions including passive methods and active methods are concluded and categorized. This work also incorporates insight into the future development needs of high-power multichip SiC module packaging and driving technologies.

*Index Terms*—Current imbalance, multichip power module, parallel connection, SiC metal oxide semiconductor field effect transistor (MOSFET).

#### I. INTRODUCTION

SILICON carbide (SiC) metal oxide semiconductor field effect transistor (MOSFET) devices have been undergoing rapid development in the past decade and a fast growth rate is forecasted in the next two decades due to the booming market of electric vehicles (EVs). SiC MOSFET is considered a preferred option in the EV powertrain inverter application, not only by academia [1], [2] but also by the mainstream automotive industry [3], [4], [5], due to its low device losses, high system efficiency, and most importantly the lower cost at the vehicle level. As the

Manuscript received 11 November 2022; revised 7 April 2023; accepted 16 May 2023. Date of publication 22 May 2023; date of current version 21 June 2023. This work was supported in part by Anhui Natural Science Foundation under Grant 2208085QE164 and in part by 111 Project under Grant BP0719039. Recommended for publication by Associate Editor M. Nawaz. (Corresponding author: Shuang Zhao.)

Helong Li, Shuang Zhao, and Lijian Ding are with the School of Electrical and Automation Engineering, Hefei University of Technology, Hefei 230009, China (e-mail: helong.li@hfut.edu.cn; shuang.zhao@ieee.org; ljding@hfut.edu.cn).

Xiongfei Wang is with the KTH Royal Institute of Technology, 114-28 Stockholm, Sweden (e-mail: xiongfei@kth.se).

Homer Alan Mantooth is with the Department of Electrical Engineering, University of Arkansas, Fayetteville, AR 72701 USA (e-mail: mantooth@uark.edu). Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2023.3278270.

Digital Object Identifier 10.1109/TPEL.2023.3278270

automotive market is enormous and extremely cost-sensitive, SiC MOSFET technology is supposed to enjoy massive investment, rapid technology iteration [6], [7], [8], [9], [10], as well as significant further cost reduction in the next 5–10 years [11], [12], [13]. As a result of technology improvements and cost reduction, other industrial markets, e.g., photovoltaic, energy storage, charging infrastructure [14], traction [15], [16], and power grid, also expect to see a high-level market penetration of SiC devices [17], [18].

Compared with silicon (Si) insulated gate bipolar transistors (IGBTs), SiC MOSFETS s feature several device superiorities: fast switching speed, high operating temperature, high breakdown voltage [19], [20], and linear current-voltage (I-V) properties These device superiorities benefit from both SiC material properties and MOSFET unipolar device structure. The SiC wide band gap (WBG) material property enables higher temperature operation [21] and a higher critical electric field. Currently, the automotive market is pushing the highest operation junction temperature from 175 °C to 200 °C, which is not hurdled by SiC material but mainly by the MOSFET gate oxide reliability [22], [23], [24], [25]. The higher critical electric field of SiC material allows a much higher doping concentration and thinner drift layer, therefore, leading to much lower specific resistance in the drift region [26]. As a consequence, a 1.2 or 1.7 kV unipolar MOSFET device is easily achieved with SiC material but not quite feasible with Si material due to the high specific resistance of the drift region [27]. At present, up to 1.7 kV SiC MOSFET, the epitaxial layer thickness is approximately 1  $\mu$ m/100 V, while for Si IGBT, the Si wafer thickness is about 10 times larger. The unipolar MOSFET structure naturally leads to a fast-switching speed and a linear *I–V* property, compared to the bipolar IGBT structure [28], which is beneficial to conduction losses at light load applications. Last but not least, unipolar MOSFET structure also results in a lower switching loss compared to bipolar IGBTs due to the absence of tail current.

While enjoying the aforementioned device superiorities of SiC MOSFETS, there are still several challenges that are impeding SiC MOSFETS from walking over the last mile into massive market applications. From the perspective of material, SiC substrate and epitaxy still have multiple defective issues (micro-pipe, dislocation, stacking fault) [29]. The material defects further impact SiC device properties, yield, as well as the maximum device size of a single chip. The immaturity of manufacturing equipment, process, and device design for SiC devices also results in a larger inconsistency of SiC device parameters. From the device level,

Fig. 1. IGBT-high-current-module with paralleled IGBTs and diodes.

SiC MOSFETS are still confronting the challenges of gate oxide reliability and threshold voltage ( $V_{\rm th}$ ) instability [30], [31], [32]. Along with the fast-switching speed benefit, it also results in high sensitivity to circuit parasitics [33], [34], [35], which poses additional challenges to the design of SiC power semiconductor packaging, gate driver, and power loop circuit layout.

In addition to the SiC material immaturity, device parameters inconsistency, and fast switching speed, the current imbalance among the paralleled SiC MOSFETS has been a practical issue for the high current application of SiC MOSFETS. In normal operating conditions, the current imbalance could lead to thermal imbalance, as well as long-term reliability concerns. Due to the current imbalance, the design margin is normally set to a high level to avoid significant excessive stress on a single device, whereas it means less utilization of the device's full potential and a higher cost.

To tackle the challenges of paralleling SiC MOSFETS, there has been an increasing amount of research work in the last decade. The research works could be classified into two categories: the investigation of the current imbalance mechanism and current sharing methodologies. This article tries to put together stateof-the-art research regarding paralleling SiC MOSFETS comprehensively. First, it explains the reasons why paralleling SiC MOSFETS is more challenging than paralleling Si IGBTs, from material defects to process immaturity and applications: smaller single die size, larger device parameters inconsistency, and faster switching speed [36], [37], [38]. Second, it describes the current imbalance mechanism, including both static and dynamic imbalances. Third, the summary of current imbalance mitigation methodologies is presented. Among the methods, there are passive mitigation methods including circuit layout design optimization and device screening measures, and active methods such as utilizing external passives and active gate drivers [39]. Following the mitigation methods, it gives insights of circuit/multichip power module designs and the application of active gate driver control to minimize the current imbalance. The final section concludes the article.

#### II. CHALLENGES OF PARALLELING SIC MOSFETS

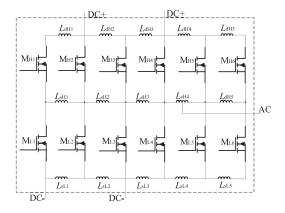

Paralleling power semiconductors are common at various levels.

At the die level, a SiC mosfet chip consists of thousands of semiconductor unit cells connecting in parallel via the drain/source metallization layers and gate runners.

Fig. 2. 6-inch wafer for the dies under different sizes. (a) 5  $\times$  5 mm die size. (b) 10  $\times$  10 mm die size.

- 2) At the module level, paralleling power semiconductor dies in multichip power modules or paralleling discrete devices is a common approach to achieve a high current rating in high-power applications. For instance, the power module in Fig. 1 has a 3600 A rated current with twenty-four IGBT chips and twelve diode chips in parallel.

- At the circuit level, for some high-current and high-power applications, parallel connection of multiple power modules is also employed to achieve the desired current level.

#### A. Challenges Associated With Small Dies of SiC MOSFETs

To further increase the current rating of a power device, it is desired to fabricate a larger die. However, several issues hinder the further increase of the die size. There is a design tradeoff between the die size and the yield. Due to SiC material defects and process imperfection, a larger die size normally means lower yield, which in turn results in a higher cost/Ampere. Fig. 2 compares the yield difference between  $5\times 5$  and  $10\times 10$  mm die size on a 6-inch wafer, which indicates that the yield is reduced significantly from 97.54% to 90.56% with the same defect density.

Compared to a Si IGBT, it is more challenging to make a large die for a SiC MOSFET. SiC substrate and epitaxial material have higher-level level defects than their Si counterparts due to their material properties [40]. In addition, the SiC MOSFET manufacturing equipment and process control are not as mature as those for Si IGBTs. At present, for lower voltage ( $\leq$ 750 V) Si IGBTs, the maximum current rating of a single IGBT chip is around 300 A with a die size of  $10 \times 12 \text{ mm}^2$ . While for the

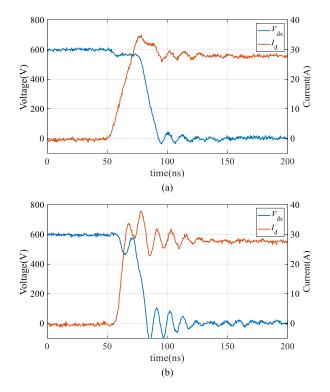

Fig. 3. Comparison of experimental switching waveform under different switching slew rates. (a) Waveform when di/dt is 2 A/ns. (b) Waveform when di/dt is 6 A/ns.

SiC MOSFETS of the same voltage level, the maximum current rating of a single SiC MOSFET die is approximately 100 A with a  $5 \times 5$  mm<sup>2</sup> die size. For the same current rating, it is necessary to parallel more SiC MOSFET dies than using Si IGBT. Since more dies are connected in parallel when using SiC MOSFET, the level of device electrical parameters' variations among the paralleled chips can increase. Therefore, it can lead to higher risks of current imbalance [41].

#### B. Challenges Due to Large Device Parameter Variations

Another challenge for paralleling SiC MOSFETS is also associated with the less maturity of the SiC MOSFET manufacturing process, which not only leads to low yield but also results in a larger variance of the device parameters. Datasheets of SiC MOSFETS specify high variation limits of the characteristics of the chip. The inconsistency of device parameters, e.g., ON-resistance ( $R_{\rm dson}$ ), transconductance ( $g_{\rm fs}$ ), and  $V_{\rm th}$  could lead to current imbalance during steady state and switching transient.

#### C. Challenges Due to Fast Switching Speed

In addition to the limited die size and device parameters' inconsistency, the fast-switching speed associated with the unipolar MOSFET structure also needs additional attention. Fast switching speed means high sensitivity to parasitic parameters since it can interact with the parasitic inductance and generate ringings, overshoot, and false-triggering. Fig. 3 is the waveform of the same circuit under different switching speeds [34] which shows that the ringing increases while the di/dt increases from

Fig. 4. Thermal performance with different distances among paralleled dies.

2 to 6 A/ns. In Fig. 3,  $V_{\rm ds}$  is the drain–source voltage and  $I_{\rm d}$  is the drain current.

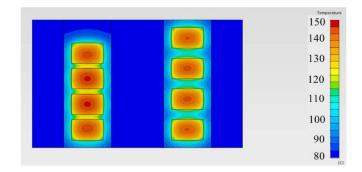

#### D. Challenges From Designing Multidiscipline of Multichip Power Modules

Another challenge for multichip power module design is its highly multidiscipline characteristic. The "optimal" design solution is often a compromised result between various aspects such as electrical, mechanical, thermal, environmental, reliability, and manufacturability [42]. In general, the design principles from different aspects are usually paradoxical. A simple example is that the distance between the paralleled chip is expected to be larger for better thermal performance, but smaller for better electrical performance [43]. Fig. 4 compares the thermal simulation of two groups of paralleled dies with different distances. It is apparent that the four MOSFETS with larger space, i.e., the right ones, have lower junction temperatures but larger stray inductance among the loops.

Apart from the tradeoff from different design principles, the performance from different aspects (e.g., electrical, thermal, mechanical) is highly coupled. For paralleled power devices, the current imbalance among paralleled devices may lead to mismatched thermal distribution, mechanical performance, and finally reliability issues. Consequently, there is no cure-all solution for the optimization of the current imbalance among the paralleled dies. Prior to mitigating the current imbalance, it is necessary to conduct an in-depth investigation into the mechanisms of the current imbalance.

## III. CATEGORIES OF CURRENT IMBALANCE AND POSSIBLE CONSEQUENCES

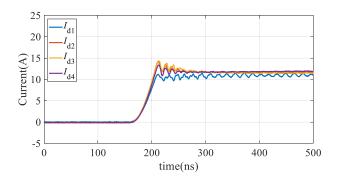

In general, the current imbalance can be categorized into two types: static and dynamic [44]. Static imbalance can lead to mismatched conduction losses while dynamic imbalance can lead to unequal switching losses and  $I_d$  peak which are pertinent to the current stress. Herein, Zhao's degree of imbalance concept is introduced.

#### A. Static Degree of Imbalance

Static imbalance is usually induced by the mismatched ON-state resistance  $R_{\rm dson}$ . For power MOSFETS, the current is proportional to the conductance. The current on the kth MOSFET  $I_{\rm d}k$

Fig. 5. Experimental waveform of steady-state current imbalance.

is determined by its ON-state-resistance  $R_{\text{dson }k}$  as given in the following:

$$I_{dk} = \frac{1/R_{dsonk}}{1/R_{dson1} + 1/R_{dson2} + \dots 1/R_{dson-n}} I_{o}.$$

(1)

In (1), n is the total number of MOSFETS in parallel and  $I_0$  is the total load current. Herein,  $I_0 = I_{\rm d1} + I_{\rm d2} + \dots I_{\rm dn}$ . A typical waveform of two parallel-connected MOSFETS with the same model number is shown in Fig. 5. It still shows a slightly mismatched static current.

For paralleled MOSFETS,  $V_{\rm ds}$  on each MOSFET is equal. According to  $V_{\rm ds}=R_{\rm dson}I_{\rm d}$ , the MOSFET with lower  $R_{\rm dson}$  has higher current  $I_{\rm d}$ . Because conduction loss can be calculated with  $P_{\rm cond}=V_{\rm ds}I_{\rm d}$ , the MOSFET with lower  $R_{\rm dson}$  withstands higher conduction losses and junction temperature. The static imbalance is usually not catastrophic due to the positive temperature coefficient of  $R_{\rm dson}$ .

To quantify the current imbalance, in this article, *the Degree* of *Imbalance* (*DoI*) is introduced. *s*DoI which denotes the DoI for static current can be calculated with the following:

$$sDoI = \sum |I_{dj} - I_{dk}| |I_{d1} - I_{d2}| + |I_{d1} - I_{d3}| + |I_{d1} - I_{d4}| + \dots |I_{d1} - I_{dn}| + |I_{d2} - I_{d3}| + |I_{d2} - I_{d4}| + \dots |I_{d2} - I_{dn}| + \dots \dots |I_{dk} - I_{dk+1}| + \dots |I_{dk} - I_{dn}| + \dots \dots = \frac{+ |I_{dn-1} - I_{dn}|}{(n-1)(|I_{d1}| + |I_{d2}| + \dots |I_{dn}|)}.$$

$$(2)$$

sDoI is an indicator between zero and one. In (2), k and j denote the kth and jth paralleling route respectively and  $j \neq k$ . n means the number of MOSFETS in parallel. It is an integer no less than 2, i.e.,  $n \geq 2$ . The scenario when sDoI equals one is the most extreme condition since all  $I_0$  is withstood by a single MOSFET and the  $I_d$  of the other MOSFETS is zero. When sDoI equals zero, the  $I_d$  on all MOSFETS is completely matched.

#### B. Dynamic Degree of Imbalance

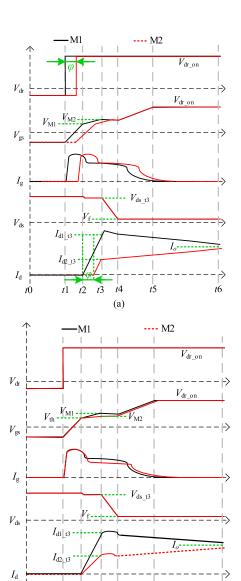

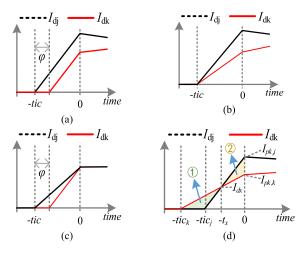

Dynamic imbalance occurs due to the mismatching switching trajectory which is brought by various factors such as mismatched stray inductance, gate resistance  $R_{\rm g}$ ,  $V_{\rm th}$ , etc. [45]. Theoretically, the dynamic imbalance can be equivalent to the combinations of two special cases: 1) synchronous gate signal

Fig. 6. Turn-ON process of the two special cases of parallel-connected MOSFETS. (a) Asynchronous gate signal and same switching slew rate. (b) Synchronous gate signal and different slew rate [47].

(b)

t2 t3

t5

t6

and different slew rate; and 2) Asynchronous gate signal and same slew rate. The turn-ON switching profiles of the two special cases are plotted in Fig. 6. M1 and M2 are the two MOSFETS under test. Since the  $V_{\rm ds}$  of the paralleled MOSFETS is similar, the switching loss is dominated by  $I_{\rm d}$ .

Fig. 6(a) shows the turn-ON process trajectory with an asynchronous gate signal and the same switching slew rate. In this case, two MOSFETS have the same switching slew rate while the gate signal of M1 lags behind M2 for  $\varphi$ . The gate signal lag is usually introduced by the gate driver propagation delay [47].  $V_{\rm dr}$  is the output voltage of the gate driver. Since the turn-ON signal of M1 is earlier than M2, the peak current of M1, i.e.,  $I_{\rm d1-t3}$ , is different from that of M2  $I_{\rm d2-t3}$ . It is apparent that M1 undergoes a higher current than M2. The difference between  $I_{\rm d1-t3}$  and  $I_{\rm d2-t3}$  will increase as the delay time  $\varphi$  increases.

Fig. 7. Turn-OFF process of the two parallel-connected MOSFETs [47].

If the overshoot current is neglected,  $I_{\rm d1\_t3} + I_{\rm d2\_t3} = 2I_{\rm o}$ . The most unbalanced condition occurs when  $I_{\rm d2\_t3}$  is zero. In this situation, M2 operates in soft turn-ON mode. All the current stress and energy loss are undergone by M1.

Fig. 6(b) shows the turn-ON process trajectory with a synchronous gate signal but a different switching slew rate. In this situation, the  $I_{\rm d}$  of M1 and M2 start to rise at the same time when the while the switching transient of M1 is faster than M2. The different slew rate is introduced by the mismatching electrical parameters of the devices such as  $C_{\rm gd}$ ,  $V_{\rm th}$ , etc. Since M1 switches faster, it withstands higher current stress and overshoot.

The analysis of the turn-OFF process is similar. The two MOSFETS turn OFF with the same switching slew rate while M2 lags behind M1 for  $\varphi$  as plotted in Fig. 7. During the turn-OFF process, M1 withstands less current stress and it operates under quasi-soft-turn-OFF mode. Accordingly, more switching loss is undergone by M2.

Similar to sDoI, the concept of dynamic degree of imbalance, i.e., dDoI, is introduced as given in (3). Generally, the two variables-of-interest during switching are di/dt and peak  $I_{\rm d}$ . Since the  $V_{\rm ds}$  is similar, peak  $I_{\rm d}$  indicates the safe-operation while both di/dt and peak  $I_{\rm d}$  determine the switching loss. If the di/dt and peak  $I_{\rm d}$  of the parallel-connected MOSFETS are equal, it can be claimed that these MOSFETS are balanced. dDoI can be defined with the following:

$$\begin{split} d \mathrm{DoI} &= \frac{\sum_{j,k=1}^{n} \int_{0}^{tic} (|I_{\mathrm{d}j} - I_{\mathrm{d}k}|) \mathrm{d}t}{(n-1) \sum_{j=1}^{n} \int_{0}^{tic} |I_{\mathrm{d}j}| \mathrm{d}t} = \\ & \int_{0}^{tic} \begin{pmatrix} |I_{\mathrm{d}1} - I_{\mathrm{d}2}| + |I_{\mathrm{d}1} - I_{\mathrm{d}3}| + |I_{\mathrm{d}1} - I_{\mathrm{d}4}| + \dots |I_{\mathrm{d}1} - I_{\mathrm{d}n}| \\ & + |I_{\mathrm{d}2} - I_{\mathrm{d}3}| + |I_{\mathrm{d}2} - I_{\mathrm{d}4}| + \dots |I_{\mathrm{d}2} - I_{\mathrm{d}n}| \\ & & + \dots \dots \\ & & |I_{\mathrm{d}k} - I_{\mathrm{d}k+1}| + \dots |I_{\mathrm{d}k} - I_{\mathrm{d}n}| \\ & & + \dots \dots \\ & & + |I_{dn-1} - I_{dn}| \end{pmatrix} \mathrm{d}t \end{split}$$

Fig. 8. Turn-ON process of the two paralleled MOSFETs. (a) Nonintersect conditions 1: asynchronous gate signal and same switching slew rate. (b) Nonintersect conditions 2: synchronous gate signal and different switching slew rate. (c) Nonintersect conditions 3: asynchronous gate signal and different switching slew rate. (d) Intersect condition.

In (3), k and j denote the kth and jth paralleling route, respectively, and  $j \neq k$ .  $I_{\rm d1} - I_{\rm dn}$  denote the  $I_{\rm d}$  of each MOSFET during current changing substage. tic is the duration of drain current rising, i.e., t2 to t3 in Fig. 6(a). For the turn-OFF process, tic starts at the beginning of  $V_{\rm ds}$  rising and ends when the total  $I_{\rm d}$  reduces to zero, i.e., t10 to t13 in Fig. 7.

Considering that the integral is usually difficult to be calculated, (3) can be further simplified. Generally, the current changing process can be linearized to a first-order function [48]. In this case, there are three critical indicators: di/dt, tic, and start moment. First, the denominator can be simplified as given in the following:

$$\int_0^{tic} (|I_{d1}| + |I_{d2}| + \dots + |I_{dn}|) dt$$

$$= 0.5 \left( \left| \frac{\mathrm{d}i_1}{\mathrm{d}t} \right| tic_1^2 + \left| \frac{\mathrm{d}i_2}{\mathrm{d}t} \right| tic_2^2 \dots + \left| \frac{\mathrm{d}i_n}{\mathrm{d}t} \right| tic_n^2 \right). \tag{4}$$

Second, the simplified calculation of nominator, i.e.,  $\int_0^{tic} |I_{\mathrm{d}k} - I_{\mathrm{d}j}| \mathrm{d}t$  is based on the practical condition. Generally, there are two basic conditions: the intersect condition and the nonintersect condition.

Fig. 8(a)–(c) show the current waveform of three typical types of nonintersect conditions which is defined when the  $I_{\rm dj}$  and  $I_{\rm dk}$  do not intersect in the range of 10%–90% of peak current. In this condition, the integral value can be easily obtained with

$$\int_{0}^{tic} (|I_{dj} - I_{dk}|) dt$$

$$= \frac{1}{2} \left\| \frac{di_{j}}{dt} tic_{j}^{2} - \frac{di_{k}}{dt} tic_{k}^{2} \right\|.$$

(5)

Fig. 8(d) shows the current waveform of intersect condition. In this condition, the current  $I_{\rm d}_j$  and  $I_{\rm d}_k$  intersect at the point (- $t_{\rm x}$ ,  $I_{\rm dx}$ ) which locates in the range of 10% to 90% of peak current.

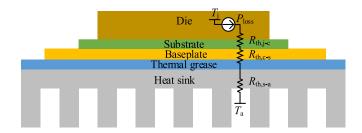

Fig. 9. Thermal network of a bottom-side cooling power device [1].

Peak currents of  $I_{\mathrm{d}j}$  and  $I_{\mathrm{d}k}$  are denoted by  $I_{pk,j}$  and  $I_{pk,k}$ , respectively. The calculation of  $\int_0^{tic} (|I_{\mathrm{d}j} - I_{\mathrm{d}k}|) \mathrm{d}t$  is actually the area of region ① and ② in Fig. 8(d). It can be calculated with the following:

$$\int_{0}^{tic} (|I_{dj} - I_{dk}|) dt$$

$$= \frac{1}{2} (tic_{j} - tic_{k}) I_{dx} + \frac{1}{2} t_{x} (I_{pk,j} - I_{pk,k}).$$

(6)

$t_x$  and  $I_{\mathrm{d}x}$  can be inspected from the oscilloscope. It can be also calculated with  $\mathrm{d}i/\mathrm{d}t$  and the current rising time of each current as given in the following:

$$\begin{cases} t_x = \frac{\frac{\mathrm{d}i_j}{\mathrm{d}t}tic_j - \frac{\mathrm{d}i_k}{\mathrm{d}t}tic_k}{\mathrm{d}i_j/\mathrm{d}t - \mathrm{d}i_k/\mathrm{d}t} \\ I_{\mathrm{d}x} = \frac{\mathrm{d}i_j}{\mathrm{d}t} \frac{\mathrm{d}i_k}{\mathrm{d}t} \frac{tic_k - tic_j}{\mathrm{d}i_j/\mathrm{d}t - \mathrm{d}i_k/\mathrm{d}t}. \end{cases}$$

(7)

#### C. Thermal Imbalance and Long-Term Reliability

The current mismatch can lead to a thermal imbalance and raise long-term reliability concerns. It can be analyzed as below. The total power loss of a MOSFET can be divided into the conduction loss and switching loss as given in the following [49]:

$$P_{\text{loss}} = \frac{V_{\text{ds}}^2}{R_{\text{dson}}} + f_{\text{sw}} \int V_{\text{ds}} I_{\text{d}} dt.$$

(8)

From (8), the static current imbalance can lead to mismatched conduction loss which is proportional to the steady-state  $I_d$  of the power device. Also, the switching power loss is proportional to the switching frequency and the switching energy loss. The equivalent thermal network of a bottom-side cooling power device can be drawn as shown in Fig. 9 [1].

In Fig. 9,  $P_{\rm loss}$  denotes the total power loss of the SiC MOSFET.  $R_{\rm th,j-c}$  is the thermal resistance and capacitance from the junction to the case, respectively, which can be found in the  $Z_{\rm th}$  plot of the datasheet, while  $R_{\rm th,c-s}$  and  $C_{\rm th,c-s}$  denote those from the case to the surface of the heatsink. s-a denotes the surface to the ambient thermal impedance.  $T_{\rm a}$  is the ambient temperature of the system and  $T_{\rm c}$  is the temperature of the case. Thus, the calculation of junction temperature  $T_{\rm j}$  of the SiC device can be referred to the following:

$$T_{\rm j} = P_{\rm loss} \left( R_{\rm th, j-c} + R_{\rm th, c-s} + R_{\rm th, s-a} \right) + T_{\rm a}.$$

(9)

From (9),  $T_{\rm j}$  is proportional to the power loss. Both the mismatching  $R_{\rm th}$  and power loss on the parallel-connected MOSFETS can lead to the  $T_{\rm i}$  difference which has a significant

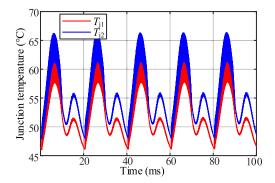

Fig. 10.  $T_{\rm j}$  profile of paralleled SiC MOSFETs in a PFC.

Fig. 11. Relationship between the number of life cycles and junction temperature

impact on lifetime. A simulation study is conducted with a power factor correction (PFC) converter. Two paralleled SiC MOSFETS with different  $R_{\rm dson}$  are utilized and their  $T_{\rm j}$  profiles are shown in Fig. 10. The normal operation of an inverter can inevitably introduce a  $T_{\rm j}$  cycle due to the sinusoidal load current. This results in power loss fluctuation and finally the junction temperature fluctuation, i.e.,  $\Delta T_{\rm j}$ .

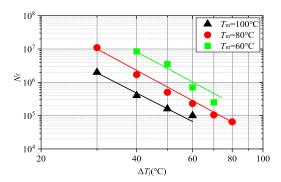

Most failures of the power devices occur on the mechanical parts due to periodical expansion/shrinking. Specifically, the coefficients of thermal expansion of the semiconductor dies, bonding wire, solder and direct bonding copper layer are different [50]. The solder layer between the die and direct bond copper layer and the bonding wires undergo a large periodical force brought by the temperature cycling fluctuation. The accumulated fatigue can result in delamination of the die attach and bonding wire damage [51]. The lifetime power cycles of a power device  $N_f$  versus  $\Delta T_j$  can be quantified with the Coffin–Manson model in the following and plotted in Fig. 11 [52]:

$$N_f = A \cdot (\Delta T_j)^{\alpha} \cdot e^{E_a/(k_B \cdot T_m)}. \tag{10}$$

In (10), A,  $\alpha$ , and  $E_{\rm a}$  are defined as the coefficients obtained from experimental results, and  $k_B$  which is Boltzmann's constant equals to  $1.38 \times 10^{-23}$  J/K.

When the current imbalance occurs, the mismatched power loss can lead to different  $T_{\rm j}$  on the paralleled MOSFETS [53]. Finally, the MOSFETS that withstand larger  $\Delta T_{\rm j}$  in paralleled devices age first and the reliability of the system reduces [54]. Therefore, the current imbalance can speed up the aging process of a system with paralleled devices [55].

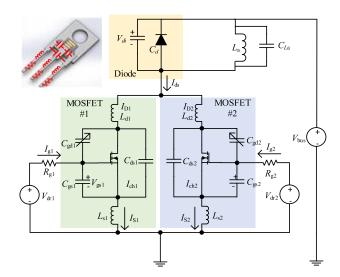

Fig. 12. Equivalent circuit of the parallel-connected power devices.

#### IV. MECHANISM OF CURRENT IMBALANCE

Prior to proposing current sharing strategies, an investigation of the current imbalance mechanism should be conducted. Various parameters that induce the current distribution are usually coupled. This section will discuss the impact of pertinent parameters on the current distribution.

#### A. Pertinent Parameters

The equivalent circuit of the paralleled power devices is given in Fig. 12 [45]. The parameters in Fig. 12 which have an impact on the current distribution can be categorized into three types: device parameters [55], circuit parameters [56], and status indicators. The intrinsic electric parameters, which are the parameters of the die, are generally determined amid the die fabrication process [57]. It includes the junction capacitance [58], internal gate resistance, transconductance, etc. The external parameters include the parasitic inductance introduced by the package stray, bonding wires, PCB, and cables [59]. The status indicators denote the parameters pertinent to statuses such as  $T_{\rm j}$ , humidity, load current, and dc bus voltage. Some typical parameters can be summarized as shown in Table I. Some equivalent parameters are highly coupled such as  $V_{\rm th}$  versus  $R_{\rm dson}$ , and  $T_{\rm j}$  versus  $R_{\rm dson}$  [60]. Also, some parameters only impact one type of current imbalance. For instance,  $R_{\rm dson}$  only affects static current distribution while  $C_{\mathrm{gs}}$  only influences dynamic distribution. Some parameters such as  $V_{\rm gs}$  and  $T_{\rm j}$  can affect both static and dynamic current distribution.

#### B. Device Parameters Variations

1)  $R_{dson}$  Variation: The current on the two paralleled MOSFETS is proportional to the conductance of the MOSFET as given in (1) and their  $R_{dson}$  can be calculated with the following:

$$\begin{cases}

R_{\rm ds1\_on} = \frac{L}{W\mu_n C_{ox}(V_{\rm gs1} - V_{\rm th1})} \\

R_{\rm ds2\_on} = \frac{L}{W\mu_n C_{ox}(V_{\rm gs2} - V_{\rm th2})}.

\end{cases}$$

(11)

TABLE I

TYPICAL PARAMETERS THAT AFFECT THE CURRENT DISTRIBUTION ON

PARALLEL-CONNECTED MOSFET

| Category             | Variable      | Definition               |

|----------------------|---------------|--------------------------|

| Device<br>parameters | $V_{ m th}$   | Gate threshold voltage   |

|                      | $C_{ m gd}$   | Gate-drain capacitance   |

|                      | $C_{ m gs}$   | Gate-source capacitance  |

|                      | $C_{ m ds}$   | Drain-source capacitance |

|                      | gs            | Transconductance         |

|                      | $R_{ m dson}$ | On-state resistance      |

| Circuit parameters   | $V_{ m dr}$   | Driver voltage           |

|                      | $L_{ m d}$    | Drain inductance         |

|                      | $L_{ m s}$    | Source inductance        |

|                      | $L_{ m g}$    | Gate inductance          |

|                      | $R_{ m g}$    | Gate resistance          |

| Status indicators    | $T_{i}$       | Junction temperature     |

|                      | $V_{ m DC}$   | DC-link voltage          |

|                      | $I_{o}$       | Load current             |

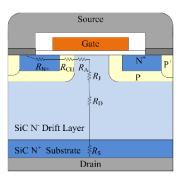

Fig. 13. Components breakdown of SiC MOSFETs  $R_{dson}$ .

It is straightforward that the MOSFET with lower  $R_{\rm dson}$  shares more current than the one with higher  $R_{\rm dson}$ . Generally, higher  $V_{\rm gs}$  can reduce  $R_{\rm dson}$ , and this is also similar for the third-quadrant mode as claimed in [61]. To better understand the mechanism of static imbalance, an in-depth analysis of  $R_{\rm dson}$  should be conducted. As shown in Fig. 13, the  $R_{\rm dson}$  of a SiC MOSFET consists of various components.

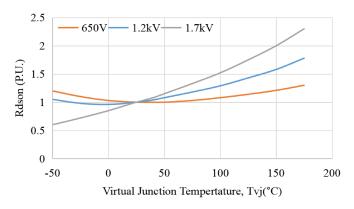

Among the several components of  $R_{\rm dson}$  in Fig. 13, the channel resistance ( $R_{\rm CH}$ ) has a negative temperature coefficient, while the drift region resistance ( $R_{\rm D}$ ) has a positive temperature coefficient. For SiC MOSFETS, higher breakdown voltage normally requires a thicker drift layer, which results in different  $R_{\rm dson}$  over temperature behavior. The curves of  $R_{\rm dson}$  versus  $T_{\rm j}$  of several commercialized SiC MOSFETS under different voltage ratings are plotted in Fig. 14. Most SiC MOSFETS on the market have positive temperature coefficients of  $R_{\rm dson}$  which enable self-balancing of the static currents [62].

For a 650 V SiC MOSFET,  $R_{\rm CH}$  can account for more than 50% of the total  $R_{\rm dson}$ , while in a 1.7 kV SiC MOSFET, the proportion of  $R_{\rm CH}$  can be reduced to be lower than 30%. Therefore, paralleling higher voltage SiC MOSFETS tends to have a stronger self-balancing effect due to the higher temperature coefficient of  $R_{\rm dson}$ .

In terms of the temperature coefficient of  $R_{\rm dson}$ , there is a tradeoff between the conduction loss and the feasibility of parallel connection. A higher ratio of positive temperature coefficient is beneficial to current balancing for parallel connection

Fig. 14. Normalized  $R_{dson}$  versus virtual junction temperature.

Fig. 15.  $V_{\rm th}$  of multiple SiC MOSFETs.

while it leads to a higher conduction loss at elevated junction temperature.

For static current imbalance, the characterization of paralleling SiC MOSFETS is discussed in [63] with  $R_{\rm dson}$  variations, which could see the small current difference between the two paralleled SiC MOSFETS with  $R_{\rm dson}$  mismatch.

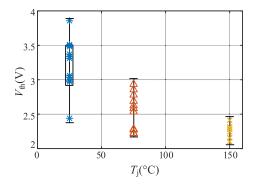

2)  $V_{th}$  Variation:  $V_{th}$  variation can be introduced in the manufacturing process of the device. As demonstrated in [64],  $V_{th}$  can also be shifted under long-term gate stress. Therefore, investigating the impact of  $V_{th}$  variation on the current imbalance is critical. Twenty SiC MOSFETS are chosen for testing with a curve tracer. The  $V_{th}$  curves are plotted in Fig. 15.

$V_{\rm th}$  variation has a major impact on the dynamic switching current distribution and  $R_{\rm dson}$  variation mainly affects the static current sharing [65], which could also be explained with the following equation:

$$I_{\rm d} = g_{\rm fs} (V_{\rm gs} - V_{\rm th})^2.$$

(12)

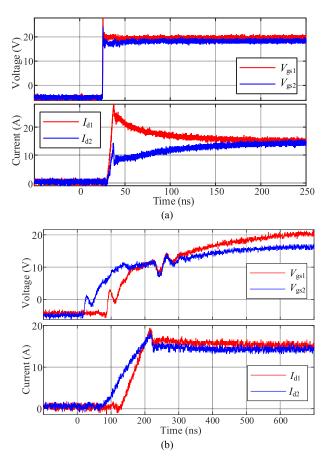

As shown in Fig. 16, in paralleled MOSFETS, the device with lower  $V_{\rm th}$  has faster turns-ON and slower turns-OFF, which leads to both higher turn-ON and turn-OFF losses. This happens because it withstands more current stress. Consequently, among the paralleled devices, the  $T_{\rm j}$  of the device with lower  $V_{\rm th}$  can be higher due to higher switching losses. Moreover, the negative temperature coefficient of  $V_{\rm th}$  can lead to a vicious circle and finally a catastrophic result [66].

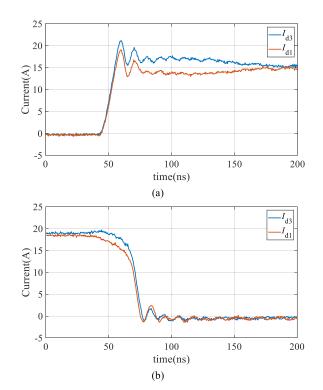

Fig. 16. Experimental dynamic current distribution with  $V_{\rm th}$  variation. (a) Turn-ON process. (b) Turn-OFF process.

Compared with the self-balancing feature of  $R_{\rm dson}$  variation among paralleled devices, this self-aggravating feature of  $V_{\rm th}$  variation could lead to severe  $T_{\rm j}$  mismatch and even thermal run-away events.

#### C. Circuit Parameters Mismatch

1)  $L_d$  Mismatch: Li et al.[63], [67] claimed that  $L_d$  has little impact on dynamic current sharing. The reason is that the  $I_d$  in switching transient is controlled by (12) while  $L_d$  has no direct impact on  $V_{gs}$ . Nonetheless, the impact of  $L_d$  on the current oscillations cannot be neglected.

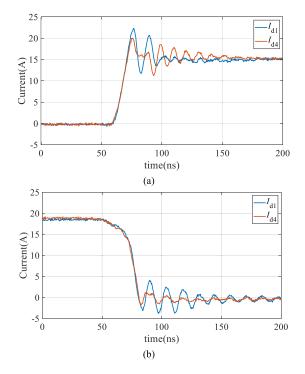

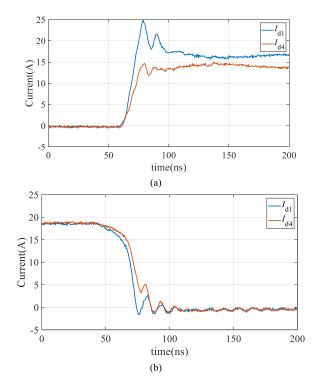

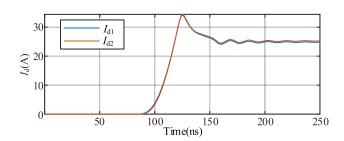

An experimental study is conducted to validate this impact. Twenty MOSFETS with the same part number are tested with a curve tracer and two MOSFETS, i.e., M1 and M4, with identical parameters are selected for the study. Fig. 17 shows the current waveform of the two paralleled MOSFETS with different  $L_{\rm d}$ .  $I_{\rm d1}$  and  $I_{\rm d4}$  in Fig. 17 denote the current of SiC MOSFETS with  $L_{\rm d4}$  = 64 nH and  $L_{\rm d1}$  = 34 nH, respectively.  $I_{\rm d4}$  has a larger ringing over  $I_{\rm d1}$ . With the analysis in [63],  $L_{\rm d}$  has an influence on the current in a short period after turn-ON and turn-OFF. SiC MOSFET with larger  $L_{\rm d}$  has a smaller oscillation frequency and a smaller damping factor after turn-ON and turn-OFF. As a result, the SiC MOSFET with larger  $L_{\rm d}$  has a larger current overshoot, and the current oscillation amplitude after turn-OFF is also larger.

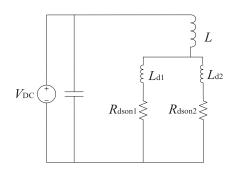

Additionally,  $L_{\rm d}$  has an impact on the static current sharing if the drain current is still changing during the ON-state period. The equivalent circuit of paralleled MOSFETS in ON-state mode is shown in Fig. 18 where L is the load inductance. It can be derived that the ON-state current difference could be calculated

Fig. 17. Experimental switching transient current with different  $L_{\rm d}$ . (a) Turn-ON process. (b) Turn-OFF process.

Fig. 18. ON-state equivalent circuit of paralleling two SiC MOSFETs.

with the following:

$$I_{\rm ds1} - I_{\rm ds2} \approx \frac{L_{\rm d2} - L_{\rm d1}}{2R_{\rm dson}} \frac{V_{\rm DC}}{L}.$$

(13)

It means that the static current difference can be influenced by four parameters: loop inductance,  $R_{\rm dson}$ , load inductor L, and dc-link voltage.

2)  $L_s$  Mismatch: In contrast to  $L_{\rm d}$ ,  $L_{\rm s}$  mismatch has a significant impact on dynamic current sharing [63] due to its influence on  $V_{\rm gs}$ . Analyzing the equivalent circuit in Fig. 12, (14) can be derived. It shows that the channel current is determined by  $V_{\rm gs}$  during switching transient while  $V_{\rm gs}$  is affected by  $L_{\rm s}$  and source current  $I_{\rm s}$

$$V_{\rm gs} = V_{\rm dr} - i_{\rm g} R_{\rm g} - L_{\rm s} \frac{\mathrm{d}I_{\rm s}}{\mathrm{d}t}.$$

(14)

Fig. 19 shows the switching current with  $L_{\rm s}$  mismatch, which demonstrates that larger  $L_{\rm s}$  results in both slower turn-ON and turn-OFF. It means that the MOSFET with larger  $L_{\rm s}$  leads to a

Fig. 19. Experimental current sharing performance of M1 and M4 ( $L_{\rm s4}>L_{\rm s1}$ ). (a) Turn-ON waveform. (b) Turn-OFF waveform.

Fig. 20. LTspice Simulation waveform with the impact of  $L_{\rm g}$  on turn-ON transient.

smaller turn-ON loss since more current stress is withstood by the MOSFETS which turn ON faster. On contrary, the turn-OFF loss of the MOSFET with larger  $L_{\rm s}$  is higher since the other MOSFET operates in quasi-zero-voltage switching mode.

3)  $L_g$  Mismatch:  $L_g$  mismatch has a small impact on transient current sharing. Even though higher  $L_g$  means a slower charging process of  $V_{\rm gs}$ , the gate current and its  ${\rm d}i/{\rm d}t$  are normally quite small in switching dynamic. Therefore, its impact on the gate voltage values is not as significant as  $L_{\rm s}$ . LTspice simulation is conducted to study the impact of  $L_{\rm g}$  on switching speed for paralleled MOSFETS. The  $L_{\rm g}$  of M1 is 10 nH, while that of M2 is 50 nH. The  $I_{\rm d}$  curves of both MOSFETS are plotted in Fig. 20. It validates that the impact of  $L_{\rm g}$  mismatch on the current distribution is not critical. However, gate inductance and its mismatch could lead to gate oscillations and instability issues, which is out of the scope of this article and therefore not discussed.

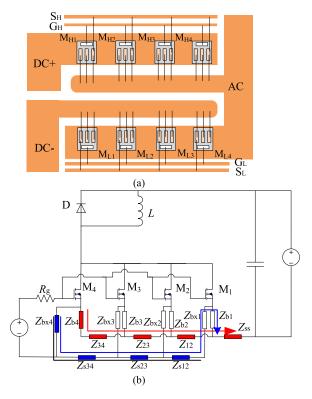

Fig. 21. Power module layouts and their modeling. (a) Package layout. (b) Equivalent circuit.

## V. ANALYSIS AND MODELING OF MULTICHIP POWER MODULE LAYOUTS

Section IV analyzes the impact of the electrical parameters mismatch on current sharing. In a multichip power module, there could be more than two devices in parallel. The accurate modeling of the multichip power module layouts is essential to the current sharing analysis.

A typical power module layout is shown in Fig. 21(a), while its equivalent circuit is shown in Fig. 21(b). The gate loop inductance and mutual inductance are not considered since only gate loops are analyzed here. The current distribution among the paralleled SiC MOSFETS with the above layout is analyzed in [63]. It is revealed that the inductance  $L_{\text{sxL}}$  has a significant impact on dynamic current sharing due to its impact on  $V_{gs}$ during the switching transient process. While the impact of  $L_{\rm dxL}$  on dynamic current sharing is not critical since  $V_{\rm gs}$  during switching transient is not influenced by  $L_{\rm dxL}$ . In this layout, the effective value of  $L_{\text{sxL}}$  and  $L_{\text{dxL}}$  is around 1–2 nH considering the magnetic coupling effects. With a di/dt of 2 kA/ $\mu$ s, the voltage on the parasitic inductance could be around 2-4 V. While this voltage is not comparable to the drain-source voltage but it has a significant impact on the gate-source voltage which is normally between -5 and 15 V.

#### A. Current Coupling Effect

Aside from the analysis above, the current coupling effect can exacerbate the current imbalance among the paralleled devices [68]. The current coupling effect means that the current of the paralleled devices affects not only its switching transient current

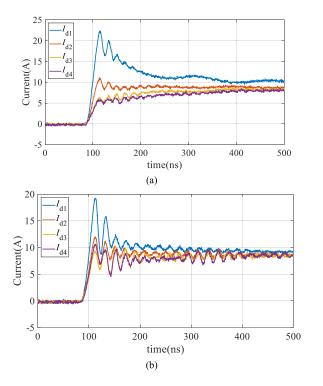

Fig. 22. Simulation result of current waveform of four paralleled MOSFETs. (a) With current coupling effects. (b) Without current coupling effects.

but also the other devices' currents. Dynamic current imbalance among the paralleled SiC MOSFET is because of the device source terminal voltage difference, the root cause of which is due to the voltage on the mismatched inductance. The mismatched inductance voltage is equal to  $L^*\mathrm{d}i/\mathrm{d}t$  during the switching transient.

Therefore, both the mismatched L and di/dt play pivotal roles. Even though the value of  $L_{\rm s4L}$  and  $L_{\rm s2L}$  are identical, the di/dt applied on  $L_{\rm s2L}$  is more than 3 times that on  $L_{\rm s4L}$ . Consequently, the dynamic current imbalance between  $M_{\rm L1}$  and  $M_{\rm L2}$  is larger than the current imbalance between  $M_{\rm L3}$  and  $M_{\rm L4}$ . Due to the current coupling effect, the same inductance mismatch leads to different current imbalances, as shown in Fig. 22.

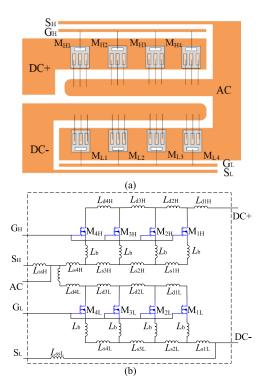

#### B. Paralleling Dies and Paralleling Half-Bridges

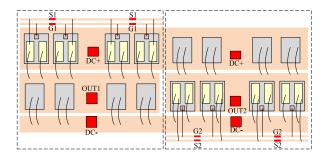

Fig. 23 shows a power module layout as well as the busbar structures, which have six substrates in parallel. Each substrate is an individual half-bridge. In other words, the layout in Fig. 23 is configured with six half-bridges in parallel. The equivalent circuit of this layout is shown in Fig. 24.

The difference between paralleling dies and paralleling half-bridges is the current commutation loop, which further influences the di/dt on the parasitic inductance [69]. As shown in Fig. 24, with paralleled half-bridges, the di/dt on  $L_{\rm sHx}$  between the top side paralleled devices is not high, since the current commutation is able to be achieved within the individual half-bridge. While with paralleling dies in Fig. 21, every current commutation between the top switch and the bottom switch leads to full load di/dt on  $L_{\rm sHx}$ .

Fig. 23. Power module layout with paralleling half-bridge configurations. (a) Package layout. (b) Bus bar layout.

Fig. 24. Modeling of the layout with paralleling half-bridges.

The di/dt interacting with parasitic inductance generates voltage among the source terminals of the paralleled SiC MOSFETs. Thus, the potential of each source terminal is different and this is the dominant reason for dynamic current imbalance among the paralleled devices.

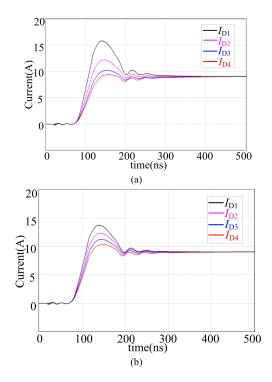

The simulation results of current sharing performance with paralleling half-bridges are plotted in Fig. 25. It can be seen that the dynamic current imbalance of the top devices is not high while that of the bottom devices is significant.

#### C. Auxiliary Source Connections

Auxiliary source connection is extensively applied in multichip power modules. It is revealed that the auxiliary source connection for paralleled devices in a multichip power module cannot fully decouple the power loop and gate loop, which is different with the Kelvin connection of a single device [70]. In order to add auxiliary source connections to the layout in Fig. 21(a), the original layout can be improved as shown in Fig. 26(a), while its equivalent circuit can be drawn in Fig. 26(b).

From Fig. 26, it can be seen that there are more than one current paths between the paralleled source terminals. The impedance of each path determines the current distribution

Fig. 25. Simulation result of current sharing performance with paralleling half-bridge configurations. (a) Current waveform of the top devices. (b) Current waveform of the bottom devices.

Fig. 26. Power module layout with auxiliary connection and its modeling. (a) Package layout. (b) Equivalent circuit.

Fig. 27. Experimental Current waveforms in a multichip power module. (a) Without auxiliary source connection. (b) With auxiliary source connection.

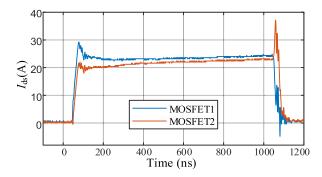

among the different paths. The impact of the auxiliary source connections on the dynamic current imbalance can be validated by the experimental results in Fig. 27 [70].

A power module with four identical dies is tested and the waveforms are plotted in Fig. 27. The difference between highest current peak and lowest current peak is 18 A which leads to high DoI. With an auxiliary source connection on the module, the difference can be reduced by half to 9 A.

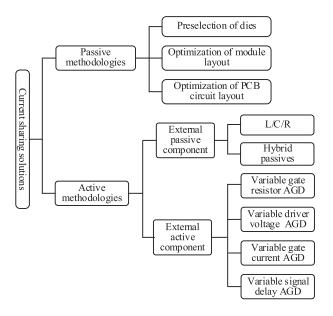

## VI. SOLUTIONS OF CURRENT MISMATCHING IN PARALLEL-CONNECTED DEVICES

Various state-of-the-art methodologies for tackling the current mismatch issue in paralleled devices can be categorized into two major types: passive methods [71] and active methods [72], [73]. Passive methods can minimize the impact of mismatched electrical parameters among loops by optimizing the package/circuit layout or preselection of the chips. Active methods employ auxiliary circuits or component to realize current rebalancing. They include external passive components and external active components. External passive components methodologies can adjust the current distribution via adding passive components in the gate loop or power loop. The external active components methods usually employ adjustable gate driver solutions to dynamically change the device characteristics cycle by cycle. In this section, the research of the aforementioned two methodologies will be illustrated.

#### A. Passive Methodologies

Passive methodologies can adjust the current distribution via selecting the dies with identical electrical parameters or

Fig. 28. Improved power module design for dynamic current imbalance mitigation.

Fig. 29. Experimental dynamic current imbalance mitigation results.

optimizing the hardware layout. From the sequence of the semiconductor device manufacturing process, it can be categorized into the preselection of dies and layout optimization of the circuit.

Preselection of chips means selecting the MOSFET chips in prior to packaging into a module. As demonstrated in Section II, the dies in one wafer usually have different electrical parameters such as  $V_{\rm th}$ ,  $R_{\rm dson}$ , and  $C_{\rm gd}$ . For a power module with multiple paralleled dies, the chips with close electrical parameters are selected for a module [74], [75]. Machine learning algorithms are utilized in paper [76] to assist in the SiC die screening for sorting paralleling SiC MOSFET. Device screening strategy is applied in paper [77] to balance the short-circuit current on the paralleling SiC MOSFETs.

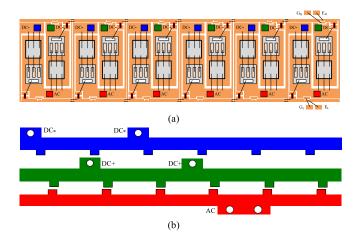

The hardware layout includes power module package layout and external circuit layouts such as a bus bar and PCB [78]. The symmetric circuit layout method can eliminate the current imbalance brought by the mismatched parasitics among different current loops. Fig. 28 shows an improved power module layout design. The layout optimization for mitigating the current imbalance is usually conducted by minimizing the following parameters:

- 1) mismatched  $L_s$ ;

- 2) di/dt across the mismatched  $L_s$ .

Comparing the layout in Figs. 21(a) and 28, it can be concluded that both the mismatched  $L_{\rm s}$  and di/dt applied on the mismatched  $L_{\rm s}$  are reduced. The experimental results before/after performing the aforementioned improved method are plotted in Fig. 29 [79].

Fig. 30. Substrate layout design with different wire-bonding lengths.

Apart from the previous optimization method, multiple emerging module layouts are summarized in [80] which also figures out the future development direction. Specifically, several design methods for symmetric the module internal layout or bus bar structure are introduced in [79], [81], [82], [81] and [83].

Fig. 30 shows another method to improve the current sharing performance, which inserts additional parasitic inductance by adjusting the length of source wire bonding for the paralleled chips [84]. This approach could potentially mitigate the current imbalance to a certain degree but it also increases the parasitic inductance, which can slow down the switching speed or pose switching oscillations. A method with a similar principle can be found in [85]. To control the parasitics on the connecting wires, copper clips are utilized to supplant bonding wires.

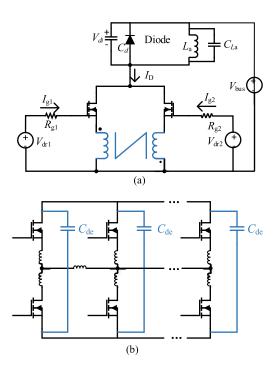

#### B. Active Methodologies: External Passive Components

An active method in the industry is inserting external passive components into the gate loop or power loop. It can manually adjust the impedance for the circulating current and finally realize current sharing. It is known that the passive components can be categorized into inductors (L), capacitors (C), and resistors (R). Different combinations of passive components can adjust the overall characteristics and finally change the current trajectory and distribution.

Employing external passive components for mitigating the current imbalance is usually conducted by optimizing the following parameters.

- Static current imbalance: adjust the resistance in the current route.

- Dynamic current imbalance: change the impedance for circulating current.

A typical inductor-based method is presented in [86], which rebalances  $I_d$  via connecting a differential mode inductor on the source side as shown in Fig. 31.

When  $I_{\rm d}$  is unbalanced, there is an equivalent circulating current between the power loops. The differential mode inductor can increase the impedance for the circulating current, thus the current imbalance is minimized. The mechanism can be further applied on the parallel-connection of power converter as demonstrated in [87] which applies coupled inductor on a resonant pulsed power converter. An RC network connected in the gate loop to suppress the circulation gate current and balance the current in paralleled MOSFET is proposed in [88].

Fig. 31. Several external passives method. (a) Differential mode inductor [86]. (b) Decoupling capacitors on each half-bridge [89].

As analyzed in Section IV-B, paralleling half-bridge has superior current sharing performance over paralleling dies. However, the lower side switch still has current imbalance caused by coupled current. To address this problem, a dynamic current sharing method proposed in [89] optimizes the layout of PCB to enable decoupling capacitors to be located close to the halfbridge. External resistors are added in series with the power MOSFET to adjust the total ON-state resistance [90]. The hybrid component method combines resistors, inductors, or capacitors to implement current sharing. A Kelvin-source resistor and a power source inductor are utilized [91] to mitigate the dynamic current imbalance. It can balance the steady-state  $I_{\rm d}$  while also increasing the conduction loss and reducing the overall efficiency. As demonstrated in [92], two switches are applied on the source side of the MOSFET to actively adjust the current distribution and finally realize current sharing. An *R–L* network connecting in the power loop is proposed to minimize the current imbalance between multiple parallel IGBTs in [93].

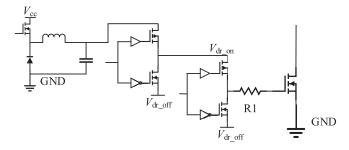

#### C. Active Methodologies: External Active Components

Generally, the aforementioned two methods have a drawback in terms of lack of flexibility. The circuit layout or the passive components cannot be changed in the operating condition, thus they are not appropriate for all conditions. Furthermore, as demonstrated in Section II,  $V_{\rm th}$  can change due to variating  $T_{\rm j}$  when the converter is operating. Therefore, online current sharing methodologies are desired. Specifically, close-loop control lends its capabilities to be applied in various operating conditions. It is known that adjusting the gate driver parameters can change the slew rate of the power MOSFET [94]. As claimed

Fig. 32. Circuit topology of the adjustable  $V_{gs}$  gate driver [99].

in [39], there are four variables for MOSFET switching trajectory adjustment from the gate side, i.e., gate resistance, gate current, gate voltage, and input capacitance. Thus, to adjust the current distribution, active methodologies are usually implemented by utilizing active gate driver (AGD). AGD is an emerging gate driver technique that can adjust its output dynamically based on real-time operation conditions [95]. Generally, the basic mechanism of using external active components for mitigating the current imbalance can be summarized as follows.

- 1) Static current imbalance: Via actively adjusting the  $R_{\rm dson}$  of the MOSFETS, the channel current distribution can be changed.

- 2) Dynamic current imbalance: By actively changing the switching slew rate di/dt or gate signal delay  $\varphi$ , the dynamic current stress on each MOSFET can be tuned.

Static current imbalance can be addressed via adjusting  $R_{\rm dson}$ . Since  $V_{\rm th}$  and other parameters in (11) are all determined in the midst of die manufacturing, the only adjustable parameter is the normal turn-ON driver voltage  $V_{\rm dron}$ . Thus, to change the static current distribution, variable static driver voltage is needed. Also, considering that  $R_{\rm dson}$  is also pertinent to  $T_{\rm j}$  which is greatly impacted by the load current, it is preferred to have a turn-ON driver voltage adjusted cycle by cycle. This mechanism is usually employed to suppress  $\Delta T_{\rm j}$  and finally maximize the life cycles. Several driver circuits to dynamically change  $V_{\rm dron}$  are proposed in [96], [97], and [98]. Via detecting the collector current of an IGBT, it can increase  $V_{\rm ge}$  at the load current peak and reduce  $V_{\rm ge}$  at the load current valley. In this way,  $\Delta T_{\rm j}$  can be minimized and the device long-term reliability is enhanced.

For paralleled MOSFETS, different  $V_{\rm dron}$  levels are applied on each MOSFET to compensate for the static current imbalance in [99] and [100]. The  $V_{\rm dron}$  adjustment can be implemented by using adjustable power supply with a buck converter as shown in Fig. 32(a) [99]. Also, there are some other circuits such as using digital/analog converter, analog adder circuit, and amplifier circuit.

The dynamic current sharing methods with AGDs are relatively challenging for the sake of the very short switching transient process. Specifically,  $V_{\rm ds}$  and  $I_{\rm d}$  changing period occurs during the Miller plateau which can be finished in a couple of nanoseconds. The  ${\rm d}V/{\rm d}t$  of a SiC MOSFET can increase to over 50 V/ns which means the voltage falling substage can be finished in 10 ns. This is challenging to the design of the active gate driver, particularly for the selection of voltage/current sensors, timing sequence, and topology of the AGD [97].

Fig. 33. Experimental results of the parallel-connected device with variable gate voltage AGD. (a) Without AGD. (b) With AGD.

Apart from the slew rate, the switching loss on paralleled MOSFETS is relevant to the gate signal lagging time between the two MOSFETS. Theoretically, the earlier MOSFET withstands higher turn-ON loss and lower turn-OFF loss. As shown in Fig. 33, the transient current waveform of two MOSFETS is not balanced. Via changing the gate lagging time, it can be rebalanced as given in Fig. 33(b). Based on this feature, a common application scenario for AGD is the hybrid switch which is comprised of a Si IGBT with a SiC MOSFET [101]. It is desired to combine the Si IGBT's low conduction loss and SiC MOSFET's low switching loss superiorities [102]. Correspondingly, by means of controlling the gate signal lag between the two devices, the overall power loss can be manually adjusted. SiC MOSFET is desired to turn ON earlier and turn OFF later than the Si IGBT, thus the switching loss is withstood by the SiC MOSFET. Thus, the high switching loss of IGBT can be avoided. The advantage is that the overall power loss can be greatly reduced while the downsides include the higher cost and higher current which may move the SiC MOSFET out of SOA. This method has been presented in [103], [104], [105], and [106] and quantifies the power loss for the hybrid switch under different gate signal delay times.

To realize dynamic current sharing, variable gate current AGD is applied in [107] while this methodology is also employed to balance the voltage in series-connected power MOSFET [108]. Both papers utilize the current mirror circuit and adjustable voltage regulator to change the gate current during the switching

Fig. 34. Summary of the state-of-the-art current sharing methodologies.

transient. Variable gate resistor AGD is employed in [109] to realize dynamic current sharing. The basic operating principle is similar to paper [97]. The capacitor coupling method is utilized in [110] to change the gate current during the switching transient and balance the voltage on series-connected power MOSFET. An adjustable gate signal delay auxiliary circuit for the gate driver is proposed to change the switching stress on paralleled MOSFETS in [111] and [112]. Several variable driver voltage AGD circuitries are introduced in [73] and [113] for the current sharing of paralleled MOSFETS.

#### D. Conclusions and Insight of Current Sharing Strategies

The state-of-the-art types of current sharing solutions can be summarized in Fig. 34.

Passive methods are generally cost-friendly and no extra component is needed. It can be implemented amid fabrication, thus it is preferred by manufacturers [43]. Via continually improving the die screening strategy and optimizing package layout, the commercialized power modules are approaching ideal switches. However, there are still some challenges from technic and cost aspects hindering the further optimization of the power module.

SiC MOSFETS tends to have the concept of known good die (KGD), which means that the key device parameters could be available. This is helpful for the die screening method to improve the current sharing performance among the paralleled devices in multichip power modules. However, there are still a few challenges. First, among the many device parameters ( $R_{\rm dson}$ ,  $V_{\rm th}$ ,  $g_{\rm fs}$ , etc.), it needs to choose one parameter or an algorithm to make the die binning or screening. At present, SiC vendors, on the one hand, are trying to improve the device process maturity to reduce the device parameters' tolerance. On the other hand, a practical algorithm for die binning is also under development and estimation. Second, the KGD concept is currently still based on room temperature. High-temperature KGD for mass production is possible but still quite challenging considering the high-temperature oxidation of the metallization, cost, efficiency, etc.

For the multichip SiC power module package, a more effective and intelligent die binning or sorting method is needed for SiC power devices. The binning or sorting should not be carried out according to one specific device parameter. A "comprehensive device parameter" should be developed to reflect the overall device performance, including paralleling performance, reliability, robustness, and cost. In addition, high-temperature, low-cost KGD measurement equipment, and efficient burn-in test equipment are expected for high-temperature device parameters acquisition.

For multichip power module layout design, some guidelines could be given here. As MOSFET is a voltage-controlled device, which means  $I_{\rm d}$  is fully controlled by  $V_{\rm gs}$  during the switching transient, the design of the multichip module layout is to reduce the differences of  $V_{\rm gs}$  for the paralleled devices. Considering that the difference in gate voltage potentials is small, the design principle is to reduce the difference in source voltage potentials. Two executable rules [79] are reducing the mismatched  $L_{\rm s}$  and the di/dt applied on the mismatched  $L_s$ . By following these design rules, the dynamic current imbalance could be significantly suppressed. The increasing penetration of artificial intelligence (AI) algorithms into manufacturing enables the design process to be smarter. Since all SiC dies are tested in advance to packaging, their electrical parameters are known and it allows the preselection to be implemented. Several computer-aided automatic layout generation methods aiming at minimizing the parasitic inductance in the current loop have been introduced in [114], [115], [116], and [117]. More AI-involved layout design will be the future trend of power semiconductor device packaging

The active methods are generally the supplementary solutions for situations when the passive methodologies no longer work. For instance, paralleled discrete devices are usually utilized in an electric vehicle since they are cost-efficient compared with using a power module. In these conditions, active methods can be adopted to improve the long-term reliability of the system. First, adding the external passive components can increase the cost and introduce extra parasitics in the loop which may lead to false-triggering, voltage overshoot, or crosstalk noise [118]. Second, AGD is a premature technology due to the very short switching transient of SiC MOSFET which is usually within 100 ns. di/dt of a SiC module can increase to 5 A/ns. The current sensing, signal processing and timing sequence in such a short time are usually challenging [39]. For instance, a variable driver voltage AGD usually changes the driver voltage during the Miller plateau to adjust the switching slew rate. The detection of the Miller plateau and calculation of optimal driver voltage for the Miller plateau is difficult. The commercialized gate driver on the market can be found in [119]. It employs a patented augmented turn-OFF driver voltage profile to suppress the overshoot voltage. However, software configuration is utilized to optimize the turn-OFF process of each SiC MOSFET. Academia has dedicated much effort to the exploration of closed-loop control for AGD including Rogowski coil [120], the voltage on the stray inductance [73], and current transformer [121], [122].

For the active gate driver method, an effective and low-cost device current measurement method or an equivalent device current acquisition method is needed for accurate device current distribution optimization. Taking one step back, the active gate driver method could be helpful given the junction temperature could be estimated via the TESP method. In most cases, the target is to limit the junction temperature differences either by controlling the steady state or the dynamic current distribution. Therefore, with AGD and junction temperature estimation of each device, the switching speed or the effective  $R_{\rm dson}$  could be adjusted by AGD in a thermal time constant. With this, the requirements of device's current measurement are not needed.

#### VII. CONCLUSION

This article comprehensively summarizes the state-of-the-art research on paralleling SiC power devices. It starts with the challenges brought by the application of SiC for the paralleling operation. It is followed by a detailed analysis of the current imbalance mechanism among parallel loops. An index *DoI* is proposed to quantify the degree of static and dynamic current imbalance. Various parameters pertinent to the static and dynamic current distribution are categorized into three major types, i.e., the device parameters which are the equivalent parameters inside the dies, the circuit parameters which are parasitics introduced by the package and circuit, and the status indicators such as junction temperature and load current.

Based on the theoretical analysis, the state-of-the-art current sharing methodologies in the industry are summarized. The passive method includes the preselection of dies based on the screening results and package/circuit layout optimization methods. This article also figures out the design criteria of a paralleled devices system. Active current sharing methods include the external passive components and active gate driver solutions are also summarized. Based on the summary of the analyses and solutions, the insight of the current sharing strategies for paralleling SiC MOSFETS is presented.

#### REFERENCE

- [1] S. Zhao, A. Kempitiya, W. T. Chou, V. Palija, and C. Bonfiglio, "Variable DC-link voltage LLC resonant DC/DC converter with wide bandgap power devices," *IEEE Trans. Ind. Appl.*, vol. 58, no. 3, pp. 2965–2977, May/Jun. 2022.

- [2] M. Hofmann, Evaluation of Potentials for Infineon Sic-Mosfets in Automotive Inverter Applications. Erlangen, Germany: Fraunhofer IISB, 2018.

- [3] A. Nisch, C. Kloffer, J. Weigold, W. Wondrak, C. Schweikert, and L. Beaurenaut, "Effects of a SiC TMOSFET tractions inverters on the electric vehicle drivetrain," in *Proc. Europe, Int. Exhib. Conf. Power Electron., Intell. Motion, Renewable Energy Manage.*, 2018, pp. 1–8.

- [4] K. Hamada, M. Nagao, M. Ajioka, and F. Kawai, "SiC—Emerging power device technology for next-generation electrically powered environmentally friendly vehicles," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 278–285, Feb. 2015.

- [5] J. P.Trovao, "What is next for automotive electronics? [Automotive electronics]," *IEEE Veh. Technol. Mag.*, vol. 17, no. 3, pp. 113–120, Sep. 2022.

- [6] A. Streibel et al., "Reliability of SiC MOSFET with danfoss bond buffer technology in automotive traction power modules," in *Proc. Europe, Int. Exhib. Conf. Power Electron., Intell. Motion, Renewable Energy Manage.*, 2019, pp. 1–7.

- [7] E. Hoene, A. Ostmann, B. The Lai, and C. Marczok, "Ultra-low-inductance power module for fast switching semiconductors," in *Proc. Europe Conf. Power Electron., Intell. Motion, Renewable Energy Manage.*, 2013.

- [8] B. Whitaker et al., "A high-density, high-efficiency, isolated on-board vehicle battery charger utilizing silicon carbide power devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2606–2617, May 2014.

- [9] W. Jakobi et al., "Benefits of new CoolSiCTM MOSFET in Hybrid-PACKTM Drive package for electrical drive train applications," in *Proc. Conf. Integr. Power Electron. Syst.*, 2018, pp. 1–9.

- [10] P. Friedrichs, High Performance Coolsic MOSFET Technology With Silicon Like Reliability. Neubiberg, Germany: Infineon, 2020.

- [11] J. W. Palmour, "Silicon carbide power device development for industrial markets," in *Proc. Int. Electron Devices Meeting*, 2014, pp. 1.1.1–1.1.8.

- [12] H. Zhang, L. M. Tolbert, and B. Ozpineci, "Impact of SiC devices on hybrid electric and plug-In hybrid electric vehicles," *IEEE Trans. Ind. Appl.*, vol. 47, no. 2, pp. 912–921, Mar./Apr. 2011.

- [13] H. Lin and A. Villamor, *Power SiC 2018: Materials, Devices, and Applications*. Lyon-Villeurbanne, France: Yole Develop., 2018.

- [14] N. Deb, R. Singh, and H. Bai, "Transformative role of silicon carbide power electronics in providing low-cost extremely fast charging of electric vehicles," in *Proc. IEEE 4th Int. Conf. DC Microgrids*, 2021, pp. 1–6.

- [15] D. Ronanki, S. A. Singh, and S. S. Williamson, "Comprehensive topological overview of rolling stock architectures and recent trends in electric railway traction systems," *IEEE Trans. Transp. Electrific.*, vol. 3, no. 3, pp. 724–738, Sep. 2017.

- [16] B. Sarlioglu, C. T.Morris, D. Han, and S. Li, "Driving toward accessibility: A review of technological improvements for electric machines, power electronics, and batteries for electric and hybrid vehicles," *IEEE Ind. Appl. Mag.*, vol. 23, no. 1, pp. 14–25, Jan./Feb. 2017.

- [17] X. She, A. Q. Huang, and R. Burgos, "Review of solid-state transformer technologies and their application in power distribution systems," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 3, pp. 186–198, Sep. 2013.

- [18] X. She, A. Q. Huang, Ó. Lucía, and B. Ozpineci, "Review of silicon carbide power devices and their applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8193–8205, Oct. 2017.

- [19] B. Ozpineci and L. M. Tolbert, Comparison of Wide-Bandgap Semiconductors for Power Electronics Applications. Oak Ridge, TN, USA: Oak Ridge Nat. Lab., 2003.

- [20] J. Rabkowski, D. Peftitsis, and H.-P. Nee, "Silicon carbide power transistors: A new era in power electronics is initiated," *IEEE Ind. Electron. Mag.*, vol. 6, no. 2, pp. 17–26, Jun. 2012.

- [21] P. G. Neudeck, R. S. Okojie, and L. Chen, "High-temperature electronicsa role for wide bandgap semiconductors?," *Proc. IEEE*, vol. 90, no. 6, pp. 1065–1076, Jun. 2002.

- [22] T. Funaki et al., "Power conversion with SiC devices at extremely high ambient temperatures," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1321–1329, Jul. 2007.

- [23] A. J. Lelis, R. Green, D. B. Habersat, and M. EI, "Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 316–323, Feb. 2015.

- [24] L. A. Lipkin and J. W. Palmour, "Insulator investigation on SiC for improved reliability," *IEEE Trans. Electron Devices*, vol. 46, no. 3, pp. 525–532, Mar. 1999.

- [25] M. Beier-Moebius and J. Lutz, "Breakdown of gate oxide of 1.2 kV SiC-MOSFETs under high temperature and high gate voltage," in Proc. Europe: Int. Exhib. Conf. Power Electron., Intell. Motion, Renewable Energy Manage., 2016, pp. 1–8.

- [26] M. Bhatnagar and B. J. Baliga, "Comparison of 6H-SiC, 3C-SiC, and Si for power devices," *IEEE Trans. Electron Devices*, vol. 40, no. 3, pp. 645–655, Mar. 1993.

- [27] J. Zhou, C. F. Huang, C. H. Cheng, and F. Zhao, "A comprehensive analytical study of dielectric modulated drift regions—Part I: Static characteristics," *IEEE Trans. Electron Devices*, vol. 63, no. 6, pp. 2255–2260, Jun. 2016.

- [28] A. Q. Huang, "New unipolar switching power device figures of merit," IEEE Electron Device Lett., vol. 25, no. 5, pp. 298–301, May 2004.

- [29] P. G. Neudeck and J. A. Powell, "Performance limiting micropipe defects in silicon carbide wafers," *IEEE Electron Device Lett.*, vol. 15, no. 2, pp. 63–65, Feb. 1994.

- [30] H. Jiang, X. Zhong, G. Qiu, L. Tang, X. Qi, and L. Ran, "Dynamic gate stress induced threshold voltage drift of silicon carbide MOSFET," *IEEE Electron Device Lett.*, vol. 41, no. 9, pp. 1284–1287, Sep. 2020.

- [31] M. Regardi et al., "How Infineon Controls and Assures the Reliability of SiC Based Power Semiconductors. Neubiberg, Germany: Infineon, 2020.

- [32] T. Aichinger and G. Rescher, "Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs," *Micro-Electron. Rel.*, vol. 80, pp. 68–78, 2017.

- [33] Z. Chen, D. Boroyevich, and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," in *Proc. Int. Power Electron. Conf.–Energy Convers. Congr. Expo. Asia*, 2010, pp. 164–169.

- [34] H. Li and S. Munk-Nielsen, "Challenges in switching SiC MOSFET without ringing," in *Proc. Europe: Int. Exhib. Conf. Power Electron.*, *Intell. Motion, Renewable Energy Manage.*, 2014, pp. 1–6.

- [35] H. Li and S. Munk-Nielsen, "Detail study of SiC MOSFET switching characteristics," in *Proc. Int. Symp. Power Electron. Distrib. Gener. Syst.*, 2014, pp. 1–5.

- [36] J. O. Gonzalez, R. Wu, S. Jahdi, and O. Alatise, "Performance and reliability review of 650 V and 900 V silicon and SiC devices: MOSFETs, cascode JFETs and IGBTs," *IEEE Trans. Ind. Electron.*, vol. 67, no. 9, pp. 7375–7385, Sep. 2020.

- [37] X. Wu, S. Cheng, Q. Xiao, and K. Sheng, "A 3600 V/80 A series-parallel-connected silicon carbide MOSFETs module with a single external gate driver," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2296–2306, May 2014.

- [38] A. Lachichi and P. Mawby, "Modeling of bipolar degradations in 4H-SiC power MOSFET Devices by a 3C-SiC inclusive layer consideration in the drift region," *IEEE Trans. Power Electron.*, vol. 37, no. 3, pp. 2959–2969, Mar. 2022.

- [39] S. Zhao, X. Zhao, Y. Wei, Y. Zhao, and H. A. Mantooth, "A review on switching slew rate control for silicon carbide devices using active gate drivers," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 4, pp. 4096–4114, Aug. 2021.

- pp. 4096–4114, Aug. 2021.

[40] Z. Wang, Z. Zhang, C. Shao, J. Robertson, S. Liu, and Y. Guo, "Defects and passivation mechanism of the suboxide layers at SiO<sub>2</sub>/4H-SiC (0001) interface: A first-principles calculation," *IEEE Trans. Electron Devices*, vol. 68, no. 1, pp. 288–293, Jan. 2021.

- [41] T. Bertelshofer, A. März, and M.-M. Bakran, "Modelling parallel SiC MOSFETs: thermal self-stabilisation vs. switching imbalances," *Inst. Eng. Technol. Power Electron.*, vol. 12, no. 5, pp. 1071–1078, Feb. 2019

- [42] J. Ke et al., "Investigation of low-profile, high-performance 62-mm SiC power module package," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 4, pp. 3850–3867, Aug. 2021.

- [43] L. Wang, Z. Zeng, P. Sun, Y. Yu, K. Ou, and J. Wang, "Current-bunch concept for parasitic-oriented extraction and optimization of multichip SiC power module," *IEEE Trans. Power Electron.*, vol. 36, no. 8, pp. 8593–8599, Aug. 2021.

- [44] D.-P. Sadik, J. Colmenares, D. Peftitsis, J.-K. Lim, J. Rabkowski, and H.-P. Nee, "Experimental investigations of static and transient current sharing of parallel-connected Silicon Carbide MOSFETs," in *Proc. Eur. Conf. Power Electron. Appl.*, 2013, pp. 1–10.

- [45] X. Chen, W. Chen, X. Yang, Y. Ren, and L. Qiao, "Common-mode EMI mathematical modeling based on inductive coupling theory in a power module with parallel-connected SiC MOSFETs," *IEEE Trans. Power Electron.*, vol. 36, no. 6, pp. 6644–6662, Jun. 2021.

- [46] Z. Zeng, X. Zhang, and X. Li, "Layout-dominated dynamic current imbalance in multichip power module: Mechanism modeling and comparative evaluation," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 11199–11215, Nov. 2019.

- [47] C. Wang, S. Zhao, J. Wang, H. Li, Y. Wei, and H. A. Mantooth, "Analytical model of the parallel-connected silicon carbide MOSFET turn-on switching behavior under asynchronous gate signals," in *Proc. Transp. Electrific. Conf. Expo.*, Asia-Pac., 2022, pp. 1–6.

- [48] T. R. McNutt, A. R. Hefner, H. A. Mantooth, D. Berning, and S.-H. Ryu, "Silicon carbide power MOSFET model and parameter extraction sequence," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 353–363, Mar. 2007.

- [49] L. Alhmoud, "Reliability improvement for a high-power IGBT in wind energy applications," *IEEE Trans. Ind. Electron.*, vol. 65, no. 9, pp. 7129–7138, Sep. 2018.

- [50] H. Oh, B. Han, P. McCluskey, C. Han, and B. D. Young, "Physics-of-failure, condition monitoring, and prognostics of insulated gate bipolar transistor modules: A review," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2413–2426, May 2015.

- [51] O. Salmela, "Acceleration factors for lead-free solder materials," *IEEE Trans. Compon. Packag. Technol.*, vol. 30, no. 4, pp. 700–707, Dec. 2007.

- [52] A. Antonopoulos, S. D'Arco, M. Hernes, and D. Peftitsis, "Limitations and guidelines for damage estimation based on lifetime models for high-power IGBTs in realistic application conditions," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 3, pp. 3598–3609, Jun. 2021.

- [53] R. Wang, L. Tan, C. Li, T. Huang, H. Li, and X. Huang, "Analysis, design, and implementation of junction temperature fluctuation tracking suppression strategy for SiC MOSFETs in wireless high-power transfer," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 1193–1204, Jan. 2021.

- [54] Z. Ni, X. Lyu, O. P. Yadav, B. N. Singh, S. Zheng, and D. Cao, "Overview of real-time lifetime prediction and extension for SiC power converters," *IEEE Trans. Power Electron.*, vol. 35, no. 8, pp. 7765–7794, Aug. 2020.

- [55] A. Raciti, M. Melito, M. Nania, and G. Montoro, "Effects of the device parameters and circuit mismatches on the static and dynamic behavior of parallel connections of silicon carbide MOSFETs," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2018, pp. 1846–1852.

- [56] J. Hu et al., "Robustness and balancing of parallel-connected power devices: SiC versus CoolMOS," *IEEE Trans. Ind. Electron.*, vol. 63, no. 4, pp. 2092–2102, Apr. 2016.