# **Aalborg Universitet**

# Accurate Prediction of Incomplete Zero-Voltage Switching Dynamics and Losses

Zäch, Mike Robin; Beczkowski, Szymon Michal; Jørgensen, Asger Bjørn; Munk-Nielsen, Stig

Published in:

2023 IEEE 10th Workshop on Wide Bandgap Power Devices and Applications, WiPDA 2023

DOI (link to publication from Publisher): 10.1109/WiPDA58524.2023.10382222

Publication date: 2023

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Zäch, M. R., Beczkowski, S. M., Jørgensen, A. B., & Munk-Nielsen, S. (2023). Accurate Prediction of Incomplete Zero-Voltage Switching Dynamics and Losses. In 2023 IEEE 10th Workshop on Wide Bandgap Power Devices and Applications, WiPDA 2023 Article 10382222 IEEE. https://doi.org/10.1109/WiPDA58524.2023.10382222

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: May 12, 2024

# Accurate Prediction of Incomplete Zero-Voltage Switching Dynamics and Losses

Mike Zäch\*, Szymon Beczkowski, Asger Bjørn Jørgensen, Stig Munk-Nielsen

AAU Energy

Aalborg University

Aalborg, Denmark

\*mrz@energy.aau.dk

Abstract—The switching losses occurring between full softswitching and hard-switching are described inadequately, and previous attempts of quantifying incomplete zero-voltage switching losses are topology specific and not applicable for any general half-bridge circuit. The ability to quantify these losses is crucial to optimize the converter efficiency across a wide operating range. This paper proposes a general method for accurately estimating the incomplete zero-voltage switching dynamics and losses in half-bridge converters, including the non-linear output capacitance of the semiconductors. The charge balance during the switching transition period is solved to determine the depth of incomplete zero-voltage switching, which can be used to predict the switching losses. The method is verified experimentally, and is shown to be able to predict the depth of incomplete zero-voltage switching accurately, which can be used to calculate the related losses.

### I. INTRODUCTION

Wide band-gap (WBG) devices such as silicon carbide (SiC) MOSFETs are extending their application range to various high power industries, such as e.g. electric transportation, due to their favorable properties [1]-[4]. Electric drive trains implementing WBG devices are both lighter and less voluminous due to their superior isolation properties and higher switching frequencies. As e-mobility advances towards larger, high voltage batteries to cover heavy-duty vehicles allowing for goods transportation, the demand for high efficient charging stations covering a wide range of battery voltages increases [5]-[8]. Charging standards such as HPC-350 and upcoming megawatt charging system (MCS) cover a large variety of voltage and current operating points [6], [9]. In order to achieve high-efficiency with fast-switching WBG devices, zero voltage switching (ZVS) topologies are an attractive choice for the power converter [6], [10]-[12]. However, ZVS converters typically need to be operated in a application-specific ZVS area. This can cause limitations in the feasible operating area, which poses design challenges for the demands of wide operating range application [13]. Furthermore, the methods to determine the ZVS area are usually subject to topologyspecific assumptions, and often do not account for the nonlinearity of the semiconductors [13]–[15]. In [14], the output capacitance of the semiconductor is linearized, which leads to inaccurate results at the initial and final stage of the switching transition. Although Incomplete zero-voltage switching (iZVS) was considered, the assumption that the inductor current would decrease linearly to zero during the dead time period required a variable dead time dependent on the inductor current. This is topology-specific and rarely the case in common converter topologies. In [15], the non-linearity of the output capacitance is considered, but the method presented is topology-specific for series resonant converters and does not consider iZVS.

This paper proposes a generally applicable method for determining the border between soft and hard-switching of any half-bridge by predicting the voltage remaining across the device under test (DUT) after the switching transition, including the non-linear output capacitance of the semiconductors, as well as the LC resonant interaction in the circuit. This can be used to quantifies the losses of operating a half-bridge with iZVS and increase the feasible operating area. The proposed method is experimentally verified, allowing to determine the remaining voltage during iZVS at any given operating point from only a handful of known circuit and datasheet parameters.

# II. QUANTIFICATION OF DEPTH OF INCOMPLETE ZERO-VOLTAGE SWITCHING

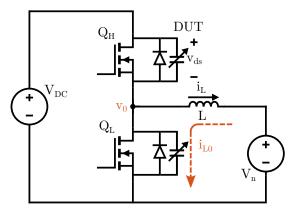

In the circuit in Figure 1, the energy stored in the magnetic field of the inductor can be used to achieve soft-switching thus reducing the switching losses in the transistor. However, if the charge provided by the inductor is insufficient to complete the switching transition, iZVS will occur. To quantify the losses during iZVS, the remaining voltage across the DUT after the switching transition period must be determined.

## A. Proposed Model

To quantify the magnitude of the remaining voltage across the DUT, the charge balance during the switching transition is solved using four key parameters: The voltages on each side of the inductor  $v_0$  and  $V_n$ , the initial current in the inductor at the start of the switching transition  $i_{L0}$ , and the non-linear output capacitance of the transistor as a function of voltage  $C_{\rm oss}(v_{\rm ds})$ . Curve-fitting or a look-up table can be used to obtain the output-capacitance function. Depending on whether  $Q_{\rm H}$  or

Fig. 1: Half-bridge circuit at the beginning of the switching transition, where  $Q_L$  was initially conducting the current  $i_{L0}$ , and is to be turned off, while  $Q_H$  (DUT) is about to turn on.

$Q_L$  is considered, the parameters  $v_0$  and initial current  $i_0$  have to be adjusted accordingly.

$$v_0 = \begin{cases} 0 \text{ if DUT} = Q_H \\ V_{DC} \text{ if DUT} = Q_L \end{cases} \qquad i_0 = \begin{cases} i_{L0} \text{ if DUT} = Q_H \\ -i_{L0} \text{ if DUT} = Q_L \end{cases}$$

(1)

At the beginning of the dead time period, the voltage across the DUT is equal to the DC voltage, and starts decreasing towards zero as the output capacitance is discharged while the output capacitance of the opposite transistor is charged to the DC voltage. During this period, the circuit shown in Figure 1 can be approximated by replacing the transistors with linearized charge-equivalent capacitors to predict the inductor current.

The output capacitance of a MOSFET is a non-linear function of the  $V_{\rm ds}$ , and changes substantially at low voltages [16]. The charge-equivalent capacitance  $C_{\rm q,eq}(\nu_{\rm ds})$  can be calculated by integrating the curve-fitted output capacitance as a function of drain-source voltage from zero to the desired drain-source voltage to get the charge stored at this voltage [14].

$$C_{q,eq}(v_{ds}) = \frac{Q_{oss}(v_{ds})}{v_{ds}}$$

(2)

$Q_{\rm oss}(v_{\rm ds})$  is obtained by integrating  $C_{\rm oss}(v_{\rm ds})$  with respect to voltage. By solving the differential equation of the resulting linearized LC-resonant circuit, the time-dependent expression of the inductor current available to discharge the output capacitance of the DUT and charge the opposite transistor can be obtained.

$$i_{L}(t, v_{ds}) = i_{0} \cdot \cos(\omega_{0}t) - \frac{v_{0} - V_{n}}{\sqrt{\frac{L}{2C_{q,eq}(v_{ds})}}} \cdot \sin(\omega_{0}t)$$

(3)

Where  $\omega_0$  denotes the natural frequency of the LC circuit and is given by

$$\omega_0 = \frac{1}{\sqrt{2C_{q,eq}L}} \tag{4}$$

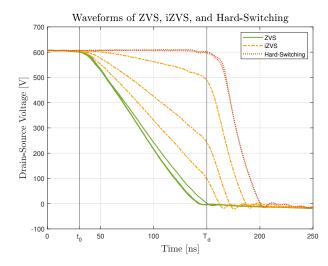

Fig. 2: Drain-source voltage of ZVS, iZVS, and hard-switching. The remaining voltage occurring at  $T_{\rm d}$  must be determined to quantify the iZVS losses.

The charge provided by the inductor during the transition period is expressed as the time-integral of the inductor current from zero to the dead time.

$$Q_{L} = \int_{t_0}^{T_d} i_L(t) dt$$

$$= -\frac{i_0}{\omega_0} \cdot \sin(\omega_0 T_d) + \frac{v_0 - V_n}{\omega_0 \sqrt{\frac{L}{2C_{q,eq}}}} \cdot \left(\cos(\omega_0 T_d) - 1\right)$$

(5)

In order to ensure ZVS, the charge provided by the inductor has to be larger than the charge stored in the output capacitance of the DUT, and the charge required to turn  $Q_L$  off, i.e. raise its voltage to the DC voltage. This relation can be used to calculate the remaining voltage across the DUT.

For ZVS to be achieved, the transistor turning off will require a larger amount of charge in the beginning of the switching transition to increase the voltage due to the nonlinearity of the output capacitance. Likewise, the opposing transistor will need to lose additional charge to completely discharge by the end of the dead time period. Integrating the output capacitance from zero to the DC voltage yields the charge stored in the output capacitance at a given voltage. The charge required to change the voltage across the DUT by some voltage  $\nu$  can be quantified as

$$Q_{\rm HB}(v) = \int_0^v C_{\rm oss}(v) + C_{\rm oss}(V_{\rm DC} - v) \, \mathrm{d}v \tag{6}$$

Where  $Q_{\rm HB}(v)$  is the charge required to change the voltage across the DUT by the voltage v, and  $V_{\rm DC}$  is the initial voltage before turn on. The voltage remaining across the DUT can then be calculated by inserting (5) into (6), and solving for  $V_{\rm rem}$ . If the remaining voltage is between zero and the DC voltage, iZVS will occur.

$$Q_{\rm L} = \int_0^{V_{\rm rem}} C_{\rm oss}(v) + C_{\rm oss} (V_{\rm DC} - v) \, dv \tag{7}$$

# Determining Remaining Voltage in Half-Bridge During Partial Soft Switching

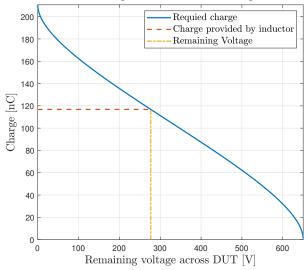

Fig. 3: Example of charge balance in half-bridge during iZVS. The transistors used are C2M0080120D from Wolfspeed [16]. The initial current is 1 A with an inductance of  $120 \,\mu\text{H}$ . The dead-time is  $110 \, \text{ns}$  and the DC voltage is set to  $650 \, \text{V}$ .

Figure 3 shows an example of the required charge to change the voltage across the DUT by v, and how the remaining voltage across the DUT can be determined by applying (5) and (7). From Figure 3, it can be observed that the charge required to achieve ZVS during the switching transition is equal to 210 nC, which is twice the output charge of the applied transistor with a DC voltage of 600 V. Thus, the initial current to achieve ZVS can be calculated by rearranging (5).

$$i_{\text{zvs}}(v_{\text{ds}}) = -\frac{\omega_0}{\sin(\omega_0 T_{\text{d}})} \cdot \left(2Q_{\text{oss}}(V_{\text{DC}}) + \frac{V_{\text{n}} - v_0}{\sqrt{\frac{L}{2C_{\text{q,eq}}} \cdot \omega_0}} \cdot (\cos(\omega_0 T_{\text{d}}) - 1)\right)$$

(8)

# B. Incomplete Zero-Voltage Switching Losses

The losses that occur during iZVS are approximated by calculating the hard-switching losses that would occur if the DUT was hard-switched with the calculated remaining voltage across it. In [17], a method is presented to accurately calculate the hard-switching losses of SiC MOSFETs based on experimental waveforms and device parameters, taking the internal and external circuit parasitics and non-linearities into account. This method is applied to estimate the turn on losses during iZVS.

$$E_{\text{on,iZVS}} = \int_0^{t_{\text{f}}} v_{\text{ds}}(t) i_{\text{ds}}(t) dt - \frac{1}{2} L_{\text{ds}} I_0^2 + \frac{1}{2} C_{\text{er}}(V_{\text{rem}}) V_{\text{rem}}^2$$

(9)

Where  $t_f$  is the fall time, defined from the end of the dead time period until the voltage across the DUT reaches zero,  $L_{ds}$  is the sum of the parasitic drain and source lead inductances,

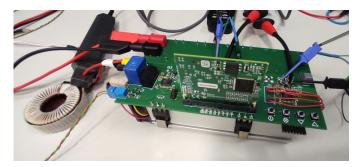

Fig. 4: Full-bridge converter to verify the proposed method.

$I_0$  is the current at the end of the dead time, and  $C_{\rm er}(V_{\rm rem})$  is the energy related capacitance of the output capacitance of the transistor evaluated from 0 V to the remaining voltage, calculated as

$$C_{\text{er}}(v) = \frac{2}{V_{\text{rem}}^2} \cdot E_{\text{oss}}(V_{\text{rem}}) = \frac{2}{V_{\text{rem}}^2} \cdot \int_0^{V_{\text{rem}}} Q_{\text{oss}}(v) dv$$

(10)

The drain-source voltage in (9) is approximated as linearly decreasing from the remaining voltage towards zero during the fall time. The drain-source current is calculated using (3).

#### III. EXPERIMENTAL VERIFICATION

A full-bridge circuit with an inductive load is used to verify the proposed method of determining the remaining voltage and iZVS losses at different operating currents. The drain-source and gate-source voltage of the DUT are observed, while the current in the inductor at the start of the switching transition period is adjusted by modulating the transistors as described in [18]. The experimental setup can be seen in Figure 4.

TABLE I: The following parameters are used in the experiment to verify the remaining voltage across the DUT.

| DUT Device                  | Drain-Source | Dead Time | Inductor           |

|-----------------------------|--------------|-----------|--------------------|

|                             | Voltage [V]  | [ns]      | $[\mu \mathrm{H}]$ |

| Wolfspeed C2M0080120D (SiC) | 600          | 110       | 170                |

| Infineon IPB65R125C7 (Si)   | 50           | 400       | 170                |

| Infineon IPB65R125C7 (Si)   | 75           | 400       | 170                |

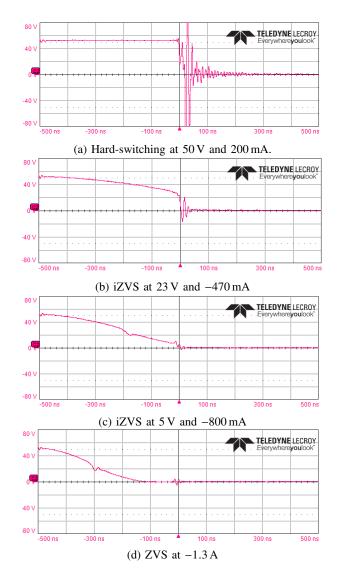

Both a Si and a SiC MOSFET are tested to verify the model for different types of transistors and output capacitances. The Si MOSFET is tested at low voltages, as the non-linearity will be most significant in these areas. Waveforms for hardswitching, iZVS, and ZVS for the Si MOSFET at 50 V can be seen in Figure 5. The magnitude of the voltage at the turn-on of the DUT shows the converter is hard-switching (a), iZVS (b & c) and ZVS (d) at different switching currents.

Moreover, the drain-source voltage oscillations are of larger magnitude at increased turn-on voltages, due to the increase in dv/dt when the device is turned on. Apart from increased switching losses at higher turn-on voltages, the resulting switching oscillations can cause undesired EMI,

Fig. 5: Experimentally measured drain-source voltage of DUT (Si MOSFET) at different switching currents. The DUT is turned-on at 0 s.

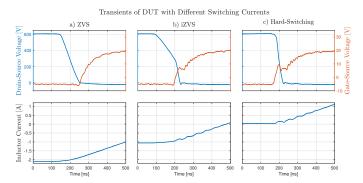

voltage overshoot, additional power losses, and even shoot-through failures, thus severely compromising the performance of the converter [19]. Figure 6 shows the drain-source and gate-source voltages during the switching transition of a SiC MOSFET operating at a DC voltage of 600 V. The remaining voltage after the switching transition at different inductor currents is used to predict the switching modes of the DUT. It can be observed that the transistor enters iZVS when the inductor current is not sufficiently large to provide the required charge to achieve ZVS during the dead time period. The experimentally measured drain-source voltages at turn-on of the DUT are used to evaluate the proposed model.

#### A. Evaluation of Proposed Model

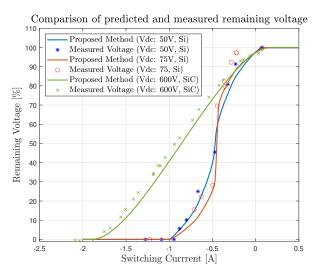

The obtained values for the remaining voltage at various switching currents are normalized with respect to the DC voltages and compared to the analytical model in Figure 7. It

Fig. 6: Experimentally measured switching transients with (a) ZVS at  $-2.08\,A$ , (b) iZVS at  $-1.05\,A$ , and (c) hardswitching at  $0\,A$ .

Fig. 7: Comparison of remaining voltage predicted by model and measured experimentally as percentage of the DC voltage of the experiments described in Table I.

can be observed that the non-linearity is most obvious with a Si DUT, which can be attested to the low voltages at which the experiments are conducted. The change in output capacitance is largest at low voltages, which can be observed both at the beginning of the switching transition, when the turn-off transistor is charged from 0 V, as well as at the end of the transition, when the DUT approaches 0 V, as shown in (7). At higher voltages, the linear region of the output charge is reached, which is reflected by the remaining voltage of the SiC device switched at 600 V. To evaluate the accuracy of the proposed model, the root-mean-square deviation (RMSD) from the predicted voltages to the measurements is calculated.

RMSD =

$$\sqrt{\frac{1}{N} \sum_{i=1}^{N} (x_i - \hat{x_i})^2}$$

(11)

Applied to the normalized data seen in Figure 7, the RMSD of the model with respect to the experimental data is 4.7%. The model does not account for measurement errors or the influence of parasitics. Furthermore, the function used to

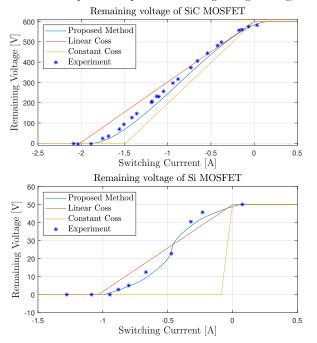

Method comparison to predict remaining voltage during iZVS

Fig. 8: Comparison of different methods for determining the ZVS current, using Wolfspeed C2M0080120D SiC MOSFET at 600 V.

TABLE II: ZVS current estimation using different methods, compared to experimentally measured

| Experiment:  | Constant:         | Linear:           | Proposed: | Measured: |

|--------------|-------------------|-------------------|-----------|-----------|

| SiC at 600 V | -1.49 A           | $-2.02\mathrm{A}$ | -1.90 A   | -1.89 A   |

| Si at 50 V   | $-0.09\mathrm{A}$ | -1.04 A           | -1.00 A   | 0.95 A    |

calculate the output charge is a numeric integration of a curvefit of the output capacitance extracted from the SPICE model provided by the manufacturer, which can also cause deviation of the model from experimentally observed results. Figure 8 shows how the proposed model compares with other common methods for predicting the ZVS current. The constant output capacitance method is widely used to determine the ZVS current and uses the value of the output capacitance listed in the datasheet of the device, usually at the rated voltage of the device [13], [20]. This method entirely disregards the effects of the non-linearity of the output capacitance and is therefore the least precise. The linear output capacitance method uses the charge equivalent capacitance as described in [14]. It provides a more accurate estimation, as the charge contribution from the non-linear part is considered. In the areas dominated by the non-linearity however, the method loses accuracy. The RMSD for the linear method is 10% compared to the experimental results, which is more than twice the RMSD of the proposed method. The predicted ZVS currents of the different methods are presented in Table II. It can be seen that both the linear output capacitance method

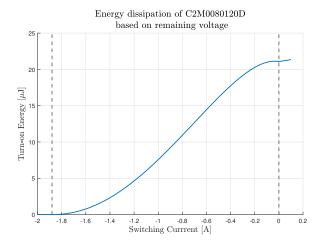

Fig. 9: Calculated turn-on energy based on remaining voltage. iZVS between -1.89 and 0 A.

and the proposed model can predict the ZVS current with high accuracy, while the constant output capacitance method fails to make a precise prediction at low DC voltages, as the significant non-linear part is not considered.

#### B. Calculation of Turn-on Energy

Finally, the remaining voltage is linked to the turn-on energy. The turn-on energy is calculated for the SiC device as described in Section II-B using (9) as a function of the remaining voltage calculated by the proposed method. The dissipated turn-on energy increases non-linearly between complete ZVS and hard-switching in accordance with the remaining voltage. However, the applied turn-on loss estimation method requires many circuit parameters to be known in order to estimate the fall-time and the drain-source parasitic inductance and can be inaccurate if the parameters are not known precisely. Therefore, further research is required to develop a simplified model tying the remaining voltage to turn-on losses, verifying it with a calorimetric test setup to eliminate deviations caused by inaccuracies of the electrical measurements.

#### IV. CONCLUSION

The proposed method can be used to accurately determine iZVS losses in any half-bridge configuration with only a handful of circuit and datasheet parameters, allowing the circuit design to be optimized accordingly. Despite many possible sources of error, such as parasitic coupling, measurement errors, and potential inaccuracies during curve-fitting of the output capacitance as a function of drain-source voltage, the proposed resonant charge balance method has a low RMSD below 5%, outperforming other methods for predicting the remaining voltage after the switching transition, as well as the ZVS current. A qualitative significance of the proposed method can clearly be observed when operating with low DC voltages, where the non-linearity of the output capacitance is dominating.

The analytical results determining the depth of iZVS in a half-bridge correlates well with experimental results, and the predicted turn-on energy corresponds to the turn-on energy based on experimental waveforms. The latter should be experimentally verified using a calorimetric test setup, removing the sources of error from electrical measurements. Furthermore, the iZVS losses can be tied to hard-switching losses at a lower DC voltage. To simplify the quantification of switching losses, further research is required to separate and measure turn-on, conduction, and turn-off losses.

#### REFERENCES

- F. Roccaforte, P. Fiorenza, G. Greco, R. L. Nigro, F. Giannazzo, F. Iucolano, and M. Saggio, "Emerging trends in wide band gap semiconductors (sic and gan) technology for power devices," *Microelectronic Engineering*, vol. 187-188, pp. 66–77, 2 2018.

- [2] L. Spaziani and L. Lu, "Silicon, gan and sic: There's room for all: An application space overview of device considerations," vol. 2018-May. Institute of Electrical and Electronics Engineers Inc., 6 2018, pp. 8–11.

- [3] A. Ghazanfari, C. Perreault, , and K. Zaghib, "Ev/hev industry trends of wide-bandgap power semiconductor devices for power electronics converters," *Hydro-Québec's Center of Excellence in Transportation Electrification and Energy Storage (CETEES)*, 2019.

- [4] Y. Berube, A. Ghazanfari, H. F. Blanchette, C. Perreault, and K. Zaghib, "Recent advances in wide bandgap devices for automotive industry." IEEE, 10 2020, pp. 2557–2564. [Online]. Available: https://ieeexplore.ieee.org/document/9254478/

- [5] B. Frieske, M. Kloetzke, and F. Mauser, "Trends in vehicle concept and key technology development for hybrid and battery electric vehicles." Institute of Electrical and Electronics Engineers Inc., 10 2014.

- [6] C. Suarez and W. Martinez, "Fast and ultra-fast charging for battery electric vehicles - a review," in 2019 IEEE Energy Conversion Congress and Exposition, ECCE 2019. Institute of Electrical and Electronics Engineers Inc., 9 2019, pp. 569–575, hPC350.

- [7] M. Yilmaz and P. T. Krein, "Review of battery charger topologies, charging power levels, and infrastructure for plug-in electric and hybrid vehicles," pp. 2151–2169, 2013.

- [8] S. Habib, M. M. Khan, F. Abbas, L. Sang, M. U. Shahid, and H. Tang, "A comprehensive study of implemented international standards, technical challenges, impacts and prospects for electric vehicles," pp. 13866– 13890, 3, 2018.

- [9] R. S. K. Moorthy, M. Starke, B. Dean, A. Adib, S. Campbell, and M. Chinthavali, "Megawatt scale charging system architecture." IEEE, 10 2022, pp. 1–8. [Online]. Available: https://ieeexplore.ieee.org/document/9947403/

- [10] S. Habib, M. M. Khan, F. Abbas, A. Ali, M. T. Faiz, F. Ehsan, and H. Tang, "Contemporary trends in power electronics converters for charging solutions of electric vehicles," *CSEE Journal of Power and Energy Systems*, vol. 6, pp. 911–929, 12 2020.

- [11] Z. Wang and H. Li, "A soft switching three-phase current-fed bidirectional de-de converter with high efficiency over a wide input voltage range," *IEEE Transactions on Power Electronics*, vol. 27, pp. 669–684, 2012.

- [12] R. Kodoth, H. T, B. K. R., and P. Kanakasabapathy, "Design and development of a resonant converter adapted to wide ouput range in ev battery," 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT-2018), 2018

- [13] T. T. Le, S. Kim, and S. Choi, "A four-phase current-fed push-pull dab converter for wide-voltage-range applications," *IEEE Transactions on Power Electronics*, vol. 36, pp. 11383–11396, 102021.

- [14] M. Kasper, R. M. Burkart, G. Deboy, and J. W. Kolar, "Zvs of power mosfets revisited," *IEEE Transactions on Power Electronics*, vol. 31, pp. 8063–8067, 12 2016.

- [15] C.-T. Truong and S.-J. Choi, "A more accurate zvs criterion for resonant converters," 2022, pp. 2264–2267.

- [16] C. Inc., "C2m0080120d silicon carbide power mosfet," Cree Inc., Tech. Rep., 2019. [Online]. Available: https://assets.wolfspeed.com/uploads/2020/12/C2M0080120D.pdf

- [17] S. K. Roy and K. Basu, "An energy based approach to calculate actual switching loss for sic mosfet from experimental measurement." Institute of Electrical and Electronics Engineers Inc., 6 2021.

- [18] J. A. Anderson, C. Gammeter, L. Schrittwieser, and J. W. Kolar, "Accurate calorimetric switching loss measurement for 900 v 10 mω sic mosfets," *IEEE Transactions on Power Electronics*, vol. 32, pp. 8963–8968, 12 2017.

- [19] T. Liu, T. T. Wong, and Z. J. J. Shen, "A survey on switching oscillations in power converters," pp. 893–908, 3 2020.

- [20] H. Song, D. Xu, and A. J. Zhang, "Re-analysis on zvs condition for llc converter." Institute of Electrical and Electronics Engineers Inc., 6 2021, pp. 1874–1880.