# **Aalborg Universitet**

# A Fully Integrated Darlington-Cascode Distributed Amplifier with m-Derived Matching Sections

Yang, Yong Mu; Lin, Xian Qi; Dong, Jin Sheng; Mei, Peng

Published in:

I E E E Microwave and Wireless Components Letters

Creative Commons License Unspecified

Publication date: 2024

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Yang, Y. M., Lin, X. Q., Dong, J. S., & Mei, P. (in press). A Fully Integrated Darlington-Cascode Distributed Amplifier with m-Derived Matching Sections. *I E E E Microwave and Wireless Components Letters*.

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# A Fully Integrated Darlington-Cascode Distributed Amplifier with m-derived Matching Sections

Yong Mu Yang, Xian Qi Lin, Senior Member, IEEE, Jin Sheng Dong, Peng Hao and Peng Mei

Abstract—This letter proposes a 0.01-40 GHz fully integrated Darlington-Cascode distributed amplifier (DA) in a commercial 0.15  $\mu$ m GaAs pHEMT process. Analysis indicates that the Darlington-Cascode gain cell (DCGC) can simultaneously enhance gain, bandwidth, and output power. The first and last stage of the DA can be equivalent to two m-derived matching sections, optimizing the return loss of the input port. An on-chip DC-fed network is employed for DC biasing of the DA. The chip area of the DA is about 1.8 mm×1.5 mm. measurement results demonstrate that the distributed amplifier (DA) achieves a gain of 11 dB with  $\pm$ 1.5 dB flatness, 14%-24% power-added efficiency (PAE), and 17.2–19.5 dBm saturated output power.

Index Terms—Distributed amplifiers, GaAs pHEMT, Darlington, Cascode, Gain, Wideband.

#### I. INTRODUCTION

amplifiers (DAs), multioctave bandwidth [1][2][3], are attractive circuit blocks for applications such as optical links, highresolution imaging, radar and measurement instrumentation. Advanced integrated circuit processes, such as InP [4][5][6], SOI [7], etc., boasting high cutoff frequencies  $(f_T)$ , can significantly augment the bandwidth of DAs. However, with a fixed  $f_T$ , the gain, bandwidth, and power consumption of DAs become a set of trade-offs. Introducing a gate series capacitor can broaden the bandwidth of DAs, albeit at the expense of gain [8]. While cascaded topology enables high gain [9], it does so at the cost of increased power consumption. Nonuniform configuration [10][11][12] improves power-added efficiency (PAE), but the tapered output impedance restricts the effective use of the number of stages. The stack gain cells [13] can increase the output power of the DA but at the cost of a high voltage power supply. The DC bias of DAs is also a challenge, due to the wideband operation characteristics, external bias tees are usually required, which leads to larger circuit module size. Distributed choke inductor in [14] is used to feed the DA, however, this method significantly increases the chip area. Active bias termination topology in [15] is used to provide bias tee free DA, however, it will decrease the linearity of DA and increase the power consumption.

This work was supported by in part by the KRDP of Zhejiang Province (No. 2022C01093), and in part by NSFC (Nos. U1966201 and 62271122) and in part by SRF for YDRI of UESTC, Huzhou (Nos. U05220004, U04210016, and U032200112)

Yong Mu Yang, Xian Qi Lin and Jin Sheng Dong and Peng Hao are with the Yangtze Delta Region Institute (Huzhou), University of Electronic Science and Technology of China, Huzhou 313001, P. R. China (e-mail: yym@csj.uestc.edu.cn; xqlin@uestc.edu.cn; dongjs@csj.uestc.edu.cn; penghao@csj.uestc.edu.cn).

Peng Mei is with the Department of Electronic Systems, Aalborg University, 9220 Aalborg, Denmark. (mei@es.aau.dk)

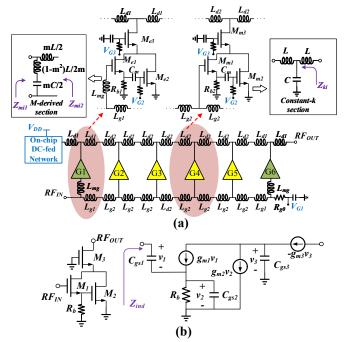

Fig. 1. (a) Schematic of the proposed DA (b) simplified topology and small-signal equivalent circuit of the DCGC.

This letter presents a fully integrated Darlington-Cascode distributed amplifier (DA) operating from 0.01 to 40 GHz, implemented in a commercial 0.15  $\mu$ m GaAs pHEMT process. The incorporation of the Darlington-cascode gain cell serves to concurrently improve the gain and bandwidth of the DA. By accommodating larger device sizes and higher operating currents without compromising bandwidth, the gain cell also enhances the output power of the DA. The first and last gain cells of the DA can be equivalent to two m-derived matching sections, maintaining the input and output return loss better than 15 dB across the entire frequency range. Additionally, an on-chip DC-fed network is proposed to supply the drain DC bias and ensure a constant impedance termination for the output artificial transmission line (ATL), thereby eliminating the need for an external bias tee.

## II. ANALYSIS AND CIRCUIT DESIGN

### A. Darlington-Cascode Gain Cells

A typical distributed amplifier (DA) comprises n gain cells and input/output artificial transmission lines (ATLs). The bandwidth of a DA is primarily dictated by the cutoff frequency  $\omega_C$  of the ATLs, which is defined as:

$$\omega_C = 2/CR_0 , \qquad (1)$$

where C denotes the input or output equivalent shunt

1

capacitance of the gain cell, and  $R_0$  is the nominal characteristic impedance of the ATL, usually set to  $50\Omega$  for impedance matching. Since the input equivalent capacitance of the gain cell is larger than the output equivalent capacitance [14], the bandwidth of a DA is primarily constrained by the cutoff frequency of the input ATL. Therefore, from (1), bandwidth expansion can be achievable by reducing the shunt capacitance. A common strategy involves diminishing the overall device size of the gain cell, thereby reducing the equivalent capacitance. For an ideal DA, its gain  $G_{dis}$  can be expressed as:

$$G_{dis} = G_m^2 N^2 R_{0q} R_{0d} / 4 (2)$$

where,  $G_m$  is the equivalent transconductance of the gain cell, N is the number of gain cells, and  $R_{0g}$  and  $R_{0d}$  are the nominal characteristic impedances of the input and output ATLs, respectively. As  $G_m$  is proportional to the device size, adopting smaller devices diminishes the gain of the DA.

Fig.1(a) illustrates the schematic of the proposed DA as with the Darlington-Cascode gain cells (DCGCs). The DA comprises six gain cells, including four middle gain cells denoted as G2 to G5 and the first and last gain cells denoted as G1 and G6. As shown in Fig. 1(a) the DCGC consists of three transistors along with a capacitor  $C_m$  for DC decoupling and a resistor  $R_b$  for bias and stability. Fig.1(b) shows the simplified topology and small-signal equivalent circuit of the DCGC. From the small-signal equivalent circuit the input impedance of DCGC can be expressed as:

$$Z_{ind} = 1/j\omega C_{gs1} + 1/j\omega C_1 + 1/j\omega C_2 + R_1 + R_2 \ . \eqno(3)$$

The parameters  $C_1$ ,  $C_2$ ,  $R_1$ ,  $R_2$  in (3) are given by:

$$C_1 = C_{gs1} (\omega^2 C_{gs2}^2 + g_b^2) / g_{m1} g_b \eqno(4)$$

$$C_2 = g_b^2/\omega^2 C_{qs2} + C_{qs2} \eqno(5)$$

$$R_1 = g_b/(\omega^2 C_{qs2}^2 + g_b^2) \tag{6}$$

$$R_2 = -g_{m1}C_{gs2}/C_{gs1}(\omega^2 C_{gs2}^2 + g_b^2)$$

(7)

where  $g_{m1}$  and  $g_{m2}$  are the transconductance of  $M_l$  and  $M_2$ ,  $C_{gs1}$  and  $C_{gs2}$  are the gate-source capacitance of  $M_l$  and  $M_2$ , and  $g_b$  is the conductance of  $R_b$ . As indicated in equation (3), the input impedance of the DCGC can be conceptualized as a series of three capacitors, namely,  $C_{gs1}$ ,  $C_1$ ,  $C_2$ , and two resistors, namely,  $R_1$ ,  $R_2$ . The total input capacitance of the gain cell is less than that of  $M_l$ . When  $R_b$  is sufficiently large that  $g_b \approx 0$ , and assuming similar sizes for  $M_l$  and  $M_2$ , then the total input capacitance is expressed as:

$$C_{in} = C_{gs1}C_{gs2}/(C_{gs1} + C_{gs2}) \approx C_{gs1}/2 \eqno(8)$$

Thus, a distributed amplifier employing DCGCs can achieve a wider bandwidth due to the reduction in input capacitance. The equivalent transconductance  $G_m$  of the DCGC can also be obtained from the small-signal equivalent circuit of Fig.1(b), which expressed as:

$$G_m = g_{m1}(g_{m2} + g_b)/(g_{m1} + g_b) \eqno(9)$$

Similarly, when  $g_b$  is much smaller than  $g_{m1}$  and  $g_{m2}$ , it can be given as  $G_m \approx g_{m2}$ . The transconductance of the gain cell is therefore mainly determined by  $g_{m2}$ . Thus, adjusting the sizes of  $M_l$ ,  $M_2$ , and  $M_3$  in the DCGC allows for individual tuning of the gain, bandwidth, and output power. For instance,

$M_1$  should have a smaller periphery to decrease input capacitance for bandwidth extension, while  $M_2$  should possess a larger periphery to enhance  $G_m$  and boost the gain. The common-gate transistor,  $M_3$ , is utilized to further enhance the gain, offer suitable output capacitance, and increase the isolation between the input and output ATLs.

From (7), it's important to note that  $R_2$  is a negative resistor. If  $g_b$  is very small that the total input resistance  $R_1+R_2\approx -g_{m1}/\omega^2C_{gs2}C_{gs1}$ . Due to the presence of negative resistance, this could lead to instability in the DA. However, if  $g_b$  is too large, it can lead to a decrease in gain. Therefore, the value of  $g_b$  needs to be chosen properly to balance stability and gain considerations [16].

#### B. M-derived Matching Sections

Traditionally, the ATL can be regarded as a cascade of n constant-k filter sections [17]. As shown in Fig. 1(a), for the input ATL, the gain cells G2 to G5 can be equivalent to four constant-k filter sections. The constant-k filter section is a symmetric two-port network, which exhibits equal input and output image impedances, defined as:

$$Z_{ki} = R_0 \sqrt{1 - (\omega^2/\omega_C^2)} \tag{10} \label{eq:2}$$

From (10), the frequency dependence of the image impedance of the constant-k filter section can result in impedance mismatch at higher frequencies, given the DA's fixed terminal impedance at 50 Ohm. Gain cells G1 and G6, with respect to the input ATL, can be equivalent to bisected m-derived matching sections. As shown in Fig. 1(a), the input and output image impedances  $Z_{mi1}$  and  $Z_{mi2}$  of the bisected m-derived matching section are defined as:

$$Z_{mi1} = R_0 [1 - (1-m^2)(\omega/\omega_C^{})^2]/\sqrt{1-(\omega/\omega_C^{})^2} \eqno(4)$$

$$Z_{mi2} = Z_{ki} = R_0 \sqrt{1 - (\omega^2 / \omega_C^2)}$$

(5)

where  $0 < m \le 1$ . The output image impedance  $Z_{mi2}$  remains the same as (1). The input image impedance  $Z_{mi1}$  allows us to use m to minimize its frequency dependence. An m value of 0.6 generally gives the best results [18]. Adjusting the device size of G1 and the inductance values of  $L_{mg}$  and  $L_{g1}$  allows achieving an m value of 0.6, thereby reducing the frequency dependence of the input ATL's image impedance.

#### C. Circuit Implementation

The proposed DAs were designed using a commercial 0.15um GaAs pHEMT process with  $100\mu m$  substrate thickness. The  $f_T$  of 90 GHz, and the high transconductance of 460 mS/mm, make it suitable for broadband DA design. The transistors  $M_{el}$ ,  $M_{e2}$  and  $M_{e3}$  of the first and last gain cells have periphery of  $2\times25\text{um}$ ,  $2\times75\text{um}$ , and  $2\times45\text{um}$ , respectively. The transistors  $M_{ml}$ ,  $M_{m2}$  and  $M_{m3}$  of the middle gain cells have periphery of  $2\times50\text{um}$ ,  $2\times100\text{um}$ ,  $2\times70\text{um}$ , respectively. The inductor  $L_{mg}$  is implemented using a microstrip line with a length of  $25\mu m$  and a width of  $7\mu m$ . Similarly, the series inductors  $L_{gl}$ ,  $L_{g2}$ ,  $L_{dl}$ , and  $L_{d2}$  are realized using microstrip lines with lengths of  $200\mu m$ ,  $248\mu m$ ,  $240\mu m$ ,  $364\mu m$ , and widths of  $7\mu m$ ,  $7\mu m$ ,  $12\mu m$ ,  $12\mu m$ , respectively.

## > REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

**Fig. 2.** (a) Schematic and (b) layout of the on-chip DC-fed network. (c) Simulated input impedance of the on-chip DC-fed network.

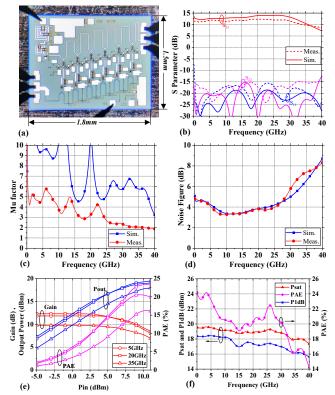

Fig. 3. (a) Micrograph of the DA chip. (b) Measured S-parameters. (c) Measured stability factor ( $\mu$ -factor). (d) Measured noise figure. (e) Measured Pout, Gain, PAE versus input power. (f) Measured Psat, P1dB, PAE versus frequency.

The resistance value of  $R_b$  is chosen to be 32 $\Omega$ , considering stability and overall gain. To ensure impedance matching of the ATLs, the right end of the input ATL is connected to a 50 $\Omega$  resistor, grounded through a capacitor. The left end of the output ATL is connected to an on-chip DC-fed network, whose schematic and layout are shown in Fig. 2(a) and Fig. 2(b). The DC current can directly flow into the amplifier through the series inductor, which, due to its low resistance, minimally increases DC power consumption. For AC signals the DC-fed network acts as a constant impedance termination, with its impedance's real part, as shown in Fig. 2(c), ranging from 40-60 $\Omega$  across the frequency range of 10MHz to 40GHz.

#### III. MEASUREMENT RESULTS

The micrograph of the chip is shown in Fig. 3(a), and the chip occupies an area of 1.8 mm×1.5 mm. The DA is on-wafer measured with the supply voltage V<sub>DD</sub> of 4V with a quiescent current of 60mA. All transistors in the DA utilize an on-chip resistive voltage-divider network for gate biasing.

TABLE I PERFORMANCE COMPARISON WITH THE STATE-OF-THE-ART

| Ref.         | Tech.                | BW<br>(GHz) | Peak<br>P1dB<br>(dBm) | P <sub>dc</sub><br>(mW) | Size<br>(mm²) | Gain<br>(dB)* | Fmax<br>(GHz) | FOM   |

|--------------|----------------------|-------------|-----------------------|-------------------------|---------------|---------------|---------------|-------|

| [10]<br>MWTL | 0.15um<br>GaAs       | 0.8-18      | 19.2                  | 330                     | 4             | 10            | 220           | 6.23  |

| [11]<br>TCAS | 0.1um<br>GaAs        | 2-45        | 9.5                   | 110                     | 1.88          | 15.2          | 180           | 11.1  |

| [15]<br>TMTT | GaAs<br>HEMT–<br>HBT | DC-43.5     | 8                     | 225                     | 2             | 8.2           | 70            | 4.47  |

| [6]<br>TMTT  | InP<br>HBT           | 3-230       | 17.6                  | 726                     | 1.28          | 13            | 550           | 14.6  |

| [3]<br>MWCL  | 0.1um<br>GaAs        | 0.01-22     | 20                    | 3040                    | 3.75          | 23            | 240           | 4.    |

| [13]<br>IMS  | 45nm<br>SOI          | 1-17        | 18                    | 427                     | 1.14          | 15.8          | 300           | 4.85  |

| [5]<br>IMS   | InP<br>HBT           | DC-90       | 19                    | 400                     | 1.12          | 10            | 380           | 14.8  |

| THIS<br>WORK | 0.15um<br>GaAs       | DC-40       | 18.3                  | 240                     | 2.7           | 11            | 220           | 18.09 |

<sup>\*</sup> The gain listed in the table represents the average gain in band.

The gate-source voltages for transistors  $M_{el}$  and  $M_{ml}$  are set to -0.85V,  $M_{e2}$  and  $M_{m2}$  to -1V, and  $M_{e3}$  and  $M_{m3}$  to -0.8V. The measured S-parameters are presented in Fig. 3(b). The average small signal gain  $(S_{21})$  is 11 dB from 0.01 to 40 GHz with the gain flatness of  $\pm 1.5$ dB. The input return loss is better than 15 dB, which benefits from the m-derived matching section. The measured stability factor (µ-factor) is greater than 2 up to 40 GHz [Fig. 3(c)]. The measured noise figure (NF) is < 8.2 dB at 0.01– 40 GHz with a minimum of 3.1 dB at 13 GHz [Fig. 3(d)]. The continuous-wave (CW) large-signal performance versus frequency is shown in Fig. 3(e) and Fig. 3(f). The DA achieves an average Psat and P1dB of 18.5 and 17 dBm, respectively. The DA demonstrates a peak Psat and P1dB of 19.5 and 18.3 dBm, respectively, around 4 GHz. The maximum and minimum PAE are 24% at 4GHz and 14% at 40GHz. The performance summary and comparison of the proposed DA with other DAs are carried out in Table I. A figure-of-merit (FOM) in [13] is proposed as:

$$FOM = \frac{Gain[abs] \cdot BW_{3dB}[GHz] \cdot P1dB[mW]}{P_{dc}[mW] \cdot f_{max}[GHz]} (\%) . \quad (13)$$

Among the literature presented in Table I, the proposed DA can achieve best FOM.

#### IV. CONCLUSION

This letter presents a 0.01-40 GHz Darlington-Cascode distributed amplifier fabricates using a 0.15  $\mu$ m GaAs process. Measurement shows it achieves 11 dB gain and 14%-24% PAE with 17.2–19.5 dBm saturated output power. The results show that the Darlington-Cascode gain cell has great potential for high gain bandwidth product distributed power amplifier designs.

#### REFERENCES

[1] G. Nikandish, R. B. Staszewski and A. Zhu, "The (R)evolution of Distributed Amplifiers: From Vacuum Tubes to Modern CMOS and GaN ICs," in IEEE Microwave Magazine, vol. 19, no. 4, pp. 66-83, June 2018, doi: 10.1109/MMM.2018.2813838.

4

[18]D. M. Pozar, Microwave Engineering 4th edition. New York: John Wiley

& Sons, Inc,2011.

- [2] K. W. Kobayashi, D. Denninghoff and D. Miller, "A Novel 100 MHz-45 GHz Input-Termination-Less Distributed Amplifier Design With Low-Frequency Low-Noise and High Linearity Implemented With A 6 Inch 0.5µm GaN-SiC Wafer Process Technology," in IEEE Journal of Solid-State Circuits, vol. 51, no. 9, pp. 2017-2026, Sept. 2016, doi: 10.1109/JSSC.2016.2558488.

- [3] A. A. Babenko, G. Lasser and Z. Popović, "0.01–22-GHz Feedback-Stabilized Single-Supply GaAs Cascode Distributed Amplifiers," in IEEE Microwave and Wireless Components Letters, vol. 31, no. 12, pp. 1291-1294, Dec. 2021, doi: 10.1109/LMWC.2021.3111133.

- [4] N. L. K. Nguyen, C. Cui, D. P. Nguyen, A. N. Stameroff and A. -V. Pham, "A 7–115-GHz Distributed Amplifier With 24-dBm Output Power Using Quadruple-Stacked HBT in InP," in IEEE Microwave and Wireless Technology Letters, vol. 33, no. 6, pp. 715-718, June 2023, doi: 10.1109/LMWT.2023.3237683.

- [5] D. P. Nguyen, N. L. K. Nguyen, A. N. Stameroff and A. -V. Pham, "A Highly Linear InP Distributed Amplifier Using Ultra-wideband Intermodulation Feedforward Linearization," 2018 IEEE/MTT-S International Microwave Symposium - IMS, Philadelphia, PA, USA, 2018, pp. 1356-1359, doi: 10.1109/MWSYM.2018.8439328.

- [6] P. T. Nguyen, N. L. K. Nguyen, N. S. Wagner, A. Stameroff and A. -V. Pham, "A Balanced Darlington Cell for a 3–230-GHz InP Distributed Amplifier," in IEEE Transactions on Microwave Theory and Techniques, doi: 10.1109/TMTT.2023.3339017.

- [7] O. El-Aassar and G. M. Rebeiz, "A 120-GHz Bandwidth CMOS Distributed Power Amplifier With Multi-Drive Intra-Stack Coupling," in IEEE Microwave and Wireless Components Letters, vol. 30, no. 8, pp. 782-785, Aug. 2020, doi: 10.1109/LMWC.2020.3001261.

- [8] C. Campbell, C. Lee, V. Williams, M. Kao, H. Tserng, P. Saunier, and T. Balisteri, "A wideband power amplifier MMIC utilizing GaN on SiC HEMT technology," IEEE J. Solid-State Circuits, vol. 44, no. 10, pp. 2640–2647, Oct. 2009

- [9] O. El-Aassar and G. M. Rebeiz, "A Cascaded Multi-Drive Stacked-SOI Distributed Power Amplifier With 23.5 dBm Peak Output Power and Over 4.5-THz GBW," in IEEE Transactions on Microwave Theory and Techniques, vol. 68, no. 7, pp. 3111-3119, July 2020, doi: 10.1109/TMTT.2020.2984226.

- [10]S. Chen et al., "A 0.8-to-18 GHz Nonuniform Distributed PA Using Reconfigurable Bias Choke in 0.15 μm GaAs pHEMT," in IEEE Microwave and Wireless Technology Letters, vol. 33, no. 9, pp. 1309-1312, Sept. 2023, doi: 10.1109/LMWT.2023.3295820.

- [11]G. Nikandish and A. Medi, "A 40-GHz Bandwidth Tapered Distributed LNA," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 11, pp. 1614-1618, Nov. 2018, doi: 10.1109/TCSII.2017.2758861.

- [12]I. Ju, S. Lee and J. D. Cressler, "An Efficient, Broadband SiGe HBT Non-Uniform Distributed Power Amplifier Leveraging a Compact, Two-Section λ/4 Output Impedance Transformer," in IEEE Transactions on Microwave Theory and Techniques, vol. 70, no. 7, pp. 3524-3533, July 2022, doi: 10.1109/TMTT.2022.3168546.

- [13]L. Gao, Q. Ma and G. M. Rebeiz, "A 1–17 GHz Stacked Distributed Power Amplifier with 19–21 dBm Saturated Output Power in 45nm CMOS SOI Technology," 2018 IEEE/MTT-S International Microwave Symposium - IMS, Philadelphia, PA, USA, 2018, pp. 454-456, doi: 10.1109/MWSYM.2018.8439435.

- [14]C. Ballı, A. Değirmenci, A. Aktuğ and A. Atalar, "Wideband Distributed Choke Inductor for Distributed Power Amplifiers," in IEEE Microwave and Wireless Technology Letters, vol. 33, no. 5, pp. 539-542, May 2023, doi: 10.1109/LMWT.2022.3233061.

- [15]H. -Y. Chang, Y. -C. Liu, S. -H. Weng, C. -H. Lin, Y. -L. Yeh and Y. -C. Wang, "Design and Analysis of a DC-43.5-GHz Fully Integrated Distributed Amplifier Using GaAs HEMT-HBT Cascode Gain Stage," in IEEE Transactions on Microwave Theory and Techniques, vol. 59, no. 2, pp. 443-455, Feb. 2011, doi: 10.1109/TMTT.2010.2092786.

- [16]G. Nikandish and A. Medi, "Design and Analysis of Broadband Darlington Amplifiers With Bandwidth Enhancement in GaAs pHEMT Technology," in IEEE Transactions on Microwave Theory and Techniques, vol. 62, no. 8, pp. 1705-1715, Aug. 2014, doi: 10.1109/TMTT.2014.2328972.

- [17]J. B. Beyer, S. N. Prasad, R. C. Becker, J. E. Nordman and G. K. Hohenwarter, "MESFET Distributed Amplifier Design Guidelines," in IEEE Transactions on Microwave Theory and Techniques, vol. 32, no. 3, pp. 268-275, Mar. 1984, doi: 10.1109/TMTT.1984.1132664.