## **Aalborg Universitet**

# An Analysis of the PLLs With Secondary Control Path

Golestan, S.; Ramezani, M.; Guerrero, J.M.

Published in: I E E E Transactions on Industrial Electronics

DOI (link to publication from Publisher): 10.1109/TIE.2013.2289904

Publication date: 2014

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Golestan, S., Ramezani, M., & Guerrero, J. M. (2014). An Analysis of the PLLs With Secondary Control Path. I E E E Transactions on Industrial Electronics, 61(9), 4824-4828 . https://doi.org/10.1109/TIE.2013.2289904

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# An Analysis of the PLLs With Secondary Control Path

Saeed Golestan, Member, IEEE, Malek Ramezani, Member, IEEE, and Josep M. Guerrero, Senior Member, IEEE

Abstract-The phase-locked loops (PLLs) are widely used in different areas of applications particularly for synchronization and control purposes in grid connected applications. A major challenge associated with the PLLs is how to improve their dynamic performance without jeopardizing their stability and filtering capability. Recently, some approaches based on adding a secondary control path (SCP) to the PLL structure have been proposed to deal with this challenge. The objective of this paper is to briefly analyze these approaches. The study starts with an overview of the PLLs with SCP. The paper proceeds with the small-signal modeling of some of these PLLs, which significantly simplifies the analysis. Using these models, the effects of adding the SCP on the PLL structure are studied. The obtained results show that the SCP may not be a practical approach to improve the PLL dynamic performance mainly because it aggravates the stability problem.

${\it Index\ Terms} {\color{red} -} Dynamic\ performance,\ phase\ locked\ loop\ (PLL),\ synchronization.$

#### I. Introduction

ENERALLY speaking, a PLL is a closed-loop feedback control system which synchronizes its output signal in frequency as well as in phase with an input signal [1]. The phase detector (PD), the loop filter (LF), and the voltage controlled oscillator (VCO) are the main building blocks of a typical PLL [2].

A major challenge associated with the PLLs is how to improve their dynamic performance without jeopardizing their stability and filtering capability. To overcome this challenge, several approaches have been proposed in literature, which are reviewed in the following.

To provide a fast dynamic response and, at the same time, to achieve a high disturbance rejection capability, Freijedo *et al.* [3] suggest to add one or more lead compensators in cascade with the LF in the forward path of the PLL. The suggested lead compensators are second order and have pairs of purely imaginary poles and zeros. So, they provide the selective cancellation like a notch filter without lagging the loop below  $-180^{\circ}$  (stability limit). Thus, the PLL can achieve a high bandwidth (a fast dynamic response) without jeopardizing the stability and the filtering capability.

Manuscript received June 14, 2013; revised August 11, 2013 and September 22, 2013; accepted October 23, 2013. This work was supported in part by the Abadan Branch-Islamic Azad University.

Copyright © 2013 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

- S. Golestan and M. Ramezani are with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Abadan 63178-36531, Iran (e-mail: s.golestan@ieee.org; m.ramezani.1982@ieee.org).

- J. M. Guerrero is with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: joz@et.aau.dk).

To improve the PLL dynamic performance during the startup and phase jumps without degrading its filtering capability, an effective method based on adaptive adjustment of the gain of the frequency estimation loop is suggested by Karimi Ghartemani *et al.* [4]. This approach has a general form and can be applied to a wide variety of three-phase and single-phase PLLs.

1

To provide a fast phase angle re-tracking during the transients, Thacker *et al.* [5] suggest to add a frequency feedback (FFB) term to the PD. During the transients, the FFB term dynamically adjusts the LF gains, while keeping the LF zero fixed, thus improves the PLL dynamic response. This approach, similar to the Karimi's approach [4], is applicable to a wide range of single-phase and three-phase PLLs.

To improve the stability and dynamic performance of the pre-filtered synchronous reference frame PLLs (SRF-PLL) while maintaining good filtering capability using a derivative filtered proportional-integral-derivative (PID) controller as the LF is suggested in [6]. Compared with the commonly adopted proportional-integral (PI) type LF, the PID-type LF provides an additional degree of freedom, and enables the designer to compensate the phase delay introduced by the pre-filtering stage of the PLL.

In recent years, some approaches based on adding a secondary control path (SCP) to the PLL structure have been proposed in literature [7]-[10]. Supposedly, the SCP improves the PLL dynamic performance without affecting its stability condition. However, no formal analysis has yet been performed to support this claim.

This paper deals with the analysis of the PLLs with SCP. The study starts with a brief overview of these PLLs. The small-signal modelling of these PLLs are then presented which simplifies the analysis. Using these models, the effects of adding the SCP on the PLL structure are briefly studied. The obtained results show that adding the SCP to the PLL structure may not be a practical approach to improve its dynamic performance mainly because it aggravates the stability problem.

#### II. OVERVIEW

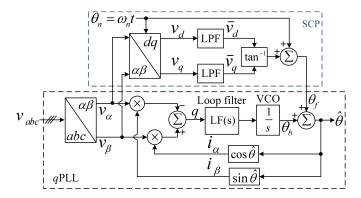

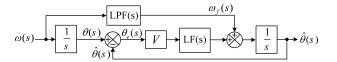

Fig. 1 shows the basic scheme of the proposed PLL by Riccardo *et al* [7], which includes a classical quadrature PLL (qPLL) and a SCP. The SCP operates in a dq reference frame, rotating synchronously with the grid voltage nominal angular frequency  $\omega_n$ , and provides an estimation of the grid voltage angle. The authors in [7] claim that the suggested SCP improves the PLL dynamic response without affecting its stability condition. To justify this, the small-signal model

Fig. 1. Basic scheme of the feedforward qPLL (FFqPLL) [7].

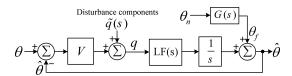

Fig. 2. Small signal model of the FFqPLL [7].

of the FFqPLL is obtained as shown in Fig 2. In this model, the action of SCP is modeled by an unknown transfer function, named G(s). Then, it is discussed that the poles of G(s) are external to the feedback loop. Consequently, the presence of the SCP has no effect on the qPLL stability.

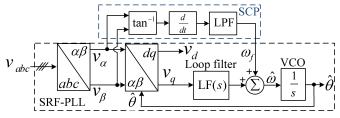

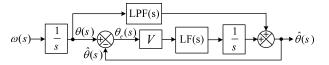

Fig. 3 shows the proposed PLL by Rani *et al.* [8], which includes a conventional SRF-PLL and a SCP. In this PLL, referred to as the feedforward frequency PLL (FPLL), the VCO's center frequency is dynamically adjusted by the SCP. The authors in [8] claim that the suggested SCP improves the PLL dynamic performance without jeopardizing its stability condition.

In [9] and [10], a PLL referred to as the all-digital PLL (ADPLL) is proposed. The ADPLL can be understood as a traditional digital PLL (DPLL) which a SCP has been included in its structure. The SCP is a period detector which makes the center frequency changeable. Its main purpose, as mentioned in [9] and [10], is to improve the DPLL tracking speed. In the small-signal model of the ADPLL, the dynamics of the SCP has been neglected (see Fig. 5 in [9] and [10]).

#### III. SMALL-SIGNAL MODELING

In this section, the small-signal modeling of the FPLL and the FFqPLL are presented. These models consider the dynamics of the SCPs. Regarding the ADPLL, this modeling cannot be done, as no detailed information about the implementation of SCP is given in [9] and [10].

#### A. FPLL

For the sake of simplicity, let the three-phase input voltages of the FPLL be of the form

$$v_a(t) = V \cos (\omega t + \phi)$$

$$v_b(t) = V \cos(\omega t + \phi - 2\pi/3)$$

$$v_c(t) = V \cos(\omega t + \phi + 2\pi/3)$$

(1)

Fig. 3. Basic scheme of the feedforward frequency PLL (FPLL) [8].

Fig. 4. The small-signal model of the conventional SRF-PLL.

where V,  $\omega$ , and  $\phi$  are the input voltages amplitude, angular frequency, and initial phase-angle, respectively.

Applying the Clarke transformation to the three-phase input voltages (1) yields the  $\alpha\beta$  coordinate voltages as

$$\begin{bmatrix} v_{\alpha}(t) \\ v_{\beta}(t) \end{bmatrix} = \begin{bmatrix} V\cos(\theta) \\ V\sin(\theta) \end{bmatrix}. \tag{2}$$

According to Fig. 3, the SCP output signal can be expressed in the Laplace domain as

$$\omega_f(s) = \text{LPF}(s) \times L\left(\frac{d\left\{\tan^{-1}\left(v_\beta\left(t\right)/v_\alpha\left(t\right)\right)\right\}}{dt}\right). \quad (3)$$

where L denotes the Laplace operator.

Substituting the  $\alpha\beta$  coordinate voltages (2) into (3), yields

$$\omega_f(s) = \text{LPF}(s) \times L\left(\frac{d\left\{\tan^{-1}\left(\tan(\theta)\right)\right\}}{dt}\right)$$

$$= \text{LPF}(s) \times L\left(\underbrace{\frac{d\left\{\theta\right\}}{dt}}\right) = \text{LPF}(s) \times \omega(s). \quad (4)$$

Using (4), and the small-signal model of the conventional SRF-PLL as shown in Fig. 4, the small-signal model of the FPLL can be obtained as shown in Fig. 5. An alternative mathematically-equivalent representation of this model is shown in Fig. 6.

#### B. FFqPLL

The small-signal modeling of the FFqPLL is performed under the same simplifying assumption as in the case of FPLL, i.e., considering the input voltages as an undistorted and balanced three-phase system.

As shown in Fig. 1, the dq coordinate voltages in the SCP are obtained by applying the Park transformation with a rotating angle of  $\theta_n = \omega_n t$  to the  $\alpha\beta$  coordinate voltages, i.e.,

$$\begin{bmatrix} v_d(t) \\ v_q(t) \end{bmatrix} = \begin{bmatrix} \cos(\theta_n) & \sin(\theta_n) \\ -\sin(\theta_n) & \cos(\theta_n) \end{bmatrix} \begin{bmatrix} V\cos(\theta) \\ V\sin(\theta) \end{bmatrix}$$

$$= \begin{bmatrix} V\cos(\theta - \theta_n) \\ V\sin(\theta - \theta_n) \end{bmatrix}$$

(5)

These dq coordinate voltages are then passed through two

Fig. 5. The small-signal model of the FPLL.

Fig. 6. Alternative mathematically-equivalent representation of the small-signal model of Fig. 5.

low-pass filters (LPFs). The SCP output signal  $\theta_f$  is finally obtained by applying the inverse tangent operation to the outputs of the LPFs, and adding  $\theta_n$  to the result. It is very difficult to analytically obtain a compact expression for  $\theta_f$ . However, based on extensive simulation studies, we have found that it can be approximated by

$$\theta_f(s) \approx LPF(s) \left[\theta(s) - \theta_n(s)\right] + \theta_n(s)$$

(6)

when the grid voltage frequency is close to its nominal value; the more closer the grid frequency to its nominal value, the more accurate the approximation.

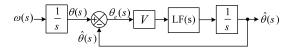

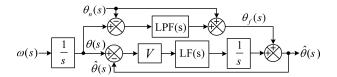

Using (6), and considering that the *q*PLL and the conventional SRF-PLL are actually the same systems, the small-signal model of the FF*q*PLL can be obtained as shown in Fig. 7, which is very similar to the FPLL's small-signal model (Fig. 6).

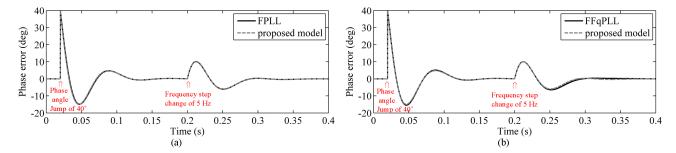

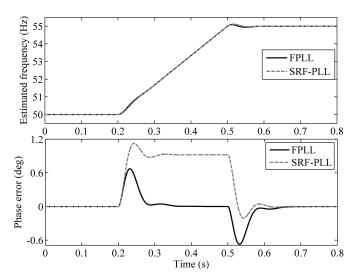

To evaluate the accuracy of the obtained small-signal models, a performance comparison between the PLLs under study and their small-signal models is carried out. In this study, a PI controller as the LF (i.e., LF(s) =  $k_p + k_i/s$  where  $k_p$  and  $k_i$  are the proportional and integral gains, respectively), and a first order LPF as the filter of the SCP (i.e., LPF(s) =  $\omega_p/(s+\omega_p)$ , where  $\omega_p$  is the cutoff frequency) is considered. The values of the control parameters are summarized in Table I. The obtained results are shown in Fig. 8. It can be observed that, for both PLLs, the small-signal model can accurately predict the actual PLL behavior.

#### IV. EFFECTS OF SCP

This section deals with the study of the effects caused by SCP. It was shown that the FPLL and the FFqPLL have almost same small-signal models. Therefore, throughout this study, the FPLL's small-signal model is considered.

TABLE I PLLS PARAMETERS VALUES.

| Parameter                     | Value                   |

|-------------------------------|-------------------------|

| Proportional gain, $k_p$      | 70                      |

| Integral gain, $k_i$          | 6500                    |

| Cutoff frequency, $\omega_p$  | 30 rad/s                |

| Amplitude, $V$                | 1 pu                    |

| Sampling frequency, $f_s$     | 10 kHz                  |

| Nominal frequency, $\omega_n$ | $2\pi 50 \text{ rad/s}$ |

Fig. 7. The small-signal model of the FFqPLL

#### A. Stability

The aim of this section is to answer this question: Does the SCP affect the PLL stability?

It is clear from Fig. 5 that without the SCP, the FPLL is the conventional SRF-PLL. Therefore, according to Fig. 4, the open-loop transfer function can be obtained as

$$G_{ol}^{SRF} = V LF(s) \frac{1}{s}.$$

(7)

3

In most applications, a PI controller is selected as the LF, i.e.,  $LF(s) = k_p + k_i/s$ . With this selection, (7) can be rewritten as

$$G_{ol}^{SRF} = V \frac{k_p s + k_i}{s^2}.$$

(8)

which describes a type-2 control system. Notice that a type-N control system is characterized by presence of N poles at the origin in its open-loop transfer function [11].

Now, the open-loop transfer function with considering the SCP is obtained. From Fig. 5, and by considering the LPF block in the SCP as a first-order LPF, i.e.,  $LPF(s) = \omega_p/(s+\omega_p)$ , the open-loop transfer function of the FPLL can be obtained as

$$G_{ol}^{\text{FPLL}} = \frac{\hat{\theta}}{\theta_e} = \frac{(Vk_p + \omega_p) s^2 + V(k_i + k_p\omega_p) s + Vk_i\omega_p}{s^3}$$

(9)

By comparing (9) with (8), it can be concluded that the SCP increases the type of the tracking loop by one. It is known that increasing the type of tracking loop aggravates the stability problem [12], [13]. Therefore, contrary to what was reported in [7] and [8], the SCP affects the PLL stability.

#### B. Static Performance

In this section, the effect of the SCP on the steady-state performance of the PLL is investigated.

It was shown in previous section that the SCP increases the type of tracking loop by one. It is well-known that increasing the type of tracking loop enables the control system to track faster reference signals with a lower steady-state error [13]. Therefore, it can be concluded that, in terms of the steady-state performance, the SCP improves the PLL performance. For example, Fig. 9 provides a comparison between the SRF-PLL (FPLL without SCP) and the FPLL when the grid voltage frequency changes linearly with time. The control parameters are given in Table I. As shown, the FPLL yields a zero steady-state phase error during frequency ramping interval, while the SRF-PLL has a steady-state phase error of about 0.9°. This result was expected as the FPLL is a type-3 control system.

Fig. 8. Performance comparison between (a) the FPLL and its small-signal model, (b) the FFqPLL and its small-signal model under a phase-angle jump of  $+40^{\circ}$  and a frequency step change of +5 Hz.

Fig. 9. Performance comparison between the FPLL and SRF-PLL (FPLL without SCP) when the grid frequency changes linearly with time.

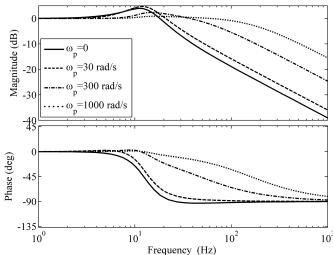

Fig. 10. Bode plots of the closed-loop transfer function (10) for V=1 pu,  $k_p=70,\,k_i=6500$  and four different values of  $\omega_p:\omega_p=0$  (solid line), 30 rad/s (dashed line), 300 rad/s (dash-dotted line), and 1000 rad/s (dotted line)

#### C. Dynamic Performance

In this section, the effect of SCP on the PLL dynamic performance is studied.

From Fig. 5, the closed loop transfer function of the FPLL can be obtained as

$$G_{cl}^{\text{FPLL}}(s) = \frac{\hat{\theta}}{\theta}$$

$$= \frac{(Vk_p + \omega_p) s^2 + V(k_i + k_p\omega_p) s + Vk_i\omega_p}{s^3 + (Vk_p + \omega_p) s^2 + V(k_i + k_p\omega_p) s + Vk_i\omega_p}$$

(10)

Fig. 10 shows the Bode plots of the closed-loop transfer function (10) for V=1 pu,  $k_p=70$ ,  $k_i=6500$ , and four different values of  $\omega_p\colon \omega_p=0$ , 30, 300, and 1000 rad/s. Notice that  $\omega_p=0$  corresponds to disconnecting the SCP from FPLL. From Fig. 10, it can be observed that the presence of the SCP increases the PLL closed-loop bandwidth, and in this way improves the PLL dynamic performance. The higher the cutoff frequency  $\omega_p$ , the higher the closed-loop bandwidth, and the faster the dynamic response.

It should be emphasized here that all conclusions drawn in section IV are for the case of using the PI-type LF in the PLL control loop, and they may not be valid as a general rule.

#### V. SCP-LESS EQUIVALENT OF PLL WITH SCP

It is shown in this section that adding the SCP to the PLL is mathematically equivalent to changing its LF.

From Fig. 5, the open-loop transfer function of the FPLL can be obtained in general form as

$$G_{ol}^{\text{FPLL}}(s) = V \times \underbrace{\frac{\text{LF}(s) + s\text{LPF}(s)/V}{1 - \text{LPF}(s)}}_{\text{LF}^{*}(s)} \times \frac{1}{s}.$$

(11)

By comparing (11) with the open-loop transfer function of the SRF-PLL, i.e., (7), it can be concluded that the FPLL is mathematically equivalent with a conventional SRF-PLL with LF\*(s) as the LF transfer function. For example, (12) expresses LF\*(s) for a simple case of LF(s) =  $k_p + k_i/s$  and LPF(s) =  $\omega_p/(s + \omega_p)$ . Notice that the coefficient(s) of LF\*(s) depend on the input voltage amplitude. Therefore, the equivalency is valid for a fixed voltage amplitude.

$$LF^*(s) = \underbrace{(k_p + \omega_p/V)}_{C_0} + \underbrace{\frac{C_1}{(k_i + k_p \omega_p)}}_{S} + \underbrace{\frac{C_2}{k_i \omega_p}}_{S^2}.$$

(12)

### VI. CONCLUSION

The aim of this paper was to analyze the PLLs with a SCP. The paper was started with an overview of these PLLs. The small-signal modeling of these PLLs was then presented. Using these models, an analysis was performed. It was shown that: 1) the SCP increases the type of PLL control loop by one, which aggravates the stability problem; 2) the SCP enables the PLL to track faster reference signals with a lower tracking error; 3) the SCP increases the PLL bandwidth, and thus improves its dynamic performance. It was also shown that adding the SCP to the PLL is mathematically equivalent to changing its LF. Considering that the SCP increases the PLL implementation complexity, and aggravates the stability problem, it can be concluded it may not be a practical approach to improve the PLL dynamic performance. However, it may be useful when tracking the fast reference signals, such as frequency ramps, is necessary for the PLL.

#### REFERENCES

- S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Dynamics assessment of advanced single-phase PLL structures," *IEEE Trans. Ind. Electron.* vol. 60, no. 6, pp. 2167-2177, Jun. 2013.

- [2] R. M. Santos Filho, P. F. Seixas, P. C. Cortizo, L. A. B. Torres, and A. F. Souza, "Comparison of three single-phase PLL algorithms for UPS applications," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2923-2932, Aug. 2008.

- [3] F. D. Freijedo, A. G. Yepes, O. Lopez, A. Vidal, and J. Doval-Gandoy, "Three-phase PLLs with fast postfault retracking and steady-state rejection of voltage unbalance and harmonics by means of lead compensation," IEEE Trans. Power Electron., vol. 26, no. 1, pp. 85-97, Jan. 2011.

- [4] M. Karimi Ghartemani, S. A. Khajehoddin, P. K. Jain, and A. Bakhshai, "Problems of startup and phase jumps in PLL systems," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1830-1838, Apr. 2012.

- [5] T. Thacker, D. Boroyevich, R. Burgos, and F. Wang, "Phase-locked loop noise reduction via phase detector implementation for single-phase systems," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2482-2490, Jun. 2011.

- [6] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Performance improvement of a pre-filtered synchronous-reference-frame PLL by ysing a PID-type loop filter," *IEEE Trans. Ind. Electron.*, vol. 99, no. PP, pp. 1-12, Sep. 2013.

- [7] F. Liccardo, P. Marino, and G. Raimondo, "Robust and fast three-phase PLL tracking system," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 221-231, Jan. 2011.

- [8] B. Indu Rani, C. K. Aravind, G. Saravana Ilango, and C. Nagamani, "A three phase PLL with a dynamic feed forward frequency estimator for synchronization of grid connected converters under wide frequency variations," *Int. J Electr. Power Energ Syst.*, vol. 41, no. 1, pp. 63-70, Oct. 2012.

- [9] H. Geng, D. Xu, and B. Wu, "A Novel hardware based All Digital Phase-Locked-Loop applied to Grid-connected Power Converters," *IEEE Trans. Ind. Electron.*, vol. 58, no. 5, pp. 1737-1745, May 2011.

- [10] H. Geng, J. Sun, S. Xiao, and G. Yang, "Modeling and implementation of an all digital phase-locked-loop for grid-voltage phase detection," *IEEE Trans. Ind. Inf.*, vol. 9, no. 2, pp. 772-780, May 2013.

- [11] K. G. Papadopoulos, E. N. Papastefanaki, and N. I. Margaris, "Explicit analytical PID tuning rules for the design of type-III control loops," *IEEE Trans. Ind. Electron.*, vol. 60, no. 10, pp. 4650-4664, Oct. 2013.

- [12] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Advantages and challenges of a type-3 PLL," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4985-4997, Now. 2013.

- [13] K. Ogata, *Modern Control Engineering*, 5th ed. Englewood Cliffs, NJ: Prentice Hall, Sep. 2009.

Saeed Golestan (M'11) received the B.Sc. degree in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2006, and the M.Sc. degree in electrical engineering from Amirkabir University of Technology, Tehran, Iran, in 2009.

He is currently a Lecturer with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Iran. His research interests include phase-locked loop and nonlinear filtering techniques for power engineering applications, power quality, and distributed generation systems.

**Malek Ramezani** (M'13) received the B.Sc. and M.Sc. degrees in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2007 and 2010, respectively.

He is currently a Lecturer with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Iran. His research interests include distributed generation, microgrid, and sustainable energy systems.

Josep M. Guerrero (S'01-M'04-SM'08) was born in Barcelona, Spain, in 1973. He received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics all from the Technical University of Catalonia, Barcelona, Spain, in 1997, 2000, and 2003, respectively.

He was an Associate Professor with the Department of Automatic Control Systems and Computer Engineering, Technical University of Catalonia, where he currently teaches courses on digital

signal processing, field-programmable gate arrays, microprocessors, and renewable energy. Since 2004, he has been responsible for the Renewable Energy Laboratory, Escola Industrial de Barcelona. He has been a visiting Professor at Zhejiang University, Hangzhou, China, and the University of Cergy-Pontoise, Pontoise, France. In 2012, he was the Guest Professor Chair at Nanjing University Aeronautics and Astronautics. Since 2011, he has been a Full Professor of microgrids at the Institute of Energy Technology, Aalborg University, Aalborg, Denmark, where he is the responsible of the microgrids research program. His research interests are oriented to different Microgrids aspects, including power electronics, distributed energy storage systems, hierarchical and cooperative control and energy management systems, and optimization of microgrids and islanded minigrids.

Dr. Guerrero is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, and the IEEE Industrial Electronics Magazine. He has been the Guest Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS Special Issues: Power Electrics for Wind Energy Conversion and Power Electronics for Microgrids; and the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS Special Sections: Uninterruptible Power Supplies systems, Renewable Energy Systems, Distributed Generation and Microgrids, and Industrial Applications and Implementation Issues of the Kalman Filter. He currently chairs the Renewable Energy Systems Technical Committee of the IEEE Industrial Electronics Society.