# **Aalborg Universitet**

# A Systematic Approach to Design High-Order Phase-Locked Loops

Golestan, Saeed; Fernandez, Francisco Daniel Freijedo; Guerrero, Josep M.

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2014.2351262

Publication date: 2015

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA): Golestan, S., Fernandez, F. D. F., & Guerrero, J. M. (2015). A Systematic Approach to Design High-Order Phase-Locked Loops. *I E E E Transactions on Power Electronics*, *30*(6), 2885 - 2890 . https://doi.org/10.1109/TPEL.2014.2351262

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Letters

# A Systematic Approach to Design High-Order Phase-Locked Loops

Saeed Golestan, Francisco D. Freijedo, and Josep M. Guerrero

Abstract—A basic approach to improve the performance of phase-locked loop (PLL) under adverse grid condition is to incorporate a first-order low-pass filter (LPF) into its control loop. The first-order LPF, however, has a limited ability to suppress grid disturbances. A natural thought to further improve the disturbance rejection capability of PLL is to use high-order LPFs. Application of high-order LPFs, however, results in high-order PLLs, which rather complicates the PLL analysis and design procedure. To overcome this challenge, a systematic method to design high-order PLLs is presented in this letter. The suggested approach has a general theme, which means it can be applied to design the PLL control parameters regardless of the order of in-loop LPF. The effectiveness of suggested design method is confirmed through different design cases.

Index Terms—Phase-locked loop (PLL), synchronization.

### I. INTRODUCTION

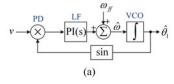

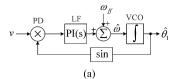

N RECENT years, the increased harmonic pollution caused by proliferation of nonlinear electrical loads such as adjustable speed drives, arc furnaces, switching power supplies, rectifiers, etc. has made the synchronization of grid-connected equipment with the utility grid a challenging task [1]. To deal with this challenge, several advanced phase-locked loops (PLLs) have been proposed recently. These PLLs are typically based on applying some modifications to the structure of a standard PLL. Fig. 1(a) and (b) shows the structure of a standard single-phase and three-phase PLL, respectively, in which PD, LF, and VCO are abbreviations of phase detector, loop filter, and voltage-controlled oscillator, respectively.

To deal with the problem of synchronization under distorted and unbalanced grid conditions, the inclusion of moving average filter (MAF) into the PLL control loop is recommended in [2] and [3]. The MAF is a linear-phase filter that effectively blocks the grid disturbances in the PLL control loop, but at the cost of slowing down its transient response. A detailed analysis of MAF-based PLLs and improving their dynamic response can be found in [4] and [5].

Manuscript received June 13, 2014; revised July 13, 2014; accepted August 18, 2014. This work was supported in part by the Abadan Branch-Islamic Azad University, and the Research Programme on Microgrids, Department of Energy Technology. Recommended for publication by Associate Editor xxx.

S. Golestan is with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Abadan 63178-36531, Iran (e-mail: s.golestan@ieee.org).

F. D. Freijedo and J. M. Guerrero are with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: fran@et.aau.dk; joz@et.aau.dk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2014.2351262

Fig. 1. (a) Standard single-phase PLL; (b) standard three-phase PLL.

Inspired from the concept of delayed signal cancellation [6], [7] the idea of cascaded delayed signal cancellation (CDSC) has recently been introduced as an effective solution to improve the disturbance rejection capability of PLL under adverse grid condition [8], [9]. The CDSC operator is a finite impulse response filter that can be used as an in-loop filter or a prefiltering stage for the PLL. A detailed analysis of PLL with in-loop CDSC operator can be found in [10].

Another approach is to include one or more notch filters (NFs) into the PLL control loop [11], [12]. The NFs may be adaptive or nonadaptive. The adaptive form is often preferred as they can block the grid disturbances even under off-nominal grid frequency conditions.

Using the complex coefficient filters (CCFs) is another method that can be applied to improve the filtering capability of three-phase PLLs [13], [14]. The main advantage of CCfs over the real coefficient filters is that they can make distinction between the positive and negative sequences (polarities) of the same frequency.

The filters that work based on the instantaneous symmetrical component method are also popular to improve the filtering capability of three-phase PLLs. The dual second-order generalized integrator based filter [15] is a well-known member of this class.

Probably, the most straightforward approach to improve the performance of PLL under distorted grid condition is to include a simple first-order low-pass filter (LPF) in its control loop. A first-order LPF, however, has a limited ability to suppress the grid disturbances. To further improve the disturbance rejection capability of PLL, using higher order LPFs are sometimes recommended. For example, using a fourth-order LPF is suggested in [16]. Application of these high-order LPFs, however, results in high-order PLLs, which rather complicates the PLL analysis and design procedure.

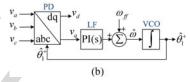

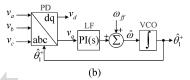

Fig. 2. Structure of PLL under study.

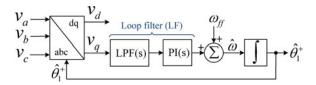

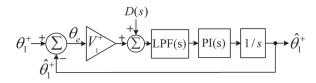

Fig. 3. Small-signal model.

In this letter, a systematic approach to design high-order PLLs is presented. The suggested method has a general form and, therefore, is applicable to design the PLL parameters regardless of the order of in-loop LPF.

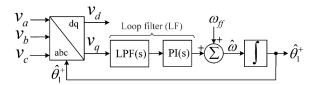

#### II. PLL STRUCTURE AND SMALL-SIGNAL MODELING

Fig. 2 shows the schematic diagram of PLL under study, which is a standard three-phase PLL with an in-loop LPF. In this structure, the proportional-integral (PI) controller acts as the main filter of control loop as it is responsible to provide a zero steady-state average phase error for the PLL. The LPF, on the other hand, supports the PI controller as it is responsible to improve the disturbance rejection capability of control loop under adverse grid condition. Throughout this letter, Butterworth LPF is considered. The LPF transfer function is considered to be of the form

LPF(s)

$$= \frac{a_0(\omega_p)^n}{a_n s^n + a_{n-1} \omega_p s^{n-1} + \dots + a_1(\omega_p)^{n-1} s + a_0(\omega_p)^n}$$

(1)

where  $\omega_p$  is the cutoff frequency, n is the LPF order, and  $a_i$  (i = 0, 1, 2, ..., n) are the LPF coefficients.

Obtaining the small-signal model of the PLL under study is very straightforward [17]. Fig. 3 shows this model in which D(s) denotes the Laplace transform of grid voltage disturbances in the dq frame. Notice that the loop gain depends on  $V_1^+$ , i.e., the amplitude of fundamental frequency positive sequence component of the grid voltage. Therefore, any variation in the grid voltage amplitude affects the PLL stability and dynamic behavior. This problem can be simply avoided by incorporating an amplitude normalization mechanism into the PLL structure [18], [19].

# III. SYSTEMATIC DESIGN APPROACH

#### A. Model Order Reduction

The key to determine the reduced-order model lies in the fact that the in-loop LPF causes phase delay in the PLL control loop, so to ensure the PLL stability, its crossover frequency should

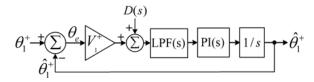

Fig. 4. Reduced-order small-signal model.

be sufficiently lower than the LPF cutoff frequency. The higher the LPF order, the greater the low-frequency phase delay is, and therefore, the smaller the PLL crossover frequency (compared to the LPF cutoff frequency) should be. According to this fact, the reduced-order model can be obtained by neglecting the high-frequency dynamics of LPF and approximating its transfer function with a first-order transfer function, i.e.,

$$LPF(s) \approx \frac{a_0(\omega_p)^n}{a_1(\omega_p)^{n-1}s + a_0(\omega_p)^n} = \frac{a_0\omega_p/a_1}{s + \underbrace{a_0\omega_p/a_1}_{\omega'}}.$$

(2)

The reduced-order model is shown in Fig. 4. This model is accurate at low frequency range (i.e., frequencies lower than the PLL crossover frequency). Therefore, it can only be used to study the stability and dynamic behavior of PLL.

### B. Stability

From Fig. 4, the open-loop transfer function of the PLL can be obtained as

$$G_{ol}^{\text{red}}(s) = \frac{\hat{\theta}_{1}^{+}(s)}{\theta_{e}(s)} = V_{1}^{+} \frac{\omega_{p}'}{s + \omega_{p}'} \frac{k_{p}s + k_{i}}{s} \frac{1}{s}$$

$$= V_{1}^{+} \omega_{p}' k_{p} \frac{s + \omega_{z}}{s^{2} (s + \omega_{p}')}$$

(3)

where  $\omega_z=k_i/k_p$ , and superscript "red" denotes this transfer function is obtained using the reduced-order model. This transfer function has two poles at the origin with a nonzero pole-zero pair. For such systems, the symmetrical optimum (SO) method is a standard design approach [20]–[22]. According to this method, the PLL crossover frequency  $\omega_c$  should be selected at the geometric mean of corner frequencies of open-loop transfer function, i.e.,  $\omega_c=\sqrt{\omega_p'\omega_z}$ . This selection provides the maximum phase margin (PM) for the PLL.

By application of the SO method to the open-loop transfer function (3), the PLL control parameters can be obtained as

$$k_{p} = \omega_{c}/V_{1}^{+}$$

$$k_{i} = \omega_{c}^{2}/\left(V_{1}^{+}b\right)$$

$$\omega_{p}' = b\omega_{c}$$

(4)

where  $b=\sqrt{\omega_p'/\omega_z}$  is a design constant. So, the PLL control parameters can be obtained by selecting appropriate values for the crossover frequency  $\omega_c$  and the design constant b.

By substituting (4) into (3), the open-loop transfer function (3) can be rewritten as

$$G_{ol}^{\text{red}}(s) = b\omega_c^2 \frac{(s + \omega_c/b)}{s^2(s + b\omega_c)}.$$

(5)

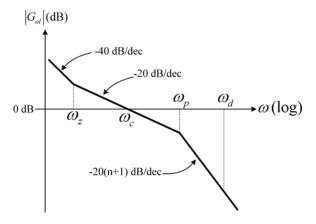

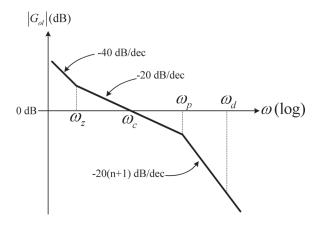

Fig. 5. Asymptotic magnitude plot of open-loop transfer function (9).

Using this transfer function, the PM of the PLL can be obtained as

$$\text{PM}^{\text{red}} = 180^{\circ} + \angle G_{ol}^{\text{red}}(s) \big|_{s=j\omega_c} = \tan^{-1} \left( \frac{b^2 - 1}{2b} \right).$$

(6)

It can be observed that the PM only depends on the design constant b. So, b can be determined by selecting a proper value for PM. In most control texts,  $30^{\circ} \leq \text{PM} \leq 60^{\circ}$  is recommended which corresponds to  $\sqrt{3} \leq b \leq 2 + \sqrt{3}$ . We select a PM in the middle of this range, i.e., PM =  $45^{\circ}$ , which corresponds to  $b = 1 + \sqrt{2}$ .

# C. Filtering Capability

In this section, the filtering capability of the PLL is studied. This study is conducted using the original small-signal model because the reduced-order model is not accurate at high frequency range.

Defining  $D'(s) = D(s)/V_1^+$  as the normalized disturbance input to the model, the disturbance transfer function of the PLL can be obtained as

$$G_d^{\text{orig}}(s) = \frac{\hat{\theta}_1^+(s)}{D'(s)} = \frac{G_{ol}^{\text{orig}}(s)}{1 + G_{ol}^{\text{orig}}(s)} \tag{7}$$

where the superscript "orig" denotes the transfer function is obtained using the original (not reduced-order) small-signal model.

From (7), it is clear that to achieve a high disturbance rejection capability, the magnitude of open-loop transfer function must be very small at high frequency range. Therefore, we can approximate (7) by (8) at high frequency range

$$G_d^{\text{orig}}(s) \approx G_{ol}^{\text{orig}}(s).$$

(8)

This approximation simplifies the analysis and design procedure.

From Fig. 3, the open-loop transfer function can be obtained as

$$G_{ol}^{\text{orig}}(s) = V_1^+ k_p \frac{s + \omega_z}{s^2} \text{LPF}(s).$$

(9)

3

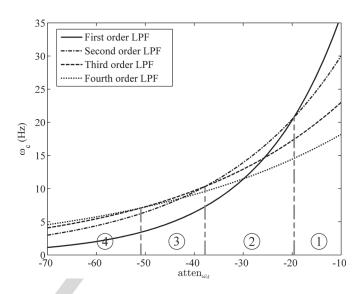

Fig. 6. Crossover frequency as a function of atten $_{\omega_d}$ . Parameters:  $\omega_d=2\pi(2\cdot 50)$  rad/s, and  $b=1+\sqrt{2}$ .

TABLE I

DESIGNED CONTROL PARAMETERS

|        | LPF order, | LPF cutoff frequency, $\omega_p$ | Proportional gain, $k_p$ | Integral gain, $k_i$ |

|--------|------------|----------------------------------|--------------------------|----------------------|

| Case 1 | 1          | 411.69 (rad/s)                   | 170.52                   | 12045                |

| Case 2 | 2          | 299.18 (rad/s)                   | 87.63                    | 3180.75              |

| Case 3 | 3          | 255.05 (rad/s)                   | 52.82                    | 1155.78              |

| Case 4 | 4          | 228.12 (rad/s)                   | 36.16                    | 541.62               |

Fig. 5 shows the asymptotic magnitude plot of the open-loop transfer function (9) in which  $\omega_d$  is the disturbance frequency of concern. Assuming the dc offset in the PLL input is negligible, the fundamental frequency negative sequence component is the disturbance component that we should be most concerned about. This disturbance component is sensed as a double-frequency component (i.e.,  $\omega_d = 2\pi(2\cdot 50)$  rad/s in a 50-Hz system) by the PLL control loop. From this plot, the magnitude of open-loop transfer function at the disturbance frequency  $\omega_d$  can be approximated in decibels by

$$20 \log \left( \left| G_{ol}^{\text{orig}}(s) \right|_{s=j\omega_d} \right) \approx -20 \log \left( \frac{\omega_d}{\omega_c} \right)$$

$$-20 n \log \left( \frac{\omega_d}{\omega_p} \right)$$

$$= -20 \log \left( \frac{(\omega_d)^{n+1}}{\omega_c(\omega_p)^n} \right).$$

(10)

Defining  $atten_{\omega_d}$  as the attenuation that the PLL provides in decibels at the disturbance frequency  $\omega_d$ , we can approximate

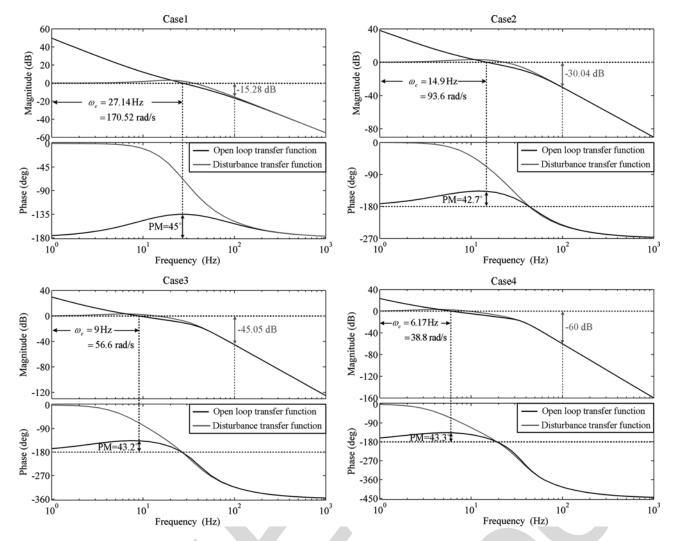

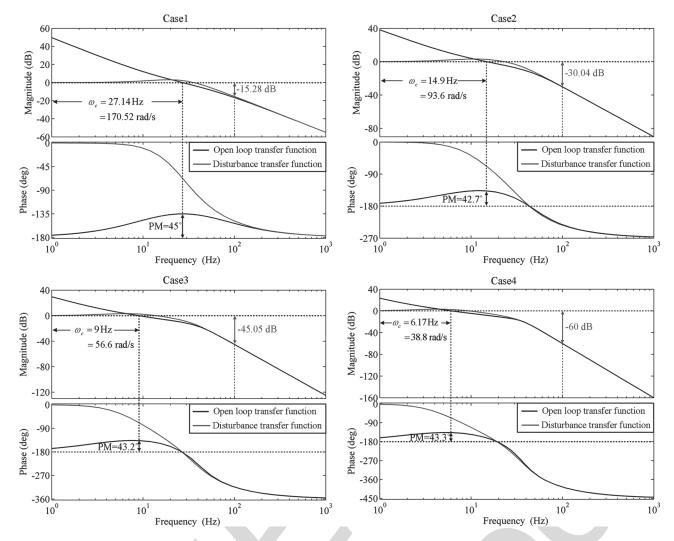

Fig. 7. Bode plots of open-loop transfer function and disturbance transfer function for four design cases.

TABLE II

INTENDED CONTROL OBJECTIVES AND OBTAINED RESULTS

|        | PM<br>Intended/Obtained   | Attenuation at $\omega_d=2\pi 100$ (rad/s) Intended/Obtained |

|--------|---------------------------|--------------------------------------------------------------|

| Case 1 | 45°/45°                   | -15  dB/-15.28  dB                                           |

| Case 2 | $45^{\circ}/42.7^{\circ}$ | -30  dB/-30.04  dB                                           |

| Case 3 | $45^{\circ}/43.2^{\circ}$ | -45  dB/-45.05  dB                                           |

| Case 4 | 45°/43.3°                 | -60 dB/-60 dB                                                |

it, using (8) and (10), by

$$\operatorname{atten}_{\omega_d} = 20 \log \left( \left| G_d^{\text{orig}}(s) \right|_{s=j\omega_d} \right)$$

$$\approx 20 \log \left( \left| G_{ol}^{\text{orig}}(s) \right|_{s=j\omega_d} \right)$$

$$\approx -20 \log \left( \frac{(\omega_d)^{n+1}}{\omega_c(\omega_p)^n} \right). \tag{11}$$

According to (2) and (4), we have  $\omega_p = a_1 \omega_p'/a_0 = a_1 b \omega_c/a_0$ . Substituting this into (11) yields

$$\operatorname{atten}_{\omega_d} \approx -20 \log \left( \frac{(\omega_d)^{n+1}}{(a_1 b/a_0)^n (\omega_c)^{n+1}} \right)$$

$$= -20 (n+1) \log \left( \frac{\omega_d}{\omega_c} \sqrt[n+1]{\left( \frac{a_0}{a_1 b} \right)^n} \right). \quad (12)$$

Using (12), it is easy to obtain

$$\omega_c \approx \sqrt[n+1]{\left(\frac{a_0}{a_1 b}\right)^n} \omega_d 10^{\left(\frac{\operatorname{atten}\omega_d}{20(n+1)}\right)}. \tag{13}$$

As (13) shows, the crossover frequency  $\omega_c$  can be simply determined by selecting a proper value for atten $_{\omega_d}$ .

# D. Selecting LPF Order

During the suggested design procedure, it was assumed that the LPF order is known. In this section, we are going to show that how this parameter should be selected.

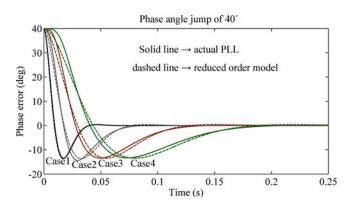

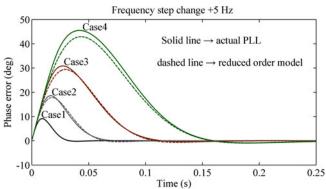

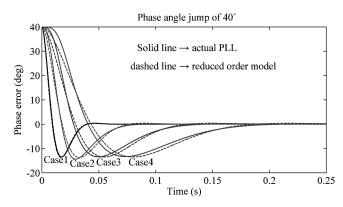

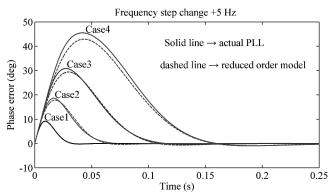

Fig. 8. Accuracy assessment of the reduced-order model in prediction of PLL dynamic behavior.

Selecting the LPF order can be easily made according to the required level of filtering at the disturbance frequency  $\omega_d$ . To illustrate this fact, Fig. 6 shows the variations of the PLL crossover frequency  $\omega_c$  as a function of atten $\omega_d$  for different orders of in-loop LPF: first-order LPF (solid line), secondorder LPF (dash-dotted line), third-order LPF (dashed line), and fourth-order LPF (dotted line). These plots are obtained using (13). In all plots,  $b = 1 + \sqrt{2}$  is considered which means regardless of the order of LPF and the value of crossover frequency, the PM of the PLL is around 45°. It can be observed that in region ① (i.e., when  $|atten_{\omega_d}| < 20 \, dB$ ), the first-order LPF gives the highest crossover frequency and, therefore, the fastest transient response. Therefore, if the required attenuation at  $\omega_d = 2\pi(2\cdot 50)$  rad/s is less than 20 dB, then a first-order LPF should be selected. Following the same reasoning, it can be concluded that in region (2), the second-order LPF is the best choice, and in regions (3) and (4), respectively, the third-order and fourth-order LPFs are proper choices. It should be emphasized here that results may slightly be different if a different value for b is selected.

The above study also shows that the LPFs of order four and higher may not be suitable to include in the PLL control loop unless a very slow transient response and high filtering capability for the PLL in needed.

### E. Summary of Design Procedure

This section summarizes the proposed design procedure:

- 1) Select the LPF order according to what was mentioned in Section III-D.

- 2) Approximate the LPF transfer function with LPF(s)  $\approx \omega_p' / \left[ s + \omega_p' \right]$ , where  $\omega_p' = a_0 \omega_p / a_1$ .

- 3) Define  $k_p = \omega_c/V_1^+$ ,  $k_i = \omega_c^2/\left(V_1^+b\right)$ , and  $\omega_p' = b\omega_c$ .

- 4) Select a proper value for the PM of the PLL, and obtain b according to PM =  $\tan^{-1} \left( \frac{b^2 1}{2b} \right)$ .

- 5) Select a proper level filtering at the disturbance frequency  $\omega_d$  (a proper value for atten $\omega_d$ ), and obtain  $\omega_c$  according to  $\omega_c \approx \sqrt[n+1]{\left(\frac{a_0}{a_1b}\right)^n} \omega_d 10^{\left(\frac{\operatorname{atten}\omega_d}{20(n+1)}\right)}$ ..

- 6) Calculate  $k_p$ ,  $k_i$ , and  $\omega'_p$  from the definitions of step 3.

7) Calculate the LPF cutoff frequency  $\omega_p$  using  $\omega_p = a_1 \omega_p'/a_0$ .

Neglect the steps 2 and 7 and consider  $\omega_p' = \omega_p$  if a first-order LPF is used.

# IV. ACCURACY ASSESSMENT OF SUGGESTED DESIGN APPROACH

The suggested design procedure involves several approximations that their accuracy need to be verified. For this purpose, we employ the suggested design approach for selecting the PLL control parameters and then compare the PLL characteristics with the intended control objectives. Four different cases are considered in this study:

- 1) Case 1: The in-loop LPF is a first-order LPF. Achieving PM =  $45^{\circ}$  and -15 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

- 2) Case 2: The in-loop LPF is a second-order LPF. Achieving PM = 45° and -30 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

- 3) Case 3: The in-loop LPF is a third-order LPF. Achieving PM =  $45^{\circ}$  and -45 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

- 4) Case 4: The in-loop LPF is a fourth-order LPF. Achieving PM =  $45^{\circ}$  and -60 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

Table I shows the designed values of control parameters for all cases. In obtaining the control parameters,  $V_1^+=1$  p.u. is considered. Fig. 7 illustrates the Bode plots of original open-loop transfer function (dark line) and disturbance transfer function (gray line) of PLL using these values. The obtained results from these plots are summarized in Table II and compared with the intended control objectives. It can be observed that, for all four cases, the obtained results are very close to the intended control objectives, confirming the accuracy of approximations made during the suggested design approach.

To further validate the accuracy of approximations, Fig. 8 compares the obtained results from the digital implementation of PLL in response to a phase angle jump and frequency step change with those obtained from the reduced-order model. In the digital implementation, the sampling frequency is set to 10 kHz, and the Tustin method is used to discretize the PI controller and

LPF. It can be observed that the reduced-order model provides good accuracy in all cases.

#### V. CONCLUSION

In this letter, a systematic approach to design high-order PLLs was proposed. It was shown that the suggested design approach has a general form and, therefore, can be applied to design the PLL control parameters regardless of the order of in-loop LPF. The effectiveness of suggested design approach was confirmed through different design cases.

#### REFERENCES

- M. Karimi Ghartemani, Enhanced Phase-Locked Loop Structures for Power and Energy Applications. New York, NY, USA: Wiley-IEEE Press, 2014.

- [2] A. Ghoshal, and V. John, "A method to improve PLL performance under abnormal grid conditions," presented at the Nat. Power Eng. Conf., Bangalore, India, Dec. 2007.

- [3] F. D. Freijedo, J. Doval-Gandoy, O. Lopez, and E. Acha, "Tuning of phase-locked loops for power converters under distorted utility conditions," *IEEE Trans. Ind. Appl.*, vol. 45, no. 6, pp. 2039–2047, Dec. 2009.

- [4] S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo, and M. Monfared, "Moving average filter based phase-locked loops: Performance analysis and design guidelines," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2750–2763, Jun. 2014.

- [5] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero, and J. Doval-Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6264–6270, Jun. 2014.

- [6] H. Awad, J. Svensson, and M. J. Bollen, "Tuning software phase-locked loop for series-connected converters," *IEEE Trans. Power Del.*, vol. 20, no. 1, pp. 300–308, Jan. 2005.

- [7] E. Bueno, F. J. Rodrguez, F. Espinosa, and S. Cbreces, "SPLL design to flux oriented of a VSC interface for wind power applications," in *Proc.* 31st Annu. IEEE IECON, 2005, pp. 2451–2456.

- [8] F. A. S. Neves, M. C. Cavalcanti, H. E. P. de Souza, F. Bradaschia, E. J. Bueno, and M. Rizo, "A generalized delayed signal cancellation method for detecting fundamental-frequency positive-sequence three-phase signals," *IEEE Trans. Power Del.*, vol. 25, no. 3, pp. 1816–1825, Jul. 2010.

- [9] Y. F. Wang and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1987–1997, Jul. 2011.

- [10] S. Golestan, M. Ramezani, J. M. Guerrero, and M. Monfared, "dq-frame cascaded delayed signal cancellation-based PLL: Analysis, design, and comparison with moving average filter-based PLL," *IEEE Trans. Power Electron.*, to be published.

- [11] F. D. Freijedo, A. G. Yepes, O. Lopez, P. Fernandez-Comesana, and J. Doval-Gandoy, "An optimized implementation of phase locked loops for grid applications," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 9, pp. 3110–3119, Sep. 2011.

- [12] F. Gonzalez-Espin, G. Garcera, I. Patrao, and E. Figueres, "An adaptive control system for three-phase photovoltaic inverters working in a polluted and variable frequency electric grid," *IEEE Trans. Power Electron.*, vol. 27, no. 10, pp. 4248–4261, Oct. 2012.

- [13] X. Guo, W. Wu, and Z. Chen, "Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid interfaced converters in distributed utility networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1194–1204, Apr. 2011.

- [14] W. Li, X. Ruan, C. Bao, D. Pan, and X. Wang, "Grid synchronization systems of three-phase grid-connected power converters: A complex vector-filter perspective," *IEEE Trans. Ind. Electron.*, vol. 61, no. 4, pp. 1855–1870, Apr. 2014.

- [15] P. Rodriguez, R. Teodorescu, I. Candela, A. V. Timbus, M. Liserre, and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," in *Proc. Power Electron. Spec. Conf.*, Jun. 2006, pp. 1–7.

- [16] R. M. Santos Filho, P. F. Seixas, P. C. Cortizo, L. A. B. Torres, and A. F. Souza, "Comparison of three single-phase PLL algorithms for UPS applications," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2923–2932, Aug. 2008.

- [17] K. Chung, "A phase tracking system for three phase utility interface inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 431–438, May 2000.

- [18] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase grid connected power conditioning systems," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3639–3650, Aug. 2012.

- [19] M. Karimi-Ghartemani, "A unifying approach to single-phase synchronous reference frame PLLs," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4550–4556, Oct. 2013.

- [20] K. Shu and E. Sanchez-Sinencio, CMOS PLL Synthesizers-Analysis and Design. New York, NY, USA: Springer-Verlag, 2005.

- [21] W. Leonard, Control of Electrical Drives. Berlin, Germansy: Springer-Verlag, 1990.

- [22] R. Teodorescu, M. Liserre, and P. Rodriguez, Grid Converters for Photovoltaic and Wind Power Systems. New York, NY, USA: IEEE-Wiley, 2011.

# Letters

# A Systematic Approach to Design High-Order Phase-Locked Loops

Saeed Golestan, Francisco D. Freijedo, and Josep M. Guerrero

Abstract—A basic approach to improve the performance of phase-locked loop (PLL) under adverse grid condition is to incorporate a first-order low-pass filter (LPF) into its control loop. The first-order LPF, however, has a limited ability to suppress grid disturbances. A natural thought to further improve the disturbance rejection capability of PLL is to use high-order LPFs. Application of high-order LPFs, however, results in high-order PLLs, which rather complicates the PLL analysis and design procedure. To overcome this challenge, a systematic method to design high-order PLLs is presented in this letter. The suggested approach has a general theme, which means it can be applied to design the PLL control parameters regardless of the order of in-loop LPF. The effectiveness of suggested design method is confirmed through different design cases.

Index Terms—Phase-locked loop (PLL), synchronization.

### I. INTRODUCTION

N RECENT years, the increased harmonic pollution caused by proliferation of nonlinear electrical loads such as adjustable speed drives, arc furnaces, switching power supplies, rectifiers, etc. has made the synchronization of grid-connected equipment with the utility grid a challenging task [1]. To deal with this challenge, several advanced phase-locked loops (PLLs) have been proposed recently. These PLLs are typically based on applying some modifications to the structure of a standard PLL. Fig. 1(a) and (b) shows the structure of a standard single-phase and three-phase PLL, respectively, in which PD, LF, and VCO are abbreviations of phase detector, loop filter, and voltage-controlled oscillator, respectively.

To deal with the problem of synchronization under distorted and unbalanced grid conditions, the inclusion of moving average filter (MAF) into the PLL control loop is recommended in [2] and [3]. The MAF is a linear-phase filter that effectively blocks the grid disturbances in the PLL control loop, but at the cost of slowing down its transient response. A detailed analysis of MAF-based PLLs and improving their dynamic response can be found in [4] and [5].

Manuscript received June 13, 2014; revised July 13, 2014; accepted August 18, 2014. This work was supported in part by the Abadan Branch-Islamic Azad University, and the Research Programme on Microgrids, Department of Energy Technology. Recommended for publication by Associate Editor xxx.

S. Golestan is with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Abadan 63178-36531, Iran (e-mail: s.golestan@ieee.org).

F. D. Freijedo and J. M. Guerrero are with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: fran@et.aau.dk; joz@et.aau.dk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2014.2351262

Fig. 1. (a) Standard single-phase PLL; (b) standard three-phase PLL.

Inspired from the concept of delayed signal cancellation [6], [7] the idea of cascaded delayed signal cancellation (CDSC) has recently been introduced as an effective solution to improve the disturbance rejection capability of PLL under adverse grid condition [8], [9]. The CDSC operator is a finite impulse response filter that can be used as an in-loop filter or a prefiltering stage for the PLL. A detailed analysis of PLL with in-loop CDSC operator can be found in [10].

Another approach is to include one or more notch filters (NFs) into the PLL control loop [11], [12]. The NFs may be adaptive or nonadaptive. The adaptive form is often preferred as they can block the grid disturbances even under off-nominal grid frequency conditions.

Using the complex coefficient filters (CCFs) is another method that can be applied to improve the filtering capability of three-phase PLLs [13], [14]. The main advantage of CCfs over the real coefficient filters is that they can make distinction between the positive and negative sequences (polarities) of the same frequency.

The filters that work based on the instantaneous symmetrical component method are also popular to improve the filtering capability of three-phase PLLs. The dual second-order generalized integrator based filter [15] is a well-known member of this class.

Probably, the most straightforward approach to improve the performance of PLL under distorted grid condition is to include a simple first-order low-pass filter (LPF) in its control loop. A first-order LPF, however, has a limited ability to suppress the grid disturbances. To further improve the disturbance rejection capability of PLL, using higher order LPFs are sometimes recommended. For example, using a fourth-order LPF is suggested in [16]. Application of these high-order LPFs, however, results in high-order PLLs, which rather complicates the PLL analysis and design procedure.

Fig. 2. Structure of PLL under study.

Fig. 3. Small-signal model.

In this letter, a systematic approach to design high-order PLLs is presented. The suggested method has a general form and, therefore, is applicable to design the PLL parameters regardless of the order of in-loop LPF.

#### II. PLL STRUCTURE AND SMALL-SIGNAL MODELING

Fig. 2 shows the schematic diagram of PLL under study, which is a standard three-phase PLL with an in-loop LPF. In this structure, the proportional-integral (PI) controller acts as the main filter of control loop as it is responsible to provide a zero steady-state average phase error for the PLL. The LPF, on the other hand, supports the PI controller as it is responsible to improve the disturbance rejection capability of control loop under adverse grid condition. Throughout this letter, Butterworth LPF is considered. The LPF transfer function is considered to be of the form

LPF(s)

$$= \frac{a_0(\omega_p)^n}{a_n s^n + a_{n-1} \omega_p s^{n-1} + \dots + a_1(\omega_p)^{n-1} s + a_0(\omega_p)^n}$$

(1)

where  $\omega_p$  is the cutoff frequency, n is the LPF order, and  $a_i$  (i = 0, 1, 2, ..., n) are the LPF coefficients.

Obtaining the small-signal model of the PLL under study is very straightforward [17]. Fig. 3 shows this model in which D(s) denotes the Laplace transform of grid voltage disturbances in the dq frame. Notice that the loop gain depends on  $V_1^+$ , i.e., the amplitude of fundamental frequency positive sequence component of the grid voltage. Therefore, any variation in the grid voltage amplitude affects the PLL stability and dynamic behavior. This problem can be simply avoided by incorporating an amplitude normalization mechanism into the PLL structure [18], [19].

# III. SYSTEMATIC DESIGN APPROACH

### A. Model Order Reduction

The key to determine the reduced-order model lies in the fact that the in-loop LPF causes phase delay in the PLL control loop, so to ensure the PLL stability, its crossover frequency should

Fig. 4. Reduced-order small-signal model.

be sufficiently lower than the LPF cutoff frequency. The higher the LPF order, the greater the low-frequency phase delay is, and therefore, the smaller the PLL crossover frequency (compared to the LPF cutoff frequency) should be. According to this fact, the reduced-order model can be obtained by neglecting the high-frequency dynamics of LPF and approximating its transfer function with a first-order transfer function, i.e.,

$$LPF(s) \approx \frac{a_0(\omega_p)^n}{a_1(\omega_p)^{n-1}s + a_0(\omega_p)^n} = \frac{a_0\omega_p/a_1}{s + \underbrace{a_0\omega_p/a_1}_{\omega'}}.$$

(2)

The reduced-order model is shown in Fig. 4. This model is accurate at low frequency range (i.e., frequencies lower than the PLL crossover frequency). Therefore, it can only be used to study the stability and dynamic behavior of PLL.

### B. Stability

From Fig. 4, the open-loop transfer function of the PLL can be obtained as

$$G_{ol}^{\text{red}}(s) = \frac{\hat{\theta}_{1}^{+}(s)}{\theta_{e}(s)} = V_{1}^{+} \frac{\omega_{p}'}{s + \omega_{p}'} \frac{k_{p}s + k_{i}}{s} \frac{1}{s}$$

$$= V_{1}^{+} \omega_{p}' k_{p} \frac{s + \omega_{z}}{s^{2} (s + \omega_{p}')}$$

(3)

where  $\omega_z=k_i/k_p$ , and superscript "red" denotes this transfer function is obtained using the reduced-order model. This transfer function has two poles at the origin with a nonzero pole-zero pair. For such systems, the symmetrical optimum (SO) method is a standard design approach [20]–[22]. According to this method, the PLL crossover frequency  $\omega_c$  should be selected at the geometric mean of corner frequencies of open-loop transfer function, i.e.,  $\omega_c=\sqrt{\omega_p'\omega_z}$ . This selection provides the maximum phase margin (PM) for the PLL.

By application of the SO method to the open-loop transfer function (3), the PLL control parameters can be obtained as

$$k_p = \omega_c / V_1^+$$

$$k_i = \omega_c^2 / (V_1^+ b)$$

$$\omega_p' = b\omega_c$$

(4)

where  $b=\sqrt{\omega_p'/\omega_z}$  is a design constant. So, the PLL control parameters can be obtained by selecting appropriate values for the crossover frequency  $\omega_c$  and the design constant b.

By substituting (4) into (3), the open-loop transfer function (3) can be rewritten as

$$G_{ol}^{\text{red}}(s) = b\omega_c^2 \frac{(s + \omega_c/b)}{s^2(s + b\omega_c)}.$$

(5)

Fig. 5. Asymptotic magnitude plot of open-loop transfer function (9).

Using this transfer function, the PM of the PLL can be obtained as

$$PM^{red} = 180^{\circ} + \angle G_{ol}^{red}(s)|_{s=j\omega_c} = \tan^{-1}\left(\frac{b^2 - 1}{2b}\right).$$

(6)

It can be observed that the PM only depends on the design constant b. So, b can be determined by selecting a proper value for PM. In most control texts,  $30^{\circ} \leq \text{PM} \leq 60^{\circ}$  is recommended which corresponds to  $\sqrt{3} \leq b \leq 2 + \sqrt{3}$ . We select a PM in the middle of this range, i.e., PM =  $45^{\circ}$ , which corresponds to  $b = 1 + \sqrt{2}$ .

# C. Filtering Capability

In this section, the filtering capability of the PLL is studied. This study is conducted using the original small-signal model because the reduced-order model is not accurate at high frequency range.

Defining  $D'(s) = D(s)/V_1^+$  as the normalized disturbance input to the model, the disturbance transfer function of the PLL can be obtained as

$$G_d^{\text{orig}}(s) = \frac{\hat{\theta}_1^+(s)}{D'(s)} = \frac{G_{ol}^{\text{orig}}(s)}{1 + G_{ol}^{\text{orig}}(s)}$$

(7)

where the superscript "orig" denotes the transfer function is obtained using the original (not reduced-order) small-signal model.

From (7), it is clear that to achieve a high disturbance rejection capability, the magnitude of open-loop transfer function must be very small at high frequency range. Therefore, we can approximate (7) by (8) at high frequency range

$$G_d^{\text{orig}}(s) \approx G_{ol}^{\text{orig}}(s).$$

(8)

This approximation simplifies the analysis and design procedure.

From Fig. 3, the open-loop transfer function can be obtained as

$$G_{ol}^{\text{orig}}(s) = V_1^+ k_p \frac{s + \omega_z}{s^2} \text{LPF}(s).$$

(9)

3

Fig. 6. Crossover frequency as a function of atten $_{\omega_d}$ . Parameters:  $\omega_d=2\pi(2\cdot 50)$  rad/s, and  $b=1+\sqrt{2}$ .

TABLE I

DESIGNED CONTROL PARAMETERS

|        | LPF order, | LPF cutoff frequency, $\omega_p$ | Proportional gain, $k_p$ | Integral gain, $k_i$ |

|--------|------------|----------------------------------|--------------------------|----------------------|

| Case 1 | 1          | 411.69 (rad/s)                   | 170.52                   | 12045                |

| Case 2 | 2          | 299.18 (rad/s)                   | 87.63                    | 3180.75              |

| Case 3 | 3          | 255.05 (rad/s)                   | 52.82                    | 1155.78              |

| Case 4 | 4          | 228.12 (rad/s)                   | 36.16                    | 541.62               |

Fig. 5 shows the asymptotic magnitude plot of the open-loop transfer function (9) in which  $\omega_d$  is the disturbance frequency of concern. Assuming the dc offset in the PLL input is negligible, the fundamental frequency negative sequence component is the disturbance component that we should be most concerned about. This disturbance component is sensed as a double-frequency component (i.e.,  $\omega_d = 2\pi(2\cdot 50)$  rad/s in a 50-Hz system) by the PLL control loop. From this plot, the magnitude of open-loop transfer function at the disturbance frequency  $\omega_d$  can be approximated in decibels by

$$20 \log \left( \left| G_{ol}^{\text{orig}}(s) \right|_{s=j\omega_d} \right) \approx -20 \log \left( \frac{\omega_d}{\omega_c} \right)$$

$$-20 n \log \left( \frac{\omega_d}{\omega_p} \right)$$

$$= -20 \log \left( \frac{(\omega_d)^{n+1}}{\omega_c(\omega_p)^n} \right).$$

(10)

Defining  $atten_{\omega_d}$  as the attenuation that the PLL provides in decibels at the disturbance frequency  $\omega_d$ , we can approximate

Fig. 7. Bode plots of open-loop transfer function and disturbance transfer function for four design cases.

TABLE II

INTENDED CONTROL OBJECTIVES AND OBTAINED RESULTS

|        | PM<br>Intended/Obtained   | Attenuation at $\omega_d=2\pi 100$ (rad/s) Intended/Obtained |

|--------|---------------------------|--------------------------------------------------------------|

| Case 1 | 45°/45°                   | −15 dB/−15.28 dB                                             |

| Case 2 | $45^{\circ}/42.7^{\circ}$ | -30  dB/-30.04  dB                                           |

| Case 3 | $45^{\circ}/43.2^{\circ}$ | -45  dB/-45.05  dB                                           |

| Case 4 | $45^{\circ}/43.3^{\circ}$ | -60  dB/-60  dB                                              |

it, using (8) and (10), by

$$\operatorname{atten}_{\omega_d} = 20 \log \left( \left| G_d^{\text{orig}}(s) \right|_{s=j\omega_d} \right)$$

$$\approx 20 \log \left( \left| G_{ol}^{\text{orig}}(s) \right|_{s=j\omega_d} \right)$$

$$\approx -20 \log \left( \frac{(\omega_d)^{n+1}}{\omega_c(\omega_p)^n} \right). \tag{11}$$

According to (2) and (4), we have  $\omega_p = a_1 \omega_p'/a_0 = a_1 b \omega_c/a_0$ . Substituting this into (11) yields

$$\operatorname{atten}_{\omega_d} \approx -20 \log \left( \frac{(\omega_d)^{n+1}}{(a_1 b/a_0)^n (\omega_c)^{n+1}} \right)$$

$$= -20 (n+1) \log \left( \frac{\omega_d}{\omega_c} \sqrt[n+1]{\left( \frac{a_0}{a_1 b} \right)^n} \right). \quad (12)$$

Using (12), it is easy to obtain

$$\omega_c \approx \sqrt[n+1]{\left(\frac{a_0}{a_1 b}\right)^n} \omega_d 10^{\left(\frac{\operatorname{atten}\omega_d}{20(n+1)}\right)}.$$

(13)

As (13) shows, the crossover frequency  $\omega_c$  can be simply determined by selecting a proper value for atten $_{\omega_d}$ .

# D. Selecting LPF Order

During the suggested design procedure, it was assumed that the LPF order is known. In this section, we are going to show that how this parameter should be selected.

Fig. 8. Accuracy assessment of the reduced-order model in prediction of PLL dynamic behavior.

Selecting the LPF order can be easily made according to the required level of filtering at the disturbance frequency  $\omega_d$ . To illustrate this fact, Fig. 6 shows the variations of the PLL crossover frequency  $\omega_c$  as a function of atten $\omega_d$  for different orders of in-loop LPF: first-order LPF (solid line), secondorder LPF (dash-dotted line), third-order LPF (dashed line), and fourth-order LPF (dotted line). These plots are obtained using (13). In all plots,  $b = 1 + \sqrt{2}$  is considered which means regardless of the order of LPF and the value of crossover frequency, the PM of the PLL is around 45°. It can be observed that in region (1) (i.e., when  $|atten_{\omega_d}| < 20 \,\mathrm{dB}$ ), the first-order LPF gives the highest crossover frequency and, therefore, the fastest transient response. Therefore, if the required attenuation at  $\omega_d = 2\pi(2\cdot 50)$  rad/s is less than 20 dB, then a first-order LPF should be selected. Following the same reasoning, it can be concluded that in region (2), the second-order LPF is the best choice, and in regions (3) and (4), respectively, the third-order and fourth-order LPFs are proper choices. It should be emphasized here that results may slightly be different if a different value for b is selected.

The above study also shows that the LPFs of order four and higher may not be suitable to include in the PLL control loop unless a very slow transient response and high filtering capability for the PLL in needed.

### E. Summary of Design Procedure

This section summarizes the proposed design procedure:

- 1) Select the LPF order according to what was mentioned in Section III-D.

- 2) Approximate the LPF transfer function with LPF(s)  $\approx \omega_p' / \left[ s + \omega_p' \right]$ , where  $\omega_p' = a_0 \omega_p / a_1$ .

- 3) Define  $k_p=\omega_c/V_1^+$ ,  $k_i=\omega_c^2/\left(V_1^+b\right)$ , and  $\omega_p'=b\omega_c$ .

- 4) Select a proper value for the PM of the PLL, and obtain b according to  $PM = \tan^{-1} \left( \frac{b^2 1}{2b} \right)$ .

- 5) Select a proper level filtering at the disturbance frequency  $\omega_d$  (a proper value for atten $\omega_d$ ), and obtain  $\omega_c$  according to  $\omega_c \approx \sqrt[n+1]{\left(\frac{a_0}{a_1b}\right)^n} \omega_d 10^{\left(\frac{\operatorname{atten}\omega_d}{20(n+1)}\right)}$ ..

- 6) Calculate  $k_p$ ,  $k_i$ , and  $\omega_p'$  from the definitions of step 3.

7) Calculate the LPF cutoff frequency  $\omega_p$  using  $\omega_p = a_1 \omega_p'/a_0$ .

Neglect the steps 2 and 7 and consider  $\omega_p' = \omega_p$  if a first-order LPF is used.

# IV. ACCURACY ASSESSMENT OF SUGGESTED DESIGN APPROACH

The suggested design procedure involves several approximations that their accuracy need to be verified. For this purpose, we employ the suggested design approach for selecting the PLL control parameters and then compare the PLL characteristics with the intended control objectives. Four different cases are considered in this study:

- 1) Case 1: The in-loop LPF is a first-order LPF. Achieving PM =  $45^{\circ}$  and -15 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

- 2) Case 2: The in-loop LPF is a second-order LPF. Achieving PM =  $45^{\circ}$  and -30 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

- 3) Case 3: The in-loop LPF is a third-order LPF. Achieving PM =  $45^{\circ}$  and -45 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

- 4) Case 4: The in-loop LPF is a fourth-order LPF. Achieving PM =  $45^{\circ}$  and -60 dB attenuation at  $\omega_d = 2\pi 100$  rad/s are the control objectives in this case.

Table I shows the designed values of control parameters for all cases. In obtaining the control parameters,  $V_1^+=1$  p.u. is considered. Fig. 7 illustrates the Bode plots of original open-loop transfer function (dark line) and disturbance transfer function (gray line) of PLL using these values. The obtained results from these plots are summarized in Table II and compared with the intended control objectives. It can be observed that, for all four cases, the obtained results are very close to the intended control objectives, confirming the accuracy of approximations made during the suggested design approach.

To further validate the accuracy of approximations, Fig. 8 compares the obtained results from the digital implementation of PLL in response to a phase angle jump and frequency step change with those obtained from the reduced-order model. In the digital implementation, the sampling frequency is set to 10 kHz, and the Tustin method is used to discretize the PI controller and

LPF. It can be observed that the reduced-order model provides good accuracy in all cases.

#### V. CONCLUSION

In this letter, a systematic approach to design high-order PLLs was proposed. It was shown that the suggested design approach has a general form and, therefore, can be applied to design the PLL control parameters regardless of the order of in-loop LPF. The effectiveness of suggested design approach was confirmed through different design cases.

#### REFERENCES

- M. Karimi Ghartemani, Enhanced Phase-Locked Loop Structures for Power and Energy Applications. New York, NY, USA: Wiley-IEEE Press, 2014.

- [2] A. Ghoshal, and V. John, "A method to improve PLL performance under abnormal grid conditions," presented at the Nat. Power Eng. Conf., Bangalore, India, Dec. 2007.

- [3] F. D. Freijedo, J. Doval-Gandoy, O. Lopez, and E. Acha, "Tuning of phase-locked loops for power converters under distorted utility conditions," *IEEE Trans. Ind. Appl.*, vol. 45, no. 6, pp. 2039–2047, Dec. 2009.

- [4] S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo, and M. Monfared, "Moving average filter based phase-locked loops: Performance analysis and design guidelines," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2750–2763, Jun. 2014.

- [5] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero, and J. Doval-Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6264–6270, Jun. 2014.

- [6] H. Awad, J. Svensson, and M. J. Bollen, "Tuning software phase-locked loop for series-connected converters," *IEEE Trans. Power Del.*, vol. 20, no. 1, pp. 300–308, Jan. 2005.

- [7] E. Bueno, F. J. Rodrguez, F. Espinosa, and S. Cbreces, "SPLL design to flux oriented of a VSC interface for wind power applications," in *Proc.* 31st Annu. IEEE IECON, 2005, pp. 2451–2456.

- [8] F. A. S. Neves, M. C. Cavalcanti, H. E. P. de Souza, F. Bradaschia, E. J. Bueno, and M. Rizo, "A generalized delayed signal cancellation method for detecting fundamental-frequency positive-sequence three-phase signals," *IEEE Trans. Power Del.*, vol. 25, no. 3, pp. 1816–1825, Jul. 2010.

- [9] Y. F. Wang and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1987–1997, Jul. 2011.

- [10] S. Golestan, M. Ramezani, J. M. Guerrero, and M. Monfared, "dq-frame cascaded delayed signal cancellation-based PLL: Analysis, design, and comparison with moving average filter-based PLL," *IEEE Trans. Power Electron.*, to be published.

- [11] F. D. Freijedo, A. G. Yepes, O. Lopez, P. Fernandez-Comesana, and J. Doval-Gandoy, "An optimized implementation of phase locked loops for grid applications," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 9, pp. 3110–3119, Sep. 2011.

- [12] F. Gonzalez-Espin, G. Garcera, I. Patrao, and E. Figueres, "An adaptive control system for three-phase photovoltaic inverters working in a polluted and variable frequency electric grid," *IEEE Trans. Power Electron.*, vol. 27, no. 10, pp. 4248–4261, Oct. 2012.

- [13] X. Guo, W. Wu, and Z. Chen, "Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid interfaced converters in distributed utility networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1194–1204, Apr. 2011.

- [14] W. Li, X. Ruan, C. Bao, D. Pan, and X. Wang, "Grid synchronization systems of three-phase grid-connected power converters: A complex vector-filter perspective," *IEEE Trans. Ind. Electron.*, vol. 61, no. 4, pp. 1855–1870, Apr. 2014.

- [15] P. Rodriguez, R. Teodorescu, I. Candela, A. V. Timbus, M. Liserre, and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," in *Proc. Power Electron. Spec. Conf.*, Jun. 2006, pp. 1–7.

- [16] R. M. Santos Filho, P. F. Seixas, P. C. Cortizo, L. A. B. Torres, and A. F. Souza, "Comparison of three single-phase PLL algorithms for UPS applications," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2923–2932, Aug. 2008.

- [17] K. Chung, "A phase tracking system for three phase utility interface inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 431–438, May 2000.

- [18] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase grid connected power conditioning systems," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3639–3650, Aug. 2012.

- [19] M. Karimi-Ghartemani, "A unifying approach to single-phase synchronous reference frame PLLs," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4550–4556, Oct. 2013.

- [20] K. Shu and E. Sanchez-Sinencio, CMOS PLL Synthesizers-Analysis and Design. New York, NY, USA: Springer-Verlag, 2005.

- [21] W. Leonard, Control of Electrical Drives. Berlin, Germansy: Springer-Verlag, 1990.

- [22] R. Teodorescu, M. Liserre, and P. Rodriguez, Grid Converters for Photovoltaic and Wind Power Systems. New York, NY, USA: IEEE-Wiley, 2011.