Aalborg Universitet

## Five Approaches to Deal With Problem of DC Offset in Phase-Locked Loop Algorithms

Design Considerations and Performance Evaluations Golestan, S.; Guerrero, J.M.; Gharehpetian, G.B.

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2015.2408113

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Golestan, S., Guerrero, J. M., & Gharehpetian, G. B. (2016). Five Approaches to Deal With Problem of DC Offset in Phase-Locked Loop Algorithms: Design Considerations and Performance Evaluations. *I E E E Transactions on Power Electronics*, *31*(1), 648 - 661. https://doi.org/10.1109/TPEL.2015.2408113

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Five Approaches to Deal With Problem of DC Offset in Phase-Locked Loop Algorithms: Design Considerations and Performance Evaluations

Saeed Golestan, Senior Member, IEEE, Josep M. Guerrero, Fellow, IEEE, and Gevork B. Gharehpetian, Senior Member, IEEE

Abstract—The presence of the dc component in the phaselocked loop (PLL) input results in fundamental frequency oscillations in the phase and frequency estimated by the PLL. The removal of these oscillations is a challenging task because of their low frequency. The aim of this paper is to provide a detailed analysis of several approaches that little work has been conducted on their application for addressing the problem of dc offset in the PLL algorithms. These approaches include using the dq-frame delayed signal cancellation (DSC) operator and the notch filter as the PLL in-loop filtering stages, and using the  $\alpha\beta$ -frame DSC operator, the complex coefficient filter, and a cross-feedback network for blocking the dc offset before the PLL input. Design aspects of these methods are presented, some methods to enhance their performances are proposed, and their advantages and disadvantages are evaluated.

*Index Terms*—DC offset, frequency estimation, phase estimation, phase-locked loop (PLL), synchronization.

## I. INTRODUCTION

The phase locked loops (PLLs) are closed-loop feedback control systems that are crucial in the synchronization and control of grid-connected power electronic based equipment [1]-[3]. They are also widely used in the control of electrical machines [4], [5], measuring power quality phenomena and indices [6], [7], implementing robust adaptive filters [8], [9], islanding detection [10], [11], etc.

The presence of the dc offset in the PLL input, which may be due to grid faults [12], measurement devices [13], A/D conversion process [14], [15], dc injection from distributed generation systems [16], [17], geomagnetic phenomena [18], half-wave rectification [19], etc., results in the fundamental frequency oscillations in the estimated quantities by the PLL [20]. Removal of these oscillations is a difficult task due to their low frequency.

In the grid-connected applications, the presence of the dc offset in the PLL input may also result in the dc injection by the grid-tied converters. The reason is that in this condition

Copyright © 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

S. Golestan is with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Abadan 63178-36531, Iran (e-mail: s.golestan@ieee.org).

J. M. Guerrero is with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: joz@et.aau.dk).

G. B. Gharehpetian is with the Department of Electrical Engineering, Amirkabir University of Technology, Tehran 4413-15875, Iran (e-mail: grptian@cic.aut.ac.ir) the PLL unit vector (the sine and cosine of the phase angle estimated by the PLL), which is often used by these converters for creating their reference current, contains a dc component [21]. The international standards, however, have imposed strict limits on the dc injection of the grid-connected converters. For example, the standard IEC61727 [22] limits the dc current injection by the grid-connected photovoltaic inverters to less than 1% of their rated output current, and the standard IEEE 1547-2003 [23] states that the dc injection by the distributed resources should not be more than 0.5% of their rated output current. These strict limits confirm the importance of the dc offset rejection capability for PLLs in the grid-connected applications.

To deal with the problem of the dc offset in PLL algorithms, several solutions have been proposed in literature. In [24]-[26], using a band-pass filter (BPF) before the PLL input is suggested. The BPF effectively blocks the dc offset, but it slows down the PLL dynamic response and causes a phase shift in the PLL input in the presence of frequency drifts. This phase shift can be avoided by using a frequency adaptive BPF, or by compensating the phase shift at the PLL output [27].

In [28], including a high-pass filter (HPF) at the PLL input is suggested. In this technique, the grid voltage is first passed through a low-pass filter (LPF) to estimate its dc component. The LPF output signal is then subtracted from the grid voltage to cancel its dc component. Depending on the LPF order and cutoff frequency, this technique may reduce the harmonic filtering capability of the PLL and also cause a phase error at its output.

In [15], the focus is on rejecting the dc offset in the singlephase synchronous reference frame PLLs. In this method, the input signal of the PLL loop filter is separately integrated over two half-cycles. The obtained results are then subtracted from each other and passed through a proportional-integral (PI) controller. The output of this PI controller, which is an estimation of the input dc component, is subtracted from the PLL input to cancel its dc component.

In [29], the difference between the PLL input and the fundamental component extracted by the PLL is passed through an integrator. The output of the integrator, which is an estimation of the input dc component, is then subtracted from the PLL input to reject this component. Some similar techniques can be found in [21] and [30].

The main aim of this paper is to provide a detailed analysis

of some less discussed techniques for rejecting the dc offset in the PLL algorithms. These techniques include using the *dq*-frame delayed signal cancelation operator (which will be briefly called the *dq*DSC operator) and the notch filter for rejecting the dc offset inside the PLL control loop, and using the  $\alpha\beta$ -frame delayed signal cancelation operator (which will be briefly called the  $\alpha\beta$ DSC operator), the complex coefficient filter (CCF), and a cross-feedback network (CFN) for blocking the dc offset before the PLL input. In addition to the analysis of each technique, design guidelines, techniques to enhance their performance and extension to unbalabced and harmonically distorted grid conditions will be provided and simulation results will be reported and discussed.

## II. DC OFFSET REMOVAL USING dqDSC OPERATOR

The dqDSC operator is a finite-impulse response filter that is defined in the Laplace domain as [31], [32]

$$dq \text{DSC}_n(s) = \frac{1 + e^{-(T/n)s}}{2} \tag{1}$$

where, T is the grid fundamental period and n, which is a positive constant, is called the delay factor.

Substituting  $s = j\omega$  into (1) gives the magnitude and phase of the dqDSC operator as

$$dq \text{DSC}_n(j\omega) = \left| \cos\left(\frac{\omega T}{2n}\right) \right| \angle -\left(\frac{\omega T}{2n}\right).$$

(2)

Using (2), it is easy to show that the dqDSC operator blocks frequencies  $f = \frac{n}{T} \left(k + \frac{1}{2}\right)$ ,  $k \in Z$  in Hertz. Therefore, to block the fundamental frequency component (i.e., f = 1/T) in the PLL control loop, the delay factor n should be  $n = \frac{2}{2k+1}$ . According to this equation, there are infinite values that can be selected for n. The optimum value for n, however, is the highest value, because, according to (2), the phase delay caused by the dqDSC operator is inversely proportional to n. Therefore, n = 2 (which corresponds to k = 0) is selected for the delay factor n.

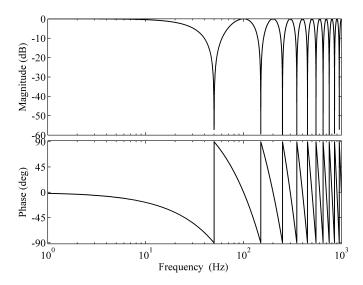

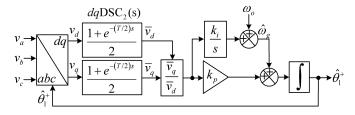

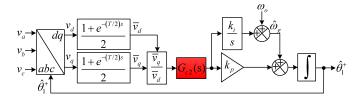

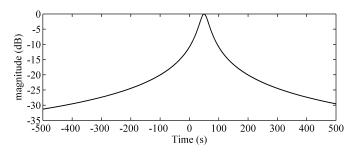

Fig. 1 shows the frequency response of the  $dqDSC_2$  operator. It can be observed that the  $dqDSC_2$  operator removes the fundamental frequency component and all oddorder harmonic components. Inclusion of this operator into the PLL control loop is shown in Fig. 2. This PLL structure is called the dqDSC-PLL. Notice that to make the PLL control loop insensitive to the grid voltage amplitude variations, an amplitude normalization mechanism (ANM) is also included in its control loop. This ANM is realized by passing the *d*-axis voltage component through the  $dqDSC_2$  operator to obtain an estimation of the grid voltage amplitude and dividing the output signal of *q*-axis DSC operator by the estimated amplitude. An additional LPF can also be cascaded with the *d*-axis DSC operator to ensure that the estimated amplitude is free of high frequency noises.

### A. Design Considerations

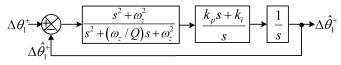

Selecting the dqDSC-PLL parameters is based on the smallsignal model of this PLL, which can be simply obtained as shown in Fig. 3. In this model,  $\Delta$  denotes the perturbation around the nominal operating point.

Fig. 1. Frequency response of the dqDSC<sub>2</sub> operator.

Fig. 2. Schematic diagram of the dqDSC-PLL.

Using Fig. 3, the open-loop transfer function can be obtained as

$$G_{ol}(s) = \frac{\Delta \hat{\theta}_1^+(s)}{\Delta \theta_1^+(s) - \Delta \hat{\theta}_1^+(s)} = \frac{1 + e^{-\frac{Ts}{2}}}{2} \frac{k_p s + k_i}{s^2}.$$

(3)

The presence of the delay term in (3) complicates the analysis and design procedure. To overcome this problem, this delay term is replaced by its first-order Padé approximation, i.e.,  $e^{-\frac{sT}{2}} \approx \frac{1-sT/4}{1+sT/4}$ , which gives

$$G_{ol}(s) \approx \frac{1}{1+s} \underbrace{T/4}_{T_d} \frac{k_p s + k_i}{s^2}.$$

(4)

Applying the symmetrical optimum design method [33] to (4) gives the proportional and integral gains as

$$k_p = 1/(bT_d) k_i = 1/(b^3 T_d^2)$$

(5)

where, b is a design constant that determines the phase margin (PM) of the PLL as  $PM \approx \tan^{-1}\left(\frac{b^2-1}{2b}\right)$ .  $b = 1 + \sqrt{2}$ , which corresponds to  $PM \approx 45^{\circ}$ , is selected in this paper. This selection gives the proportional and integral gains as  $k_p = 82.84$ , and  $k_i = 2842.7$ .

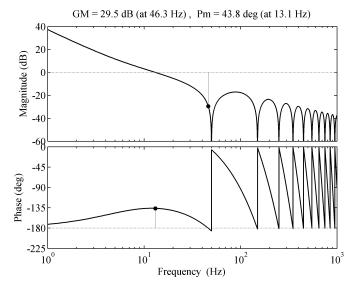

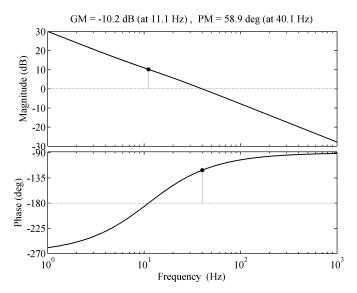

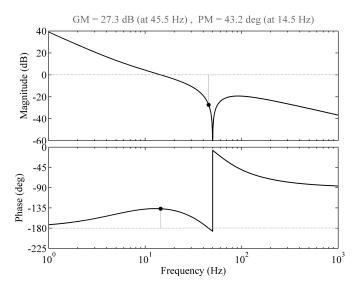

Fig. 4 shows the open-loop Bode plot of the *dq*DSC-PLL. Notice that the crossover frequency corresponds to the peak of the phase plot, which is a direct result of the symmetrical optimum design method. As it can be observed, the PM is  $43.8^{\circ}$ , which is very close to the intended PM.

Fig. 3. Small-signal model of the dqDSC-PLL.

Fig. 4. Open-loop Bode plot of the dqDSC-PLL.

#### B. Performance Evaluation

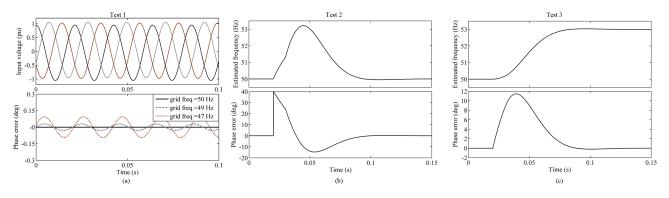

In this section, the dynamic performance of the dqDSC-PLL and its dc offset rejection capability are evaluated through simulation results. To this end, three test cases are designed:

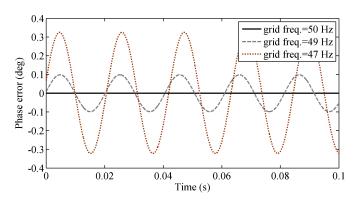

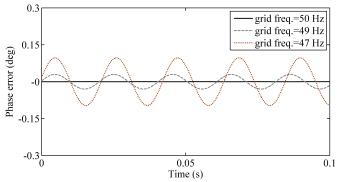

- 1) **Test case 1**: The grid voltage is contaminated with the dc offset ( $v_{a,dc} = -0.05$  pu,  $v_{b,dc} = 0.05$  pu, and  $v_{c,dc} =$ 0.025 pu). The steady-state peak-to-peak value of the fundamental frequency oscillatory error in the estimated phase is considered as the performance index in this test. To take into account the effect of the grid frequency variations on the PLL dc offset rejection capability, this test is carried out under the nominal frequency (i.e., 50 Hz) and off-nominal frequencies 49 and 47 Hz.

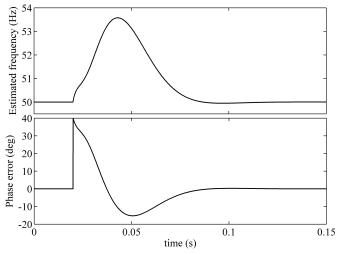

- 2) **Test case 2**: The grid voltage undergoes a  $+40^{\circ}$  phase angle jump. The 2% settling time, i.e., the time after which the PLL phase error reaches and remains within  $0.8^{\circ}$  of neighbourhood of zero, is the main performance index in this test.

- 3) Test case 3: The grid voltage undergoes a +3 Hz frequency step change. The 2% settling time, i.e., the time after which the estimated frequency reaches and remains inside the band of 0.06 Hz around its final value, is the main performance index in this test.

The simulations are carried out in the Matlab/Simulink environment. Throughout the simulation studies, the sampling frequency is fixed at 10 kHz. The z-domain transfer function of the dqDSC<sub>2</sub> operator is as follows

$$dq \text{DSC}_2(z) = \frac{1 + z^{-N_2}}{2}$$

(6)

where,  $N_2 = \text{round} \left[ \left( T/2 \right) / T_s \right] = 100$ , and  $T_s$  is the sampling time.

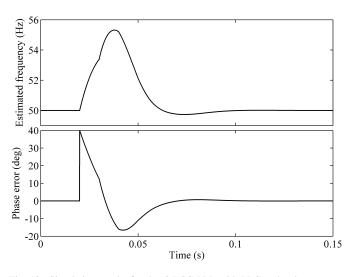

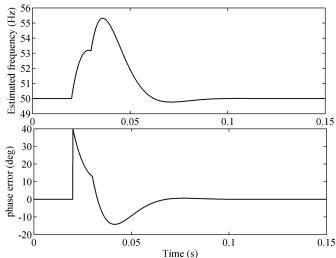

Fig. 5(a) shows the dqDSC-PLL simulation results for the test case 1. It can be observed that the dqDSC-PLL provides a good dc offset rejection capability even when the grid frequency deviation from its nominal value is high. Fig. 5(b) and (c) show the dqDSC-PLL simulation results under the test case 2 and 3, respectively. The 2% settling time of the dqDSC-PLL is around 72 ms and 58.1 ms for these tests, respectively, which indicate a rather slow transient response. Therefore, the dqDSC-PLL can be useful in applications where a slow and damped dynamic behavior from the PLL is expected. For those applications where a faster dynamic response is needed, the dynamic performance of the dqDSC-PLL can be improved as will be shown in the next section.

## C. Dynamic Performance Enhancement

The rather slow dynamic response of the dqDSC-PLL is mainly due to the large phase delay induced by the dqDSC<sub>2</sub> operator in the control loop. Therefore, the dynamic response of the dqDSC-PLL can be improved by compensating this phase delay. To achieve this goal, we suggest to incorporate a phase-lead compensator (PLC) with a z-domain transfer function of the following form into the dqDSC-PLL control loop

$$G_{c2}(z) = \frac{1 + r^{N_2}}{1 + r^{N_2} z^{-N_2}}$$

(7)

where,  $r \in [0 \ 1)$  is called the attenuation factor, and  $N_2$ , as defined before, is the number of samples within the the dqDSC<sub>2</sub> delay time T/2. Notice that (7) is the inverse of (6) for r = 1.

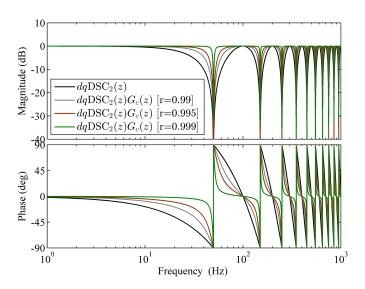

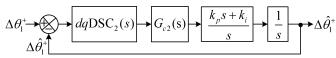

Incorporating the PLC into the dqDSC-PLL control-loop is shown in Fig. 6. To better visualize the effect of the PLC, Fig. 7 compares the frequency responses of single dqDSC<sub>2</sub> operator and the cascade connection of dqDSC<sub>2</sub> operator and PLC for different values of r. As shown, the phase delay introduced by the dqDSC<sub>2</sub> operator can be effectively compensated by selecting a close to unity value for the attenuation factor r. In this paper, r = 0.99 is selected.

Fig. 8 shows the small-signal model of the dqDSC-PLL with PLC. Using this model, the open-loop transfer function can be obtained as

$$G_{ol}(s) = \frac{\Delta \hat{\theta}_1^+}{\Delta \theta_1^+ - \Delta \hat{\theta}_1^+} = \underline{dq \text{DSC}_2(s)} G_{c2}(s) \frac{k_p s + k_i}{s^2}.$$

(8)

The underlined term in (8) can be neglected without significantly affecting the accuracy, because this term provides a close to unity gain and small phase delay at low frequency range. Therefore, (8) can be approximated by

$$G_{ol}(s) \approx \frac{k_p s + k_i}{s^2}.$$

(9)

Using (9), the closed loop transfer function of the dqDSC-PLL with PLC can be obtained as

$$G_{cl}(s) = \frac{G_{ol}(s)}{1 + G_{ol}(s)} \approx \frac{k_p s + k_i}{s^2 + \underbrace{k_p}_{2\zeta\omega_n} s + \underbrace{k_i}_{\omega_n^2}}$$

(10)

Fig. 5. dqDSC-PLL simulation results under (a) test case 1, (b) test case 2, and (c) test case 3.

Fig. 6. *dq*DSC-PLL with PLC.

Fig. 7. A comparison between the frequency response of single dqDSC<sub>2</sub> operator and cascade connection of the dqDSC<sub>2</sub> operator and the PLC for three different values of r.

where,  $\zeta$  is the damping factor and  $\omega_n$  is the natural frequency. Therefore, the proportional and integral gains can be determined by selecting appropriate values for  $\zeta$  and  $\omega_n$ . Special care should be taken in selecting  $\omega_n$ , as a high value for  $\omega_n$  can result in instability. This fact can be easily shown by calculation of the PM of the PLL as a function of  $\omega_n$ , as discussed in [34]. To achieve the optimum damping,  $\zeta = 1/\sqrt{2}$ is selected, and to obtain a rather fast dynamic response while maintaining an adequate stability margin,  $\omega_n = 2\pi 14$  rad/s is chosen. These selections gives  $k_p = 124.4$  and  $k_i = 7737.8$ .

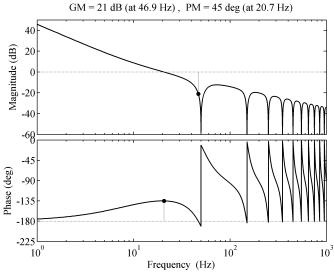

Fig. 9 shows the open-loop Bode plot of the dqDSC-PLL with PLC. It can be observed that the PLC enables the dqDSC-PLL to achieve a higher bandwidth and, therefore, a faster dynamic response without jeopardizing its stability condition.

Fig. 8. Small-signal model of the dqDSC-PLL with PLC.

Fig. 9. Open-loop Bode plot of the dqDSC-PLL with PLC. Parameters:  $k_p = 124.4$ ,  $k_i = 7737.8$ , and r = 0.99.

To confirm the effectiveness of the PLC in improving the dynamic response of the dqDSC-PLL, Fig. 10 evaluate the PLL dynamic performance under the test case 2. The 2% settling time is 47.4 ms which indicates a faster dynamic response compare to the original dqDCS-PLL.

This improvement in settling time, however, is at the cost of decreasing the dc offset rejection capability of the dqDSC-PLL, particularly when the deviation of grid frequency from its nominal value is high. This fact can be better visualized through Fig. 11, which shows the simulation results under the test case 1. This result was expected, because the PLC reduces the bandwidth of notches in the frequency response of the dqDSC<sub>2</sub> operator (see Fig. 7).

Fig. 10. Simulation results for the dqDSC-PLL with PLC under the test case

Fig. 11. Simulation results for the dqDSC-PLL with phase lead compensator under the test case 1.

## D. Extension to the Harmonically Distorted and Unbalanced Grid Condition

Although the focus in this paper is on adding the dc offset rejection capability to the standard PLL structure, the presence of harmonic components in the PLL input cannot be ignored. Therefore, we are going to briefly discuss here how the PLL structure should be extended to take into account the presence of harmonic components and the grid voltage unbalance.

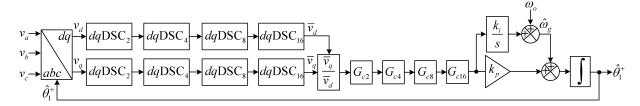

As Fig. 9 shows, the dqDSC<sub>2</sub> operator blocks the evenorder harmonic components of the PLL input. Therefore, we should focus on removing the fundamental frequency negative sequence (FFNS) component and odd-order harmonic components. The FFNS component, which appears as a double frequency component in the control loop, can be blocked by including the dqDSC<sub>4</sub> operator into the PLL control loop [34]. In addition to the FFNS component, this operator blocks the harmonics of order -5 and +7, which are the most dominant harmonic components in the grid voltage. To block the remaining harmonic components, incorporating the dqDSC<sub>8</sub> and dqDSC<sub>16</sub> operators into the PLL control is needed. Finally, to minimize the phase delay caused by these additional dqDSC operators, including three extra lead compensators into the PLL control is required, as shown in Fig. 12.

#### III. DC OFFSET REMOVAL USING $\alpha\beta$ DSC OPERATOR

The  $\alpha\beta$ DSC operator can be understood as the stationaryreference frame equivalent of the *dq*DSC operator. This operator is defined in the s-domain as [31], [32]

$$\alpha\beta \text{DSC}_n(s) = \frac{1 + e^{\frac{j2\pi}{n}} e^{-\frac{T}{n}s}}{2}$$

(11)

where n, as defined before, is the delay factor.

By substituting  $s = j\omega$  into (11), the magnitude and phase of the  $\alpha\beta$ DSC operator can be obtained as

$$\alpha\beta \text{DSC}_n(j\omega) = \left|\cos\left(\frac{\omega T}{2n} - \frac{\pi}{n}\right)\right| \angle -\left(\frac{\omega T}{2n} - \frac{\pi}{n}\right).$$

(12)

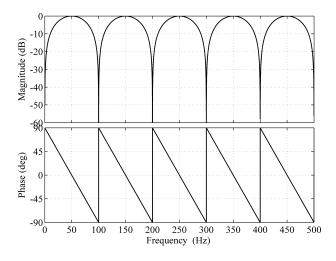

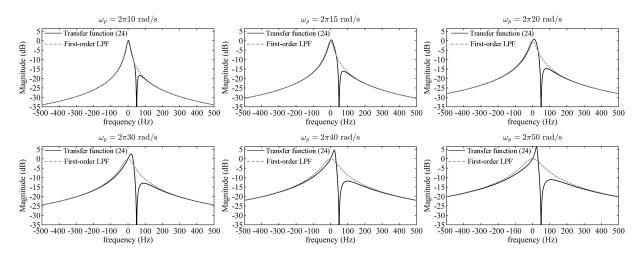

Using (12), it is easy to show that n = 2 is the best choice for our objective, i.e., blocking the dc offset at the PLL input. Fig. 13 shows the frequency response of the  $\alpha\beta DSC_2$ operator. It can be observed that the  $\alpha\beta DSC_2$  operator passes the fundamental component and rejects the dc component and even-order harmonic components.

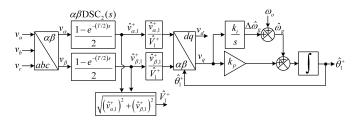

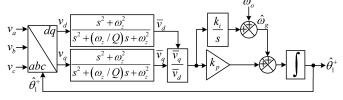

Fig. 14 shows the basic scheme of the  $\alpha\beta$ DSC-PLL, which is a standard synchronous reference frame PLL (SRF-PLL) with the  $\alpha\beta$ DSC<sub>2</sub> operator as its pre-filtering stage. We have also added an ANM before the SRF-PLL input to make its dynamics insensitive to the grid voltage amplitude variations. A LPF can also be added to the ANM to ensure the estimated amplitude is free from any noises.

#### A. $\alpha\beta$ DSC-PLL with the phase error compensator

From Fig. 13, it can be observed that the  $\alpha\beta$ DSC<sub>2</sub> operator provides zero phase shift at the fundamental frequency when the grid frequency is at its nominal value; however, a phase shift happens in the presence of frequency drifts. To compensate this phase shift, which results in a bias error in the estimated phase by the PLL, it is traditionally recommended to feedback the estimated frequency by the PLL and make the  $\alpha\beta$ DSC operator frequency adaptive [31], [32]. This feedback loop, however, makes the PLL highly nonlinear. In this condition, it is rather difficult to ensure the PLL stability under all circumstances [35]. To avoid this problem, we compensate this error at the PLL output [27].

Considering  $\omega_g = \omega_o + \Delta \omega_g$  as the grid frequency, where  $\Delta \omega_g$  denotes the deviation of grid frequency from the nominal frequency  $\omega_o$ , the phase shift caused by the  $\alpha\beta DSC_2$  operator at the fundamental frequency can be obtained using (12) as

$$\angle \alpha \beta \text{DSC}(j\omega_g) = -\frac{T}{4} \Delta \omega_g.$$

(13)

Considering that the output signal of the integrator of the PI controller is an estimation of  $\Delta \omega_g$ , this phase-error can be easily compensated as highlighted in Fig. 15, in which  $k_{\varphi} = T/4$ .

### B. Design Considerations

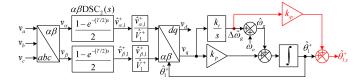

Selecting the parameters of the  $\alpha\beta$ DSC-PLL with phaseerror compensator (PEC) is based on the small-signal model of this PLL, which is shown in Fig. 16. Notice that the dynamics of pre-filtering stage of the PLL (i.e., the  $\alpha\beta$ DSC<sub>2</sub> operator)

Fig. 12. Extension of dqDSC-PLL with phase lead compensator to take into consideration the presence of harmonics and the grid unbalance.

Fig. 13. Frequency response of  $\alpha\beta DSC_2$  operator.

Fig. 14. Block diagram description of  $\alpha\beta$ DSC-PLL.

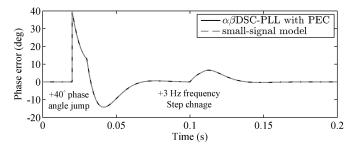

is modeled by its synchronous reference frame equivalent, i.e., the dqDSC<sub>2</sub> operator. For the sake of brevity, the procedure of derivation of this model is not presented. Its high accuracy, however, is verified using the simulation results, as shown in Fig. 17.

From Fig. 16, the open-loop<sup>1</sup> and closed loop transfer functions can be obtained as

$$G_{ol}(s) = \frac{\left(k_p + k_i k_\varphi\right) s + k_i}{s(s - k_i k_\varphi)} \tag{14}$$

$$G_{cl}(s) = \frac{\Delta \theta_{1,c}^+}{\Delta \theta_1^+} = \frac{dq \text{DSC}_2(s) \left[ (k_p + k_i k_\varphi) \, s + k_i \right]}{s^2 + k_p s + k_i}.$$

(15)

As it can be observed, the open-loop transfer function is unstable (it has a right hand side pole), however the closed loop transfer function is stable for  $k_p > 0$  and  $k_i > 0$ . Defining  $k_p = 2\zeta\omega_n$  and  $k_i = \omega_n^2$ ,  $k_p$  and  $k_i$  can be determined by selecting appropriate values for  $\zeta$  and  $\omega_n$ .

Fig. 15.  $\alpha\beta$ DSC-PLL with phase-error compensator (PEC).

Fig. 16. Small-signal model of  $\alpha\beta$ DSC-PLL with PEC.

$\zeta = 1/\sqrt{2}$  and  $\omega_n = 2\pi 20$  rad/s are chosen in this paper, which ensure a good damping, a rather fast dynamic response, and a sufficient stability margin for the PLL. These selections give the proportional and integral gains as  $k_p = 177.71$  and  $k_i = 15791$ .

Fig. 18 shows the open-loop Bode plot of the  $\alpha\beta$ DSC-PLL with PEC. It can be observed that the designed control parameters result in PM = 58.9° and  $\omega_c = 40.1$  Hz ( $\omega_c$  denotes the crossover frequency), which ensures a rather fast transient response and sufficient stability margin for the PLL. The gain margin (GM) of the PLL is GM = -10.2 dB. Notice that the negative GM does not mean instability. It just means that the system may become unstable if the PLL loop gain reduces too much [36]. Fortunately, the ANM in the  $\alpha\beta$ DSC-PLL prevents the PLL loop gain from reducing during the voltage sags and faults.

## C. Performance Evaluation

In this section, the performance of the  $\alpha\beta$ DSC-PLL with PEC is evaluated through simulation results. The same test cases designed to evaluate the performance of the *dq*DSC-PLL are used for this purpose.

Thanks to the zero gain of  $\alpha\beta$ DSC<sub>2</sub> at zero frequency, the  $\alpha\beta$ DSC-PLL with PEC provides a zero steady-state phase error in the presence of dc offset in its input (test case 1). This result is not shown here to save the space. It is the main advantage of the  $\alpha\beta$ DSC-PLL over the *dq*DSC-PLL.

Fig. 19 shows the simulations results for the  $\alpha\beta$ DSC-PLL with PEC under the test case 2. The 2% settling time is 44.4 ms in this test, which indicates a rather fast dynamic response. The PLL presents a similar fast dynamic response under the test case 3.

<sup>&</sup>lt;sup>1</sup>The open-loop transfer function is the ratio of feedback signal to the error signal in the equivalent classical feedback form of the small-signal model shown in Fig. 16.

Fig. 17. Accuracy assessment of the small-signal model of the  $\alpha\beta \text{DSC-PLL}$  with PEC.

Fig. 18. Open-loop Bode plot of the  $\alpha\beta$ DSC-PLL with PEC.

## D. Extension to the Harmonically Distorted and Unbalanced Grid Condition

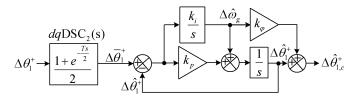

The  $\alpha\beta$ DSC<sub>2</sub> operator, as clearly shown in Fig. 13, can only block the even-order harmonic components. Therefore, to remove the FFNS component and odd-order harmonic components, three  $\alpha\beta$ DSC operators with delay factors 4, 8, and 16 should be cascaded with the  $\alpha\beta$ DSC<sub>2</sub> operator. In this case, the gain of the PEC should be considered as  $k_{\varphi} = \frac{1}{2} \left( \frac{T}{2} + \frac{T}{4} + \frac{T}{8} + \frac{T}{16} \right) = \frac{15T}{32}$ .

## IV. DC OFFSET REMOVAL USING NOTCH FILTER

A notch filter (NF) is a band rejection filter that significantly attenuates the signals within a band of frequencies and passes all other frequencies almost unchanged. The NF can be adaptive or non-adaptive. In this study, we focus on the application of non-adaptive NF in the PLL control loop, but some comments on the application of frequency-adaptive NF is also given at the end of this section.

The non-adaptive NF (hereafter just called the NF) can be defined in the Laplace-domain as

$$NF(s) = \frac{s^2 + \omega_{nf}^2}{s^2 + \underbrace{(\omega_{nf}/Q)}_{BW} s + \omega_{nf}^2}$$

(16)

in which  $\omega_{nf}$  is the notch frequency, Q is the quality factor,

Fig. 19. Simulation results for the  $\alpha\beta$ DSC-PLL with PEC under the test case

Fig. 20. Block diagram description of the NF-PLL

Fig. 21. Small-signal model of the NF-PLL

and BW denotes the 3 dB bandwidth of NF. The structure of NF-PLL and its small-signal model is shown in Fig. 20 and 21, respectively.

## A. Design Considerations

Since the dc offset is sensed as the fundamental frequency component in the PLL control loop, the notch frequency of the NF should be set at  $\omega_{nf} = 2\pi 50$  rad/s. Selecting the quality factor of the NF, on the other hand, should be made based on the anticipated range of variations for the grid frequency. In this paper, the NF quality factor is selected to be  $Q = 1/\sqrt{2}$ , which results in BW =  $50\sqrt{2}$  Hz for the NF. This wide bandwidth NF enables the PLL to effectively block the fundamental frequency disturbance component even in the presence of large variations in the grid frequency. This advantage, however, is at cost of inducing considerable phase delay in the PLL control loop, which may jeopardize the PLL stability unless special care is taken in selecting the proportional and integral gains of the PLL.

From Fig. 21, the open-loop transfer function can be ob-

Fig. 22. Open-loop Bode plot of the NF-PLL.

tained as

$$G_{ol}(s) = \frac{s^2 + \omega_{nf}^2}{s^2 + (\omega_{nf}/Q)s + \omega_{nf}^2} \frac{k_p s + k_i}{s^2}.$$

(17)

Without significantly affecting the accuracy, the NF transfer function can be approximated by (18) at low frequency range.

$$NF(s) \approx \frac{\omega_{nf}^2}{(\omega_{nf}/Q)s + \omega_{nf}^2} = \frac{Q\omega_{nf}}{s + Q\omega_{nf}}.$$

(18)

Substituting (18) into (17) gives

$$G_{ol}(s) \approx \frac{Q\omega_{nf}}{s + Q\omega_{nf}} \frac{k_p s + k_i}{s^2}.$$

(19)

Applying the symmetrical optimum method to (19) gives the proportional and integral gains as

$$k_p = Q\omega_{nf}/b$$

$$k_i = (Q\omega_{nf})^2/b^3$$

(20)

where, as defined before, b is a design constant that determines the phase margin (PM) as  $PM \approx \tan^{-1}\left(\frac{b^2-1}{2b}\right)$ . Like before, we select  $b = 1 + \sqrt{2}$ , which gives  $PM \approx 45^{\circ}$ . Substituting  $Q = 1/\sqrt{2}$ ,  $\omega_{nf} = 2\pi 50$  rad/s, and  $b = 1 + \sqrt{2}$  into (20) gives  $k_p = 92$   $k_i = 3507.1$ .

Fig. 22 shows the open-loop Bode plot of the NF-PLL. It can be observed that the PM of the PLL is close to the intended PM, i.e.,  $PM \approx 45^{\circ}$ , which confirms the accuracy of approximation made during the design procedure.

## B. Performance Evaluation

Fig. 23 shows the NF-PLL simulation result under the test case 1. It can be observed that the NF-PLL effectively suppresses the dc offset even when the deviation of grid frequency from its nominal value is high.

The NF-PLL dynamic performance is evaluated under the test case 2. The obtained results are shown in Fig. 24. The settling time of the NF-PLL is 63.9 ms, which indicates a rather slow transient response. The slow dynamic response of

Fig. 23. The NF-PLL simulation results under the test case 1.

Fig. 24. Simulation results for the NF-PLL under the test case 2.

the NF-PLL is mainly due to the considerable phase delay caused by the wide-bandwidth NF in the PLL control loop. Therefore, depending on the application is hand, the following modifications can be applied to improve the NF-PLL dynamic behavior:

- For applications where small variations for the grid frequency are expected, the transient behavior of the NF-PLL can be improved by replacing the wide-bandwidth non-adaptive NF by a narrow-bandwidth one.

- For applications where large frequency variations are anticipated, a narrow-bandwidth adaptive NF can be employed. Different approaches to realize adaptive NFs can be found in [37], [38].

## C. Extension to the Harmonically Distorted and Unbalanced Grid Condition

To improve the disturbance rejection capability of the NF-PLL under unbalanced and distorted grid conditions, additional NFs can be included into its control loop. In most practical cases, the harmonic components of order h =-5, +7, -11, +13 are dominant harmonic components in the grid voltage. These components are sensed by the PLL control loop as the  $h = \pm 6, \pm 12$  order components. On the other hand, the FFNS component in the grid voltage, as mentioned before, is sensed as a double frequency component in the PLL control

Fig. 25. Schematic diagram of the CFN-PLL.

loop. Therefore, using three extra NFs with notch frequencies at  $2\pi(2.50)$ ,  $2\pi(6.50)$ , and  $2\pi(12.50)$  rad/s in the PLL control loop is good enough for the most practical cases. Nevertheless, if the rejection of more harmonic components is required, more NFs can be included in the PLL control loop, but at the cost of higher computational effort.

## V. DC OFFSET REMOVAL USING CROSS-FEEDBACK NETWORK

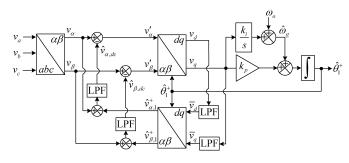

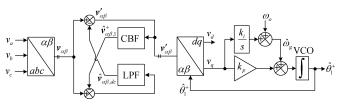

Fig. 25 shows the schematic diagram of the conventional SRF-PLL with a cross-feedback network (CFN), which is called the CFN-PLL. The LPF block in this structure can be any kind of LPF. Throughout this paper, it is considered to be a first-order LPF with transfer function of the form  $LPF(s) = \omega_p/(s + \omega_p)$ , where  $\omega_p$  is its cutoff frequency. To ensure the CFN-PLL is insensitive to the grid voltage amplitude variations, the PI controller input,  $v_q$ , can be divided by  $\bar{v}_d$ , which is an estimation of grid voltage amplitude.

The operation principle of the CFN is as follows. First, the *d*-axis and *q*-axis voltage components are passed through two LPFs to remove their possible disturbances. The filtered *d*- and *q*-axis voltage components are then transformed back to the stationary ( $\alpha\beta$ ) reference frame, which yields an estimation of the grid voltage FFPS components. These components are then subtracted from the grid voltage signals and passed through two LPFs, which gives an estimation of the grid voltage dc components. These dc components are finally subtracted from the grid voltage signals, which removes the dc offset from the SRF-PLL input. To better visualize the effectiveness of CFN, the transfer function relating the SRF-PLL inputs (i.e.,  $v'_{\alpha}$  and  $v'_{\beta}$ ) to the grid voltage signals (i.e.,  $v_{\alpha}$  and  $v_{\beta}$ ) are derived in the following.

From Fig. 25, the SRF-PLL input and the estimated FFPS component can be described in the space vector notation as

$$\boldsymbol{v}_{\alpha\beta}'(s) = \boldsymbol{v}_{\alpha\beta}(s) - \hat{\boldsymbol{v}}_{\alpha\beta,dc}(s)$$

= (1 - LPF(s))  $\boldsymbol{v}_{\alpha\beta}(s) + LPF(s)\hat{\boldsymbol{v}}_{\alpha\beta,1}^{+}(s)$  (21)

$$\hat{\boldsymbol{v}}_{\alpha\beta,1}^{+}(s) = \mathrm{LPF}(s - j\hat{\omega}_g)\boldsymbol{v}_{\alpha\beta}'(s)$$

(22)

where,  $\hat{v}^+_{\alpha\beta,1}(s) = \hat{v}^+_{\alpha,1} + j\hat{v}^+_{\beta,1}$ ,  $v'_{\alpha\beta}(s) = v'_{\alpha} + jv'_{\beta}$ , and  $\hat{v}_{\alpha\beta,dc}(s) = \hat{v}_{\alpha,dc}(s) + j\hat{v}_{\beta,dc}(s)$ . Substituting (22) into (21) gives the transfer function relating the grid voltage and the SRF-PLL input as

$$\frac{\boldsymbol{v}_{\alpha\beta}'(s)}{\boldsymbol{v}_{\alpha\beta}(s)} = \frac{1 - \text{LPF}(s)}{1 - \text{LPF}(s)\text{LPF}(s - j\hat{\omega}_g)}.$$

(23)

Fig. 26. Bode magnitude plot of the transfer function (23).

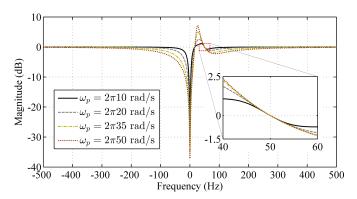

Fig. 26 shows the Bode magnitude plot of (23). It can be observed that regardless of the value of the LPF cutoff frequency, the CFN completely blocks the dc component and passes the FFPS component.

## A. Design Considerations

Selecting a proper value for the LPF cutoff frequency is the first step of the design procedure. To simplify this task, the transfer function between the dc components estimated by the CFN and the grid voltage signals is first determined. Substituting (21) into (23) and performing some simple mathematical manipulations give this transfer function as

$$\frac{\hat{\boldsymbol{v}}_{dc,\alpha\beta}(s)}{\boldsymbol{v}_{\alpha\beta}(s)} = \frac{\mathrm{LPF}(s)\left[1 - \mathrm{LPF}(s - j\hat{\omega}_g)\right]}{1 - \mathrm{LPF}(s)\mathrm{LPF}(s - j\hat{\omega}_g)}.$$

(24)

The solid lines in Fig. 27 shows the magnitude frequency response of (24) for different values of the LPF cutoff frequency. To provide a base for comparison, the magnitude frequency response of a first order LPF is also shown in this figure. It can be observed that the frequency response of (24) converges to that of first-order LPF for small values of  $\omega_p$ , which implies the CFN provides a rather slow and well-damped dynamic response for small values of  $\omega_p$ . The dynamic response of CFN, however, becomes fast and oscillatory<sup>2</sup> for large values of  $\omega_p$ . Therefore, selecting the LPF cutoff frequency  $\omega_p$  involves a tradeoff between the speed of response and damping. To achieve a satisfactory compromise,  $\omega_p = 2\pi 15$  rad/s is selected in this paper.

The selected value for the LPF cutoff frequency ensures that the CFN has a rather small effect on the SRF-PLL dynamic behavior. This fact can be confirmed using the simulation results. Therefore, in selecting the proportional and integral gains  $k_p$  and  $k_i$ , the dynamic interaction between the CFN and the SRF-PLL can be neglected, and the same design approach as that of the conventional SRF-PLL (i.e., defining  $k_p = 2\zeta\omega_n$  and  $k_i = \omega_n^2$ , and selecting appropriate values for  $\zeta$  and  $\omega_n$ ) can be used for their selection. Like before  $\zeta = 1/\sqrt{2}$  is selected which ensures the optimum damping, and  $\omega_n = 2\pi 17$  rad/s is chosen, which provides a fast dynamic response (a settling time of around two cycles of the nominal

<sup>2</sup>The oscillatory dynamic response of the CFN when choosing a large value of  $\omega_p$  can be inferred from relatively large peaks in its frequency response and can be confirmed through numerical results.

Fig. 27. Magnitude frequency response of (24) and a first-order LPF for different values of the cutoff frequency  $\omega_p$ .

Fig. 28. CFN-PLL simulation under the test case 2.

frequency) for the PLL. These selections result in  $k_p = 151$ and  $k_i = 11409$ .

## B. Performance Evaluation

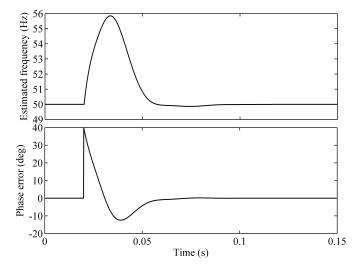

The CFN-PLL can provide a zero steady-state phase error under the test case 1 regardless the value of grid frequency. These results are not shown here due to space limitations. Fig. 28 shows the CFN-PLL simulation results under the test case 2. The settling time of the CFN-PLL is 41 ms, which confirms the fast dynamic response of this PLL. The CFN-PLL fast transient response can also be confirmed under the test case 3.

## C. Extension to the Harmonically Distorted and Unbalanced Grid Condition

Extension of the CFN to take into account the low order harmonic components can be carried out by adding extra synchronous reference frames rotating at the desired angular speeds to the standard structure. Considering the extra computational effort that removal of each harmonic component demands (i.e., two LPFs, two trigonometric function calculation,

Fig. 29. Block diagram description of the CCF-PLL

and several additions and multiplications), a tradeoff between the computational effort and rejection of harmonics should be found.

## VI. DC OFFSET REMOVAL USING COMPLEX COEFFICIENT FILTER

The complex coefficient filters (CCFs) have an asymmetrical frequency response around zero, which enables them to make distinction between the positive and negative polarities (sequences) of the same frequency component. This feature has made them very popular in improving the filtering capability of PLLs [3], [39]-[40].

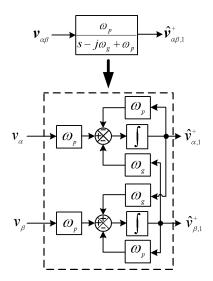

The removal of dc offset in the PLL input using the CCF is shown in Fig. 29. This PLL structure is called the CCF-PLL. In this approach, the  $\alpha\beta$ -frame FFPS component is estimated using a complex bandpass filter (CBF) with center frequency at the fundamental frequency of positive sequence. Equation (25) describes the CBF transfer function, Fig 30 shows its Bode magnitude plot, and Fig. 31 shows its *s*-domain implementation.

$$CBF(s) = \frac{\omega_p}{s - j\omega_g + \omega_p}.$$

(25)

As the Bode plot shows, the CBF only passes the FFPS component and attenuates other frequency components. The extracted FFPS component by the CBF, as shown in Fig. 29, is subtracted from the grid voltage signal and passed through the LPF, which give an estimation of dc component. The dc component is finally subtracted from the grid voltage and fed to the SRF-PLL. Notice that the frequency estimated by the SRF-PLL should be fed back to the CBF to make it frequency

Fig. 30. Bode magnitude plot of (25) for  $\omega_g = 2\pi 50$  rad/s and  $\omega_p = 2\pi 15$  rad/s.

Fig. 31. Implementation of the CBF.

adaptive. The voltage-controlled oscillator (VCO) input, which provides a faster estimate for the grid frequency than the integrator output (within the PI unit), is used for this purpose.

#### A. Equivalence of the CCF-PLL and CFN-PLL

Here, it is shown that the CCF-PLL and CFN-PLL are mathematically equivalent systems, which implies the same design procedure as that proposed for the CFN-PLL can be applied for selecting the CCF-PLL control parameters. This equivalence also shows that the dynamic performance and disturbance rejection capability of the CCF-PLL are the same as those of the CFN-PLL.

From Fig. 29, the SRF-PLL input signal can be expressed in the space vector notation as

$$\boldsymbol{v}_{\alpha\beta}'(s) = \boldsymbol{v}_{\alpha\beta}(s) - \hat{\boldsymbol{v}}_{\alpha\beta,dc}(s)$$

= (1 - LPF(s))  $\boldsymbol{v}_{\alpha\beta}(s) + LPF(s)\hat{\boldsymbol{v}}_{\alpha\beta,1}^+(s)$

= (1 - LPF(s))  $\boldsymbol{v}_{\alpha\beta}(s) + LPF(s)CBF(s)\boldsymbol{v}_{\alpha\beta}'(s).$  (26)

Using (26), the transfer function relating the SRF-PLL input (i.e.,  $v'_{\alpha\beta}$ ) and the grid voltage (i.e.,  $v_{\alpha\beta}$ ) can be obtained as

$$\frac{\boldsymbol{v}_{\alpha\beta}'(s)}{\boldsymbol{v}_{\alpha\beta}(s)} = \frac{1 - \text{LPF}(s)}{1 - \text{LPF}(s) \underbrace{\text{CBF}(s)}_{\text{LPF}(s - i\hat{\omega}_{\alpha})}}.$$

(27)

Fig. 32. A comparison between the dynamic performance and dc offset rejection capability of the CCF-PLL and CFN-PLL. Control parameters:  $k_p = 151, k_i = 11409$ , and  $\omega_p = 2\pi 15$  rad/s.

It can be observed this transfer function is the same as (23), which confirms the CCF-PLL and CFN-PLL are mathematically equivalent systems.

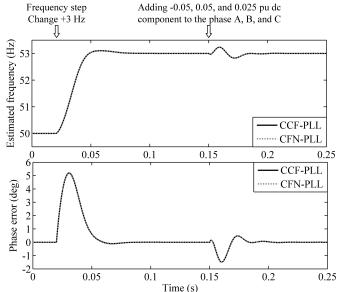

To support this mathematical analysis, the dynamic performance and dc-offset rejection capability of the CCF-PLL and CFN-PLL are compared through simulation results, as shown in Fig. 32. As expected, both PLLs give well-matched responses.

## *B. Extension to the Harmonically Distorted and Unbalanced Grid Condition*

Extension of this approach to take into account the low order harmonic components can be easily carried out by adding extra CBFs with center frequency at the targeted harmonic components.

#### VII. SUMMARY OF RESULTS

Table I summarizes the obtained results. It can be observed that the *dq*DSC-PLL provides a good dc offset rejection capability particularly when the grid frequency is close to its nominal value; however, it suffers from a rather slow transient response. Using the PLC in the *dq*DSC-PLL control loop, as can be seen, improves the PLL dynamic response, but degrades its dc offset rejection capability. The performance of the NF-PLL is comparable with the *dq*DSC-PLL performance. The  $\alpha\beta$ DSC-PLL, CFN-PLL, and CCF-PLL, all demonstrate a fast dynamic response and excellent dc offset rejection capability. It should be mentioned that in our appraisal about the PLLs dynamic behavior, more weight has been given to the results of the phase-angle jump test than those of frequency step change test. The reason is that the grid frequency has a stable nature in practice and its step (sudden) variations are not expected.

|                                               | <i>dq</i> DSC-PLL<br>without PLC / with PLC  | $\alpha\beta$ DSC-PLL with PEC | NF-PLL                | CFN-PLL/CCF-PLL       |

|-----------------------------------------------|----------------------------------------------|--------------------------------|-----------------------|-----------------------|

| dc offset rejection capability                |                                              |                                |                       |                       |

| Peak-to-peak Oscillatory error ( $f = 50$ Hz) | 0° / 0°                                      | 0°                             | 0°                    | 0°                    |

| Peak-to-peak Oscillatory error ( $f = 49$ Hz) | $0.059^{\circ}$ / $0.197^{\circ}$            | 0°                             | $0.059^{\circ}$       | 0°                    |

| Peak-to-peak Oscillatory error ( $f = 47$ Hz) | $0.188^{\circ}$ / $0.647^{\circ}$            | 0°                             | $0.194^{\circ}$       | 0°                    |

| +40° phase-angle jump                         |                                              |                                |                       |                       |

| 2% settling-time                              | 72 ms (3.6 cycles) / 47.4 ms (2.37 cycles)   | 44.4 ms (2.22 cycles)          | 63.9 ms (3.19 cycles) | 41 ms (2.05 cycles)   |

| Phase overshot                                | 14.69° (36.72%) / 16.23° (40.57%)            | 14.17° (35.43%)                | 15.26° (38.15%)       | 12.4° (31%)           |

| Peak frequency error                          | 3.21 Hz / 5.42 Hz                            | 5.32 Hz                        | 3.57 Hz               | 5.8 Hz                |

| +3 Hz frequency step change                   |                                              |                                |                       |                       |

| 2% settling-time                              | 58.1 ms (2.9 cycles) / 57.8 ms (2.92 cycles) | 52.8 ms (2.64 cycles)          | 51.8 ms (2.59 cycles) | 49.6 ms (2.48 cycles) |

| Frequency overshoot                           | 0.03 Hz (1%) / 0.13 Hz (4.3%)                | 0.11 Hz (3.6%)                 | 0.03 Hz (1%)          | 0.1 Hz (3.33%)        |

| Peak phase error                              | 11.49° / 7.1°                                | 6.65°                          | $10.44^{\circ}$       | $5.18^{\circ}$        |

| Stability margin                              |                                              |                                |                       |                       |

| Phase margin                                  | 43.8° / 45°                                  | $58.9^{\circ}$                 | $43.2^{\circ}$        |                       |

| Gain margin                                   | 29.5 dB / 21 dB                              | -10.2 dB                       | 27.3 dB               |                       |

| DC component Estimation                       | No / No                                      | No                             | No                    | Yes                   |

TABLE I SUMMARY OF RESULTS.

#### VIII. CONCLUSION

In this paper a detailed analysis of several techniques to deal with the problem of the dc offset in PLL algorithms has been presented. Using the dqDSC operator as the PLL inloop filtering stage was the first technique. It was shown that the dqDSC operator can significantly improve the dc offset rejecting capability of the PLL, but at the cost of slowing down its dynamic response. To tackle this issue, incorporating a special lead compensator into the PLL control was suggested. it was shown that the lead compensator effectively compensates the phase delay induced by the dqDSC operator and, therefore, enables the dqDSC-PLL to achieve a faster dynamic response without jeopardizing its stability margins. The dc offset reaction capability of the dqDSC-PLL with phase lead compensator is also acceptable. The control parameter design guidelines were also presented.

Using the  $\alpha\beta$ DSC operator as the PLL pre-filtering stage was the second technique. It was shown that  $\alpha\beta$ DSC operator completely blocks the dc offset regardless of the grid voltage frequency value. To eliminate the need for adapting the  $\alpha\beta$ DSC operator to the grid frequency variations, a simple yet effective method was proposed. The small-signal modeling, the stability analysis, and the design guidelines were other contributions of this part.

Employing the wide-bandwidth NF as the PLL in-loop filtering stage was the third technique. A systematic method to design the control parameters of the NF-PLL was proposed and its performance was analyzed. It was shown that the NF enables the PLL to effectively suppress the fundamental frequency oscillatory errors caused by the dc offset, but at the cost of slowing down its dynamic response. Improving the dynamic performance of the NF-PLL was also briefly discussed.

Using the CFN was the fourth technique. The complete rejection of the dc offset from the PLL input, providing an estimation of the grid voltage dc component, and having a fast dynamic response can be considered as the main advantages of this technique.

Using the CCF was the last technique. It was shown that this technique is mathematically equivalent with the CFN based

method. Therefore, it offers the same advantages of the CFN based method.

#### REFERENCES

- T. V. Tran, T. W. Chun, H. H. Lee, H. G. Kim, and E. C. Nho, "PLL-based seamless transfer control between grid-connected and islanding modes in grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5218-5228, Oct. 2014.

- [2] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase grid connected power conditioning systems," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3639-3650, Aug. 2012.

- [3] X. Guo, W. Wu, and Z. Chen, "Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid interfaced converters in distributed utility networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1194-1204, Apr. 2011.

- [4] G. Wang, H. Zhan, G. Zhang, X. Gui, and D. Xu, "Adaptive compensation method of position estimation harmonic error for EMF-based observer in sensorless IPMSM drives," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 3055-3064, Jun. 2014.

- [5] T. Li Tong, X. Zou, S. S. Feng, Y. Chen, Y. Kang, Q. Huang, and Y. Huang, "An SRF-PLL-based sensorless vector control using the predictive deadbeat algorithm for the direct-driven permanent magnet synchronous generator,", *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2837-2849, Jun. 2014

- [6] A. Cataliotti, V. Cosentino, and S. Nuccio, "A phase-locked loop for the synchronization of power quality instruments in the presence of stationary and transient disturbances," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 6, pp. 2232-2239, Dec. 2007.

- [7] M. Karimi Ghartemani, and M. R. Iravani, "A nonlinear adaptive filter for online signal analysis in power systems applications," *IEEE Trans. Power Del.*, vol. 17, no. 2, pp. 617-622, Apr. 2002.

- [8] S. Golestan, and J. M. Guerrero, "Conventional synchronous reference frame phase-locked loop is an adaptive complex filter," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1679-1682, Mar. 2015.

- [9] S. Khajehoddin, M. Karimi-Ghartemani, A. Bakhshai, and P. Jain, "A power control method with simple structure and fast dynamic response for single-phase grid-connected DG systems," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 221-233, Jan. 2013.

- [10] D. Dong, B. Wen, P. Mattavelli, D. Boroyevich, and Y. Xue, "Modeling and design of islanding detection using phase-locked loops in threephase grid-interface power converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 4, pp. 1032-1040, Dec. 2014.

- [11] D. Dong, T. Thacker, I. Cvetkovic, R. Burgos, D. Boroyevich, F. F. Wang, and G. Skutt, "Modes of operation and system-level control of single-phase bidirectional PWM converter for microgrid systems," *IEEE Trans. Smart Grid*, vol. 3, no. 1, pp. 93-104, Mar. 2012.

- [12] A. Hooshyar, and M. Sanaye-Pasand, "Accurate measurement of fault currents contaminated with decaying DC offset and CT saturation," *IEEE Trass. Power Del.* vol. 27, no. 2, pp. 773-783, Apr. 2012.

- [13] Y. Shi, B. Liu, and S. Duan, "Eliminating DC current injection in current-transformer-sensed STATCOMs," *IEEE Trans. Power Electron.*, vol. 28, no. 8, pp. 3760-3767, Aug. 2013.

- [14] M. Ciobotaru, R. Teodorescu, and V. Agelidis, "Offset rejection for pll based synchronization in grid-connected converters," *in Proc. 23rd Annu. IEEE Appl. Power Electron. Conf. Expo.*, Feb. 2008, pp. 1611-1617.

- [15] S. Hwang, L. Liu, H. Li, and J. M. Kim, "DC offset error compensation for synchronous reference frame PLL in single-phase grid-connected converters," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3467-3471, Aug. 2012.

- [16] G. Buticchi, E. Lorenzani, and G. Franceschini, "A dc offset current compensation strategy in transformerless grid-connected power converters," *IEEE Trans. Power Del.*, vol. 26, no. 4, pp. 2743-2751, Oct. 2011.

- [17] S. V. Araujo, P. Zacharias, and R. Mallwitz, "Highly efficient singlephase transformerless inverters for grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 9, pp. 3118-3128, Sep. 2010.

- [18] E. E. Bernabeu, "Modeling geomagnetically induced currents in dominion virginia power using extreme 100-year geoelectric field scenarios-part 1," *IEEE Trans. Power Del.*, vol. 28, no. 1, pp. 516-523, Jan. 2010.

- [19] F. D. Freijedo, Contributions to Grid-Synchronization Techniques for Power Electronic Converter, PhD thesis, Department of Electronic Technology, Vigo University, Vigo, Spain, 2009.

- [20] S. K. Chung, "A phase tracking system for three phase utility interface inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 431-438, May 2000.

- [21] S. Lubura, M. Soja, S. Lale, M. Ikic, "Single-phase phase locked loop with DC offset and noise rejection for photovoltaic inverters," *IET Power Electron.*, vol. 7, no. 9, pp. 2288-2299, Sep. 2014.

- [22] Photovoltaic (PV) Systems-Characteristics of the Utility Interface, IEC Standard 61727, 2004.

- [23] IEEE standard for interconnecting distributed resources with electric power systems, IEEE standard 1547-2003

- [24] M. Karimi Ghartemani, S. Khajehoddin, P. Jain, and A. Bakhshai, "Comparison of two methods for addressing DC component in phaselocked loop (PLL) systems," *in Proc IEEE ECCE*, 2011, pp. 3053-3058.

- [25] M. Karimi Ghartemani, M. Mojiri, A. Safaee, J. A. Walseth, S. A. Khajehoddin, P. Jain, and A. Bakhshai, "A new phase-locked loop system for three-phase applications," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1208-1218, Mar. 2013.

- [26] B. E. O. B. Luna, C. B. Jacobina, A. C. Oliveira, "A new PLL structure for single-phase grid-connected systems," in Proc. 37nd Annual Conference of the IEEE Industrial Electronics Society (IECON) 2011, pp. 1081-1084.

- [27] J. W. Choi, Y. K. Kim, and H. G. Kim, "Digital PLL control for single phase photovoltaic system," *Proc. Inst. Elect. Eng.-Elect. Power Appl.*, vol. 153, no. 1, pp. 40-46, Jan. 2006.

- [28] D. Dong, D. Boroyevich, P. Mattavelli, and I. Cvetkovic, "A highperformance single-phase phase-locked-loop with fast line-voltage amplitude tracking," in Proc. 2011 26th Annual IEEE Applied Power Electronics Conference and Exposition (APEC 2011), Mar. 2011, pp. 1622-1628.

- [29] M. Karimi Ghartemani, S. Khajehoddin, P. Jain, A. Bakhshai, and M. Mojiri, "Addressing DC component in PLL and notch filter algorithms," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 78-86, Jan. 2012.

- [30] G. Fedele, and A. Ferrise "A frequency-locked-loop filter for biased multi-sinusoidal estimation," *IEEE Trans. Signal Process.*, vol. 62, no. 5, pp. 1125-1134, Mar. 2014.

- [31] Y. F. Wang, and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1987-1997, Jul. 2011.

- [32] Y. F. Wang, and Y. Li, "Analysis and digital implementation of cascaded delayed-signal-cancellation PLL," *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1067-1080, Apr. 2011.

- [33] W. Leonard, Control of Electrical Drives. Berlin, Germany: Springer-Verlag, 1990.

- [34] S. Golestan, M. Ramezani, J. M. Guerrero, and M. Monfared, "dq-frame cascaded delayed signal cancellation-based PLL: analysis, design, and comparison with moving average filter-based PLL," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1618-1632, Mar. 2015.

- [35] F. A. S. Neves, H. E. P. de Souza, M. C. Cavalcanti, F. Bradaschia, and E. Bueno, "Digital filters for fast harmonic sequence components separation of unbalanced and distorted three-phase signals," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3847-3859, Oct. 2012.

- [36] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Advantages and challenges of a type-3 PLL," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4985-4997, Nov. 2013.

- [37] P. Rodriguez, A. Luna, I. Candela, R. Mujal, R. Teodorescu, and F. Blaabjerg, "Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid conditions," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 127-138, Jan. 2011.

- [38] F. Gonzalez-Espin, E. Figueres, and G. Garcera, "An adaptive synchronous-reference-frame phase-locked loop for power quality improvement in a polluted utility grid," *IEEE Trans. Ind. Electron.*, vol. 59, no. 6, pp. 2718-2731, Jun. 2012.

- [39] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Performance improvement of a prefiltered synchronous reference frame PLL by using a PID type loop filter," *IEEE Trans. Ind. Electron.* vol. 61, no. 7, pp. 3469-3479, Jul. 2014.

- [40] W. Li, X. Ruan, C. Bao, D. Pan, and X. Wang, "Grid synchronization systems of three-phase grid-connected power converters: a complex vector-filter perspective," *IEEE Trans. Ind. Electron.*, vol. 61, no. 4, pp. 1855-1870, Apr. 2014.

**Saeed Golestan** (M'11-SM'15) received the B.Sc. degree in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2006, and the M.Sc. degree in electrical engineering from Amirkabir University of Technology, Tehran, Iran, in 2009.

In 2009, he joined the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Iran as a lecturer, where he is now head of department. His research interests include phaselocked loop and nonlinear filtering techniques for power and energy applications, power quality mea-

surement and improvement, estimation of power system parameters, and microgrid.

Josep M. Guerrero (S'01-M'04-SM'08-F'15) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000 and 2003, respectively. Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where he is responsible for the Microgrid Research Program. From 2012 he is a guest Professor at the Chinese Academy of Science and the Nanjing

University of Aeronautics and Astronautics; from 2014 he is chair Professor in Shandong University; and from 2015 he is a distinguished guest Professor in Hunan University.

His research interests is oriented to different microgrid aspects, including power electronics, distributed energy-storage systems, hierarchical and cooperative control, energy management systems, and optimization of microgrids and islanded minigrids. Prof. Guerrero is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANS-ACTIONS ON INDUSTRIAL ELECTRONICS, and the IEEE Industrial Electronics Magazine, and an Editor for the IEEE TRANSACTIONS on SMART GRID and IEEE TRANSACTIONS on ENERGY CONVERSION. He has been Guest Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS Special Issues: Power Electronics for Wind Energy Conversion and Power Electronics for Microgrids; the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS Special Sections: Uninterruptible Power Supplies systems, Renewable Energy Systems, Distributed Generation and Microgrids, and Industrial Applications and Implementation Issues of the Kalman Filter; and the IEEE TRANSACTIONS on SMART GRID Special Issue on Smart DC Distribution Systems. He was the chair of the Renewable Energy Systems Technical Committee of the IEEE Industrial Electronics Society. In 2014 he was awarded by Thomson Reuters as Highly Cited Researcher, and in 2015 he was elevated as IEEE Fellow for his contributions on "distributed power systems and microgrids."

Gevork B. Gharehpetian (M'00-SM'08) received his BS, MS and Ph.D. degrees in electrical engineering in 1987, 1989 and 1996 from Tabriz University, Tabriz, Iran and Amirkabir University of Technology (AUT), Tehran, Iran and Tehran University, Tehran, Iran, respectively, graduating all with First Class Honors. As a Ph.D. student, he has received scholarship from DAAD (German Academic Exchange Service) from 1993 to 1996 and he was with High Voltage Institute of RWTH Aachen, Aachen, Germany.

He has been holding the Assistant Professor position at AUT from 1997 to 2003, the position of Associate Professor from 2004 to 2007 and has been Professor since 2007. The power engineering group of AUT has been selected as a Center of Excellence on Power Systems in Iran since 2001. He is a member of this center.

He was selected by the ministry of higher education as the distinguished professor of Iran and by IAEEE (Iranian Association of Electrical and Electronics Engineers) as the distinguished researcher of Iran and was awarded the National Prize in 2008 and 2010, respectively.

Prof. Gharehpetian is a senior and distinguished member of IEEE and IAEEE, respectively, and a member of the central board of IAEEE. Since 2004, he is the Editor-in-Chief of the Journal of IAEEE.

He is the author of more than 700 journal and conference papers. His teaching and research interest include Smart Grid, DGs, Monitoring of Power Transformers, FACTS Devices, HVDC Systems and Power System Transients