#### **Aalborg Universitet**

#### Modified discontinuous PWM for size reduction of the circulating current filter in parallel interleaved converters

Gohil, Ghanshyamsinh Vijaysinh: Maheshwari, Ram Krishan: Bede, Lorand: Kerekes, Tamas: Teodorescu, Remus: Liserre, Marco: Blaabjerg, Frede

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2014.2339392

Publication date: 2015

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Gohil, G. V., Maheshwari, R. K., Bede, L., Kerekes, T., Teodorescu, R., Liserre, M., & Blaabjerg, F. (2015). Modified discontinuous PWM for size reduction of the circulating current filter in parallel interleaved converters. E E E Transactions on Power Electronics, 30(7), 3457-3470. https://doi.org/10.1109/TPEL.2014.2339392

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

### **Aalborg University**

## Modified Discontinuous PWM for Size Reduction of the Circulating Current Filter in Parallel Interleaved Converters

Gohil, Ghanshyamsinh; Maheshwari, Ramkrishan; Bede, Lorand; Kerekes, Tamas; Teodorescu, Remus; Liserre, Marco; Blaabjerg, Frede

Published in:

IEEE Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2014.2339392

Publication date: July, 2014

Link to publication from Aalborg University - VBN

#### Suggested citation format:

Gohil, G.; Maheshwari, R.; Bede, L.; Kerekes, T.; Teodorescu, R.; Liserre, M.; Blaabjerg, F., "Modified Discontinuous PWM for Size Reduction of the Circulating Current Filter in Parallel Interleaved Converters," *IEEE Transactions on Power Electronics*, vol.30, no.7, pp.3457,3470, July 2015.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognize and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain.

- You may freely distribute the URL identifying the publication in the public portal.

#### Take down policy

If you believe that this document breaches copyright please contact us at <a href="mailto:vbn@aub.aau.dk">vbn@aub.aau.dk</a> providing details, and we will remove access to the work immediately and investigate your claim.

1

# Modified Discontinuous PWM for Size Reduction of the Circulating Current Filter in Parallel Interleaved Converters

Ghanshyamsinh Gohil, Student Member, IEEE, RamKrishan Maheshwari, Member, IEEE, Lorand Bede, Student Member, IEEE, Tamas Kerekes, Member, IEEE, Remus Teodorescu, Fellow, IEEE, Marco Liserre, Fellow, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Parallel Voltage Source Converters (VSCs) require an inductive filter to suppress the circulating current. The size of this filter can be minimized by reducing either the maximum value of the flux linkage or the core losses. This paper presents a modified Discontinuous Pulsewidth Modulation (DPWM) scheme to reduce the maximum value of the flux linkage and the core losses in the circulating current filter. In the proposed PWM scheme, the dwell time of an active vector is divided within a half-carrier cycle to ensure simultaneous occurrence of the same zero vectors in both VSCs. A function to decide the ratio of the dwell time of the divided active vector is also presented. The effect of the proposed PWM scheme on the maximum value of the flux linkage and the core losses is analyzed and compared with that of the space vector modulation and 60° clamped DPWM schemes. The analytical expressions for the maximum value of the flux linkage are derived for each of these PWM schemes. In addition, the effect of the proposed PWM scheme on the line current ripple and the switching losses is also analyzed and compared. To verify the analysis, experimental results are presented, which prove the effectiveness of the proposed PWM scheme.

#### I. INTRODUCTION

Three-phase voltage source converter (VSC) is widely used as a dc/ac converter in power electronics applications and often connected in parallel to meet the ever increasing demand for higher power rating converter [1], [2]. In grid-connected application, the total harmonic distortion (THD) in the line current should be low [3]. Due to limited switching frequency in the high power converters, large filters are required [4]. This leads to the increase in the size, weight, and cost of the overall converter system. For VSC fed variable speed machines, the harmonic distortion in the line current must be low for satisfactory operation of the drive [5]. The harmonic distortion depends primarily on the switching sequence, modulation index, and the switching frequency [5]. Several efforts have been made to improve the performance of the VSC in terms of the harmonic distortion and switching losses by using optimal switching sequences for modulation of the VSC legs [6]-[8].

The harmonic distortion in the line current can be reduced by increasing the switching frequency. However, the switching frequency of the semiconductor devices for high power applications is often limited. The effective switching frequency can be increased by using interleaved carriers in parallel-connected VSCs, and the line current quality can be improved [9]. The selection of the proper interleaving angle leads to the reduction

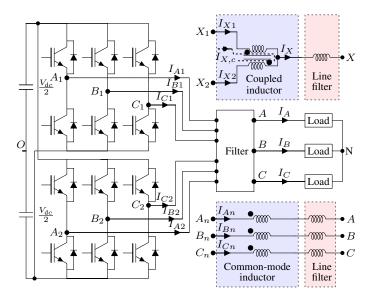

Fig. 1. Two parallel interleaved VSCs with a common dc-link. The filter arrangement for circulating current suppression using the CI and the CM inductor is depicted, where  $X = \{A, B, C\}$  and  $n = \{1, 2\}$ .

in the line current ripple [9]–[15]. This implies that with interleaved parallel VSCs, the size of the line filter can be reduced, or the switching frequency can be reduced for a given set of filter components without violating the THD constraints.

The circulating current is generated in the parallel VSCs due to hardware and control asymmetries [2]. When carrier interleaving is used, the pole voltages (measured with respect to the fictitious mid-point of the dc-link O, as shown in Fig. 1) of the interleaved parallel legs are phase shifted. Therefore, there exists a potential difference that further increases the circulating current [16]. This is a high frequency circulating current with harmonic components concentrated around the odd multiples of the switching frequency [12]. This unwanted current increases stress on the semiconductor switches and causes additional losses. Therefore, it should be suppressed.

The circulating current is strongly influenced by the Pulsewidth Modulation (PWM) scheme. The conventional Space Vector Modulation (SVM) uses two adjacent active vectors and both of the zero vectors to synthesize a reference space vector. The zero vectors are applied at the beginning and at the end of a half-carrier cycle. Various other variants of the

SVM scheme can be obtained by merely dividing the dwell time of the zero vectors unequally [17]. The Discontinuous PWM (DPWM) schemes use only one zero vector in each half-carrier cycle. The commutation of each phase leg is ceased for the one third period of the fundamental cycle [18], [19]. The PWM schemes, which modify the DPWM schemes by dividing one of the active vectors into two equal halves, are proposed in [20], [21]. These PWM schemes affect the line current ripple. A hybrid PWM scheme, which is a combination of the conventional SVM and different DPWM schemes, is proposed in [14] to minimize the line current ripple for the parallel VSCs. However, separate dc-links are used and thus the circulating current filter is not present.

To avoid the circulating current, galvanic isolated transformer can be used for each VSC [22]. However, the use of the bulky transformer adds to the cost and increases the size. Therefore, it should be avoided. Instead of this, a coupled inductor (CI) [23]-[26] for each phase or a common-mode (CM) [27] inductor for each VSC can be used as a circulating current filter (Fig. 1). Assuming strong magnetic coupling in the circulating current filter, the flux linkage in the core due to the line current can be neglected. Therefore, the flux linkage has only the high frequency components determined by the switching frequency. These high frequency components result in high core losses, and the circulating current filter requires larger surface area to dissipate the heat. Ewanchuk et al. [28] proposed a modified DPWM scheme that can make the CM voltage zero. This permits the use of a three limb inductor only. However, the number of commutations are increased. Therefore, it may not be feasible for medium/high power applications. Another PWM scheme is proposed in [29] to change the zero vector pattern by introducing an additional switching. This avoids the coexistence of the different zero vectors at a sector transition, and thus the jumping of the circulating current can be avoided.

The CI is used to provide magnetic coupling between the parallel interleaved legs [23]-[26]. A modified CI, which is proposed in [30], combines the functionality of both the line filter inductor and the circulating current filter. To reduce the flux linkage in the CI, a PWM scheme is proposed in [25]. This PWM scheme adds an optimal common-mode offset to the reference signals based on the modulation index. This can lead to the reduction of the maximum value of the flux linkage, but the discussion on the core losses is not given. However, the core losses are an important parameter to consider in the design of the circulating current filter. As discussed before, the high frequency components of the flux linkage increase the core losses. This may lead to a thermally limited design of the circulating current filter, where the maximum flux density in the core is limited by the heat dissipation capability and not by the magnetic saturation. In this case, the core losses can be reduced by reducing the peak flux density for a given switching frequency and core dimensions.

An active method to reduce the peak flux linkage as well as the core losses for the circulating current filter is proposed in this paper. The method divides the dwell time of an active vector within a half-carrier cycle to ensure simultaneous occurrence of the same zero vectors in both VSCs. A function to calculate the division of the dwell time are also proposed. This reduces both the maximum value of the flux linkage and the core losses in the circulating current filter.

The paper is organized as follows. Section II presents the basic theory of the circulating current. In addition, the relationship between the flux linkage in the circulating current filter and the pole voltages is discussed for the interleaved VSCs. The effect of the different switching sequences on the flux linkage in the core is analyzed in Section III. Section IV presents the proposed DPWM scheme. The effect of the proposed PWM on the flux linkage in the CI and the CM inductor, the harmonic distortion in the line current, and the switching losses are also discussed and compared with that of the SVM and the 60° clamped DPWM. The experimental results are presented in Section V.

#### II. PARALLEL INTERLEAVED VSCs

#### A. Circulating Current

The parallel-connected VSCs are operated with interleaved carrier signals. The circulating current  $(I_{X,c})$  flows through the VSC legs in addition to the line current component  $I_{X1,l}$ , as shown in Fig. 1. Therefore, the phase currents can be given by

$$I_{X1} = I_{X1,l} + I_{X,c}$$

$I_{X2} = I_{X2,l} - I_{X,c}$  (1)

where  $I_{X1,l}$  and  $I_{X2,l}$  are the components of the phase currents contributing to the resultant line current  $I_X$ .  $I_{X,c}$  is the circulating current, where  $X = \{A, B, C\}$ . Assuming ideal VSCs and neglecting the effect of the hardware/control asymmetries, the current component of each VSC, contributing to the grid current, are considered to be equal  $(I_{X1,l} = I_{X2,l})$ . Therefore,

$$I_{X,c} = \frac{I_{X1} - I_{X2}}{2} \tag{2}$$

The differential equation describing phase X circulating current can be given as

$$\frac{dI_{X,c}}{dt} = \frac{V_{X1O} - V_{X2O}}{L_c}$$

(3)

where  $L_c$  is the inductance offered to the circulating current.  $V_{X1O}$  and  $V_{X2O}$  are the pole voltages measured with respect to the fictitious dc-link mid point O.

#### B. Flux Linkage in Circulating Current Filter

To offer the desired inductance  $L_c$  to the circulating current, a CI and a CM inductor based solution is proposed in literature. To design the inductor, the maximum value of the flux linkage should be known. Therefore, the flux linkage analysis for both the CI and the CM inductors is presented in this subsection.

1) Coupled Inductor: In case of the CI, the flux density in the core is given by

$$B_X(t) = \frac{1}{2NA_c} \int (V_{X1O} - V_{X2O})dt \tag{4}$$

and the flux linkage is

$$\lambda_X(t) = \lambda_{X1}(t) + \lambda_{X2}(t) = \int (V_{X1O} - V_{X2O})dt$$

(5)

where N is the number of turns, and  $A_c$  is the core cross-sectional area. The differential voltage across the filter  $(V_{X1O} - V_{X2O})$  is responsible for the flux linkage, and in order to reduce the flux linkage, the time integral of this differential voltage should be reduced [26], [31].

Let L be the self inductance, and M be the mutual inductance of the CI. The pole voltage difference is given by

$$V_{X1O} - V_{X2O} = (L+M)\frac{dI_{X1}}{dt} - (L+M)\frac{dI_{X2}}{dt}$$

(6)

Using (2) and (6), the dynamic equation of the circulating current is given as

$$\frac{dI_{X,c}}{dt} = \frac{V_{X1O} - V_{X2O}}{2(L+M)} \tag{7}$$

If strong coupling is ensured  $(L \approx M)$ , the inductance offered to the circulating current is  $L_c = 4L$ . From (5) and (7), the flux linkage in the CI is proportional to the circulating current  $I_{X,c}$ , which is half of the difference of the phase currents.

2) Common-mode Inductor: In the CM inductor, the magnetic coupling between the phases is used to suppress the circulating current. Since all three phases are wound on the same core, the flux linkage is proportional to the average of the phase currents, and the flux linkage is three times the CM flux linkage, where the CM flux linkage is given as

$$\lambda_{CM}(t) = \frac{\lambda_A(t) + \lambda_B(t) + \lambda_C(t)}{3} = \int (V_{CM1} - V_{CM2}) dt$$

(8)

where  $V_{CMn}$  is the CM voltage of the nth VSC, and it is given by

$$V_{CMn} = \frac{V_{AnO} + V_{BnO} + V_{CnO}}{3}$$

(9)

where  $n = \{1, 2\}.$

The size of the CM inductor can be made smaller by reducing the peak flux linkage, which can be achieved by minimizing the time integral of the difference of the CM voltages. The difference depends on the interleaving angle, modulation index, and the PWM scheme used, and it is described in the following section.

#### III. SWITCHING SEQUENCES AND THEIR EFFECT ON THE FLUX LINKAGE

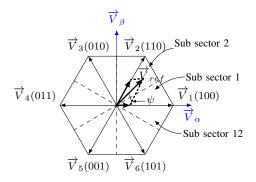

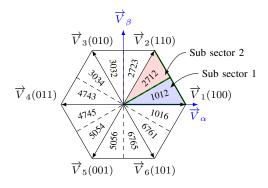

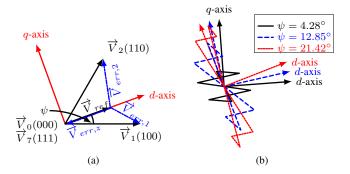

The two-level VSC has eight voltage vectors defined by the combination of the switch states. These states generate six active vectors  $(\overrightarrow{V}_1 - \overrightarrow{V}_6)$  and two zero vectors  $(\overrightarrow{V}_0, \overrightarrow{V}_7)$ , as shown in Fig. 2. The three-phase reference signals can be represented by a complex reference vector  $\vec{V}_{ref}$ . Based on the magnitude  $(|\overrightarrow{V}_{ref}|)$  and angle  $(\psi)$  of the sampled

Fig. 2. Basic space vector sectors and states in complex  $\alpha\beta$  plane.

$\overrightarrow{V}_{ref}$ , two adjacent active voltage vectors and zero vectors are commonly applied to synthesize the reference vector [19], [32], [33]. The respective dwell time of the active vectors is chosen to maintain the volt-sec balance. Let  $T_1$ ,  $T_2$ , and  $T_z$  be the dwell time of  $\overrightarrow{V}_1$ ,  $\overrightarrow{V}_2$ , and  $\overrightarrow{V}_0/\overrightarrow{V}_7$ , respectively, and they are given by

$$T_1 = \frac{2}{\sqrt{3}} \frac{|\vec{V}_{ref}|}{V_{dc}} T_s \sin(60^\circ - \psi)$$

(10a)

$$T_2 = \frac{2}{\sqrt{3}} \frac{|\overrightarrow{V}_{ref}|}{V_{dc}} T_s \sin(\psi)$$

$$T_z = T_s - T_1 - T_2$$

(10b)

$$T_z = T_s - T_1 - T_2 (10c)$$

where  $T_s$  is the carrier interval. The dwell time of the zero voltage vectors  $\overline{V}_0$  and  $\overline{V}_7$  are given by  $K_zT_z$  and  $(1 - K_z)T_z$ , respectively, where  $0 \le K_z \le 1$ . Different modulation possibilities exist with variation in the parameter  $K_z$  [32]. For example,  $K_z = 0.5$  results in the conventional SVM. By changing the value of  $K_z$  between zero and one with a frequency three times higher than the frequency of the reference signal, several DPWM schemes can be realized [32]. If the value of  $K_z$  is changed from zero to one in the middle of the sector 1, the reference signals for 60° clamped DPWM (DPWM1) is generated. Although the number of commutations is two-third of that of the SVM, the switching losses can be reduced up to 50% for unity power factor applications. However, the reduction in the switching losses strongly depend on the displacement power factor angle. For equal switching losses, the carrier frequency of the DPWM1 can be increased by a factor of  $K_f$  times than that of the SVM. The value of  $K_f$  varies in a wide range with the displacement power factor angle [19]. Therefore, the carrier frequency is taken to be the same in all of the cases for comparing the effect of the PWM schemes on the design of the circulating current filter. In addition, the switching losses are also compared for a fair evaluation. The effect of the switching sequences of the SVM and the DPWM1 on the CM flux linkage is analyzed. The interleaving angle is considered to be 180°.

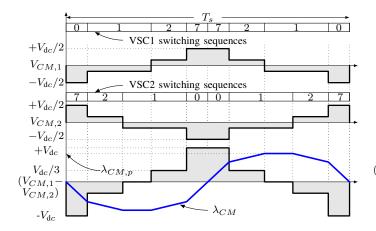

#### A. Conventional Space Vector Modulation

In SVM, the opposite polarity zero vectors are applied at the same time and result in a maximum value of the CM voltage difference, as depicted in Fig. 3. The simultaneous occurrence of  $\overrightarrow{V}_7$  in VSC1 and  $\overrightarrow{V}_0$  in VSC2 results in more flux linkage since the polarity of the CM voltage is opposite in

Fig. 3. SVM: Common mode voltages of individual VSCs and their voltage difference when the carriers are interleaved by an angle of  $180^{\circ}$ .

this case. The same argument applies when both  $\overrightarrow{V}_0$  in VSC1 and  $\overrightarrow{V}_7$  in VSC2 coexist. Both of these undesirable voltage vectors appear when SVM is used with the interleaving angle of  $180^\circ$ . For low modulation indices, the dwell time of the zero vectors is dominant. This results in high flux linkage at lower modulation indices.

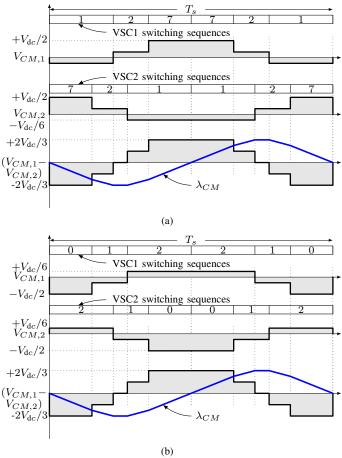

#### B. 60°Clamped Discontinuous PWM (DPWM1)

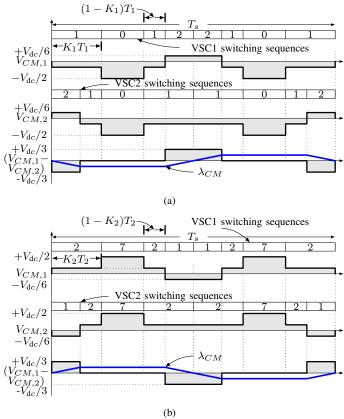

The DPWM1 uses two different switching sequences in each sector. For  $0^{\circ} \leq \psi < 30^{\circ}$  (sub-sector 1), the voltage vectors  $\overrightarrow{V}_1$ ,  $\overrightarrow{V}_2$ , and  $\overrightarrow{V}_7$  (127) are applied sequentially and vice-versa, as shown in Fig. 4(a). Accordingly,  $\overrightarrow{V}_0$ ,  $\overrightarrow{V}_1$ , and  $\overrightarrow{V}_2$  (012) are applied for  $30^{\circ} \leq \psi < 60^{\circ}$  (sub-sector 2), as shown in Fig. 4(b). The CM voltages, their difference, and the CM flux linkage in both of the sub-sectors are depicted in Fig. 4. The use of  $\overrightarrow{V}_1$  and  $\overrightarrow{V}_7$  results in opposite polarity CM voltages. Similarly, the polarities of the CM voltages are different when the voltage vectors  $\overrightarrow{V}_0$  and  $\overrightarrow{V}_2$  are used. The CM voltage difference increases if the polarities of the CM voltages are different in both VSCs. These undesirable vectors appear in both sub-sectors, when DPWM1 is used, as shown in Fig. 4.

## IV. MODIFIED DPWM FOR CIRCULATING CURRENT REDUCTION

It is evident that the PWM sequences determine the flux linkage pattern. Therefore, the design of the circulating current filter is strongly influenced by the PWM scheme used. Some vectors in a PWM scheme which may lead to high flux linkage are summarized below.

- The simultaneous application of  $\overrightarrow{V}_7$  in VSC1 and  $\overrightarrow{V}_0$  in VSC2 and vice-versa.

- The simultaneous occurrence of a zero vector in VSC1 and an active vector in VSC2 and vice-versa. For example, the simultaneous occurrence of  $\overrightarrow{V}_7$  and  $\overrightarrow{V}_1$  (vectors with opposite polarity CM voltage).

Since these vectors cause high flux linkage in the circulating current filter, they should be avoided. However, if the same

Fig. 4. DPWM1: Switching sequences and common-mode voltages of both the VSCs. (a) sub-sector: 1,  $0^{\circ} \le \psi < 30^{\circ}$ , (b) sub-sector: 2,  $30^{\circ} \le \psi < 60^{\circ}$ .

zero vectors in both VSCs (e.g.  $\overrightarrow{V}_7$  in both VSCs) are applied simultaneously, a significant reduction in the flux linkage can be achieved. Based on these observations, a PWM scheme is presented where the division of an active vector within a half-carrier cycle is used to align the same zero vector in both VSCs.

The PWM schemes where the dwell time of the active vector are divided into two equal intervals in each half-carrier cycle is proposed in [5], [20], [21], [34], [35]. However, the dwell time of an active vector is not divided equally in this paper. It is divided in a manner to align the same zero vectors of both VSCs. The ratio, in which the dwell time is divided, varies with the reference space vector angle, and it is updated in each half-carrier cycle.

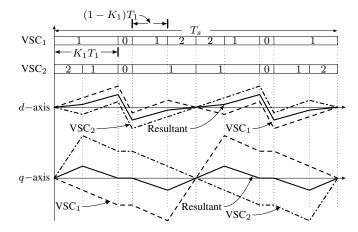

The sequences used in the proposed PWM scheme are depicted in Fig. 5. The numbers shown in Fig. 5 represent the sequence in which the voltage vectors are applied, e.g. 1012 represents that  $\overrightarrow{V}_1$ ,  $\overrightarrow{V}_0$ ,  $\overrightarrow{V}_1$ , and  $\overrightarrow{V}_2$  are applied in sequence. The discussion is restricted to the first sector of the space vector diagram. The same discussion applies to other sectors due to the symmetry. From Fig. 5, it is evident that each phase discontinues switching for one third period of the fundamental cycle. For example, phase A is clamped twice to the positive dc-link for  $30^\circ \leqslant \psi < 60^\circ$  and  $300^\circ \leqslant \psi < 330^\circ$

Fig. 5. Switching sequences of the proposed scheme in each sub-sector.

Fig. 6. Proposed modulation scheme: Switching sequences and CM voltages of both the VSCs with an interleaving angle of  $180^\circ$ . (a) sub-sector 1:  $0^\circ \le \psi < 30^\circ$ , (b) sub-sector 2:  $30^\circ \le \psi < 60^\circ$ .

and clamped twice to the negative dc-link for  $120^\circ \leqslant \psi < 150^\circ$  and  $210^\circ \leqslant \psi < 240^\circ$  in a fundamental period. The active voltage vector with the maximum dwell time is divided into two intervals and applied twice in a half-carrier cycle. Therefore, one of the phase legs is switched twice. In the proposed PWM scheme, one phase does not switch, whereas one of the phases is switched twice in a half-carrier cycle. Hence, it is referred to as the modified DPWM in this paper.

If the reference vector is in sub-sector 1, as shown in Fig. 5, the dwell time of  $\overrightarrow{V}_1$  is more than the dwell time of  $\overrightarrow{V}_2$ . Thus, the dwell time of  $\overrightarrow{V}_1$  is divided, and  $\overrightarrow{V}_0$  is applied in between to ensure simultaneous occurrence of the same zero vector in both VSCs. The reverse is true for sub-sector

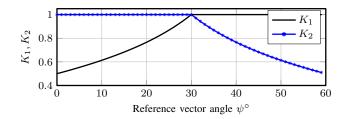

Fig. 7. Variation in parameter  $K_1$ ,  $K_2$  with reference vector angle  $\psi$ . Due to the symmetry the plot is restricted to the first sector.

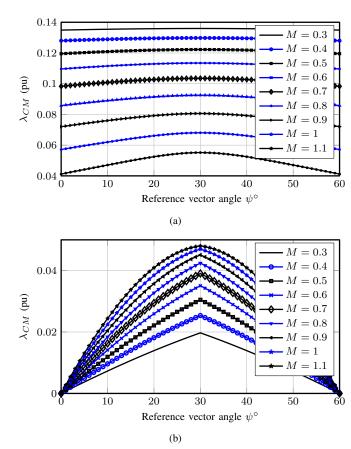

Fig. 8. RMS value of the CM flux linkage  $\lambda_{CM}$  vs. reference space vector angle  $\psi$  in a switching cycle for (a) SVM and (b) the proposed PWM scheme. The flux linkage is normalized with respect to the  $V_{\rm dc}T_{\rm s}$ .

2. Therefore, in sub-sector 1 (0°  $\leq \psi < 30^{\circ}$ ),  $T_1$  is divided into two intervals and can be given as

$$T_1 = K_1 T_1 + (1 - K_1) T_1 \tag{11}$$

where  $0 \leqslant K_1 \leqslant 1$ . Similarly, in sub-sector 2 (30°  $\leqslant \psi < 60^{\circ}$ ),  $T_2$  is divided into two intervals;

$$T_2 = K_2 T_2 + (1 - K_2) T_2 \tag{12}$$

where  $0 \le K_2 \le 1$ . The flexibility offered by the division of the active vectors is used to ensure simultaneous occurrence of the same zero vectors in both VSCs.

The switching sequences and the CM voltages in sub-sector 1 and sub-sector 2 for the proposed scheme are shown in Fig. 6(a) and Fig. 6(b), respectively for one switching cycle. In sub-sector 1, the value of  $K_1$  is updated in each half-carrier cycle,

while  $K_2$  is equal to one. In sub-sector 2,  $K_2$  is varied, and  $K_1$  is equal to one. The careful observation of the switching sequence depicted in Fig. 6 reveals that the same zero vector of both VSCs can coexist if

$$K_1 = \frac{T_1 + T_2}{2T_1}, K_2 = 1 \tag{13}$$

in sub-sector 1 and

$$K_1 = 1, K_2 = \frac{T_1 + T_2}{2T_2} \tag{14}$$

in sub-sector 2. The variation of  $K_1$  and  $K_2$  over a sector is depicted in Fig. 7. The rms value of the CM flux linkage  $\lambda_{CM}$  in a switching cycle for the proposed scheme is shown in Fig. 8 and compared with that of the SVM. A substantial reduction in  $\lambda_{CM}$  is achieved, especially at low values of the modulation indices.

As discussed in Section II, the PWM schemes strongly influence the flux linkage and the core losses in the circulating current filter. Therefore, the effects of the proposed PWM scheme on the filter design along with the line ripple current and the switching losses are discussed and compared with that of the SVM and the DPWM1 in the following subsections.

#### A. Effect of the Switching Sequences on the Circulating Current Filter Design

The circulating current is suppressed by introducing an impedance in the circulating current path. Typically, this impedance can be introduced by inserting CM inductor in series with the line filter inductors [27] or using CI for each phase group [23]–[25], [30]. Assuming a strong coupling between the windings, the effect of the leakage flux is neglected in the analysis. Therefore, the flux linkage in the core has only high frequency components, which result in more core losses. In addition to this, the maximum value of the flux linkage in the core also influences the core size. Therefore, both maximum value of the flux linkage and the core losses should be considered while designing both the CI and the CM inductor, and they are discussed below.

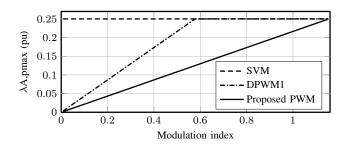

1) Coupled Inductor: The CI provides magnetic coupling between the interleaved legs, and the schematic is shown in Fig. 1. The flux linkage in the coupled inductor of phase A is evaluated using (5). Since the dwell time is updated in each half carrier cycle, the peak flux linkage is also different for each half-carrier cycle. The formulas describing the maximum value of the peak flux linkage as a function of the modulation index is given in Table. I, and plotted in Fig. 9. The maximum value of the peak flux linkage is the same in all cases. However, the flux linkage pattern is different, which affects the core losses, and thus the design of the CI.

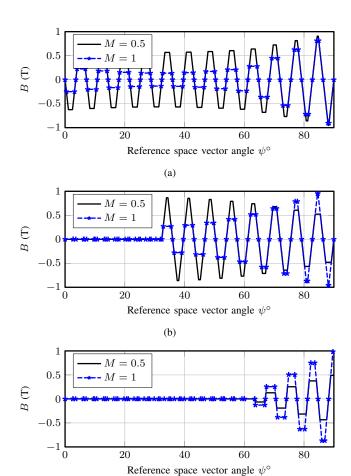

Due to the quarter wave symmetry of the reference signal, the flux density pattern is the same in each quarter period of the fundamental cycle. Thus, it is sufficient to evaluate the core losses for that period (e.g.  $0^{\circ} \leq \psi \leq 90^{\circ}$ ). The flux density behavior in a half-carrier cycle for the proposed PWM scheme is described by the piecewise linear equations given in Table IV and depicted in Fig. 10(c). The piecewise linear equations, describing the flux density behavior in the CI, for the SVM and

TABLE I

MAXIMUM VALUE OF THE PEAK FLUX LINKAGE IN A CI FOR DIFFERENT

MODULATION SCHEMES

| Scheme   | Max. value of peak flux linkage $(\lambda_{A,pmax})$                                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SVM      | $\lambda_{A,pmax} = \frac{1}{4} V_{dc} T_s$                                                                                                                                                              |

| DPWM1    | $\lambda_{A,pmax} = \begin{cases} V_{dc} T_s(\frac{1}{\sqrt{3}} \frac{ \vec{\mathbf{V}}_{ref} }{V_{dc}}), & 0 \le M < 1/\sqrt{3} \\ \frac{1}{4} V_{dc} T_s, & 1/\sqrt{3} \le M < 2/\sqrt{3} \end{cases}$ |

| Proposed | $\lambda_{A,pmax} = V_{dc} T_s (\frac{1}{2\sqrt{3}} \frac{ \overrightarrow{V}_{ref} }{V_{dc}})$                                                                                                          |

Fig. 9. Comparison of the maximum value of the peak flux linkage as a function of the modulation index. The flux linkage is normalized with respect to the  $V_{\rm dc}T_s$ .

the DPWM1 are given in Table II and Table III, respectively. The term  $T_3$  in those tables is the dwell time of the voltage vector  $\overrightarrow{V}_3$ .

In case of SVM, the core is excited over an entire fundamental cycle. However, for the DPWM1, the core is excited for two third of the fundamental cycle, as shown in Fig. 10. On the other hand, in the proposed PWM scheme, the core is excited only for one third of the fundamental cycle, as depicted in Fig. 10(c).

The core losses with the proposed PWM scheme are expected to reduce due to the reduction in both the peak flux linkage and the duration of the core excitation, and it is evaluated using the Improved Generalized Steinmetz Equation (IGSE) [36], [37] given as

$$P_v = \frac{1}{T} \int_0^T k_i \left| \frac{dB(t)}{dt} \right|^{\alpha} (\Delta B)^{\beta - \alpha} dt$$

(15)

where  $\alpha$ ,  $\beta$ , and  $k_i$  are the constants determined by the material characteristics, and  $P_v$  is the core loss per unit volume. Using (15), the core losses averaged over a quarter of the fundamental cycle is given as

$$P_{v,avg} = \frac{2}{(\frac{f_{sw}}{f_0})} \sum_{k=1}^{(\frac{f_{sw}}{2f_0})} \frac{2}{T_s} \int_{0}^{\frac{T_s}{2}} k_i |\frac{dB_k(t)}{dt}|^{\alpha} (\Delta B_k)^{\beta-\alpha} dt$$

(16)

where  $f_0$  is the fundamental frequency, and  $f_{sw}$  is the switching frequency. In order to make the core loss analysis more general (independent of the core dimensions), the loss behavior

TABLE II

FLUX DENSITY DESCRIPTION IN A HALF-CARRIER CYCLE USING PIECEWISE LINEAR EQUATIONS FOR SVM

| PWM scheme | Sub-sector                          | Peak flux density $B_p$           | Flux density $B(t)$                                                                                                                                                                                                                                                                           |

|------------|-------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SVM        | $0^{\circ} \le \psi \le 90^{\circ}$ | $B_p = \frac{V_{dc}(T_z)}{8NA_c}$ | $B(t) = \frac{4B_p}{T_z}t \text{ for } 0 \le t \le \frac{T_z}{4}$ $B(t) = B_p \text{ for } \frac{T_z}{2} \le t \le (\frac{T_s}{2} - \frac{T_z}{4})$ $B(t) = B_p - \frac{4B_p}{T_z}[t - (\frac{T_s}{2} - \frac{T_z}{4})] \text{ for } (\frac{T_s}{2} - \frac{T_z}{4}) \le t \le \frac{T_s}{2}$ |

TABLE III

DPWM1: Flux density description in a half switching cycle using piecewise linear equations

| Sub-sector                           | $\overrightarrow{V}_{ref}$ position               | Peak flux density $B_p$                 | Flux density $B(t)$                                                                                                                                                |

|--------------------------------------|---------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $0^{\circ} \le \psi \le 30^{\circ}$  | -                                                 | $B_p = 0$                               | B(t) = 0                                                                                                                                                           |

|                                      | $M_{\text{ang}}(20, -4) > 1$                      | $V_{do}T_{z}$                           | $B(t) = \frac{-2B_p}{T_z}t,  \text{for } 0 \le t \le \frac{T_z}{2}$                                                                                                |

|                                      | $M\cos(30 - \psi) \geqslant \frac{1}{\sqrt{3}}$   | $B_p = \frac{V_{dc}T_z}{4NA_c}$         | $B(t) = -B_p$ , for $\frac{T_z}{2} \le t \le \frac{T_s - T_z}{2}$                                                                                                  |

| $30^{\circ} \le \psi \le 60^{\circ}$ |                                                   |                                         | $B(t) = -B_p + \frac{2B_p}{T_z} [t - (\frac{T_s - T_z}{2})], \text{ for } \frac{T_s - T_z}{2} \le t \le \frac{T_s}{2}$                                             |

|                                      | $M\cos(30 - \psi) < \frac{1}{\sqrt{3}}$           | $B_p = \frac{V_{dc}(T_1 + T_2)}{4NA_c}$ | $B(t) = \frac{-2B_p}{T_1 + T_2}t$ , for $0 \le t \le \frac{T_1 + T_2}{2}$                                                                                          |

|                                      |                                                   |                                         | $B(t) = -B_p$ , for $\frac{T_1 + T_2}{2} \le t \le \frac{T_s - T_1 + T_2}{2}$                                                                                      |

|                                      |                                                   |                                         | $B(t) = -B_p + \frac{2B_p}{T_1 + T_2} [t - (\frac{T_s - T_1 - T_2}{2})],  \text{for } \frac{T_s - T_1 - T_2}{2} \le t \le \frac{T_s}{2}$                           |

|                                      |                                                   | TV (TT + TT )                           | $B(t) = \frac{-2B_p}{T_z + T_2}t$ , for $0 \le t \le \frac{T_z + T_3}{2}$                                                                                          |

|                                      | $M\sin(60 - \psi_s) \geqslant \frac{1}{\sqrt{3}}$ | $B_p = \frac{V_{dc}(I_z + I_3)}{4NA_c}$ | $B(t) = -B_p$ , for $\frac{T_z + T_3}{2} \le t \le \frac{T_s - T_z - T_3}{2}$                                                                                      |

| $60^{\circ} \le \psi \le 90^{\circ}$ |                                                   |                                         | $B(t) = -B_p + \frac{2B_p}{T_z + T_3} \left[ t - \left( \frac{T_s - T_z - T_3}{2} \right) \right],  \text{for } \frac{T_s - T_z - T_3}{2} \le t \le \frac{T_s}{2}$ |

|                                      | 16 1 (00 1) 1                                     | _ V. To                                 | $B(t) = \frac{-2B_p}{T_2}t,  \text{for } 0 \le t \le \frac{T_2}{2}$                                                                                                |

|                                      | $M\sin(60-\psi_s)\geqslant \frac{1}{\sqrt{3}}$    | $B_p = \frac{V_{dc}T_2}{4NA_c}$         | $B(t) = -B_p$ , for $\frac{T_2}{2} \le t \le \frac{T_s - T_2}{2}$                                                                                                  |

|                                      |                                                   |                                         | $B(t) = -B_p + \frac{2B_p^2}{T_z + T_3} [t - (\frac{T_s - \tilde{T_2}}{2})], \text{ for } \frac{T_s - T_2}{2} \le t \le \frac{T_s}{2}$                             |

TABLE IV

FLUX DENSITY DESCRIPTION IN CI FOR THE PROPOSED PWM SCHEME USING PIECEWISE LINEAR EQUATIONS

| Sub-sector                           | Peak flux density $B_p$           | Flux density $B(t)$                                                                                                                                                                                                                                         |

|--------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $0^{\circ} \le \psi \le 60^{\circ}$  | $B_p = 0$                         | B(t) = 0                                                                                                                                                                                                                                                    |

| $60^{\circ} \le \psi \le 90^{\circ}$ | $B_p = \frac{V_{dc}(T_3)}{4NA_c}$ | $B(t) = \frac{2B_p}{T_3}t \text{ for } 0 \le t \le \frac{T_3}{2}$ $B(t) = B_p \text{ for } \frac{T_3}{2} \le t \le \frac{T_s - T_3}{2}$ $B(t) = B_p - \frac{2B_p}{T_3}[t - (\frac{T_s - T_3}{2})] \text{ for } \frac{T_s - T_3}{2} \le t \le \frac{T_s}{2}$ |

is described in terms of  $B_{max}$  and  $T_s$ , as

$$P_{v,avg} = \frac{2}{\left(\frac{f_{sw}}{f_0}\right)} \sum_{k=1}^{\left(\frac{f_{sw}}{2f_0}\right)} \frac{2}{T_s} \int_{0}^{\frac{T_s}{2}} k_i (4B_{max}f_{sw})^{\alpha} (\Delta B_k)^{\beta-\alpha} dt$$

(17)

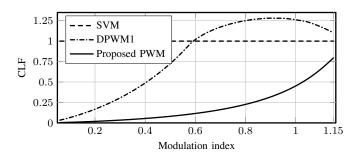

To make the core losses comparison independent of the design parameters, the analysis is presented in terms of the Core Loss Function (CLF), where CLF is given as the ratio of the average volumetric core loss for a PWM scheme to the average volumetric core loss for the SVM at a given modulation index M.

$$CLF = \frac{P_{v,avg}(M)}{P_{v,avg(SVM)}(M)}$$

(18)

The CLFs for all considered PWM schemes are depicted in Fig. 11. Amorphous metal core is considered, where  $\alpha=1.51$ ,  $\beta=1.74$ , and  $k_i=0.622$ . Lower core losses over the entire modulation range are observed for the proposed method compared to the other considered schemes. The use of the SVM results in highest core losses in the CI for low modulation indices (M<0.6), whereas the core losses are the highest in case of DPWM1 at high modulation indices.

The volume optimized design of the inductor often results in non-saturated thermally limited design, and the core losses primarily determine the size of the CI [38]. Due to the substantial reduction in the core losses with the proposed scheme, small size of the CI with minimal thermal management can be achieved with the proposed PWM scheme.

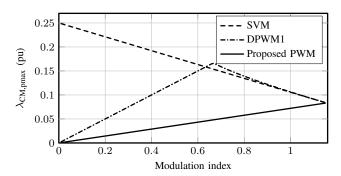

2) Common-mode Inductor: Asiminoaei et al. [27] proposed the use of a CM inductor to reduce the circulating current. This solution permits un-equal load sharing between the parallel interleaved VSCs and scalability, and may be a preferred solution when the modularity is the main design objective. The volume of the CM inductor can be minimized by reducing either the maximum value of the peak CM flux linkage or the core losses. The maximum value of the peak CM flux linkage as a function of the modulation index is given in Table V and plotted in Fig. 12 for the proposed PWM scheme along with that of the SVM and the DPWM1.

For SVM, the maximum value of the peak flux linkage increases as the modulation index decreases. Therefore, for applications demanding operation over the full modulation range, the CM inductor has to be designed for the maximum flux linkage, which occurs at low modulation indices. On the

| TABLE V                                   |  |  |  |  |  |

|-------------------------------------------|--|--|--|--|--|

| MAXIMUM VALUE OF THE PEAK CM FLUX LINKAGE |  |  |  |  |  |

| PWM scheme          | Max of the peak CM flux linkage $(\lambda_{CM,pmax})$                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SVM                 | $\lambda_{CM,pmax} = V_{dc}T_s(\frac{1}{4} - \frac{1}{3\sqrt{3}}\frac{ \overrightarrow{V}_{ref} }{V_{dc}})$                                                                                                                                                                                                                                                                                                                           |

| DPWM1               | $\lambda_{CM,pmax} = V_{dc} T_s \left( \frac{1}{3} \frac{ \overrightarrow{\boldsymbol{V}}_{ref} }{V_{dc}} \right) \text{ for } (0 \le M \le \frac{2}{3})$ $\lambda_{CM,pmax} = V_{dc} T_s \left( \frac{1}{3} - \frac{1}{3} \frac{ \overrightarrow{\boldsymbol{V}}_{ref} }{V_{dc}} \cos(60 - \arcsin \frac{\sqrt{3}V_{dc}}{4 \overrightarrow{\boldsymbol{V}}_{ref} }) \right) \text{ for } (\frac{2}{3} \le M \le \frac{2}{\sqrt{3}})$ |

| Proposed PWM scheme | $\lambda_{CM,pmax} = V_{dc} T_s (\frac{1}{6\sqrt{3}} \frac{ \overrightarrow{V}_{ref} }{V_{dc}})$                                                                                                                                                                                                                                                                                                                                      |

Fig. 10. The flux density pattern in the CI core for modulation indices of 0.5 and 1. (a) SVM, (b) DPWM1, (c) Proposed scheme.

(c)

Fig. 11. CLF as a function of the modulation index.

Fig. 12. Comparison of the maximum values of the peak CM flux linkage as a function of the modulation index. The flux linkage is normalized with respect to  $V_{\rm dc}T_{\rm s}$ .

other hand, the CM is subjected to maximum flux linkage for a modulation index M=2/3 if DPWM1 is employed. The proposed PWM scheme has the lowest peak flux linkage, compared to other PWM schemes, for the entire modulation range. The reduction in the maximum flux linkage in case of the CM filter is achieved by using the proposed DPWM scheme. As a result, small CM inductor can be realized.

#### B. Ripple Current Analysis

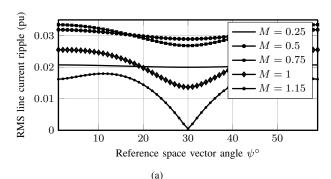

The line current ripple of the proposed PWM scheme is analyzed and compared with that of the SVM and the DPWM1. The reference vector is synthesized using the discrete vectors. Thus, at any given instant, an error between the applied voltage vector and the reference vector exists. The error voltage vectors for a given sampling instance are shown in Fig. 13(a). The time integral of the error vectors gives the harmonic flux vector, which is proportional to the ripple current [5], [20], [21].

In the synchronously rotating reference frame, the instantaneous error voltage vectors depicted in Fig. 13(a) are given as

$$\overrightarrow{\boldsymbol{V}}_{err,1} = [\cos \psi - V_{ref}] - j \sin \psi$$

$$\overrightarrow{\boldsymbol{V}}_{err,2} = [\cos(60^{\circ} - \psi) - V_{ref}] + j \sin(60^{\circ} - \psi) (19b)$$

$$\overrightarrow{\boldsymbol{V}}_{err,z} = -V_{ref}$$

(19c)

In the proposed scheme, the time duration, for which an active vector is applied, is divided unequally, and the division of the active vector follows the rule given by (13) and (14). For the

Fig. 13. (a) The active and zero vectors to synthesize given reference vector and corresponding error voltage vectors, (b) Harmonic flux vector trajectory for different values of reference vector angle  $\psi$  for 1012 sequence in subsector 1.

Fig. 14. d-axis and q-axis ripple components of a harmonic flux vector over a switching cycle for two parallel VSCs and their resultant with an interleaving angle of  $180^{\circ}$  and reference vector angle  $\psi=12.8^{\circ}$ .

proposed PWM scheme, the harmonic flux vector is given as

$$\overrightarrow{V}_{err,1}K_1T_1 = [\cos \psi - V_{ref}]K_1T_1 - jK_1T_1 \sin \psi(20a)$$

$$\overrightarrow{V}_{err,1}(1 - K_1)T_1 = [\cos \psi - V_{ref}](1 - K_1)T_1$$

$$-j(1 - K_1)T_1 \sin \psi \qquad (20b)$$

$$\overrightarrow{V}_{err,2}T_2 = [\cos(60^\circ - \psi) - V_{ref}]T_2$$

$$+jT_2 \sin(60^\circ - \psi) \qquad (20c)$$

$$\overrightarrow{V}_{err,z}T_z = -V_{ref}T_z \qquad (20d)$$

and it is plotted in Fig. 13(b) for different values of the reference space vector angles. The harmonic flux vector is decomposed into d-axis and q-axis components, as shown in Fig. 14. The resultant vector for an interleaving angle of  $180^{\circ}$  is also shown, and it is used to evaluate the ripple current/harmonic content in the line current.

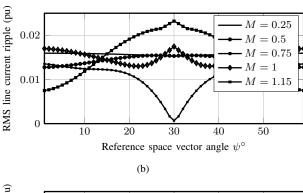

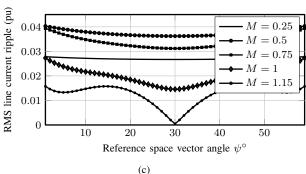

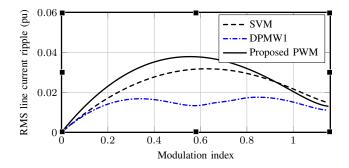

The normalized rms value of the line current ripple over a half-carrier cycle [14] for different modulation indices for the proposed PWM scheme is plotted in Fig. 15(c) as a function of the  $\psi$ . The variation in the rms value of the line current ripple for SVM and DPWM1 are also shown in Fig. 15(a) and 15(b), respectively. The variation of the total rms value of the line current ripple over the entire modulation range is also shown in Fig. 16. DPWM1 demonstrates better line current quality

Fig. 15. Space dependency of the rms value of the line current ripple (normalized) for different modulation indices. (a) SVM, (b) DPWM1, (c) Proposed scheme.

Fig. 16. Total rms value of the line current ripple (normalized) as a function of modulation index.

over an entire modulation range. The total rms value of the line current ripple for the proposed PWM scheme closely matches that of the SVM. For SVM, the harmonic content for low modulation indices is slightly less compared to the proposed PWM scheme. On the other hand, the line current quality in the case of the proposed PWM scheme is marginally better

Fig. 17. Comparison of the switching losses.

than that of the SVM at higher modulation indices (M>0.9).

#### C. Semiconductor losses

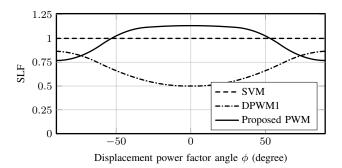

Although one of the phase legs is clamped to dc-link for one third period of the fundamental cycle in the proposed scheme, an additional commutation is introduced in another leg as explained in the previous section. Thus, the switching losses are also evaluated in this paper. The switching losse function (SLF) [18] is used to compare the switching losses of the proposed PWM with other PWM schemes. The turn-on and turn-off characteristics of the semiconductor devices are assumed to be linear with respect to time. The contribution of the ripple current towards the switching losses is also neglected. Since the SLF normalizes the switching loss of the proposed method with respect to the switching loss of SVM, the relative error is small despite the simplified loss model [18] used. The SLF for the proposed method is given as

$$SLF = \begin{cases} 1 + (\frac{2-\sqrt{3}}{2})\cos\phi, & 0 \leqslant |\phi| < \frac{\pi}{6} \\ \cos\phi + \frac{1}{2}\sin\phi, & \frac{\pi}{6} \leqslant |\phi| < \frac{\pi}{3} \\ 2 - (\frac{2\sqrt{3}-1}{2})\sin\phi, & \frac{\pi}{3} \leqslant |\phi| \leqslant \frac{\pi}{2} \end{cases}$$

(21)

where  $\phi$  is the displacement power factor angle. The SLFs for the proposed PWM scheme along with that of the SVM and DPWM1 are plotted in Fig. 17. For the unity power factor applications, the switching losses are minimum if DPWM1 is used. For a displacement power factor angle higher than 53°, the proposed method has lower switching losses compared to that of the SVM. However, for a displacement power factor angle in the vicinity of zero, the proposed method has high switching losses. For the reactive power compensation applications, the use of the proposed PWM scheme results in the lowest switching losses, as shown in Fig. 17.

#### V. EXPERIMENTAL RESULTS

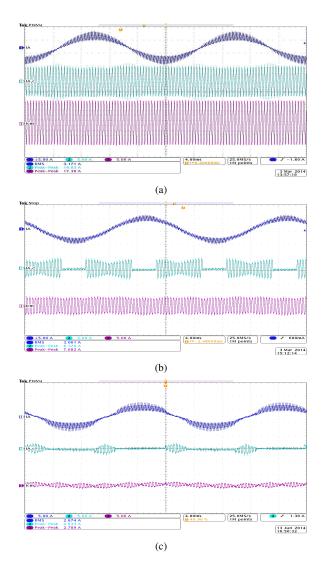

The experiments have been performed using single-phase inductors, which act as both line filter inductor and the circulating current filter. This arrangement is used to simplify the measurement [39]. The results for  $I_{A1}-I_{A2}$  are obtained, which is equal to  $2\times I_{A,c}$ . As explained in Section II, the  $I_{A,c}$  is proportional to the flux linkage in CI. Similarly, the sum of three-phase currents of each VSC is obtained. This current is equal to  $3\times I_{CM}$ , and it is proportional to the CM flux linkage. The dc-link voltage of 600 V is used. The carrier frequency is

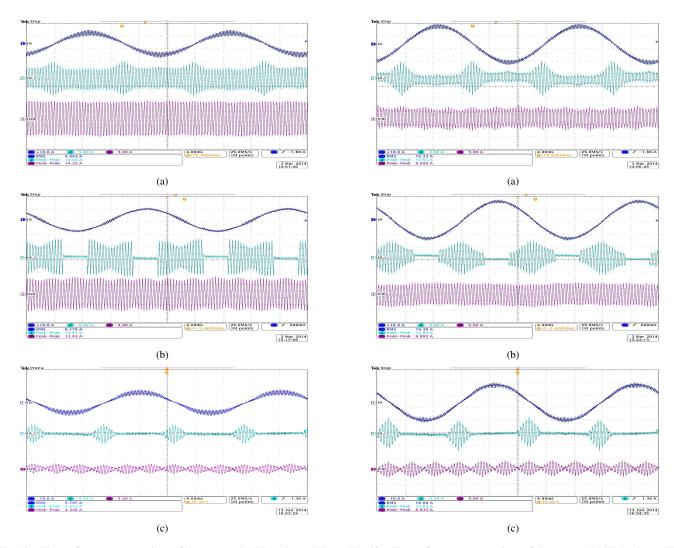

Fig. 18. The performance comparison of the proposed PWM scheme. The modulation index M=0.3. Ch1: Phase A line current (5 A/div), Ch2: Phase A circulating current (2  $\times$   $I_{A,c}$ ) (5 A/div), Ch3: CM circulating current (3  $\times$   $I_{CM}$ ) (5 A/div). (a) SVM, (b) DPWM1, (c) Proposed scheme.

taken to be 2.5 kHz and interleaving angle of  $180^{\circ}$  is chosen. The line filter inductor of 6.8 mH is used, and a resistive load is set to 20  $\Omega$ . The inductance in the circulating current path is  $L_c = 2 \times 6.8$  mH.

The line current of phase A  $(I_A)$ , the circulating current of Phase A  $(2 \times I_{A,c})$ , and the CM current  $(3 \times I_{CM})$  for modulation index of 0.3, 0.6, and 1 for SVM, DPWM1, and the proposed PWM scheme is depicted in Fig. 18, 19, and 20, respectively. The experiments have been performed for the entire linear range of the modulation index and the results are given in Table VI. The line current THD, the maximum value of the peak circulating current of phase A, and the maximum value of the peak CM circulating current of the proposed method are compared with that of the SVM and the DPWM1. The THD is calculated by performing discrete Fourier transform of the measured line current.

For the SVM, the maximum value of the peak circulating current of phase A remains almost constant over the entire modulation range. Since, the phase A circulating current is

TABLE VI PERFORMANCE COMPARISON OF THE PROPOSED METHOD

| M    | Max. of $I_{A,c}$ (A) |       |          | Max. of $I_{CM}(A)$ |       |          | Line current THD (%) |       |          |

|------|-----------------------|-------|----------|---------------------|-------|----------|----------------------|-------|----------|

|      | SVM                   | DPWM1 | Proposed | SVM                 | DPWM1 | Proposed | SVM                  | DPWM1 | Proposed |

| 0.1  | 3.55                  | 0.79  | 0.59     | 3.98                | 0.52  | 0.32     | 24.15                | 26.14 | 28.62    |

| 0.2  | 3.52                  | 1.46  | 0.85     | 3.12                | 0.93  | 0.33     | 22.30                | 19.29 | 25.31    |

| 0.3  | 3.50                  | 2.09  | 1.15     | 2.89                | 1.28  | 0.46     | 19.60                | 15.21 | 22.06    |

| 0.4  | 3.55                  | 2.68  | 1.42     | 2.71                | 1.62  | 0.52     | 17.63                | 11.56 | 19.68    |

| 0.5  | 3.50                  | 3.23  | 1.76     | 2.57                | 1.94  | 0.61     | 15.86                | 7.95  | 16.49    |

| 0.6  | 3.48                  | 3.72  | 2.03     | 2.38                | 2.27  | 0.73     | 13.85                | 6.03  | 14.38    |

| 0.7  | 3.48                  | 3.63  | 2.28     | 2.20                | 2.39  | 0.82     | 11.88                | 5.92  | 12.38    |

| 0.8  | 3.42                  | 3.55  | 2.53     | 2.03                | 2.10  | 0.91     | 10.03                | 5.85  | 10.26    |

| 0.9  | 3.40                  | 3.50  | 2.81     | 1.85                | 1.86  | 0.98     | 8.25                 | 5.28  | 8.09     |

| 1.0  | 3.40                  | 3.48  | 3.03     | 1.64                | 1.64  | 1.14     | 6.37                 | 4.49  | 6.17     |

| 1.1  | 3.36                  | 3.48  | 3.19     | 1.46                | 1.49  | 1.27     | 4.71                 | 3.66  | 4.47     |

| 1.15 | 3.38                  | 3.39  | 3.37     | 1.39                | 1.28  | 1.29     | 4.05                 | 3.31  | 3.87     |

Fig. 19. The performance comparison of the proposed PWM scheme. The modulation index M=0.6. Ch1: Phase A line current (10 A/div), Ch2: Phase A circulating current ( $2 \times I_{A,c}$ ) (5 A/div), Ch3: CM circulating current ( $3 \times I_{CM}$ ) (5 A/div). (a) SVM, (b) DPWM1, (c) Proposed scheme.

Fig. 20. The performance comparison of the proposed PWM scheme. The modulation index M=1. (a) SVM: Ch1: Phase A line current (10 A/div), Ch2: Phase A circulating current ( $2 \times I_{A,c}$ ) (5 A/div), Ch3: CM circulating current ( $3 \times I_{CM}$ ) (5 A/div), (b) DPWM1, (c) Proposed scheme.

proportional to the flux linkage in the CI, it can be concluded that the maximum value of peak flux linkage in the CI over the full modulation range also remains constant. The use of SVM also results in more core losses in case of CI compared to the proposed PWM scheme, as the core is excited over the entire

fundamental cycle. The  $I_{CM}$  is proportional to the flux linkage in the CM inductor and the experimental results of  $I_{CM}$  are also obtained. For the SVM, the maximum value of the peak CM circulating current decreases with the increase in the modulation index, which is in agreement with the analytical

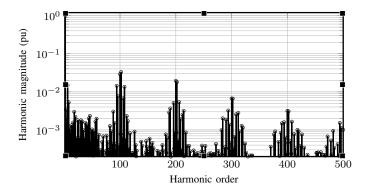

Fig. 21. Proposed scheme: Experimental line current harmonic spectrum for a modulation index of 1. The harmonic magnitude is normalized to the magnitude of the fundamental component.

result presented in Section IV and illustrated in Fig. 12. In the proposed scheme, the maximum value of the  $I_{CM}$  occurs at full modulation index, and it decreases with decrease in the modulation index. The maximum value of the peak CM current is 1.29 A at a modulation index of one in the proposed scheme, compared to 3.98 A at modulation index of 0.1 in case of the SVM and 2.39 A at a modulation index of 0.7 for DPWM1. Thus, for applications demanding the operation over the full modulation range, the use of the proposed PWM scheme results in size reduction of CM inductor.

The undesirable effect of larger duration of  $T_z$  at lower modulation indices can be reduced by the same zero vector alignment in the proposed scheme. In case of CI, the core is excited only for the one third period of the fundamental cycle, as evident from the waveform of the  $I_{A,c}$  in experimental results. If the design of CI is thermally limited, the reduced core losses result in more compact design. The harmonic analysis of the line current is shown in Fig. 21. The major harmonic components are pushed close to the double of the switching frequency by the interleaving effect.

#### VI. CONCLUSION

A PWM scheme to reduce the maximum value of the flux linkage and the core losses in the circulating current filter is presented in this paper. This PWM scheme uses the division of the active vectors within a half-carrier cycle to ensure simultaneous occurrence of the same zero vector in both of the VSCs. The effect of the proposed PWM scheme on the flux linkage and the core losses in the circulating current filter is analyzed. Both the maximum value of the flux linkage and the core losses are reduced substantially by the same zero vector alignment in the proposed PWM scheme. Thus, the size of the circulating current filter can be reduced. The switching losses are also analyzed for the proposed PWM scheme and compared with that of the SVM and 60° clamped DPWM. The proposed PWM scheme demonstrates superior efficiency for the reactive power compensation applications, as it is evident from the core losses and switching losses comparisons presented in this paper. However, for the applications, where the displacement power factor angle is in the vicinity of zero, the use of proposed method results in high switching losses. The line current ripple for the proposed scheme is also analyzed, which shows that the THD of the line current closely matches that of the SVM. The line current quality is superior in the case of the DPWM1, however the improvement is marginal at the higher modulation indices. The PWM scheme and the analysis presented in this paper are also supported by the experimental results.

#### REFERENCES

- M. Baumann and J. Kolar, "Parallel connection of two three-phase three-switch buck-type unity-power-factor rectifier systems with dc-link current balancing," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 3042– 3053, 2007.

- [2] Z. Xu, R. Li, H. Zhu, D. Xu, and C. Zhang, "Control of parallel multiple converters for direct-drive permanent-magnet wind power generation systems," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1259–1270, March 2012.

- [3] "Technical guidline: Generating plants connected to the medium-voltage network." BDEW Bundesverband der Energie- und Wasserwirtschaft e.V., [Online]. Available: http://www.bdew.de, 2008.

- [4] A. Rockhill, M. Liserre, R. Teodorescu, and P. Rodriguez, "Grid-filter design for a multimegawatt medium-voltage voltage-source inverter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1205–1217, 2011.

- [5] G. Narayanan, V. T. Ranganathan, D. Zhao, H. Krishnamurthy, and R. Ayyanar, "Space vector based hybrid pwm techniques for reduced current ripple," *IEEE Trans. Ind. Electron.*, vol. 55, no. 4, pp. 1614– 1627, 2008.

- [6] D. Casadei, G. Serra, A. Tani, and L. Zarri, "Theoretical and experimental analysis for the rms current ripple minimization in induction motor drives controlled by svm technique," *IEEE Trans. Ind. Electron.*, vol. 51, no. 5, pp. 1056–1065, Oct 2004.

- [7] M. Meco-Gutierrez, F. Perez-Hidalgo, F. Vargas-Merino, and J. R. Heredia-Larrubia, "A new pwm technique frequency regulated carrier for induction motors supply," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1750–1754, Oct 2006.

- [8] K. Taniguchi, M. Inoue, Y. Takeda, and S. Morimoto, "A pwm strategy for reducing torque-ripple in inverter-fed induction motor," *IEEE Trans. Ind. Appl.*, vol. 30, no. 1, pp. 71–77, Jan 1994.

- [9] J. Prasad and G. Narayanan, "Minimization of Grid Current Distortion in Parallel-Connected Converters Through Carrier Interleaving," *IEEE Trans. Ind. Electron.*, vol. 1, no. c, pp. 1–1, 2013.

- [10] S. Miller, T. Beechner, and J. Sun, "A comprehensive study of harmonic cancellation effects in interleaved three-phase vscs," in *Proc. IEEE Power Electronics Specialists Conference*, 2007. PESC 2007., 2007, pp. 29–35.

- [11] L. Asimmoaei, E. Aeloiza, J. Kim, P. Enjeti, F. Blaabjerg, L. Moran, and S. Sul, "An interleaved active power filter with reduced size of passive components," in *Proc. Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition*, 2006. APEC '06., 2006, pp. 1–7.

- [12] D. Zhang, F. Wang, R. Burgos, L. Rixin, and D. Boroyevich, "Impact of Interleaving on AC Passive Components of Paralleled Three-Phase Voltage-Source Converters," *IEEE Trans. Power Electron.*, vol. 46, no. 3, pp. 1042–1054, 2010.

- [13] T. Bhavsar and G. Narayanan, "Harmonic analysis of advanced busclamping pwm techniques," *IEEE Trans. Power Electron.*, vol. 24, no. 10, pp. 2347–2352, 2009.

- [14] X. Mao, A. Jain, and R. Ayyanar, "Hybrid interleaved space vector pwm for ripple reduction in modular converters," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1954–1967, 2011.

- [15] M. Abusara and S. Sharkh, "Design and control of a grid-connected interleaved inverter," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 748–764, Feb 2013.

- [16] K. Xing, F. Lee, D. Borojevic, Z. Ye, and S. Mazumder, "Interleaved pwm with discontinuous space-vector modulation," *IEEE Trans. Power Electron.*, vol. 14, no. 5, pp. 906–917, 1999.

- [17] D. G. Holmes and T. A. Lipo, Pulse Width Modulation for Power Converters: Principles and Practice. Hoboken, NJ: Wiley-IEEE Press, 2003.

- [18] A. Hava, R. Kerkman, and T. Lipo, "Simple analytical and graphical methods for carrier-based pwm-vsi drives," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 49–61, Jan 1999.

- [19] J. Kolar, H. Ertl, and F. C. Zach, "Influence of the modulation method on the conduction and switching losses of a pwm converter system," *IEEE Trans. Ind. Appl.*, vol. 27, no. 6, pp. 1063–1075, 1991.

- [20] G. Narayanan and V. T. Ranganathan, "Analytical evaluation of harmonic distortion in pwm ac drives using the notion of stator flux ripple," *IEEE Trans. Power Electron.*, vol. 20, no. 2, pp. 466–474, 2005.

- [21] G. Narayanan, H. Krishnamurthy, D. Zhao, and R. Ayyanar, "Advanced bus-clamping pwm techniquesbased on space vector approach," *IEEE Trans. Power Electron.*, vol. 21, no. 4, pp. 974–984, 2006.

- [22] H. Akagi, A. Nabae, and S. Atoh, "Control strategy of active power filters using multiple voltage-source pwm converters," *IEEE Trans. Ind. Appl.*, vol. IA-22, no. 3, pp. 460–465, 1986.

- [23] R. Hausmann and I. Barbi, "Three-phase multilevel bidirectional dc-ac converter using three-phase coupled inductors," in *Proc. IEEE Energy Conversion Congress and Exposition*, 2009. ECCE 2009., Sept 2009, pp. 2160–2167.

- [24] F. Forest, E. Laboure, T. Meynard, and V. Smet, "Design and comparison of inductors and intercell transformers for filtering of pwm inverter output," *IEEE Trans. Power Electron.*, vol. 24, no. 3, pp. 812–821, 2009.

- [25] B. Cougo, T. Meynard, and G. Gateau, "Parallel Three-Phase Inverters: Optimal PWM Method for Flux Reduction in Intercell Transformers," *IEEE Trans. Power Electron.*, vol. 26, no. 8, pp. 2184–2191, Aug. 2011.

- [26] B. Cougo, G. Gateau, T. Meynard, M. Bobrowska-Rafal, and M. Cousineau, "PD modulation scheme for three-phase parallel multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 690–700, 2012.

- [27] L. Asiminoaei, E. Aeloiza, P. N. Enjeti, and F. Blaabjerg, "Shunt active-power-filter topology based on parallel interleaved inverters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1175–1189, 2008.

- [28] J. Ewanchuk, S. Member, and J. Salmon, "Three-limb Coupled Inductor Operation for Voltage Sourced Inverters," *IEEETrans. on Ind. Electron.*, vol. 60, no. 5, pp. 1979–1988, 2013.

- [29] D. Zhang, F. Wang, R. Burgos, and D. Boroyevich, "Common-mode circulating current control of paralleled interleaved three-phase two-level voltage-source converters with discontinuous space-vector modulation," *IEEE Trans. Power Electron.*, vol. 26, no. 12, pp. 3925–3935, Dec 2011.

- [30] D. Zhang, F. Wang, R. Burgos, and D. Boroyvich, "Total flux minimization control for integrated inter-phase inductors in paralleled, interleaved three-phase two-level voltage-source converters with discontinuous space-vector modulation," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1679–1688, April 2012.

- [31] F. Luo, S. Wang, F. Wang, D. Boroyevich, N. Gazel, Y. Kang, and A. Baisden, "Analysis of cm volt-second influence on cm inductor saturation and design for input emi filters in three-phase dc-fed motor drive systems," *IEEE Trans. Power Electron.*, vol. 25, no. 7, pp. 1905– 1914, 2010.

- [32] V. Blasko and V. Kaura, "A novel control to actively damp resonance in input lc filter of a three-phase voltage source converter," *IEEE Trans. Ind. Appl.*, vol. 33, no. 2, pp. 542–550, Mar 1997.

- [33] A. Hava, R. Kerkman, and T. Lipo, "A high-performance generalized discontinuous pwm algorithm," *IEEE Trans. Ind. Appl.*, vol. 34, no. 5, pp. 1059–1071, 1998.

- [34] H. Krishnamurthy, G. Narayanan, R. Ayyanar, and V. T. Ranganathan, "Design of space vector-based hybrid pwm techniques for reduced current ripple," in *Proc. Eighteenth Annual IEEE Applied Power Electronics Conference and Exposition*, 2003. APEC '03., vol. 1, 2003, pp. 583–588.

- [35] A. C. Binojkumar, J. Prasad, and G. Narayanan, "Experimental investigation on the effect of advanced bus-clamping pulsewidth modulation on motor acoustic noise," *IEEE Trans. Ind. Electron.*, vol. 60, no. 2, pp. 433–439. Feb 2013.

- [36] K. Venkatachalam, C. Sullivan, T. Abdallah, and H. Tacca, "Accurate prediction of ferrite core loss with nonsinusoidal waveforms using only steinmetz parameters," in *Computers in Power Electronics*, 2002. Proceedings. 2002 IEEE Workshop on, 2002, pp. 36–41.

- [37] J. Li, T. Abdallah, and C. Sullivan, "Improved calculation of core loss with nonsinusoidal waveforms," in *Industry Applications Conference*, 2001. Thirty-Sixth IAS Annual Meeting. Conference Record of the 2001 IEEE, vol. 4, 2001, pp. 2203–2210 vol.4.

- [38] A. V. d. Bossche and V. C. Valchev, Inductors and Transformers for Power Electronics. Boca Raton, FL: CRC Press, 2004.

- [39] B. Cougo, T. Meynard, and G. Gateau, "Parallel three-phase inverters: Optimal pwm method for flux reduction in intercell transformers," *IEEE Trans. Power Electron.*, vol. 26, no. 8, pp. 2184–2191, Aug 2011.

Ghanshyamsinh Gohil (S'13) received the M.Tech. degree in electrical engineering with specialization in power electronics and power systems from the Indian Institute of Technology-Bombay, Mumbai, India. in 2011.

He is currently working towards the Ph.D. degree at the Department of Energy Technology, Aalborg University, Denmark. Prior to joining the Ph.D. studies, he was employed at Siemens Corporate Research, Bangalore. His research interests include parallel operation of voltage source convert-

ers, pulsewidth modulation techniques and the design of the inductive power components.

Ramkrishan Maheshwari (S'10-M'11) was born in Allahabad, India. He received the master of engineering (M.E.) degree in electrical engineering from the Indian Institute of Science (IISc), Bangalore, India in 2005 and the Ph.D. degree in electrical engineering from Aalborg University, Aalborg, Denmark in 2012.

From 2005 to 2008, he was with Honeywell Technology Solution Lab, Bangalore, India. He is currently working as an Assistant Professor with the Department of Energy Technology, Aalborg Univer-

sity, Denmark. His research interests include modeling and control of power converters.

Lorand Bede (S'11) was born in Romania in 1989. He received the engineering degree in electrical engineering from Sapientia Hungarian University of Transilvania, Trgu Mure, Romania, 2011,the MSc. degree in Power Electronics and Drives from Aalborg University, Aalborg, Denmark, in2013. Currently he is a PhD Fellow at the Department of Energy Technology, at Aalborg University, Aalborg. His research interest include grid connected applications based on parallel interleaved converters for wind turbine applications.

Tamas Kerekes (S'06-M'09) obtained his Electrical Engineer diploma in 2002 from Technical University of Cluj, Romania, with specialization in Electric Drives and Robots. In 2005, he graduated the Master of Science program at Aalborg University, Institute of Energy Technology in the field of Power Electronics and Drives. In Sep. 2009 he obtained the PhD degree from the Institute of Energy Technology, Aalborg University. The topic of the PhD program was: "Analysis and modeling of transformerless PV inverter systems". He is currently employed as an

Associate professor and is doing research at the same institute within the field of grid connected renewable applications. His research interest include grid connected applications based on DC-DC, DC-AC single- and three-phase converter topologies focusing also on switching and conduction loss modeling and minimization in case of Si and new wide-bandgap devices.

Remus Teodorescu (S'94-A'97-M'99-SM'02-F'12) received the Dipl.Ing. degree in electrical engineering from Polytechnical University of Bucharest, Romania in 1989, and PhD. degree in power electronics from University of Galati, Romania, in 1994. In 1998, he joined Aalborg University, Department of Energy Technology, power electronics section where he currently works as full professor. Since 2013 he is a visiting professor at Chalmers University. He has coauthored the book Grid Converters for Photovoltaic and Wind Power Systems, ISBN: 978-

0-470-05751-3, Wiley 2011 and over 200 IEEE journals and conference papers. His areas of interests includes: design and control of grid-connected converters for photovoltaic and wind power systems, HVDC/FACTS based on MMC, SiC-based converters, storage systems for utility based on Li-Ion battery technology. He was the coordinator of the Vestas Power Program 2008 2013.

Frede Blaabjerg (S'86-M'88-SM'97-F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he was a Ph.D. Student with Aalborg University, Aalborg, Denmark. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives.

He has received 15 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014 and the Villum Kann Rasmussen Research Award 2014. He was an Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011.

Marco Liserre (S'00-M'02-SM'07-F'13) received the MSc and PhD degree in Electrical Engineering from the Bari Polytechnic, respectively in 1998 and 2002. He has been Associate Professor at Bari Polytechnic and Professor in reliable power electronics at Aalborg University (Denmark). He is currently Full Professor and he holds the Chair of Power Electronics at Christian-Albrechts-University of Kiel (Germany). He has published 200 technical papers (56 of them in international peer-reviewed journals), 3 chapters of a book and a book (Grid Converters

for Photovoltaic and Wind Power Systems, ISBN-10: 0-470-05751-3 IEEE-Wiley, second reprint, also translated in Chinese). These works have received more than 9000 citations. Marco Liserre is listed in ISI Thomson report The worlds most influential scientific minds, 2014.

He has been recently awarded with an ERC Consolidator Grant for an overall budget of 2 MEuro for the project The Highly Efficient And Reliable smart Transformer (HEART), a new Heart for the Electric Distribution System.

He is member of IAS, PELS, PES and IES. He is Associate Editor of the IEEE Transactions on Industrial Electronics, IEEE Industrial Electronics Magazine, IEEE Transactions on Industrial Informatics, where he is currently Co-Eic, IEEE Transactions on power electronics and IEEE Journal of Emerging and Selected Topics in Power Electronics. He has been Founder and Editor-in-Chief of the IEEE Industrial Electronics Magazine, Founder and the Chairman of the Technical Committee on Renewable Energy Systems, Co-Chairman of the International Symposium on Industrial Electronics (ISIE 2010), IES Vice-President responsible of the publications. He has received the IES 2009 Early Career Award, the IES 2011 Anthony J. Hornfeck Service Award, the 2014 Dr. Bimal Bose Energy Systems Award, the 2011 Industrial Electronics Magazine best paper award and the Third Prize paper award by the Industrial Power Converter Committee at ECCE 2012, 2012. He is senior member of IES AdCom. In 2013 he has been elevated to the IEEE fellow grade with the following citation for contributions to grid connection of renewable energy systems and industrial drives.