# **Aalborg Universitet**

# Influences of Device and Circuit Mismatches on Paralleling Silicon Carbide MOSFETs

Li, Helong; Munk-Nielsen, Stig; Wang, Xiongfei; Maheshwari, Ram Krishan; Beczkowski, Szymon; Uhrenfeldt, Christian; Franke, Toke

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2015.2408054

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Li, H., Munk-Nielsen, S., Wang, X., Maheshwari, R. K., Beczkowski, S., Uhrenfeldt, C., & Franke, T. (2016). Influences of Device and Circuit Mismatches on Paralleling Silicon Carbide MOSFETs. *I E E Transactions on Power Electronics*, 31(1), 621 - 634. https://doi.org/10.1109/TPEL.2015.2408054

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

© 2015 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Digital Object Identifier (DOI): 10.1109/TPEL.2015.2408054

IEEE Transactions on Power Electronics, Vol. PP, No. 99, Early Access Article, Mar. 2015.

# Influences of Device and Circuit Mismatches on Paralleling Silicon Carbide MOSFETs

Helong Li Stig Munk-Nielsen Xiongfei Wang Ramkrishan Maheshwari Szymon Beczkowski Christian Uhrenfeldt Toke Franke

# **Suggested Citation**

H. Li, S. Munk-Nielsen, X. Wang, R. Maheshwari, S. Beczkowski, C. Uhrenfeldt, and T. Franke, "Influences of device and circuit mismatches on paralleling silicon carbide MOSFETS," *IEEE Trans. Power Electron.*, vol. PP, no. 99, Early Access Article, Mar. 2015.

# Influences of Device and Circuit Mismatches on Paralleling Silicon Carbide MOSFETs

Helong Li, Stig Munk-Nielsen, Xiongfei Wang, *Member*, *IEEE*, Ramkrishan Maheshwari, Szymon Bęczkowski, Christian Uhrenfeldt and Toke Franke

hel@et.aau.dk, smn@et.aau.dk, xwa@et.aau.dk, rkmahesh@ee.iitd.ac.in,sbe@et.aau.dk, chu@et.aau.dk, toke.franke@danfoss.com

Abstract-This paper addresses the influences of device and circuit mismatches on paralleling the Silicon Carbide (SiC) MOSFETs. Comprehensive theoretical analysis and experimental validation from paralleled discrete devices to paralleled dies in multichip power modules are first presented. Then, the influence of circuit mismatch on paralleling SiC MOSFETs is investigated and experimentally evaluated for the first time. It is found that the mismatch of the switching loop stray inductance can also lead to on-state current unbalance with inductive output current, in addition to the on-state resistance of the device. It further reveals that circuit mismatches and a current coupling among the paralleled dies exist in a SiC MOSFET multichip power module, which is critical for the transient current distribution in the power module. Thus, a power module layout with an auxiliary source connection is developed to reduce such a coupling effect. Lastly, simulations and experimental tests are carried out to validate the analysis and effectiveness of the developed layout.

Index Terms—DBC layout, parallel connection, power module, SiC MOSFET, WBG devices

#### I. INTRODUCTION

IC Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) have been undergoing a rapid development in recent years, thanks to its high breakdown voltage, fast switching speed, and good thermal conductivity [1]-[6]. Compared with Silicon (Si) Insulated Gate Bipolar Transistors (IGBTs), SiC MOSFETs have no tail current due to their unipolar structure and thus allowing reduced switching losses and higher switching frequency [5], [7]-[10]. However, the lower current rating of SiC MOSFETs often requires paralleled connection of discrete SiC MOSFETs [11]-[13] or using multichip power module [14]-[22].

For the paralleled operation of power semiconductor devices, current unbalance has always been an important concern, which may cause unequal conduction loss and switching loss [23], [24]. Moreover, besides the steady-state current unbalance, the unequal transient current distribution can further result in higher current overshoot in the device, which may be out of the Safety Operation Area (SOA). Consequently, the current capability of the multichip module tends to be derated [25].

There are generally two main causes of current unbalance in paralleled power semiconductor devices, which are the device mismatch and the asymmetrical circuit layout, i.e. the circuit mismatch. Among the device parameters of MOSFETs, the on-state resistance ( $R_{\rm on}$ ) and the gate threshold voltage ( $V_{\rm th}$ ) have more obvious effect on the current sharing performance in

parallel connection. The different  $R_{\rm on}$  leads to unequal steady-state current, while the different  $V_{\rm th}$  results in unbalanced transient current [26]. Asymmetrical circuit layout will result in unequal parasitic inductances, which are mainly switching loop stray inductance ( $L_{\rm d}$ ) and common source stay inductance ( $L_{\rm s}$ ).

To address the current unbalance, a number of research works are reported on paralleling SiC MOSFETs [11]-[13], [27], [28]. However, only the current unbalance caused by the device mismatch of discrete devices is discussed. The influence of the asymmetrical circuit layout is often overlooked, even though the effects of the circuit parasitic parameters on a single device have been well documented [29], [30]. In [12], a current balancing method based on active gate driver is developed for paralleling discrete devices. This scheme requires accurate current information, which is possible for the pulse currents, but it is challenging for the continuous current due to the limits of bandwidth, galvanic isolation, and physical size of current sensors. Furthermore, in a SiC MOSFET multichip module, it is also important to characterize the effect of circuit layout mismatch on the current distribution among the dies. The switching characteristic and thermal performance of SiC MOSFET modules have been discussed in [17], [20]-[22]. However, the current distribution among the paralleled dies has not been studied yet.

This paper, therefore, presents a systematic analysis of the influences of device and circuit mismatches on paralleling SiC MOSFETs. First, the main sources of device mismatches are discussed, with particular attentions to the material property and fabrication process of SiC MOSFETs. Influences of device mismatches are experimentally investigated regarding the device parameter  $R_{\rm on}$  and  $V_{\rm th}$ . Then, the mathematic analysis and experimental tests on the effects of asymmetrical circuit design with paralleled discrete devices are carried out. It is shown that the mismatch of the switching loop stray inductance may also lead to on-state current unbalance, besides the difference of  $R_{on}$ . This is followed by a detailed analysis of the current distribution in a full SiC MOSFET multichip power module. The circuit mismatch of the Directed Bonded Circuit (DBC) layout and a current coupling effect among the paralleled dies are both found for the first time, which are shown to have a significant influence on the transient current distribution among the dies based on the theoretical analysis. A DBC layout with auxiliary source connection is then developed to mitigate such a current coupling effect, and is validated through simulations and experimental results.

#### II. DEVICE MISMATCH

#### A. Device Mismatch Description

Define Among the device parameters of SiC MOSFETs, the on-state resistance and the threshold voltage are two most critical parameters that affect the current sharing performance in parallel connection.  $R_{\rm on}$  determines the on-state current distribution among the devices, whereas  $V_{\rm th}$  influences the sharing of transient current.

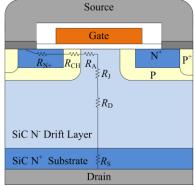

Fig. 1 shows a cross-section schematic of a unit cell for the planar SiC MOSFET [31], which is similar to that of Si MOSFET [32]. Compared to Si MOSFETs, SiC MOSFETs have a lower drift region resistance ( $R_{\rm D}$ ), but a higher channel resistance ( $R_{\rm CH}$ ), due to its lower carrier mobility [31] and a higher level of the channel defect density, which also contributes to the overall on-resistance. At the low Gate-Source voltages ( $V_{\rm GS}$ <13V),  $R_{\rm CH}$  dominates the total  $R_{\rm on}$ , which has a negative temperature coefficient. Hence, it is always recommended to turn on SiC MOSFETs with  $V_{\rm GS}$  higher than 18V [31], [33]. Otherwise, paralleling SiC MOSFETs does not have a self-balancing capability and there is a risk of thermal run away.

Fig. 1. A cross-section schematic of unit cell for the planar SiC MOSFET.

From semiconductor physics, it is known that the threshold voltage  $V_{th}$  of the MOS structure is affected by non-idealities, which can lead to shifts in the threshold voltage during long term of cycling. Such non-idealities can be oxide trap states that contain fixed charges or interface states, which are imperfections at the atomic level at the boundary between the oxide and the SiC [34]. Moreover, the material processes of SiC are not as mature as Si, the manufacturing process and the interface quality remains a material issue [35], [36], although this is being addressed by improving material processing, like nitridation of the gate oxide [37]-[40]. As a consequence, slight synthesis variations in the processing may lead to process related variations in the interface and oxide quality, with a variation in threshold voltage as a result[40]. Therefore, SiC MOSFETs are more likely to operate with  $V_{th}$  mismatch, especially after long term of cycling.

#### B. Device Parameters Test and Hardware Setup

To demonstrate the effect of device mismatch, 8 SiC MOSFETs (C2M0160120D) from Cree are tested in the lab. They are denoted as  $M_1$ - $M_8$ .  $R_{\rm on}$  and  $V_{\rm th}$  variations of these devices are plotted in Fig. 2. The procedure of measuring  $R_{\rm on}$  variation is summarized as the following. First, the gate source voltage is kept constant at 20V. The drain and the source terminals are connected to a power supply, which operates in

the current source mode and is adjusted from 0 to 10A. The MOSFETs are mounted on a heatsink with fan cooling. Then, the drain source voltage ( $V_{\rm DS}$ ) is measured after  $V_{\rm DS}$  becomes stable. Even though there is self-heating effect during the testing procedure, the  $R_{\rm on}$  variation of the MOSFETs can still be demonstrated under the almost identical testing condition.

Fig. 2. MOSFETs parameters variation

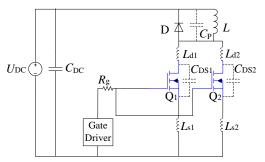

(a) Double Pulse Test Circuit

(b) Hardware prototype

Fig. 3. Double pulse test circuit and hardware prototype

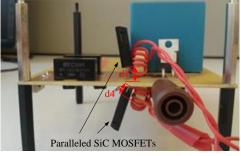

The current sharing of paralleling SiC MOSFETs is evaluated with a double pulse test circuit, as shown in Fig. 3(a). The hardware implementation is shown in Fig. 3(b). In the simulation and experimental study in this paper, the gate source voltage bias is 25V and -5V unless otherwise specified. Since the device mismatch is of the main concern in this test, two SiC MOSFETs are paralleled in a flipped way, as shown in Fig.3(b),

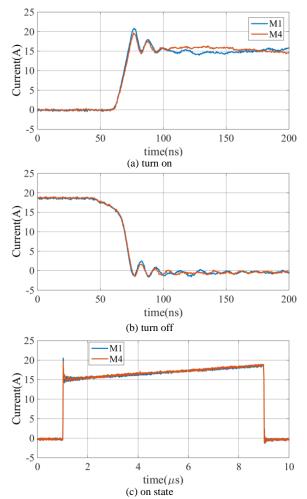

Fig. 4. Current sharing performance of  $M_1$  and  $M_4$  with little mismatch in order to reduce the influence of circuit mismatch. The MOSFET drain current is measured with a two stage current measurement method, which includes a 10 turns current transformer at the first stage and a Pearson Current Monitor 2877 in the second stage [41].

# C. Influences of On-Resistance Mismatch

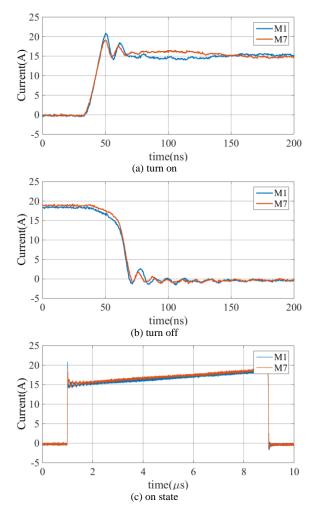

SiC MOSFETs  $M_1$  and  $M_7$  are used for the study of  $R_{\rm on}$  mismatch influence, as they have nearly same  $V_{\rm th}$  but different  $R_{\rm on}$ ,  $M_1$  has a higher  $R_{\rm on}$  than  $M_7$ . As shown in Fig. 5(a), during turn-on transient,  $M_1$  and  $M_7$  have identical current. After the turn-on,  $M_1$  has lower current than  $M_7$ .  $M_1$  has lower on-state current because of its higher  $R_{\rm on}$ , as shown in Fig. 5(c). It is confirmed that the  $R_{\rm on}$  mismatch has an impact on on-state current sharing performance but little influence on transient current sharing.

### D. Influences of Threshold Voltage Mismatch

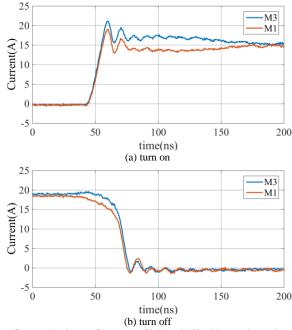

$M_1$  and  $M_3$  are selected for the study of  $V_{th}$  mismatch influence, as they have nearly identical  $R_{on}$  but different  $V_{th}$ ,  $M_1$  has a higher  $V_{th}$  than  $M_3$ . The switching transient current sharing with the mismatched  $V_{th}$  is given in Fig. 6.

$M_3$  turns on faster yet turns off slower than  $M_1$ . During turn-on,  $v_{GS}$  first reach  $V_{th}$  of  $M_3$ , and then  $M_3$  starts to turn-on and  $i_{D3}$  starts rising. When  $v_{GS}$  continue increasing and reaches  $V_{th}$  of  $M_1$ ,  $M_1$  turns on and  $i_{D1}$  starts rising. However, during turn-off, the process is slightly different. The minimum gate

Fig. 5. Current sharing performance of  $M_1$  and  $M_7$  with  $R_{on}$  mismatch

Fig. 6. Current sharing performance of M1 and M3 with  $V_{\rm th}$  mismatch source voltage maintaining the specific drain current is defined as  $V_{\rm p}$ . If the reduced  $v_{\rm GS}$  is still larger than  $V_{\rm p}$ , the drain current will not fall and the channel resistance of the SiC MOSFET will increases. Only if  $v_{\rm GS}$  keeps decreasing to be lower than  $V_{\rm p}$ , the

SiC MOSFET will start to work in the saturation region, and the drain current will be determined by  $v_{GS}$ .  $v_{GS}$  first decreases to the point  $V_{P1}$ , at which  $M_1$  cannot sustain its drain current.  $i_{D1}$  starts to decrease.  $v_{GS}$  continues falling to the point  $V_{P3}$ , at which  $M_3$  can no longer sustain  $i_{D3}$ , and then  $i_{D3}$  starts decreasing. Since the drain current  $i_{D}$  is determined by  $v_{GS}$  in the saturation region, as (1).

$$i_D = g_{fs}(v_{GS} - V_{th}) \tag{1}$$

$V_{\rm th1} > V_{\rm th3}$ , trans-conductance of these two SiC MOSFET  $g_{\rm fs1} = g_{\rm fs3}$  and on-state current  $i_{\rm D1} = i_{\rm D3}$  before turning off,  $V_{\rm P1} > V_{\rm P3}$ . As  $i_{\rm D1}$  first decreases but the load inductor current  $i_{\rm L}$  keeps unchanged and the diode is not conducted,  $M_3$  needs to handle more current. Therefore, during turn-off,  $i_{\rm D3}$  first increases small amplitude before it starts decreasing, as shown in Fig. 6(b).

#### III. CIRCUIT MISMATCH

#### A. Circuit Mismatch Description

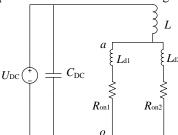

The difference in switching loop stray inductance  $(L_d)$  and common source stray inductance (Ls) are the main causes of current unbalance due to circuit mismatch, as shown in Fig. 3(a).  $L_{d1}$  and  $L_{d2}$  represent switching loop stray inductance.  $L_{s1}$ and  $L_{\rm s2}$  are the common source stray inductances.  $C_{\rm P}$  is the total capacitance of the diode junction capacitor and the parasitic paralleled capacitor of load inductor.  $C_{DS1}$  and  $C_{DS2}$  are junction capacitance of  $Q_1$  and  $Q_2$ . The switching loop stray inductance includes the equivalent-series-inductor (ESL) of the dc-link capacitors, the stray inductance of the power connection, including PCB trace and partial inductance from the package of power devices. The common source stray inductance is mainly from the package of SiC MOSFETs and PCB trace which is both in the gate-source loop and drain-source loop. The mismatch of  $L_d$  and  $L_s$  can easily be increased in the case of paralleling more than two SiC MOSFETs, where an ideally symmetric layout is difficult to achieve, especially when a large heat sink is needed.

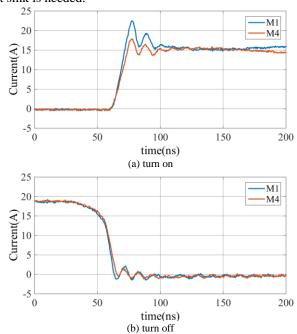

Fig. 7. Current sharing performance with d1=6mm and d4=10mm

In the study of circuit mismatch influence,  $M_1$  and  $M_4$  are selected as they have little device parameter mismatch. The  $L_s$  mismatch is realized by different effective source pin length, as shown in Fig.3 (b).  $d_1$  and  $d_4$  are the effective source pin length for  $M_1$  and  $M_4$ .  $L_d$  mismatch is by inserting different small air core inductors in the drain connection.

# B. Influences of Common Source Stray Inductance Mismatch

$L_{\rm s}$  influences the switching characteristics by its negative feedback effect on  $v_{\rm GS}$ , which can be explained with (2)-(3) during saturation region in transient switching time. In this condition, SiC MOSFET source current  $i_{\rm s}$  is considered identical with drain  $i_{\rm D}$ , because gate source current is much smaller than the  $i_{\rm D}$ .

$$v_{\rm GS} = V_{\rm driver} - i_{\rm G} R_{\rm G} - L_{\rm s} \frac{\mathrm{d}i_{\rm s}}{\mathrm{d}t} \tag{2}$$

$$i_{\rm D1} - i_{\rm D2} = g_{\rm fs} (L_{\rm s2} - L_{\rm s1}) \frac{\mathrm{d}i_{\rm L}}{2\mathrm{d}t}$$

(3)

According to (2) and (3), during turn-on transient, SiC MOSFET with larger  $L_s$  turns on slower and takes less current compared to the one with smaller  $L_s$ . During turn-off transient, the SiC MOSFET with larger  $L_s$  turns off slower but has more current.

Fig. 7 and Fig. 8 show the  $L_s$  mismatch influence on the current sharing performance of paralleled SiC MOSFETs. The  $L_s$  mismatch is adjusted by changing the effective source pin lengths, which are specified as  $d_1$  and  $d_4$  in Fig.2 (b).  $d_1$  and  $d_4$  are the source pin length connected to the power loop, i.e. the distance from the PCB trace to the end of the source pin, which can be readily adjusted by lifting the MOSFET up and down with different distances. With  $L_s$  mismatch increased, the current unbalance during switching transient also increases. For the SiC MOSFET with larger  $L_s$ , both the processes of turn-on and turn-off become slower. The current overshoot of the SiC MOSFET with smaller  $L_s$  increases with the increase of  $L_s$  mismatch. The current unbalance leads to uneven turn-on and turn-off losses during switching transient.

Fig. 8. Current sharing performance with d1=6mm and d4=16mm

The current overshoot and switching loss analysis are shown in Fig. 9 for different values of  $(d_4-d_1)$ .  $E_{on}$  and  $E_{off}$  are SiC MOSFET turn-on loss and turn-off losses. It can be seen from Fig. 9(a) that the current overshoot of the SiC MOSFET increases with the increase of  $L_s$  mismatch. On the other hand,  $L_s$  mismatch has little effect on the on-state current sharing performance since it affects the current sharing performance through  $v_{GS}$ .

$\begin{tabular}{ll} (b) switching losses analysis \\ Fig. 9. Current overshoot analysis and switching losses analysis with Ls \\ mismatch \end{tabular}$

## C. Influences of Switching Loop Stray Inductance Mismatch

The capacitor  $C_P$  shown in Fig.3 (a) could lead to a current overshoot during turn-on transient.  $L_d$  and  $C_P$  form a resonant circuit and causes oscillations in a short period after turn-on. The oscillation frequency could be determined as (4). For the oscillation,  $R_{on}$  of SiC MOSFET in series with the equivalent series resistance (ESR) of the dc-link capacitors ( $R_C$ ) acts as the damping resistor and the damping factor  $\xi$  is given by (5).

$$f = \frac{1}{2\pi\sqrt{L_{\rm d}C_{\rm P}}}\tag{4}$$

$$\xi = \frac{(R_{\rm on} + R_{\rm C})}{2} \sqrt{\frac{C_{\rm P}}{L_{\rm d}}}$$

(5)

$$f = \frac{1}{2\pi\sqrt{L_{\rm d}C_{\rm DS}}}\tag{6}$$

$$\xi = \frac{(R_{\rm d} + R_{\rm C})}{2} \sqrt{\frac{C_{\rm P}}{L_{\rm d}}} \tag{7}$$

During turn-off, there is a current charging the drain-source capacitor ( $C_{DS}$ ) of SiC MOSFET. In a short period after turn-off,  $L_d$  and  $C_{DS}$  form a resonant circuit and the oscillation frequency could be determined as (6). Damping resistor for this oscillation is ESR of DC capacitors and the ESR of diode ( $R_d$ ). Damping factor  $\xi$  is as (7).

With the above analysis,  $L_{\rm d}$  has an influence on the current in a short period after turn-on and turn-off. SiC MOSFET with larger  $L_{\rm d}$  has smaller oscillation frequency and smaller damping factor after turn-on and turn-off. As a result, the SiC MOSFET

with larger  $L_d$  has a larger current overshoot and the current oscillation amplitude after turn-off is also larger.

Fig. 10. On-State equivalent circuit of paralleling two SiC MOSFETs

Besides  $L_{\rm d}$  mismatch influences on the transient period current sharing performance, mismatch of  $L_{\rm d}$  also has an impact on the on-state current distribution. During on-state, there are cases that the SiC MOSFETs see an inductive load current and  $i_{\rm D}$  has a changing slope. During on-state period, the equivalent power circuit is shown as Fig. 10. The drain current can be described with (8). In condition of  $R_{\rm on1}=R_{\rm on2}$  and  $di_{\rm D1}/dt=di_{\rm D2}/dt$  (determined by load), the current difference of  $i_{\rm D1}$  and  $i_{\rm D2}$  can be determined as (9), which means different  $L_{\rm d}$  lead to different on-state current. Larger  $L_{\rm d}$  results smaller on-state current.

$$\begin{cases} i_{D1} + i_{D2} = i_{L} \\ L \frac{di_{L}}{dt} + u_{ao} = U_{DC} \\ L_{1} \frac{di_{D1}}{dt} + R_{on1}i_{D1} = L_{2} \frac{di_{D2}}{dt} + R_{on2}i_{D2} \end{cases}$$

$$i_{D1} - i_{D2} \approx \frac{L_{d2} - L_{d1}}{2R_{on}} \frac{U_{DC}}{L}$$

$$(9)$$

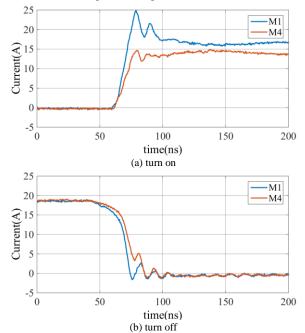

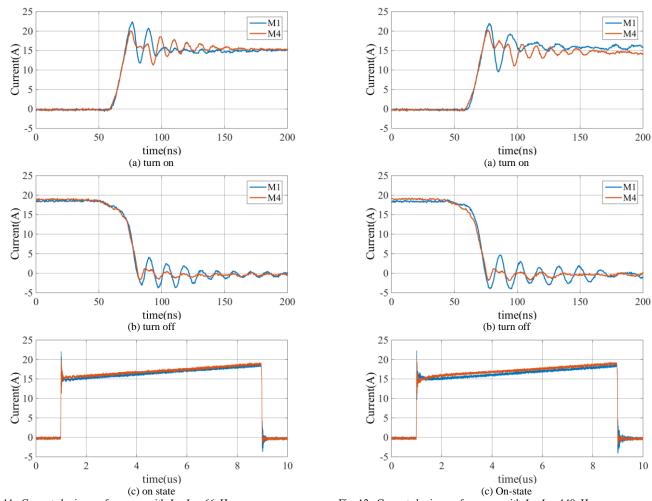

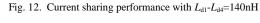

The experiment of  $L_{\rm d}$  mismatch influence is realized by inserting a small inductors in the drain of SiC MOSFET  $M_1$ . The experiment results are shown in Fig. 11 and Fig. 12. With the increase of  $L_{\rm d}$ , the current oscillation frequency decreases but the oscillation amplitude increases. With the increases of  $L_{\rm d}$  mismatch, on-state current unbalance increases.

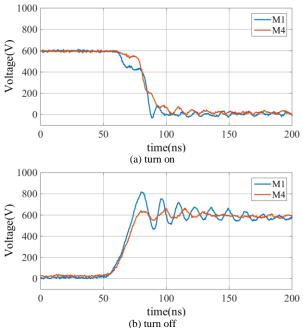

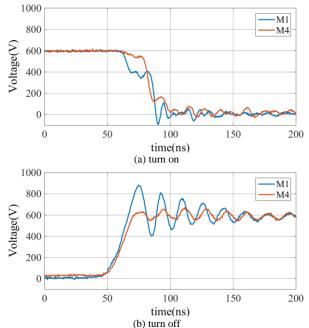

Besides the influence on current,  $L_{\rm d}$  has a large impact on the drain source voltage ( $V_{\rm DS}$ ) during switching transient. The effect of  $L_{\rm d}$  on a single MOSFET  $V_{\rm DS}$  has been analyzed in [29], [30]. The conclusion is with the larger  $L_{\rm d}$ ,  $V_{\rm DS}$  has larger voltage dip during turn-on and higher voltage overshoot during turn-off, which results a smaller turn-on loss but larger turn-off loss. For the paralleled connection, the experiment results of  $V_{\rm DS1}$  and  $V_{\rm DS4}$  are given in Fig. 13 and Fig. 14.  $V_{\rm DS}$  overshoot and switching losses analysis with  $L_{\rm d}$  mismatch are summarized as Fig. 15.

# IV. CURRENT DISTRIBUTION IN SIC MOSFET MULTICHIP POWER MODULES

# A. DBC Layout Mismatch in Multichip Power Modules

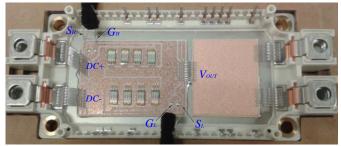

To describe the influence of the DBC layout mismatch on the current distribution among the paralleled dies, a SiC MOSFETs multichip power module is considered. Fig. 16 shows the half-bridge SiC power module, which is consisted with 8 SiC MOSFETs dies and 4 of them are in parallel. This power module is made by Danfoss and dedicated for testing the DBC for high current modules.

Fig. 11. Current sharing performance with  $L_{\rm d1}$ - $L_{\rm d4}$ =66nH

Fig. 13. Drain-Source voltage of M1 and M4 with  $L_{\rm d1}$ - $L_{\rm d4}$ =66nH

Fig. 14. Drain-Source voltage of M1 and M4 with  $L_{d1}$ - $L_{d4}$ =140nH

Fig. 15 Drain-source voltage overshoot analysis and switching losses analysis

Fig. 16. Half-bridge SiC MOSFET power module from Danfoss

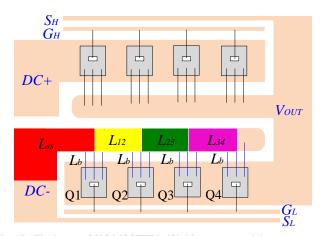

Fig. 17. The layout of SiC MOSFET half bridge power module

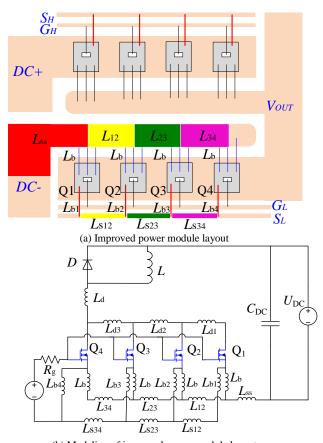

Fig. 17shows the layout of the power module with the stray inductance indicated in different colors. The layout of this power module is designed to minimize mismatch of  $L_{\rm d}$  for the paralleled four SiC MOSFETs dies,  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$ . However, the common source stray inductance  $L_{\rm s}$  of each die is significantly different from each other. In Fig. 17,  $L_{\rm b}$  is the stray inductance of the source connection bond-wire (blue) for each die.  $L_{\rm ss}$  is the stray inductance of the DBC trace (red) from  $Q_1$  to DC negative.  $L_{12}$ ,  $L_{23}$  and  $L_{34}$  are the stray inductance of the

DBC trace between  $Q_1$  and  $Q_2$  (yellow),  $Q_2$  and  $Q_3$  (green),  $Q_3$  and  $Q_4$  (purple), respectively. According to Fig. 17, the common source stray inductance ( $L_{s1}$ ,  $L_{s2}$ ,  $L_{s3}$  and  $L_{s4}$ ) for each SiC MOSFET die can be determined as (10). It is clear that all the four paralleled SiC MOSFET dies have different common source stray inductances.

$$\begin{cases} L_{s1} = L_{ss} + L_b \\ L_{s2} = L_{ss} + L_{12} + L_b \\ L_{s3} = L_{ss} + L_{12} + L_{23} + L_b \\ L_{s4} = L_{ss} + L_{12} + L_{23} + L_{34} + L_b \end{cases}$$

(10)

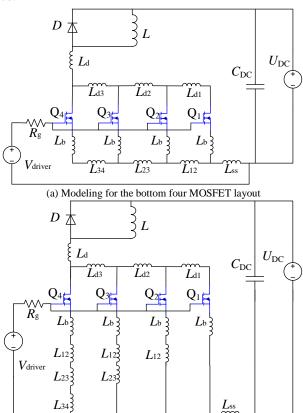

B. Influences of DBC Layout Mismatch and Current Coupling Effect

(b) Artificial DBC layout modeling without current coupling effect Fig. 18. DBC layout modeling

Besides the mismatch of the common source stray inductance, the paralleled SiC MOSFET dies has current coupling effect between each other, which means the gate source voltage of one SiC MOSFET is affected by the slope of the source current of other three SiC MOSFETs.

$$\begin{bmatrix} i_{\rm D1} \\ i_{\rm D2} \\ i_{\rm D3} \\ i_{\rm D4} \end{bmatrix} = g_{\rm fs} \begin{bmatrix} V_{\rm driver} - i_{\rm G} R_{\rm G} - V_{\rm th} - \triangle V_{\rm LS1} \\ V_{\rm driver} - i_{\rm G} R_{\rm G} - V_{\rm th} - \triangle V_{\rm LS2} \\ V_{\rm driver} - i_{\rm G} R_{\rm G} - V_{\rm th} - \triangle V_{\rm LS3} \\ V_{\rm driver} - i_{\rm G} R_{\rm G} - V_{\rm th} - \triangle V_{\rm LS4} \end{bmatrix}$$

$$(11)$$

The modeling of the power module layout is shown in Fig. 18(a). To describe the current coupling effect, the modeling of an artificial layout is made as shown in Fig. 18(b), which has identical  $L_{\rm s}$  mismatch with Fig. 18(a) but no current coupling effect. For both two modeling, in saturation region during

transient time, the current can be determined as (11).  $\Delta V_{\rm LS1}$ ,  $\Delta V_{\rm LS2}$ ,  $\Delta V_{\rm LS3}$  and  $\Delta V_{\rm LS4}$  are the voltage drop of the common source stray inductance  $L_{\rm s1}$ ,  $L_{\rm s2}$ ,  $L_{\rm s3}$  and  $L_{\rm s4}$ .

For the modeling in Fig. 18(a),  $\Delta V_{\rm LS1}$ ,  $\Delta V_{\rm LS2}$ ,  $\Delta V_{\rm LS3}$  and  $\Delta V_{\rm LS4}$  are determined as (12) and the current unbalances between the paralleled dies are as (13). On the other hand, for the modeling of Fig. 18(b) without the current coupling effect,  $\Delta V_{\rm LS1}$ ,  $\Delta V_{\rm LS2}$ ,  $\Delta V_{\rm LS3}$  and  $\Delta V_{\rm LS4}$  are determined as (14) and the current unbalances among the paralleled dies are as (15).

In (13) and (15), in high current multichip modules, the current differences slope, e.g.  $d(i_{D1}-i_{D2})/dt$ ,  $d(i_{D2}-i_{D3})/dt$ , and  $d(i_{D3}-i_{D4})/dt$ , are much smaller than the sum of drain currents slope, e.g.  $d(i_{D2}+i_{D3}+i_{D4})/dt$ ,  $d(i_{D3}+i_{D4})/dt$ , and  $di_{D4}/dt$ .

Consequently, the bond-wire inductance  $L_b$  effect in (13) and (15) could be ignored for the current unbalance analysis.

During turn-on transient, the MOSFET drain currents increases. According to (13) and (15), for both these two modeling, the MOSFETs drain currents should follow  $i_{\rm D1} > i_{\rm D2} > i_{\rm D3} > i_{\rm D4}$ . During turn-off transient, the MOSFET current decreases. The MOSFETs drain current should follow  $i_{\rm D1} < i_{\rm D2} < i_{\rm D3} < i_{\rm D4}$ . Therefore, in both cases, there are current unbalances during transient switching period. However, compared to that of (15), it is obvious that with the current coupling effect, the current unbalance is larger in (13).

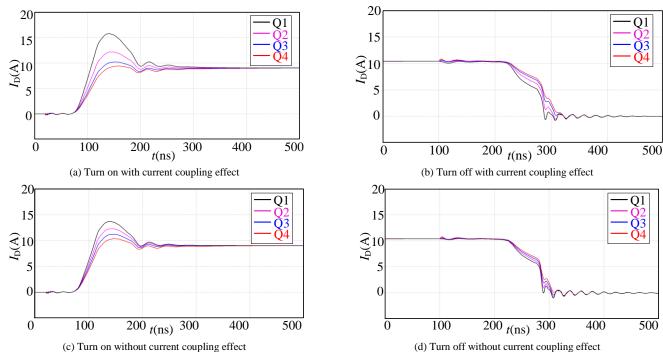

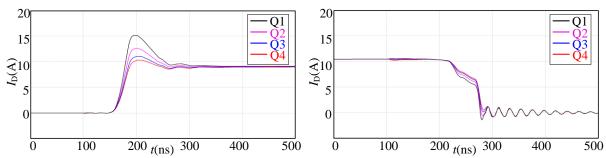

To validate the analysis, simulations of different models in Fig. 18(a) and Fig. 18(b) are made with LTspice. The simulation results can be compared in Fig. 19. With the current coupling effect, the drain current has a larger current overshoot and the current unbalance is also larger. It is clear that the coupling effect worsens the current sharing performance.

$$\begin{bmatrix} \triangle V_{\text{LS1}} \\ \triangle V_{\text{LS2}} \\ \triangle V_{\text{LS3}} \\ \triangle V_{\text{LS4}} \end{bmatrix} = \begin{bmatrix} L_{\text{b}} + L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{b}} + L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} & L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{12} & L_{\text{ss}} + L_{12} + L_{23} & L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} + L_{\text{ss}} \\ L_{$$

$$\begin{bmatrix}

i_{D1} - i_{D2} = g_{fs} \left[ L_b \frac{d(i_{D2} - i_{D1})}{dt} + L_{12} \frac{d(i_{D2} + i_{D3} + i_{D4})}{dt} \right] \\

i_{D2} - i_{D3} = g_{fs} \left[ L_b \frac{d(i_{D3} - i_{D2})}{dt} + L_{23} \frac{d(i_{D3} + i_{D4})}{dt} \right] \\

i_{D3} - i_{D4} = g_{fs} \left[ L_b \frac{d(i_{D4} - i_{D3})}{dt} + L_{34} \frac{di_{D4}}{dt} \right] \\

i_{D1} - i_{D4} = g_{fs} \left[ L_b \frac{d(i_{D4} - i_{D3})}{dt} + L_{12} \frac{d(i_{D2} + i_{D3} + i_{D4})}{dt} + L_{23} \frac{d(i_{D3} + i_{D4})}{dt} + L_{34} \frac{di_{D4}}{dt} \right]

\end{cases}$$

(13)

$$\begin{bmatrix} \triangle V_{\text{LS1}} \\ \triangle V_{\text{LS2}} \\ \triangle V_{\text{LS3}} \\ \triangle V_{\text{LS4}} \end{bmatrix} = \begin{bmatrix} L_{\text{b}} + L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{b}} + L_{\text{ss}} + L_{12} & L_{\text{ss}} & L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} & L_{\text{ss}} \\ L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} \\ L_{\text{ss}} & L_{\text{ss}} & L_{\text{ss}} & L_{\text{b}} + L_{\text{ss}} + L_{12} + L_{23} + L_{34} \end{bmatrix} \begin{bmatrix} i_{\text{D1}} \\ i_{\text{D2}} \\ i_{\text{D3}} \\ i_{\text{D4}} \end{bmatrix}$$

$$(14)$$

$$\begin{cases} i_{D1} - i_{D2} = g_{fs} (\Delta V_{LS2} - \Delta V_{LS1}) = g_{fs} \left[ L_{b} \frac{d(i_{D2} - i_{D1})}{dt} + L_{12} \frac{di_{D2}}{dt} \right] \\ i_{D2} - i_{D3} = g_{fs} (\Delta V_{LS3} - \Delta V_{LS2}) = g_{fs} \left[ L_{b} \frac{d(i_{D3} - i_{D2})}{dt} + L_{23} \frac{di_{D3}}{dt} \right] \\ i_{D3} - i_{D4} = g_{fs} (\Delta V_{LS4} - \Delta V_{LS3}) = g_{fs} \left[ L_{b} \frac{d(i_{D4} - i_{D3})}{dt} + L_{34} \frac{di_{D4}}{dt} \right] \\ i_{D1} - i_{D4} = g_{fs} (\Delta V_{LS4} - \Delta V_{LS1}) = g_{fs} \left[ L_{b} \frac{d(i_{D4} - i_{D1})}{dt} + (L_{12} + L_{23} + L_{34}) \frac{di_{D4}}{dt} \right] \end{cases}$$

$$(15)$$

$$i_{D1} - i_{D2} = g_{fs} \left[ (L_b + L_{12}) \frac{di_{D2}}{dt} - L_b \frac{di_{D1}}{dt} \right]$$

(16)

$$i_{D1} - i_{D2} = g_{fs} \frac{2L_{b1} + L_{s12}}{2L_{b1} + L_{b2} + 2L_{b1} + L_{b2}} [(L_b + L_{12}) \frac{di_{D2}}{dt} - L_b \frac{di_{D1}}{dt}]$$

(17)

Fig. 19. LTspice simulation results comparison with and without current coupling effect

#### C. Improved Layout of SiC MOSFET Power Module

The difference of modeling in Fig. 18 (a) and Fig. 18(b) is the current coupling effect among the paralleled dies. However, a layout corresponding to the model of Fig. 18(b) does not exist in the real power modules.

(b) Modeling of improved power module layout Fig. 20. Improved power module layout and modeling

To reduce the current coupling effect and mitigate the transient current unbalance in the SiC MOSFET power module, a slight modification is introduced based on this layout. An auxiliary source bond-wire for the gate driver source path is added. The new layout is shown in Fig. 20(a). The modeling of the new layout is shown as Fig. 20(b).

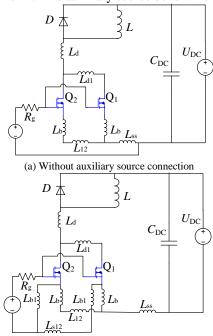

To analyze the modeling in Fig. 20(b) and the current distribution with the auxiliary source bond-wire, it is reasonable to simplify the model to paralleling two SiC MOSFETs, as shown in Fig. 21. Fig. 21(a) shows the modeling of paralleling two SiC MOSFETs without the auxiliary source bond-wire. Fig. 21(b) shows the modeling of paralleling two SiC MOSFETs with the auxiliary source bond-wire.

(b) With auxiliary source connection Fig. 21. Modeling of paralleling two SiC MOSFETs

The current unbalance of the paralleled SiC MOSFETs in Fig 21(a) and Fig. 21 (b) can be described as (16) and (17). With (16) and (17), it is clear that the current unbalance of the paralleled two SiC MOSFETs with the auxiliary source is reduced by a factor of  $(2L_{b1}+L_{s12})/(2L_{b1}+L_{s12}+2L_b+L_{12})$ . In the case of paralleling more than 2 SiC MOSFETs, the current unbalance can be mitigated even more because the current coupling effect increases with the number of paralleled dies.

The LTspice simulation results of the modeling in Fig. 18(a) are shown in Fig. 22. The simulation results of modeling in Fig. 20(b) with the auxiliary source bond-wire are shown in Fig. 23

and Fig. 24. Compared Fig. 22 and Fig. 23, with the auxiliary source bond-wire, the four paralleled MOSFETs turn on and turn off faster. Meanwhile, the drain current unbalance of the four paralleled MOSFETs is also reduced. To make the comparison fairly, the gate resistance of the simulation of Fig. 24 is increased to make the current rising time  $(t_r)$  similarly with that in Fig. 22. In this case, during turn-on, the drain current unbalance of  $Q_1$  and  $Q_4$  is reduced from 7A to 3.5A. The current overshoot of  $Q_1$  is reduced from almost 100% to less than 50%.During turn-off, the current delay among the paralleled dies are reduced.

Fig. 22. Current sharing performance without the auxiliary source connection ( $R_g$ =10 $\Omega$ , tr=60ns)

Fig. 23. Current sharing performance with the auxiliary source connection ( $R_g$ =10 $\Omega$ , tr=30ns)

Fig. 24. Current sharing performance with the auxiliary source connection ( $R_g$ =23 $\Omega$ , tr=60ns)

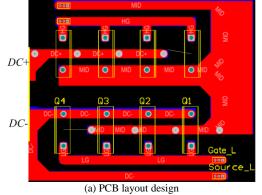

Fig. 25. PCB layout and double pulst test PCB circuit

(b) Hardware prototype

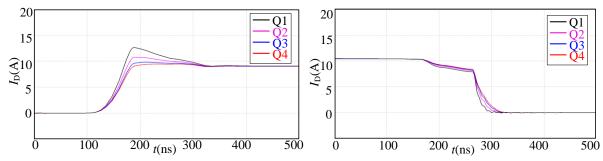

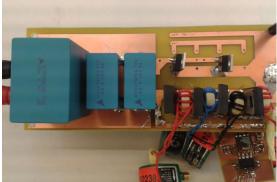

#### D. Experimental Study

The current measurement of dies in the power module is difficult. To experimentally evaluate the current sharing performance in the power module, a PCB circuit with similar layout of the power module is designed as Fig. 25 (a). The hardware setup is shown in Fig. 25 (b).

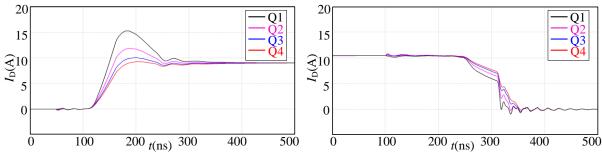

Fig. 26 shows the experimental results corresponding to the layout of Fig. 18(a), which is without the auxiliary source bond-wire. The largest current unbalance between paralleled SiC MOSFETs is more than 15A while the on state current is only around 10A. Q1 turns on and turns off fastest and takes highest current during turn-on. The current overshoot of  $Q_1$  is larger than 200%, even though the total turn-on current has only around 30% overshoot, which means Q1 may be working out of SOA although the total module current is operating within SOA of the power module. This phenomenon may easily lead to device failure.

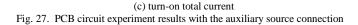

Fig. 27 shows the experimental results corresponding to the layout of Fig. 20(b), which is with the auxiliary source connection. Compared with the experiment results in Fig. 26, the 4 paralleled SiC MOSFETs have a better current sharing performance. The largest drain current overshoot is reduced from 22A to 18A. The current turn-on and turn-off delay between each SiC MOSFET is much smaller, which could mitigate the switching losses unbalance. Moreover, the total current of these 4 SiC MOSFETs turn on and turn off faster.

Fig. 26. PCB circuit experiment results without the auxiliary source connection

200

(a) MOSFETs turn-on

time(ns)

100

100

25

20

Current(A)

60

Current(A) 50

0 0

200

time(ns)

300

400

O1

Q2

Q3

500

500

Compared with Fig. 26, the total current even has a higher overshoot and more oscillations during turn-on period. That is because the 4 paralleled SiC MOSFETs has smaller common source inductance, which makes these SiC MOSFETs switch faster. It indicates that a "good" total current performance of the power module cannot prove that the paralleled dies also operate with a "good" current. The paralleled dies in the multichip power module may work in the border or out of the SOA of the SiC MOSFET dies, which affects the reliability of the power module.

With the auxiliary source connection, the current sharing performance is improved. However, the auxiliary source connection is not as good as Kelvin-source connection [42]. In case of 4 SiC MOSFETs are paralleled, Kelvin-source connections for all the paralleled dies could not be achieved. The auxiliary source connection can also take part of the drain current which cannot be avoided in parallel connection. It requires that the auxiliary source bond-wires should be capable of handling power current.

#### V. CONCLUSION

This paper presents a systematic analysis on the influences of device and circuit mismatches on paralleling SiC MOSFETs. From the experimental study on the effects of device mismatch and asymmetrical circuit design of paralleled discrete devices, it is shown that the mismatch of the switching loop stray inductance may also lead to on-state current unbalance, besides the different on-state resistance of devices. The mismatch of common source stray inductance causes transient current unbalance. Moreover, from the detailed analysis of the current distribution in a full SiC MOSFET multichip power module, the mismatch of common source stray inductance in the DBC layout is investigated. Furthermore, there is a current coupling effect among the paralleled dies, which is found to have a significant influence on the transient current distribution among the dies. Then, a current coupling mitigation method is developed by introducing an auxiliary source connection bond-wire. Simulation and experimental results validate the analysis and the effectiveness of the developed power module layout.

#### REFERENCES

- [1] Honggang Sheng, Zheng Chen, F. Wang and A. Millner, "Investigation of 1.2 kV SiC MOSFET for high frequency high power applications," in Proc. 25th Annu. IEEE Appl. Power Electron. Conf. Expo., 2010, pp. 1572-1577.

- [2] A. Antonopoulos, H. Bangtsson, M. Alakula and S. Manias, "Introducing a silicon carbide inverter for hybrid electric vehicles," in *Proc. Power Electron. Spec. Conf.*, 2008, pp. 1321-1325.

- [3] S. V. Araujo and P. Zacharias, "Perspectives of high-voltage SiC-semiconductors in high power conversion systems for wind and photovoltaic sources," in *Proc. Eur. Conf. Power Electron. Appl.*,2011, pp. 1-10.

- [4] B. Burger and D. Kranzer, "Extreme high efficiency PV-power converters," in *Proc. Eur. Conf. Power Electron. Appl.*, 2009, pp. 1-13.

- [5] J. Rabkowski, D. Peftitsis and H. Nee, "Silicon Carbide Power Transistors: A New Era in Power Electronics Is Initiated," *IEEE Ind. Electron. Mag.*, vol.6, no.2, pp.17-26, Jun. 2012.

- [6] A. Kadavelugu, V. Baliga, S. Bhattacharya, M. Das and A. Agarwal, "Zero voltage switching performance of 1200V SiC MOSFET, 1200V silicon IGBT and 900V CoolMOS MOSFET," in *Proc. IEEE Energy*

- Convers. Congr. Expo., 2011, pp. 1819-1826.

- [7] Gangyao Wang, Fei Wang, G. Magai, Yang Lei, A. Huang and M. Das, "Performance comparison of 1200V 100A SiC MOSFET and 1200V 100A silicon IGBT," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2013, pp. 3230-3234.

- [8] J. Biela, M. Schweizer, S. Waffler and J. W. Kolar, "SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors," *IEEE Trans. Ind. Electron.*, vol. 58, no.7, pp. 2872-2882, Jun. 2011.

- [9] Tiefu Zhao, Jun Wang, A. Q. Huang and A. Agarwal, "Comparisons of SiC MOSFET and si IGBT based motor drive systems," in *Proc. IEEE Ind. Appl. Conf. IAS Ann. Meeting Conf. Record*, 2007, pp. 331-335.

- [10] A. M. Abou-Alfotouh, A. V. Radun, Hsueh-Rong Chang and C. Winterhalter, "A 1-MHz hard-switched silicon carbide DC-DC converter," *IEEE Trans. Power Electron.*, vol. 21, no. 4, pp. 880-889, Jul. 2006.

- [11] D. -. Sadik, J. Colmenares, D. Peftitsis, Jang-Kwon Lim, J. Rabkowski and H. -. Nee, "Experimental investigations of static and transient current sharing of parallel-connected silicon carbide MOSFETs," in *Proc. Eur. Conf. Power Electron. Appl.*, 2013, pp. 1-10.

- [12] Yang Xue, Junjie Lu, Zhiqiang Wang, L. M. Tolbert, B. J. Blalock and F. Wang, "Active current balancing for parallel-connected silicon carbide MOSFETS," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2013, pp. 1563-1569

- [13] Y. Cui, M. S. Chinthavali, F. Xu and L. M. Tolbert, "Characterization and modeling of silicon carbide power devices and paralleling operation," in *IEEE Proc. Int. Symp. Ind. Electron.*, 2012, pp. 228-233.

- [14] L. Boteler, D. Urciuoli, G. Ovrebo, D. Ibitayo and R. Green, "Thermal performance of a dual 1.2 kV, 400 a silicon-carbide MOSFET power module," in *IEEE Proc.SEMI-THERM Symposium.*, 2010, pp. 170-175.

- [15] M. K. Das, C. Capell, D. E. Grider, R. Raju, M. Schutten, J. Nasadoski, S. Leslie, J. Ostop and A. Hefner, "10 kV, 120 A SiC half H-bridge power MOSFET modules suitable for high frequency, medium voltage applications," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2011, pp. 2689-2692.

- [16] J. Fabre, p. Ladoux and M. Piton, "Characterization and Implementation of Dual-SiC MOSFET Modules for future use in Traction Converters," *IEEE Trans. Power Electron.*, vol. PP, no. 99, pp. 1-13, Aug. 2014.

- [17] Y. Hinata, M. Horio, Y. Ikeda, R. Yamada and Y. Takahashi, "Full SiC power module with advanced structure and its solar inverter application," in *Proc.* 28<sup>th</sup> Annu. IEEE Appl. Power Electron. Conf. and Expo., 2013, pp. 604-607.

- [18] T. Salem, D. Urciuoli, R. Green and G. Ovrebo, "High-temperature high-power operation of a 100 A SiC DMOSFET module," in *Proc. 24th Annu. IEEE Appl. Power Electron. Conf. and Expo.*, 2009, pp. 653-657.

- [19] J. D. Scofield, J. N. Merrett, J. Richmond, A. Agarwal and S. Leslie, "Performance and reliability characteristics of 1200 V, 100 A, 200 C half-bridge SiC MOSFET-JBS diode power modules," in *IMAPS Int. Conf. High Temperat. Electron.*, 2010, pp, 289-296.

- [20] D. Urciuoli, R. Green, A. Lelis and D. Ibitayo, "Performance of a dual, 1200 V, 400 A, silicon-carbide power MOSFET module," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2010, pp. 3303-3310.

- [21] R. A. Wood and T. E. Salem, "Evaluation of a 1200-V, 800-A all-SiC dual module," *IEEE Trans. Power Electron.*, vol. 26, pp. 2504-2511, Jan. 2011

- [22] Zheng Chen, Yiying Yao, Wenli Zhang, D. Boroyevich, Khai Ngo, P. Mattavelli and R. Burgos, "Development of a 1200 V, 120 A SiC MOSFET module for high-temperature and high-frequency applications," in *IEEE Workshop Wide Bandgap Power Devices Appl.*, 2013, pp. 52-59.

- [23] D. Peftitsis, R. Baburske, J. Rabkowski, J. Lutz, G. Tolstoy and H. Nee, "Challenges Regarding Parallel Connection of SiC JFETs," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1449-1463, Oct. 2013.

- [24] H. Li, S. Munk-Nielsen, C. Pham and S. Beczkowski, "Circuit mismatch influence on performance of paralleling silicon carbide MOSFETs," in *Proc. Eur. Conf. Power Electron. Appl.*, 2014, pp. 1-8.

- [25] Xue Yang, Lu Junjie, Wang Zhiqiang, Tolbert Leon M., Blalock Benjamin J., Wang Fred., "Active current balancing for parallel-connected silicon carbide MOSFETs," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2013, pp.1563-1569

- [26] J. Forsythe, "Paralleling Of Power MOSFETs For Higher Power Output," International Rectifier Applications Note.[Online] Available: http://www.irf.com/technical-info/appnotes/para.pdf

- [27] W. Gangyao, M. John, R. Julius and S. Marcelo, "Dynamic and Static

- Behavior of Packaged Silicon Carbide MOSFETs in Paralleled Applications," *Proc. Appl. Power Electron. Conf. Expo.*, 2014, pp. 1478 1483.

- [28] J. B. Forsythe, "Paralleling of power MOSFETs for higher power output," in IEEE-IAS Conference Record, 1981.

- [29] Jianjing Wang, H. S. -. Chung and R. T. -. Li, "Characterization and Experimental Assessment of the Effects of Parasitic Elements on the MOSFET Switching Performance," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 573-590, Jan. 2013.

- [30] Zheng Chen, D. Boroyevich and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," in *Proc. Int. Power Electron. Conf.*, 2010, pp. 164-169.

- [31] "SiC Power Devices and Modules," ROHM semiconductor. JA. [Online] Available: http://rohmfs.rohm.com/en/products/databook/applinote/discrete/sic/common/sic\_appli-e.pdf

- [32] K. Oh. (2013, Sep). "MOSFET basics," Fairchild semiconductor. [Online] Available: https://www.fairchildsemi.com/application-notes/AN/AN-9010.pdf

- [33] "SiC MOSFET only module increases current at reduced on resistance," ROHM semiconductor, 2013. [Online] Available: http://www.power-mag.com/pdf/feature\_pdf/1380720266\_Rohm\_Feature\_Layout\_1.pdf

- [34] D. A. Neamen and B. Pevzner, Semiconductor Physics and Devices: Basic Principles. McGraw-Hill New York, 2003.

- [35] N. Kaminski and O. Hilt, "SiC and GaN devices-competition or coexistence?" in *Proc. Int. Conf. Integr. Power Electron*. Systems, 2012, pp. 1-11.

- [36] F. Roccaforte, P. Fiorenza, G. Greco, M. Vivona, R. Lo Nigro, F. Giannazzo, A. Patti and M. Saggio, "Recent advances on dielectrics technology for SiC and GaN power devices," *Appl. Surf. Sci.*, vol. 301, pp. 9-18, May. 2014.

- [37] M. K. Das, C. Capell, D. E. Grider, R. Raju, M. Schutten, J. Nasadoski, S. Leslie, J. Ostop and A. Hefner, "10 kV, 120 A SiC half H-bridge power MOSFET modules suitable for high frequency, medium voltage applications," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2011, pp. 2689-2692.

- [38] M. K. Das, R. Callanan, D. C. Capell, B. Hull, F. Husna, J. Richmond, M. O'loughlin, M. J. Paisley, A. Powell and Q. Zhang, "State of the art 10 kV NMOS transistors," in *Proc. ISPSD Int. Sympo. Power Semicond. Devices*,, 2008, pp. 253-255.

- [39] H. Matsunami, "Current SiC technology for power electronic devices beyond Si," *Microelectronic Engineering*, vol. 83, pp. 2-4, Jan. 2006.

- [40] R. J. Callanan, A. Agarwal, A. Burk, M. Das, B. Hull, F. Husna, A. Powell, J. Richmond, S. Ryu and Q. Zhang, "Recent progress in SiC DMOSFETs and JBS diodes at cree," in *IEEE Ann. Conf. Ind. Electron.*, 2008, pp. 2885-2890.

- [41] Bob Callanan. (2011, Feb). "SiC mosfet double pulse fixture," Cree, Inc., US, . [Online] Available: http://www.cree.com/Power/Document-Library

- [42] Stueckler Franz, Vecino-Vazquez Enrique. (2013, May). "CoolMOS C7 650V Switch in a Kelvin Source Configuration," Infineon Technologies, GE. [Online] Available:

- $http://www.infineon.com/dgdl/Infineon+-+Application+Note+-+TO-24\\7-4pin+-+650V+CoolMOS+C7+Switch+in+a+Kelvin+Source+Configuration.pdf?folderId=db3a304333b8a7ca0133c6bec0956188&fileId=db3a30433e5a5024013e6a9908a26410$