# **Aalborg Universitet**

# A Multipulse Pattern Modulation Scheme for Harmonic Mitigation in Three-Phase Multimotor Drives

Davari, Pooya; Yang, Yongheng; Zare, Firuz; Blaabjerg, Frede

Published in:

I E E E Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2015.2461018

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Davari, P., Yang, Y., Zare, F., & Blaabjerg, F. (2016). A Multipulse Pattern Modulation Scheme for Harmonic Mitigation in Three-Phase Multimotor Drives. *I E E Journal of Emerging and Selected Topics in Power Electronics*, *4*(1), 174-185. https://doi.org/10.1109/JESTPE.2015.2461018

## **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

1

# A Multi-Pulse Pattern Modulation Scheme for Harmonic Mitigation in Three-Phase Multi-Motor Drives

Pooya Davari, Member, IEEE, Yongheng Yang, Member, IEEE, Firuz Zare, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract— Continuous improvement of power electronics technology has widely increased the applications of adjustable speed motor drives in many areas. Beyond the control flexibility, the power electronics devices (e.g., diode rectifiers) are also the main harmonic source to the grid due to their nonlinearity, which thus deteriorates the power grid quality and also lowers the conversion efficiency. Both degradations are apt to occur in motor drive applications. At present, many industrial drives are equipped with three-phase diode rectifiers and employ passive filtering techniques on the AC or DC side of the rectifier. In such topologies, it is difficult to implement the prior-art harmonic control strategies. Moreover, the total cost and complexity has become the main obstacle for these harmonic elimination approaches in multiple drive systems. Therefore, in this paper, a new cost-effective harmonic mitigation approach has been proposed for multiple drives. The proposed approach can control the generated current harmonics by benefiting of the nonlinearity of the drive units and through a novel current modulation scheme. The obtained results at the simulation and experimental level validate the effectiveness of the proposed approach.

Index Terms— Adjustable speed drives, active filters, current modulation, harmonic mitigation, multiple drives, three-phase rectifiers.

### I. INTRODUCTION

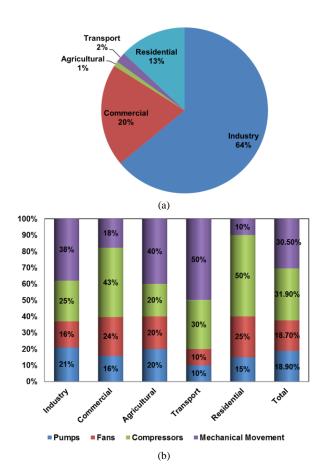

ELECTRIC motor-driven systems consume more than 40% of the global electricity. In fact, the high demand for electric motors as shown in Fig. 1(a) has made them to be the major source of electricity use [1]. As the global electricity demand is continuously growing at a rapid rate, industry as a key player according to Fig. 1(b) has been pushed towards an era of developing more energy-efficient drives. With the

Manuscript received March 16, 2015; revised June 19, 2015; accepted July 18, 2015. Recommended for publication by Associate Editor xxx.

P. Davari, Y. Yang and F. Blaabjerg are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark. (Email: pda@et.aau.dk; yoy@et.aau.dk; fbl@et.aau.dk).

F. Zare is with the Department of EMC and Harmonics, Global R&D Center, Danfoss Power Electronics A/S, 6300 Gråsten, Denmark. (Email: fza@danfoss.com).

This is the preprint version of the manuscript. When it is published, color versions of one or more of the figures in this paper will be available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JESTPE.2015.xxxxxxx

Fig. 1. Estimated share of electricity consumption for all electric motors from International Energy Agency (IEA) by: (a) sector and (b) sector and application [1].

advancement of power electronic devices and their decreasing price due to the market demand, Adjustable Speed Drive (ASD) systems are becoming increasingly common in many applications. Although the benefit of adjustable speed control on energy saving is clear, the penetration of ASD systems is still relatively low, due to the dependency of ASD market trend on the cost and efficiency.

Employing the adjustable speed technology for power electronics based drive systems can improve the efficiency to some extent [2]. However, the generated harmonics as a consequence of employing power electronics devices will

inevitably deteriorate the power grid quality [3]-[5]. These highly-distorted currents appearing in the power grid, cause unnecessary losses and thus may lead to heat in power system transformers, nuisance tripping of circuit breakers, and overstressing of power factor correction capacitors. This highlights the necessity for the drive systems to comply with international standards like IEC61000 standard [6]. Therefore, it calls for more intelligent and advanced harmonic elimination strategies for the drive systems.

Typically, a standard drive system comprises of three main sections: the front-end power converter that converts AC power from the main grid to DC power, an energy storage unit called the DC-link, and finally an inverter as the rear-end power converter, which converts the DC back to AC at the voltage and frequency demanded by the motor. A three-phase diode bridge rectifier is usually employed, which is an almostindustry-standard choice at the front-end stage, being witnessed as the main harmonic source. As a consequence, a vast of harmonic mitigation methods have been introduced to such drive systems in order to improve the input current quality by shaping it as close as possible to a sinusoidal waveform [4], [5], [7]-[9] as well as using active damping methods [10]-[15]. However, a significant increase of complexity and cost has been observed in the harmonic elimination strategies. As a result, diode rectifiers (uncontrolled) or thyristor-based rectifiers (phase-controlled) of less complexity and cost are still widely used in the modern drive systems like in the ASD systems.

In addition, the undesirable nonlinearity of the conventional AC-DC conversion stage becomes significant, when a large number of industrial converters and ASD systems are connected to the Point of Common Coupling (PCC). It has been found that a proper arrangement of these nonlinear loads either single-phase or three-phase units can contribute to an effective harmonic mitigation, where some of the harmonics from one unit (e.g., diode rectifier) can be cancelled out by the other/s units [16]. The feasibility of this solution is attained only when suitable and accessible communication among the nonlinear units can be performed. It can be observed in many practical applications, where multitudes of ASD based industrial pumps, fans or compressors are operated all together.

In fact, improving the input current quality by combining the nonlinear loads was first introduced in multi-pulse rectifiers [17]. In this method, by employing phase-shifting transformers, the harmonics of each unit can be phase-displaced with respect to each other, and thus they can cancel out certain harmonics. Depending on the number of connected units, a range of harmonics can be eliminated. Taking a 24-pulse rectifier [17] as an example, the current Total Harmonic Distortion (THD<sub>i</sub>) can significantly be improved (lower than 5%) using this method. Despite the effectiveness in harmonic mitigation, the volume, associated losses, and the cost of the phase-shifted transformer are the main concerns and these drawbacks become more evident at medium and high power applications.

Therefore, in this paper, a novel harmonic elimination approach is proposed to tackle the aforementioned challenges.

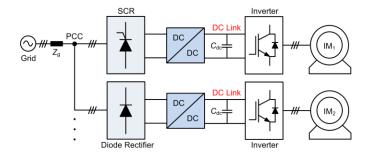

Fig. 2. Typical configuration for a multi-drive application with the proposed harmonic mitigation method: IM – Induction Motor.

The proposed method does not require any phase-shifting transformers like what have been used in multi-pulse rectifiers. Instead, as depicted in Fig. 2, it is based on a combination of the three-phase diode rectifier and three-phase Silicon Controlled Rectifier (SCR) units to cancel out the harmonics of interest. Additionally, in Section II, in order to improve the performance and flexibility of the system, each unit is equipped with a new current modulation technique is applied to the employed DC-DC converter (e.g., boost converter) at the DC-link, which can individually mitigate a certain number of current harmonics. Considering the employed DC-DC converter, the intended power ratings of each drive unit can be in the range of low power (<1 kW) up to medium power (<100 kW). However, depending on the application requirement, the power rating can be extended to a high power range by applying the multi-drive configuration. Optimization of the current modulation technique has also been conducted in Section II to further reduce the harmonic emissions from drive systems. Experimental tests and simulations have been carried out on a 5.5 kW system. Results presented in Section IV have verified the effectiveness of the proposed harmonic elimination method.

### II. PROPOSED HARMONIC ELIMINATION METHOD

### A. Nonlinear Loads Combination for Harmonic Cancellation

In order to demonstrate and evaluate the proposed harmonic mitigation method, the front-end stage of a multi-drive system consisting of two three-phase rectifier units is built up as it is shown in Fig. 2. The system operation details are illustrated in Fig. 3, which shows that the current source at the DC-link side of the rectifier draws a constant current (i.e.,  $I_{dc}$ ). In practice, the current source can be implemented in a DC-DC converter (e.g., boost converter) which emulates an ideal inductor behavior [18]-[21]. Therefore, for both rectifiers as shown in Fig. 3, the input currents (i.e.,  $i_s$  and  $i_d$ ) of the rectifiers will be square-wave currents with a conduction angle of  $120^\circ$ , since at each instant of time interval only two phases conduct and circulate the DC-link current through the grid.

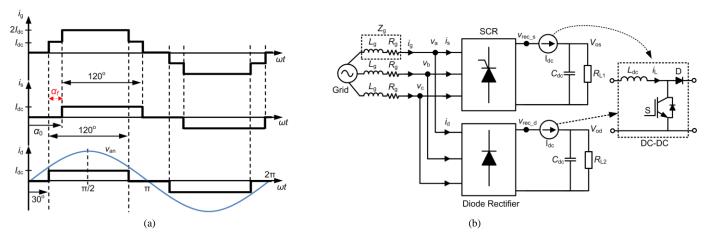

For the rectifier system shown in Fig. 3, Fourier series analysis has been adopted to identify the harmonic content of the input currents drawn from the power grid. According to Fig. 3(a), in a controlled rectifier (i.e., an SCR), the harmonics (i.e.,  $i_s(n)$ ) of the square-wave input current with a conduction angle of 120° and an adjustable phase angle of  $\alpha_0$  can be

Fig. 3. Current distribution at the PCC of a multi-drive system with one diode rectifier and one SCR unit: (a) ideal currents and (b) system schematic.

identified as:

$$i_s(n) = \sqrt{(a_n)^2 + (b_n)^2}$$

(1)

with

$$\begin{cases} a_{n} = \frac{2I_{dc}}{n\pi} \left[ -\sin(n\alpha_{0}) + \sin(n\alpha_{0} + \frac{2\pi n}{3}) \right] \\ b_{n} = \frac{2I_{dc}}{n\pi} \left[ \cos(n\alpha_{0}) - \cos(n\alpha_{0} + \frac{2\pi n}{3}) \right] \end{cases}$$

in which  $n=1, 5, 7, \ldots$ , is the harmonic order. As for the three-phase diode rectifier, it can be taken as a special case of the SCR with a firing angle of  $\alpha_f = 0^\circ$  or a fixed phase angle of  $\alpha_0 = 30^\circ$  ( $\alpha_0 = 30^\circ + \alpha_f$ ). In that case,  $\alpha_n = 0$  according to (1), and thus the harmonics of the input current induced by the diode rectifier can be given by,

$$i_{d}(n) = \frac{4I_{dc}}{n\pi} \cos\left(\frac{n\pi}{6}\right) \tag{2}$$

According to Fig. 3, the total current drawn from grid can be expressed as  $i_g = i_s + i_d$ . Thus, the harmonics appearing in the grid current (i.e.,  $i_g$ ) can be calculated as,

$$i_{g}(n) = \sqrt{(a_{n})^{2} + (i_{d}(n) + b_{n})^{2}}$$

(3)

As a consequence, based on (3), if the transcendental equations given in (4) are solved, any n-th harmonic appearing in the grid current can be cancelled out, and at the same time, the desired fundamental content of the grid current as the modulation index ( $M_a$ ) can be achieved.

$$\begin{cases} i_g(1) = M_a \\ a_n = 0 \\ b_n + i_d(n) = 0 \end{cases}$$

$$(4)$$

### B. Novel Current Modulation Technique

Although an appropriate adjustment of the phase angle of the SCR unit can contribute to an improvement of the current quality, a new current modulation technique is applied to each DC-DC converter in order to further improve the current quality. In the new current modulation approach, certain low order harmonics in the three-phase input line currents (i.e., the grid currents) can be eliminated by adding (or subtracting) phase-displaced current levels, thus leading to a better overall grid power quality, which will be detailed in the following.

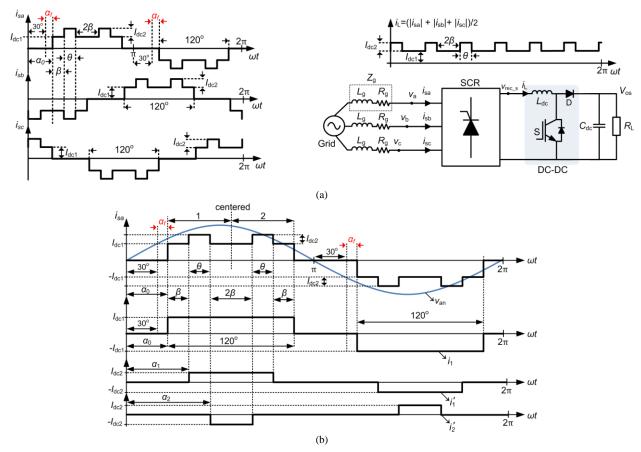

The novel current modulation technique is based on the calculation of a pre-programmed switching pattern (current reference) for the DC-link current to achieve elimination of those specific harmonics in the grid currents. Fig. 4(a) demonstrates the basic idea of the proposed current modulation method for one rectifier unit (i.e., SCR). The illustrated currents in Fig. 4(a), show the new added current levels at the DC-link ( $i_L$ ) in relation to the three-phase input currents.

For ease to analyze the harmonic characteristics, the switching patterns have been centralized and synchronized in respect to the grid phase voltage. In this approach, the new added current level should be repeated every 1/6 of the fundamental period in order to mitigate the triple harmonics. For instance, in the two sectors of 1 and 2 as shown in Fig. 4(b), where in each sector  $i_a$  is circulated through one of the other phase currents, if the new current level is added into sector 1, it should be exactly repeated in sector 2. This means that the frequency of the added pulses at the DC-link should be six times of the fundamental frequency (i.e.,  $i_L$  in Fig. 4(a)).

It can be seen in Fig. 4(b) that the proposed current modulation pattern consists of three square-wave signals with different magnitudes and angles. The first current waveform has the magnitude of  $I_{\rm dc1}$  with the conduction at a phase angle of  $\alpha_0$ . Notably, for a three-phase diode rectifier, this phase angle is constant,  $\alpha_0 = 30^{\circ}$  ( $\alpha_f = 0$ ). The second current waveform has the magnitude of  $I_{\rm dc2}$  with the conduction at a phase angle of  $\alpha_1$ . The third current waveform has the magnitude of  $I_{\rm dc2}$  but with the conduction at a phase angle of  $\alpha_2$ . According to (1), the input current harmonics can then be

Fig. 4. Illustration of the proposed current modulation with selected harmonic cancellation: (a) typical waveforms in a SCR unit ( $\alpha_f = 0^\circ$  in the case of diode rectifiers) and (b) conceptual illustration of the proposed modulation scheme.

calculated as:

$$i_a(n) = \sqrt{(a_n + a'_n)^2 + (b_n + b'_n)^2}$$

(5)

with

$$\begin{cases} a'_{n} = \sum_{j=1}^{2} \frac{2I_{dc2}(-1)^{j+1}}{n\pi} \left[ -\sin(n\alpha_{j}) + \sin(2n\alpha_{0} - n\alpha_{j} + \frac{2\pi n}{3}) \right] \\ b'_{n} = \sum_{j=1}^{2} \frac{2I_{dc2}(-1)^{j+1}}{n\pi} \left[ \cos(n\alpha_{j}) - \cos(2n\alpha_{0} - n\alpha_{j} + \frac{2\pi n}{3}) \right] \end{cases}$$

where  $i_a$  is the phase A current of the grid,  $a'_n$  and  $b'_n$  are the Fourier coefficients of the new added current levels that conduct at  $\alpha_1$  and  $\alpha_2$ , and  $\alpha_0 < \alpha_1 < \alpha_2 < \alpha_0 + 60^\circ$ . Hence, in order to individually cancel out up to two low order harmonics, e.g.,  $i_a(m)$  and  $i_a(k)$ , the following condition holds,

$$2\beta + \theta = 60$$

or  $2(\alpha_1 - \alpha_2) + (\alpha_2 - \alpha_1) = 60$  (6)

In respect to the three-phase diode rectifier, the conduction starts at a fix phase angle  $a_0 = 30^{\circ} (a_f = 0^{\circ})$ . Thus, according to (5) and (6), in the case of a three-phase diode rectifier,  $a_n = a'_n = 0$ . Therefore, the harmonics of the diode rectifier input current represented in (5) can be simplified as,

$$i_{d}(n) = \frac{4}{n\pi} \left[ I_{dc1} \cos\left(\frac{n\pi}{6}\right) + I_{dc2} \cos\left(n\alpha_{1}\right) - I_{dc2} \cos\left(\frac{2\pi n}{3} - n\alpha_{1}\right) \right]$$

(7)

Hence, applying the proposed current modulation technique to both of the rectifier units can significantly improve the input current quality. Notably, the harmonics appearing in the supply line (i.e., grid currents  $i_g$ ) can be calculated as,

$$i_{g}(n) = \sqrt{(a_{n} + a'_{n})^{2} + (i_{d}(n) + b_{n} + b'_{n})^{2}}$$

(8)

which results in a flexible harmonic elimination in the grid currents by solving,

$$\begin{cases} i_{g}(1) = M_{a} \\ a_{n} + a'_{n} = 0 \\ i_{d}(n) + b_{n} + b'_{n} = 0 \end{cases}$$

(9)

where  $M_a$  is the desired fundamental value and  $a_n$ ,  $a'_n$ ,  $b_n$ ,  $b'_n$  are the Fourier series coefficients mentioned in (1) and (5).

### C. Optimum Harmonic Solution

The above illustrates the impact on the harmonics by selecting proper modulation parameters (amplitudes and switching angles) for the proposed current modulation scheme. However, an optimization for these parameters may result in a more suitable solution and also higher flexibility to eliminate the harmonics of interest. The following demonstrates the harmonic optimization solution considering the maximum allowable harmonic level defined by the application or the grid code. In other words, instead of fully nullifying the distortions, the harmonics could be reduced to acceptable levels by adding suitable constraints ( $L_n$ ). Then, an optimization problem ( $Obj_n$ ) that searches a set of  $\alpha_n$  and  $I_{dc}$  values over the allowable intervals can be defined as,

$$\begin{cases} Obj_{1} = M_{a} - \left| i_{g}(1) \right| \leq L_{1} \\ Obj_{n} = \frac{\left| i_{g}(n) \right|}{\left| i_{g}(1) \right|} \leq L_{n} \end{cases}$$

$$(10)$$

where  $n = 6k\pm 1$  with k being 1, 2, 3, ....

Based on (9), an objective function  $F_{obj}$  has to be formed to minimize the error [22]. The objective function plays an important role in leading the optimization algorithm to a suitable solution set. Here,  $F_{obj}$  is formed based on a squared error with more flexibility by adding constant weight values  $(w_n)$  to each squared error function as,

$$F_{obj} = \sum w_n \cdot \left(Obj_n - L_n\right)^2 \tag{11}$$

in which  $n = 1, 6k \pm 1$  with k being 1, 2, 3, ....

In addition to the maximum allowable harmonic level, the  $THD_i$  restriction could also be the objective function or included in (10) and prioritized with a suitable weight value. Notably, apart from the optimization constraint  $L_n$ , the following condition on the angles has to be included as well in order to ensure a proper rectification operation,

$$\alpha_{\scriptscriptstyle 0} < \alpha_{\scriptscriptstyle 1} < \alpha_{\scriptscriptstyle 2} < \dots < \alpha_{\scriptscriptstyle m} < \alpha_{\scriptscriptstyle 0} + \frac{\pi}{3} \tag{12}$$

### III. SINGLE SWITCH THREE-PHASE BOOST RECTIFIER SYSTEM

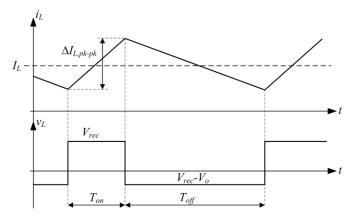

In order to control DC-link current shape and magnitude following the waveforms shown in Fig. 2, a boost converter topology based on the electronic inductor [8], [18]-[21] concept is employed. Using the conventional boost topology has the advantage of boosting the output DC voltage to a suitable level when it is fed to an inverter. Moreover, as the DC-link current is controlled based on the load power, it has the advantage of keeping the THD<sub>i</sub> independent of load profile. To better understand this, the inductor current in a steady-state Continuous Conduction Mode (CCM) is illustrated in Fig. 5. Here the switching frequency is considered to be high enough so that the rectified voltage and

Fig. 5. Inductor current and voltage waveforms in one switching cycle.

output voltage are constant during one switching cycle. Therefore, the inductor value can be calculated as,

$$L = \frac{V_o D(1 - D)}{f_{sw} \Delta I_{L,pk-pk}} \quad \text{with} \quad f_{sw} = \frac{1}{T_{sw}} = \frac{1}{T_{on} + T_{off}}$$

(13)

where  $V_o$  is the output voltage,  $f_{sw}$  is the switching frequency,  $\Delta I_{L,pk-pk}$  is the peak to peak inductor current ripple and D is the steady-state duty cycle of the boost converter. Using (13) the minimum required switching frequency ( $f_{sw}$ ) can be selected by considering the maximum peak to peak inductor current ripple (D = 0.5) as,

$$f_{sw} \ge \frac{V_o}{4L\Delta I_{L,pk-pk,\text{max}}} \tag{14}$$

Following (13) and (14) optimum switching frequency can be selected by making a tradeoff among the system efficiency, size and cost [23]. For example the system efficiency can be optimized by minimizing the switching frequency by allowing more ripple current for high power applications, therefore resulting in lower switching losses.

As mentioned before the  $THD_i$  can be independent of the load profile. The equation (13) can be rewritten based on output average current as,

$$L = \frac{V_o D (1 - D)^2}{f_{sw} k_{ripple} I_o}$$

with

$$k_{ripple} = \frac{\Delta I_{L,pk-pk}}{I_L} = \frac{\Delta I_{L,pk-pk} (1 - D)}{I_o}$$

(15)

in which  $k_{ripple}$  is the ripple factor,  $I_L$  is the average inductor current, and  $I_o$  is the average output current. Hence, keeping the ripple factor as a constant value will make the input current quality independent of the load profile. However, careful selection of the ripple factor is needed, as it has a direct relation with the ripple current, which as stated in (14) can affect the inductor size, system efficiency and cost [23].

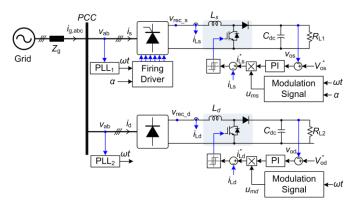

Fig. 6. Block diagram of the overall control structure implemented for the multi-rectifier system.

Fig. 6 depicts the block diagram of the overall control structure for the multi-rectifier units, where a hysteresis controller is adopted as the current controllers for the boost converters. The reference tracking performance of the current controller has an important role in the harmonic mitigation, thus fast current control methods such as hysteresis or deadbeat control should be employed. In order to synchronize the current controllers with the grid, for each rectifier unit a Second-Order Generalized Integrator (SOGI) based Phase Locked Loop (PLL) system is adopted [24]. For simplicity, only one line-to-line voltage is fed to the PLL. Therefore, the result will have a phase shift of 30° in respect to the phase voltage, which should be corrected within the reference current generator algorithm. Moreover, as it can be seen from the system schematics shown in Fig. 6, the firing angle of the thyristor based rectifier (i.e., SCR) should be applied according to the phase detected by the PLL.

### IV. RESULTS

Referring to Fig. 6, the proposed approach has been validated through simulation and practical experiments. To bring simulation and experiments in a close agreement, practical parameters have been fully considered in simulation. Here the grid phase voltage is 220  $V_{RMS}$  and the grid frequency is 50 Hz. The total output power was set at 5.5 kW and the output voltage of the boost converter is maintained at 700  $V_{DC}$  by employing a Proportional Integrator (PI) controller and a hysteresis controller is adopted as the current controller, as shown in Fig. 6.The main component parameters of the entire systems are the same in the SCR and diode rectifier as listed in Table I.

### A. Simulation Results

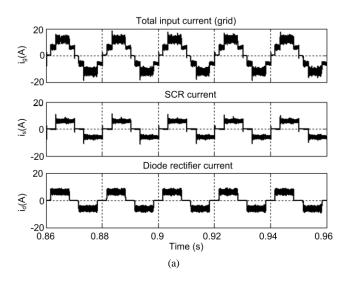

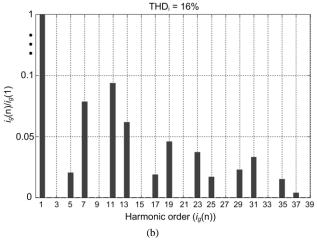

Simulations have firstly been conducted to verify the effectiveness of the proposed method. In the first study case, the effect of applying phase-shift strategy to the multisystem is tested with a simple flat current modulation, as it is shown in Fig. 3. The simulation results are presented in Fig. 7. As it can be observed in Fig. 7(a), the input currents of each unit ( $i_s$  and  $i_d$ ) and the total current at the grid side ( $i_g$ ) are controlled to be the desirable levels (flat currents). Theoretically, applying a phase-shift of  $36^\circ$  to the SCR unit should completely remove

$\label{eq:Table I} \textbf{M} \textbf{AIN CIRCUIT COMPONENTS OF THE ENTIRE MULTI-RECTIFIER} \\ \textbf{System.}$

| Component                     | Symbol                 | Value                      |

|-------------------------------|------------------------|----------------------------|

| DC-link inductor              | $L_{\rm s}, L_{\rm d}$ | 2 mH                       |

| DC-link Capacitor             | $C_{ m dc}$            | $470 \mu F$                |

| Snubber (RC) across thyristor |                        | $100~\Omega$ - $0.1~\mu F$ |

| Snubber (RC) across IGBT      |                        | $82 \Omega - 1 nF$         |

| Grid impedance                | $Z_g(L_g, R_g)$        | $0.18$ mH, $0.1$ $\Omega$  |

Fig. 7. Performance of the proposed method with flat currents applying a phase-shift of  $36^{\circ}$ : (a) current waveforms and (b) spectrum of the low-order harmonics at the total power level of 5.5~kW.

the 5<sup>th</sup> harmonic appearing in the grid. However, the presence of non-ideal parameters especially the grid impedance reduces the performance of the system slightly, and nonetheless the 5<sup>th</sup> harmonic is relatively lowered (i.e., 2.1 %), as shown in Fig. 7(b).

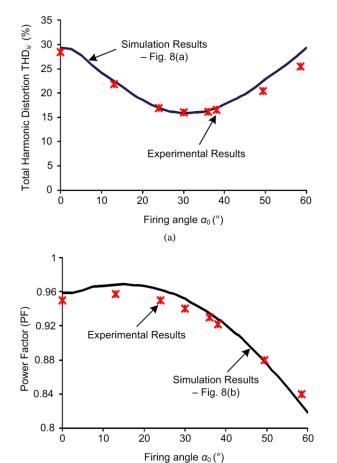

In order to further illustrate the influence of the phase-shift of the SCR unit on the grid current quality, the performance of the system has been analyzed by applying a wide range of the phase-shifts to the SCR unit. Fig. 8 shows the effect of applying different phase-shifts to the SCR on the grid current  $THD_i$ , the low-order harmonics (i.e.,  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$ , and  $13^{th}$ ) of the grid current  $i_g$ , and the Power Factor (PF). As it can be seen in Fig. 8(a), an increase of the firing can alter the power quality of the grid current. The lowest  $THD_i$  is observed in the case of a firing angle of  $30^\circ$ , where the grid current will be of 5-level with a relatively large PF = 0.952.

Moreover, mitigating of the low order harmonics (e.g., the 7th) can also be achieved by introducing a phase-shift to the SCR unit (e.g.,  $\alpha_f = 27^{\circ}$ ). However, in return, the phase displacement increases when a large firing angle is applied, i.e. leading to a lower PF, as it is shown in Fig. 8(b). Specifically, seen from Fig. 8(a), it is better to control the firing angle within 20° to 40° in order to maintain a satisfactory THD<sub>i</sub> while also minimize the low order harmonics. In contrast, when keeping the firing angle within 0° to 30°, the PF will be maintained between 0.95 and 0.97, as it is shown in Fig. 8(b). Therefore, for the case of applying square-wave current, the optimum firing angle (phase-shift) can be selected by applying an optimization algorithm as mentioned in Section II in order to mitigate the harmonics of interest when considering the THD; and also the power factor. The above has confirmed that it is a flexible solution to mitigate the harmonics in multiple drive systems by using phase-shifted SCR units.

Fig. 8. Simulation results of the multi-rectifier system with different firing angles for the SCR unit: (a) total harmonic distortion and the low-order harmonic distribution of the input current  $i_g$  and (b) power factor.

According to the simulation results, an almost-complete elimination of the 5<sup>th</sup> harmonic occurs at 38° instead of 36°, which is the theoretical calculation (i.e., 180°/5 = 36°). This is due to the presence of the line impedance, which delays the charging of the DC-link inductor and therefore a slight phase shift from the theoretical value occurs [25]. However, in reality, the grid impedance is unknown and applying a real-time calculation of the grid-impedance to the proposed modulation method is not a feasible approach.

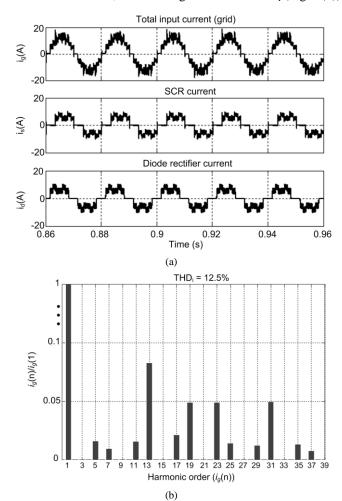

In the third case, in order to further reduce the  $THD_i$  and target at minimizing a higher number of the low order harmonics, novel current modulation has to be applied. Since only the low-order harmonics are of interest, the proposed method has been optimized according to (9)-(11) in order to attenuate the 5<sup>th</sup>, 7<sup>th</sup> and 11<sup>th</sup> harmonics to be less than 1 % of the fundamental component (i.e., the selected optimization constraints). In addition,  $THD_i$  is also included in the objective function ( $THD_i < 13\%$ ). A MATLAB function – "fmincon" has been used for optimization in this case study. Fig. 9(a) presents the results of the multi-rectifier system with the proposed current modulation strategy, which confirms that a multi-level input current is achieved by the phase-shift based modulation scheme, contributing to a lower  $THD_i$  (Fig. 9(b)).

Fig. 9. Performance of the proposed method with current modulation when  $5^{th}$ ,  $7^{th}$  and  $11^{th}$  harmonics are optimized for reduction where the total power level is 5.5 kW: (a) current waveforms (phase a) and (b) spectrum of the low-order harmonics in the grid current.

Fig. 10. Performance of the proposed method with current modulation when  $THD_i$  is optimized where the total power level is 5.5 kW: (a) current waveforms (phase a) and (b) spectrum of the low-order harmonics in the grid current.

However, due to the presence of non-ideal parameters, the 5<sup>th</sup> and the 11<sup>th</sup> harmonics are slightly higher than the optimization target (less than 1%), resulting from the effect of the grid impedance as previously discussed.

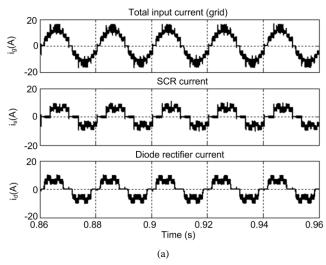

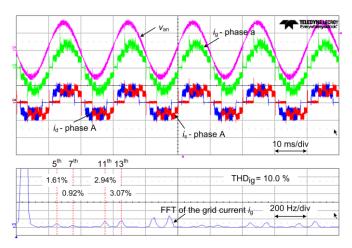

In addition, the flexibility of the proposed optimization method is also demonstrated in another case study, where the THD<sub>i</sub> is selected as the optimization objective function, and the optimization results are shown in Fig. 10, where the grid current, the diode rectifier input current, the SCR input current, and the Fast Fourier Transform (FFT) spectrum of the total grid current are illustrated. It can be observed in Fig. 10(b) that a THD<sub>i</sub> of 10.2 % is attained in the multi-rectifier system with the proposed method. Moreover, Table II summarizes the detailed harmonic content of the rectifier systems at a constant power level of 5.5 kW for comparison. It should be pointed out that different objectives have been included in the optimization algorithm as discussed in Section II. Following (5) and (7), Table III illustrates the estimated current modulation parameters for the two optimized cases with normalized amplitudes.

It should be noted that the aforementioned case studies were performed based on an assumption that each rectifier unit

TABLE II HARMONIC DISTRIBUTION OF DIFFERENT SIMULATED CASES AT A POWER LEVEL OF 5.5 KW.

|                                                                 | Harmonic Distribution and THD <sub>i</sub> (%) |                         |                          |                          |      |

|-----------------------------------------------------------------|------------------------------------------------|-------------------------|--------------------------|--------------------------|------|

| Harmonic<br>Mitigation Strategy                                 | $\frac{i_g(5)}{i_g(1)}$                        | $\frac{i_g(7)}{i_g(1)}$ | $\frac{i_g(11)}{i_g(1)}$ | $\frac{i_g(13)}{i_g(1)}$ | THDi |

| Phase-Shifted Flat<br>Current (Fig. 7)                          | 2.1                                            | 7.9                     | 9.4                      | 6.2                      | 16   |

| <sup>1</sup> Optimized Novel<br>Current Modulation<br>(Fig. 9)  | 1.6                                            | 0.9                     | 1.5                      | 8.3                      | 12.5 |

| <sup>2</sup> Optimized Novel<br>Current Modulation<br>(Fig. 10) | 2.4                                            | 0.3                     | 1.4                      | 4.8                      | 10.2 |

- 1. Optimization objective is to minimize the low order harmonics and also a lower  $THD_i$ .

- 2. Optimization objective is only to achieve a lower THD<sub>i</sub>.

Table III

OPTIMIZED CALCULATED CURRENT MODULATION PARAMETERS

(Normalized with  $M_a = 1$ ).

| Harmonic Diod                                                      |           | e Rectifier |                         |           | SC        |                     |                           |

|--------------------------------------------------------------------|-----------|-------------|-------------------------|-----------|-----------|---------------------|---------------------------|

| Mitigation<br>Strategy                                             | $I_{dc1}$ | $I_{dc2}$   | $\alpha_{I}^{\text{o}}$ | $I_{dc1}$ | $I_{dc2}$ | ${\alpha_I}^{ m o}$ | $lpha_{\!f}^{\mathrm{o}}$ |

| <sup>1</sup> Optimized<br>Novel Current<br>Modulation<br>(Fig. 9)  | 0.4       | 0.22        | 50                      | 0.4       | 0.22      | 50                  | 36                        |

| <sup>2</sup> Optimized<br>Novel Current<br>Modulation<br>(Fig. 10) | 0.41      | 0.2         | 50                      | 0.41      | 0.2       | 49.9                | 38.7                      |

- 1. Optimization objective is to minimize the low order harmonics and also a lower  $THD_i$ .

- 2. Optimization objective is only to achieve a lower  $THD_{i}$ .

draws an equal amount of current from the grid; otherwise, the rectified voltages  $V_{rec\_s}$  and  $V_{rec\_d}$  (see Fig. 6) are different due to the phase-shift and thus leading to different boost conversion gain ratio and may complicate the harmonic distributions.

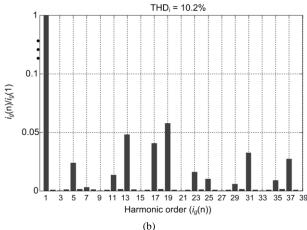

In addition to the effect of phase-shift, in real-world applications the two rectifier units do not necessarily operate at the same power level. Since the system is not dependent on the load profile, the power level itself is not the concern, and the ratio between output-power levels of the rectifier units are of importance. Therefore, as long as the following equation holds true, the rectifiers will draw equal amount of current from the grid; otherwise it should be reflected in the optimization process in one of the objective functions.

$$\frac{P_{o_{-}d}}{P_{o_{-}s}} \times \cos(\alpha_f) = 1 \tag{16}$$

where  $P_{o\_d}$  and  $P_{o\_s}$  are the output power of the diode rectifier and SCR unit, respectively.

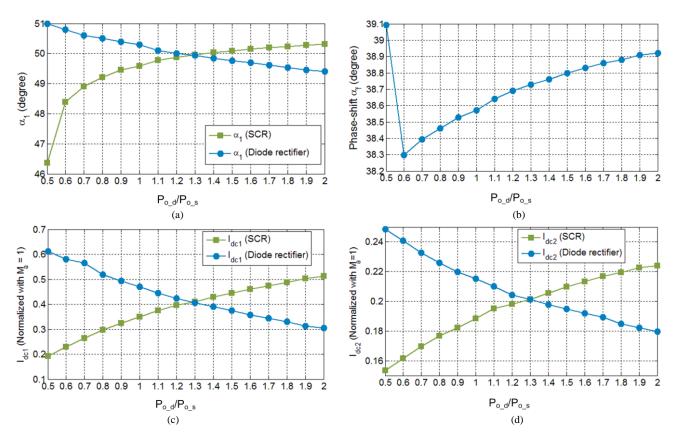

Fig. 11. Performance comparison of the multi-drive system at different output power ratios.

To examine the performance of the system when the output power of each rectifier unit is not balanced according to (16), different power ratios have been evaluated as illustrated in Fig. 11. In order to better realize this effect, the last case where the THD<sub>i</sub> was targeted for optimization for different power level is considered again. The optimized firing angle for this case  $(\cos(\alpha_0) \approx 1/1.3)$  denotes that the rectifiers draw an equal amount of currents, when the output power of the diode rectifier is 1.3 times of the output power of the SCR unit;

otherwise the  $THD_i = 10.2\%$  mentioned in Table II cannot be obtained. This is clearly demonstrated in Fig. 11, where the system is tested at different output power ratios (blue curve). However, if this situation is considered in the optimization objective function by reflecting (16), a compensated result can be obtained (red curve).

As it can be seen, by applying a specific set of current modulation parameters at each operating point (i.e., power ratio) the increased THD<sub>i</sub> due to the unbalanced loading of the rectifier units can be maintained at a lower level. Fig. 12 shows the estimated parameters for a wide range of power ratio variations (i.e., unbalanced loads) following Fig. 11.

Notably, to reduce computation complexity and to guarantee the smooth performance of the proposed method different precalculated current modulation parameters with their corresponding power ratios should be included as a look-up table in the controller. Therefore, by including a communication between each rectifier unit, suitable combinations of the input currents at the PCC can be made under variety situations.

# B. Practical Verification

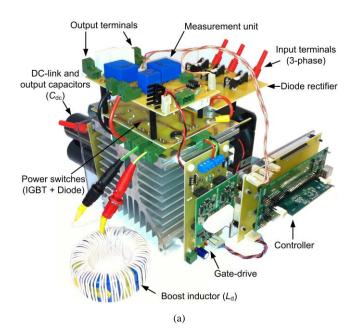

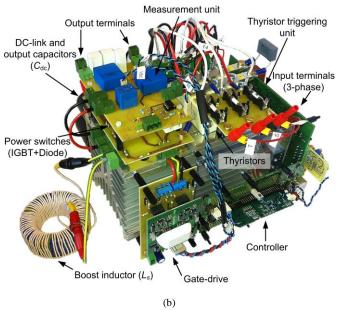

Experimental tests have been carried out on a 5.5-kW multirectifier system, which consists of two rectifier units (one diode rectifier and one SCR unit). Fig. 13 shows the prototypes used in the experimental tests, where Fig. 13(a) depicts a photograph of the three-phase diode rectifier unit and

Fig. 12. Estimated modulation parameters of the rectifier units for minimizing grid current THD<sub>i</sub> optimized for different power ratios ( $P_{0\_d}/P_{0\_s}$ ): (a) phase angle  $\alpha_{\rm I}$ , (b) applied phase-shift between rectifiers (firing angle), (c) magnitude of the first added level ( $I_{\rm dc1}$ ), and (d) second added level magnitude ( $I_{\rm dc2}$ ) at the DC-link.

Fig. 13. Photograph of implemented single switch three-phase boost rectifier for (a) diode rectifier and (b) SCR system.

Fig. 13(b) shows the three-phase SCR unit, including the boost converter for each unit. Table IV summarizes the employed modules in the implemented prototypes.

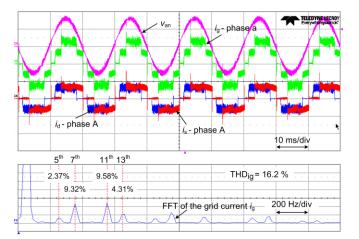

Fig. 14 shows the performance of the two-rectifier system with a flat current modulation, where the firing angle for the SCR unit is set to  $36^{\circ}$  for comparison and the input power is also measured ( $P_{\rm in} \approx 6$  kW). It can be seen that a relatively low  $5^{\rm th}$ -order harmonic (0.3 A, i.e., 2.37 % of the fundamental) is achieved by introducing a phase-shift of  $36^{\circ}$  for the SCR unit. Moreover, the THD of the input grid current is around 16.2 %. When compared with the simulations, the experimental results are in a close agreement with those shown Fig. 7.

The occurrence of the current spikes in the SCR current

TABLE IV

EMPLOYED MODULES IN THE IMPLEMENTED PROTOTYPES.

| Module                      | Part-Number   | Qty |

|-----------------------------|---------------|-----|

| Three-phase diode rectifier | SKD30         | 1   |

| Three-phase SCR             | SKKT 106/16   | 3   |

| IGBT-diode                  | SK60GAL125    | 2   |

| IGBT gate drive             | Skyper 32-pro | 2   |

| SCR triggering circuit      | RT380T        | 1   |

| Current measurement         | HX-15         | 2   |

| Voltage measurement         | LV25-P        | 4   |

| Controller                  | TMS320F28335  | 2   |

Fig. 14. Experimental results (phase a) of the multi-drive system with a flat-current modulation at  $\alpha_f = 36^\circ$ ,  $P_{\rm in} \approx 6$  kW,  $V_{\rm o} = 700$  V: grid current  $i_{\rm g}$  [10 A/div], grid phase voltage  $v_{\rm an}$  [200 V/div], diode rectifier input current  $i_{\rm d}$  [10 A/div], SCR unit input current  $i_{\rm s}$  [10 A/div], and Fast Fourier Transform (FFT) analysis of the grid current [500 mA/div].

(e.g.,  $i_s$ ) at the point of commutation is due to the presence of the snubber branches in the SCR unit. In practice, to avoid SCR unit failure and to reduce the overvoltage to a reasonable limit, an RC snubber branch is connected across each thyristor. In order to damp the current spikes, small AC-side inductors can be placed in series prior to the SCR unit.

In order to further verify the effect of phase-shifting operation of the SCR unit on the power quality of the grid currents, more tests have been conducted on the same system with different phase-shifting angles (i.e., firing angles). The results are shown in Fig. 15 and it is also compared with the simulation results shown in Fig. 8. It can be observed in Fig. 15 that the lowest THD<sub>i</sub> (i.e., 16.04 %) is achieved with a relatively large PF of 0.94 when  $a_f = 36^\circ$ . The results are in good consistence with the simulation results. The above tests have validated that by introducing an appropriate phase-shift to the SCR unit, a lower THD<sub>i</sub> and/or a minimization of the low order harmonics can be achieved.

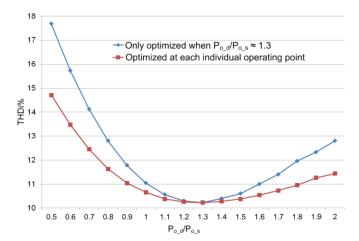

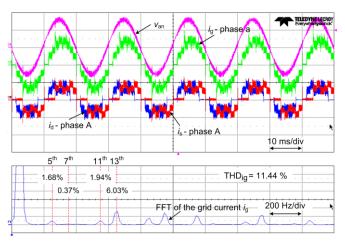

Furthermore, the novel current modulation scheme is then applied to the two-rectifier system in order to increase the control flexibility in terms of minimizing the selected harmonics of interest and also the  $THD_i$  (i.e., Table III). Firstly, the control objective is to lower the  $THD_i$  and also to reduce the  $5^{th}$ ,  $7^{th}$ , and  $11^{th}$  harmonics, where thus the optimization algorithm is also used. Fig. 16 demonstrates the

Fig. 15. Experimental results of the multi-drive system with different firing angles for the SCR unit: (a) total harmonic distortion of the input current  $i_g$  and (b) power factor.

(b)

performance of the multi-drive system equipped with the novel modulation technique, which targets not only a lower THD<sub>i</sub> but also an elimination of the low order harmonics. It can be seen in Fig. 16 that the 5<sup>th</sup>, 7<sup>th</sup>, and 11<sup>th</sup> order harmonics are almost completely eliminated, since they are considered in the optimization function as shown in (11). In addition, a THD<sub>i</sub> of 11.5 % of the grid current is also obtained when applying the novel modulation scheme to both rectifier units, which is better than the case of only using the flat current modulation.

In order to further demonstrate the flexibility of the novel modulation scheme, another test has been carried out on the system. In this case, the optimization target is to only minimize the THD<sub>i</sub>. Fig. 17 presents the performance of the multirectifier system with a control objective to lower the THD<sub>i</sub>, where it shows that around 1.5% reduction of the THD<sub>i</sub> has been achieved compared to the case shown in Fig. 16. At the same time, the low order harmonics are at relatively low levels. The results are quite in agreement with the simulations. To sum up, both the experimental tests and the simulations have validated the effectiveness of current harmonic mitigations in multi-rectifier systems by means of: a) phase-shifting the currents drawn by SCR units and b) a novel current modulation scheme at the DC-link using a DC-DC converter.

Fig. 16. Experimental results (phase a) of the multi-drive system with the novel current modulation scheme at  $P_{\rm in}\approx 6$  kW,  $V_{\rm o}=700$  V, targeting at reducing the low order harmonics and also a lower THD<sub>i</sub>: grid current  $i_{\rm g}$  [10 A/div], grid phase voltage  $v_{\rm an}$  [200 V/div], diode rectifier input current  $i_{\rm d}$  [10 A/div], SCR unit input current  $i_{\rm s}$  [10 A/div], and Fast Fourier Transform (FFT) analysis of the grid current [500 mA/div].

Fig. 17. Experimental results (phase a) of the multi-drive system with the novel current modulation scheme at  $P_{\rm in} \approx 5.85$  kW,  $V_{\rm o} = 700$  V, targeting at a minimized THD<sub>i</sub>: grid current  $i_{\rm g}$  [10 A/div], grid phase voltage  $v_{\rm an}$  [200 V/div], diode rectifier input current  $i_{\rm d}$  [10 A/div], SCR unit input current  $i_{\rm s}$  [10 A/div], and Fast Fourier Transform (FFT) analysis of the grid current [500 mA/div].

Those can significantly contribute to a good power quality in both the single-drive and the multi-drive systems.

### V. CONCLUSION

In this paper, a new harmonic elimination approach by combining different non-linear loads has been proposed for three-phase multi-drive systems, where also Silicon Controlled Rectifiers (SCR) are adopted. The proposed method can enable the selected harmonic cancellation by adjusting the phase angle of the SCR, and thus it can contribute to an improved power quality of the main grid. Moreover, in order to further reduce the harmonics, a novel modulation scheme has been applied to the DC-DC converter at the DC-link of the drive system. The modulation scheme is able to eliminate the

harmonics of interest by adding or subtracting specific current levels with respect to the conventional modulation approach. As a consequence, the combination of multiple non-linear loads with the new modulation scheme offers much flexibility as well as cost-effectiveness for the multi-drive systems in terms of harmonic elimination. A main advantage of the proposed method is that the harmonic distribution remains the same regardless of load profile variations.

In order to maximize the system efficiency, the added boost converter at the DC-link of the front-end rectifier should be optimized. Design and optimization of the traditional boost converter has been studied extensively in the past years. However, the traditional boost topology efficiency can be improved to a limited extent, as it should be designed for the total output power. Therefore, the future work will be focused on investigating alternative topologies and smart control strategies to minimize the power losses covering a wide range of power levels.

### REFERENCES

- P. Waide and C. Brunner, "Energy-Efficiency Policy Opportunities for Electric Motor-Driven Systems," *International Energy Agency Working Paper, Energy Efficiency Series*, 2011.

- [2] B.K. Bose, B.K., "Power electronics and motor drives recent progress and perspective," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 581-588, 2009.

- [3] J.W. Gray and F. J. Haydock, "Industrial power quality considerations when installing adjustable speed drive systems," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 646-652, May/Jun 1996.

- [4] D. Kumar and F. Zare, "Analysis of harmonic mitigations using hybrid passive filters," in *Proc. of PEMC*, 2014, pp. 945-951, 21-24 Sept. 2014.

- [5] F. Zare, "Harmonics issues of three-phase diode rectifiers with a small DC link capacitor," in *Proc. of PEMC*, 2014, pp. 912-917, 21-24 Sept. 2014.

- [6] G.K. Andersen and F. Blaabjerg, "Current programmed control of a single-phase two-switch buck-boost power factor correction circuit," *IEEE Trans. Ind. Electron.*, vol. 53, no. 1, pp. 263-271, Feb. 2006.

- [7] J. W. Kolar and T. Friedli, "The Essence of Three-Phase PFC Rectifier Systems - Part I," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 176-198, Jan. 2013.

- [8] F. Zare, "A novel harmonic elimination method for a three-phase diode rectifier with controlled DC link current," in *Proc. of PEMC*, 2014, pp. 985-989, 2014.

- [9] C. Klumpner, F. Blaabjerg, and P. Thogersen, "Converter topologies with low passive components usage for the next generation of integrated motor drives," in *Proc. of PESC*, vol. 2, pp. 568-573, 2003.

- [10] H. Akagi and K. Isozaki, "A hybrid active filter for a three-phase 12-pulse diode rectifier used as the front end of a medium-voltage motor drive," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 69-77, Jan. 2012.

- [11] M. Liserre, A. Dell'Aquila, and F. Blaabjerg, "An overview of three-phase voltage source active rectifiers interfacing the utility," in *Proc. of Power Tech Conf.*, pp. 1-8, vol. 3, 2003.

- [12] M. Liserre, F. Blaabjerg, and S. Hansen, "Design and control of an LCL-filter-based three-phase active rectifier," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1281-1291, 2005.

- [13] H. Akagi, "Modern active filters and traditional passive filter," Bulletin of the polish academy of sciences technical sciences, vol. 54, 2006.

- [14] J. W. Kolar and H. Ertl, "Status of the techniques of three-phase rectifier systems with low effects on the mains," in *Proc. of Telecommunication Energy Conf.*, pp. 1-16, 1999.

- [15] S. Hansen, P. N. Enjeti, H. Jae Hong, and F. Blaabjerg, "An integrated single-switch approach to improve harmonic performance of standard PWM adjustable speed drives," in *Proc. of IAS Annual Meeting*, vol. 2, pp. 789-795, 1999.

- [16] S. Hansen, P. Nielsen, and F. Blaabjerg, "Harmonic cancellation by mixing nonlinear single-phase and three-phase loads," *IEEE Trans. Ind. Appl.*, vol. 36, no. 1, pp. 152-159, Jan/Feb 2000.

- [17] S. Choi, B.S. Lee, and P.N. Enjeti, "New 24-pulse diode rectifier systems for utility interface of high-power AC motor drives," *IEEE Trans. Ind. Appl.* vol. 33, no. 2, pp. 531-541, Mar./Apr. 1997.

- [18] K. Mino, M. L. Heldwein, and J. W. Kolar, "Ultra compact three-phase rectifier with electronic smoothing inductor," in *Proc. of APEC*, 2005, pp. 522-528, 2005.

- [19] J. Salmon and D. Koval, "Improving the operation of 3-phase diode rectifiers using an asymmetrical half-bridge DC-link active filter," in *Proc. of IAS Annual Meeting*, vol. 4, pp. 2115-2122, 2000.

- [20] P. J. Grbovic, P. Delarue, and P. Le Moigne, "A Novel Three-Phase Diode Boost Rectifier Using Hybrid Half-DC-Bus-Voltage Rated Boost Converter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1316-1329, 2011.

- [21] C. Galea and L. Asiminoaei, "New topology of electronic smoothing inductor used in three phase electric drives," in *Proc. of EPQU*, pp. 1-6, 2011.

- [22] L. G. Franquelo, J. Napoles, R. C. P. Guisado, J. I. Leon, and M. A. Aguirre, "A Flexible Selective Harmonic Mitigation Technique to Meet Grid Codes in Three-Level PWM Converters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 3022-3029, 2007.

- [23] T. Nussbaumer, K. Raggl, and J.W. Kolar, "Design Guidelines for Interleaved Single-Phase Boost PFC Circuits," *IEEE Trans. Ind. Electron.*, vol.56, no.7, pp.2559-2573, July 2009.

- [24] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A New Single-Phase PLL Structure Based on Second Order Generalized Integrator," in *Proc.* of PESC, 2006, pp. 1-6, 18-22 June 2006.

- [25] N. Mohan, T.M. Undeland, and W.P. Robbins. Power Electronics: Converters, Applications, and Design. John Wiley & Sons, 2007.

Pooya Davari (S'11–M'13) received B.Sc. and M.Sc. degrees in electronic engineering from the University of Mazandaran (Noushirvani), Babol, Iran, in 2004, 2008, respectively and the Ph.D. degree in power electronics from the Queensland University of Technology (QUT), Brisbane, Australia in 2013. From 2005 to 2010 he was involved in several electronics and power electronics projects as a Development Engineer. During 2010-2014, he has designed and developed high-power high-voltage power electronic systems for multi-disciplinary

projects such as ultrasound application, exhaust gas emission reduction and tissue-materials sterilization. From 2013 to 2014 he was with Queensland University of Technology, Brisbane, Australia, as a Lecturer.

Currently, Dr. Davari is with the Department of Energy Technology at Aalborg University as a Postdoctoral Researcher. His research interests include active front-end rectifiers, harmonic mitigation in adjustable speed drives, EMC/EMI in power electronics, and pulsed power applications.

Yongheng Yang (S'12–M'15) received his B.Eng. degree in 2009 from Northwestern Polytechnical University, China, and the Ph.D. degree from Aalborg University, Denmark, in 2014. During 2009-2011, he was with Southeast University, Nanjing, China as a postgraduate, where he worked on modeling and control of single-phase grid-connected PV systems. From March to May 2013, he was a Visiting Scholar at the Department of Electrical and Computer Engineering at Texas A&M University, USA.

Currently, Dr. Yang is with the Department of Energy Technology at Aalborg University as a Postdoc Researcher. He is also involved in the IEEE Industry Applications Society student activities, and the IEEE Power Electronics Society Young Professionals activities. He serves as a Guest Associate Editor of IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS Special Issue on Power Electronics for Energy Efficient Buildings. His research is focused on grid integration and control of renewable energy systems, including PV systems, and harmonics in power converters. Dr. Yang is also working on the reliability of power electronics.

Firuz Zare (S'98-M'01-SM'06) received his Ph.D. in Power Electronics from Queensland University of Technology in 2002. He has spent several years in industry as a team leader and development engineer working on power electronics and power quality projects. Dr. Zare won a student paper prize at the Australian Universities Power Engineering Conference (AUPEC) conference in 2001 and was awarded a Symposium Fellowship by the Australian Academy of Technological Science and

Engineering in 2001. He received the Vice Chancellor's research award in 2009 and faculty excellence award in research as an early career academic from Queensland University of Technology in 2007.

Dr. Zare has published over 150 journal and conference papers and technical reports in the area of power electronics. He is currently a Lead Engineer with Danfoss Power Electronics, Graasten, Denmark. He is a Task Force Leader of Active Infeed Converters within Working Group one at the IEC Standardization Committee. His current research interests include problem-based learning in power electronics, power electronics topologies and control, pulsewidth modulation techniques, EMC/EMI in power electronics, and renewable energy systems.

Frede Blaabjerg (S'86-M'88-SM'97-F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he was a Ph.D. Student with Aalborg University, Aalborg, Denmark. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor in power electronics and drives since 1998 at Aalborg University. He has been a part-time Research Leader with the Research Center Risoe working with wind turbines. In 2006-2010, he was the Dean of the Faculty of Engineering,

Science and Medicine. His research areas are in power electronics and its applications such as wind turbines, photovoltaic systems, and adjustable speed drives.

Prof. Blaabjerg has received 15 IEEE Prize Paper Awards, the IEEE Power Electronics Society (PELS) Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award in 2014, and the Villum Kann Rasmussen Research Award 2014. He was an Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been a Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011. He was nominated in 2014 by Thomson Reuters to be among the most 250 cited researchers in Engineering in the world.