### **Aalborg Universitet**

#### Small-Signal Modeling, Stability Analysis and Design Optimization of Single-Phase **Delay-Based PLLs**

Golestan, Saeed; Guerrero, Josep M.; Vidal, Ana; Yepes, Alejandro G.; Doval-Gandoy, Jesus; Freijedo Fernandez, Francisco Daniel

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2015.2462082

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Golestan, S., Guerrero, J. M., Vidal, A., Yepes, A. G., Doval-Gandoy, J., & Freijedo Fernandez, F. D. (2016).

Small-Signal Modeling, Stability Analysis and Design Optimization of Single-Phase Delay-Based PLLs. I E E Transactions on Power Electronics, 31(5), 3517-3527. https://doi.org/10.1109/TPEL.2015.2462082

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 15, 2025

# Small-Signal Modeling, Stability Analysis and Design Optimization of Single-Phase Delay-Based PLLs

Saeed Golestan, Senior Member, IEEE, Josep M. Guerrero, Fellow, IEEE, Ana Vidal, Student Member, IEEE, Alejandro G. Yepes, Member, IEEE, Jesus Doval-Gandoy, Member, IEEE, and Francisco D. Freijedo, Member, IEEE

Abstract—Generally speaking, designing single-phase phaselocked loops (PLLs) is more complicated than three-phase ones, as their implementation often involves the generation of a fictitious orthogonal signal for the frame transformation. In recent years, many approaches to generate the orthogonal signal have been proposed, the simplest perhaps being the transfer delay based method. In the transfer delay based PLL (TD-PLL), the orthogonal signal is generated by delaying the original singlephase signal by T/4 (one-quarter of a period). The phase shift caused by the transfer delay block, however, will not be exactly 90° under off-nominal grid frequencies, which results in errors in the estimated quantities by the TD-PLL. To alleviate this issue, an improved version of TD-PLL, called the non-frequency dependent TD-PLL (NTD-PLL), has recently been proposed. The NTD-PLL uses another T/4 delay unit in its feedback path to make the PLL immune to grid frequency variations. To the best of the authors' knowledge, the accurate small-signal modeling of the TD-PLL and NTD-PLL has not yet been carried out, and no detailed analysis of their performance has been presented. The main aim of this paper is to address these issues and explore new methods to enhance their performance. The stability analysis, control design guidelines and performance comparison with the state-of-the-art PLLs are presented as well.

Index Terms—Orthogonal signal generator, phase-locked loop (PLL), synchronization.

#### I. INTRODUCTION

A phase-locked loop (PLL) is a negative-feedback system that tries to generate a sinusoidal signal with the same phase and frequency as its input signal [1]. PLLs are now widely used for synchronization and control purposes in the areas of electrical machines, power distribution systems and power electronics thanks to the great advantages that they offer, such as their ease of digital implementation, effectiveness and robustness [2]-[4]. The phase detector (PD), the loop filter and

This work was supported in part by the Research Programme on Microgrids, Department of Energy Technology, Aalborg university, in part by the Spanish Ministry of Science and Innovation, and in part by the European Commission, European Regional Development Fund (ERDF) under Project DPI2012-31283.

Copyright © 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

S. Golestan, J. M. Guerrero, and F. D. Freijedo are with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: s.golestan@ieee.org; joz@et.aau.dk; fran@et.aau.dk;).

A. Vidal, A G. Yepes, and J. Doval-Gandoy are with the Department of Electronics Technology, University of Vigo, Vigo 36310, Spain (e-mail: anavidal@uvigo.es; agyepes@uvigo.es; jdoval@uvigo.es).

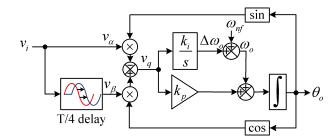

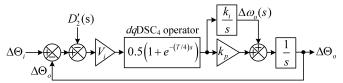

Fig. 1. Schematic of the TD-PLL.

the voltage controlled oscillator are three basic parts of almost all PLLs [1].

In recent years, many single-phase PLLs have been designed by different researchers. The main difference among these PLLs typically lies in the implementation of their PDs. A mixer, also called the product type PD, is probably the simplest option [1]. This PD generates the phase error information by multiplying the PLL input signal by the PLL output. This multiplication, nevertheless, causes a double frequency component at the mixer output, which results in double frequency ripples on the quantities estimated by the PLL [5]. To deal with this problem of product type PDs, including double frequency decoupling networks into the PLL structure is suggested in [6]-[8].

The orthogonal signal generation (OSG) based PDs are presumably the most popular PDs in single-phase PLLs. The main difference among these PDs typically lies in the technique they use to create the orthogonal signal. The transfer delay [9], [10], all-pass filter [11], Hilbert transform [12], Kalman filter [13], second order generalized integrator [14], [15] and inverse Park technique [5], [15] are the most common methods to create the orthogonal signal.

Using the transfer delay is probably the simplest method to generate the orthogonal signal. Fig. 1 shows the schematic diagram of the single-phase transfer delay based PLL (TD-PLL). As illustrated in this figure, the orthogonal signal is generated by delaying the original single-phase signal by T/4, where T is the grid fundamental period. This approach, however, suffers from high sensitivity to the grid frequency variations, because the phase shift caused by the transfer delay will not be exactly  $90^{\circ}$  in the presence of frequency drifts. To deal with this problem, the frequency estimated by the PLL can be fed

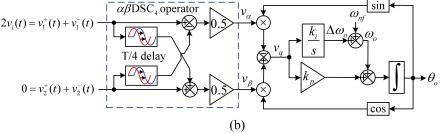

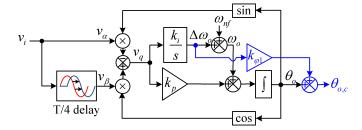

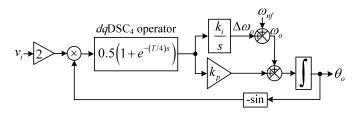

Fig. 2. Block diagram of the NTD-PLL.

back to the delay block to make it frequency adaptive. This frequency feedback loop, nevertheless, makes the PLL highly nonlinear. In this condition, it is rather difficult to analyse the PLL and ensure its stability under all circumstances [16]. Recently, another approach has been proposed in [17] and [18] to tackle this problem. In this method, as shown in Fig. 2, the TD-PLL uses another delay block in the feedback loop to generate  $\cos(\theta_o)$  from  $\sin(\theta_o)$ , where  $\theta_o$  is the phase estimated by the PLL. This PLL structure is called the non-frequency dependent TD-PLL (NTD-PLL).

In this paper, for the first time, the accurate small-signal modeling of the TD-PLL and NTD-PLL is presented. A detailed analysis of the performance of these PLLs is then carried out and some approaches to enhance their performance are presented. The stability analysis, control design guidelines, and performance comparison with the state-of-the-art PLLs are other contributions of this paper.

#### II. TD-PLL

#### A. Small-Signal Modeling

For the sake of simplicity in the modeling procedure, let the TD-PLL input voltage,  $v_i$ , be clean and undistorted as

$$v_i(t) = v_{\alpha}(t) = V_i \cos(\theta_i) \tag{1}$$

where  $V_i$  is the input voltage amplitude and

$$\theta_i = \int \omega_i dt = \omega_{nf} t + \underbrace{\int \Delta \omega_i dt}_{\Delta \theta}$$

(2)

is the grid voltage phase, while  $\omega_i = \omega_{nf} + \Delta\omega_i$ ,  $\omega_{nf} = 2\pi/T$  and  $\Delta\omega_i$  denote the grid frequency, the nominal value of grid frequency and the deviation of grid frequency from its nominal value, respectively. Assuming a constant value for the grid frequency, the  $\beta$ -axis voltage (i.e., the delay block output signal) can be expressed as

$$v_{\beta}(t) = v_{i} \left( t - \frac{T}{4} \right) = V_{i} \cos \left( \theta_{i} - \frac{\omega_{i} T}{4} \right)$$

$$= V_{i} \cos \left( \theta_{i} - \frac{\pi}{2} - \frac{\Delta \omega_{i} T}{4} \right)$$

$$= V_{i} \sin \left( \theta_{i} - \frac{\Delta \omega_{i} T}{4} \right). \tag{3}$$

Using Fig. 1, (1) and (3), the proportional-integral (PI)

2

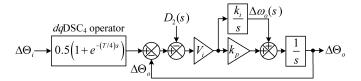

Fig. 3. Small-signal model of the TD-PLL.

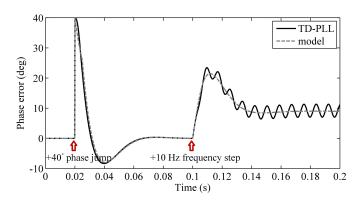

Fig. 4. Accuracy assessment of the TD-PLL small-signal model.

controller input signal,  $v_q$ , can be obtained as

$$v_{q}(t) = -v_{\alpha}(t)\sin(\theta_{o}) + v_{\beta}(t)\cos(\theta_{o})$$

$$= \frac{V_{i}}{2}\sin(\theta_{i} - \theta_{o}) + \frac{V_{i}}{2}\sin\left(\theta_{i} - \frac{\Delta\omega_{i}T}{4} - \theta_{o}\right)$$

$$-V_{i}\underbrace{\left[\frac{1}{2}\sin(\theta_{i} + \theta_{o}) - \frac{1}{2}\sin\left(\theta_{i} - \frac{\Delta\omega_{i}T}{4} + \theta_{o}\right)\right]}_{D_{2}(t)}(4)$$

where  $\theta_o = \omega_{nf}t + \Delta\theta_o$ , as mentioned before, is the phase estimated by the PLL and  $D_2(t)$  denotes a double frequency term. Notice that  $D_2(t)$  is equal to zero when the grid frequency is at its nominal value, i.e., when  $\Delta\omega_i = 0$ .

Under a quasi-locked state, (4) can be approximated by

$$v_{q}(t) \approx \frac{V_{i}}{2} (\theta_{i} - \theta_{o}) + \frac{V_{i}}{2} \left(\theta_{i} - \frac{\Delta\omega_{i}T}{4} - \theta_{o}\right) - V_{i}D_{2}(t)$$

$$= \frac{V_{i}}{2} (\Delta\theta_{i} - \Delta\theta_{o}) + \frac{V_{i}}{2} \left(\Delta\theta_{i} - \frac{\Delta\omega_{i}T}{4} - \Delta\theta_{o}\right)$$

$$-V_{i}D_{2}(t). \tag{5}$$

Taking the Laplace transform from both sides of (5) gives

$$v_q(s) \approx V_i \left[ \left( \frac{1 + e^{-sT/4}}{2} \right) \Delta\Theta_i - \Delta\Theta_o - D_2(s) \right]$$

(6)

where  $\Delta\Theta_i$  and  $\Delta\Theta_o$  denote the Laplace transform of  $\Delta\theta_i$  and  $\Delta\theta_o$ , respectively.

Using (6) and Fig. 1, the small-signal model of the TD-PLL can be obtained as shown in Fig. 3. As it can be seen, the dynamics of the delay based OSG in the TD-PLL is modeled by what is known as the dq-frame delayed signal cancellation (dqDSC) operator [19]-[21]. This operator is a finite impulse response (FIR) filter that is defined in general form as

$$dq DSC_n(s) = \frac{1 + e^{-\frac{T}{n}s}}{2} \tag{7}$$

Fig. 5. Alternative mathematically equivalent representations of the TD-PLL.

where n is the operator delay factor.

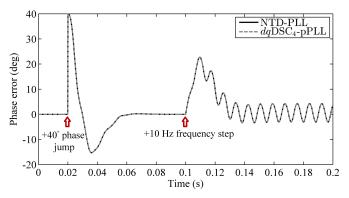

To evaluate the model accuracy, any arbitrary values can be assigned to the proportional and integral gains  $k_p$  and  $k_i$ . Here,  $k_p=180$  and  $k_i=2500$  are selected. For the sake of simplicity, the double frequency disturbance input to the model is neglected. A phase-angle jump of  $+40^{\circ}$  and subsequently an exaggeratedly large frequency jump (+10 Hz) are programmed for the model accuracy assessment, whose results are shown in Fig. 4. It can be observed that the derived model accurately predicts the TD-PLL behavior.

The major drawbacks of the TD-PLL, i.e., its non-zero average phase error and its double frequency oscillatory error in the presence of frequency drifts, are also evident from Fig. 4. To remove these errors, as mentioned before, the frequency estimated by the TD-PLL can be fed back to the delay block to make it frequency adaptive. Such frequency feedback loop, however, makes the TD-PLL highly nonlinear. In this condition, it is rather difficult to evaluate and ensure the TD-PLL stability under all circumstances. Achieving a zero phase-error for the TD-PLL without using a frequency-feedback loop is discussed in the next sections.

## B. Performance Enhancement Under Frequency-Varying Conditions

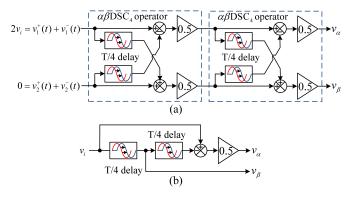

Let the single-phase input signal of the TD-PLL be as expressed in (1). Considering that a single-phase system is an unbalanced two-phase system, alternative mathematically equivalent representations of the TD-PLL can be obtained as shown in Fig. 5, in which  $v_1^+$  and  $v_2^+$  denote the positive-sequence components of the unbalanced two-phase system and  $v_1^-$  and  $v_2^-$  indicate its negative-sequence components. The system inside the dashed box is a well-known FIR filter called the  $\alpha\beta$ -frame DSC ( $\alpha\beta$ DSC) operator [22]. The s-domain transfer function of this operator in general form is as follows:

$$\alpha\beta \mathrm{DSC}_n(s) = \frac{1 + e^{\frac{j2\pi}{n}} e^{-\frac{T}{n}s}}{2}$$

(8)

3

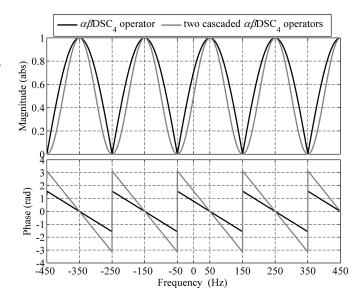

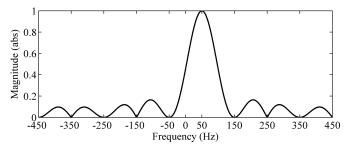

Fig. 6. Frequency response of the  $\alpha\beta DSC_4$  operator (dark line) and two cascaded  $\alpha\beta DSC_4$  operators (gray line).

where n, as defined before, is the delay factor. In our case, the delay factor n is equal to 4.

The dark line in Fig. 6 shows the frequency response of the  $\alpha\beta DSC_4$  operator. It can be observed that the  $\alpha\beta DSC_4$  operator has unity gain and zero phase shift at +50 Hz, and zero gain at -50 Hz. This means that the  $\alpha\beta DSC_4$  operator [the dashed box in Fig. 5(b)] passes the fundamental-frequency positive-sequence (FFPS) component and blocks the fundamental-frequency negative-sequence (FFNS) one when the grid frequency is at its nominal value, i.e., 50 Hz. In the presence of frequency drifts, nevertheless, this operator is unable to completely block the FFNS component. It also causes a phase shift in the FFPS component. That is the reason why the TD-PLL suffers from a double frequency oscillatory error and a non-zero average phase error under off-nominal

Fig. 7. TD-PLL with phase error compensator.

Fig. 8. (a) Two cascaded  $\alpha\beta DSC_4$  operators and (b) its mathematically equivalent structure.

grid frequencies.

Using (8), the phase shift caused by the  $\alpha\beta DSC_4$  operator at the fundamental frequency of positive sequence can be calculated as

$$\angle \alpha \beta \text{DSC}_4(j\omega_i) = -\left(\frac{\omega_i T}{8} - \frac{\pi}{4}\right).$$

(9)

Substituting  $\omega_i = \omega_{nf} + \Delta\omega_i$  into (9) and performing some mathematical manipulations yields

$$\angle \alpha \beta \text{DSC}_4(j\omega_i) = -\underbrace{\left(\frac{T}{8}\right)}_{k_{col}} \Delta \omega_i.$$

(10)

As (10) shows, the phase shift caused by the  $\alpha\beta DSC_4$  operator depends on  $\Delta\omega_i$ . Therefore, correcting this phase shift requires an estimation of  $\Delta\omega_i$ . Fortunately, the integral action of the PI controller provides an estimation of  $\Delta\omega_i$ . Therefore, the TD-PLL non-zero average phase error can be easily corrected by multiplying the PI controller integral output (i.e.,  $\Delta\omega_o$ ) by  $k_{\varphi 1}=T/8$  and adding the result to the TD-PLL output, as shown in Fig. 7. It should be mentioned here that correcting the phase shift caused by the PLL prefiltering stage at the PLL output has been first proposed in [23].

Adding this compensator, as it will be confirmed numerically later, enables the TD-PLL to achieve a zero average phase error in the presence of frequency drifts. However, it has no effect on its double frequency oscillatory error. This error, as mentioned before, is due to imperfect cancellation of the FFNS component by the  $\alpha\beta DSC_4$  operator under offnominal grid frequencies. An easy yet effective approach to deal with this problem is the repeated passes of the signal through the identical filter [24] as shown in Fig. 8(a), which

Fig. 9. TD-PLL with two-stage  $\alpha\beta \mathrm{DSC_4}$  operator and phase-error compensator.

Fig. 10. Resultant magnitude frequency response of cascading  $\alpha\beta DSC_8$  and  $\alpha\beta DSC_{16}$  operators with two  $\alpha\beta DSC_4$  operators.

is mathematically equivalent to the structure depicted in Fig. 8(b). The effectiveness of this approach can be better visualized by obtaining the frequency response of two cascaded  $\alpha\beta \mathrm{DSC_4}$  operators, which is shown by a gray line in Fig. 6. As it can be observed, two cascaded  $\alpha\beta \mathrm{DSC_4}$  operators provide a wider notch around -50 Hz compared to the single  $\alpha\beta \mathrm{DSC_4}$  operator and, therefore, can more effectively reject the FFNS component in the presence of frequency drifts.

The phase error caused by the cascaded  $\alpha\beta DSC_4$  operators under off-nominal frequencies can be compensated for in the same manner as shown in Fig. 7; however, it should be noticed that the phase error compensator gain in this case is twice that of the previous case, i.e.,  $k_{\varphi_2}=2k_{\varphi 1}=T/4$ . Fig. 9 shows the schematic of TD-PLL with two-stage  $\alpha\beta DSC_4$  operator and phase-error compensator.

It should be mentioned that a similar structure to the one in Fig. 9, but without the phase error compensator can be found in [25]. Such structure, consequently, is not able to track the grid phase-angle in the presence of frequency drifts and, therefore, it can only be used in applications where the grid frequency is fixed at (or very close to) its nominal value.

## C. Performance Enhancement Under Harmonically-Distorted Condition

As shown in Fig. 6, the two cascaded  $\alpha\beta DSC_4$  operators block the odd harmonics of order h=4k-1 ( $k=\pm 1,\pm 2,\pm 3,\ldots$ ) and slightly attenuate the even harmonics, but leave other odd harmonics unchanged. This means that they have a limited harmonic filtering capability. Therefore, additional  $\alpha\beta DSC$  operators with appropriate delay factors should be cascaded with them to improve their filtering capability. Selecting these additional operators should be made based on the grid harmonic pattern and application in hand. In this paper, the presence of even harmonics is neglected. In such scenario, cascading  $\alpha\beta DSC_8$  and  $\alpha\beta DSC_{16}$  operators with two  $\alpha\beta DSC_4$  operators, which results in the magnitude

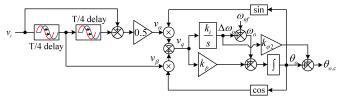

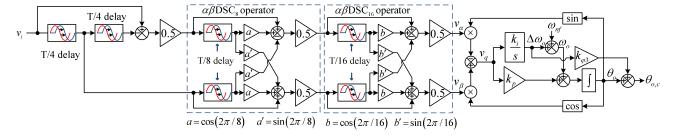

Fig. 11. ETD-PLL.

Fig. 12. Small-signal model of the ETD-PLL.

frequency response shown in Fig. 10, is good enough. For those applications where the even harmonics are not negligible, using  $\alpha\beta DSC_2$  operator may also be required. More detailed information about selecting  $\alpha\beta DSC$  operators for different grid scenarios can be found in [19], [20].

Including these additional operators into the TD-PLL results in the structure illustrated in Fig. 11. For the sake of brevity, this structure is called the enhanced TD-PLL (ETD-PLL). The phase error compensator gain in the ETD-PLL, as calculated in (11), is  $k_{\varphi 3} = \frac{11T}{32}$ :

$$\angle \left\{ \left[ \alpha \beta \text{DSC}_4(j\omega_i) \right]^2 \alpha \beta \text{DSC}_8(j\omega_i) \ \alpha \beta \text{DSC}_{16}(j\omega_i) \right\}$$

$$= -\underbrace{\frac{11T}{32}}_{k_{\varphi 3}} \Delta \omega_i. \quad (11)$$

#### D. Stability Analysis and Parameter Design Guidelines

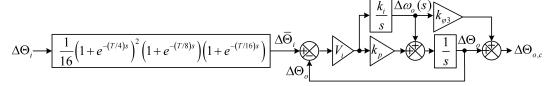

Fig. 12 shows the ETD-PLL small-signal model, which can be obtained by following the same procedure used for deriving the TD-PLL model. The presence of double frequency disturbance input to the model is neglected as the two-stage  $\alpha\beta DSC_4$  operator effectively suppresses it.

Using Fig. 12, the ETD-PLL open-loop<sup>1</sup> and closed-loop transfer functions can be obtained as

$$G_{ol}(s) = \frac{\Delta\Theta_{o,c}}{\Delta\overline{\Theta}_i - \Delta\Theta_{o,c}} = \frac{V_i \left[ (k_p + k_i k_{\varphi 3}) \, s + k_i \right]}{s \left( s - V_i k_i k_{\varphi 3} \right)} \quad (12)$$

$$G_{cl}(s) = \frac{\Delta\Theta_{o,c}}{\Delta\Theta_i} = \frac{1}{16} \left( 1 + e^{-(T/4)s} \right)^2 \left( 1 + e^{-(T/8)s} \right)$$

$$\left( 1 + e^{-(T/16)s} \right) \frac{V_i \left[ (k_p + k_i k_{\varphi 3}) s + k_i \right]}{s^2 + V_i k_p s + V_i k_i}. \tag{13}$$

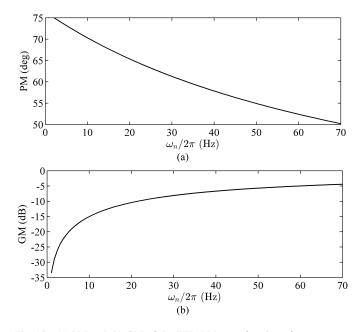

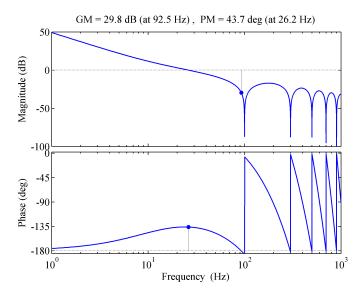

As (12) shows, the ETD-PLL has an unstable open-loop pole, which is created by the phase error compensator. This unstable pole makes the gain margin (GM) negative (in dB) and

<sup>1</sup>To derive the open-loop transfer function, the small-signal model should be rearranged to its classic feedback form.

adversely affects the phase margin (PM). Having a negative GM, however, does not mean that the ETD-PLL is unstable. Indeed, as the characteristic polynomial of (13) shows, the ETD-PLL is stable for positive values of  $k_p$  and  $k_i$ . The characteristic polynomial also indicates that the grid voltage amplitude variations affect the ETD-PLL dynamics. To avoid this, signals  $v_\alpha$  and  $v_\beta$  can be divided by an estimation of  $V_i$ , which can be calculated as  $\hat{V}_i = \sqrt{v_\alpha^2 + v_\beta^2}$ .

The proportional and integral gains  $k_p$  and  $k_i$  can be determined by defining  $k_p = 2\zeta\omega_n$  and  $k_i = \omega_n^2$ , where  $\zeta$  is the damping factor and  $\omega_n$  is the natural frequency, and selecting appropriate values for  $\zeta$  and  $\omega_n$ . Recommended values for the damping factor are  $\zeta = 0.707$  and  $\zeta = 1$ [26]. The latter is a more suitable choice for the ETD-PLL. The reason is that a higher value for  $\zeta$  compensates more effectively the negative effects of the phase-error compensator. Selecting the natural frequency  $\omega_n$ , on the other hand, involves a trade-off between the speed of response and the stability: Increasing  $\omega_n$  raises the PLL bandwidth and, therefore, makes its dynamic response fast, but degrades its stability margin as shown in Fig. 13. Here,  $\omega_n=2\pi 35$  rad/s is selected, which corresponds to a PM around  $60^{\circ}$ , a GM about -7 dB, and a 2\% settling time equal to around two cycles of the nominal frequency in response to phase-angle jumps and frequency steps. The selected values for  $\zeta$  and  $\omega_n$  result in  $k_p=440$ and  $k_i = 48361$ .

#### III. NTD-PLL

#### A. Small-Signal Modeling of NTD-PLL

The small-signal model of the NTD-PLL is derived under the same assumptions as those described in Section II-A.

Using Fig. 2, (1) and (3), the input signal of the NTD-PLL

Fig. 13. (a) PM and (b) GM of the ETD-PLL as a function of  $\omega_n$ .

PI controller can be obtained as

$$v_{q}(t) = -v_{\alpha}(t)\sin(\theta_{o}) - v_{\beta}(t)\sin\left(\theta_{o} - \frac{\omega_{o}T}{4}\right)$$

$$= \frac{V_{i}}{2}\sin(\theta_{i} - \theta_{o}) + \frac{V_{i}}{2}\sin\left(\left(\theta_{i} - \frac{\omega_{i}T}{4}\right) - \left(\theta_{o} - \frac{\omega_{o}T}{4}\right)\right)$$

$$-\frac{V_{i}}{2}\underbrace{\sin(\theta_{i} + \theta_{o})}_{D'_{2}(t)} - \frac{V_{i}}{2}\underbrace{\sin\left(\theta_{i} - \frac{\omega_{i}T}{4} + \theta_{o} - \frac{\omega_{o}T}{4}\right)}_{D'_{2}(t - T/4)}$$

$$(14)$$

where  $D'_2(t)$  denotes a double frequency term.

Under a quasi-locked state, (14) can be approximated by

$$v_{q}(t) \approx \frac{V_{i}}{2} \left[ (\theta_{i} - \theta_{o}) + \left( \theta_{i} - \frac{\omega_{i}T}{4} \right) - \left( \theta_{o} - \frac{\omega_{o}T}{4} \right) - D'_{2}(t) - D'_{2}(t - T/4) \right]$$

$$= \frac{V_{i}}{2} \left[ (\Delta \theta_{i} - \Delta \theta_{o}) + \left( \Delta \theta_{i} - \frac{\Delta \omega_{i}T}{4} \right) - \left( \Delta \theta_{o} - \frac{\Delta \omega_{o}T}{4} \right) - D'_{2}(t) - D'_{2}(t - T/4) \right]. (15)$$

Taking the Laplace Transform from (15) yields

$$v_q(s) \approx V_i \frac{1 + e^{-sT/4}}{2} \left[ \Delta \Theta_i - \Delta \Theta_o - D_2'(s) \right]. \tag{16}$$

Using (16) and Fig. 2, the small-signal model of the NTD-PLL can be obtained as shown in Fig. 14.

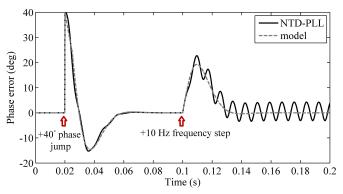

Fig. 15 checks out the small-signal model accuracy in the prediction of the NTD-PLL dynamic behavior. As shown, the model is very accurate.

Fig. 14. Small-signal model of the NTD-PLL.

Fig. 15. Accuracy assessment of the NTD-PLL small-signal model.

#### B. Stability Analysis and Parameter Design Guidelines

Using the NTD-PLL small-signal model, the open-loop transfer function can be obtained as

$$G_{ol}(s) = \frac{\Delta\Theta_o}{\Delta\Theta_i - \Delta\Theta_o} \bigg|_{D_2'(s) = 0} = V_i \frac{1 + e^{-(T/4)s}}{2} \frac{k_p s + k_i}{s^2}.$$

(17)

The delay term in the open-loop transfer function (17) complication  $-\frac{V_i}{2}\underbrace{\sin\left(\theta_i+\theta_o\right)}_{D_2'(t)}$   $-\frac{V_i}{2}\underbrace{\sin\left(\theta_i-\frac{\omega_i T}{4}+\theta_o-\frac{\omega_o T}{4}\right)}_{D_2'(t-T/4)}$  (14) cates the stability analysis and the parameter tuning procedure. For this purpose, the delay term in (17) is replaced by its first-order Padé approximation, i.e.,  $e^{-(T/4)s}\approx\frac{1-(T/8)s}{1+(T/8)s}$ , which results in

$$G_{ol}(s) \approx V_i \underbrace{\frac{1}{(T/8)} s + 1}_{T_d} \frac{k_p s + k_i}{s^2}.$$

(18)

Using the symmetrical optimum method [6], the integral and proportional gains  $k_i$  and  $k_p$  can be selected as

$$k_i = 1/\left(V_i g^3 T_d^2\right) k_p = 1/\left(V_i g T_d\right)$$

(19)

where g is a design constant which determines the PM of the PLL as  $PM = \tan^{-1}\left(\frac{g^2-1}{2g}\right)$ .

The recommended range of PM for stability of control systems is  $30^{\circ} \leq PM \leq 60^{\circ}$ . It is shown in [6] that  $PM = 45^{\circ}$  is the optimum choice, as this value minimizes the 2% settling time in response to phase-angle jumps. Therefore,  $PM = 45^{\circ}$  is selected, which corresponds to  $g = 1 + \sqrt{2}$ .

Once the design constant g is selected,  $k_p$  and  $k_i$  can be calculated from (19) as  $k_i=11371$  and  $k_p=166$ . Fig. 16 shows the open-loop Bode plot of the NTD-PLL using the selected values of  $k_p$  and  $k_i$ . It can be seen that the PM of PLL is very close to the intended value, i.e.,  $45^{\circ}$ , which confirms the accuracy of the suggested design procedure.

Fig. 16. Open-loop Bode plot of NTD-PLL.

Fig. 17. pPLL with in-loop dqDSC<sub>4</sub> operator.

#### C. A More Straightforward Implementation of NTD-PLL

The small-signal model of the NTD-PLL (Fig. 14) seems to be the same as the small-signal model of a power-based PLL (pPLL)<sup>2</sup> with an in-loop dqDSC<sub>4</sub> operator. Fig. 17 shows the schematic of this pPLL. Therefore, it is reasonable to say that the NTD-PLL and the pPLL with in-loop dqDSC<sub>4</sub> operator (briefly called the dqDSC<sub>4</sub>-pPLL) are mathematically equivalent. To support this fact, a performance comparison between the NTD-PLL and the dqDSC<sub>4</sub>-pPLL under the same condition as in Fig. 15 is carried out. Fig. 18 shows the obtained results. It can be observed that the NTD-PLL and the dqDSC<sub>4</sub>-pPLL have identical responses, which proves their equivalence. This equivalence implies that it is more straightforward and even computationally beneficial to use the dqDSC<sub>4</sub>-pPLL structure when the implementation of the NTD-PLL is intended.

## D. Performance Enhancement Under Frequency Varying and Harmonically Distorted Conditions

As Fig. 18 shows, the NTD-PLL and, therefore, its mathematically equivalent structure, i.e., the  $dq\mathrm{DSC_4}$ -pPLL, achieve a zero average phase error in the presence of a frequency drift, but they suffer from a double frequency oscillatory error in this condition. This problem, as recommended in [10], can be alleviated by including an additional  $dq\mathrm{DSC_4}$  operator into the  $dq\mathrm{DSC_4}$ -pPLL control loop. The harmonic

Fig. 18. A performance comparison between the NTD-PLL and the  $dq\mathrm{DSC_4}$ -pPLL.

filtering capability of this PLL is also rather low, and it can be improved by incorporating a  $dq \mathrm{DSC_8}$  operator and a  $dq \mathrm{DSC_{16}}$  operator into its control loop. Using these additional operators, however, causes a considerable phase delay in the PLL control loop, which significantly slows down its dynamic response. Therefore, this approach is only useful for specific applications where a slow and damped dynamic response for the PLL is needed. An example of such applications is described in [27]. Considering the limited application of such PLLs, this issue will not be further discussed here.

#### IV. SIMULATION AND EXPERIMENTAL RESULTS

In this section, the dynamic behavior and filtering capability of the ETD-PLL (Fig. 11) and NTD-PLL (Fig. 2) is evaluated through simulation and experimental results. Simulations are carried out in Matlab/Simulink environment and experimental results are obtained using a dSPACE MABXII DS1401 platform. Throughout the simulation and experimental studies, the sampling frequency and nominal grid frequency are considered to be 8 kHz and 50 Hz, respectively.

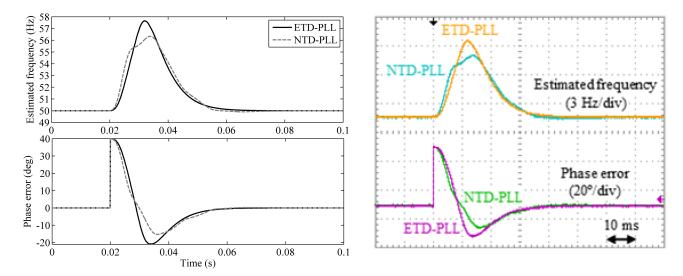

Fig. 19 shows the simulation and experimental results for the ETD-PLL and NTD-PLL in response to a  $+40^{\circ}$  phase-angle jump. It can be observed that both PLLs have comparable dynamic behaviors. The 2% settling time for both PLLs is around two cycles of the nominal frequency.

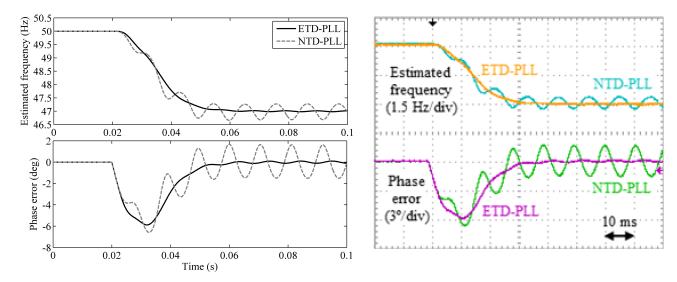

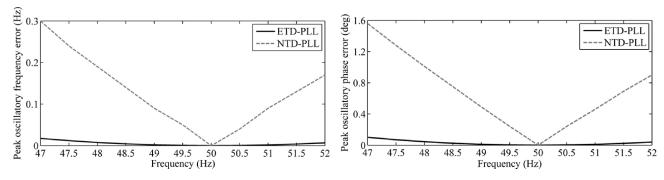

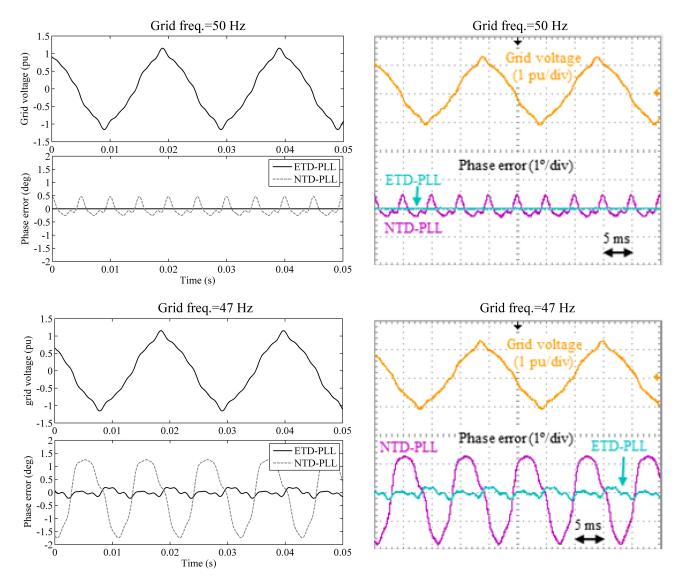

Fig. 20 illsutrates the ETD-PLL and NTD-PLL performance when the grid voltage frequency undergoes a step change of -3 Hz. Contrary to the NTD-PLL, which suffers from double frequency oscillatory errors, the ETD-PLL provides an accurate estimation of phase and frequency in this condition. To have a better view, Fig. 21 illustrates the magnitude of double frequency oscillatory errors in the phase and frequency estimated by the ETD-PLL and NTD-PLL as a function of the grid frequency. According to the EN50160 standard [28], the grid frequency variations are considered to be in the range of 47 to 52 Hz. These results highlight the high ability of ETD-PLL to reject double frequency errors in the presence of large frequency drifts. They also show that the NTD-PLL may not be a suitable choice for applications where the grid frequency deviation from its nominal value is high.

Fig. 22 evaluates the harmonic filtering capability of the ETD-PLL and NTD-PLL in the presence of 4% third har-

<sup>&</sup>lt;sup>2</sup>The pPLL is a standard single-phase PLL [5], [6], [15].

Fig. 19. Simulation and experimental results for the ETD-PLL and NTD-PLL in response to a  $+40^{\circ}$  phase-angle jump.

Fig. 20. Simulation and experimental results for the ETD-PLL and NTD-PLL in response to a -3 Hz frequency step change.

Fig. 21. Magnitude of double frequency oscillatory errors in the estimated frequency and phase of the ETD-PLL and NTD-PLL in the frequency range defined by the standard EN50160.

monic component, 5% fifth harmonic component, 4% seventh harmonic component, 1% ninth harmonic component and 3% eleventh harmonic component in the grid voltage. The total harmonic distortion of the grid voltage is 8.18%. As shown, the filtering capability of the ETD-PLL is quite good even in

the presence of large frequency drifts. The filtering capability of the NTD-PLL, however, is acceptable only when the grid frequency is at (or very close to) its nominal value.

To highlight the advantages and disadvantages of the ETD-PLL and NTD-PLL, two advanced single-phase PLLs, i.e., the

Fig. 22. Simulation and experimental results under harmonically distorted grid conditions.

second-order generalized integrator based PLL (SOGI-PLL) [14] and pPLL with in-loop moving average filter (briefly called the MAF-pPLL) [29], are also evaluated under the same tests as the ones in Figs. 19, 20 and 22 and their results are compared with those of the ETD-PLL and NTD-PLL. The control parameters of the SOGI-PLL and MAF-pPLL are designed using the symmetrical optimum method, as described in [15] and [29], respectively. Table I summarizes the obtained results, in which the best performance is highlighted in bold font.

#### V. SUMMARY AND CONCLUSION

For the first time, the accurate small-signal model of the TD-PLL was derived in this paper. It was shown that the dynamics of the transfer delay unit, contrary to what was believed, is not negligible. Indeed, its dynamics appear as a set-point filter in the TD-PLL small-signal model. Regardless of the importance of such model in the analysis and design of the TD-PLL, it may stimulate new ideas in the modeling of other single-phase

OSG based PLLs, because neglecting the dynamics of OSG unit during the modeling of these PLLs is a common practice.

It was then shown that the drawbacks of the standard TD-PLL, i.e., its poor harmonic filtering capability and its phase offset and oscillatory errors in the presence of frequency drifts, can be overcome by adding additional delay based filtering stages and a phase error compensator into its structure. These modifications only require  $10 \times /\div$ , 10 +/- and storing  $\frac{5T}{8T_s}$  samples (100 samples, for a sampling frequency 8 kHz) in the DSP memory, which means they demand a very low computational effort.

The NTD-PLL small-signal modeling was then presented, which indicated that the NTD-PLL is mathematically equivalent to a pPLL with in-loop  $dq\mathrm{DSC_4}$  operator ( $dq\mathrm{DSC_4}$ -pPLL). Considering this equivalence and more straightforward implementation of the  $dq\mathrm{DSC_4}$ -pPLL, it is recommended in this paper to use the  $dq\mathrm{DSC_4}$ -pPLL when the implementation of the NTD-PLL is intended. A systematic method based on the symmetrical optimum method to fine-tune the NTD-PLL control parameters was also proposed.

|                                        | ETD-PLL               | NTD-PLL               | SOGI-PLL                 | MAF-pPLL              |

|----------------------------------------|-----------------------|-----------------------|--------------------------|-----------------------|

| +40° phase-angle jump                  |                       |                       |                          |                       |

| 2% settling time                       | 37.1 ms (1.85 cycles) | 35.6 ms (1.78 cycles) | 48.7 ms (2.43 cycles)    | 75.9 ms (3.8 cycles)  |

| Phase overshoot                        | 20.8° (52%)           | 15.28° (38.2%)        | $12.28^{\circ} (30.7\%)$ | 13.43° (33.6%)        |

| Peak frequency deviation               | 7.66 Hz               | 6.34 Hz               | 6.03 Hz                  | 3.22 Hz               |

| -3 Hz frequency step change            |                       |                       |                          |                       |

| 2% settling time                       | 36.4 ms (1.82 cycles) |                       | 37.6 ms (1.88 cycles)    | 96.4 ms (4.82 cycles) |

| Peak phase deviation                   | 5.88°                 | $6.58^{\circ}$        | $6.34^{\circ}$           | $11.64^{\circ}$       |

| Peak oscillatory frequency error       | 0.017 Hz              | 0.3 Hz                | 0 Hz                     | $0.049 \; Hz$         |

| Peak oscillatory phase error           | 0.1°                  | $1.56^{\circ}$        | <b>0</b> °               | $0.51^{\circ}$        |

| Harmonically distorted grid condition  |                       |                       |                          |                       |

| Peak-to-peak phase error (freq.=50 Hz) | <b>0</b> °            | $0.72^{\circ}$        | $0.51^{\circ}$           | <b>0</b> °            |

| Peak-to-peak phase error (freq.=47 Hz) | $0.41^{\circ}$        | $3^{\circ}$           | $0.54^{\circ}$           | 1°                    |

| Phase margin (PM)                      | 59.5°                 | 43.7°                 | 44.7°                    | 43.6°                 |

| Gain margin (GM)                       | -7.32  dB             | 29.8 dB               | Inf.                     | 14.1 dB               |

TABLE I PERFORMANCE COMPARISON

The paper finally evaluated the performance of the ETD-PLL and NTD-PLL through simulation and experimental results and compared their performance with the state-of-the-art single-phase PLLs. It was shown that the ETD-PLL has a fast dynamic response (a settling time of less than two cycles of the nominal frequency) and a good harmonic filtering capability. These features along with its ease of implementation make the ETD-PLL a suitable choice for the synchronization of single-phase grid-connected equipment. The NTD-PLL, like the ETD-PLL, has a fast dynamic response, but it suffers from a limited harmonic filtering capability and considerable double frequency oscillatory error in the presence of frequency drifts. Therefore, it can be a suitable choice only for applications where the grid frequency is at or very close to its nominal value.

#### REFERENCES

- [1] F. M. Gardner, *Phaselock Techniques*, 3rd ed. Hoboken, NJ: Wiley, 2005.

- [2] T. Tran, T. W. Chun, H. H. Lee, H. G. Kim, and E. C. Nho, "PLL-based seamless transfer control between grid-connected and islanding modes in grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5218-5228, Oct. 2014.

- [3] S. Bifaretti, P. Zanchetta, and E. Lavopa, "Comparison of two three-phase PLL systems for more electric aircraft converters," *IEEE Trans. Power Electron.*, vol. 29, no. 3, pp. 6810-6820, Dec. 2014.

- [4] T. Li Tong, X. Zou, S. S. Feng, Y. Chen, Y. Kang, Q. Huang, and Y. Huang, "An SRF-PLL-based sensorless vector control using the predictive deadbeat algorithm for the direct-driven permanent magnet synchronous generator," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2837-2849, Jun. 2014

- [5] R. M. Santos Filho, P. F. Seixas, P. C. Cortizo, L. A. B. Torres, and A. F. Souza, "Comparison of three single-phase PLL algorithms for UPS applications," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2923-2932, Aug. 2008.

- [6] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase grid connected power conditioning systems," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3639-3650, Aug. 2012.

- [7] T. Thacker, D. Boroyevich, R. Burgos, and F. Wang, "Phase-locked loop noise reduction via phase detector implementation for single-phase systems," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2482-2490, Jun. 2011.

- [8] S. Golestan, J. M. Guerrero, A. M. Abusorrah, and M. M. Al-Hindawi "An analysis of modified demodulation based grid voltage parameters estimator," *IEEE Trans. Power Electron.*, vol. PP, no. 99, pp. 1-6, Jun. 2015.

- [9] S. Sakamoto, T. Izumi, T. Yokoyama, and T. Haneyoshi, "A new method for digital PLL control using estimated quadrature two phase frequency detection," in Proc. Power Conversion Conference, 2002.

- [10] A. Elrayyah, Y. Sozer and M. Elbuluk, "Robust phase locked-loop algorithm for single-phase utility-interactive inverters," *IET Power Electron.*, vol. 7, no. 5, pp. 1064-1072, May. 2014.

- [11] T. Thacker, R. Wang, D. Dong, R. Burgos, F. Wang, and D. Boroyevich, "Phase-locked loops using state variable feedback for single-phase converter systems," in Proc. IEEE Appl. Power Electron. Conf. (APEC), 2009, pp. 864-870.

- [12] P. Hao, W. Zanji, and C. Jianye, "A measuring method of the single-phase AC frequency, phase, and reactive power based on the Hilbert filtering," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 3, pp. 918-923, Jun. 2007.

- [13] K. De Brabandere, T. Loix, K. Engelen, B. Bolsens, J. Van den Keybus, J. Driesen, and R. Belmans, "Design and operation of a phase-locked loop with Kalman estimator-based filter for single-phase applications," in Proc. IEEE Ind. Electron. Soc. Annu. Conf. (IECON), 2006, pp. 525-530.

- [14] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new single-phase PLL structure based on second order generalized integrator," in Proc. IEEE Power Electron. Spec. Conf. (PESC), 2006, pp. 1511-1516.

- [15] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Dynamics assessment of advanced single-phase PLL structures," *IEEE Trans. Ind. Electron.*, vol. 60, no. 6, pp. 2167-2177, Jun. 2013.

- [16] F. A. S. Neves, H. E. P. de Souza, M. C. Cavalcanti, F. Bradaschia, and E. Bueno, "Digital filters for fast harmonic sequence components separation of unbalanced and distorted three-phase signals," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3847-3859, Oct. 2012.

- [17] S. B. Kjaer, "Design and control of an inverter for photovoltaic applications," Ph.D. dissertation, Inst. Energy Technol., Aalborg Univ., Aalborg, Denmark, 2005.

- [18] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "Improved PLL structures for single-phase grid inverters," in Proc. Int. Conf. PELINCEC, 2005, pp. 1-6.

- [19] F. Wang, and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1987-1997, Jul. 2011.

- [20] Y. F. Wang and Y. W. Li, "Analysis and digital implementation of cascaded delayed-signal-cancellation PLL," *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1067-1080, Apr. 2011.

- [21] S. Golestan, M. Ramezani, J. M. Guerrero, and M. Monfared, "dq-frame cascaded delayed signal cancellation-based PLL: Analysis, design, and comparison with moving average filter-based PLL," IEEE Trans. Power Electron., vol. 30, no. 3, pp. 1618-1632, Mar. 2015.

- [22] Y. F. Wang, and Y. Li, "Three-phase cascaded delayed signal cancellation PLL for fast selective harmonic detection," *IEEE Trans. Ind. Electron.*, vol. 60, no. 4, pp. 1452-1463, Apr. 2013.

- [23] J. W. Choi, Y. K. Kim, and H. G. Kim, "Digital PLL control for single phase photovoltaic system," *Proc. Inst. Elect. Eng. Elect. Power Appl.*, vol. 153, no. 1, pp. 4046, Jan. 2006.

- [24] J. Kaiser and R. Hamming, "Sharpening the response of a symmetric nonrecursive filter by multiple use of the same filter," *IEEE Trans. Acoust.*, *Speech, Signal Process.*, vol. ASSP-25, no. 5, pp. 415-422, Oct. 1977.

- [25] A. Elrayyah, Y. Sozer, M. Elbuluk, "A robust and efficient PLL algorithm for single-phase grid-connected renewable energy sources," in Proc. IEEE Appl. Power Electron. Conf. (APEC), 2013, pp. 2940-2946.

- [26] S. Golestan, and J. M. Guerrero, "Conventional synchronous reference

frame phase-locked loop is an adaptive complex filter," *IEEE Trans. Ind. Electron.*, pp. 1679-1682, vol. 62, no. 3 Mar. 2015.

- [27] H. Awad, J. Svensson, and M. J. Bollen, "Tuning software phase-locked loop for series-connected converters," *IEEE Trans. Power Del.*, vol. 20, no. 1, pp. 300-308, Jan. 2005.

- [28] Voltage Characteristics of Public Distribution Systems, CENELEC Std. European Standard EN-50160, Nov. 1999.

- [29] S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo and M. Monfared, "Moving Average Filter Based Phase-Locked Loops: Performance Analysis and Design Guidelines," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2750-2763, Jun. 2014.

Saeed Golestan (M'11-SM'15) received the B.Sc. degree in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2006, and the M.Sc. degree in electrical engineering from Amirkabir University of Technology, Tehran, Iran, in 2009.

From 2009 to 2015, he was a lecturer in the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Iran. Currently, he is a PhD student at the Department of Energy Technology of Aalborg University, Denmark. His research interests include phase-locked loop and nonlinear filtering

techniques for power and energy applications, power quality measurement and improvement, estimation of power system parameters, and microgrid.

Josep M. Guerrero (S'01-M'04-SM'08-F'15) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000 and 2003, respectively. Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where he is responsible for the Microgrid Research Program. From 2012 he is a guest Professor at the Chinese Academy of Science and the Nanjing

University of Aeronautics and Astronautics; from 2014 he is chair Professor in Shandong University; and from 2015 he is a distinguished guest Professor in Hunan University.

His research interests is oriented to different microgrid aspects, including power electronics, distributed energy-storage systems, hierarchical and cooperative control, energy management systems, and optimization of microgrids and islanded minigrids. Prof. Guerrero is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANS-ACTIONS ON INDUSTRIAL ELECTRONICS, and the IEEE Industrial Electronics Magazine, and an Editor for the IEEE TRANSACTIONS on SMART GRID and IEEE TRANSACTIONS on ENERGY CONVERSION. He has been Guest Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS Special Issues: Power Electronics for Wind Energy Conversion and Power Electronics for Microgrids; the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS Special Sections: Uninterruptible Power Supplies systems, Renewable Energy Systems, Distributed Generation and Microgrids, and Industrial Applications and Implementation Issues of the Kalman Filter; and the IEEE TRANSACTIONS on SMART GRID Special Issue on Smart DC Distribution Systems. He was the chair of the Renewable Energy Systems Technical Committee of the IEEE Industrial Electronics Society. In 2014 he was awarded by Thomson Reuters as Highly Cited Researcher, and in 2015 he was elevated as IEEE Fellow for his contributions on "distributed power systems and microgrids."

**Ana Vidal** (S'10) received the M.Sc. and the Ph.D. degrees from the University of Vigo, Vigo, Spain, in 2010 and 2015, respectively.

Since 2009, she has been with the Applied Power Electronics Technology Research Group. Her research interests include control of grid-connected converters and distributed power generation systems.

**Alejandro G. Yepes** (S'10-M'12) received the M.Sc. and the Ph.D. degree from University of Vigo, Vigo, Spain in 2009 and 2011, respectively.

Since 2008 he is with the Applied Power Electronics Technology Research Group, University of Vigo. His main research interests include control of switching power converters and ac drives.

**Jesus Doval-Gandoy** (M'99) received the M.Sc. degree from Polytechnic University of Madrid, Madrid, Spain, in 1991 and the Ph.D. degree from the University of Vigo, Vigo, Spain in 1999.

From 1991 till 1994 he worked at industry. He is currently an Associate Professor at the University of Vigo. His research interests are in the areas of ac power conversion.

**Francisco D. Freijedo** received the M.Sc. degree in Physics from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 2002 and the Ph.D. degree from the University of Vigo, Vigo, Spain, in 2009.

From 2005 to 2011, he was a Lecturer with the Department of Electronics Technology of the University of Vigo. From 2011 to 2014, he worked in the wind power industry as a control engineer.

Since 2014, he is a Postdoctoral Researcher at the Department of Energy Technology of Aalborg

University. His main research interests are in the areas of ac power conversion.