### **Aalborg Universitet**

## Inrush Transient Current Analysis and Suppression of Photovoltaic Grid-Connected **Inverters During Voltage Sag**

Li, Zhongyu; Zhao, Rende; Xin, Zhen; Guerrero, Josep M.; Savaghebi, Mehdi; Li, Peide

Proceedings of 2016 IEEE Applied Power Electronics Conference and Exposition (APEC)

DOI (link to publication from Publisher): 10.1109/APEC.2016.7468402

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Li, Z., Zhao, R., Xin, Z., Guerrero, J. M., Savaghebi, M., & Li, P. (2016). Inrush Transient Current Analysis and Suppression of Photovoltaic Grid-Connected Inverters During Voltage Sag. In *Proceedings of 2016 IEEE Applied Power Electronics Conference and Exposition (APEC)* (pp. 3697 - 3703). IEEE Press. https://doi.org/10.1109/APEC.2016.7468402

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

# Inrush Transient Current Analysis and Suppression of Photovoltaic Grid-Connected Inverters During Voltage Sag

Zhongyu Li, Rende Zhao

Zhen Xin, Josep M.Guerrero, Mehdi Savaghebi

Peide Li

**Electrical Engineering Department** China University of Petroleum (Eastern China) Qingdao China

lzyupc619@gmail.com, zhaorende@126.com

**Energy Department** Aalborg University Aalborg Denmark zxi@et.aau.dk, joz@et.aau.dk, mes@et.aau.dk

Shandong Jinan Power Equipment Factory Co., LTD Jinan China peidezhilin@163.com

Abstract—The Inrush Transient Current (ITC) in the output of the photovoltaic grid-connected inverters is usually generated when grid voltage sag occurs, which can trigger the protection of the grid-connected inverters, and even destroy the semiconductor switches. Then, the grid-connected inverters will thus fail to ride through the voltage sag and even further cause more serious grid faults. This paper analyzes the generation principle of ITC and explores its influence factors, upon which, the suppression approaches are presented. Simulation and experimental results validate the theoretical analysis and the effectiveness of the proposed method.

Keywords—the inrush transient current (ITC); photovoltaic grid-connected inverters; voltage sag; influence factors; suppression approaches

#### I. INTRODUCTION

The recent interest in solar energy is increasing tremendously. And the installation of large photovoltaic (PV) power generation systems, which are interconnected with the utility grid, is accelerating [1], [2]. However, the PV power generation systems may lead to instability when grid disturbances occur. The mainly reason is that the photovoltaic grid-connected inverters (PGI) is sensitive to grid disturbances, especially, the voltage sags [3], [4]. Therefore, to maintain the stability of the power system, one important grid code issued in many countries is that the PGI should success riding through voltage sags [5-8]. In order to meet the requirement of the grid code, firstly, PGI shouldn't disconnect from the grid by the reason of the fault current.

The fault current studies of grid-connected inverters have been widely reported in many literatures [2], [9-13]. In [9], a fault current limiter is used to reduce overcurrent in the converter, but it has the drawback of absorbing active power. Also, in the field of overcurrent reduction, there are other methods relying on the control scheme, which can avoid any increase of devices cost in the system. A study reported in [10] proposes a proportional-resonant (PR) current controller for the current limiter to make sure the output current without overcurrent, this current limiter is acquired indirectly by using an active power limiter. In [11] and [12], a proper reference current is selected to ride through grid faults and achieve requirements of different power quality. Among these methods, although low currents can be acquired, the control scheme does not assure its minimum value, but [13] overcomes this problem. On the other hand, for unbalanced voltage sags, there is also a control algorithm [2] to limit the peak current.

Obviously, the above mentioned technical literatures are all having concerns about the fault current limitation when the digital controller can take control of the output voltage of PGI. However, when a sudden decrease of grid voltage occurs, the output voltage of the PGI cannot change instantaneously. This is because of the time delay in its digital control system. Therefore, a large voltage drop will be generated on the output L-filters or LCL-filters of the inverter, which will further lead to an inrush transient current (ITC). This ITC may trigger the overcurrent protection of the inverter and in the worst case may even destroy the semiconductor switches, causing the disconnection of the PGI from the grid. The disconnection of too many PGI from the grid system will aggravate the voltage sags and lead to more severe grid faults.

Therefore, it is of great importance to study the ITC suppression solutions for the PGI. Obviously, a good understanding of the ITC influence factors will contribute a lot to this work. Actually, although the generation principle of ITC is not complex, the ITC influence factors have not been fully investigated so far. Therefore, in this paper, a thorough study of the ITC influence factors is carried out. Based on these findings, the appropriate ITC suppression approaches are then discussed. Finally, some experimental results are given to validate the theoretical analysis and the effectiveness of the proposed ITC suppression method.

#### PRINCIPLE AND CAUSE OF INRUSH TRANSIENT **CURRENT**

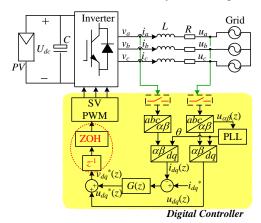

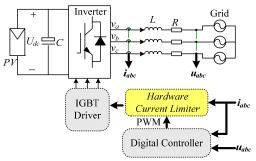

Fig.1 shows the basic control structure of the three-phase PGI. To explain the generation principle of ITC, the gridconnected inverter with L filter is analyzed for example. u, v, i, L, R represent the grid phase voltage, inverter output voltage, phase current, grid-connected inductance and its resistance, respectively. In this paper, a proportional-integral (PI) current controller is used, which is denoted by G(z) in Fig.1.

Fig. 1 The basic control structure of the three-phase PGI

As shown in Fig.1, the inverter output voltage reference  $v^*_{dq}$  is influenced by two components, which are the output of current controller  $u^*_{dq}$  and the direct feed-forward gird voltage  $u_{dq}$ . Due to the time inertial of the current PI controller, the direct feed-forward gird voltage is the effective component to control the inductor current during the process of the grid voltage sag.

Traditionally, the single-sampling approach is widely used in PGI digital control system, then the state variables (i.e., inductor currents and grid voltages) needed in the control algorithm are sampled once per switching period [14]. Because of this sampling approach, it is hard to guarantee that the instantaneous voltage can be sampled instantly, and with considering the zero-order hold (ZOH) effect of the PWM [14], [15], the valid output voltage, which can limit the ITC, need at least one and half switching period to be produced by DSP. Due to this delay, the voltage difference on the grid-connected inductor is large and will result in the rapidly rising of the inductor current in this short time. Thus, ITC is generated.

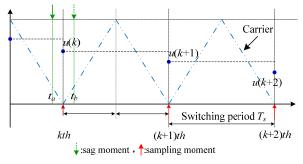

Fig. 2 Generation mechanism of the digital control delay

The generation mechanism of the digital control delay is shown in Fig.2.  $T_s$  is the switching period which is equal to the sampling period by using the single-sampling approach. In Fig.2, suppose that the voltage sags at  $t_a$  just before the kth sampling, the controller could catch the voltage. After one sampling period, the digital regulator could update the command signal to u(k+1) based on the newly sampled state variables of the fault grid voltage, together with the ZOH effect

of PWM, the digital control delay is at least  $1.5T_s$  when the inverter could control the PGI current. However, as the sag occurs at  $t_b$  which lags behind the kth sampling, it's impossible to capture the fault voltage at this period. Only during the (k+1)th sampling period, the effective voltage command u(k+2) could be produced by the controller. Therefore, the delay expands to  $2.5T_s$ . During this  $1.5\sim2.5T_s$  time delay, the DSP is not able to trace the variation of voltage, hence the PGI current rapidly increases to form the ITC. In the event the ITC was large enough and beyond the device component limit, a destructive damage of semiconductors could occur. Thus, the analysis the value of ITC is imperative in the next part.

#### III. INFLUENCE FACTORS OF INRUSH TRANSIENT CURRENT

According to Fig. 1, the mathematical model of the PGI in the three phase stationary reference frame is shown as following

$$\begin{cases} S_{a}U_{dc} - u_{a} - Ri_{a} - L\frac{di_{a}}{dt} \\ = S_{b}U_{dc} - u_{b} - Ri_{b} - L\frac{di_{b}}{dt} \\ = S_{c}U_{dc} - u_{c} - Ri_{c} - L\frac{di_{c}}{dt} \end{cases}$$

(1)

where  $S_a$ ,  $S_b$ ,  $S_c$  are switch function. In the three-phase three-wire system, the sum of the current is  $i_a+i_b+i_c=0$ , so (1) becomes

$$\begin{cases} L \frac{di_{a}}{dt} = v_{a} - u_{a} - Ri_{a} + \frac{1}{3}u_{x} \\ L \frac{di_{b}}{dt} = v_{b} - u_{b} - Ri_{b} + \frac{1}{3}u_{x} \\ L \frac{di_{c}}{dt} = v_{c} - u_{c} - Ri_{c} + \frac{1}{3}u_{x} \end{cases}$$

(2)

where  $v_a$ ,  $v_b$ ,  $v_c$  are the inverter output voltage. And their expression can be given by

$$\begin{cases} v_{a} = \left[ S_{a} - \frac{S_{a} + S_{b} + S_{c}}{3} \right] U_{dc} \\ v_{b} = \left[ S_{b} - \frac{S_{a} + S_{b} + S_{c}}{3} \right] U_{dc} \\ v_{c} = \left[ S_{c} - \frac{S_{a} + S_{b} + S_{c}}{3} \right] U_{dc} \end{cases}$$

(3)

$u_x$  is the sum of the three phase voltage and is given by

$$u_x = u_a + u_b + u_c \tag{4}$$

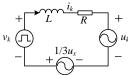

According to (2), any single phase equivalent circuit diagram can be seen in Fig. 3 when considering the balance sag.

Fig. 3 Single phase equivalent circuit diagram

where k is the symbol of a, b, c phase. Before the voltage sags, according to Fig.3, the single phase voltage expression for this system can be given by

$$L\frac{di_k}{dt} = v_k - u_k - Ri_k + \frac{1}{3}u_x \tag{5}$$

When the voltage sag occurs, (5) changes to

$$L\frac{di_{k_{-}f}}{dt} = v_{k_{-}f} - u_{k_{-}f} - Ri_{k_{-}f} + \frac{1}{3}u_{x_{-}f}$$

(6)

where  $v_{k,f}$ ,  $u_{k,f}$  and  $u_{x,f}$  are the output voltage of PGI, grid phase voltage and the sum of the three phase voltage, respectively.

In (6), the resistance of the grid-connected inductor is so small that its influence to the ITC can be neglected in the following analysis.

When a sudden decreasing of the grid voltage occurs, DSP may not sample the voltage instantly. Hence, the PGI output voltage remains unchanged, with  $v_{k,f} = v_k$ . However, the grid voltage could be significantly different and (5) changes to:

$$L\frac{di_{k_{-}f}}{dt} = v_k + \frac{1}{3}u_{x_{-}f} - u_{k_{-}f}$$

(7)

In (7), for different sag type, the value of  $u_x$  is different. According to [16], the value of  $u_x$  under the four typical sag conductions are shown in Table I, where  $p_u$  is the sag depth and  $p_u \in (0, 1]$ .

TABLE I  $u_x$  VALUE UNDER DIFFERENT SAG TYPE

| Sag type | $u_x$            | Sag type | $u_x$        |

|----------|------------------|----------|--------------|

| (A)1Φn   | $(p_u$ -1) $U_m$ | (C)2Фn   | $(1-p_u)U_m$ |

| (В)2Ф    | 0                | (D)3Φ    | 0            |

where  $U_m$  is the normal phase voltage. Assuming that the three voltage symmetrical sag occurs in the grid, then  $u_{x,f}$ =0 and  $u_{k,f}$ = $p_uu_k$ . At the sag moment, the current in the inductor can be given by

$$i_{k_{-}f} = \frac{1}{L} \int_{t_{1}}^{t_{2}} (v_{k} - p_{u}u_{k})dt + i_{0}$$

(8)

Thus, the ITC  $\Delta i_k$  is given by

$$\Delta i_k = \frac{1}{L} \int_{t_1}^{t_2} (v_k - p_u u_k) dt = \frac{1}{L} \Delta u \Delta t \tag{9}$$

where  $\Delta t = t_2 - t_1$  represents the digital control delay.  $\Delta u = v_k - p_u u_k$  represents the voltage difference of the inductor. It shows obviously that ITC is influenced by the digital control delay  $\Delta t$ , the voltage difference  $\Delta u$  and the inductor L.  $v_k$  is the PGI output voltage and kept unchanged during  $\Delta t$ , while the grid voltage is changed to  $p_u u_k$ .

Under normal grid-connected condition, assuming that the power factor is unit, hence the difference between  $u_k$  and  $v_k$  is

very small compared with the fault condition, approximately,  $u_k \approx v_k$ . So (9) can be rewritten by

$$\Delta i_k \approx \frac{1}{L} \int_{t_1}^{t_2} (u_k - p_u u_k) dt = \frac{1}{L} (1 - p_u) u_k \Delta t$$

(10)

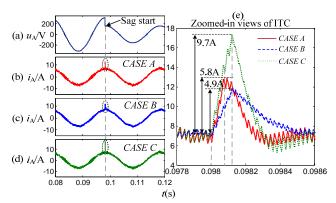

According to (10), Figs.4-6 show how the ITC are influenced by these factors.

1) The influence of grid-connected inductor L and the digital control delay  $\Delta t$  to the ITC: The influencing factors were set by following conditions (see Fig. 4):

$$u_k = 311 \text{V}$$

$p_u = 50\%$   $L = 2\text{mH}$   $\Delta t = 2.5T_s = 75\mu s$

b) CASE B:

$$u_k$$

=311V  $p_u$ =50%  $L$ =4mH  $\Delta t$ =2.5 $T_s$  =125 $\mu s$

c) CASE C:

$$u_k$$

=311V  $p_u$ =50%  $L$ =2mH  $\Delta t$ =1.5 $T_s$ =125 $\mu s$

By the comparison between CASE B and CASE C of Fig. 4, given that the grid-connected inductor is 2mH, the ITC is larger. As shown in CASE A and CASE C, the only difference is the sampling time which leads to the digital control delay are  $75\mu s$  and  $125\mu s$ , respectively. Clearly, the longer the digital control delay is, the larger the ITC is.

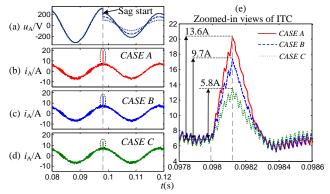

Fig. 4 The influence of L and the digital control delay  $\Delta t$  to the ITC: (a) Phase A grid voltage, (b)-(d) phase A grid-connected current, and (e) zoomed-in views of ITC.

2) The influence of sag depth  $p_u$  to the ITC: The influence factors were set by the following conditions (see Fig. 5):

a) CASE A:

$$u_k$$

=311V  $p_u$ =70%  $L$ =2mH  $\Delta t$ =125 $\mu s$

b) CASE B:

$$u_k = 311V$$

$p_u = 50\%$   $L = 2mH$   $\Delta t = 125 \mu s$

c) CASE C:

$$u_k$$

=311V  $p_u$ =30%  $L$ =2mH  $\Delta t$ =125 $\mu s$

As shown in Fig. 5, it's clearly to see that the ITC is 13.6A when the sag depth is 70%, which is larger than the other two cases (9.7A and 5.8A).

Fig. 5 The influence of sag depth  $p_u$  to the ITC: (a) Phase A grid voltage, (b)-(d) phase A grid-connected current, and (e) zoomed-in views of ITC.

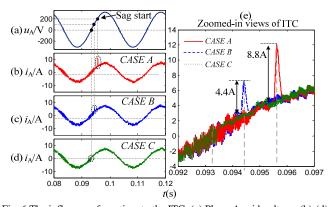

3) The influence of sag time to the ITC: The influence factors were set by the following conditions (see Fig. 6):

a) CASE A:  $u_k$ =200V  $p_u$ =70% L=2mH  $\Delta t$ =125 $\mu s$ b) CASE B:  $u_k$ =100V  $p_u$ =70% L=2mH  $\Delta t$ =125 $\mu s$

c) CASE C:  $u_k$ =0V  $p_u$ =70% L=2mH  $\Delta t$ =125 $\mu s$

Fig. 6 shows the ITC at different sag time. The ITC is 8.8A, 4.4A, 0A, respectively. It's easy to find out that the ITC is much larger as the voltage reaches the peak value.

Fig. 6 The influence of sag time to the ITC: (a) Phase A grid voltage, (b)-(d) phase A grid-connected current, and (e) zoomed-in views of ITC.

The validity of the (10) is demonstrated by the simulation results above.

In the high power PGI, the switching frequency can be hundreds hertz per second [17]-[18]. Moreover, considering the worst voltage sag condition, the ITC could reach the destructive value of the semiconductor.

#### IV. CURRENT SUPPRESSION METHOD

From the above analysis, obviously, the ITC can be suppressed by regulating the influence factors. The ITC can be substantially reduced by using a larger grid-connected inductance, adopting the multi-sampling scheme approach, etc. However, if the system is not able to change these influence

factors, the methods mentioned above will be invalid. Due to the time delay of ITC can be dozens of  $\mu s$ , to suppress this inrush current, this paper proposed a hardware suppression method to limit the ITC under the safe range.

As shown in Fig.7, the hardware current limiter in PGI is positioned between the DSP controller and the IGBT driver, when a phase current is sampled with a value exceeding the limiting value, the limiter can thus set a low level of the PWM signals to the IGBT driver. By shutting down the IGBT about dozens of  $\mu s$ , the ITC is suppressed and then the PWM signals resume normal again. Thus, the PGI overcurrent protection will not be triggered and the system will continuously work in the grid-connected condition. This is biggest different between the hardware current limiter and the overcurrent protection circuit. Meanwhile, the limiter does not influence the normal condition. The block diagram of hardware current limiter is shown in Fig.8.

Fig. 7 The location of the hardware current limiter

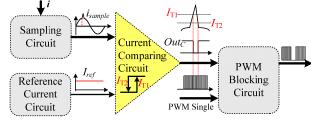

As shown in Fig. 8, the first part of hardware current limiter is the current sampling circuit whose function is removing the higher harmonics from the sampled current and properly scaling the sampled current. Both the reference current circuit output  $I_{ref}$  and the processed current signal  $i_{sample}$ are sent to a current comparing circuit. The kernel of the comparing circuit is the hysteresis comparator, which has two thresholds ( $I_{T1}$ ,  $I_{T2}$  and  $I_{T1} > I_{T2}$ ). This hysteresis comparator is realized by a differential comparator, like LM339. When isample is larger than  $I_{T1}$ , the comparator output  $Out_C$  goes low. When  $i_{sample}$  is lower than the value of  $I_{T2}$ ,  $Out_C$  will go high. Suppose that Out<sub>C</sub> is low, when the PWM signals pass through the PWM blocking circuit which is realized by an AND gate, the PWM signals would be set to low level and until Out<sub>C</sub> is changed to a high level, the PWM signals then become normal. According to this mechanism, the ITC can be suppressed. This is quite different from the overcurrent protection circuit which will shut down the PGI. Although the above discussion is with one phase case, it also applies to three-phase system.

Fig. 8 The block diagram of hardware current limiter

The hardware of the current limiter is shown in Fig. 10. Because the devices used in the hardware limiter is inexpensive, the additional cost of the limiter is quite little.

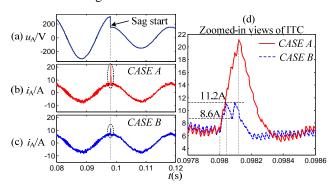

The simulation results of ITC without and with the hardware current limiter are shown in Fig. 9, where the influence factors were set by the following condition

$$u_k = 311 \text{V}$$

$p_u = 70\%$   $L = 2\text{mH}$   $\Delta t = 125 \mu s$

In Fig. 9, *CASE A* and *B* are the ITC waveform without and with the hardware current limiter. In *CASE B*, the current is suppressed under 11.2A due to the hysteresis of comparator. When the current goes beyond the first threshold (11.2A), the PWM signals are blocked, and this blocking status remains until the current goes down below the second threshold (8.6A). Then the PWM signals resume normal.

Fig. 9 ITC without and with the hardware current limiter: (a) Phase A grid voltage, (b)-(c) phase A grid-connected current, and (d) zoomed-in views of ITC.

#### V. EXPERIMENTAL RESULT

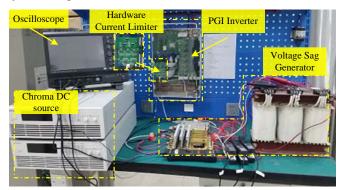

To examine the theoretical analysis and the current limiter proposed in this paper, the experiments with a PGI system are performed shown in Fig.10. In the experimental setup, a voltage sag generator (VSG) is used to simulate the voltage sags. And the inverter is controlled by DSP TMS320F28335. The photovoltaic power source is implemented by a programmed Chroma DC source. The parameters of the actual system are given in Table II.

Fig. 10 Experimental system

| TABLE II EXPERIMENTAL I | PARAMETERS |

|-------------------------|------------|

|-------------------------|------------|

| Grid phase voltage amplitude | 311 V                    |

|------------------------------|--------------------------|

| Grid frequency               | 50 Hz                    |

| Grid inductance              | 2.0 mH                   |

| DC filter capacitance        | 1660 μF                  |

| Switching frequency          | 20 kHz                   |

| Voltage sag type             | Three phase voltage sags |

| Sag duration time            | 0.5 s                    |

In the actual system, the grid voltage and current are sampled by the hardware circuit. Due to the existence of the low-pass filter circuit, a hardware delay would be inevitably introduced in digital control. In this PGI system, the hardware delay is  $t_d$ =50 $\mu$ s.

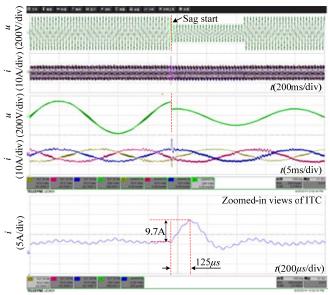

In Fig. 11, the influence factors of ITC were set by the following condition:

$$u_k$$

=311V  $p_u$ =50%  $L$ =2mH  $\Delta t$ =1.5 $T_s$ +  $t_d$ =125 $\mu$ s

As shown in Fig. 11, under the normal condition, the grid-connected current is 7.0A, yet the ITC is 9.7A as the voltage sags. Substituting the influence factors (L=2.0mH,  $p_u$ =50%,  $u_{ks}$ =311V,  $\Delta t$ =125 $\mu$ s) into (10), the theoretical result of ITC is 9.69A, which is consistent with the experimental result.

Fig. 11 The experiment waveform when voltage sags at peak value

In Fig. 12, the influence factors of ITC were set as below

$$u_k=190V$$

$p_u=50\%$   $L=2mH$   $\Delta t=1.5T_s+t_d=125\mu s$

Under this conduction, according to (10), the calculated theoretical result of ITC is 6.0A, which is similar to the experimental result (6.2A). By comparing Fig.11 and Fig.12, the analysis of Fig. 6 is verified.

Fig. 12 The experiment waveform when voltage sags at 190V

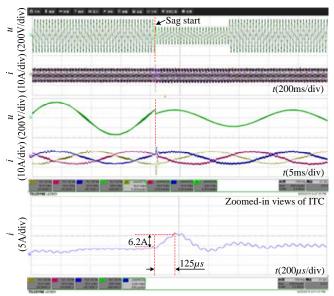

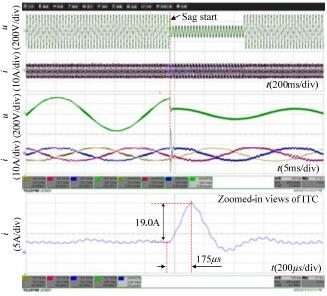

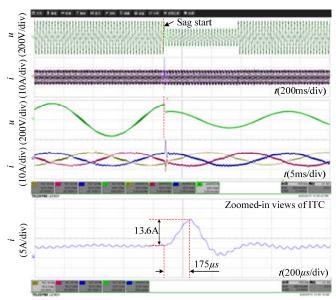

In Fig.13 and Fig.14, the influence factors of ITC were set by the following conditions:

$$u_k$$

=311V  $p_u$ =70%  $L$ =2mH  $\Delta t$ =2.5 $T_s$ +  $t_d$ =175 $\mu$ s  $u_k$ =311V  $p_u$ =50%  $L$ =2mH  $\Delta t$ =2.5 $T_s$ +  $t_d$ =175 $\mu$ s

As shown in Fig. 13, when the sag depth is 70%, the ITC is 19.0A which is larger than the ITC in Fig. 14. The only difference between two Figures is that sag depth is changed to  $175\mu s$  in Fig. 14 from  $125\mu s$  in Fig. 11, consequently the ITC increases to 13.6A from 9.7A. By substituting the above influence factors into (10), the ITC are 19.05A and 13.56A, respectively. By observing the results given in Fig. 11, Fig. 13 and Fig. 14, obviously, the deeper of the voltage sag and the longer of the digital control delay, the greater destructive of ITC.

Fig. 13 The experiment waveform when the sag depth is 70%

Fig. 14 The experiment waveform when the digital control delay is 175us

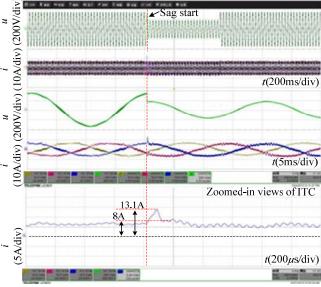

Fig. 15 shows the effect of the hardware current limiter, the influence factors of ITC were the same as that of Fig. 13. The current limiter suppresses the current under 13.1A, which should be 20.56A in Fig. 13. Meanwhile, because of the hysteresis comparator, as the current is less than 8A, the current limiter releases the PWM signals and the current increases again. In this case, obviously, the PGI does not disconnect from grid. Therefore, Fig. 15 demonstrates the effectiveness of the hardware current limiter.

Fig. 15 The experiment waveform with the hardware current limiter

#### VI. CONCLUSION

In this paper, the influence factors of the Inrush Transient Current (ITC) and its suppression method are presented. By using a hysteresis comparator, the proposed hardware current limiter has fast and excellent suppression ability to suppress the ITC. Thus, the PGI can uninterruptedly work in the grid-

connected condition without the influence of the ITC. Both simulation and experimental results validate the theoretical analysis and the proposed suppression method. Moreover, the proposed methods in this paper can also be used in other applications, where PWM inverters are used.

#### REFERENCES

- [1] G. M. S. Islam, A. AI-Durra, S. M. Muyeen, and J. Tamura, "Low voltage ride through capability enhancement of grid connected large scale photovoltaic system," in *IECON 2011 37th Annual Conference on IEEE Industrial Electronics Society*, 2011, pp. 884-889.

- [2] J. Miret, M. Castilla, A. Camacho, L. G. Vicuna, and J. Matas, "Control scheme for photovoltaic three-phase inverters to minimize peak currents during unbalanced grid-voltage sags," *IEEE Trans. Power Electron.*, vol. 27, no. 10, pp. 4262–4271, Oct. 2012.

- [3] I. J. Gabe, F´. F. K. Palha and H. Pinheiro, "Grid Connected Voltage Source Inverter Control During Voltage Dips," in *IECON 2013 - 35th Annual Conference on IEEE Industrial Electronics Society*, 2009, pp. 4571-4576.

- [4] G. Saccomando and J. Svenssan, "Transient Operation of Grid Connected Voltage Source Converter Under Unbalanced Voltage Conditions," in *IEEE Industry Applications Society Annual Meeting*, 2001, vol. 4. pp. 2419 -2424.

- [5] F. K. A. Lima, A. Luna, P. Rodriguez, E. H. Watanabe, and F. Blaabjerg, "Rotor voltage dynamics in the doubly fed induction generator during grid faults," *IEEE Trans. on Power Electron.*, vol. 25, no. 1, 2010, pp. 118--130.

- [6] M. Tsili and S. Papathanassiou, "A review of grid code technical requirements for wind farms," *IET Renew. Power Gener.*, vol. 3, no. 3, 2009, pp. 308--332.

- [7] M. Molinas, J. A. Suul, and T. Undeland, "Low voltage ride through of wind farms with cage generators: STATCOM versus SVC," *IEEE Trans.* on *Power Electron.*, vol. 23, no. 3, 2008, pp. 1104--1117.

- [8] "Grid Code: High and Extra High Voltage," E.ON Netz GmbH, Bayreuth, Germany, Apr. 2006.

- [9] M. Taghizadeh, J. Sadeh, and E. Kamyab, "Protection of grid connected photovoltaic system during voltage sag," in 2011 Inter. Conference on Advanced Power System Automation and Protection., vol. 3, pp. 2030-2035.

- [10] G. M. S. Azevedo, G. Vazquez, A. Luna, D. Aguilar and A. Rolan, "Photovoltaic Inverters with Fault Ride-Through Capability," in *IEEE International Symposium on Industrial Electronics*, 2009, pp. 549-553.

- [11] P. Rodriguez, AV. Timbus, R. Teodorescu, M. Liserre, and F. Blaabjerg, "Flexible active power control of distributed power generation systems during grid faults," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2583-2592, Oct. 2007.

- [12] M. Castilla, J. Miret, J. L. Sosa, J. Matas, and L. García de Vicuña, "Grid-fault control scheme for three-phase photovoltaic inverters with adjustable power quality characteristics," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 2930–2940, Dec. 2010.

- [13] A. Camacho, M. Castilla, J. Miret, A. Borrell, and L. G. de. Vicuña, "Active and Reactive Power Strategies With Peak Current Limitation for Distributed Generation Inverters During Unbalanced Grid Faults," *IEEE Trans. Ind. Appl.*, vol. 62, no. 3, pp. 1515-1525, Dec. 2009. Mar. 2015.

- [14] S. Buso, and P. Mattavelli. "Digital Control in Power Electronics," Synthesis Lectures on Power Electronics. 2006.

- [15] L. Corradini, W. Stefanutti, and P. Mattavelli, "Analysis of multisampled current control for active filters," *IEEE Trans. Ind. Appl.*, vol. 44, no. 6, pp. 1785–1794, Nov./Dec. 2008.

- [16] R. Zeng, H. Nian, and P. Zhou, "A three-phase programmable voltage sag generator for low voltage ride-through capability test of wind turbines," *Energy Conversion Congress and Exposition (ECCE)*, 2010, pp. 305-311.

- [17] A. Edpuganti, and A. K. Rathore. "A Survey of Low Switching Frequency Modulation Techniques for Medium-Voltage Multilevel Converters," *IEEE Trans. Ind. Appl.*, vol. 51, no. 5, pp. 4212-4228, Sep./Oct. 2015.

- [18] A. Khambadkone, and J. Holtz. "Low switching frequency and high dynamic pulsewidth modulation based on field-orientation for high-power inverter drive," *IEEE Trans. on Power Electron.*, vol. 7, no. 4, 1992,pp.627-632.