#### **Aalborg Universitet**

#### Lifetime Estimation of DC-link Capacitors in Adjustable Speed Drives Under Grid Voltage Unbalances

Wang, Haoran; Davari, Pooya; Wang, Huai; Kumar, Dinesh; Zare, Firuz; Blaabjerg, Frede

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2018.2863701

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Wang, H., Davari, P., Wang, H., Kumar, D., Zare, F., & Blaabjerg, F. (2019). Lifetime Estimation of DC-link Capacitors in Adjustable Speed Drives Under Grid Voltage Unbalances. *I E E Transactions on Power* Electronics, 34(5), 4064 - 4078. Article 8426003. https://doi.org/10.1109/TPEL.2018.2863701

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

1

# Lifetime Estimation of DC-link Capacitors in Adjustable Speed Drives Under Grid Voltage Unbalances

Haoran Wang, Student Member, IEEE, Pooya Davari, Member, IEEE, Huai Wang, Senior Member, IEEE, Dinesh Kumar, Member, IEEE, Firuz Zare, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Electrolytic capacitor with a DC-side inductor is a typical DC-link filtering configuration in grid-connected diode rectified Adjustable Speed Drives (ASDs). The criteria to size the DC-link filter are mainly from the aspects of stability and power quality. Nevertheless, the reliability of the DC-link filter is also an essential performance factor to be considered, which depends on both the component inherent capability and the operational conditions (e.g., electro-thermal stresses) in the field operation. Nowadays, unbalanced voltage has the most frequent occurrence in many distribution networks. It brings more electrical-thermal stress to the component, affecting the reliability of the capacitors. In order to study the reliability performance of the LC filter in an ASD system quantitatively, this paper proposes a mission profile based reliability evaluation method for capacitors. Different from the conventional lifetime estimation, a nonlinear accumulated damage model is proposed for the long-term estimation, considering the nonlinear process of ESR growth and capacitance reduction during the degradation. Based on the proposed lifetime estimation procedure, four case studies are investigated: 1) Lifetime benchmarking of capacitors in LC filtering and slim capacitor filtering configurations; 2) Scalability analysis for the lifetime of capacitors in terms of system power rating and grid-unbalanced levels; 3) Lifetime estimation of capacitors in DC-link filter with long-term mission profile, and 4) The impact of the capacitor sizing on the lifetime of DC-link capacitor under grid-balanced and grid-unbalanced conditions. The results serve as a guideline for proper selection of DC-link configurations and parameters to fulfill a specification in adjustable speed drives.

Index Terms—Grid-connected ASD drives, DC-link capacitor, reliability, lifetime, unbalance voltage.

#### I. Introduction

The advancement of power electronic devices and their decreasing price due to market demand have increased the use of gird-connected Adjustable Speed Drive (ASD) systems as an effective energy saving solution in various industrial, commercial and residential applications [1], [2]. DC-link

Partial results of this manuscript have been presented at the IEEE Energy Conversion Congress and Exposition (ECCE), 2017 and the IEEE Applied Power Electronics Conference and Exposition (APEC) 2018, sponsored by power electronics society.

filters are an important part of a standard ASD, in terms of size, cost, and failure. It serves to limit the DC-link voltage ripple, absorb harmonics, and provide certain amount of energy storage for abnormal and transient operations [3], [4]. In many power electronics applications, DC-link LC filter including a large electrolytic capacitor is preferred due to cost-effectiveness and simplicity. The criteria for sizing DClink filters are mostly from the stability and power quality point of view, such as voltage and current ripple limitations, dynamic response, hold-up energy requirement, stability of the overall grid-connected drives and so on [5]. However, the use of electrolytic capacitor raises reliability concern. The primary cause of electrolytic capacitor degradation is due to electrolyte evaporation and electro-chemical reaction, which highly depends on the electro-thermal stresses. High ripple currents cause internal self-heating, increasing the hot-spot temperature, and resulting in aging. Moreover, it can cause an increased capacitor Equivalent Series Resistor (ESR) over time. An increase in its ESR causes more heating for a given ripple current, thus increasing the core temperature rise and accelerating the degradation process [3]. Thus, for capacitor sizing in DC-link LC filter, the reliability performance is an essential aspect to be investigated. It depends on both the inherent capability of the selected capacitors and the operational conditions (e.g., electro-thermal stresses) in the field operation [6], [7]. In recent years, drives with significantly smaller DC-link capacitance (i.e., slim drive) implemented by film capacitors have been in the market, due to the reduction of line current harmonics emission and the potential to an improved reliability [8]. However, a comprehensive analysis of the lifetime estimation and comparison between the conventional LC filters and slim capacitor DC-link solutions do not exist in the literature.

Modern distribution networks face different power quality issues, such as voltage unbalance, background harmonic distortion, voltage sag, swell and line frequency variation, etc. Recent power quality issues show that among the different types of power quality disturbances, the unbalanced voltage has the most frequent occurrence in many distribution networks [9, 10]. Some of the main issues affecting the voltage unbalance in a distribution network are [11]: 1) unequal distribution of single-phase load on three-phase power system; 2) asymmetrical feeders and transformer winding impedances, and 3) asymmetrical power generation of grid connected single-phase distributed generations, such as roof-

H. Wang, P. Davari, H. Wang and F. Blaabjerg are with the Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark (e-mail:hao@et.aau.dk, pda@et.aau.dk, hwa@et.aau.dk and fbl@et.aau.dk).

D. Kumar is with Development Center, Danfoss Drives A/S, Denmark (e-mail: dinesh@danfoss.com).

F. Zare is with The University of Queensland, Australia (email: f.zare@uq.edu.au).

top solar inverters. In fact, considering the above-mentioned factors, maintaining an exact voltage balance at the Point of Common Coupling (PCC) is essentially unmanageable [12]. Therefore, unbalanced voltage conditions may persist as a steady-state condition. Standard regulations for US (ANSI C84. 1 [13]) and European distribution networks (IEC 60038 [14]) recommend limits for the maximum voltage unbalance of 3 \% and 2 \% respectively. However, some power electronic systems such as ASDs are very sensitive to voltage unbalance and even 2-3 % voltage unbalance may cause significant unbalanced currents, which can have undesirable consequences on electronic components lifetime span. Currently, most ASD systems are equipped with three-phase diode rectifiers as front-end AC-DC conversion stage. During voltage unbalance events, three-phase diode rectifiers may enter into single-phase operation mode (depending on the load level and unbalance level), which can generate low-order harmonic components (100 Hz, 200 Hz at 50 Hz mains) in the DC-link voltage. These low-order voltage harmonics result in undesirable impact on electro-thermal stresses, and therefore, the reliability of the DC-link capacitors. The DC-link capacitor stresses under one specific steady-state operating condition are studied in [15], where the current and voltage stresses in ASD system can be obtained mathematically. But the existing lifetime estimation of capacitor is based on a simple empirical equation and the long-term mission profile is not considered. [16] and [17] studied the mission profile based reliability assessment procedure for the DC-link capacitors in Photovoltaics (PV) systems. The damage is accumulated linearly for long time and then the lifetime of the capacitor can be estimated. However, there are still limitations in prior studies:

- 1) The existing mission profile based lifetime estimation is lack of Physics-of-Failure (PoF) understanding [18]. For example, the accumulated damage model in existing lifetime estimation is a linear model [16]. However, from capacitor lifetime testing results [18], it can be seen the damage of capacitor represented by the ESR raise in the life cycle follows an exponent expression.

- 2) The grid unbalance alters the electro-thermal stresses of the key components in a motor drive [19–21]. In ASD system, no quantitative lifetime comparison between the LC and silm capacitor filter types is available under grid unbalance. The impact of the grid voltage amplitude and phase angle unbalance on the lifetime of the two cases is not studied.

- 3) Mission profile based estimated lifetime has not been taken into account to size the capacitor.

In order to evaluate and optimize the reliability performance of the DC-link filter in ASD systems, a novel mission profile based lifetime estimation procedure for capacitors is studied in this paper. The nonlinear damage model for long-term estimation is considered, which is used to obtain the process of nonlinear damage accumulation, ESR raise ratio and capacitance reduction ratio in the life cycle. The procedure has been published in a conference paper in [22], while the derivation of the nonlinear model, scalable case study and comparison analysis are not investigated. Extending the research in [22], the lifetime estimation procedure with nonlinear accumulated damage model is discussed step by step

in this paper, and the quantitative reliability performance are investigated comprehensively from the following aspects: 1) lifetime benchmarking between the DC-link LC filter and the slim capacitor in ASDs under scalable loading conditions; 2) lifetime estimation for DC-link capacitors under grid voltage balanced and unbalanced conditions; 3) the real mission profile based long-term lifetime estimation; 4) impact of the capacitor sizing on the lifetime of DC-link filters. It serves as a guideline for proper selection of DC-link configurations and parameters to fulfill a certain lifetime requirement. It is worth mentioning that voltage sag is also a relevant reliability issue for capacitors, which may increase its electro-thermal stresses and therefore the wear out. Moreover, it might induce single-event failure due to overstress under voltage sag (e.g., over-voltage, over-temperature). The studied lifetime estimation method can also be applied to voltage sag condition.

The rest of this paper is organized as follows. In section II, the harmonic emission of different DC-link filter configurations are described. In section III, the mission profile based lifetime estimation procedure is presented considering the nonlinear accumulated damage model during the evaluation process. Experimental case studies and scalability analysis are presented in section IV, then followed by the conclusions.

#### II. HARMONIC EMISSION OF GRID-CONNECTED DRIVES

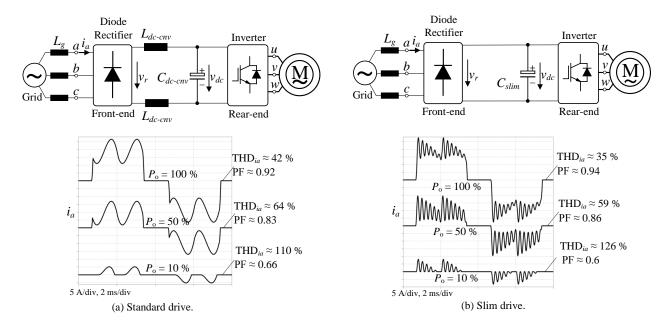

Fig. 1 shows the block diagram of the three-phase gridconnected adjustable speed drives with the specification in Table I investigated in this paper. Fig. 1 (a) shows the conventional drive, which is implemented with a DC-link LC filter. Large size DC inductor  $L_{dc-cnv}$  is used to reduce the line current harmonics as well as a large DC capacitor  $C_{\rm dc-cnv}$  to limit the DC-link voltage fluctuation.  $C_{\rm dc-cnv}$ is implemented with two electrolytic capacitors connected in series for higher voltage rating and then two in parallel for large capacitance. Fig. 1 (b) presents the second case, where the ASD utilizes a small DC-link capacitor  $C_{\rm slim}$ . One of the main problems is the resonant frequency generated by the DClink capacitor and the line inductance  $L_{\rm g}$ . The line inductance of a low-voltage distribution network is mainly defined by the size and the type of the step-down transformer. Ripple current stress is an important stressor that affects the DClink capacitor lifetime. According to the circuit analysis, the capacitor current spectrum can be divided into two frequency ranges: 0-2 kHz (i.e., Low-frequency harmonics introduced by unbalanced input and output power) and above 2 kHz (i.e., high-frequency harmonics introduced by the power electronic switching). The Root Mean Square (RMS) value of the current in the whole frequency range contributes to the thermal loading of the capacitor, which greatly impacts the reliability of the capacitor. It mainly depends on two factors: resonant frequency of the DC-link filter and the operating status of the ASDs with different grid conditions:

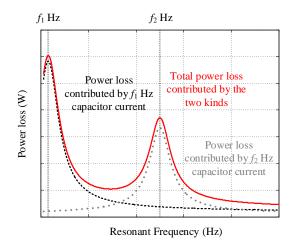

1) Resonant frequency of the DC-link filter. The schematic diagram in Fig. 2 shows the relationship between the resonant frequency and the power loss of the DC-link capacitor. At a specific frequency, power loss of the capacitor is a function of ripple current and ESR, while the total power loss is the sum

Fig. 1. A block diagram of a 7.5 kW ASD systems with two kinds of DC-link configurations and their input waveforms at different loads. The parameters of the ASD systems are based on the specification in Table I.

$\begin{tabular}{ll} TABLE\ I \\ Specification\ of\ the\ motor\ drive\ and\ the\ DC-link\ configurations. \\ \end{tabular}$

| Motor drive specifications                         |     | Standard LC filter (C <sub>dc-cnv</sub> ) |                                            | Slim capacitor filter (C <sub>slim</sub> )  |

|----------------------------------------------------|-----|-------------------------------------------|--------------------------------------------|---------------------------------------------|

| Rated power (kW)                                   | 7.5 | Physical configurations                   | Four 450V/680uF electrolytic capacitors    | 1000 V/ 30 uF Film capacitor                |

| Grid phase RMS voltage (V)                         | 230 | ESR of single capacitor                   | 150 mΩ @100 Hz                             | 15 mΩ @100 Hz                               |

| Grid frequency (Hz)                                | 50  | Thermal resistance                        | 6 °C/W                                     | 13 °C/W                                     |

| Switching frequency (kHz)                          | 5   | Rated load lifetime                       | 5000 hours @105°C and rated ripple current | 100000 hours @70°C and rated ripple current |

| DC-link voltage (V) @ 7.5 kW balanced grid voltage | 535 | L <sub>DC-cnv</sub>                       | 1.25 mH                                    |                                             |

| Ambient temperature (°C)                           | 45  |                                           |                                            |                                             |

Fig. 2. Relationship between resonant frequency and the power loss of capacitor in a drive system. Assume  $f_1$  Hz and  $f_2$  Hz harmonics are the two main components in the capacitor current.

of the power loss at a whole frequency range, which is shown

below

$$P_{\text{loss}} = \sum_{i=1}^{n} [ESR(f_i) \times I_{\text{rms}}^2(f_i)]$$

(1)

where  $ESR(f_i)$  is the equivalent series resistance at frequency  $f_i$ ,  $I_{\rm rms}(f_i)$  is the RMS value of the ripple current at frequency  $f_i$ . Assuming  $f_1$  Hz and  $f_2$  Hz harmonics are the two main components in the capacitor current, the power loss contributed by  $f_1$  Hz current reaches the peak when the resonant frequency is  $f_1$  Hz. With a higher resonant frequency, the gain at  $f_1$  Hz decreases, so that the power loss decreases. Similar phenomenon can be obtained from the power loss contributed by  $f_2$  Hz capacitor current. The power loss reaches the peak value when the resonant frequency is  $f_2$  Hz. The amplification for the current harmonics at a specific frequency is determined by the LC filter in terms of resonant frequency and damping factor. It impacts the power loss distribution in the frequency range and therefore changes the lifetime of the capacitor.

2) The operating status of the ASDs, and the grid conditions: such as during voltage unbalanced events, three-phase diode rectifier may enter in single-phase operation mode, which generates low-order harmonic components in DC-link voltage.

TABLE II

VOLTAGE UNBALANCE CASES USED FOR DRIVE ANALYSIS.

| Balanced                                           |            |            |            |  |  |  |

|----------------------------------------------------|------------|------------|------------|--|--|--|

| $U_{\scriptscriptstyle A}$ =230 $\angle 0^{\rm o}$ |            |            |            |  |  |  |

| Amplitude unbalanced (phase a)                     |            |            |            |  |  |  |

|                                                    | 3%         | 5%         | 10%        |  |  |  |

| $U_a$                                              | 209.7∠0°   | 196.7∠0°   | 165.5∠0°   |  |  |  |

| $U_b$                                              | 230∠-120°  | 230∠-120°  | 230∠-120°  |  |  |  |

| $U_c$                                              | 230∠120°   | 230∠120°   | 230∠120°   |  |  |  |

| Phase angle unbalance (phase c)                    |            |            |            |  |  |  |

|                                                    | 3%         | 5%         | 10%        |  |  |  |

| $U_a$                                              | 230∠0°     | 230∠0°     | 230∠0°     |  |  |  |

| $U_b$                                              | 230∠-120°  | 230∠-120°  | 230∠-120°  |  |  |  |

| $U_c$                                              | 230∠125.2° | 230∠128.6° | 230∠102.9° |  |  |  |

These low-frequency harmonics alternate the electro-thermal loadings of the DC-link capacitors. Therefore, the reliability estimation under grid voltage-balanced operation conditions is no longer valid. In this paper, the different power rating levels and grid-unbalanced levels are taken into account to investigate their impact on the lifetime, since they are the two main impact factors in practical applications which have significant impact on the electrical stress of the DC-link capacitor. Detail discussion regarding to the two factors are shown below:

a. Power rating. For the same filtering configuration and parameters, the higher power level increases the DC-link ripple voltage and also introduces more deteriorate effect on the reliability of capacitor, since it increases the thermal loading of the DC-link capacitor. The dominant major harmonics of this ripple current under balanced condition is six times of the grid frequency  $(6f_{\rm g})$ . Moreover, the output power not only affects the voltage ripple across the capacitor, but also affects the grid-side current quality as well. As most motor drive applications operate under partial loading condition, a scalable power level is more realistic and applicable for reliability analysis.

#### b. Grid voltage-unbalanced levels.

Grid voltage-unbalanced conditions may result in a singlephase operation of the front-end rectifier system and consequently could severely affect the DC-link capacitor lifetime. The amount of voltage unbalance is calculated based on IEC61000-2-2 for three-phase systems expressed as:

$$U_{\text{unbalanced}}(\%) = \sqrt{\frac{6(U_{\text{ab}}^2 + U_{\text{bc}}^2 + U_{\text{ca}}^2)}{U_{\text{ab}} + U_{\text{bc}} + U_{\text{ca}}} - 2}$$

(2)

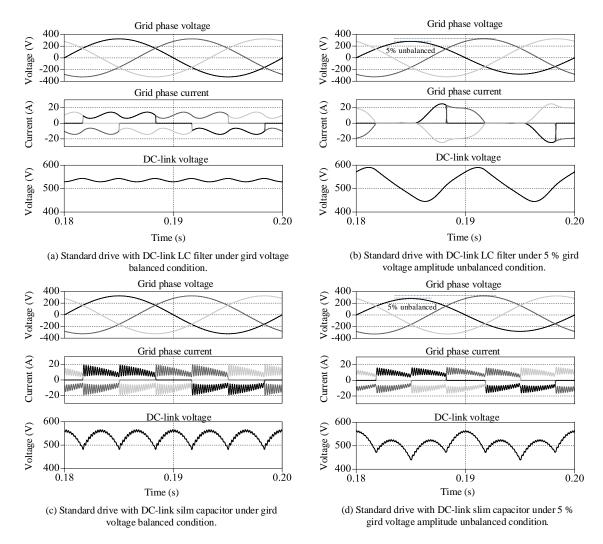

where  $U_{\rm ab}$ ,  $U_{\rm bc}$ , and  $U_{\rm ca}$  are line-line RMS voltages in a three-phase system. The applied grid conditions in the following case study are summarized in Table II. Comparing with the balanced condition, it is clear that, regardless of the output power level, the output voltage ripple increases significantly under unbalanced condition as shown in Fig. 3 with 5 % voltage amplitude unbalance. It is because the front-end rectifier is forced to operate in single-phase mode (i.e., due to partial or non-conducting of the rectifier phase leg) during grid voltage-unbalanced conditions. The single-phase operation introduces low-frequency harmonics in the DC link, therefore, it contributes more thermal loading on

the DC-link capacitor. Notably, taking the effect of the output power level in addition to the unbalanced situation could significantly reduce the performance of the capacitor reliability. The reliability analysis for the capacitors under these operating conditions are presented in the following section.

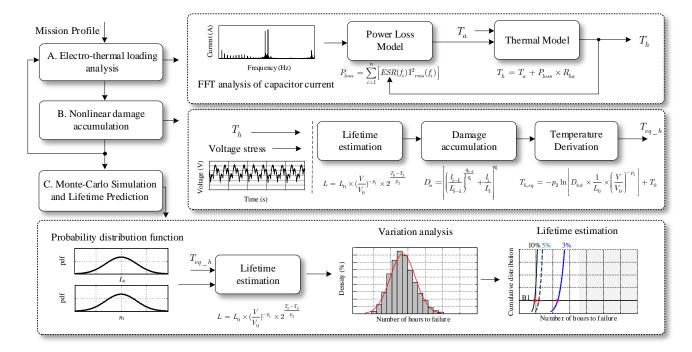

## III. RELIABILITY ANALYSIS OF CAPACITORS WITH NONLINEAR ACCUMULATED DAMAGE MODEL

The proposed mission profile based reliability evaluation procedure for capacitors is shown in Fig. 4. The procedure includes three major steps: electro-thermal loading analysis, nonlinear damage accumulation, and Monte-Carlo simulation based variation analysis. A mission profile (i.e., ambient temperature, loading condition) is applied as the input. The output is the lifetime of the capacitor with a certain confidence level (e.g., 90 %). The feedback loop from the accumulated damage to the electrical model of the capacitor shows the accelerated degradation effect, corresponding to the capacitance reduction and the ESR raise. The purpose of the method is to provide a systematic lifetime estimation procedure to evaluate the capacitor reliability based on a specified mission profile.

#### A. Electro-thermal Loading Analysis

Thermal stress is a critical stressor to capacitor wear out [3]. The ripple current and ambient temperature are the contributors to the capacitor hot-spot temperature. For electrolytic capacitors, the dominant degradation mechanisms are electro-chemical reaction in the oxide layer and the electrolyte vaporization. Both factors lead to an increase of ESR over time. Especially, the increase of capacitor power loss causes a higher operating temperature inside the capacitor. The hot-spot temperature of the capacitor, which is affected by the current stress and ambient temperature, is presented by

$$T_{\rm h} = T_{\rm a} + R_{\rm ha} \times \sum_{i=1}^{n} [ESR(f_{\rm i}) \times I_{\rm rms}^2(f_{\rm i})]$$

(3)

where  $T_{\rm h}$  is the hot-spot temperature and  $T_{\rm a}$  is the ambient temperature.  $R_{\rm ha}$  is the equivalent thermal resistance from hot-spot to ambient which contains two parts, from hot-spot to case depending on the solid material and from case to ambient depending on the heat spread through the nature air. In this case study, the thermal resistance is obtained from datasheet directly which is shown in Table I. The capacitor spacing is larger than 10 mm, so that the thermal coupling between capacitors is very small.  $ESR(f_{\rm i})$  is the equivalent series resistance at frequency  $f_{\rm i}$ ,  $I_{\rm rms}(f_{\rm i})$  is the RMS value of the ripple current at frequency  $f_{\rm i}$ .

#### B. Nonlinear Damage Accumulation

1) Nonlinear Accumulated Damage Model: For electrolytic capacitors and film capacitors, a widely used lifetime model is as given in [23] and [3]:

$$L = L_0 \times (\frac{V}{V_0})^{-p_1} \times 2^{\frac{T_0 - T_h}{p_2}}$$

(4)

Fig. 3. Simulation waveforms of the standard drive with DC-link LC filter and slim capacitor filter under grid voltage balance and amplitude unbalanced conditions.

where  $L_0$ ,  $V_0$ , V,  $T_0$  and  $T_{\rm h}$  are the rated lifetime, rated voltage, real voltage, ambient temperature and hot-spot temperature of the capacitor. For film capacitors, the exponent  $p_1$  is from around 7 to 9.4, which is used by leading capacitor manufacturers. For electrolytic capacitors, the value of  $p_1$  typically varies from 3 to 5. In this paper,  $p_1=9$  for film capacitor and  $p_1=4$  for electrolytic capacitor.  $p_2$  is a coefficient around 10. From the above equation, it can be seen that the lifetime is a function of  $T_{\rm h}$  which is the hot-spot temperature of the capacitor.

The nonlinear accumulated damage model is developed to describe the real damage progress through a reliable physical basic. It is recognized that the major manifestation of damage is the ESR growth which involves many complicated processes. Based on the phenomenological recognition, one of the formulated models that accounts for the effects of growth [24], but without a specific identification is represented by

$$a = a_0 + (a_f - a_0)r^{q} (5)$$

where  $a_0$ , a, and  $a_f$  are normalized ESR growth at initial, instantaneous, and final state, respectively; q is a function of

lifetime and different stresses, which represents the degradation speed of the capacitor under operating condition. It is determined by the capacitor material, technology and different operating stresses. r is the ratio  $l_{\rm i}/L_{\rm i}$ , where  $l_{\rm i}$  and  $L_{\rm i}$  are the instantaneous equivalent operating time and total lifetime under the same loading condition, respectively. The damage under a specified stress is then defined as the ratio of the instantaneous to the final ESR raise. In most cases,  $a_0=0$ , and the damage function becomes

$$D = r^{\mathbf{q}} \tag{6}$$

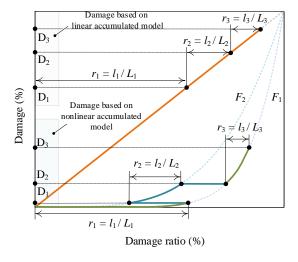

The comparisons between the linear damage model and non-linear damage model are shown in Fig. 5. The orange curve is the linear model and green curves  $F_1$  and  $F_2$  are the nonlinear models for different loading conditions. Assume three stages in the damage accumulation in Fig. 5: Stage 1 is under the first loading condition and the operating time is  $l_1$ . It can be seen that the damage with linear accumulated model is much higher than that with the nonlinear model. This significant difference can not be ignored. Stage 2 is under the second loading condition and the operating time is  $l_2$ . For the linear model

Fig. 4. Lifetime estimation procedure of DC-link capacitor.

based case, the damage will continue accumulated linearly. For the nonlinear model based case, the damage will accumulate following the damage curve of the second loading condition. Stage 3 is under the first loading condition and the operating time is  $l_3$ . It can be seen that the linear model will introduce error in the damage estimation. The mathematical model of the nonlinear accumulated damage model is discussed below. Under the first stress, the damage of the capacitor is

$$D_1 = F_1 \left(\frac{l_1}{L_1}\right) = \left(\frac{l_1}{L_1}\right)^{q_1} \tag{7}$$

where  $F_1$  is the nonlinear accumulated model. Under the second stress, the damage of the component is

$$D_2 = F_2 \left[ \frac{F_2^{-1}(D_1)L_2 + l_2}{L_2} \right] = \left[ \left( \frac{l_1}{L_1} \right)^{\frac{q_1}{q_2}} + \frac{l_2}{L_2} \right]^{q_2}$$

(8)

where  $F_2^{-1}$  is the inverse function of  $F_2$  which is the nonlinear model of the second loading condition. The extended nonlinear accumulated damage model is

$$D_{\text{tot}} = \left[ \left( \frac{l_{i-1}}{L_{i-1}} \right)^{\frac{q_{i-1}}{q_i}} + \frac{l_i}{L_i} \right]^{q_i}$$

(9)

where  $q_{i-1}$  and  $q_i$  are the coefficient of the nonlinear model for loading condition i-1 and i.  $D_{\rm tot}$  is the damage of the long-term accumulation.

2) Equivalent Hot-spot Temperature Derivation: By accumulating the damage, the dynamical stresses are converted into static values for each type of temperature stress. Taking the accumulated damage to the lifetime model, the equivalent hot-spot temperature can be derived inversely.

$$T_{\text{h,eq}} = -p_2 \ln \left[ D_{\text{tot}} \times \frac{1}{L_0} \times \left( \frac{V}{V_0} \right)^{-p_1} \right] + T_0 \qquad (10)$$

Fig. 5. Comparison of linear and nonlinear accumulated damage model.

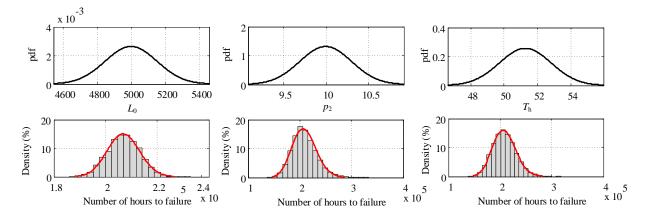

#### C. Monte-Carlo Analysis and Lifetime Prediction

The application of the lifetime model results in a fixed accumulated damage. It is far from reality since the capacitor parameter variations and the statistical properties of the lifetime model are not considered. In field operations, the time to the end-of-life for the capacitor could vary within a range due to the tolerance in physical parameters and the difference in the experienced stresses. Therefore, a statistical approach based on Monte-Carlo simulations is applied. Especially, the distributions of the temperature-related lifetime constants  $L_0$ ,  $p_2$  and the temperature tolerance-related parameter  $T_{\rm h}$  are plotted. Different values of constants result into different lifetimes. Then, the sensitivity of the lifetime to  $L_0$ ,  $p_2$  and  $T_{\rm h}$  can be evaluated individually or collectively. Finally, the

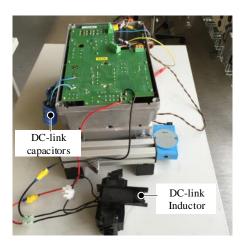

Fig. 6. Experimental prototype of the motor drive with DC-link LC filter.

distribution of the end-of-life of the capacitors can be obtained, allowing a lifetime analysis with a specified confidence level [25].

## D. Feedback for Electrical Analysis Due to Capacitance Reduction

Along with the damage accumulation, the capacitance will reduce continually and the ESR will increase corresponding to the damage ratio. In the same application, the parameters change of the capacitor lead to an increase on the electrical loading (e.g., DC-link voltage ripple and capacitor current ripple) and thermal loading (e.g., hot-spot temperature). It determines that the actual degradation of the capacitor with variable loading condition is faster than the capacitor under constant loading conditions. A feedback loop is considered in the lifetime estimation procedure as shown in Fig. 4 to represent the accelerated degradation. Therefore, the capacitance, electrical stresses and the hot-spot temperature are changing sequentially during the lifetime estimation, which matches well with the real conditions.

## IV. Lifetime Analysis of the DC-link Filters in An ASD System

An ASD system with two different DC-link configurations are considered for reliability analysis. The experimental prototype is shown in Fig. 6, and the specification of the experimental setup is shown in Table I. Even though the power rating of the system is 7.5 kW, however in many application drives operate at partial load conditions, therefore in this study we have consider three different power level: 1kW, 3kW and 5kW. The lifetime estimation for LC filter in ASD is firstly studied in terms of power rating, voltage amplitude, and voltage phase angle unbalanced conditions, while the slim capacitor in ASD is studied with the same conditions for doing a comparison. Based on the proposed capacitor lifetime estimation procedure, the measured mission profile is taken into account, offering a more realistic interpretation of the long-term loading and lifetime evaluation. In the end of this section, the relationship between lifetime and capacitance in an LC filter is investigated, which can be a guideline for sizing the capacitor.

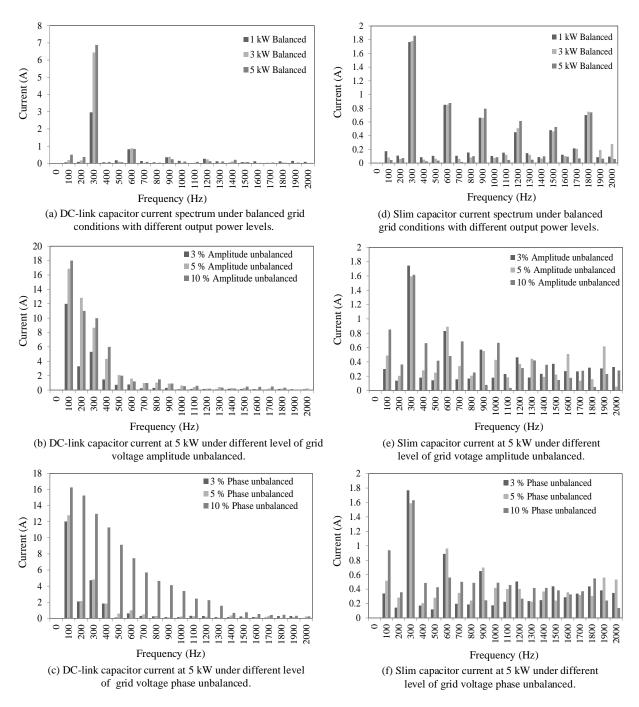

#### A. Lifetime Prediction of DC-link Filters

1) Electro-thermal Stress Analysis: The DC-link capacitor ripple current and voltage have been extensively measured under grid voltage-balanced, voltage amplitude-unbalanced and phase-unbalanced conditions. For the DC-link LC filtering configuration, the measured capacitor current spectrums under these operating conditions are shown in Fig. 7 (a), Fig. 7 (b), and Fig. 7 (c), respectively. It can be seen that: a) the harmonic component under grid voltage-balanced condition is mainly 300 Hz current. With higher power rating, the ripple component will increase. Notably, there are other harmonics existing in the spectrum, which is due to that low percentage voltage unbalance always exists during the normal operation; b) for grid voltage amplitude and phase unbalanced conditions, due to loss of symmetry in the three-phase system, 100 Hz related ripple current components become significant, which highly increases the electrical stress of the capacitor. These low-frequency harmonics will greatly alternate the electrical loadings of the DC-link capacitors. For the slim capacitor filtering configuration, the same trend as the DC-link LC filtering configuration can be found, while the capacitor current value at the frequency range 0-2 kHz are smaller. Even though the low frequency current harmonics under unbalanced condition increase more than 2 times, it is still much smaller than the capacitor current in the LC filtering configuration. Based on the above discussions, the reliability estimation under balanced grid operation conditions are no longer valid, which should be carefully considered in the design phase of the motor drive with scalable operating conditions.

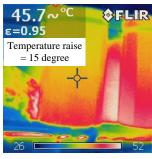

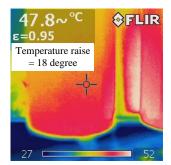

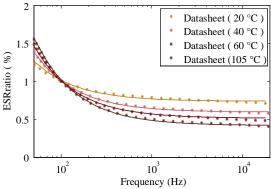

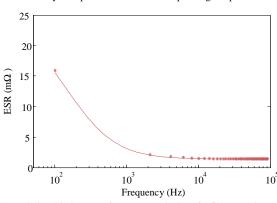

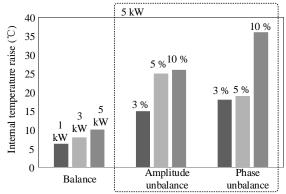

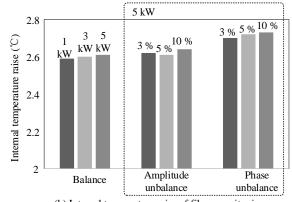

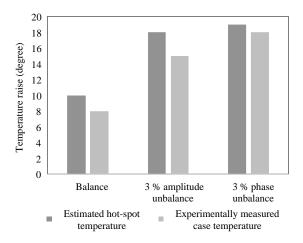

Thermal stresses are introduced by both ambient temperature and internal temperature rise due to ripple current stresses. Fig. 8 shows the frequency-dependent ESR of the applied capacitors in the DC-link LC filtering configuration for thermal loading analysis. The ESR of the electrolytic capacitor is frequency and temperature (which is ignored in the analysis) dependent. The larger ESR at low frequency range indicates that low frequency harmonics will contribute more to the total power loss and thermal loading. The thermal loading of the capacitor under different loading conditions are shown in Fig. 9. Under voltage-balanced operating conditions, the temperature variations are lower than 10 °C. Notably, as the output power level increases the thermal stresses increase as well. Under amplitude and phase angle unbalanced conditions from 3 % to 10 % unbalance levels, the thermal stresses increase severely. Especially under 5 % and 10 % voltage amplitude unbalanced conditions and 10 % voltage phase unbalanced condition, the temperature variation is higher than 20 °C. The experimental results are shown in Fig. 10, where the motor drive is tested at 5 kW under balanced, 3 % amplitude unbalanced and 3 % phase unbalanced conditions. The capacitors in the testing setup do not have temperature sensors inside, therefore the case temperature is measured for comparison. For the estimated and experimental results, the temperature difference between the estimated hot-spot temperature and the measured case temperature is around 3 degrees and the trend is the same, which is shown in Fig. 11.

Compared with the LC filtering configuration, the hot-spot

Fig. 7. Measured DC-link capacitor current spectrums under different balanced and unbalanced grid voltages.

temperature variation of the capacitor in slim capacitor filtering configuration is much smaller. There are two reasons for this effect: the capacitor current in the slim capacitor is smaller than in the LC filter as shown in Fig. 7, and the ESR of the film capacitor is much smaller than the electrolytic capacitor, especially in the low frequency range.

2) Nonlinear Damage Accumulation: The degradation effect leads to capacitance reduction, so that the electrical stresses of the DC-link capacitor are not constant. Assuming the damage is accumulated every l (l=100 in following case study) hours, the whole life cycle can be divided into fractions to update the realtime capacitance and ESR. Each consumption

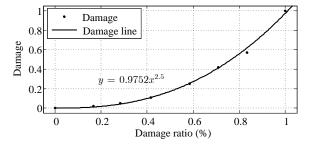

fraction is summed up to obtain the accumulated damage. Fig. 12 shows the accumulated damage model obtained from the lifetime testing results shown in [18] by curve fitting. It can be seen that ESR which is the indicator of the capacitor wear out is according to the exponent way, due to the material aging. At the beginning, the ESR is the initial value, which indicate the damage as 0. When the ESR is two times of the initial value, the capacitor assumes damage. After this time, the ESR growth rate will significantly increase. Damage ratio is defined as the ratio of measurement period and the total lifetime. Therefore, the nonlinear accumulated damage model is a function of damage ratio, which can be obtained

(a) Drive is tested at 5 kW under balanced condition.

(b) Drive is tested at 5 kW under 3 % grid voltage amplitude unbalanced condition.

(c) Drive is tested at 5 kW under 3 % grid voltage phase unbalanced condition.

Fig. 10. Experimental results of capacitor temperature in LC filtering configuration with 5 kW loading condition.

(a) Relationship between frequency and ESR ratio for 100 Hz of the electrolytic capacitor with different operating temperatures.

(b) Relationship between frequency and ESR of a film capacitor.

Frequency-dependent equivalent series resistance (ESR) of the electrolytic capacitor B43630 from EPCOS and film capacitors B32776 from EPCOS.

by curve fitting. Meanwhile, the capacitance is also a function of the damage ratio. At the beginning, the damage ratio is 0, and the capacitance is the initial value. Increasing with the damage ratio, the capacitance will reduce simultaneously. The relationship between the capacitance reduction and the damage ratio is shown in Fig. 13, which is used for updating the capacitance with different degradation ratios. Therefore, the accelerated degradation of the capacitor can be considered

3) Monte-Carlo Based Analysis: This section investigates the reliability of DC-link capacitors by taking into account the

in the lifetime estimation procedure.

(a) Internal temperature raise of electrolytic capacitor in LC filter configuration.

(b) Internal temperature raise of film capacitor in slim capacitor filter configuration.

Fig. 9. Internal temperature raise of the capacitors under different loading condition.

relevant parameter variations. Two types of uncertainties are considered: a) parameter uncertainties in the applied lifetime model; b) parameter uncertainties due to manufacturing process variations among capacitors with the same product part number. Regarding the first type of uncertainty, each lifetime model has its limitations due to the specific test conditions, component technologies, and failure mechanism considered. Therefore, the uncertainty of fitting coefficients corresponds to the thermal stress  $p_2$  is taken into account. Regarding the second type of uncertainty, the end-of-life of a large population of capacitors with the same specification and same product

Fig. 14. Probability density functions of the parameters under analysis and lifetime probability distribution function.

Fig. 11. Comparison between experimental and estimated capacitor temperature in LC filtering configuration with 5 kW loading condition.

part number varies in field operations due to variances in the manufacturing process. The variances in  $L_0$  and  $T_{\rm h}$  are taken into account in this analysis, since it has a direct effect on the capacitor lifetime. All the parameters in the analysis are modeled by means of normal probability distribution functions as shown in Fig. 14.  $p_2$ ,  $L_0$  and  $T_{\rm h}$  are assumed to have a 5 % variation, respectively, with a 90 % confidence level.

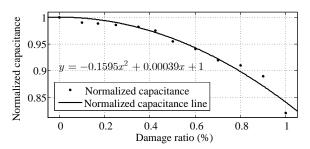

Following the lifetime estimation procedure, the lifetime of the capacitors in the LC filter are shown in Fig. 15. The study does not consider the varying loading conditions and grid conditions. Moreover, the lifetime prediction of film capacitors in the slim drive solution is limited to the electro-thermal stresses only, while humidity aspect failure mechanisms are not considered for this comparative study. Under the grid voltage-balanced condition, the lifetime of the two cases decrease with the increasing output power of the system. Compared with the conventional LC filter, the slim capacitor has longer lifetime under balanced condition. With the increase of the grid voltage-unbalanced level, the reliability behavior will change accordingly. For the LC filter, the lifetime might be significantly shortened, such as the scenarios of 5 % and 10 % amplitude unbalance, and 10 % phase unbalance. The reason is that the low frequency harmonics introduced

Fig. 12. Nonlinear accumulated damage model of capacitor.

Fig. 13. The relationship between the capacitance reduction and damage ratio.

by the unbalance condition are increasing with the unbalance level and further amplified by the resonant oscillation, where the resonant frequency of the LC filter is around 120 Hz. For the slim capacitor, under amplitude unbalance condition, the lifetime do not decrease with the increasing unbalance level. The high frequency harmonics around the resonant frequency play a critical role compared with the low frequency harmonics. But because of low ESR at whole frequency range, it has insignificant impact on the power loss, thermal loading and reliability. This study does not intend to be conclusive to a field application, since the focus of Fig. 15 is to investigate the impact of loading levels and unbalance levels on the lifetime of the DC-link capacitors. Nevertheless, Fig. 15 reveals that the grid voltage unbalances have obvious impact on the capacitor reliability, which should be taken into account in the design phase of the motor drives.

Fig. 15. Lifetime estimation results of the ASD system with two different DC-link configurations. The results do not consider the varying loading conditions and grid conditions. Moreover, the lifetime prediction of film capacitors in the slim drive solution is limited to the electro-thermal stresses only, while humidity aspect failure mechanisms are not considered for this comparative study. The lifetime in the proposed method are the B1 lifetime, which means that 1 % of the sample fails when the capacitors reach its lifetime.

## B. Mission Profile Based Lifetime Estimation of Capacitor in LC Filter

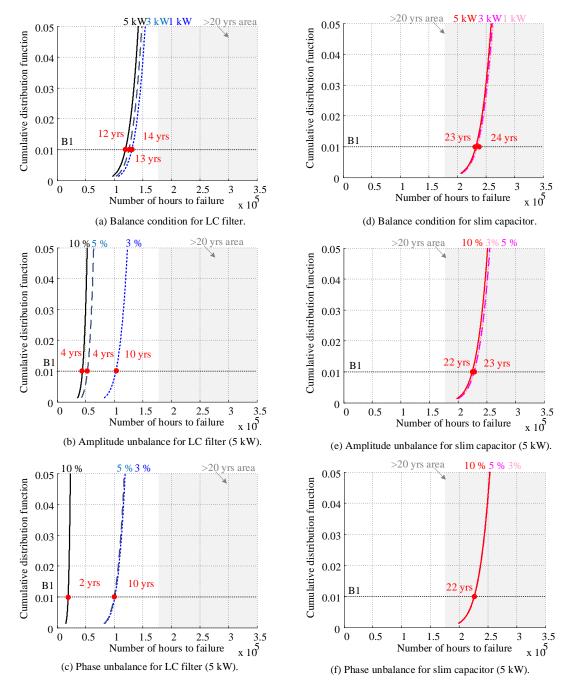

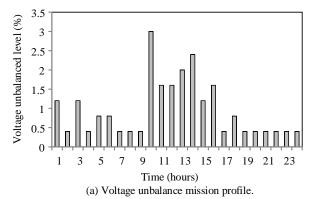

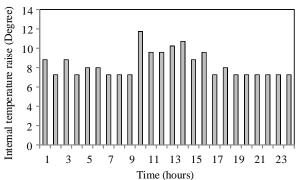

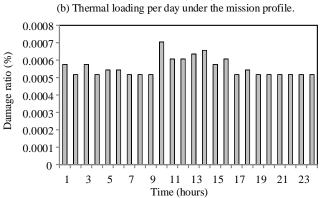

In order to evaluate the lifetime of the capacitors under real operating conditions, a mission profile, which is a representation of the operating condition of the system, is needed. In the case of the ASD application, the voltage amplitude unbalanced level is considered as mission profile, since the capacitors' lifetime are strongly dependent on the grid conditions. Fig. 16 (a) shows a one-day mission profile case from China [26]. The unbalanced level varies in a range, where the minimum value

reaches 0.4 %, and the maximum value reaches 3 %.

According to the proposed lifetime estimation procedure, the mission profile need to be translated to thermal loading at the beginning. Based on the electrical stress in a range of the voltage unbalanced levels extracted from simulation, the thermal loading under certain mission profiles can be obtained as shown in Fig. 16 (b). The hot-spot temperature in the mission profile per day varies from 7 °C to 12 °C. If ignore the grid voltage-unbalanced mission profile, the temperature variation under balanced condition is 2 °C. Based on the

(c) Damage ratio per hour under the mission profile per day.

Fig. 16. Mission profile and damage ratio of capacitor per day.

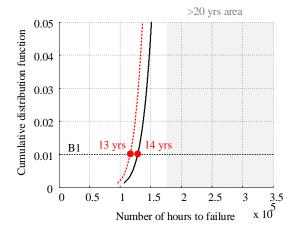

estimated thermal loading and the nonlinear accumulated damage model discussed in above section, the damage for one day can be accumulated, which is shown in Fig. 16 (c). Because of the data availability, the mission profile per day shown in Fig. 16 (a) is extended to the whole year to estimate the B1 lifetime. Fig. 17 shows the lifetime estimation results with the voltage unbalanced mission profile. The B1 lifetime of the mission profile based estimation is one year shorter than that the lifetime with the grid voltage balanced condition. It indicates the mission profile introduces a significant difference in the lifetime and can not be ignored during the lifetime estimation procedure when doing design.

### C. Capacitor Sizing Considering Reliability Performance

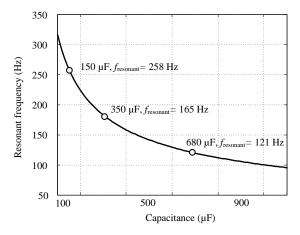

The conventional LC filter sizing criteria provide a capacitance range based on the stability analysis, while it does

Fig. 17. Lifetime comparison of a 5 kW ASD under grid voltage balanced condition (black curve) and grid voltage unbalanced mission profile (red dashed curve).

Fig. 18. Relationship between capacitance and resonant frequency of the DC-link LC filter using the parameters in Table I.

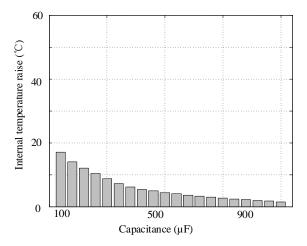

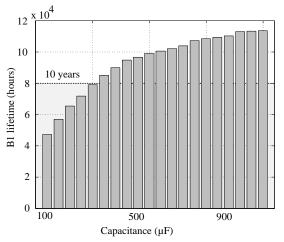

not consider reliability into the sizing procedure. This section studies the lifetime variation due to different capacitance. The range of capacitance results in different DC-link capacitor current spectrum, which will further change the lifetime of the DC-link capacitor. If the inductance is constant, the resonant frequency of the LC filter is changed with the capacitance. For a case study, the motor drive with the same series components shown in Table I and range of capacitance is investigated. The relationship between capacitance and the resonant frequency is shown in Fig. 18. In the conventional LC filter sizing procedure, the resonant frequency of the LC filter is always designed below 300 Hz to filter the six times fundamental ripple component. From the resonant frequency perspective, larger capacitance values move the resonant frequency away from 300 Hz, which will reduce the gain for the 300 Hz ripple and it has the potential to reduce the thermal loading.

The lifetime estimation procedure proposed in this paper is applied. The current spectrum with different capacitance can be obtained through a mathematical model, circuit simulation or experimental measurement. The data incorporated in the following analysis are based on simulation in Matlab R2014a.

Fig. 19. Estimated internal temperature raise of the capacitor with different capacitance under balanced condition.

Fig. 20. Estimated lifetimes of DC-link capacitor with different capacitances under balanced grid voltages.

The estimated hot-spot temperature can be seen in Fig. 19 and shows that with larger capacitance, the hot-spot temperature is reduced due to a) smaller gain for the 300 Hz ripple current, and b) larger value capacitor has smaller ESR. The estimated lifetime can be seen in Fig. 20. The lifetime will increase with the capacitance, which follows the opposite trend to the temperature. If it is assumed that 10 years is the design target under balanced conditions, the capacitance should be sized larger than 300  $\mu$ F from the reliability point of view.

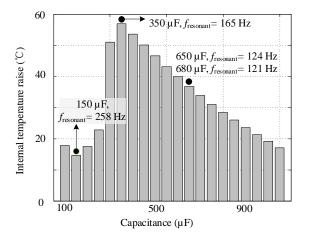

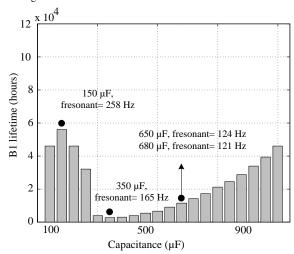

From Fig. 15, it can be seen that the lifetime of the DC-link capacitor under unbalanced conditions has different performance compared with balanced condition, and the worst case in this study is in 5 kW drive under 10 % phase angle unbalance condition. Therefore, the case study corresponding to the impact of the capacitance is based on the worst case. Following the same evaluation procedure with the balanced condition, the hot-spot temperature of the capacitors under 10 % phase angle unbalanced condition can be estimated, which can be seen in Fig. 21. The relationship between capacitance and estimated hot-spot temperature is not linear as the case study with balanced condition in Fig. 19. It not

Fig. 21. Estimated  $T_{\rm h}$  of the capacitor with different capacitance under 10 % phase angle unbalanced condition.

Fig. 22. Estimated lifetimes of the DC-link capacitor with different capacitances under 10 % phase angle unbalance condition.

only depends on the gain of the harmonics, but it is also related to the nonlinear current distribution. Fig. 22 shows the estimated lifetime of the DC-link capacitors with range of capacitance. With larger capacitance, the resonant frequency will move to lower frequency range and get closer to the harmonic frequency. When the resonant frequency is around the harmonic frequency, the shortest lifetime can be found where the capacitance is 350  $\mu$ F. With further larger capacitance value, the resonant frequency becomes even smaller and consequently reduces the gain at the harmonic frequency as well as the thermal loading of the DC-link capacitor. Based on the above estimated lifetime, it can be seen that the capacitance should be selected larger than 350  $\mu$ F in order to reach the lifetime target for both balanced and unbalanced conditions.

#### V. CONCLUSIONS

This paper investigates the reliability of the DC-link capacitors in grid-connected adjustable speed drives. A capacitor lifetime estimation procedure considering the nonlinear accumulated damage model for long-term and variable loading conditions is proposed. Based on the proposed estimation

method, the lifetime of the DC-link capacitor in a LC filter and a comparable slim capacitor DC-link filter under grid voltage balanced and unbalanced conditions are investigated. It quantifies that significant impact of power rating and grid conditions, which should be considered in the concept phase and design phase of a motor drive development. Based on the case study with the presented specification, it can be concluded that:

- 1) The lifetime of the LC filter DC-link configuration is lower than half of the slim capacitor, especially under amplitude and phase unbalance conditions;

- 2) In normal operation, the existing grid voltage-unbalanced conditions reduce the lifetime of the capacitor around 1 year. Due to the unbalanced condition existed all the time, the long-term mission profile based lifetime estimation is more compatible with the real situation.

- 3) From the reliability point of view, the capacitor in the DC-link LC filtering configuration of the motor drive should be larger than 350  $\mu$ F in order to keep lifetime longer than 10 years in the studied case.

#### REFERENCES

- F. Zare, H. Soltani, D. Kumar, P. Davari, H. A. M. Delpino, and F. Blaabjerg, "Harmonic emissions of three-phase diode rectifiers in distribution networks," *IEEE Access*, vol. 5, pp. 2819–2833, 2017.

- [2] M. Hinkkanen and J. Luomi, "Induction motor drives equipped with diode rectifier and small dc-link capacitance," *IEEE Trans. Ind. Electron.*, vol. 55, no. 1, pp. 312–320, Jan. 2008.

- [3] H. Wang and F. Blaabjerg, "Reliability of capacitors for dc-link applications in power electronic converters-an overview," *IEEE Trans. Ind. Appl.*, vol. 50, no. 5, pp. 3569–3578, Sep. 2014.

- [4] H. Wen, W. Xiao, X. Wen, and P. Armstrong, "Analysis and evaluation of dc-link capacitors for high-power-density electric vehicle drive systems," *IEEE Trans. Vehicular Tech.*, vol. 61, no. 7, pp. 2950–2964, Sep. 2012.

- [5] K. S. Rajashekara, V. Rajagopalan, A. Sevigny, and J. Vithayathil, "Dc link filter design considerations in three-phase voltage source inverter-fed induction motor drive system," *IEEE Trans. Ind. Appl.*, vol. 23, no. 4, pp. 673–680, Jul. 1987.

- [6] B. Sun, X. Fan, C. Qian, and G. Zhang, "Pof-simulation-assisted reliability prediction for electrolytic capacitor in led drivers," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 6726–6735, Nov. 2016.

- [7] VISHAY, General Technical Information.

- [8] M. Hinkkanen and J. Luomi, "Induction motor drives equipped with diode rectifier and small dc-link capacitance," *IEEE Trans. Ind. Electron.*, vol. 55, no. 1, pp. 312–320, Jan. 2008.

- [9] Council of European Energy Regulators (CEER), 5th Ceer Benchmarking Report on the Quality of Electricity Supply, 2011.

- [10] S. Elphick, P. Ciufo, G. Drury, V. Smith, S. Perera, and V. Gosbell, "Large scale proactive power-quality monitoring: An example from australia," *IEEE Trans. Power Del.*, vol. 32, no. 2, pp. 881–889, Apr. 2017.

- [11] A. V. Jouanne and B. Banerjee, "Assessment of voltage unbalance," *IEEE Trans. Power Del.*, vol. 16, no. 4, pp. 782–790, Apr. 2001.

- [12] E. P. E. A. Center, "Input performance of asds during supply voltage unbalance," *Power Quality Testing Network PQTN Brief*, no. 28, 1996.

- [13] ANSI C84. 1: American National Standard for electric power systems and equipment-voltage ratings (60 Hertz), 2006.

- [14] IEC 60038: IEC standard voltages, 2002.

- [15] K. Lee, T. M. Jahns, G. Venkataramanan, and W. E. Berkopec, "Dc-bus electrolytic capacitor stress in adjustable-speed drives under input voltage unbalance and sag conditions," *IEEE Trans. Ind. Appl.*, vol. 43, no. 2, pp. 495–504, Mar. 2007.

- [16] Y. Yang, K. Ma, H. Wang, and F. Blaabjerg, "Instantaneous thermal modeling of the dc-link capacitor in photovoltaic systems," in *Proc. IEEE APEC*, Mar. 2015, pp. 2733–2739.

- [17] ——, "Mission profile translation to capacitor stresses in gridconnected photovoltaic systems," in *Proc. IEEE ECCE*, Sep. 2014, pp. 5479–5486.

- [18] D. Zhou, H. Wang, and F. Blaabjerg, "Mission profile based system-level reliability analysis of dc/dc converters for a backup power application," *IEEE Trans. on Power Electron.*, pp. 1–1, 2017.

- [19] D. Kumar, P. Davari, F. Zare, and F. Blaabjerg, "Analysis of three-phase rectifier systems with controlled dc-link current under unbalanced grids," in *Proc. IEEE APEC*, Mar. 2017, pp. 2179–2186.

- [20] X. Pei, W. Zhou, and Y. Kang, "Analysis and calculation of dc-link current and voltage ripples for three-phase inverter with unbalanced load," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5401–5412, Oct. 2015.

- [21] H. Wang, P. Davari, D. Kumar, F. Zare, and F. Blaabjerg, "The impact of grid unbalances on the reliability of dc-link capacitors in a motor drive," in *Proc. IEEE ECCE*, Oct. 2017, pp. 4345– 4350

- [22] H. Wang, P. Davari, H. Wang, D. Kumar, F. Zare, and F. Blaabjerg, "Lifetime benchmarking of two dc-link passive filtering configurations in adjustable speed drives," in *Proc. IEEE APEC*, Mar. 2018, pp. 1–1.

- [23] S. G. Parler, "Deriving lifet multipliers for electrolytic capacitors," in *IEEE Power Electronics Society Newsletter*, vol. 16, no. 1, Feb. 2004, pp. 11–12.

- [24] A. Fatemi and L. Yang, "Cumulative fatigue damage and life prediction theories: a survey of the state of the art for homogeneous materials," *International journal of fatigue*, vol. 20, no. 1, pp. 9–34, 1998.

- [25] P. D. Reigosa, H. Wang, Y. Yang, and F. Blaabjerg, "Prediction of bond wire fatigue of igbts in a pv inverter under a long-term operation," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 7171–7182, Oct. 2016.

- [26] http://www.gzweix.com/article/sort0662/sort0664/info-305423.html.

**Haoran Wang** (S'15) received the B.S. and M.S. degrees in control science and engineering from Wuhan University of Technology, Wuhan, China, in 2012 and 2015, respectively. He is currently an PhD fellow in Center of Reliable Power Electronics (CORPE), Aalborg University, Aalborg, Denmark.

From 2013 to 2014, he was research assistant with the Department of Electrical Engineering, Tsinghua University, Beijing, China. He was a Visiting Scientist with the ETH Zurich, Switzerland, from 2017 to 2018. His research interests include reliability of

capacitors and multi-objective life-cycle performance optimization of power electronic systems.

Pooya Davari (S'11-M'13) received the B.Sc. and M.Sc. degrees in electronic engineering from the University of Mazandaran, Babolsar, Iran, in 2004 and 2008, respectively, and the Ph.D. degree in power electronics from Queensland University of Technology (QUT), Brisbane, Australia, in 2013. From 2005 to 2010, he was involved in several electronics and power electronics projects as a Development Engineer. From 2010 to 2014, he investigated and developed high-power high-voltage power electronic systems for multidisciplinary projects,

such as ultrasound application, exhaust gas emission reduction, and tissue-materials sterilization. From 2013 to 2014, he was a Lecturer with QUT. He joined, as a Postdoctoral Researcher, the Department of Energy Technology, Aalborg University, Aalborg, Denmark, in 2014, where he is currently an Associate Professor. His current research interests include EMI/EMC in power electronics, WBG-based power converters, active front-end rectifiers, harmonic mitigation in adjustable-speed drives, and pulsed power applications. Dr. Davari received a research grant from the Danish Council of Independent Research (DFF-FTP) in 2016.

Firuz Zare (S'98-M'01-SM'06) received his PhD in Power Electronics from Queensland University of Technology in Australia in 2002. He has spent several years in industry as a team leader working on power electronics and power quality projects. Prof. Zare has received several awards such as an Australian Future Fellowship, Symposium Fellowship by the Australian Academy of Technological Science, early career academic excellence research award and John Madsen Medal from Engineers Australia. He has published over 220 journal and conference

papers and technical reports in the area of Power Electronics. He is an academic staff at the University of Queensland in Australia and a Task Force Leader of Active Infeed Converters within Working Group one at the IEC standardization TC77A. Prof Zare is a senior member of IEEE, the Editor in Chief of International Journal of Power Electronics and the associate editor of IEEE Access journal. His main research areas are a) Power Electronics Topology, Control and Applications, b) Power Quality and Regulations and c) Pulsed Power Applications.

Huai Wang (M'12-SM'17) received the B.E. degree in electrical engineering, from Huazhong University of Science and Technology, Wuhan, China, in 2007 and the Ph.D. degree in power electronics, from the City University of Hong Kong, Hong Kong, in 2012. He is currently an Associate Professor at the Center of Reliable Power Electronics (CORPE), Aalborg University, Aalborg, Denmark. He was a Visiting Scientist with the ETH Zurich, Switzerland, from Aug. to Sep. 2014, and with the Massachusetts Institute of Technology (MIT), USA, from Sep. to

Nov. 2013. He was with the ABB Corporate Research Center, Switzerland, in 2009. His research addresses the fundamental challenges in modelling and validation of power electronic component failure mechanisms, and application issues in system-level predictability, condition monitoring, circuit architecture, and robustness design. Dr. Wang received the Richard M. Bass Outstanding Young Power Electronics Engineer Award from the IEEE Power Electronics Society in 2016, and the Green Talents Award from the German Federal Ministry of Education and Research in 2014. He is currently the Award Chair of the Technical Committee of the High Performance and Emerging Technologies, IEEE Power Electronics Society, and the Chair of IEEE PELS/IAS/IE Chapter in Denmark. He serves as an Associate Editor of IET POWER ELECTRONICS, IEEE JOURNAL OF EMERGING AND SELECT-ED TOPICS IN POWER ELECTRONICS, and IEEE TRANSACTIONS ON POWER ELECTRONICS.

**Dinesh Kumar** (S'08-M'12) received Master of Technology (M. Tech) in power system engineering from Indian Institute of Technology (IIT), Roorkee, India, in 2004, and Ph.D. degree in power electronics from the University of Nottingham, U.K., in 2010. From 2004-2005, he served as a Lecturer in Electrical Engineering Department at National Institute of Technology, Kurukshetra, India. In 2006, he joined Technical University Chemnitz, Germany as a Research Fellow. From 2006 to 2010, he investigated and developed matrix converter based multidrive

system for aerospace applications. Since 2011, he has been with the Danfoss Drives A/S, Denmark, where he is involved in many research and industrial projects. His current research interests include motor drive, harmonic analysis and mitigation techniques, power quality and electromagnetic interference in power electronics. He is the Editor of International Journal of Power Electronics and the Associate Editor of IEEE Transaction on Industry Applications.

Frede Blaabjerg (S'86-M'88-SM'97-F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives.

He has published more than 500 journal papers in the fields of power electronics and its applications. He is the co-author of two monographs and editor of 7 books in power electronics and its applications. He has received 24 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014 and the Villum Kann Rasmussen Research Award 2014. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2018 he is President Elect of IEEE Power Electronics Society. He is nominated in 2014, 2015, 2016 and 2017 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world. In 2017 he became Honoris Causa at University Politehnica Timisoara (UPT), Romania.