## **Aalborg Universitet**

## Three-Phase ZVR Topology and Modulation Strategy for Transformerless PV System

Guo, Xiaoqiang; Zhang, Xue; Guan, Honglei; Kerekes, Tamas; Blaabjerg, Frede

Published in: **IEEE Transactions on Power Electronics**

DOI (link to publication from Publisher): 10.1109/TPEL.2018.2849074

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Guo, X., Zhang, X., Guan, H., Kerekes, T., & Blaabjerg, F. (2019). Three-Phase ZVR Topology and Modulation Strategy for Transformerless PV System. *IEEE Transactions on Power Electronics*, *34*(2), 1017 - 1021. Article 8389205. https://doi.org/10.1109/TPEL.2018.2849074

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# Three Phase ZVR Topology and Modulation Strategy for Transformerless PV System

Xiaoqiang Guo, Senior Member, IEEE, Xue Zhang, Honglei Guan, Tamas Kerekes, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Leakage current reduction is crucial for operating transformerlss PV systems. In this letter, a new three-phase topology and modulation strategy is proposed. It is derived from the single-phase ZVR (zero-voltage state rectifier) topology, but the operation mechanism is quite different. Therefore, a new modulation strategy based on the Boolean logic function is proposed to achieve the constant common mode voltage, so as to eliminate the leakage current. Finally, the experimental tests are carried out to verify the feasibility and effectiveness of the proposed solution.

Index Terms—Transformerless PV system, inverter, modulation, leakage current

#### I. INTRODUCTION

Pulse-width modulated inverters have been typically used for transformerless PV system applications [1], [2]. However, the conventional three-phase six-switch inverter suffers from high-frequency common mode voltage, which results in the high leakage current [3]. High leakage current results in grid current distortion, electromagnetic interference and potential safety issues [4], [5]. That is the reason why many attempts have been done to reduce the leakage current in grid connected PV systems. Many interesting solutions have been presented in literature. In general, these can be classified into two groups. One group is the topology-based method [6]-[12], and the other is the modulation-based one. The latter is mainly for three-phase systems. Cavalcanti, et al, presented an improved modulation strategy [13-14]. It can achieve a constant common mode voltage to leakage current, but the modulation index is limited. Lee, et al proposed a modified modulation [15]. The idea is interesting and insightful, but the common-mode voltage is not constant for eliminating the leakage current, so there is still room for improvement. Another modulation strategy was presented for the leakage current suppression in [16], but it is limited to cascaded inverters. On the other hand, the leakage current reduction can be achieved by modifying the topology such as H5, oH5, H6, HERIC, HB-ZVR, and so on. Note that most of these are single-phase topologies. But the three-phase topologies with leakage current reduction are not well explored.

This work was supported by the National Natural Science Foundation of China (51677161) and Hundred Excellent Innovation Talents Support Program of Hebei Province(SLRC2017059).

X. Guo, X. Zhang and H. Guan are with the Department of Electrical Engineering, Yanshan University, Qinhuangdao, 066004, China (e-mail: gxq@ysu.edu.cn, 737268003@qq.com, 2478472578@qq.com).

T. Kerekes and Frede Blaabjerg are with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: tak@et.aau.dk). fbl@et.aau.dk).

Inspired by the previous work [12], a new three-phase ZVR topology is proposed. It is derived from the single-phase ZVR topology, but the operation mechanism is quite different. Therefore, a new modulation strategy based on the Boolean logic function is proposed to achieve the constant common mode voltage, so as to eliminate the leakage current. The rest of the paper is organized as follows. Section II present the operation principle and modulation strategy. Section III provides the simulation and experimental results. Conclusion is drawn in Section IV.

#### II. TOPOLOGY AND MODULATION STRATEGY

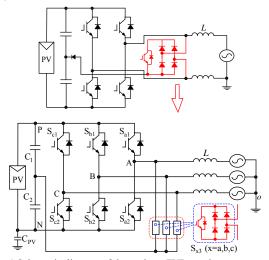

The schematic diagram of the proposed three-phase ZVR is shown in Fig.1, where the zero-voltage state rectifier (ZVR) is integrated into the three-phase six-switch inverter. Different from the single-phase ZVR topology, a special modulation procedure is needed for three-phase ZVR inverter regarding the leakage current reduction.

Fig. 1 Schematic diagram of three-phase ZVR topology

Compared with the conventional three-phase six-switch inverter, the proposed three-phase ZVR one needs more power switches. The reader might wonder whether the efficiency would be lower. In practice, the efficiency mainly depends on the switching losses, which include both switching commutation loss and conduction loss. For the latter, the conduction loss would be increased due to three more power devices. Note that the voltage stresses of three more power devices is only half of the dc bus voltage, which is much lower than those of previous six switches, so the MOSFET can be used, instead of IGBT, to reduce the conduction loss. Moreover, with the

rapid development of the wide-bandgap semiconductors such as the commercially available SiC and GaN switches [1], the conduction loss would be much smaller. For the former, the switching commutation loss with ZVR is lower than that without ZVR, since the voltage stresses of three more power devices is only half of the dc bus voltage, which is much lower than those of previous six switches. Furthermore, the conventional inverter without ZVR fails to reduce the leakage current. Therefore, the proposed three-phase ZVR topology is attractive for transformerless PV systems.

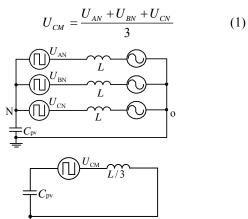

The three-phase ZVR inverter can be simplified as shown in Fig. 2, where common mode voltage is defined in (1). More details about the simplified diagram can be found in [13]. It can be observed that the leakage current can be eliminated if the common mode voltage is constant.

Fig. 2 Simplified diagram

Different from the conventional three-phase six-switch topology, the phase voltage of  $U_{AN}$ ,  $U_{BN}$  and  $U_{CN}$  have three states, depending on the switching pattern, as shown in (2), where  $U_d$  is the dc bus voltage and x=a, b, c. And the states of 2, 1, 0 are also defined in (2).

$$U_{xN} = \begin{cases} U_{d}, & "2" \ S_{x1} \ \text{on, } S_{x2} \text{and} S_{x3} \ \text{off} \\ U_{d}/2, & "1" \ S_{x3} \ \text{on, } S_{x1} \text{and} S_{x2} \ \text{off} \\ 0, & "0" \ S_{x2} \ \text{on, } S_{x1} \text{and} S_{x3} \ \text{off} \end{cases}$$

(2)

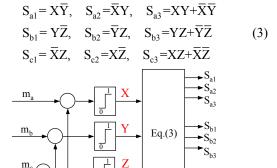

Table I shows the switching states and their corresponding common mode potential. It can be observed that there are seven groups of switching states. Note that the common mode voltage should be constant to eliminate the leakage current, so group 4 is selected in this paper. In order achieve the switching states of group 4, a new modulation strategy is proposed as shown in Fig. 3. Firstly, three modulating signals, (c.f.  $m_a$ ,  $m_b$  and  $m_c$ ) are compared with one carrier to get the three logic signals (c.f. X, Y, and Z in Table II). Secondly, three logic signals pass through the equation (3) to get the switching signals, as shown in Table II, where 9 variables of  $S_{a1} \sim S_{c3}$  are defined as follows. For example,  $S_{a1} = 1$  means the switch is on. While  $S_{a1} = 0$  means the switch is off.

Tab. I

COMMON MODE VOLTAGE AND SWITCHING STATES

Group

Switching sates

CMV

1

222

U<sub>d</sub>

| 7 | 000                               | 0                 |

|---|-----------------------------------|-------------------|

| 6 | 100, 010, 001                     | $U_d/6$           |

| 5 | 110, 101, 011, 200, 020, 002      | $U_d/3$           |

| 4 | 210, 201, 120, 102, 012, 021, 111 | $U_{\text{d}}/2$  |

| 3 | 220, 202, 022, 211, 121,112       | $2U_{\text{d}}/3$ |

| 2 | 221, 212, 122                     | $5U_d/6$          |

Fig. 3 Proposed modulation strategy

| Tab.II DETAILED SWITCHING LOGICS OF FIG. 4 |     |                 |                 |          |                 |                 |          |          |                 |         |

|--------------------------------------------|-----|-----------------|-----------------|----------|-----------------|-----------------|----------|----------|-----------------|---------|

| XYZ                                        | Sal | S <sub>a2</sub> | S <sub>a3</sub> | $S_{b1}$ | S <sub>b2</sub> | S <sub>b3</sub> | $S_{cl}$ | $S_{c2}$ | S <sub>c3</sub> | group 4 |

| 100                                        | 1   | 0               | 0               | 0        | 0               | 1               | 0        | 1        | 0               | 210     |

| 010                                        | 0   | 1               | 0               | 1        | 0               | 0               | 0        | 0        | 1               | 021     |

| 001                                        | 0   | 0               | 1               | 0        | 1               | 0               | 1        | 0        | 0               | 102     |

| 101                                        | 1   | 0               | 0               | 0        | 1               | 0               | 0        | 0        | 1               | 201     |

| 110                                        | 0   | 0               | 1               | 1        | 0               | 0               | 0        | 1        | 0               | 120     |

| 011                                        | 0   | 1               | 0               | 0        | 0               | 1               | 1        | 0        | 0               | 012     |

| 000<br>111                                 | 0   | 0               | 1               | 0        | 0               | 1               | 0        | 0        | 1               | 111     |

It should be noted that for the proposed strategy in Eq. (3) and Fig. (4), the classical duty cycles are modified so that the generated common-mode voltage is kept constant. Therefore, the duty cycles are modified, and the applied voltages at the output of the three-phase ZVR inverter are different from those of the conventional three-phase inverter, where the common mode voltage can't be kept constant with the classic modulation.

Take line 2 of Table II for example, in case of X=1, Y=0, Z=0, and

$$\begin{split} &S_{a1} = X \overline{Y} = 1, \quad S_{a2} = \overline{X} Y = 0, \quad S_{a3} = XY + \overline{X} \overline{Y} = 0 \\ &S_{b1} = Y \overline{Z} = 0, \quad S_{b2} = \overline{Y} Z = 0, \quad S_{b3} = YZ + \overline{Y} \overline{Z} = 1 \quad (4) \\ &S_{c1} = \overline{X} Z = 0, \quad S_{c2} = X \overline{Z} = 1, \quad S_{c3} = XZ + \overline{X} \overline{Z} = 0 \end{split}$$

According to definition of (2),  $S_{a1} = X\overline{Y} = 1$ ,  $S_{a2} = \overline{X}Y = 0$ ,  $S_{a3} = XY + \overline{X}\overline{Y} = 0$  means '2'.  $S_{b1} = Y\overline{Z} = 0$ ,  $S_{b2} = \overline{Y}Z = 0$ ,  $S_{b3} = YZ + \overline{Y}\overline{Z} = 1$  means '1'.  $S_{c1} = \overline{X}Z = 0$ ,  $S_{c2} = X\overline{Z} = 1$ ,  $S_{c3} = XZ + \overline{X}\overline{Z} = 0$  means '0'. Therefore, when XYZ = 100, the output will be '210' as shown in group 4. It is in agreement with the result in Table II. Other cases are similar and not duplicated here for simplicity. In this way,

the common mode voltage can be kept constant with the proposed modulation strategy of the new three-phase ZVR topology. Note that the proposed topology is similar to the conventional three-phase six-switch one, except for the additional ZVR (zero-voltage state rectifier) branch. So the design procedure is almost the same as that of the conventional one, and thus the following only provides the design procedure for the additional ZVR branch. As can be seen from the experimental results, the current stress of the ZVR is the same as that of the conventional six switches, but the voltage stress of the ZVR is much lower than that of the conventional six switches. Therefore, the design procedure is almost the same with conventional six switches, except for voltage stress. That is a low voltage rating ZVR can be designed for the proposed topology. The following will present the experimental evaluation.

#### III. EXPERIMENTAL RESULTS

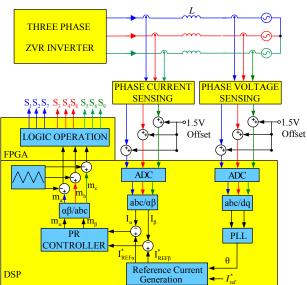

In order to verify the effectiveness of the proposed solution, the hardware experimental prototype is built and tested. The experimental parameters are listed below. The dc bus voltage is 120V, the switching frequency is 10 kHz, filter inductor is 5 mH, filter capacitors are 9.4 uF, the stray capacitor is 300 nF. As shown in Fig. 4, the reference currents of  $I_{REF\alpha}^* = I_{ref}^* \sin\theta$  and  $I_{REF\beta}^* = I_{ref}^* \cos\theta$  are generated by the reference current amplitude of  $I_{ref}^*$  and phase angular  $\theta$ , which is the output of PLL (phase-locked loop). The current is control by PR (Proportional-Resonant) controller [17]. The modulation algorithms are implemented in TMS320F28335 DSP, and the logic operations are programmed with XC3S400 FPGA.

Fig. 4 Close-loop control structure

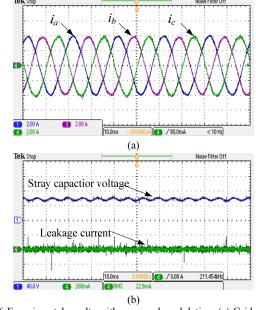

Fig.5 shows the experimental results with the dual-carrier modulation (c.f. Fig.3) of three-phase ZVR topology. It can be observed that the grid current consists of the high-frequency harmonics, which are the results of the leakage current. The total harmonic distortion (THD) is 5.9%, which fails to meet the requirements of IEEE

Standard (c.f. THD<5%). Fig. 5(b) shows the stray capacitor voltage and leakage current. Obviously, the stray capacitor voltage consists of high-frequency components. It leads to the high leakage current. The peak value of the leakage current is far beyond 300mA, as specified in VDE-0126-1-1 standard.

Fig. 5 Experimental results with the dual-carrier modulation. (a) Grid current; (b) Stray capacitor voltage and leakage current

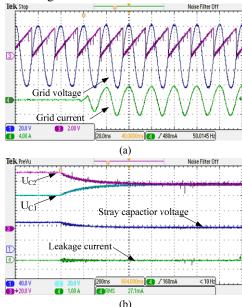

Fig. 6 Experimental results with proposed modulation. (a) Grid current; (b) Stray capacitor voltage and leakage current

Fig.6 shows the experimental results with the proposed modulation (c.f. Fig.4) of three-phase ZVR topology. It can be observed that the high-frequency harmonics of the grid is significantly reduced. The reason behind it is that the grid current consists of the common-mode and differential-mode currents. In this case, the high-frequency common-mode leakage current is small. So the total harmonic distortion of the grid current is as low as 3.5%, which is meet the requirements of IEEE Standard (c.f. THD<5%). Fig. 5(b) shows the stray capacitor voltage and leakage current. Obviously, the

stray capacitor voltage is free of any high-frequency components. Therefore, the leakage current is significantly reduced. The peak value of the leakage current is well below 300mA, which meets the VDE-0126-1-1 standard. Note that the zero sequence injection is used for the proposed carried-based modulation for the better utilization of the dc-link voltage. That is the reason why a small zero sequence component is on stray capacitor. Note that this frequency of variation is very low, so the leakage current would not be affected, as shown in Fig. 6.

Fig.7 Dynamic experiments with proposed modulation. (a) Phase\_A grid voltage and current, (b) dc-link capacitor voltages, stray capacitor voltage and leakage current

In order to further validate the effectiveness of the proposed method, the dynamic experiments are carried out in Fig. 7, where the triangular waveform is the grid synchronization signal from the phase-locked loop. In this case, the grid current changes 0 to 4A. The dc-link capacitor voltages of  $C_1$  and  $C_2$  are well balanced. The comprehensive theoretical analysis of the capacitor voltage balancing mechanism of the proposed solution is beyond the scope of this letter. And the leakage current is well below 300mA. The dynamic tests further verify the effectiveness of the proposed solution.

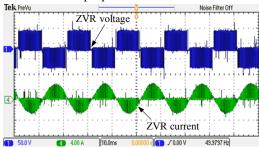

Fig.8 The current and voltage through the ZVR

The current and voltage through the ZVR are shown in Fig. 8. It can be observed that the current stress of the ZVR is the same as that of the conventional six switches, but the voltage stress of the ZVR is much lower than that

of the conventional six switches. Therefore, the power losses are lower than that of the conventional six switches. Note that the additional switches  $S_{a3} \sim S_{c3}$  and their drive circuits are needed, but the leakage current can be well suppressed, and no bulky, costly and low-efficient EMI filter is needed. Therefore, the overall performance is better than the conventional solution.

#### IV. CONCLUSION

This letter has presented the analysis and experimental verification of a new three-phase ZVR topology and its modulation strategy to eliminate the leakage current for transformerless PV systems. The findings reveal that the leakage current can be effectively reduced well below 300mA by selecting the switching states of new three-phase ZVR topology. Aside from that, the proposed modulation is simple to implement. Therefore, it is attractive for three-phase transformerless PV systems. The future research is toward the comprehensive theoretical analysis the capacitor voltage balancing mechanism of the proposed solution.

#### REFERENCE

- X. Guo, Y. Yang, and T. Zhu, "ESI: A novel three-phase inverter with leakage current attenuation for transformerless PV systems," *IEEE Trans. Ind. Electron.*, vol. 65, no. 4, pp. 2967-2974, Apr. 2018.

- [2] T. Kerekes, R. Teodorescu, M. Liserre, C. Klumpner, M. Summer, "Evaluation of three-phase transformerless photovoltaic inverter topologies," *IEEE Trans. Power Electron.*, vol.24, no.9, pp.2202-2211, Sep. 2009.

- [3] H. Xiao, L. Zhang, and Y. Li, "An improved zero-current-switching single-phase transformerless PV H6 inverter with switching loss-free," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 7896-7905, Oct. 2017.

- [4] L. Wang, Y. Shi, Y. Shi, R. Xie, and H. Li, "Ground leakage current analysis and suppression in a 60-kW 5-Level T-type transformerless SiC PV inverter," *IEEE Trans. Power Electron.*, vol.33, no.2, pp. 1271-1283, Feb. 2018.

- [5] X. Guo, J. Zhou, R. He, X. Jia, and Christian A. Rojas, "Leakage current attenuation of a three-phase cascaded inverter for transformerless grid-connected PV systems," *IEEE Trans. Ind. Electron.*, vol. 65, no.1, pp. 676-686, Jan. 2018.

- [6] Yam Siwakoti, and Frede Blaabjerg, "Common-ground-type transformerless inverters for single-phase solar photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 2100–2111 Mar. 2018.

- [7] W. Li, Y. Gu, H. Luo, W. Cui, X. He, and C. Xia, "Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression," *IEEE Trans. Ind. Electron.*, vol. 62, no. 7, pp. 4537–4551, Jul. 2015.

- [8] L. Zhang, K. Sun, Y. Xing, and M. Xing, "H6 transformerless full-bridge PV grid-tied inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 3, pp. 1229–1238, Mar. 2014.

- [9] Y. Zhou and H. Li, "Analysis and suppression of leakage current in cascaded-multilevel- inverter- based PV systems," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5265–5277, Oct. 2014.

- [10] Y. Xia, J. Roy and R. Ayyanar, "A capacitance-minimized, doubly grounded transformer less photovoltaic inverter with inherent activepower decoupling," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5188-5201, Jul. 2017.

- [11] X. Guo, "A novel CH5 inverter for single-phase transformerless photovoltaic system applications," *IEEE Trans. Circuits and Systems II: Express Briefs*, vol. 64, no. 10, pp. 1197-1201, Oct. 2017.

- [12] T. Kerekes, R. Teodorescu, P. Rodríguez, G. Vázquez, and E. Aldabas, "A new high-efficiency single-phase transformerless PV inverter topology," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 184–191, Jan. 2011.

- [13] M. C. Cavalcanti, K. C. de Oliveira, A. M. de Farias, F. A. S. Neves, G. M. S. Azevedo, and F. Camboim, "Modulation techniques to eliminate leakage currents in transformerless three-phase photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp.

- 1360-1368, Apr. 2010.

- [14] F. Bradaschia, M. C. Cavalcanti, P. E. P. Ferraz, F. A. S. Neves, E. C. dos Santos, Jr., and J. H. G. M. da Silva, "Modulation for three-phase transformerless Z-source inverter to reduce leakage currents in photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 58, no. 12, pp. 5385–5395, Dec. 2011.

- [15] J. S. Lee and K. B. Lee, "New modulation techniques for a leakage current reduction and a neutral-point voltage balance in transformerless photovoltaic systems using a three-level inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1720–1732, Apr.

2014.

- [16] X. Guo, and X. Jia, "Hardware-based cascaded topology and modulation strategy with leakage current reduction for transformerless PV systems," *IEEE Trans. Ind. Electron.*, vol. 62, no. 12, pp. 7823–7832, Dec. 2016.

- [17] F. Blaabjerg, R. Teodorescu, M. Liserre, and A. V. Timbus, "Overview of control and grid synchronization for distributed power generation systems," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1398–1409, Oct. 2006.