# **Aalborg Universitet**

# The Temperature Dependence of the Flatband Voltage in High Power IGBTs

Baker, Nicholas Raymond; Iannuzzo, Francesco

Published in:

IEEE Transactions on Industrial Electronics

DOI (link to publication from Publisher): 10.1109/TIE.2018.2854568

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Baker, N. R., & Iannuzzo, F. (2019). The Temperature Dependence of the Flatband Voltage in High Power IGBTs. *IEEE Transactions on Industrial Electronics*, *66*(7), 5581 - 5584. Article 8411445. https://doi.org/10.1109/TIE.2018.2854568

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

# Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: June 18, 2025

# The Temperature Dependence of the Flatband Voltage in High Power IGBTs

Abstract—This letter experimentally demonstrates the temperature dependence of the Flatband Voltage (V<sub>FB</sub>) in high power Insulated-Gate-Bipolar-Transistors (IGBTs). The gate voltage during the turn-on delay is shown to fluctuate up to 5mV/°C as a result of this temperature dependence. The practical implications for this temperature dependence are that the V<sub>FB</sub> could be a potential unreported addition to the genre of IGBT junction temperature measurement methods known as Temperature Sensitive Electrical Parameters (TSEPs). The letter will outline some possible measurement circuits and highlight areas for future research to enable the V<sub>FB</sub> to be used in this manner.

Index Terms—Power semiconductor devices, insulatedgate bipolar-transistor (IGBT), temperature measurement.

#### I. INTRODUCTION

In a MOS-gated device, the flatband voltage ( $V_{FB}$ ) corresponds to the voltage, which, when applied to the gate terminal yields a flat energy band in the semiconductor. This voltage separates the accumulation and depletion conditions [1].

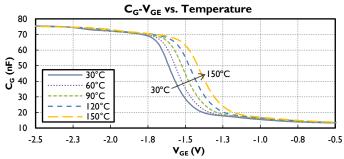

The effect of sweeping the gate voltage ( $V_{GE}$ ) from a value below the  $V_{FB}$ , to a value above the  $V_{FB}$  is shown in Fig. 1. Here, a capacitance-voltage (CV) profile of an *Infineon FS200R12PT4* IGBT module is shown. While  $V_{GE}$  is below  $V_{FB}$ , the accumulation condition is present and the gate capacitance consists of the oxide capacitance. When  $V_{GE}$  increases beyond  $V_{FB}$ , a depletion region is formed, and the gate capacitance now consists of two capacitances in series: the oxide capacitance, and the depletion capacitance. Therefore, the size of the gate capacitance decreases considerably.

Fig. 1. CV profile of an Infineon FS200R12PT4 IGBT module from 30°C to 150°C, at 50V collector-emitter voltage. 1MHz test frequency.

The temperature dependence of the  $V_{FB}$  arises from the fact that the  $V_{FB}$  equals the work-function difference between the gate metal and the semiconductor [1]. An example of this temperature dependence is displayed in Fig. 1 from 30°C to 150°C, where the  $V_{GE}$  at which the decrease in gate capacitance occurs increases approximately  $+2.5 \text{mV}/^{\circ}\text{C}$ .

### II. VFB DURING THE SWITCHING PROCESS

Since the occurrence of  $V_{FB}$  is at a negative  $V_{GE}$  below the threshold voltage ( $V_{TH}$ ), its effect can be observed during the turn-on delay of an IGBT provided that the IGBT is being driven by a gate driver with a negative turn-off voltage.

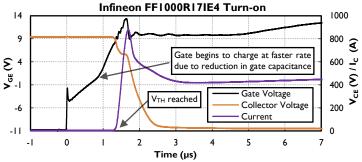

Specifically, the crossing of the  $V_{FB}$  coincides with a marked increase in the speed at which the gate is charged. This is demonstrated in Fig. 2, which shows the turn-on process of an *Infineon FF1000R17IE4* IGBT module. The turn-on process is initiated with the gate voltage at around -10.4V. Consequently, the gate driver begins to charge up a large gate capacitance (due to  $V_{GE}$  being below the value of  $V_{FB}$ ). After around 900ns, the charge on the gate capacitor reaches the level of the  $V_{FB}$ . At this point, the gate capacitance reduces sharply and the gate begins to charge significantly faster before reaching the  $V_{TH}$  approximately 400ns afterwards.

Fig. 2. Turn-on waveforms for an Infineon FF1000R17IE4 IGBT

Despite the effect of  $V_{FB}$  illustrated above, previous literature discussing the switching of IGBTs has typically omitted mentioning the influence of  $V_{FB}$  [2-4]. The variance of the gate capacitance during the turn-on delay is also not accounted for in device datasheets. For example, for the *Infineon FF1000R17IE4* from Fig. 2, the datasheet lists a gate capacitance of 81nF — while the actual capacitance the gate driver begins to charge in the period from 0ns to 900ns is actually close to 300nF.

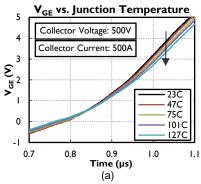

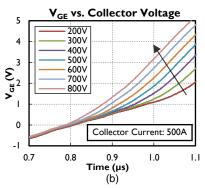

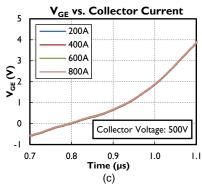

The point of inflection in the  $V_{GE}$  caused by the  $V_{FB}$  during the turn-on delay is characterised in with respect to junction temperature, DC-link voltage, and collector current in Fig. 3.

After the point of inflection, the gate voltage exhibits a negative temperature dependence of around -5mV/ $^{\circ}$ C, as shown in Fig. 3a. Figs. 3b and 3c display the dependence of V<sub>GE</sub> on collector voltage and collector current, respectively. In line with theoretical expectations, no dependence on collector current is present. Nevertheless, a large influence from the collector voltage can be seen. This data was obtained from a double pulse test on an *Infineon FF1000R17IE4* where an auxiliary IGBT is used to ramp up the inductor current. In this manner, self-

Fig. 3. Experimental waveforms of V<sub>GE</sub> around inflection point caused by surpassing of V<sub>FB</sub>, at (a) different temperatures (b) different collector voltages (c) different collector currents.

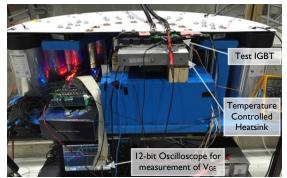

heating can be eliminated from the test IGBT [2, 5]. A photo of this setup is displayed in Fig. 4. To perform the measurements with a varied junction temperature, a temperature controlled heatsink was used.

Fig. 4. Photograph of test setup used for double pulse test

# III. V<sub>FB</sub> AS A TSEP

The junction temperature of a power semiconductor device directly influences both reliability and efficiency. Therefore, it is advantageous if the junction temperature of a power semiconductor is known.

Temperature Sensitive Electrical Parameters (TSEPs) are one popular way of estimating the junction temperature inside a power semiconductor module. This genre of measurements directly use the electrical behavior of the semiconductor as the temperature sensor. In doing so, non-invasive junction temperature measurements can be performed without any modification to standard semiconductor packaging [6-8].

The past three years have seen a significant number of proposals relating to the use of TSEPs [2-5, 9-17]. There are however several practical issues that hamper the use of TSEPs. For example, several TSEPs require measurement procedures that force significant medication to the normal operation of the semiconductor [6, 7]. Another problem is that the majority of TSEPs have a dependency on load current. These TSEPs must undergo complex calibration procedures since the load current causes self-heating in the semiconductor which consequently must be compensated for [4, 6, 7].

To the authors' knowledge, the  $V_{FB}$  has not previously been highlighted as a TSEP in prior literature. The experiments conducted in Section II were with the intention of performing a preliminary investigation on the feasibility of  $V_{FB}$  as a TSEP. The results showed that there is an attraction for further investigation since the  $V_{FB}$  was shown to be independent from

primary load current variation, and should be possible to observe solely by using measurements of the gate voltage during a normal hard-switching turn-on.

The following sections will describe two measurement circuits that we investigated for measuring the variation of the  $V_{FB}$  with junction temperature, along with mentioning the drawbacks and difficulties that we encountered.

# IV. VFB MEASUREMENT CIRCUITS

For this letter we investigated two op-amp based measurement circuits in order to trigger a  $V_{GE}$  measurement during the turn-on delay which is dependent on the temperature variation of  $V_{FB}$ . The following circuits were investigated with a combination of experimental and simulation data. The  $V_{GE}$  waveforms were acquired experimentally from an *Infineon FF1000R17IE4*, while the op-amp circuits were simulated with LTSpice using the experimental data as the input.

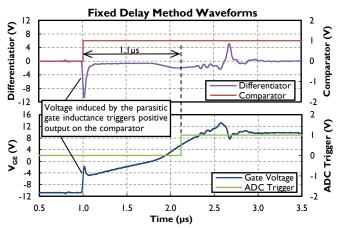

The first option is to simply sample the  $V_{GE}$  at a fixed point during the turn-on delay. This process can be made straight forward by using a differentiator op-amp, a comparator and a delay buffer. The concept is shown in Fig. 5, where the voltage induced by the parasitic gate inductance triggers a differentiator and comparator op-amp at the start of the turn-on process. After a fixed delay of  $1.1\mu s$ , the  $V_{GE}$  is sampled. The delay of  $1.1\mu s$  is selected since this is after the  $V_{FB}$  has been surpassed, but before the  $V_{TH}$  is reached and the IGBT is turned on.

Fig. 5. Waveforms for the 'Fixed Delay' measurement principle.

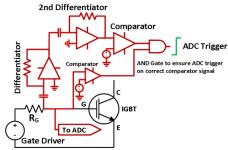

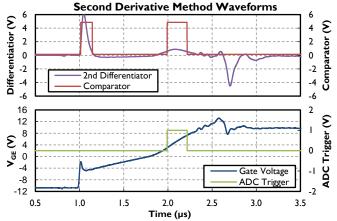

The second measurement principle is a more specific attempt to measure the  $V_{FB}$ . A schematic is included in Fig. 6 and is referred to as the 'Second Derivative Method'. Two

differentiator op-amp stages are used to identify the  $V_{GE}$  at which the fastest capacitance drop occurs (i.e. the highest point of acceleration in the charging rate). This point should correspond to the moment the  $V_{FB}$  is reached.

Fig. 6. Circuit schematic for 'Second Derivative' measurement principle.

Fig. 7. Waveforms for the 'Second Derivative' measurement principle.

Fig. 7 displays waveforms of this measurement principle. A comparator is triggered when the output of the  $2^{nd}$  differentiator stage exceeds a specified reference voltage level. It can be seen from Fig. 7 that the comparator produces two positive pulses during the turn-on process. The first is due to the parasitic inductance of the gate terminal, while the second is due to the surpassing of  $V_{FB}$  and the rapid acceleration in charging rate. Therefore, an additional comparator and an AND gate are used to ensure that the ADC is triggered on the correct transition.

# V. V<sub>FB</sub> SENSITIVITY AND TSEP DRAWBACKS

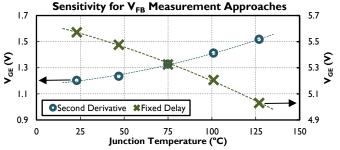

The sensitivity delivered by each measurement principle is displayed in Fig. 8. The Fixed Delay method displays a negative temperature dependence of around -5.1mV/°C. The negative dependence occurs since the  $V_{FB}$  increases with temperature. Therefore, the total capacitance charged by the gate driver is smaller at the point of sampling, and thus a higher gate voltage is achieved.

The Second Derivative method shows a positive temperature dependence of around  $+3.1 \text{mV}/^{\circ}\text{C}$ , in line with the positive sensitivity depicted in Fig. 1. However, the voltage range is between +1.2 V and +1.6 V – not a negative voltage expected from Fig. 1. This is due to the ratio between the external and internal gate resistors, which causes the measured gate voltage to overestimate the gate charge during fast transient conditions. This phenomenon is also experienced in  $V_{TH}$  measurement during full power switching [18].

Similar to other TSEP proposals based on the switching process [10-12], the  $V_{FB}$  is dependent on collector voltage (from

Fig. 3b). This is a particularly critical issue for the  $V_{FB}$  since the dependency on collector voltage is around 5mV/V. Therefore, a 1% error in collector voltage at 800V could result in an 8°C temperature measurement error. A method for compensating the influence of collector voltage is therefore essential. We have not investigated such a method in this preliminary investigation, nevertheless it is an area that must be considered in any future work on  $V_{FB}$  as a TSEP.

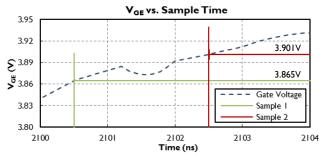

Another pertinent issue is related to the sensitivity to noise. Fig. 9 displays a close up zoom of two samples of  $V_{GE}$  taken 2ns apart. This results in 36mV discrepancy between the two samples. This is potentially a significant issue when using differentiator op-amp stages to trigger comparators if hysteresis is not carefully selected, or if there is any jitter on hardware implementation of delays. Potentially up to 7°C in temperature measurement error results from 2ns of jitter. One solution to reduce this problem would be to increase the gate resistance to several hundred  $\Omega s$  in order to significantly extend the turn-on delay [18]. This would rule out the use of  $V_{FB}$  in fully operational IGBTs, however it does not preclude it from perhaps being selected for monitoring in controlled laboratory experiments where periodic use of high gate resistances are tolerable.

Fig. 8. Waveforms for the 'Second Derivative' measurement principle.

Fig. 9.  $V_{\text{GE}}$  samples with 2-nanosecond jitter.

# VI. CONCLUSION

This letter introduces the temperature dependence of the  $V_{FB}$  in high power IGBTs. The temperature dependence of the  $V_{FB}$ , along with its influence during the turn-on process, is experimentally demonstrated. The letter suggests  $V_{FB}$  as an addition to the genre of junction temperature measurement methods known as TSEPs. Initial analysis showed the  $V_{FB}$  to be attractive as a TSEP since it is one of the few TSEPs independent of load current variation. However, the method suffers from high dependence on collector voltage and is highly susceptible to noise. The letter concludes that the  $V_{FB}$  is unlikely to be viable for real-world use as a TSEP, but may find some future use in controlled laboratory environments.

#### REFERENCES

- Simon M. Sze, Kwok K. Ng, "Physics of Semiconductor Devices," 3rd Edition, Nov. 2006.

- [2] N. Baker, S. Munk-Nielsen, F. Iannuzzo and M. Liserre, "IGBT Junction Temperature Measurement via Peak Gate Current," in IEEE Transactions on Power Electronics, vol. 31, no. 5, pp. 3784-3793, May 2016.

- [3] B. Shi, S. Feng, L. Shi, D. Shi, Y. Zhang and H. Zhu, "Junction Temperature Measurement Method for Power MOSFETs Using Turn-On Delay of Impulse Signal," in IEEE Transactions on Power Electronics, vol. PP, no. 99, pp. 1-1.

- [4] R. Mandeya, C. Chen, V. Pickert and R. T. Naayagi, "Pre-threshold Voltage as a Low Component Count Temperature Sensitive Electrical Parameter without Self-Heating," in IEEE Transactions on Power Electronics, vol. PP, no. 99, pp. 1-1.

- [5] M. Hoeer, M. Meissner, F. Filsecker and S. Bernet, "Online temperature estimation of a high-power 4.5 kV IGBT module based on the gateemitter threshold voltage," Power Electronics and Applications (EPE'15 ECCE Europe), 2015 17th European Conference on, Geneva, 2015.

- [6] Y. Avenas, L. Dupont, Z. Khatir, "Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review", IEEE Trans. Power Electron., vol.27, no.6, pp.3081-3092, June 2012.

- [7] N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods," IEEE Industrial Electronics Magazine, vol.8, no.3, pp.17-27, Sept. 2014.

- [8] D.L. Blackburn, "A review of thermal characterization of power transistors," in Proc. 4th Annu. IEEE Semicond. Therm. Temp. Meas. Symp., San Diego, CA, Feb. 10–12, 1988.

- [9] F. Forest, A. Rashed, J.-J. Huselstein, T. Martiré, P. Enrici, "Fast power cycling protocols implemented in an automated test bench dedicated to IGBT module ageing", Microelectron. Reliabil., Vol. 55, Issue 1, Pages 81-92, Jan. 2015.

- [10] V. Sundaramoorthy, E. Bianda, R. Bloch, F. Zurfluh, "Simultaneous online estimation of junction temperature and current of IGBTs using emitter-auxiliary emitter parasitic inductance," PCIM Europe 2014, 20-22 May 2014.

- [11] V. Sundaramoorthy, E. Bianda, R. Bloch, I. Nistor, G. Knapp, A. Heinemann, "Online estimation of IGBT junction temperature (Tj) using gate-emitter voltage (Vge) at turn-off," 15th European Conference on Power Electronics and Applications (EPE), 2-6 Sept. 2013

- [12] H. Luo, Y. Chen, P. Sun, W. Li and X. He, "Junction Temperature Extraction Approach With Turn-Off Delay Time for High-Voltage High-Power IGBT Modules," in IEEE Transactions on Power Electronics, vol. 31, no. 7, pp. 5122-5132, July 2016.

- [13] C. Butron, J, Alexander; B. Strauss, G. Mitic, A. Lindemann, "Investigation of Temperature Sensitive Electrical Parameters for Power Semiconductors (IGBT) in Real-Time Applications," PCIM Europe 2014, 20-22 May 2014

- [14] Z. Xu, F. Wang, P. Ning, "Junction temperature measurement of IGBTs using short circuit current", in Proc. Energy Conversion Congress and Exposition (ECCE), 15-20 Sept. 2012, pp.91-96.

- [15] M. Denk, M. Bakran, "An IGBT Driver Concept with Integrated Real Time Junction Temperature Measurement," PCIM Europe 2014, 20-22 May 2014.

- [16] L. Dupont and Y. Avenas, "Preliminary Evaluation of Thermo-Sensitive Electrical Parameters Based on the Forward Voltage for Online Chip Temperature Measurements of IGBT Devices," in IEEE Transactions on Industry Applications, vol. 51, no. 6, pp. 4688-4698, Nov.-Dec. 2015.

- [17] I. Bahun, N. Cobanov, and Z. Jakopovic, "Real-time measurement of IGBTs operating temperature," AUTOMATIKA: Journal for Control, Measurement, Electronics, Computing and Communications, vol. 54, no. 4, March 2012.

- [18] H. Chen, V. Pickert, D. J. Atkinson, L. S. Pritchard, "On-line monitoring of the MOSFET device junction temperature by computation of the threshold voltage", Proc. 3rd IET Int. Conf. Power Electronics Machine Drives, pp. 440-444, 2006-Apr.-4–6.