#### **Aalborg Universitet**

#### Investigation and Classification of Short-Circuit Failure Modes Based on Three-**Dimensional Safe Operating Area for High-Power IGBT Modules**

Chen, Yuxiang; Li, Wuhua; Iannuzzo, Francesco; Luo, Haoze; He, Xiangning; Blaabjerg, Frede

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2017.2682114

Publication date: 2018

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Chen, Y., Li, W., Iannuzzo, F., Luo, H., He, X., & Blaabjerg, F. (2018). Investigation and Classification of Short-Circuit Failure Modes Based on Three-Dimensional Safe Operating Area for High-Power IGBT Modules. *I E E E* Transactions on Power Electronics, 33(2), 1075-1086. Article 7878673. https://doi.org/10.1109/TPEL.2017.2682114

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Investigation and Classification of Short-Circuit Failure Modes Based on Three-Dimensional Safe Operating Area for High-Power IGBT Modules

Yuxiang Chen<sup>1</sup>, Wuhua Li<sup>1</sup>, Member IEEE, Francesco Iannuzzo<sup>2</sup>, Senior Member *IEEE*, Haoze Luo<sup>1,2</sup>, Xiangning He<sup>1</sup>, *Fellow IEEE*, Frede Blaabjerg<sup>2</sup>, *Fellow IEEE* (<sup>1</sup>College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China <sup>2</sup>Energy Technology Department, Aalborg University, 9220 Aalborg East, Denmark) Abstract -IGBT short-circuit failure modes have been under research for many years, successfully paving the way for device short-circuit ruggedness improvement. The aim of this paper is to classify and discuss the recent contributions about IGBT short-circuit failure modes, in order to establish the current state of the art and trends in this area. First, a 3D-SCSOA is introduced as the IGBT's operational boundary to divide the short-circuit failure modes of device into short-circuit VDC/Vrated-ISC SOA limiting and short-circuit endurance time limiting groups. Then, the discussion is centered on currently reported IGBT short-circuit failure modes in terms of their relationships with the 3D-SCSOA characteristics. In addition, further investigation on the interaction of 3D-SCSOA characteristics is implemented to motivate advanced contributions in future dependency research of device short-circuit failure modes on temperature. Consequently, a comprehensive and thoughtful review of where the development of short-circuit failure mode researches of IGBT stands and is heading is provided.

Index terms— High power IGBTs, Short-circuit failure mode, 3D-SCSOA, Self-heating, Temperature dependency

None of the material in this paper has been published or is under consideration for publication elsewhere.

Corresponding Author: Dr. Wuhua Li

College of Electrical Engineering, Zhejiang University

Hangzhou 310027, P.R. CHINA

Tel: +86-571-87952416

Fax: +86-571-87951797

Email: woohualee@zju.edu.cn

This work is sponsored by the National Basic Research Program of China (973)

Program 2014CB247400) and the National Nature Science Foundation of China

(5167716)

#### I. Introduction

Nowadays, Insulated-Gate-Bipolar-Transistors (IGBTs) are one of the most important power devices in medium and high power converter applications ranging from few hundred volts to several thousand volts [1-2]. However, recent studies also report that IGBT is the major fragile component for power conversion systems. More specifically, it accounts for nearly 34% of failures in converter systems [3-4]. Especially, in the field of high power converter applications, such as high speed traction systems and megawatt-level renewable energy generation systems, the damage could not be limited in device itself once the failure occurs. There is not so low possibility that the damage would extend to the entire facility or system. Consequently, it would cost both economically and socially expensive. Thus, it is necessary not only to minimize the device power dissipation but also to disclose the failure modes limiting the ruggedness of IGBTs under extreme operating conditions which cannot be avoided in long-term operations.

One of the most common scenarios of the extreme operating conditions for IGBTs is the short-circuit operation, under which the device is unexpectedly turned on or operating at a negligible load inductance [5-6]. As a result, a huge current flows though the IGBT only limited by the device itself, meanwhile the full DC-link voltage is held across it. Due to the large energies normally involved, an IGBT short-circuit failure can have a severe influence if left uncontrolled.

Generally, in terms of the intrinsic thermal limit of IGBTs, manufacturers can guarantee short-circuit withstand capability of commercial devices up to 10µs to

prevent the device from those direct thermal runaway failure types [7-8]. However, besides reaching this thermal limit, additional transient failure modes can occur to instantly destabilize the IGBT under the short-circuit operation, which makes the specification of  $10\mu$ s short-circuit withstand capability on longer valid. For example, the peak current failure [10-11] and self-turn-off failure [12-13] can drive the device into destruction instantly during the  $v_{ce}$ -desaturation process of short-circuit operation. So far, no withstand capability nor safe operating area (SOA) of IGBTs is specified or related to each of these transient short-circuit failure modes. Moreover, some critical operation conditions, such as the DC-link voltage, bus-bar parasitic inductances, and gate driving conditions, can even worsen the impacts of these device failure modes on the entire system. As a result, the requirements concerning short-circuit reliability and ruggedness for IGBTs in practical applications are much higher [14]. Thus, constructing the short-circuit SOA (SCSOA) to prevent the device from as many failure modes as possible is more important than ever before.

However, to enable a wide SCSOA for IGBTs, one key starting point is to fully understand the limiting impacts of different failure modes on the device short-circuit ruggedness. It is of great importance to disclose the detailed relationships between the IGBT short-circuit failure modes and SCSOA boundaries. Therefore, the main focus of this paper is on this topic. More specifically, this paper is structured as follows. In Section II, A three-dimensional SCSOA (3D-SCSOA) is proposed first to classify the device short-circuit failure modes as the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA limiting group and short-circuit endurance time limiting group. Basing on it, the present

reported device short-circuit failure modes covered by the upper two groups are respectively reviewed and discussed in Section III and Section IV, in terms of their connections with the 3D-SCSOA characteristics. Moreover, in Section V, the interaction of 3D-SCSOA characteristics is pointed out to motivate further investigation of dependencies of different device short-circuit failure modes on temperature. Finally, some conclusions are drawn in Section VI.

#### II. 3D-SHORT-CIRCUIT SAFE OPERATING AREA FOR IGBT MODULES

In general, for IGBTs, the traditional SCSOA is specified as the short-circuit endurance time  $t_w$  in terms of the device thermal runaway limit induced by the energy accumulation [7-9]. It is usually characterized as an index how long an IGBT can withstand the thermal accumulation until the protection circuit can shut off the unexpected large short-circuit current safely. But, as mentioned in Section I, except those direct thermal runaway failure types, some transient failure modes can still occur to immediately destroy the device. Thus, it is necessary not only to define  $t_w$  for those direct thermal runaway failure modes but also to specify SCSOA for those transient failure types, in order to maintain sufficient short-circuit ruggedness for the IGBT.

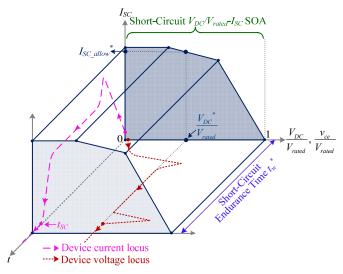

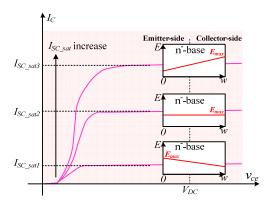

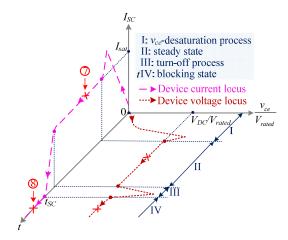

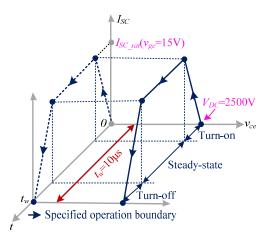

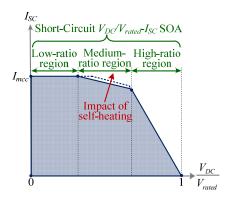

Therefore, a 3D-SCSOA for IGBTs is proposed and illustrated in Fig.1, of which  $I_{SC}$  is the short-circuit current and t stands for the short-circuit operation time. In general, for a given IGBT, the maximum voltage that can be sustained by the device is its rating voltage  $V_{rated}$ . Therefore, the full-voltage range that can be applied to the device is approximate to  $(0V \sim V_{rated})$ . Meanwhile, the full-voltage range of the

3D-SCSOA for a given IGBT is also  $(0V\sim V_{rated})$ . In order to describe the voltage sustaining condition across the device within its full-voltage range  $(0\sim V_{rated})$ , the voltage ratio  $V_{DC}/V_{rated}$  between the applied DC-link voltage  $V_{DC}$  and  $V_{rated}$  is used to define the device 3D-SCSOA instead of directly using  $V_{DC}$ . Under this scenario, the full-voltage range of the device 3D-SCSOA can be accordingly expressed as  $(0\sim 1)$ .

Fig.1. 3D-SCSOA characteristics for IGBT (using short-circuit type II operation of device as an example,  $v_{ce}$  is the device collector-emitter voltage,  $t_{SC}$  is the short-circuit operation time)

In Fig.1, except for the classical  $t_w^*$  specified by the direct thermal runaway failure modes, a new short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA is added for those transient failure types. Thus, the IGBT 3D-SCSOA is made up of two characteristics, namely the short-circuit endurance time and short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA. Actually, basing on the detailed failure mechanism, for each of those transient short-circuit failures, a  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA exists which can guide the device operation to avoid the corresponding failure occurring. Consequently, the overlap region of these individual  $V_{DC}/V_{rated}$ - $I_{SC}$  SOAs will form the final short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA for an IGBT. As shown in Fig.1, for the given DC-link voltage  $V_{DC}$ \*, the maximum allowable

short-circuit current  $I_{SC\_allow}^*$  is specified for the device by this final short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA. Thus, keeping short-circuit current locus of an IGBT lower than  $I_{SC\_allowe}^*$  can guarantee the device getting rid of all of those transient failures at the  $V_{DC}^*$  case.

Moreover, in terms of the intrinsic thermal limit of IGBTs,  $t_w$  has distinct dependencies on  $I_{SC}$  and  $V_{DC}$ . Therefore, for each of the individual short-circuit operation condition ( $V_{DC}/V_{rated}$ ,  $I_{SC}$ ) located at the boundary of the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA, the corresponding value of  $t_w$  should be different. For example, in Fig.1,  $t_w^*$  is the short-circuit endurance time corresponding to the short-circuit operation condition ( $V_{DC}^*/V_{rated}$ ,  $I_{SC\_allow}^*$ ). In other words,  $t_w^*$  represents the maximum allowable short-circuit operation time at the  $V_{DC}^*$  and  $I_{SC\_allow}^*$  case, that can guide the protection circuit to activate timely (namely keeping  $t_{SC} \leq t_w^*$ ) and avoid driving the device into directly thermal runaway failure types.

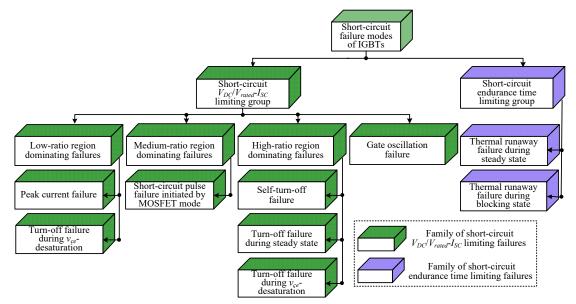

Fig.2. IGBT short-circuit failure modes classification

Consequently, the IGBT short-circuit failure modes can be accordingly classified into the short-circuit  $V_{DC}/V_{rated}$ -Isc limiting group and short-circuit endurance time

limiting group. The overview of the present reported short-circuit failure types of IGBTs are summarized and highlighted in Fig.2. The detailed analysis and discussion will be addressed in the following sections.

## III. SHORT-CIRCUIT $V_{DC}/V_{RATED}$ - $I_{SC}$ SOA LIMITING GROUP

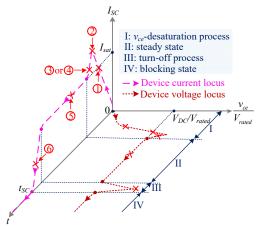

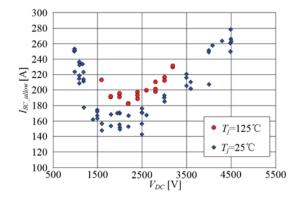

In this section, a comprehensive survey of short-circuit  $V_{DC}/V_{rated}$ -Isc SOA limiting failure modes is presented and discussed. As illustrated in Fig.3, six distinct failure modes of an IGBT may occur to instantly drive the device to destruction at different time during short-circuit type II operation. The same is true for the short-circuit type I operation with a lager parasitic inductance.

Fig.3. IGBT transient failure modes during short-circuit type II operating (①turn-off failure during  $v_{ce}$ -desaturation, ②peak current failure, ③self-turn-off failure, ④gate oscillation failure, ⑤short-circuit pulse failure initiated by MOSFET mode, ⑥turn-off failure during steady state)

However, as limiting factors for the device short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA, these six transient failures will compete with each other to play the dominating role within the device full-voltage range. As for which one will attract more attentions mainly depends on their dependencies on the voltage sustained by the device during the short-circuit operations [9, 15-20]. In other words, within the device full-voltage

range ( $0V\sim V_{rated}$ ), different voltages applied across the device will result in different dominating-failures during the short-circuit operations. As defined in Section II, the voltage ratio  $V_{DC}/V_{rated}$  is used to describe the voltage applied condition across the device within the device full-voltage range. Thus, the dependencies of six different transient failures on the applied voltage can be characterized by this voltage ratio.

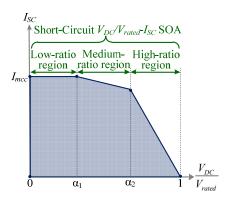

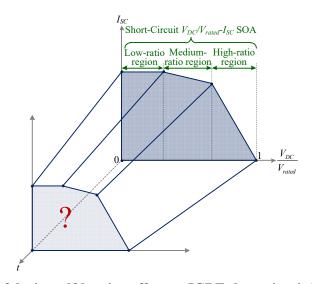

Consequently, in terms of different voltage-dependent properties of these six transient failures, the full-voltage range (0~1) of the device short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA can be accordingly divided into three regions, namely: low-ratio, medium-ratio and high-ratio region, seeing Fig.4. Meanwhile, the dominating transient failures corresponding to each region have been classified into the same subgroups, as the low-ratio region dominating failures, medium-ratio region dominating failures, and high-ratio region dominating failures, as displayed in Fig.2. As for the detailed voltage-dependent characteristics of these transient failures, they will be explained in the following parts relating to each subgroup.

Fig.4. Dependency of IGBT short-circuit V<sub>DC</sub>/V<sub>rated</sub>-I<sub>SC</sub> SOA on V<sub>DC</sub>

Moreover, as mentioned in Section II, the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA of an IGBT is actually the final overlap region of each of the individual  $V_{DC}/V_{rated}$ - $I_{SC}$  SOAs corresponding to six different transient failure modes. However, after incorporating

the dependencies of different failure modes on the applied voltage, the device short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA can be formed by three individual  $V_{DC}/V_{rated}$ - $I_{SC}$  SOAs. They are respectively corresponding to the low-ratio region, medium-ratio region and high-ratio region dominating subgroups. More specifically, for each transient-failure subgroup, a maximum allowable short-circuit current  $I_{SC\_allow}$  at a given  $V_{DC}/V_{rated}$  can be predicted to the device. It is the last-past short-circuit current of the device without triggering the corresponding transient failure at the given  $V_{DC}/V_{rated}$ . As shown in Fig.4,  $\alpha_1$  and  $\alpha_2$  are respectively the voltage-ratio values of the cross-points between these three  $V_{DC}/V_{rated}$ - $I_{SC}$  SOAs. However, the detailed building process of this final short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA is out of the range of this paper.

#### A. Low-Ratio Region Dominating Failures

Peak current failure is generally considered as the predominant limiting factor for the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA at low  $V_{DC}/V_{rated}$  applications [8-9, 15-18]. It means that this peak current failure has the highest possibility to be triggered when the applied  $V_{DC}$  across the device is belongs to the low-ratio region of the device full voltage range (0V~ $V_{rated}$ ). It can be usually connected with the latch up of the intrinsic parasitic thyristor inside the IGBT [9, 21] and expected to occur close to peak current during the short-circuit operation as shown in Fig.3.

As known to all, IGBT is characterized by its MOS channel capability in current self-limiting which can saturate the device short-circuit current [9, 13]. But when the latch up of the internal parasitic thyristor is activated, this current self-limiting capability will be malfunctioned immediately. Then, a continual increase is observed

of the device short-circuit current, eventually resulting in the peak current failure. This is to say, this peak current failure limits the maximum controllable current  $I_{mcc}$  of IGBT which is also the upper current boundary of device short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA at the low-ratio region of the device full-voltage range, seeing Fig. 4.

Actually, for today's commercial IGBTs, they are relatively less sensitive to this failure than those old generations due to the advanced latch-up suppress designs [22]. It is especially the case when the short-circuit current is homogeneously distributed between the cells. Therefore, recent research focus about this latch-up mechanism has gradually transformed to as a subsequent failure mechanism initiated by the current inhomogeneity phenomenon, such as the current filamentation effect [23-24].

However, if the holes sustained by extracting the n<sup>-</sup>-base region electron-hole plasma take part in the current transport, the IGBT sensitivity to this latch-up mechanism will increase significantly. It is the generally called dynamic latch-up phenomenon, for which the maximum controllable current is much lower comparing with the one determined by the former latch-up effect [21]. Meanwhile, this dynamic latch-up phenomenon can be generally connected with a high-plasma turn-off process, especially at the low  $V_{DC}/V_{rated}$  applications [25-26]. As for the short-circuit operation, the turn-off condition during the  $v_{ce}$ -desaturation process before  $v_{ce}$  reaches  $V_{DC}$  is a typical high-plasma turn-off case [27]. Therefore, under this scenario, in combination with a low  $V_{DC}/V_{rated}$  application, the impact of the dynamic latch-up mechanism will set in to result in a turn-off failure during the  $v_{ce}$ -desaturation process, as displayed in Fig.3. Thus, it generally must be ensured that a hard turn-off is not initiated before  $v_{ce}$

rises to  $V_{DC}$ . Otherwise, this turn-off failure during the  $v_{ce}$ -desaturation process will severely shrink the low-ratio region boundary of the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA defined by the former peak current failure.

#### B. Medium-Ratio Region Dominating Failures

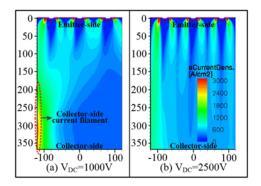

With the increase of the applied  $V_{DC}$ , the maximum allowable short-circuit current  $I_{SC\_allow}$  for a given  $V_{DC}$  specified by the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA will be lower than  $I_{mcc}$  determined by the former latch-up relating failure types. It is the short-circuit pulse failure initiated by the MOSFET mode that limits  $I_{SC\_allow}$  at the medium  $V_{DC}/V_{rated}$  region of the device full-voltage range [15, 27-28]. It can be generally triggered by a current filamentation effect of the device operating under the MOSFET mode and characterized as a typical failure type for the steady state of short-circuit process (as shown in Fig.3).

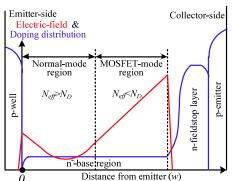

As mentioned above, the MOSFET-mode operation of IGBT plays a critical role in activating this failure [14-15, 27, 29-32]. Comparing with the normal-mode operation, the most distinct difference of it is the location of the electric-field peak  $E_{max}$  inside the n<sup>-</sup>-base region. More specifically, under the MOSFET-mode operation,  $E_{max}$  can shift from the emitter-side p-well/n<sup>-</sup>-base junction to collector-side n<sup>-</sup>-base/field-stop junction with the rising short-circuit saturated current  $I_{SC\_sat}$ , seeing Fig.6. In contrast,  $E_{max}$  is typically located at the emitter-side p-well/n<sup>-</sup>-base junction for the normal-mode.

Further, under this scenario, the impact of  $V_{DC}$  on the operation-mode transformation sets in [15, 27]. Especially, for a medium  $V_{DC}/V_{rated}$  application within

the device full-voltage range, a mixed situation with the normal mode operating at the emitter side and MOSFET mode operating at the collector side of n<sup>-</sup>-base region develops, seeing Fig.7. It is the critical condition to accelerate and sustain a current self-constraint process inside the IGBT which can be readily initiated by any potential inhomogeneity due to the manufacturing [27]. As a result, a collector-side current filament will form inside the device and leads to an instant destruction of an IGBT at the short-circuit steady state.

Fig.6. Transformation of  $n^-$ -base region electric-field distribution E with increasing current under MOSFET-mode operation (output characteristic is displayed in the background,  $I_C$  is the device collector current, w is the distance from the emitter side.)

Fig.7. Mixed operation mode of device at medium DC-link voltage application ( $N_{eff}$ : effective doping concentration of n<sup>-</sup>-base,  $N_D$ : intrinsic doping concentration of n<sup>-</sup>-base)

In contrast, this mixed operation condition would be replaced by a full normal-mode or MOSFET-mode operation inside the  $n^-$ -base region, respectively for the low  $V_{DC}/V_{rated}$  and high  $V_{DC}/V_{rated}$  applications. Then, the necessary condition for

the self-enhancing formation of current filament is missing. In other words, this collector-side current filament is more possible to form at the medium  $V_{DC}/V_{rated}$  application for a given  $I_{SC\_sat}$  within the device full-voltage range (as displayed in Fig.8) [15, 27]. Therefore, the boundary of short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA at the medium-ratio region is usually limited by this short-circuit pulse failure.

Fig.8. Electron current density of a 3.3kV IGBT for different DC-link voltages during steady-state phase of short-circuit [15]

Moreover, an optimized large bipolar current gain  $\beta_{PNP}$  is pointed out that can enable the device to avoid the MOSFET mode and prevent the device from this short-circuit pulse failure [33]. As for the value of  $\beta_{PNP}$ , it is directly related to the device collector-side design, such as the thickness and doping profile of the field-stop layer and p-emitter layer [34-35].

#### C. High-Ratio Region Dominating Failures

As explained in Part B, the IGBT ruggedness to resist the upper short-circuit pulse failure increases with the rising  $V_{DC}$ . Thus, at high  $V_{DC}/V_{rated}$  region of the device full-voltage range, this failure mode is less crucial for restricting  $I_{SC\_allow}$ , and then there comes the influence of turn-off failures [20, 32, 36]. For an IGBT operating under short-circuit conditions, three different kinds of turn-off failures probably occur to destroy the device. They are respectively the turn-off failure during the

*vce*-desaturation process, self-turn-off failure and turn-off failure during the steady state, as presented in Fig.3.

Further, these three turn-off failures can be distinguished by whether a high-concentration electron-hole plasma exists in the n<sup>-</sup>-base region or not during the initial short-circuit turn-off process. As mentioned in Part A, the turn-off failure during the  $v_{ce}$ -desaturation process is generally triggered during a high-plasma turn-off transition. In contrast, the latter two failure modes usually take place without a high-plasma inside the n<sup>-</sup>-base region [27-28]. Actually, the corresponding turn-off processes for them are initiated after  $v_{ce}$  reaches  $V_{DC}$ , under which the electron-hole plasma stored in the n<sup>-</sup>-base region has been exhausted. Therefore, comparing with the turn-off failure during the  $v_{ce}$ -desaturation process, the latter two failure modes can all get rid of the impacts of the electron-hole plasma. However, a distinct difference of the initial turn-off mechanism exists between them.

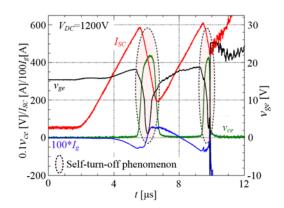

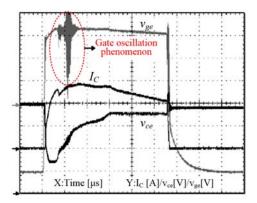

More specifically, for the self-turn-off failure, the negative differential Miller capacitance effect generally sets in to drive the IGBT turning itself off rather than receiving a turn-off signal from the superior control [12, 28]. It is a typical IGBT unstable mechanism for short-circuit types with the  $v_{ce}$ -desaturation process, such as the short-circuit type I with large parasitic inductances or short-circuit type II. In general, it can be characterized by a negative displacement current flowing though the device Miller capacitance, which initiates the discharge of the gate-emitter capacitance [37-38]. Consequently, a self-turn-off phenomenon is activated with a drop in the gate voltage  $v_{ge}$  after  $v_{ce}$  reaches  $V_{DC}$  during the  $v_{ce}$ -desaturation process, as

#### illustrated in Fig.9.

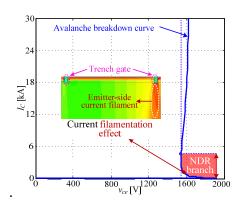

Besides, the failure characterization and mechanism of the latter two turn-off failures are almost the same. As for the underlying failure mechanism, another current filamentation effect caused by the negative differential resistance (NDR) region is the necessary destruction precondition [28, 36, 39-40]. Differing from the former collector-side current filament forming under the MOSFET-mode operation, this one appears at the emitter-side of the IGBT. Moreover, the indispensable triggering condition for it is that the device is operating at the NDR branch of the avalanche breakdown curve, initiated by strong avalanche breakdown inside the IGBT (as displayed in Fig.10). Meanwhile, the critical role of the device bipolar current gain  $\beta_{PNP}$  in generating this NDR branch of the device avalanche breakdown curve has been indicated by many researches [28, 34-35]. As presented in Part B,  $\beta_{PNP}$  can be adjusted and optimized by the IGBT collector-side designs.

Fig.9. IGBT self-turn-off phenomenon during  $v_{ce}$ -desaturation process under short-circuit type II operation [28]

In addition, for this emitter-side filamentary current, two different kinds of current-filament form exist, respectively leading to different subsequent failure mechanisms for the IGBT. More specifically, one is the static current filament which

will directly drive the device into thermal runaway [41]. In contrast, the other one is the hopping current filament, of which the latch up of the corresponding cells is more likely to be triggered as a subsequent failure mechanism [42]. As for the factors that influence the forms of the current filament, both the layout of the chip level and gate drive voltage are of great importance [43-44]. Especially, the chip-level layout, it can be generally connected with an interplay between the device active and termination region. It plays a crucial role in determining the detailed form and location of the current filament inside the device. Meanwhile, in terms of different turn-off voltages applied at the device gate terminal, this interplay between the device active and termination region can be correspondingly weakened or strengthened.

Fig.10. 1700V/1000A IGBT avalanche breakdown curve and current distributing characteristics

Generally, in terms of the avalanche breakdown during the IGBT turn off, no high plasma exists inside the  $n^-$ -base region will distinctly improve the avalanche ruggedness of the device [45]. As a result, the designed static voltage blocking capability  $V_{rated}$  of the IGBT can be more fully utilized under a self-turn-off process or a turn-off process during the steady state. This is to say, the relative values of the triggering voltages for the self-turn-off failure and turn-off failure during the steady

state against  $V_{rated}$  are more approaching to 1. In other words, as limiting factors for the IGBT short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA, these two turn-off failures will play dominating roles in high-ratio region of the device full-voltage range [20, 32, 39].

However, as introduced in Part A, for a high-plasma turn-off process, the holes extracted from the n<sup>-</sup>-base region plasma will participate in the transport of the  $I_{SC}$ . At the high  $V_{DC}/V_{rated}$  applications, the avalanche breakdown effect is more sensitive to this hole extraction phenomenon than the latch-up effect, which will weaken the avalanche ruggedness of the device [20, 27]. This is the usually called dynamic avalanche phenomenon. Moreover, at high  $V_{DC}/V_{rated}$  cases, it is the major failure mechanism for the turn-off failure during the  $v_{ce}$ -desaturation process before  $v_{ce}$  reaches  $V_{DC}$ . Thus, the high-ratio region boundary specified by the former self-turn-off failure and turn-off failure during the steady state will be further shrunk by this turn-off failure. In combination with the low  $V_{DC}/V_{rated}$  case presented in Part A, a short-circuit turn off is generally recommended that should not be initiated before  $v_{ce}$  reaches  $v_{DC}$ , in order to enable a wide short-circuit  $v_{DC}/v_{rated}$ - $v_{DC}$ -so SOA.

#### D. Gate Oscillation Failure

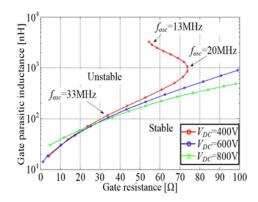

Differing from the upper investigated six failure modes, a stability map defined by the gate parasitic inductance and gate resistance is usually specified to the gate oscillation failure mode instead of a  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA, as displayed in Fig.11 [46].

In general, this gate oscillation failure is initiated by the gate oscillation phenomenon (illustrated in Fig.12). Due to the fact that this unstable oscillation phenomenon can be usually connected with the negative differential Miller

capacitance effect [48], thus it is also a typical failure mode for the IGBT operating at the short-circuit condition with a  $v_{ce}$ -desaturation process.

Fig.11. Stability map for device gate oscillation phenomenon at  $V_{DC}$ =400V, 600V and 800V; for some point, the oscillation frequency is also reported [46]

Fig.12. Gate oscillation phenomenon under short-circuit type I with large parasitic inductance [47]

More specifically, this failure mode is intrinsically triggered by the interaction among the equivalent negative Miller capacitance, gate parasitic inductance and gate resistance. Above all, the equivalent negative Miller capacitance can further enable a more readily condition for a diverging and unstable gate oscillation which would finally result in the gate oxide breakdown of the IGBT [49]. However, as mentioned at the beginning of this part, a stability map usually can be specified to help the device avoiding this diverging oscillation phenomenon.

#### IV. SHORT-CIRCUIT ENDURANCE TIME LIMITING GROUP

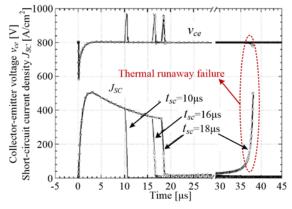

In this section, a review of the short-circuit endurance time limiting failure types is explored. More specifically, two potential short-circuit failure modes that limit the device short-circuit endurance time  $t_w$  are illustrated in Fig.13. One is the thermal runaway failure during the steady state ( $\bigcirc$ ), the other one is the thermal runaway failure during the blocking state ( $\bigcirc$ ) [26, 50-51]. Both of them are initiated by the thermal accumulation during the short-circuit pulse without any other failure mechanism setting in.

Fig.13. IGBT short-circuit endurance time limiting failure types during short-circuit type 2 operating

#### A. Thermal Runaway Failure During Steady-state

In general, due to the large current and high voltage characteristics of the short-circuit steady state, a huge amount of energy is deposited in the IGBT which will result in a high rise in the device temperature. Further, without timely shutting off this large short-circuit current, the IGBT temperature would eventually reach the device critical thermal runaway limit. As a result, the doped silicon becomes intrinsic and the IGBT voltage blocking capability deteriorates due to the burn down of the device [52]. This is why and how the traditional SCSOA (namely the short-circuit

endurance time  $t_w$ ) is specified and defined by the device manufacture. As shown in Fig.13, a 10 $\mu$ s of  $t_w$  under specified short-circuit operation conditions (as listed in Table I) is generally guaranteed by the device manufacture. In other words, operating within the specified operation boundary, the IGBT can enable itself at least 10 $\mu$ s withstand capability for the energy accumulation without triggering the thermal runaway failure during the short-circuit pulse.

Fig.13. Traditional SCSOA boundary in 3D for INFINEON 3.3kV/1.5kA IGBT

TABLE I. SPECIFIED OPERATION CONDITIONS FOR TRADITIONAL SCSOA

DEFINITION OF INFINEON 3.3kV/1.5kA IGBTs

| Operation Condition                             | Value |

|-------------------------------------------------|-------|

| Gate voltage $v_{ge}$                           | 15V   |

| DC-link voltage $V_{DC}$                        | 2500V |

| Case temperature $T_C$                          | 125℃  |

| Maximum allowable junction temperature $T_{vj}$ | 150℃  |

Nowadays, the manufactures devote themselves in enlarging  $t_w$  for IGBTs. In Fig.13, during the short-circuit pulse, the high amount of energy  $E_{SC}$  deposited in the device can be approximately calculated by

$$E_{SC} = V_{DC} \times I_{SC \quad sat} \times t_w \tag{1}$$

of which the critical energy  $E_{SC}$  accumulated in the device to activate the thermal runaway failure is almost uniquely limited by the silicon material itself [8]; Moreover,  $V_{DC}$  is also constant in the general application. Thus, the only solution to extend  $t_w$  for

an IGBT is to maintain *IsC\_sat* sufficiently low. In general, this can be realized by the optimized design of the IGBT cell structure, such as the advanced wide cell pitch CSTBTs (carrier stored trench-gate bipolar transistors) from Mitsubishi [8].

#### B. Thermal Runaway Failure During Blocking-State

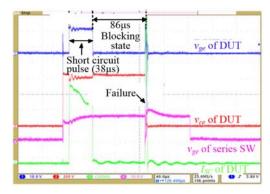

As mentioned above, an IGBT can generally avoid the former thermal runaway failure under the guidance of  $t_w$ . Nowadays, the device thermal runaway failure is actually more likely to occur during the blocking state rather than during the steady state of short-circuit operation, as illustrated in Fig.14 [26].

Fig.14. IGBT short-circuit failure by thermal runaway at 86μs after safety turn-off [26]

In Fig.14, after successful withstanding the short-circuit operation of 38µs, the device under test (DUT) is turned off safely. But, this IGBT is still destroyed by a thermal runaway failure after 86µs of the turn off. This type of thermal runaway failure can be usually connected with the high-temperature leakage current caused by the heat spreading from the IGBT p-well/n<sup>-</sup>-base junction to the collector-side layer after the short-circuit turn-off process [27-28].

More specifically, in the blocking state, the IGBT collector side will be heated up by the energy accumulated during the short-circuit pulse, due to the heat diffusing. Then, the influence of  $\beta_{PNP}$  which is mainly determined by the IGBT collector-side

properties sets in. As a result, in terms of the positive temperature-dependent  $\beta_{PNP}$ , the leakage current I<sub>leakage</sub> that flows though the IGBT during the blocking state increases with the rising device collector-side temperature [53]. Thus, in this scenario, a high leakage current in combination with the full DC-link voltage across the device would drive the IGBT into a destructive self-heating loop with a thermal runaway failure as a practical operations, various factors Moreover, producing inhomogeneous operation inside the device definitely exist, which will accelerate this failure occurring [54]. For example, for a multi-cell IGBT chip, considering the possible deviations in the threshold voltage, transconductance and so on, it is obvious that the short-circuit current should have some variations for each unit cell. Thus, the local region in active area, which has the largest applied energy, will obviously more possible to suffer this thermal runaway failure. Besides these electrical-property deviations, the distributions in the thermal parameters of the IGBT module are also important to investigate the cause of the inconsistencies. Consequently, this thermal runaway failure during the blocking state also plays an important role in limiting  $t_w$  of the device, as presented in Fig.15 [54].

Fig.15. IGBT short-circuit waveforms for different short-circuit operation time  $t_{SC}$  [54] Nowadays, the device manufactures also try to help the IGBT getting rid of this

type of the thermal runaway failure. As explained above, it can be intrinsically ascribed to the positive dependency of  $\beta_{PNP}$  on temperature. Currently, a field-stop layer with a deep-level doping (such as the selenium) is used to mitigate or even eliminate this positive dependency of  $\beta_{PNP}$  on temperature [55-56]. In addition, optimized layout designs of the device chip level and module level are also promising ways to help to improve the device ruggedness for this thermal runaway failure.

#### V. INTERACTION INVESTIGATION OF 3D-SCSOA CHARACTERISTICS

The evolution of researches on the short-circuit failures over the last two decades has paved the way for several state-of-the-arts in the device ruggedness and reliability improvement. Basing on this well-developed area, as summarized in this paper, some further investigation on future constructing the device 3D-SCSOA can be implemented.

As introduced in Section II, the 3D-SCSOA is made up of two different characteristics, namely the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA and short-circuit endurance time  $t_w$ . They are respectively specified to guide the IGBT to avoid the two short-circuit failure groups classified above. More specifically, for the two thermal runaway failure modes presented in Section IV, at least 10 $\mu$ s of  $t_w$  can be generally guaranteed by the manufactures. In contrast, so far, no available short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA has been realistically reported for those transient failure modes displayed in Section III. But it is of great importance to guide the IGBT surviving the extreme short-circuit operations. Moreover, the well-investigated connections between those transient failure modes and boundaries of the SOA, as summarized in

Section III, have laid a good foundation for further predicting the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA. Therefore, more attention should be paid to the construction of this short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA.

However, some interactions exist between these two 3D-SCSOA characteristics that would impose some critical impacts on the construction of the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA. As mentioned in Section IV, IGBT would be heated up by the deposited energy during the short-circuit pulse. However, considering the thermal diffusing capability of an IGBT module, the 10 $\mu$ s duration of the short-circuit operation is not long enough to propagate the heat from the silicon chip to the baseplate of the IGBT module. Thus, it is the silicon chips that mainly being heated up. Therefore, the temperature rise  $\Delta T_{SC}$  of the silicon chip during short-circuit pulse can be approximately calculated in terms of the device thermal capacity and regardless of the thermal conduction [6, 28]

$$\Delta T_{SC} = \frac{V_{DC} \times I_{SC\_sat} \times t_w}{c_{th,si} \times \rho \times d \times A}$$

(2)

Where  $c_{th,si}$  and  $\rho$  are the specific heat capacitance and density of the silicon, d and A are the thickness and active area of the chip. Then, form (2), it can be proved that the thin-chip IGBT modules will have a strong temperature rise during the short-circuit operation, seeing Table II [28]. Meanwhile, the collector side of the thin-chip IGBT is also more probable to be heated up during the short-circuit pulse.

Nowadays, the thin-wafer technology has paved its wave for various ratings of IGBT modules with high performance and reliability [57-58]. This is to say such a severe self-heating effect inside the device cannot be ignored any longer under the

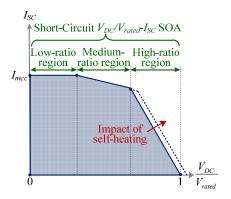

short-circuit conditions. Moreover, it can be intensified with the extending of the device short-circuit endurance time  $t_w$ . On the other hand, this device self-heating effect would impose strong impacts on operating behaviors of the IGBT during the short-circuit pulse, especially, those device unstable behaviors limited by the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA. Whereas, the boundaries of the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA should change with the duration of the short-circuit operation, in order to fit those temperature-dependent transient failure modes, as illustrated in Fig.16. As for detailed variation trends of each of these boundaries, further investigations should focus on dependencies of the transient failure modes (investigated in Section III) on temperature.

**TABLE II.** TEMPERATURE RISE COMPARISON BETWEEN LOW-VOLTAGE IGBT CHIP (INFINEON) AND HIGH VOLTAGE IGBT CHIP (ABB) [28]

| Chip Parameter                                | LV IGBT            | HV IGBT             |

|-----------------------------------------------|--------------------|---------------------|

| Voltage Rating V <sub>rated</sub>             | 600V               | 4.5V                |

| Current Rating $I_{rated}$                    | 200A               | 55A                 |

| Short-circuit Endurance Time $t_w$            | 10μs               | 10μs                |

| Short-circuit Saturated Current $I_{SC\_sat}$ | 730A(360V)         | 200A(3.4kV)         |

| Chip Thickness d                              | 70μm               | 530µm               |

| Chip Active Area A                            | $99.5 \text{mm}^2$ | $205.5 \text{mm}^2$ |

| $\Delta T_{SC} (T_{start} = 400 \text{K})$    | 204K               | 24K                 |

As described above, the heat is primarily deposited in the IGBT chip during the steady state of the short-circuit operation. Thus, an assumption can be made, namely the self-heating effect doesn't come into play until the beginning of the steady state. Therefore, from Fig.3, the short-circuit pulse failure initiated by the MOSFET mode and turn-off failure during the steady state are more possible to suffer the impact of this self-heating phenomenon than others.

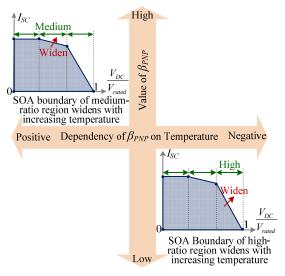

For the short-circuit pulse failure initiated by the MOSFET mode, the

self-heating effect mainly sets in though the temperature-dependent  $\beta_{PNP}$ . As mentioned in Section III, a large  $\beta_{PNP}$  can strengthen the device ruggedness to avoid this failure. Thus, when the self-heating effect is involved, a positive temperature-dependent  $\beta_{PNP}$  can contribute to this device ruggedness improvement. Under this scenario, as shown in Fig.17, the maximum allowable short-circuit current  $I_{SC\_allow}$  that the device can withstand before this short-circuit pulse failure is activated increases with the rising temperature at a given  $V_{DC}$ .

Fig.16. Impacts of device self-heating effect on IGBT short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA

Fig.17. 6.5kV IGBT ruggedness for short-circuit pulse failure induced by MOSFET mode under two different starting temperatures [27]

Thus, the corresponding medium-ratio region boundary of the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA should accordingly extend to a higher current level for a given

$V_{DC}/V_{rated}$ , as illustrated in Fig.18.

Fig.18. Impact of IGBT self-heating effect on medium-ratio region boundary for positive temperature-dependent  $\beta_{PNP}$  condition

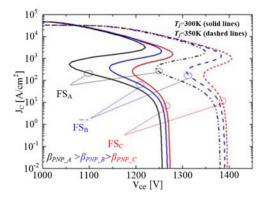

Next, coming to the turn-off failure during the steady state, there has two possible ways for the device self-heating effect to impose its impacts. One is through the temperature-dependent impact ionization coefficient, the other one is still though the temperature-dependent bipolar current gain. As disclosed in Section III, the shape of the device avalanche breakdown curve plays an important role in triggering this turn-off failure. Thus, the dependency of this turn-off failure on temperature is actually determined by the influences of the temperature-dependent impact ionization coefficients and bipolar current gain on the avalanche curve shape, seeing Fig.19.

Fig.19. Impacts of temperature on IGBT avalanche breakdown curve for three FS structures [35]

In Fig.19, the IGBT avalanche breakdown curve shifts to a much higher voltage

region with the increasing temperature. It is mainly caused by the negative dependency of the carrier impact ionization coefficients on temperature. Thus, for a high temperature case, IGBT can sustain a much higher voltage level before this turn-off failure is triggered. Consequently, the high-ratio region boundary of the device short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA should correspondingly shifts to a higher voltage-ratio region for a given short-circuit current, as presented in Fig.20.

Fig.20. Impact of device self-heating effect on high-ratio region boundary of short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA

What's more, a negative temperature-dependent  $\beta_{PNP}$  can further improve the device turn-off ruggedness by confining the development of the NDR branch on the device avalanche breakdown curve. In Fig.19, the extension of the NDR branch shrinks with the rising temperature, resulting in a decreasing possibility for the current-filament formation during the short-circuit turn off. Thus, being opposite to the former short-circuit pulse failure, a negative temperature-dependent  $\beta_{PNP}$  would be more preferable for this short-circuit turn-off failure.

However, for currently widespread trench gate/field-stop IGBTs, a positive or negative dependency of  $\beta_{PNP}$  on temperature is actually determined by the field-stop layer design. A field-stop layer with a deep-level doping is more likely to have a

negative temperature dependency, while a shallow-level doped one is more possible to be enabled with a positive temperature dependency [55-56]. Therefore, a careful trade-off between the device medium-ratio and high-ratio region ruggedness under the short-circuit conditions should be considered into the further  $\beta_{PNP}$  design, see Fig.21.

Fig.21. Trade-off between device ruggedness for medium-ratio and high-ratio region dominating failure modes in terms of optimized design of  $\beta_{PNP}$

### VI. CONCLUSION

The present state of the art about the IGBT short-circuit failure modes has been investigated and classified into the short-circuit  $V_{DC}/V_{rated}$ - $I_{SC}$  SOA limiting and short-circuit endurance time limiting groups by introducing a 3D-SCSOA for IGBTs. At this point, the detailed relationships between eight short-circuit failure modes and 3D-SCSOA boundaries of the IGBT have been proposed and identified, giving a deep insight into the limiting effects of these failure modes on the device short-circuit ruggedness. Moreover, a self-heating effect during the short-circuit pulse has been discussed. It points out the importance of the dependency investigation of IGBT short-circuit failure modes on temperature for further device short-circuit

$V_{DC}/V_{rated}$ - $I_{SC}$  SOA construction. Meanwhile, the critical roles of  $\beta_{PNP}$  and its temperature-dependency in device short-circuit ruggedness and SOA optimizations have also been disclosed. Consequently, a comprehensive and thoughtful overview of the short-circuit failure modes of the IGBT has been provided, which will drive and shape the future of IGBT short-circuit ruggedness and 3D-SCSOA improvements.

# References

- [1] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, J. Rodriguez, M. A. Perez, J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [2] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, "Operation, control, and applications of the modular multilevel converter: A review," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 37-53, Jan. 2015.

- [3] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran, and P. Tavner, "An Industry-Based Survey of Reliability in Power Electronic Converters," *IEEE Trans. Ind. Appl.*, vol. 47, no. 3, pp. 1441-1451, May/June 2011.

- [4] U. M. Choi, F. Blaabjerg, K. B. Lee, "Study and Handling Methods of Power IGBT Module Failures in Power Electronic Converter Systems," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2517-2533, May 2015.

- [5] J. Lutz, R. Dobler, J. Mari, M. Menzel, "Short circuit III in high power IGBTs," *13th Euro. Conf. on Power Electronics and Applications*, 2009, pp.1-8.

- [6] J. Lutz. Semiconductor Power Devices: Physics, Characteristics, Reliability. Berlin: Springer Verlag, 2011.

- [7] R. S. Chokhawala, J. Catt, L. Kiraly, "A discussion on IGBT short-circuit behavior and fault protection schemes," *IEEE Trans. Ind. Appl.*, vol. 31, no. 2, pp. 256-263, Mar./Apr. 1995.

- [8] T. Minato. Safety Operation Area Based Design Methodology for Gate

- Controlled Power Semiconductor Device. Application manual, PSRC Industrial Scholar form Mitsubishi Electric Company, 2014.

- [9] B. J. Baliga. Fundamentals of Power Semiconductor Devices. New York: Springer Verlag, 2008.

- [10] T. Shoji, M. Ishiko, S. Kawaji, T. Sugiyama, K. Hotta, T. Fukami, K. Hamada, "Investigation of Short-circuit Capability of IGBT under High Applied Voltage Conditions," *R&D Review of Toyota CRDL*, vol. 39, no. 4, pp. 22-26, Sem. 2004.

- [11] R. Wu, F. Blaabjerg, H. Wang, M. Liserre, and F. Iannuzzo, "Catastrophic failure and fault-tolerant design of IGBT power electronic converters—An overview," *in Proc. 39th Annu. Conf. IEEE Ind. Electron. Soc.*, Nov. 2013, pp. 507–513.

- [12] T. Basler, J. Lutz, T. Brückner and R. Jakob, "IGBT Self-Turn-Off under Short-Circuit-Condition," *in Proc. ISPS*, 2010.

- [13] J. Lutz, T. Basler, "Short-circuit ruggedness of high-voltage IGBTs," 28th Int. Conf. on Microelectronics, 2012, pp. 243-250.

- [14] H.-J. Schulze, F.-J. Niedernostheide, F. Pfirsch, and R. Baburske, "Limiting factors of the safe operating area for power devices," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 551–562, Feb. 2013.

- [15] A. Kopta, M. Rahimo, and U. Schlapbach, "Limitation of the short-circuit ruggedness of high-voltage IGBTs," *in Proc. ISPSD*, 2009, pp. 33–36.

- [16] N. Iwamuro, B. J. Baliga, R. Kurlagunda, G. Mann, "Comparison of RBSOA of ESTs with IGBTs and MCTs," in Proc. ISPSD, 1994, pp. 195-200.

- [17] B. You, A. Q. Huang, "Theoretical limitation of the RBSOA of MOS-controlled thyristors," *Solid-State Electronics*, vol. 42, no. 5, pp. 785–794, May. 1998.

- [18] Yin Liu, Budong You, A. Q. Huang, "Reverse-bias safe operation area of large area MCT and IGBT," *Solid-State Electronics*, vol. 47, no. 1, pp. 1–14, Jan. 2003.

- [19] N. Lophitis, M. Antoniou, F. Udrea, B. D. Friedelm, "The Destruction Mechanism in GCTs," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 819–

- 826, Feb. 2013.

- [20] R. Baburske, F. J. Niedernostheide, H. J. Schulze, F. Pfirsch, "Low-inductive power systems to overcome short-circuit ruggedness limits," *in Proc. ISPSD*, 2016, pp. 323–326.

- [21] V. K. Khanna. Insulated Gate Bipolar Transistor IGBT Theory and Design. New Jersey: Wiley-IEEE Press, 2009.

- [22] A. Muller, F. Pfirsch, and D. Silber, "Trench IGBT behaviour near to latch-up conditions," in Proc. *IEEE Int. Symp. Power Semicond. Devices*, May 2005, pp. 255–258.

- [23] C. Toechterle, F. Pfirsch, C. Sandow, G. Wachutka, "Evolution of current filaments limiting the safe-operating area of high-voltage trench-IGBTs," *in Proc. ISPSD*, *2014*, pp. 135–138.

- [24] C. Toechterle, F. Pfirsch, C. Sandow, G. Wachutka, "Analysis of the latch-up process and current filamentation in high-voltage trench-IGBT cell arrays," *in Proc. 18th SISPAD*, 2013, pp. 296-299.

- [25] A. Bhalla, S. Shekhawat, J. Gladish, J. Yedinak, "IGBT behavior during desat detection and short circuit fault protection," in Proc. 10th ISPSD, 1998, pp. 245-248.

- [26] Z. Xu, M. Li, F. Wang, and Z. Liang, "Investigation of Si IGBT operation at 200°C for traction application," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2604-2615, May. 2013.

- [27] A. Kopta. Short-Circuit Ruggedness of High-Voltages IGBTs, University of Bremen, 2010.

- [28] T. Basler. Ruggedness of High-Voltage IGBTs and Protection Solutions, Chemnitz University of Technology, 2014.

- [29] T. Matsudai, A. Nakagawa, "Ultra high switching speed 600 V thin wafer PT-IGBT based on new turn-off mechanism," *in Proc. 14th ISPSD*, 2002, pp. 285-288.

- [30] A. Nakagawa, T. Matsudai, M. Yamaguchi, "MOSFET-mode ultra-thin wafer PTIGBTs for soft switching application -theory and experiments," *in Proc. 16th*

- ISPSD, 2004, pp. 103-106.

- [31] M. Tanaka, A. Nakagawa, "Simulation studies for short-circuit current crowding of MOSFET-Mode IGBT," *in Proc. 26th ISPSD*, 2014, pp. 119-122.

- [32] R. Baburske, V. V. Treek, F. Pfirsch, F. J. Niedernostheide, "Comparison of critical current filaments in IGBT short circuit and during diode turn-off," *in Proc. 26th ISPSD*, 2014, pp. 47-50.

- [33] M. Rahimo, A. Kopta, U. Schlapbach, "A study of switching-self-clamping-mode "SSCM" as an over-voltage protection feature in high voltage IGBTs," *in Proc. 17th ISPSD*, 2005, pp. 67-70.

- [34] P. Spirito, G. Breglio, A. Irace, L. Maresca, "Physics of the Negative Resistance in the Avalanche I-V Curve of Field Stop IGBTs: Collector Design Rules for Improved Ruggedness," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp.1457– 1463, Mar. 2014.

- [35] P. Spirito, , L. Maresca, M. Riccio, G. Breglio, "Effect of the Collector Design on the IGBT Avalanche Ruggedness: A Comparative Analysis Between Punch-Through and Field-Stop Devices," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2535-2541, Jul. 2015.

- [36] T. Basler, R. Bhojani, J. Lutz, R. Jakob, "Dynamic self-clamping at short-circuit turn-off of high-voltage IGBTs," *in Proc. ISPSD*, 2013, pp. 277–280.

- [37] J. Böhmer, J. Schumann, H. G. Eckel, "Negative differential miller capacitance during switching transients of IGBTs," *in Proc. 14th EPE*, 2011, pp. 1-9.

- [38] J. Böhmer, J. Schumann, H. G. Eckel, "Effect of the miller-capacitance during switching transients of IGBT and MOSFET," *in Proc. 15th EPE/PEMC*, 2012, pp. LS6d.3-1-LS6d.3-5.

- [39] T. Basler, R. Bhojani, J. Lutz, R. Jakob, "Measurement of a complete HV IGBT I-V-characteristic up to the breakdown point," *13th Euro. Conf. on Power Electronics and Applications*, 2013, pp.1-9.

- [40] B. Riteshkumar, T. Basler, J. Lutz, R. Jakob, "IGBTs working in the NDR region of their I-V characteristics," *Electronics and Energetics*, vol. 28, no. 1, pp. 1–15, Mar. 2015.

- [41] C. C. Shen, A. R. Kefner, D. W. Berning, J. B. Bernstein, "Failure dynamics of the IGBT during turn-off for unclamped inductive loading conditions," *IEEE Trans. Ind. Appl.*, vol. 36, no. 2, pp. 614-624, Mar./Apr. 2000.

- [42] G. Breglio, A. Irace, E. Napoli, M. Riccio, P. Spirito, "Experimental Detection and Numerical Validation of Different Failure Mechanisms in IGBTs During Unclamped Inductive Switching," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 563-570, Dec. 2012.

- [43] K. Perpina, I. Cortes, J. U. Ibanez, X. Jorda, J. Rebollo, "Layout Role in Failure Physics of IGBTs Under Overloading Clamped Inductive Turnoff," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 598-605, Feb. 2013.

- [44] M. Riccio, L. Maresca, A. Irace, G. Breglio, Y. Iwahashi, "Impact of gate drive voltage on avalanche robustness of trench IGBTs," *Microelectronics Reliability*, vol. 54, no. 9-10, pp. 1828-1832, Sep./Oct. 2014.

- [45] J. Lutz and R. Baburske, "Dynamic avalanche in bipolar power devices", *Microelectronics Reliability*, vol. 52, no. 3, pp. 475-481, Mar. 2012.

- [46] C. Abbate, G. Busatto, A. Sanseverino, F. Velardi, "Analysis of Low- and High-Frequency Oscillations in IGBTs During Turn-On Short Circuit," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2952-2958, Sept. 2015.

- [47] A. Volke, M. Hornkamp. IGBT Modules: Technologies, Driver and Application.

Munich: Infineon Technologies AG, 2012.

- [48] C. Ronsisvalle, H. Fischer, K. S. Park, C. Abbate, "High Frequency Capacitive behavior of field stop trench gate IGBTs operating in Short Circuit," *IEEE Appl. Power Electron. Conf. and Expo.*, 2013, pp. 183-188.

- [49] P. D. Reigosa, R. Wu, F. Iannuzzo, F. Blaabjerg, "Evidence of Gate Voltage Oscillations during Short Circuit of Commercial 1.7 kV / 1 kA IGBT Power Modules," in Proc. PCIM Europe, 2015, pp. 1-8.

- [50] S. Lefebvre, Z. Khatir, F. Saint-Eve, "Experimental behavior of single-chip IGBT and COOLMOS devices under repetitive short-circuit conditions," *IEEE Trans. Electron Devices*, vol. 52, no. 2, pp. 276–283, Feb. 2005.

- [51] X. Perpina, X. JOrda, J. Leon, M. Vellvehi, D. Anton, S. Llorente, "Comparison

- of temperature limits for Trench silicon IGBT technologies for medium power applications," *Microelectronics Reliability*, vol. 54, no. 9-10, pp. 1839-1844, Sep/Oct 2014.

- [52] C. Raynaud, D. Tournier, H. Morel, D. Planson, "Comparison of high voltage and high temperature performances of wide bandgap semiconductors for vertical power devices," *Diamond and Related Materials*, vol. 19, no. 1, pp. 1–6, Jan. 2010.

- [53] L. Storasta, S. Matthias, A. Kopta, M. Rahimo, "Bipolar transistor gain influence on the high temperature thermal stability of HV-BiGTs," in Proc. 24th ISPSD, 2012, pp. 157-160.

- [54] M. Otsuki, Y. Onozawa, H. Kanemaru, Y. Seki, "A study on the short-circuit capability of field-stop IGBTs," *IEEE Trans. Electron Devices*, vol. 50, no. 6, pp.1525–1531, Jun. 2003.

- [55] S. Voss, H. J. Schulze, F. J. Niedrnostheide, "Optimization of the temperature dependence of the anode-side current gain of IGBTs by field-stop design," *in Proc. 22th ISPSD*, 2010, pp. 141-144.

- [56] H. J. Schulze, S. Voss, H. Huesken, F. J. Niedernostheide, "Reduction of the temperature dependence of leakage current of IGBTs by field-stop design," in Proc. 23th ISPSD, 2011, pp. 120-123.

- [57] J. F. Donlon, E. R. Motto, T. Takahashi, H. Fujii, "Chip Improvements for Future IGBT Modules," in Proc. IEEE Ind. Appl. Soc. Annu. Meeting, 2008, pp. 1–7. M.

- [58] Rahimo, "Future trends in high-power bipolar metal-oxide semi-conductor controlled power semi-conductors," *IET Circuits, Devices & Systems*, vol. 8, no. 3, pp.155–167, Jun. 2014.