### **Aalborg Universitet**

#### A DDS-Based Wait-Free Phase-Continuous Carrier Frequency Modulation Strategy for **EMI Reduction in FPGA-Based Motor Drive**

Chen, Y.; Yang, M.; Long, J.; Xu, D.; Blaabjerg, F.

Published in: **IEEE Transactions on Power Electronics**

DOI (link to publication from Publisher): 10.1109/TPEL.2019.2891572

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Chen, Y., Yang, M., Long, J., Xu, D., & Blaabjerg, F. (2019). A DDS-Based Wait-Free Phase-Continuous Carrier Frequency Modulation Strategy for EMI Reduction in FPGA-Based Motor Drive. *IEEE Transactions on Power* Electronics, 34(10), 9619-9631. Article 8606101. https://doi.org/10.1109/TPEL.2019.2891572

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# A DDS-Based Wait-Free Phase-Continuous Carrier Frequency Modulation Strategy for EMI Reduction in FPGA-Based Motor Drive

Yangyang Chen, Ming Yang, Senior Member, IEEE, Jiang Long, Dianguo Xu, Fellow, IEEE, Frede Blaabjerg, Fellow, IEEF

Abstract- In AC motor drives, the fixed-frequencies harmonic components of output voltage and current from the inverter with fixed frequency pulse width modulation (FFPWM) usually lead to electromagnetic interference (EMI). The spread spectrum clock generation (SSCG) is a widely used solution of this problem. Adjusting the switching frequency to reduce EMI is one kind of practicable scheme among SSCG methods. How to design an optimal or suitable modulation profile is a research emphasis of scholars and has been discussed in depth in many literatures. However, apart from modulation profile, the mode and quality of carrier are also important and can be improved. In most frequency modulation methods, due to the limitation of the conventional carrier generation mode, the implementation of the new frequency instruction has to wait to the termination of the last switching period. In order to eliminate the waiting state and design a simpler algorithm, this paper has proposed a wait-free phase-continuous carrier frequency modulation strategy (WPCFM) by combining the direct digital frequency synthesizer (DDS) theory and proper temporal planning of control interruptions. Besides, theoretical analysis of WPCFM including quantization error, frequency jitter, phase delay and voltage distortion have been finished. Moreover, compared with conventional methods, a more convenient, feasible and simpler field-programmable gate array (FPGA) based algorithm implementation method and the control structure of WPCFM are also introduced. Analysis shows that, although WPCFM causes a slight increase of the current ripple, it can solve the partial frequency nonuniform distribution problem of conventional method and it has potential value of applications in the wide band gap (WBG) motor drive systems. The effectiveness of the WPCFM is verified by several sets of EMI reduction experiments where classical periodic carrier frequency modulations are applied.1

Index Terms—Direct digital frequency synthesizer, spread spectrum frequency modulation, EMI, motor drive, FPGA.

#### NOMENCLATURE

N Register bit.

M Counting threshold.

*n* Step number.

*K* DDS step length.

R Steps to complete each period.

*P* Phase delay.

$U_E$ ,  $U_R$  Expected and actual average voltage.

q, p Phase node of frequency and level switching.

f<sub>c</sub> Control clock frequency.

f<sub>e</sub> Desired output frequency.

$f_P$  Frequency generated by DDS.

$f_T$  Frequency generated by conventional method.

$f_r$  Jitter frequency.  $f_s$  Switching frequency.

$f_m$  Modulation profile frequency.

$m_f$  Modulation index.  $\cdot^*$  Ideal parameter.

$\Delta$  Symbol of error and variation.

$\cdot_{inf}$  Upper bound.

$\cdot_+$ ,  $\cdot_-$  Ceiling and floor function.

#### I. INTRODUCTION

NOISE is a common problem in most motor drives and other electrical systems fed by the fixed-frequency pulse width modulation (FFPWM) inverter [1]-[6]. Severe noise causes problems, impacts the user experience and finally reduces the market competitiveness of products. Hence, the suppression of noise is an important question. Conventional noise can be divided into two categories: Mechanical and Electrical Noise (EMI). Mechanical noise has lower frequency and usually comes from the vibration of mechanical structures. Suitable teeth pairing, rotor design or reduction of electromagnetic exciting force can solve this problem [7]-[9]. Besides, EMI comes from the switching action of the power devices [10]. The high values of current surge di/dt and voltage variation dv/dt come from the switching actions are mainly responsible for the different mode (DM) noise and common mode (CM) noise respectively [11]. These noises interfere with the stability of other devices that share the common direct current (DC) bus, especially for those highly

Manuscript received June 04, 2018; revised September 23, 2018 and November 20, 2018; accepted December 29, 2018. This work was supported in part by the National key R&D program of China (2017YFB1300801), by the grants from the Power Electronics Science and Education Development Program of Delta Environmental & Educational Foundation (DREK2017004). (Corresponding author: Ming Yang.)

Y. Chen, M. Yang, J. Long, and D. Xu are with the School of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin 150001, China (e-mail: chenyangyang\_hit@163.com; yangming\_hit@163.com; volkswage.n@163.com; xudiang@hit.edu.cn).

F. Blaabjerg is with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: fbl@et.aau.dk).

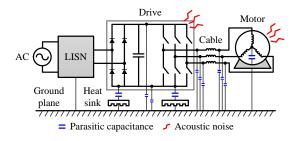

Fig. 1. The circuit schematic of a motor drive system.

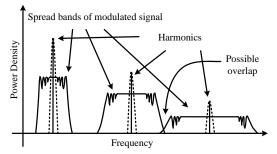

Fig. 2. Spread bands of harmonics in modulated square signals.

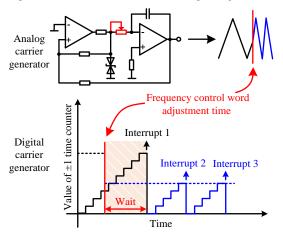

Fig. 3. The comparison of digital and analog carrier generation processes.

integrated systems like submarine system, satellite, and electric vehicle [11], [12]. In order to narrow down the pollution of EMI within an acceptable range, various electromagnetic compatibility (EMC) standards established. Since the normal switching frequency of the motor drive inverter is comparatively slow, especially in high power rate system, the reduction of the conducted EMI is the focus in this paper. Moreover, due to the switching frequency of Si device in motor drive is usually lower than 20 kHz, thus, this noise from switching action of power device and the vibration caused by harmonic current are also acoustic. Fig. 1 is one kind of the EMI test platform of a motor drive system [13]. The motor drive is fed by an AC power supply through a line impedance stabilization network (LISN). The parasitic capacitances between ground and different components of the motor drive system (heat sink, dc bus, device baseplate, cable, motor winding and etc.) build bridges for the flowing of CM current while DM noise propagates through the operation paths [14], [15]. Because the inductance of the motor is comparatively larger than stray capacitances, the impedance for di/dt is larger than dv/dt. In addition, part of the DM current is absorbed by the voltage regulated capacitor that parallel to the DC bus. Thus, CM noise is more serious than DM noise in motor drive [15], [16].

About conducted EMI reduction, adding additional components such as busbar filter, LCL filter, capacitor bank, and etc., or improving the hardware design is the most direct solution [12], [15], [17]-[19]. However, the adjustment of structure and redesign of the hardware are both costly and not flexible enough. Among software solutions, the method based on Parseval theorem, which can weaken the peak-level of the spectrum (modulation gain) by spreading the dominant harmonic clusters, is called spread spectrum clock generation (SSCG) [20]-[23]. The spread spectrum based PWM techniques can be classified into four groups, including programmed PWM, periodic modulation, random modulation and chaotic modulation [24]-[26]. 1) Programmed PWM [27], [28]: achieving harmonic elimination or minimize by predetermined and optimized switching instances of generated square waveforms. However, its performance decreases when the number of harmonics becomes larger. 2) Periodic modulation [24], [26], [29]-[34]: adjusting the carrier frequency periodically, usually, triangular, sinusoidal and exponential modulation profile are preferred. 3) Random modulation [21], [35]-[42]; varying one or more gating signal parameters (switching frequency, pulse width and pulse position) randomly to spread the harmonic energy. 4) Chaotic modulation [13], [43], [44]: utilizing erratic and irregular chaotic signal generated by chaotic map or circuit to change switch signal. As an example, **Fig. 2** shows the performance of the periodic modulation based spread frequency modulation, in which the narrowed and sharp harmonic clusters are attenuated effectively.

Furthermore, spread spectrum methods can be classified according to whether switching frequency is changed or not. In those methods the switching frequency is variable, the carrier generation schemes can also be divided into two types. The first one is adding a voltage controlled oscillator into the control circuit, and changing the frequency of the carrier by tuning the hardware component parameters. Another one is based on the interrupt module of microchips like advanced RISC machines (ARM), digital signal processor (DSP), FPGA and etc. Its detailed carrier frequency adjustment process is: the controller writes next predetermined count period and interrupt trigger into control registers each time when the whole interrupt count period is finished. The second method is preferable, since no additional circuit is needed. However, in the conventional interrupt module, the response of control word of new switching frequency needs to wait for the accomplishment of last counting cycle. Thus, a delay exists and it also brings extra consideration and computational burden to the design of the frequency modulation profile. The difference between analog and digital carrier generator mention above is intuitively displayed in Fig. 3.

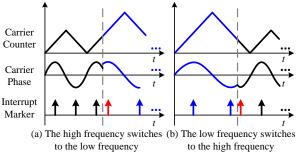

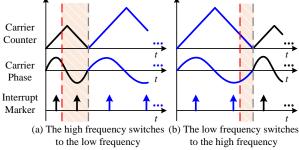

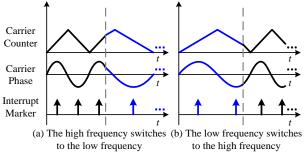

Fig. 4. The frequency switching effect of the real time modification.

Fig. 5. The frequency switching effect of the full period modification.

In order to avoid the delay of the frequency control and make the whole process smoother, the implementation and disadvantage of the conventional carrier generation method are discussed in detail. Then, a brief introduction to the direct digital frequency synthesizer (DDS) theory [45], [46] is done. Based on DDS, a wait-free phase-continuous carrier frequency modulation strategy (WPCFM), easy to implement, is proposed. Comprehensive analysis about WPCFM, including quantization error, frequency jitter, phase delay and voltage distortion are presented, and design method for the control parameters are derived. Analysis shows that the WPCFM has a smaller delay and simpler than the conventional methods. Furthermore, as the FPGA has many advantages at high switching frequencies [47]-[50], a Zynq-7000 system-on-achip (SoC) [51] based WPCFM implementation and control structure is presented in this paper. Finally, the effectiveness of WPCFM is verified by several sets of experiments where classical periodic carrier frequency modulations are applied.

#### II. TRADITIONAL INTERRUPTION MECHANISM AND DDS STRATEGY

In motor drives, the carrier and interrupts are related to the switching state of the power device and the sequential logic of the current control. Thus, the key point of the carrier frequency modulation is to guarantee no erroneous trigger and timing disorder of current loop control logic. In other words, the phase of the carrier need to be continuous during the modulation process and it is described in detail in the following discussion. In this section, two kinds of classical interruption mechanisms, real time modification and full period modification, are discussed. Besides, the DDS strategy is introduced in brief.

#### A. Real Time Modification

Most of the microchips have well-established interruption modules. In the case of timer interruption, each module has a timing counter, a counting threshold register and a phase trigger register. Each time the control clock arrives, the value of timing counter will be plus one or minus one. When the counting value reaches the phase trigger or threshold, an interruption happens and the timing counter is emptied. Hence, users can adjust the frequency and trigger easily by modifying the control words.

Assuming that the timing counter is an N-bit register, the counting threshold is M, step length is 1, and the frequency of control clock is  $f_c$ . Considering the Shannon theory and taking a sine signal as an example, the signal  $\varphi_T(t)$  which is generated by a classical method can be expressed as

$$\varphi_T(t) = \sin\left(2\pi \frac{f_c}{M}t\right) , \left\{M \left| 1 < M < 2^{N-1}\right.\right\}$$

(1)

Furthermore, using the number of steps n to replace variable t. (1) can be rewritten as

$$\varphi_T(n) = \sin\left(2\pi \frac{f_c}{M} \frac{n}{f_c}\right) = \sin\left(2\pi \frac{n}{M}\right) , \left\{M \mid 1 < M < 2^{N-1}\right\}$$

(2)

On the basis of (2), the frequency adjustment process of real time modification is to modify the counting threshold and phase trigger as long as the new frequency instruction is generated, even if the last counting period is not finished. Although real time modification is fast enough, it might cause a phase discontinuity of the signal and spurious triggering of the interruption, which can be shown in **Fig. 4**. The predetermined phase triggers in **Fig. 4** are  $0.5\pi$  and  $1.5\pi$  (they are arranged at the crest and trough of the sine wave). The frequency of carrier is changed directly at the dotted line. The red arrow is a spurious triggering of the interruption.

#### B. Full Period Modification

According to the analysis of real time modification, the reason of the phase discontinuity of the signal from real time modification is the modification of the control word that does not take the phase of current count state into consideration. Thus the full period modification in which the adjustment position is fixed at the end of the last counting period (the phase is zero) can solve this problem easily. In detail, if several instructions are happening during the waiting state, only the newest one is updated. To sum up, full period modification guarantees the continuous phase of the signal at the expense of the delay. The frequency switching progress and the waiting phenomenon of the full period modification are shown in Fig. 5. The instruction is written into the control register at the moment of the red dotted line. However, the new instruction can only be responded at the gray dotted line (the nearest point that its phase is zero).

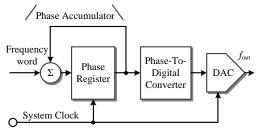

#### C. Digital Frequency Synthesizer

The direct digital frequency synthesizer (DDS) strategy was proposed in 1971 and this method can achieve frequency synthesizing and adjust the frequency of signal on-line from the concept of phase. Nowadays, it is applied into radar, communications, electronic countermeasures, instruments and

Fig. 6. The direct digital frequency synthesizer schematic diagram.

Fig. 7. The frequency switching effect of the direct digital frequency synthesizer.

other fields. **Fig. 6** shows a schematic diagram of the classical DDS algorithm. A phase accumulator is used to count the frequency word and control the phase of the signal directly.

Assuming the timing counter is an N-bit register with a step length of  $K(K \in \mathbb{N}+)$ , and the frequency of the control clock is  $f_c$ . Considering the Shannon theory and taking the sine signal as an example, the signal  $\varphi_P(t)$  which is generated by the DDS can be expressed as

$$\varphi_{P}(t) = \sin\left(2\pi \frac{K}{2^{N}} f_{c} t\right) , \left\{K | 1 < K < 2^{N-1}\right\}$$

(3)

Furthermore, using the number of steps n to replace variable t, (3) can be rewritten as

$$\varphi_{P}(n) = \sin\left(2\pi \frac{K}{2^{N}} f_{c} \frac{n}{f_{c}}\right) = \sin\left(2\pi \frac{K}{2^{N}} n\right) , \{K | 1 < K < 2^{N-1}\}$$

(4)

According to (4), dislike real time modification and full period modification, the modification of K, instead of the threshold, is used to achieve the carrier and make the interruption. In addition, the trigger condition is also changed from reaching the phase trigger to crossing the phase trigger. Owing to those slight changes, a delay-free phase-continuous carrier frequency modulation becomes possible. In **Fig. 7**, the frequency switching process is given out.

#### III. PERFORMANCE EVALUATION AND PARAMETER DESIGN

According to the comparison above, the DDS can be a good candidate to generate the carrier for WPCFM. In order to assess the DDS comprehensively, analyses of the DDS including quantization error, frequency jitter, phase delay and voltage distortion are presented, and design formulas of the control parameters are given also. Furthermore, the design methods of the WPCFM control parameters are presented.

#### A. Quantization Error

Assuming that the DDS and full period modification (FPM) have the same N and  $f_c$ , and the frequency of the desired output signal is  $f_e(f_e < f_c/2)$ . The control parameter K and M of the DDS and FPM can be calculated as

$$\begin{cases} K = \left[ 2^{N} \frac{f_{e}}{f_{c}} + \frac{1}{2} \right] \\ M = \left[ \frac{f_{c}}{f_{e}} + \frac{1}{2} \right] \end{cases}$$

(5)

The integral function in (5) is the cause of the quantization error. Supposing  $K^*$  and  $M^*$  are the ideal parameters without quantization error, and the actual frequencies of the signals which are generated by DDS and FPM are  $f_P$  and  $f_T$  by considering the quantization error. The absolute errors  $\Delta f_P(f_e)$  and  $\Delta f_T(f_e)$  of  $f_P$  and  $f_T$  with the expected frequency  $f_e$  can be given as

$$\begin{cases}

\Delta f_{p}(f_{e}) = |f_{e} - f_{p}| = \left| \frac{f_{c}}{2^{N}} K^{*} - \frac{f_{c}}{2^{N}} K \right| = \frac{f_{c}}{2^{N}} \left| 2^{N} \frac{f_{e}}{f_{c}} - \left| 2^{N} \frac{f_{e}}{f_{c}} + \frac{1}{2} \right| \right| \\

\leq \frac{f_{c}}{2^{N}} \cdot \frac{1}{2} = \frac{f_{c}}{2^{N+1}} \\

\Delta f_{T}(f_{e}) = |f_{e} - f_{T}| = \left| \frac{f_{c}}{M^{*}} - \frac{f_{c}}{M} \right| = f_{c} \left| \left( \frac{f_{c}}{f_{e}} \right)^{-1} - \left( \left| \frac{f_{c}}{f_{e}} + \frac{1}{2} \right| \right)^{-1} \right| \\

\leq f_{c} \left| \left( \left( \frac{f_{c}}{f_{e}} - \frac{1}{2} \right) \right)^{-1} - \left( \frac{f_{c}}{f_{e}} \right)^{-1} \right| = \frac{f_{e}^{2}}{2f_{c} - f_{e}}

\end{cases} \tag{6}$$

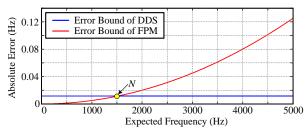

According to (6), the upper bound functions of  $\Delta f_P(f_e)$  and  $\Delta f_{T,inf}(f_e)$ , which are  $\Delta f_{P,inf}(f_e)$  and  $\Delta f_{T,inf}(f_e)$ , can be given as

$$\begin{cases}

\Delta f_{P \text{inf}} \left( f_e \right) = \frac{f_c}{2^{N+1}} \\

\Delta f_{T \text{inf}} \left( f_e \right) = \frac{f_e^2}{2 f_c - f_e}

\end{cases} \tag{7}$$

Differentiating  $\Delta f_{Tinf}(f_e)$  on  $f_e$

$$\frac{\mathrm{d}\Delta f_{T\,inf}(f_e)}{\mathrm{d}f_e} = \frac{2f_e(2f_c - f_e) + f_e^2}{(2f_c - f_e)^2} = \frac{-f_e(f_e - 4f_c)}{(2f_c - f_e)^2}$$

(8)

As  $f_e < f_c / 2$  (based on Shannon sampling theorem), there has  $f_e < 4f_c$ . Thus, according to (8),  $\Delta f_{Tinf}(f_e)$  is monotonically increasing in period of (0,  $f_c / 2$ ). Considering  $\Delta f_{Pinf}(f_e)$  to be a constant and the cross over point of  $\Delta f_{Tinf}(f_e)$  and  $\Delta f_{Pinf}(f_e)$   $f_{ec}$  is positive,  $f_{ec}$  can be expressed as

$$f_{ec} = \frac{\sqrt{1 + 2^{N+4}} - 1}{2^{N+2}} f_c \quad , \left\{ f_{ec} \middle| 0 < f_{ec} < \frac{f_c}{2} \right\}$$

(9)

Considering any frequency within the modulation range, can be an expected frequency for system to response, if the lowest modulation frequency is larger than  $f_{ec}$ ,  $\Delta f_{Pinf}(f_e)$  is better than  $\Delta f_{Tinf}(f_e)$ . Assuming  $x = f_{ec}/f_c$  (0<x<0.5), the describing equation of the control parameter N can be expressed as

$$\frac{\sqrt{1+2^{N+4}}-1}{2^{N+2}} = \frac{f_{ec}}{f_c} = x \tag{10}$$

According to (10), N can be calculated as (because N is a positive integer, top integral function is used)

Fig. 8. The error comparison between the direct digital frequency synthesizer and the full period modification.

Fig. 9. The frequency jitter of the direct digital frequency synthesizer.

Fig. 10. The voltage distortion caused by the PWM frequency modulation.

$$N = \left\lceil \log_2 \left( \frac{2 - x}{x^2} \right) - 1 \right\rceil \tag{11}$$

**Fig. 8** shows a the comparison  $\Delta f_{Tinf}(f_e)$  and  $\Delta f_{Pinf}(f_e)$  in the case of  $f_c$ =100 MHz, N=32.

#### B. Quantization Error

Because the interruption triggering condition of the DDS, in contrary to FPM, is the phase of the counter whether crosses the phase trigger or not, the frequency jitter might exist in the DDS-based carrier signal.

Ideally, the steps required to complete each counting period  $R^*$  can be expressed as

$$R^* = 2^N / K \tag{12}$$

Actually, considering the influence of the discrete counting, when the initial value is zero, the steps required to complete each counting period  $R_+$  can be expressed as

$$R_{+} = \lceil 2^{N} / K \rceil \tag{13}$$

However, if  $R^*$  is not an integer, the remaining margin will be accumulated to the next period, after each time the counting period is finished. Until these remaining numbers are accumulated to more than one complete step length, the steps required to complete each counting period  $R_+$  changes to  $R_-$ , which can be expressed as

$$R_{-} = \lfloor 2^{N}/K \rfloor \tag{14}$$

In **Fig. 9**, the counting threshold is 3, the length of step is 2. Because the margin exists, the blue counting period need 2 steps, but 1 step is enough for red period. However, in general, 1.5 step is needed for one counting period.

Taking the frequency overlap effect [52], [53], the frequency of jitter  $f_R$  can be calculated as

$$f_{R(k \in N)} = \begin{cases} \left(R^* - k\right) \frac{K}{2^N} f_c & , R^* \in [k, k + 0.5) \\ \left(k + 1 - R^*\right) \frac{K}{2^N} f_c & , R^* \in [k + 0.5, k + 1) \end{cases}$$

(15)

Because there is a periodic or random change of the carrier frequency in SSCG, the frequency jitter in DDS is acceptable, especially when  $f_e \ll f_c$ . It is also worth mentioning that the frequency jitter is the reason for why DDS has lower frequency error upper bound than FPM.

#### C. Phase Delay

In motor drives, the adjustment of the carrier frequency changes the switching frequency of the power device and the modulation frequency of PWM. Usually, the zero order holder (ZOH) model is widely used to analyze the delay of PWM [50], [54]. Taking the dual sample dual update (DSDU) method into consideration [50], the actual delay constant is half of the switching period. The transfer function of ZOH  $G_h(s)$  can be given as  $(f_s)$  is the switching frequency)

$$G_h(s) = \frac{1 - e^{-sT_h}}{s} \bigg|_{T_h = 1/(2f_s)} = \frac{1 - e^{-s/(2f_s)}}{s}$$

(16)

Substituting  $s=j\omega$  into (16) yields

$$G_h(j\omega) = \frac{2e^{-j\omega/(4f_s)} \left( e^{j\omega/(4f_s)} - e^{-j\omega/(4f_s)} \right)}{2j\omega} = \frac{1}{2f_s} \cdot \frac{\sin\left[\omega/(4f_s)\right]}{\omega/(4f_s)} e^{-j\omega/(4f_s)}$$

(17)

According to (17), the phase of  $G_h(s)$  can be expressed as

$$\angle G_h(s) = \angle e^{-j\omega/(4f_s)} = -\frac{\pi}{2} \cdot \frac{f}{f_s}$$

(18)

Assuming the initial carrier frequency of FFPWM is  $f_m$ , the increased phase lag percentage  $\Delta P$  of the system when the switching frequency reduced by  $\Delta f$  can be given as

$$\Delta P = \frac{\Delta f}{f_s - \Delta f} \tag{19}$$

According to (19), if the acceptable maximum phase lag increment is  $\Delta P_m$ , the lowest frequency  $f_L$  during the modulation process can be calculated as

$$f_L = f_s - \Delta f > \frac{f_s}{1 + \Delta P_m} \tag{20}$$

It is worth mentioning that a wider modulation range also means a better EMI reduction effect on the premise of unfolding of the frequency. Thus, there is a trade-off between stability and performance, and a moderate modulation range is recommended.

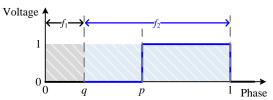

#### D. Voltage Distortion

The DDS algorithm is able to response to new instructions directly and ensure that the whole process is phase continuous. However, because the output voltage of the PWM method comes from the time domain integral, the frequency switching

Fig. 11. The current control framework of the surface permanent magnet synchronous motor.

process leads to voltage distortion. In **Fig. 10**, a simple PWM model is built up to evaluate the voltage distortion in this part.

In **Fig. 10**, q represents the phase node of the frequency switching and p is the phase node of level conversion (from 0 to 1). Assuming the constraint of q and p can be given as

$$0 \le q \le p \le 1 \tag{21}$$

Suppose that  $f_1$  and  $f_2$  to represent the carrier frequency before and after the switching respectively,  $T_1=1/f_1$ ,  $T_2=1/f_2$ , and that only one time of frequency switching exists in each period. The expected average voltage  $U_E$  and actual average voltage  $U_R$  can be expressed as

$$\begin{cases}

U_E = 1 - p \\

U_R = \frac{(1-p)T_2}{qT_1 + (1-q)T_2} = \frac{(1-p)f_1}{qf_2 + (1-q)f_1}

\end{cases}$$

(22)

Through observations, it can be seen that a maximum voltage distortion appears in the case of q = p. Assuming that  $f_2=f_1 \pm \Delta f$ , the bound of actual average voltage  $U_{RB}$  can be given as

$$U_{RB} = \frac{(1-p)f_1}{p(f_1 \pm \Delta f) + (1-p)f_1} = \frac{(1-p)f_1}{f_1 \pm p\Delta f}$$

(23)

Also assuming that  $\Delta U_m(0 \le \Delta U_m \le 1)$  represents the acceptable maximum voltage distortion  $\Delta U_m$ , the constraint of  $\Delta f$  can be expressed as

$$|U_E - U_{RB}| = \left| (1 - p) - \frac{(1 - p)f_1}{f_1 \pm p\Delta f} \right| < \Delta U_m$$

(24)

Based on (24), by discussing the case of frequency increase and reduction separately, the design equations of  $\Delta f$  can be given as

$$\begin{cases}

(1-p) - \frac{(1-p)f_1}{f_1 + p\Delta f} < \Delta U_m \\

\frac{(1-p)f_1}{f_2 - p\Delta f} - (1-p) < \Delta U_m

\end{cases}, \{p|0 < p < 1\} \cap \{\Delta U_m|0 < \Delta U_m < 1\} \quad (25)$$

Using a reasonable scaling to eliminate the parameter p and assuming the modulation range of frequency to be  $[f_L,f_U]$ , (25) can be rewritten as

$$\begin{cases} \Delta f < \frac{-\Delta U_m}{p \left[ p - \left( 1 - \Delta U_m \right) \right]} f_1 < \frac{4\Delta U_m}{\left( 1 - \Delta U_m \right)^2} f_L \\ \Delta f < \frac{-\Delta U_m}{p \left[ p - \left( 1 + \Delta U_m \right) \right]} f_1 < \frac{4\Delta U_m}{\left( 1 + \Delta U_m \right)^2} f_L \end{cases}, \left\{ \Delta U_m \left| 0 < \Delta U_m < 1 \right\} \tag{26} \end{cases}$$

By preserving a minimum constraint in (26), the finally constraint of  $\Delta f$  can be given as

$$\Delta f < \frac{4\Delta U_m}{\left(1 + \Delta U_m\right)^2} f_L , \left\{ \Delta U_m \middle| 0 < \Delta U_m < 1 \right\}$$

(27)

The tuning of  $\Delta f$  based on (27) can limit the voltage distortion within a reasonable range and avoid excessive current fluctuation during the frequency switching process.

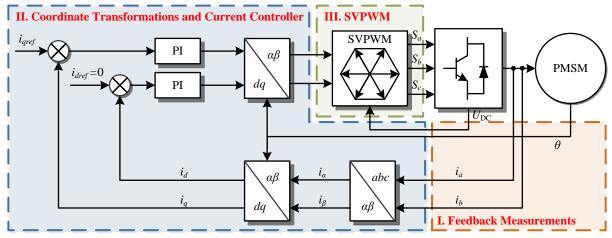

## IV. SoC-Based WPCFM IMPLEMENTATION METHOD AND CONTROL STRUCTURES

#### A. Algorithm Implementation

The classical PI current control structure of the surface permanent magnet synchronous motor (SPMSM) can be shown as **Fig. 11**. According to sequential logic, the interruption of the algorithm can be divided into three groups as follows

- I. Feedback Measurement: Detecting the phase currents, bus voltage and rotor position.

- II. Coordinate Transformation and Current Controller: Dealing with feedback signal and obtaining voltage reference from PI controller.

- III. SVPWM: Calculating the switching time of the power device and update the registers twice each period.

In the DSDU model, after updating the switching time in the control register, SVPWM generates six new phase triggers. Except the switching time, the phase triggers of other control interruptions are not changed. Since the adjustment of the switching time register only happens at the time when the half carrier is finished, no erroneous interruption exists during the whole process, which is one of the reasons that DDS can be applied into motor drives.

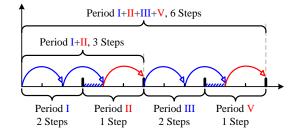

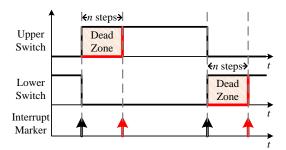

Based on the aforementioned classification, the typical control sequence on triangular carrier is illustrated in **Fig. 12**. The red, blue and green arrows are correspond with the

Fig. 12. The sequence diagram of the current control (The color of the interrupt marker is corresponding to the interruption in Fig. 11).

interruption I, II and III in Fig. 11 respectively. Meanwhile, the gray and black arrows are the phase triggers of the switch device state reversal. Owing to the parallel operation mode of FPGA, the sampling of the current and voltage can be built as an independent module in order to simplify the control structure. Besides, the interruption phase of reading the rotor position need to take the communication delay of encoder into consideration. In this paper, a 2500 impulses/revolution incremental optical encoder is used in the experiment platform. The communication delay can be ignored. Thus, each time the interruption I happens, only a short clearance is needed for the measurement module to prepare the feedback signal for the calculation. In interruption II, the coordinate transformations and current control can be finished within 40 steps (control clocks). Because the frequency of the control clock is 100 MHz, the whole process needs 0.4 us. The phase margin of trigger can be calculated based on the upper limit of the predetermined modulation frequency. As for interruption III, actually, the switching time calculation can also be finished in the program of interruption II. Thus, the FPGA only needs to update the switching time register when interruption III happens and control the state of power device during half of the next carrier period.

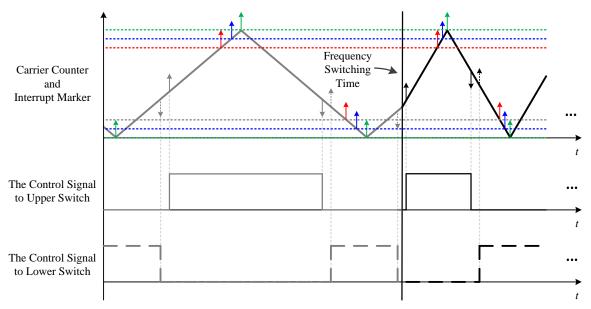

The generation of dead time has a phase margin problem

Fig. 13. The generation process of the dead time in a half-bridge in the inverter.

either. There are two kinds of solutions. The first one is to give a conservative phase margin estimation of the dead time according to the upper limit of the predetermined modulation frequency like interruption II. However, an oversized dead time means a poor quality of the current and the extra torque ripple. Besides, the second method is to fix the step number of the dead time, which can be shown in **Fig. 13**.

In **Fig. 13**, the turn off signal of the upper and lower switch is the original control signal, but there is fixed n steps delay in turn on action than initial signal. Hence, because the step number is related to the time length directly and it is fixed, whether the step length is changed or not, the delay time of dead time is fixed and the margin do not need to be too conservative.

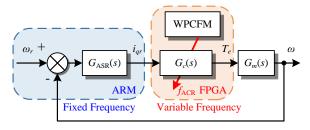

#### B. Control Structures and Controller Design

The control structure of SoC-based (which integrates ARMs and FPGA into one chip) WPCFM motor drive is shown as **Fig. 14**.  $G_{ASR}(s)$  is the transfer function of speed controller.  $G_c(s)$  and  $G_m(s)$  represent the transfer function of the current loop and mechanical part respectively. The output of  $G_{ASR}(s)$ is the current reference in q-axis  $i_{qr}$ , and it is calculated from the difference between the speed reference  $\omega_r$  and motor speed  $\omega$ . The electromagnetic torque  $T_e$  comes from the  $G_c(s)$  and it is used to drive motor. One ARM is responsible for speed loop control and the generation of frequency modulation instruction. In addition, the program in ARM is triggered by an external interrupt from the FPGA with a fixed frequency. Using this design, the traditional constant step length discrete control theory is still applicable for this control structure. Besides, the phase of the current and rotor position sampling is fixed in the carrier, which can guarantee the current vectors is precise and fully decoupled. Nevertheless, the controller in the ARM can also be triggered by the WPCFM. However, it needs to introduce a variable step length for applying discrete control theory and it increases programming burden. Thus, the

Fig. 14. The wait-free phase-continuous carrier frequency modulation strategy based control structure.

structure in **Fig. 14** is finally adopted in the experiment of this paper. Owing to the WPCFM, only one parameter, the step length in carrier generation, is needed for adjusting the switching frequency.

In addition, the classical PI structure based current and speed controller are selected for system dual closed-loop control. Based on the theory in [55], the transfer function of current controller  $G_{\rm ACR}(s)$  and speed controller  $G_{\rm ASR}(s)$  can be given as

$$\begin{cases} G_{ACR}(s) = K_{cp} (1 + K_{ci}/s) \\ G_{ASR}(s) = K_{sp} (1 + K_{si}/s) \end{cases}$$

(28)

in which  $K_{cp}$  and  $K_{ci}$  represent the proportional and integral gain of current controller, while  $K_{sp}$  and  $K_{si}$  are the proportional and integral gain of speed controller.

Next, in the situation that the expected closed-loop bandwidth of current loop  $\omega_{cc}$  is much higher than that of speed loop  $\omega_{sc}$ , the PI parameters in (28) can be calculated as

$$\begin{cases}

K_{cp} = L\omega_{cc} \\

K_{ci} = R/L \\

K_{sp} = J\omega_{sc}/K_{T} \\

K = \omega_{c}/5

\end{cases} (29)$$

in which L and R represent the phase inductance and phase resistance of the SPMSM respectively;  $K_T$  is the torque constant and J is the moment of inertia. All of these values are constant and predetermined.

Setting  $T_{\rm ACR}$  and  $T_{\rm ASR}$  as the sampling period of current loop and speed loop, and applying Tustin transformation to discretize the PI controller in (29), the equations of controller parameters in discrete model can be expressed as

$$\begin{cases}

K_{cpdis} = K_{cp} - \frac{K_{cp}K_{ci}T_{ACR}}{2} = L\omega_{cc} \left( 1 - \frac{R}{2L}T_{ACR} \right) \\

K_{cidis} = \frac{2K_{ci}T_{ACR}}{2 - K_{ci}T_{ACR}} = \frac{2RT_{ACR}}{2L - RT_{ACR}} \\

K_{spdis} = K_{sp} - \frac{K_{sp}K_{si}T_{ASR}}{2} = \frac{J\omega_{sc}}{K_{T}} \left( 1 - \frac{\omega_{sc}T_{ASR}}{10} \right) \\

K_{sidis} = \frac{2K_{si}T_{ASR}}{2 - K_{si}T_{ASR}} = \frac{2\omega_{sc}T_{ASR}}{10 - \omega_{sc}T_{ASR}}

\end{cases}$$

(30)

in which  $K_{cidis}$  and  $K_{cpdis}$  are the integral and proportional gain of current controller in z-domain;  $K_{sidis}$  and  $K_{spdis}$  are the integral and proportional gain of speed controller in z-domain.

Because the variation range of switching frequency is small (in most situation is from 9 kHz to 11 kHz) in this paper and the on-line adjustment of PI parameters increases the

Fig. 15. Experimental setup.

TABLE I: MAIN PARAMETERS OF 750W SPMSM

| Parameter            | Value                                                  |  |

|----------------------|--------------------------------------------------------|--|

| Motor Power          | 750 W                                                  |  |

| Nominal Motor Torque | 2.39 N·m                                               |  |

| Nominal Motor Speed  | 3000 rpm                                               |  |

| Nominal Current      | inal Current 3 A                                       |  |

| Phase Inductance     | 3.9e-3 H                                               |  |

| Phase Resistance     | Resistance $2.88 \Omega$                               |  |

| Poles                | 4                                                      |  |

| Motor Inertia        | $1.82\times10^{\text{-4}}\text{kg}\!\cdot\!\text{m}^2$ |  |

computing burden of FPGA, the parameters of PI current controller are fixed (setting  $f_{ACR} \equiv 20$  kHz,  $T_{ACR} \equiv 5\text{e-}5$  s). Besides, taking the anti-windup of PI controllers into consideration, the incremental structure is used in current controller while the integration weakening PI regulation strategy is applied in speed controller.

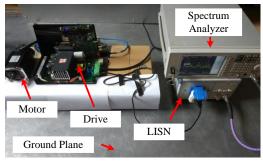

#### V. EXPERIMENTAL RESULTS

Fig. 15 shows the EMI experimental setup of WPCFM. The specifications of the motor are presented in Table I. An impedance stabilization network (LISN, R&S ENV216) is connected between the power source and the drive. Considering the switching frequency is relatively low ( $\leq 12$ kHz), the EMI signal from LISN is measured on a spectrum analyzer (Agilent N9320B) which is set to peak mode with a 10 Hz resolution bandwidth (RBW). All instruments are placed on an earthed conductive plane and the structure is match with **Fig. 1**. In order to reduce  $\Delta f$  while keeping the modulation profile unchanged, the interruption frequency of ARM is raised to 10kHz (f<sub>ASR</sub>) and the speed measurement method mentioned in [53] is used to improve the accuracy of speed feedback. The control chip is Xilinx Zyng series SoC, which integrates ARM (two Cortex-A9s but only one is used) and FPGA into one chip. The communication between ARM and FPGA is realized by advanced eXtensible interface (AXI) bus inside SoC. In addition, the random access memory (RAM) of Zynq is extended to 1 GB by adding external memory chip to record experiment data. In the experimental of WPCFM with periodic triangular wave, the  $f_c$  of FFPWM and WPCFM are both 100 MHz. The carrier frequency of FFPWM (equal to switching frequency  $f_s$ ) is fixed as 10 kHz. The counting register of WPCFM is 32-bit. For verifying the effectiveness

Fig. 17. The performance of the WPCFM based sinusoidal spread spectrum frequency modulation.

Fig. 18. PSD results of phase currents under different modulation schemes.

of the control structure in **Fig. 14**, the experiment drive system is working in the speed control mode with speed reference is 1000 rpm. Besides, three top and bottom insulated gate bipolar transistors (IGBTs) are switching on or off simultaneously around 50% duty ratio [15], [24] to maximized the conducted EMI by making motor work in no-load state.

#### A. EMI Reduction

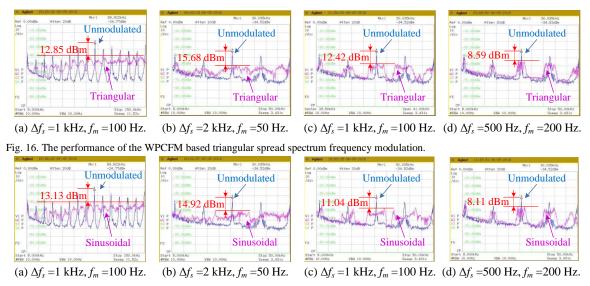

Fig. 16 and Fig. 17 are the performances of triangular and sinusoidal modulation profile based on WPCFM algorithm. The spectrum from 9 kHz to 150 kHz is recorded in Fig. 16 (a) and Fig. 17 (a), while only the data from 9 kHz to 50 kHz is shown in others.  $\Delta f_s$  is the peak deviation of the switching frequency and  $f_m$  is the frequency of modulation profile.  $m_f$  (=  $\Delta f_s / f_m$ ) is the modulation index. Using the 3rd harmonic of the 10 kHz central frequency as a symbol, its amplitude decreases with the increases of triangular and sinusoidal profile modulation index. Fig. 16 (b) and Fig. 17 (b) have the largest  $m_f$  and the most obvious attenuation of the conducted EMI harmonic peak (triangular: 15.68 dBm, sinusoidal: 14.92 dBm), but the overlap (which has been shown in Fig. 2) is appear earlier. In general, compared with sinusoidal profile, triangular profile has better spread spectrum performance. Overall, the dominant EMI clusters in power spectral density (PSD) of WPCFM based periodical spread spectrum frequency modulation (SSFM) are spread effectively which

coincides with the spread spectrum theory and also proves WPCFM is a qualified carrier for SSFM.

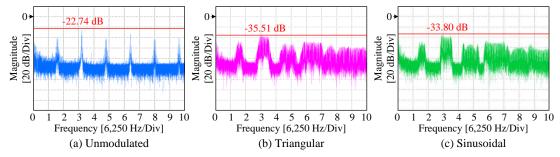

#### B. Harmonic Currents Suppression

Because the switching frequency of motor drive inverter is smaller than 20 kHz, the noise caused by switching action and harmonic currents is also acoustic. The harmonic clusters in phase current can also be a reference value to judge the performance of SSFM [35], [56]. In this part of experiment, the phase current is recorded by an oscilloscope (YOKOGAWA, DLM2054) with 1.25 MHz sampling frequency, and analyzed offline by its software kit Xviewer. In addition, the triangular and sinusoidal profile modulation have the same constant  $\Delta f_s$  (=1 kHz) and  $f_m$  (=100 Hz). The PSD results of phase currents under different modulation schemes are shown in Fig. 18. For example, the 2nd harmonic of the 10 kHz central frequency decreases from -22.74 dB (unmodulated) to -35.51 dB (triangular profile) and -33.80 dB (sinusoidal profile) remarkably. The outline envelops of the current spectrum are also in accordance with the periodical SSFM. Overall, the measured current spectrum shows similar results with the previous EMI reduction experiments.

#### C. Closed-Loop Control Performance

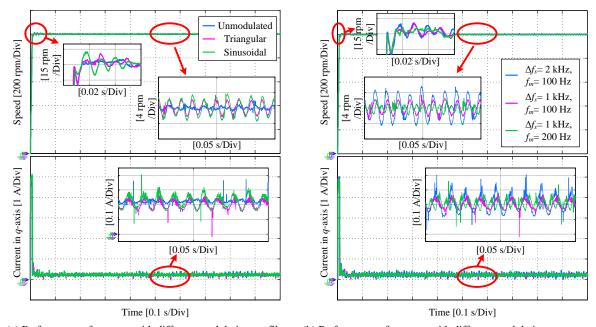

In order to evaluate the speed control performance of the system with WPCFM control structure, in **Fig. 19**, the speed step response in time domain is recorded. The speed and

(a) Performance of systems with different modulation profiles (b) Performance of systems with different modulation parameters

Fig. 19. The speed step response of the system with the WPCFM control structure.

| TABLE II: RMS VALUE OF THE MOTOR SPEED ERROR |                                                    |                                                      |                                                      |

|----------------------------------------------|----------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| Inertia Ratio $J/J_m$                        | $\Delta f_s = 500 \text{ Hz}, f_m = 50 \text{ Hz}$ | $\Delta f_s = 1000 \text{ Hz}, f_m = 100 \text{ Hz}$ | $\Delta f_s = 1500 \text{ Hz}, f_m = 150 \text{ Hz}$ |

| 1.00                                         | 1.902 rpm                                          | 1.854 rpm                                            | 1.554 rpm                                            |

| 3.84                                         | 0.644 rpm                                          | 0.571 rpm                                            | 0.538 rpm                                            |

current feedback of system with different modulation profile is shown in Fig. 19 (a), the  $\Delta f_s$  and  $f_m$  of triangular and sinusoidal profile is also fixed as 1 kHz and 100 Hz respectively. The rise time of three kinds of modulation schemes is almost same, but the overshoot is larger after SSFM is adopted, especially under the sinusoidal profile modulation (nearly 15 rpm). The steady state fluctuation of sinusoidal profile (≤4 rpm) is larger than that of triangular profile ( $\leq 2.5$  rpm) either, but the speed fluctuation frequency of this two kind of periodical SSFM is same (=100 Hz =  $f_m$ ). Similar phenomenon is also exist in the q-axis current waveform. In Fig. 19 (b), the comparison results under different control parameters are given out. Although a larger modulation index  $m_f$  commonly means better EMI reduction performance, the current and speed ripple also increase with the increase of  $m_f$ . There is an unavoidable trade-off between EMI reduction and a smooth output. Considering the EMI attenuation function with  $m_f$  is nonlinear [24], usually, a moderate  $m_f$  is preferred. Especially, in motor drive system, apart from current ripple, speed ripple is another important or even more priority index. Fortunately, the moment inertia of system can be regard as a self-equipped filter to damp the ripple impact caused by current to motor speed. According to Fig. 19 (b), the ripple frequency of current is equal to the frequency of modulation profile  $f_m$ . More detailed, the root mean square (RMS) value of motor speed error under same  $m_f$ but different  $f_m$  is recorded in **Table II**. Considering motor has to equip with additional load inertia in most industrial

applications, a set of comparison experimental results that under larger inertia is also given out ( $J_m$  is the inertia of motor itself). According to **Table II**, when  $m_f$  is fixed, the RMS of speed ripple decreases with the increase of inertia and  $f_m$ . It means, when inertia and  $m_f$  are fixed, the higher  $f_m$  can degrade the impact from the current ripple caused by SSFM and achieve smoother speed control performance.

To sum up, in the system with periodical SSFM, although the speed fluctuation is increased, the variation range is still acceptable. In order to avoid sharp current fluctuation, a moderate modulation index  $m_f$  ( $10 < m_f < 20$ ) is recommended. Moreover, because the fluctuation frequency is equal to  $f_m$ , this disturbance can be absorbed by the inertia of system gradually when  $f_m$  becomes higher. Hence, when  $m_f$  is fixed, a higher  $f_m$  can reduce the ripple of motor speed. It also means that the WPCFM based SSFM is more suitable for wide band gap (WBG) motor drive systems (which can achieve higher  $f_s$  and  $f_m$ , but have more serious EMI pollution). Due to limitation of experiment platform, the verification of the proposed method on WBG devices (the platform is still being set up in our lab) will be our future focus.

#### D. Comparison of Wait and Wait-Free Algorithms

Owing to the redesign of carrier generation mode, the switching frequency adjustment order from SSFM can be executed without any delay using WPCFM. Compared with the wait algorithm, this wait-free method mainly has two advantages.

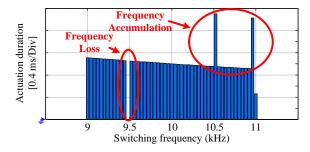

Fig. 20. The frequency accumulation phenomenon of the wait algorithm.

Fig. 21. Comparison results of wait and wait-free algorithms.

- 1) No frequency loss and accumulation: In Fig. 20, the frequency order update progress of the conventional wait method is simulated and the actuation time of different frequency orders during half of the triangular modulation period is recorded ( $f_c = 100 \text{ MHz}$ ,  $\Delta f_s = 1 \text{ kHz}$ ,  $f_s = 10 \text{ kHz}$ , and  $f_m = 100$  Hz). More detailed, the frequency order calculation frequency is 10 kHz and the order only can be updated at the beginning of each switching period. According to Fig. 20, due to the asynchrony between frequency order calculation and update, some orders are unable to be executed (frequency loss), and some orders are executed twice (frequency accumulation) probability during half of the modulation period. Although the switching frequency of conventional method is evenly distributed within a long time scale, the partial nouniform distribution still exists in some situations. As for wait-free algorithm, this problem is avoidable because the new frequency order can be executed immediately.

- 2) More feasible: After adding several order update judgement conditions and buffer registers, WPCFM can conveniently realize the switching between wait and wait-free mode. Moreover, users can randomly choose specific phase nodes on carrier wave to adjust the switching frequency. It means WPCFM is a more feasible algorithm. In additional, not only for EMI reduction, this DDS-based carrier frequency modulation strategy can also be used in other applications, like synchronous modulation, in which a larger range of on-line switching frequency adjustment is needed.

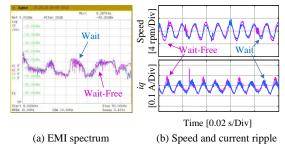

- In **Fig. 21**, several comparison experiment results of wait and wait-free algorithms are given out. The  $\Delta f_s$  and  $f_m$  of wait and wait-free algorithms are fixed as 1 kHz and 100 Hz respectively, and the speed command of motor is 1000 rpm without any additional load inertia. The EMI reduction effects of wait and wait-free algorithms recorded by the spectrum analyzer are almost the same. Because within a long time scale,

wait method can also achieve uniform distribution of switching frequency. Both wait and wait-free methods can spread the dominant clusters in frequency spectrum successfully. As for the current ripple of q-axis in **Fig. 21** (b), due to the voltage distortion caused by WPCFM (which have been discussed in Section. III), the fluctuation of wait-free method is slightly increased.

Overall, the proposed wait-free algorithm is more feasible and easy-implemented, but it has relatively larger current ripple than conventional method as a trade-off.

#### VI. CONCLUSION

In this paper, with the goal to reduce the delay of conventional variable carrier frequency SSCG, a DDS-based carrier generation method in a FPGA is adopted to replace the conventional interruption method in the microchip. The quantization error, frequency jitter, phase delay and voltage distortion of this strategy are modeled and analyzed comprehensively. Results show that the DDS-based carrier generation method can guarantee the phase continuity of waveform and no wait state is needed to update the instruction. In addition, this wait-free algorithm is more feasible and can be adjusted expediently according to the users' demands. Therefore, this paper has proposed an all-digital wait-free phase-continuous carrier frequency modulation strategy through reasonable current control logic and dead zone design. Besides, easily achieved algorithm and control structure are presented based on a SoC platform. The effectiveness of WPCFM is verified in several sets of experiments. Results prove that WPCFM is a qualified carrier for SSFM. To apply WPCFM to a wide band gap platform to fully demonstrate its advantages in higher switching frequency motor drive is the focus of future work.

#### REFERENCES

- [1] D. Torregrossa, D. Paire, F. Peyraut, B. Fahimi, and A. Miraoui, "Active mitigation of electromagnetic vibration radiated by PMSM in fractional-horsepower drives by optimal choice of the carrier frequency," *IEEE Trans. Ind. Electron.*, vol. 59, no. 3, pp. 1346-1354, Mar. 2012.

- [2] A. Ruiz-Gonzalez, F. Vargas-Merino, J. R. Heredia-Larrubia, M. J. Meco-Gutierrez, and F. Perez-Hidalgo, "Application of slope PWM strategies to reduce acoustic noise radiated by inverter-fed induction motors," *IEEE Trans. Ind. Electron.*, vol. 60, no. 7, pp. 2555-2563, Jul. 2013

- [3] J. L. Besnerais, V. Lanfranchi, M. Hecquet, and P. Brochet, "Characterization and reduction of audible magnetic noise due to PWM supply in induction machines," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp. 1288-1295, Apr. 2010.

- [4] H. Soltani, P. Davari, F. Zare, and F. Blaabjerg, "Effects of modulation techniques on the input current interharmonics of adjustable speed drives," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 167-178, Jan. 2018.

- [5] K. Cui, V. Adrian, B. Gwee, and J. S. Chang, "A noise-shaped randomized modulation for switched-mode DC-DC converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 1, pp. 394-405, Jan. 2018

- [6] Y. Cho, M. Kim, and C. Kim, "A low switching-noise and high-efficiency buck converter using a continuous-time reconfigurable delta-sigma modulator," *IEEE Trans. Power Electron.*, to be published 2018.

- [7] J. Jung, S. Lee, G. Lee, J. Hong, D. Lee, and K. Kim, "Reduction design of vibration and noise in IPMSM type integrated starter and generator for HEV," *IEEE Trans. Magn.*, vol. 46, no. 6, pp. 2454-2457, Jun. 2010.

- [8] S. Hwang, J. Eom, G. Hwang, W. Jeong, and Y. Jung, "Cogging torque and acoustic noise reduction in permanent magnet motors by teeth pairing," *IEEE Trans. Magn.*, vol. 36 no. 5, pp. 3144-3146, Sep. 2000.

- [9] J. Brudny, J. Lecointe, "Rotor design for reducing the switching magnetic noise of AC electrical machine variable-speed drives," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 5112-5120, Nov. 2011.

- [10] D. Gonzalez, J. Gago, and J. Balcells, "New simplified method for the simulation of conducted EMI generated by switched power converters," *IEEE Trans. Ind. Electron.*, vol. 50, no. 6, pp. 1078-1084, Dec. 2003.

- [11] T. Rahimi, S. H. Hosseini, M. Sabahi, and R. S. Alishah, "EMI consideration of high reliability DC-DC converter: In aerospace based electric transport system charger application," *Progress In Electromagnetics Research*, vol. 46, 125-133, 2016.

- [12] N. Mousavi, T. Rahimi, and H. M. Kelk, "Reduction EMI of BLDC motor drive based on software analysis," *Advances in Materials Science and Engineering*, 2016.

- [13] Z. Zhang, T. W. Ching, C. Liu, and C. H. T. Lee, "Comparison of chaotic PWM algorithms for electric vehicle motor drives," in *Proc. IECON*, 2012, pp.4087-4092.

- [14] R. Kahoul, Y. Azzouz, B. Ravelo, and B. Mazari, "New behavioral modeling of EMI for DC motors applied to EMC characterization," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5482-5496, Dec. 2013.

- [15] X. Gong, J. Ferreira, "Comparison and reduction of conducted EMI in SiC JFET and Si IGBT-Based motor drives," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1757-1767, Oct. 2014.

- [16] D. Zhao, J. A. Ferreira, H. Polinder, A. Roch, and F. B. J. Leferink,, "Investigation of EMI noise transfer characteristic of variable speed drive system," in Proc. IEEE Int. Symp. Power Electron., Electr. Drives, Autom. Motion, 2006, pp. 603–608.

- [17] J. Gago, J. Balcells, D. GonzÁlez, M. Lamich, J. Mon, and A. Santolaria, "EMI susceptibility model of signal conditioning circuits based on operational amplifiers," *IEEE Trans. Electromagn. Compat.*, vol. 49, no. 4, pp. 849-859, Nov. 2007.

- [18] F. Luo, A. C. Baisden, D. Boroyevich, K. D. T. Ngo, S. Wang, and P. Mattavelli, "Design of a hybrid busbar filter combining a transmission-line busbar filter and a one-turn inductor for DC-fed three-phase motor drive systems," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5588-5602, Dec. 2013.

- [19] D. Han, S. Li, Y. Wu, W. Choi, and B. Sarlioglu, "Comparative analysis on conducted CM EMI emission of motor drives: WBG versus Si devices," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8353-8363, Oct 2017

- [20] A. Santolaria, J. Balcells, and D. Gonzalez, "Theoretical and experimental results of power converter frequency modulation," in *Proc. IECON*, 2002, pp.193-197.

- [21] A. M. Trzynadlowski, F. Blaabjerg; J. K. Pedersen, R. L. Kirlin, and S. Legowski, "Random pulse width modulation techniques for converter-fed drive systems-a review," *IEEE Trans. Ind. Appl.*, vol. 30, no. 5, pp. 1166-1175, Sept/Oct. 1994.

- [22] K. K. Tse, H. S. Chung, S. Y. R. Hui, and H. C. So, "A comparative study of carrier-frequency modulation techniques for conducted EMI suppression in PWM converters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 3, pp. 618-627, Jun. 2002.

- [23] A. Santolaria, J. Balcells, D. Gonzalez, and J. Gago, "Evaluation of switching frequency modulation in EMI emissions reduction applied to power converters," in *Proc. IECON*, 2003, pp.2306-2311.

- [24] D. Gonzalez, J. Balcells, A. Santolaria, J. L. Bunetel, J. Gago, D. Magnon, and S. Brehaut, "Conducted EMI reduction in power converters by means of periodic switching frequency modulation," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2271-2281, Nov. 2007.

- [25] R. Gamoudi, D. Chariag, and L. Sbita, "A review of spread spectrum based PWM techniques \_a novel fast digital implementation," *IEEE Trans. Power Electron.*, to be published 2018.

- [26] J. Balcells, A. Santolaria, A. Orlandi, D. Gonzalez, and J. Gago, "EMI reduction in switched power converters using frequency modulation techniques," *IEEE Trans. Electromagn. Compat.*, vol. 47, no. 3, pp. 569-576, Aug. 2005.

- [27] C. Zhao, and D. Costinett, "GaN-based dual-mode wireless power transfer using multifrequency programmed pulse width modulation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 9165-9176, Nov. 2017.

- [28] M. S. A. Dahidah, G. Konstantinou, and V. G. Agelidis, "A review of multilevel selective harmonic elimination PWM: formulations, solving

- algorithms, implementation and applications," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4091-4106, Aug. 2015.

- [29] Y. Xu, Q. Yuan, J. Zou, B. Wang, and J. Li, "Periodic carrier frequency modulation in reducing low-frequency electromagnetic interference of permanent magnet synchronous motor drive system," *IEEE Trans. Magn.*, vol. 51, no. 11, Nov. 2015, Art. ID 8109604.

- [30] F. Pareschi, G. Setti, R. Rovatti, and G. Frattini, "Practical optimization of EMI reduction in spread spectrum clock generators with application to switching DC/DC converters," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4646-4657, Sept. 2014.

- [31] M. Yeh, W. Liou, H. Hsieh, and Y. Lin, "An electromagnetic interference (EMI) reduced high-efficiency switching power amplifier," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 710-718, Mar. 2010.

- [32] M. Song, S. Ahn, I. Jung, Y. Kim, and C. Kim, "Piecewise linear modulation technique for spread spectrum clock generation," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 21, no. 7, pp. 1234-1245, Jul. 2013.

- [33] D. D. Caro, "Optimal discontinuous frequency modulation for spreadspectrum clocking," *IEEE Trans. Electromagn. Compat.*, vol. 55, no. 5, pp. 891-900, Oct. 2013.

- [34] J. Huang, and R. Xiong, "Study on modulating carrier frequency twice in SPWM single-phase inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3384-3392, Jul. 2014.

- [35] L. Mathe, F. Lungeanu, D. Sera, P. O. Rasmussen, and J. K. Pedersen, "Spread spectrum modulation by using asymmetric-carrier random PWM," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3710-3718, Oct. 2012.

- [36] Y. Lim, Y. Jung, S. Oh, and J. Kim, "A two-phase separately randomized pulse position PWM (SRP-PWM) scheme with low switching noise characteristics over the entire modulation index," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 362-369, Jan. 2012.

- [37] R. L. Kirlin, C. Lascu, and A. M. Trzynadlowski, "Shaping the noise spectrum in power electronic converters," *IEEE Trans. Ind. Electron.*, vol. 58, no. 7, pp. 2780-2788, Jul. 2011.

- [38] C. Jin, M. Tan, and K. Y. See, "Filterless class-D amplifier with pseudorandomized carrier frequency modulation for EMI reduction," *IEEE Trans. Electromagn. Compat.*, vol. 55, no. 1, pp. 74-80, Feb. 2013.

- [39] X. Ming, Z. Chen, Z. Zhou, and B. Zhang, "An advanced spread spectrum architecture using pseudorandom modulation to improve EMI in class D amplifier," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 638-646, Feb. 2011.

- [40] Y. Chang, and C. Liaw, "A flyback rectifier with spread harmonic spectrum," *IEEE Trans. Ind. Electron.*, vol. 58, no. 8, pp. 3485-3499, Aug. 2011.

- [41] C. Tsai, C. Yang, and J. Wu, "A digitally controlled switching regulator with reduced conductive EMI spectra," *IEEE Trans. Ind. Electron.*, vol. 60, no. 9, pp. 3938-3947, Sept. 2013.

- [42] Y. Lai, Y. Chang, and B. Chen, "Novel random-switching PWM technique with constant sampling frequency and constant inductor average current for digitally controlled converter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 8, pp. 3126-3135, Aug. 2013.

- [43] K. K. Tse, and R. W. -M. Ng, H. S. -H. Chung, and S. Y. R. Hui, "An evaluation of the spectral characteristics of switching converters with chaotic carrier-frequency modulation," *IEEE Trans. Ind. Electron.*, vol. 50, no. 1, pp. 171-182, Feb. 2003.

- [44] H. Li, Z. Li, B. Zhang, F. Wang, N. Tan, and W. A. Halang, "Design of analogue chaotic PWM for EMI suppression," *IEEE Trans. Electromagn. Compat.*, vol. 52, no. 4, pp. 1001-1007, Nov. 2010.

- [45] P. P. Sotiriadis, "Spurs-free single-bit-output all-digital frequency synthesizers with forward and feedback spurs and noise cancellation," *IEEE Trans. Circuits Syst. I, Reg. Papers.*, vol. 63, no. 5, pp. 567-576, May. 2016.

- [46] G. Rubio-Cidre, A. Badolato, L. Úbeda-Medina, J. Grajal, B. Mencia-Oliva, and B. Dorta-Naranjo, "DDS-based signal-generation architecture comparison for an imaging radar at 300 GHz," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 11, pp. 3085-3098, Nov. 2015.

- [47] R. Horvat; K. Jezernik, and M. Čurkovič, "An event-driven approach to the current control of a BLDC motor using FPGA," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3719-3726, Jul. 2014.

- [48] L. Diao, J. Tang, P. C. Loh, S. Yin, L. Wang, and Z. Liu, "An efficient DSP-FPGA-based implementation of hybrid PWM for electric rail traction induction motor control," *IEEE Trans. Power Electron.*, vol. 33,

- no. 4, pp. 3276-3288, Apr. 2018.

- [49] N. Milivojevic, M. Krishnamurthy, Y.Gurkaynak, A. Sathyan, Y. Lee, and A. Emadi, "Stability analysis of FPGA-Based control of brushless DC motors and generators using Digital PWM technique," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 343-351, Jan. 2012.

- [50] E. Jung, H. Lee, and S. Sul, "FPGA-based motion controller with a high bandwidth current regulator," in *Proc. PESC*, 2008, pp. 3043-3047.

- [51] Q. Gu, Y. Li, and P. Niu, "SoC-based solution for multi-axis control systems using high-level synthesis," *Proc IMechE, Part I: J Systems and Control Engineering*, vol. 299, no. 1, pp. 63-73, Jan. 2014.

- [52] C. K. Pang, W. Yan, and C. Du, "Multirate identification of mechanical resonances beyond the Nyquist frequency in high-performance mechatronic systems," *IEEE Trans. Syst., Man, Cybern., Syst.*, vol. 46, no. 4, pp. 573-581, Apr. 2016.

- [53] Y. Chen, M. Yang, J. Long, D. Xu, and F. Blaabjerg, "M/T method based incremental encoder velocity measurement error analysis and selfadaptive error elimination algorithm," in *Proc. IECON*, 2017, pp. 2085-2090

- [54] W. Yao, Y. Yang, X. Zhang, F. Blaabjerg, and P. C. Loh, "Design and analysis of robust active damping for LCL filters using digital notch filters," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2360-2375, Mar. 2016.

- [55] S.-K. Sul, Control of electric machine drive systems, Wiley-IEEE, 2010.

- [56] G. Wang, L. Yang, G. Zhang, X. Zhang, and D. Xu, "Comparative investigation of pseudorandom high-frequency signal injection schemes for sensorless IPMSM drives," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2123-2132, Mar. 2017.

Yangyang Chen received the B.S. degree in electrical engineering in 2016 from Harbin Institute of Technology, Harbin, China, where he is currently working toward the Ph.D. degree in power electronics and electrical drives in the School of Electrical Engineering and Automation.

His current research interests include multiaxis servo systems, mechanical resonance and control parameter self-tuning strategy.

**Ming Yang** (M'14–SM'18) received the B.S. and M.S. and Ph.D. degrees in Electrical Engineering from Harbin Institute of Technology (HIT), Harbin, China, in 2000, 2002 and 2007, respectively.

In 2004, he joined as a Lecturer with the Department of Electrical Engineering, HIT, where he has been a Professor of Electrical Engineering since 2015. From 2009 to 2012, he was a Postdoctoral Fellow with Shanghai STEP Electric Corporation. He has authored more

than 40 technical papers published in journals and conference proceedings. He is the holder of 14 Chinese patents. His current major research interests include PMSM servo systems, predictive current control and mechanical resonance suppression.

Jiang Long received the M.S. degree in power electronics and electrical drives in 2015, from the Harbin University of Science and Technology, Harbin, China. He is currently working towards Ph.D. degree in power electronics and electrical drives with the School of Electrical Engineering and Automation of Harbin Institute of Technology.

His current research interests include on PMSM servo systems, predictive current control and parameter identification.

**Dianguo Xu** (M'97–SM'12–F'17) received the B.S. degree in Control Engineering from Harbin Engineering University, Harbin, China, in 1982, and the M.S. and Ph.D. degrees in Electrical Engineering from Harbin Institute of Technology (HIT), Harbin, China, in 1984 and 1989, respectively.

In 1984, he joined the Department of Electrical Engineering, HIT, as an Assistant Professor Since 1994, he has been a Professor

in the Department of Electrical Engineering, HIT. He was the Dean of the School of Electrical Engineering and Automation, HIT, from 2000 to 2010. He is currently the Vice President of the HIT. His research interests include renewable energy generation, power quality mitigation, sensorless motor drives, and high performance servo systems.

Dr. Xu is an Associate Editor of the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS.

**Frede Blaabjerg** (S'86–M'88–SM'97–F'03) received the Ph.D. degree in electrical engineering from Aalborg University, Aalborg, Denmark, in 1992.

He was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of Power Electronics and Drives in 1998 with Aalborg University. His current research

interests include wind turbines, PV systems, reliability, harmonics, and adjustable speed drives.

Dr. Blaabjerg was a recipient of 15 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the IEEE William E. Newell Power Electronics Award 2014, and the Villum Kann Rasmussen Research Award 2014. He was an Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been a Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011. He was nominated in 2014 by Thomson Reuters to be among the most 250 cited researchers in engineering in the world.