Aalborg Universitet

A Novel Submodule Voltage Balancing Scheme for Modular Multilevel Cascade Converter—Double-Star Chopper-Cells (MMCC-DSCC) Based STATCOM

Jin, Y.; Xiao, Qian; Dong, Chaoyu; Jia, Hongjie; Mu, Yunfei; Xie, Bing; Ji, Yanchao; Chaudhary, Sanjay Kumar; Teodorescu, Remus

Published in: **IEEE** Access

DOI (link to publication from Publisher): 10.1109/ACCESS.2019.2924609

Creative Commons License CC BY 3.0

Publication date: 2019

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Jin, Y., Xiao, Q., Dong, C., Jia, H., Mu, Y., Xie, B., Ji, Y., Chaudhary, S. K., & Teodorescu, R. (2019). A Novel Submodule Voltage Balancing Scheme for Modular Multilevel Cascade Converter—Double-Star Chopper-Cells (MMCC-DSCC) Based STATCOM. *IEEE Access*, *7*, 83058-83073. Article 8744284. https://doi.org/10.1109/ACCESS.2019.2924609

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: February 07, 2025

Received June 2, 2019, accepted June 15, 2019, date of publication June 24, 2019, date of current version July 11, 2019. *Digital Object Identifier* 10.1109/ACCESS.2019.2924609

# A Novel Submodule Voltage Balancing Scheme for Modular Multilevel Cascade Converter–Double-Star Chopper-Cells (MMCC-DSCC) Based STATCOM

## YU JIN<sup>1,3</sup>, QIAN XIAO<sup>®2,3</sup>, CHAOYU DONG<sup>®2</sup>, HONGJIE JIA<sup>®2</sup>, YUNFEI MU<sup>®2</sup>, (Member, IEEE), BING XIE<sup>1</sup>, YANCHAO JI<sup>1</sup>, (Member, IEEE), SANJAY K. CHAUDHARY<sup>®3</sup>, (Member, IEEE), AND REMUS TEODORESCU<sup>®3</sup>, (Fellow, IEEE) <sup>1</sup>Department of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin 150006, China <sup>2</sup>Key Laboratory of Smart Grid of Ministry of Education, Tianjin University, Tianjin 300072, China

<sup>3</sup>Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark

Corresponding author: Qian Xiao (xiaoqian@tju.edu.cn)

This work was supported in part by the National Key Research and Development Program of China under Grant 2017YFB0903300, in part by the Project of National Natural Science Foundation of China under Grant 51625702 and Grant 51807135, and in part by the Joint Fund Project of National Natural Science Foundation—State Grid Corporation under Grant U1766210.

**ABSTRACT** A novel capacitor voltage balancing scheme for modular multilevel cascade converter—doublestar chopper-cells (MMCC-DSCC)-based STATCOM is proposed in this paper. Compared with the conventional software voltage balancing methods, the proposed scheme has three main advantages. First, only six voltage sensors are needed, and other voltage sensors have been removed. Then, the control framework can be simple without sort and select process, or some balancing control loops. Additional delay process caused by the sampling and control signals transmission is also mitigated. Finally, the faster capacitor balancing speed can be obtained. In addition, compared with some other hardware voltage balancing schemes, there are superior characteristics in terms of the reduced number of switches and only the popular power modules in the additional units are applied. For these additional modules, the parameters design guide of the proposed scheme has been discussed. Verified results from the 13-level simulated system and 9-level experimental platform for the MMCC-DSCC based STATCOM show the effectiveness of the proposed scheme. By the proposed scheme, both DC capacitor voltage balancing control and reactive power compensation are simultaneously realized for the MMCC-DSCC-based STATCOM even in balanced and unbalanced load.

**INDEX TERMS** Diode-clamped circuit, double-star chopper-cell (DSCC), modular multilevel cascade converter (MMCC), voltage balancing, STATCOM.

## I. INTRODUCTION

With the development of medium and high voltage converters, it raises a series of harsh requirements for the high-power converters. Modular Multilevel Cascaded Converter (MMCC) has many advantages such as modularity, scalability, high fault-tolerant ability, and so on [1], [2]. Consequently, MMCC has been considered as one of the most attractive topologies for HVDC [3]–[5], high-voltage voltage source converter (VSC) [6], [7], active power

The associate editor coordinating the review of this manuscript and approving it for publication was Tariq Masood.

filter (APF) [8], [9], STATCOM [10], energy storage system [11], [12], and so on.

As one of the most important applications for reactive power compensation, Modular Multilevel Cascade Converter — Double-Star Chopper-Cells (MMCC-DSCC) based STAT-COM is gaining much more attention to generate the dynamic reactive power, improve power factor and power quality of grid [13], [14]. For the STATCOM, a lot of studies have been conducted on various improvements about the operation performance [15]–[17].

For MMCC-DSCC based STATCOM, the capacitor voltage balancing control for the floating submodules (SMs) in each arm remains to be a challenging issue, which is a common problem in the multilevel converters [18]. The mainstream of the balancing method can be divided into three categories, an additional injection of modulation wave for each SM, voltage sorting and select methods, and hardware balancing schemes.

For the first category, reference [19]-[22] inject an additional component to the modulation wave of each module according to the voltage derivation of capacitors from the voltage reference. Reference [23] reveals the quantitative relation between the capacitor voltage of SM and other operating parameters. Based on this, the additional injection is calculated and injected to balance the capacitor voltages according to the equation derived in this paper. Another voltage balancing method switching at grid frequency is proposed [24]. By assigning the low-frequency pulses with different pulse widths, the charges of the capacitor are controlled for keeping the capacitor voltage balancing in MMCC-DSCC. Furthermore, reference [25] manages to decouple the SM capacitor voltages balancing process from the DC bus voltage balancing. The SM voltage is controlled with a better result than traditional balancing control methods. However, these methods introduce the feedforward of capacitor voltages in the modulation, which lowers the voltage utilization of modulation wave [26].

For the second category, reference [27] propose the hierarchical control method. All SMs in one arm are grouped, and the sorting algorithm of the voltage balancing in each group is implemented in a decentralized control unit, and the balancing between different groups is realized by an additional injection component. To lower the computation burden of conventional model predictive control (MPC) method reference [28] and [29] propose an improved MPC based sorting and balancing approach which reserves the system performance, especially in high voltage systems. On the basis of these two papers, a priority sorting approach based on simplified MPC is proposed for MMCC in reference [30]. Reference [31] proposes an improved balancing approach based on space vector pulse width modulation (SVPWM). This method simplifies the complexity of balancing control by avoiding the sorting algorithm of all the voltages in one arm. The comparison between different modulators is further performed [32]. It also discusses the priority of each modulator. However, the relationship between sorting frequency and switching is not discussed in detail. Therefore, an adaptive method is proposed to achieve a trade-off between the switching losses and the balancing effect through closed-loop control of the alternating number of the SMs [33]. Reference [34] further proposes an improved balancing method based on the estimation of the current direction, which reduces the current sensors. Despite the flexibility and widely application of software balancing methods, the number of voltage sensors, the extra calculation burden and the signal delay caused by sampling and transmission is still the disadvantage of the software balancing methods.

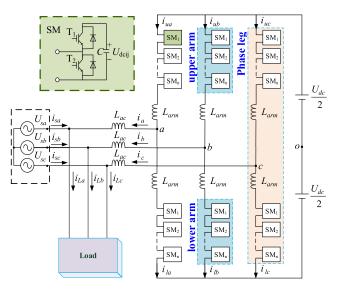

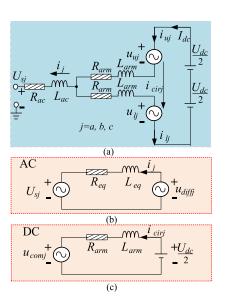

FIGURE 1. The topology of MMCC-DSCC.

In order to decrease the number of voltage sensors and reduce the influence of control delay, hardware balancing methods are gaining popularity [35]-[39]. A simple and low-loss capacitor static voltage balancing method based on self-power supplies is adopted in [35]. Considering the influence of self-power supplies on capacitor voltages, this method can keep the capacitor static voltage balanced by controlling the input characteristic of the self-power supplies. However, this method increases system cost with an additional controller on self-power supplies. In [36], a diode-clamped MMCC topology is proposed, the balancing control between the first and the last module in each arm is realized through an additional transformer. The control of the additional transformer requires a certain resource for this control system, and this will enlarge the volume of the whole device. Based on this paper, reference [37] proposes a parallel-connected improved diode-clamped topology where each arm is composed of two parallel clusters. The rated current of the topology also increases at the same time. However, the structure is much more complex where more switches are needed. In [38], a voltage balancing topology with fault ride-through ability is proposed. Although this topology can operate under DC fault and only need only 3 voltage sensors, the structure is a little complicated. Besides, the power exchange between the upper and the lower arm through hardware may lead to bigger power loss in the additional circuits. Another novel local balancing topology, especially for hybrid SM of half-bridge and full-bridge, is proposed in [39]. For the two adjacent modules, the voltage balancing can be realized within them. It is noted that this presented topology has increased power capacity and the fault ride-through ability. However, only half of the voltage sensors are reduced, and more switches are needed.

In order to achieve SM capacitor voltage balancing control, a novel MMCC-DSCC topology is proposed. It can significantly reduce the number of SM voltage sensors and

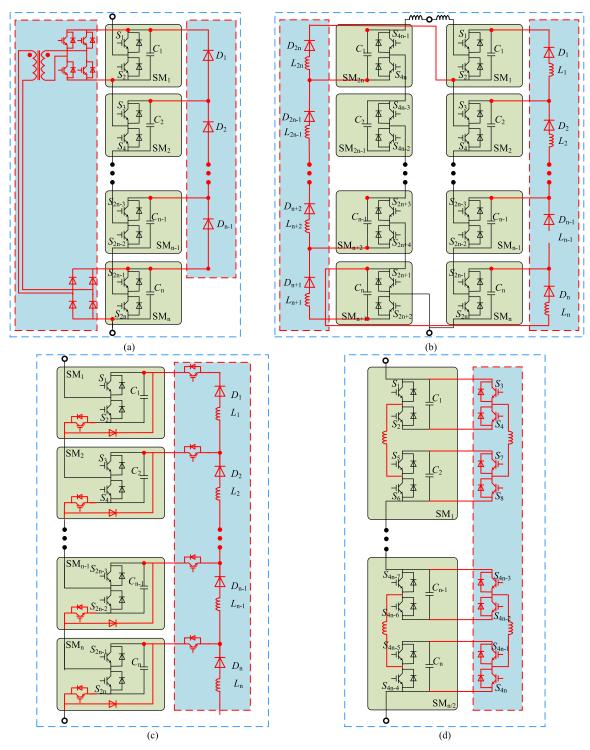

FIGURE 2. Conventional MMCC-DSCC topologies for SM voltage balancing in each arm. (a) The presented diode-clamped topology [36], (b) Parallel-connected diode-clamped topology [37]. (c) Balancing topology with fault ride-through ability [38]. (d) Local voltage balancing topology with increased power capacity [39].

mitigate additional delay process caused by the sampling and control signals transmission. The rest of the paper is organized as follows. In Section II, the proposed topology and its working principle are described, and some comparisons with conventional schemes are presented. Section III introduces its modeling and control method. The parameters selection guide of the proposed scheme and cost analysis are discussed in Section IV. Simulations and experimental results verify the effectiveness proposed topology in Section V and Section VI. The conclusion is presented in Section VII.

## II. DESCRIPTION OF THE PROPOSED MMCC-DSCC

In this section, firstly, some conventional topologies for voltage balancing are presented. Then, the proposed scheme and working principle are described. Finally, detailed comparison results are presented.

The topology of MMCC-DSCC is shown in Fig. 1. It is composed of three identical phase legs, each of which includes the upper arm and the lower arm. The inductor  $L_{arm}$ is series-connected in each arm, each of which contains *n* modules. The output terminal of each phase leg is connected to the grid through a filter inductor  $L_{ac}$ .  $U_{sa}$ ,  $U_{sb}$ , and  $U_{sc}$  are three-phase grid voltages.  $i_{La}$ ,  $i_{Lb}$ , and  $i_{Lc}$  are the three-phase currents of the load,  $i_a$ ,  $i_b$ , and  $i_c$  are output currents of MMCC and  $i_{sa}$ ,  $i_{sb}$ , and  $i_{sc}$  are currents of the grid.  $i_{uj}$  and  $i_{lj}$  (j = a, b, c) are the output currents of the upper and the lower arm.

## A. CONVENTIONAL TOPOLOGIES

Four main conventional MMC topologies for SM voltage balancing in each arm are shown as Fig. 2 [36]–[39].

Fig. 2 (a) shows the presented diode-clamped topology [36], where some additional transformers must be added to achieve SM voltage balancing. Then, Fig. 2 (b) describes the parallel-connected diode-clamped topology where each arm is composed of two parallel clusters [37]. In addition, a novel topology with SM voltage self-balancing and DC fault ride-through ability is described in Fig. 2 (c) [38], where the full bridge SMs are removed from the original topology. Finally, a local voltage balancing topology with bigger power capacity is presented in Fig. 2 (d) [39].

#### B. THE PROPOSED MMCC-DSCC TOPOLOGY

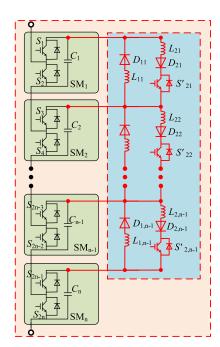

The proposed MMCC-DSCC topology is shown in Fig. 3. It consists of MMCC-DSCC and n - 1 additional series units. Each unit includes two parallel branches. Branch 1 is a series-connected diode and inductor, and Branch 2 is the reversed series-connected diode, inductor, and switch (IGBT and reversed parallel diode). For these switches of n units, no additional switching signals are needed where each switch  $(S'_{2,i-1})$  can be controlled by the corresponding IGBT  $(S_{2,i})$  PWM signals.

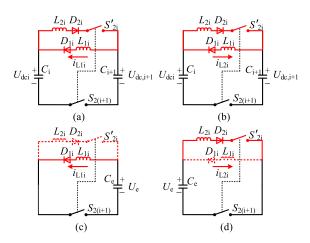

The basic working principle is described in detail as follows. It is assumed that all the switches in the proposed topology in Fig. 3 are ideal devices. There are two situations (**Situation 1** and **Situation 2**) are introduced, and the corresponding equivalent circuit are respectively described as Fig. 4 (a) and Fig. 4 (b).

Situation 1: When the capacitor voltages of the two adjacent capacitors satisfy the constraint  $U_{dc,i+1} > U_{dci}$ , Fig. 4 (a) can be simplified as Fig. 4 (c).

Situation 2: When the capacitor voltages of the two adjacent capacitors satisfy the constraint  $U_{dc,i+1} < U_{dci}$ , the equivalent circuit in Fig. 4 (b) can be simplified as Fig. 4 (d). The switching signal of  $S'_{2,i-1}$ , and detailed working principle are discussed later in this Subsection.

FIGURE 3. The proposed MMCC-DSCC topology.

FIGURE 4. The equivalent circuit between two adjacent modules. (a) The equivalent circuit of situation 1. (b)The equivalent circuit of situation 2. (c) Simplified circuit of (a). (d) Simplified circuit of (b).

Based on KVL law, the equivalent voltage in Fig. 4 can be expressed as

$$U_{e} = \begin{cases} U_{dc,i+1} - U_{dci}, & U_{dc,i+1} > U_{dci} \\ U_{dci} - U_{dc,i+1}, & U_{dc,i+1} < U_{dci} \end{cases}$$

$$C_{e} = \frac{C_{i}}{2}$$

(1)

where  $U_e$  and  $C_e$  represent the equivalent voltage and capacitor, respectively.

In addition, the basic function of total units for every two branches can be introduced as

Branch 1 of all units:

$$U_{dc1} \ge U_{dc2} \ge U_{dc3} \ge \dots \ge U_{dcn} \tag{2}$$

#### TABLE 1. Switching status and balancing operation.

|                   | SM capacitor voltage balancing |                       |   |                         |                |

|-------------------|--------------------------------|-----------------------|---|-------------------------|----------------|

| IGBT              | $C_1$ and                      | $C_2$ and             |   | $C_{n-2}$ and           | $C_{n-1}$ and  |

|                   | <i>C</i> <sub>2</sub>          | <i>C</i> <sub>3</sub> |   | <i>C</i> <sub>n-1</sub> | C <sub>n</sub> |

| $S_1$             | - (on/off)                     | -                     | - | -                       | -              |

| $S_2$             | I                              | I                     | I | I                       | -              |

| $S_3$             | -                              | -                     | - | -                       | -              |

| $S_4$             | on                             | -                     | - | -                       | -              |

| •                 | -                              | -                     |   | -                       | -              |

| S <sub>2n-3</sub> | I                              | I                     | I | I                       | -              |

| S <sub>2n-2</sub> | I                              | I                     | I | on                      | -              |

| S <sub>2n-1</sub> | -                              | -                     | - | -                       | -              |

| S <sub>2n</sub>   | -                              | -                     | - | -                       | on             |

Branch 2 of all units:

$$U_{dc1} \le U_{dc2} \le U_{dc3} \le \dots \le U_{dcn} \tag{3}$$

Therefore, voltage balancing control of SM capacitors can be achieved where the relationship between switching status and balancing operation can be listed in Table 1.

With the proposed topology,  $S'_{2,i}$  can be controlled by the corresponding IGBT ( $S_{2(i+1)}$ ) PWM signals. In situation 2, when  $S_{2(i+1)}$  is turned on, the negative sides of the two adjacent capacitors are connected. Then,  $S'_{2i}$  should be turned on simultaneously to connect the positive sides of the two adjacent capacitors at the same time. When both  $S_{2(+1)}$  and  $S'_{2,i}$  are on, the capacitor can exchange the power freely, and capacitor voltage balancing is thus realized.

It is also noted that with the proposed SM balancing method, only 6 voltage sensors (one in each arm) are needed to detect and regulate the arm voltage balancing for the following reason. In order to precisely control the output currents, the arm voltage has to be regulated. As the SM capacitor voltages in the same arm have been already balanced with the proposed balancing method, only one SM capacitor voltage in each arm are needed to monitor the arm voltage.

#### C. COMPARISONS BETWEEN DIFFERENT TOPOLOGY

For the MMCC-DSCC, comparison results in each arm of different topologies are listed in Table 2. Based on these analysis results, compared with the conventional software balancing or some improved balancing control methods, the proposed topology has some advantages:

- 1) It significantly reduces the number of SM capacitor voltage sensors.

- Control framework can be simple without sort and select process, or some balancing control loops. Additional delay process caused by the sampling and control signals transmission is also mitigated.

- 3) The faster capacitor balancing speed can be obtained [36], [37].

In addition, compared with the presented hardware balancing schemes, some main advantages of the proposed scheme can be found as follow.

- 1) Based on some additional popular diodes insertion, the IGBT number (n < 5) can be reduced, and a transformer can be removed [36].

- The number of power modules including IGBT, diodes, clamping inductors can be greatly reduced, and no additional arm inductor integration [37].

- The number of IGBT, diodes are reduced, and no additional resource is needed to regulate the voltage of the first module [38].

- 4) The number of IGBT and voltage sensors are significantly reduced. Besides, instead of local voltage

| Topology             | Conventional<br>MMCC-DSCC | Fig. 2 (a), [36]             | Fig. 2 (b), [37]        | Fig. 2(c), [38]                      | Fig. 2(d), [39]                         | Fig. 3, proposed |

|----------------------|---------------------------|------------------------------|-------------------------|--------------------------------------|-----------------------------------------|------------------|

| SM capacitors        | n                         | n                            | 2*n                     | n                                    | n                                       | n                |

| IGBT                 | 2*n                       | 2*n+4                        | 4*n                     | 4*n                                  | 4*n                                     | 3*n-1            |

| Clamping diodes      | 0                         | n+3                          | 2*n                     | 2*n                                  | 0                                       | 2*n-2            |

| Clamping inductors   | 0                         | 0                            | 2*n                     | n                                    | n                                       | 2*n-2            |

| Voltages sensors     | n                         | 1                            | 1                       | 1                                    | n/2                                     | 1                |

| Additional resources | Software balancing        | One transformer              | One inductor            | Control on the first<br>SM           | Balancing control<br>of SMs             | None             |

| Advantage            | Fewer power components    | SM voltage Self-<br>balanced | Increased rated current | Arm balancing,<br>Fault ride-through | Increased energy,<br>Fault ride-through | Listed below     |

TABLE 2. Comparison results in each arm of different topologies.

**FIGURE 5.** The equivalent circuit of MMCC-DSCC. (a). Overall equivalent circuit. (b). The equivalent circuit of the AC path. (c). The equivalent circuit of the DC path.

balancing [39], no sorting algorithm is needed for SM balancing.

## III. MODELING AND CONTROL STRATEGY OF MMCC-DSCC BASED STATCOM

This section includes two parts. Firstly, the modeling of MMCC-DSCC is presented. Then, a simple control method is applied.

#### A. MODELING OF MMCC-DSCC

The equivalent circuit of MMCC-DSCC in Fig. 1 is shown in Fig. 5(a), where the equivalent circuit of the AC and DC paths are respectively as Fig. 5(b) and Fig. 5(c).

The AC part can be characterized as (4), where  $R_{eq}$  and  $L_{eq}$  are expressed as (5). In equation (5),  $R_{arm}$  and  $L_{arm}$  are arm resistor and arm inductor,  $R_{ac}$  and  $L_{ac}$  are AC output resistor and arm inductor.

$$\begin{cases}

u_{diffj} = \frac{u_{lj} - u_{uj}}{2} \\

i_j = \frac{i_{uj} - i_{lj}}{2} \\

di

\end{cases}$$

(4)

$$R_{eq}i_j + L_{eq}\frac{di_j}{dt} = u_{diffj} - U_{sj}$$

$$R_{eq} = R_{ac} + R_{arm}/2$$

$$L_{eq} = L_{ac} + L_{arm}/2$$

(5)

Then, the DC part can be characterized as

$$\begin{aligned} u_{comj} &= \frac{u_{lj} + u_{uj}}{2} \\ R_{arm}i_{cirj} + L_{arm}\frac{di_{cirj}}{dt} &= \frac{U_{dc}}{2} - u_{comj} \end{aligned}$$

(6)

#### **B. CURRENT CONTROL**

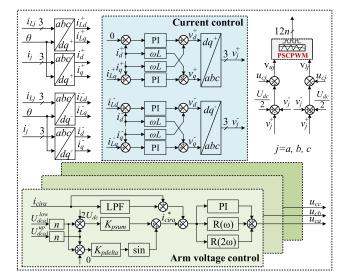

Fig. 6 illustrates the overall control diagram of MMCC-DSCC based STATCOM. The control diagram can be divided into three parts. The first part controls the active

FIGURE 6. Overall control diagram of MMCC-DSCC based STATCOM.

and reactive power in positive and negative sequence dq frames, which can be applied in unbalanced power condition. The second part is adopted to control the sum voltage of each arm. The third part generates the voltage references of each arm and the drive signals of each switch.

The positive and negative sequence current can be transformed into a DC component through an individual transformation in positive and negative sequence dq frame. As a result, the DC component can be accurately tracked by simple PI controllers. The derivation process is exhibited as follows.

The positive sequence and negative sequence is expressed as

$$I_p = \begin{bmatrix} \sin(\omega t + \varphi_p) \\ \sin(\omega t - \frac{2\pi}{3} + \varphi_p) \\ \sin(\omega t + \frac{2\pi}{3} + \varphi_p) \end{bmatrix}, \quad I_n = \begin{bmatrix} \sin(\omega t + \varphi_n) \\ \sin(\omega t + \frac{2\pi}{3} + \varphi_n) \\ \sin(\omega t - \frac{2\pi}{3} + \varphi_n) \end{bmatrix}$$

(7)

The transfer matrix of the positive and negative sequence dq frame can be expressed as

$$C_{dq/abc} = \begin{bmatrix} \sin \omega t \, \sin(\omega t - \frac{2}{3}\pi) \, \sin(\omega t + \frac{2}{3}\pi) \\ \cos \omega t \, \cos(\omega t - \frac{2}{3}\pi) \, \cos(\omega t + \frac{2}{3}\pi) \end{bmatrix}$$

(8)

$$C_{dq/abc}^{*} = \begin{bmatrix} \sin(-\omega t) \, \sin(-\omega t - \frac{2}{3}\pi) \, \sin(-\omega t + \frac{2}{3}\pi) \\ \cos(-\omega t) \, \cos(-\omega t - \frac{2}{3}\pi) \, \cos(-\omega t + \frac{2}{3}\pi) \\ \end{bmatrix}$$

(9)

With the transformation of  $C_{dq/abc}$ , it can be concluded from (10) that the positive sequence current is transferred into the DC component and the negative sequence current is transferred into the second order component.

$$I_{dq}^{p} = \frac{3}{2} I_{p} \begin{bmatrix} \cos \varphi_{p} \\ \sin \varphi_{p} \end{bmatrix}, \quad I_{dq}^{n} = \frac{3}{2} I_{n} \begin{bmatrix} -\cos(2\omega t + \varphi_{n}) \\ \sin(2\omega t + \varphi_{n}) \end{bmatrix}$$

(10)

With the transformation of  $C^*_{dq/abc}$ , it can be concluded from (11) that the negative sequence current is transferred into the DC component and the positive sequence current is transferred into the second order component.

$$I_{dq}^{p*} = \frac{3}{2} I_p \begin{bmatrix} \cos(2\omega t + \varphi_p) \\ \sin(2\omega t + \varphi_p) \end{bmatrix}, \quad I_{dq}^{n*} = \frac{3}{2} I_n \begin{bmatrix} -\cos\varphi_n \\ \sin\varphi_n \end{bmatrix}$$

(11)

The similar design principle of PI controllers can be found in the reference [40], and it is not be discussed in this paper.

## C. ARM VOLTAGE CONTROL

The second part is adopted to regulate the sum voltage of SMs in each arm. The SM voltages within each arm have already been balanced through the proposed topology. It can be easily seen that the arm voltage can be reflected from the measurement of a single SM voltage in (12). Thus, this capacitor voltage balancing process significantly reduces the number of voltage sensors.

$$\sum U_{dcij}^{up} = n \cdot U_{dci1}^{up}, \quad \sum U_{dcij}^{low} = n \cdot U_{dci1}^{low}$$

(12)

where  $U_{dci1}^{up}$  and  $U_{dci1}^{low}$  (i = a, b, c) are the capacitor voltages of the first SM in the upper and the lower arm respectively. It's noted that only one SM voltage sensor in each arm is needed. In this paper, the first SM in each arm is applied.

The arm voltage is regulated by control of circulating current. The circulating current reference to regulate the arm voltage includes two components. The first component is to control the sum voltage of two arms in the same phase and the second component is used to control the voltage difference between the upper and the lower arm. According to [39], the reference values of circulating currents can be expressed as

$$i_{c}^{*} = K_{psum}(2U_{dc} - \text{LPF}\{U_{\Sigma}\}) - K_{pdelta}(0 - \text{LPF}\{U_{\Delta}\}) \sin \omega t$$

$$U_{\Sigma} = \sum U_{dcij}^{up} + \sum U_{dcij}^{low}, \quad U_{\Delta} = \sum U_{dcij}^{up} - \sum U_{dcij}^{low}$$

(13)

In order to control the circulating currents, the PIR controller is adopted. The PI controller is used to control the DC component of the circulating currents. In addition, the other two resonant (R) controllers are adopted to respectively achieve the fundamental current control and suppress the second order components of circulating currents. For the control parameters design guide of this PIR controller can also be found in reference [41].

#### **D. MODULATION**

In this paper, the popular phase shifted carrier (PSC) PWM is used [40], and the final voltage reference of each arm can be expressed as

$$\begin{bmatrix} V_{uj} \\ V_{lj} \end{bmatrix} = \begin{bmatrix} \frac{U_{dc}}{2} - v_j + u_{cj} \\ \frac{U_{dc}}{2} + v_j + u_{cj} \end{bmatrix}$$

(14)

where  $V_{uj}$  and  $V_{lj}$  (j = a, b, c) are the voltage reference of the upper and the lower arm.

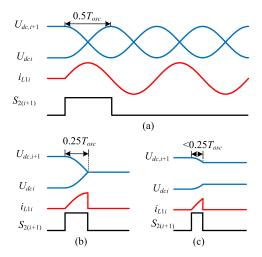

**FIGURE 7.** The relationship of voltage and current in the diode-clamped circuit. (a) Conduction period of clamping circuit  $\Delta T = 0.5T_{osc}$ . (b) Conduction period of clamping circuit  $\Delta T = 0.25T_{osc}$ . (c) Conduction period of clamping circuit  $\Delta T < 0.25T_{osc}$ .

### **IV. DISCUSSION**

In this section, the parameters design guide for the proposed scheme is discussed first, including clamping inductor, diodes, and IGBT switches. Then, the cost of the proposed balancing scheme is analyzed.

# A. PARAMETER SELECTION OF THE CLAMPING INDUCTOR

As the balancing analysis principle of situation 1 and situation 2 is identical, situation 1 is used as an example to describe the parameter selection process. According to Fig. 4 (a), when the switch  $S_{2,(i+1)}$  is on, based on KVL law, the following equations can be calculated as

$$\begin{cases} L_e C_e \frac{d^2 U_e}{dt} + U_e = 0\\ L_e = L_{1i} = L_{2i} \end{cases}$$

(15)

Thus, it's clearly shown that it is a second-order system and the solution of the linear differential equation can be expressed as

$$\begin{cases} U_e = \frac{U_0}{2} (e^{\gamma t} + e^{-\gamma t}) \\ i_{L1i} = C_e \frac{dUe}{dt} = \frac{C_e U_0 \gamma}{2} (e^{\gamma t} - e^{-\gamma t}) \end{cases}$$

(16)

where  $U_0$  is the initial voltage of  $U_e$ ,  $i_{L1i}$  is the clamping current of the diode-clamped circuit, and  $\gamma$  is system eigenvalue.

$$\gamma = j\omega_0 = j\frac{1}{\sqrt{L_e C_e}} \tag{17}$$

The solution can be further expressed as

$$\begin{cases} U_e = U_0 \cos(\omega_0 t) \\ i_{L1i} = \sqrt{\frac{C_e}{L_e}} U_0 \sin(\omega_0 t) \end{cases}$$

(18)

$$T_{osc} = 2\pi \sqrt{L_e C_e} \tag{19}$$

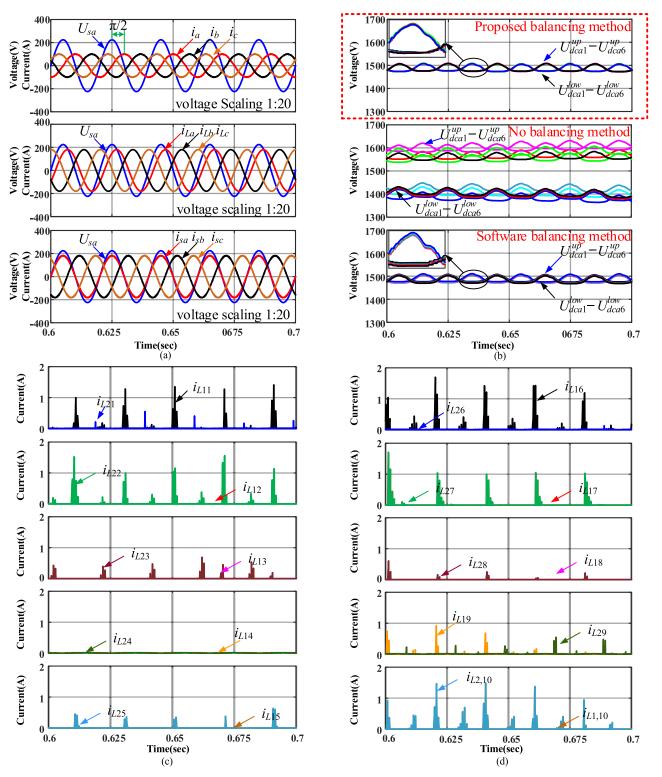

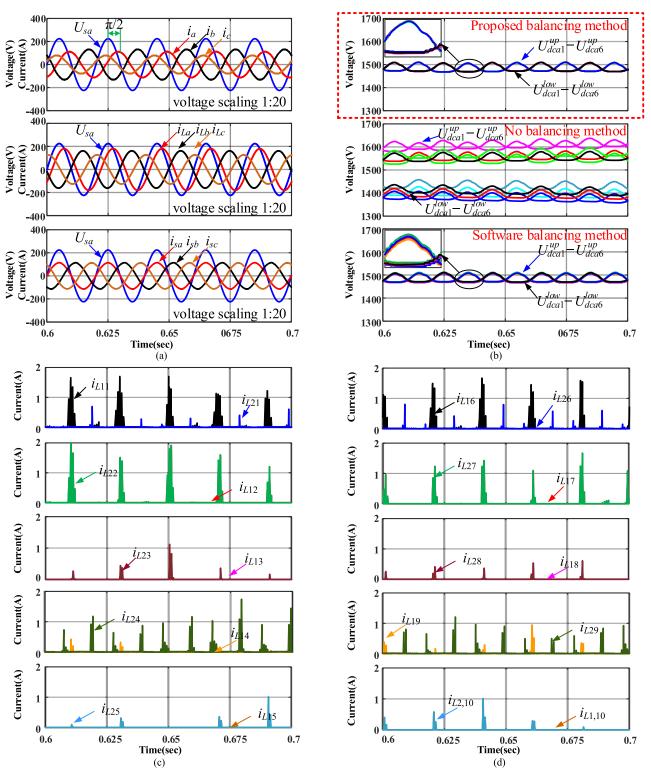

FIGURE 8. Simulation results of MMCC-DSCC based STATCOM under balanced load. (a) System current waveforms. (b) Comparison of SM voltages with different balancing methods. (c) Clamping currents in the upper arm. (d) Clamping currents in the lower arm.

It is clearly seen that the waveform of  $U_e$  fluctuates as the sine wave and the period of fluctuation  $T_{osc}$  is closely related to the value of clamping inductor  $L_e$ .

$L_{\rm e}$  has a close relationship with system performance. That is to say, if  $L_{\rm e}$  gets larger, the  $T_{osc}$  will be larger, and the SM voltage balancing effect will be worse. However, if  $L_{\rm e}$  gets smaller,  $T_{osc}$  will be smaller, and the possibility of oscillation

FIGURE 9. Simulation results of MMCC-DSCC based STATCOM under balanced load. (a)System current waveforms. (b) Comparison of SM voltages with different balancing methods. (c) Clamping currents in the upper arm. (d) Clamping currents in the lower arm.

and extra power loss may be higher. Thus, it is very necessary to give the constraint for the inductor selection.

Assuming  $U_{dc,i+1} > U_{dci}$ , the relationship of the voltage  $U_e$  and the clamping current  $i_{L1i}$  is shown as Fig. 7 according

to (18). Thus,  $\Delta T$ , the active period of the switch  $S_{2(i+1)}$ , is supposed to be smaller than  $0.25T_{osc}$ . However, it is unrealistic to keep each  $\Delta T$  smaller than  $0.25T_{osc}$  in the real application. In a word, an average of  $\Delta T$  can be described

as

$$\Delta \bar{T} = \lambda m T_{sw} < 0.25 T_{osc} \tag{20}$$

where *m* is the modulation index,  $\lambda$  is the average coefficient (0 <  $\lambda$  < 1), and  $T_{sw}$  is the reciprocal of the switching frequency.

Therefore, based on the last two equations, the constraint can be presented as

$$L_e > \frac{4\lambda^2 m^2}{\pi^2 f_{sw}^2 C_e} \tag{21}$$

## B. PARAMETER SELECTION OF CLAMPING DIODE AND SWITCH

As the manufacture errors, PSC modulation, and other disturbances in the real SM circuits, power unbalance among SMs in each arm occurs.

Each SM power and power difference among SMs in each arm can be respectively defined as

$$P_{SM} = \frac{1}{2}C\left(\frac{U_{dc}}{n}\right)^2 \tag{22}$$

$$P_{dif} = (\sigma + \gamma + \delta)P_{SM} \tag{23}$$

where  $\sigma$ ,  $\gamma$ , and  $\delta$  are power difference proportion values caused by the manufacture errors, PSC modulation, and other disturbances respectively.

The system can be in a balanced condition when exchange power between two adjacent SMs is equal to about half of the power difference  $P_{dif}$ . Based on the energy conservation law, it can be described as

$$0.5P_{dif} = \frac{U_{dc}}{n} i_{DCC\_ave} \tag{24}$$

where  $i_{DCC\_ave}$  is the average clamping current through the Branch 1.

In order to withstand this clamping current, the forward current of clamping diodes is

$$i_{DF} = \alpha i_{DCC\_ave} \tag{25}$$

where  $\alpha$  is large than 1 for enough current margin of diodes.

$$v_{RDF} = \varepsilon \frac{U_{dc}}{n} \tag{26}$$

where  $\varepsilon$  is usually less than 10%.

Based on these analysis results, the diode can be selected. In addition, IGBT switch selection is discussed as follows.

For the switch, the maximum conduction current is the same as (25).

$$i_{SF} = i_{DF} = \alpha i_{DCC\_ave} \tag{27}$$

The maximum value of the reserved voltage for the switch is described as

$$v_{RSF} = \frac{U_{dc}}{n} \tag{28}$$

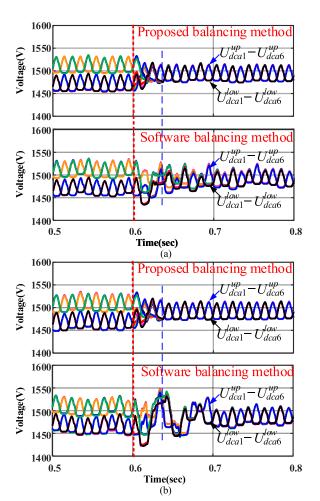

FIGURE 10. Comparisons results of the proposed balancing method and conventional software balancing method. (a) Comparisons under balanced load in Scenario 1. (b) Comparisons under unbalanced load in Scenario 2.

Based on the above analysis results, the diode and switch can be selected considering some real constraints.

## C. COST ANALYSIS OF THE PROPOSED BALANCING TOPOLOGY

Compared with traditional software balancing method, the reduced resources and additional resources are listed below.

## 1) REDUCED RESOURCES

6n-6 reduced voltage sensors, 6n-6 reduced optical senders, 6n-6 reduced optical receivers, 6n-6 reduced optical fiber cables, and lowered controller requirement.

#### 2) ADDITIONAL RESOURCES

6n-6 IGBTs, 6n-6 drivers, 12n-12 diodes and 12n-12 inductors. The additional cost of the proposed method can be calculated through the following equation.

$$\Sigma_{\text{cost}} = (6n - 6)(\Sigma_{\text{IGBT}} + \Sigma_{peri}) + (12n - 12)(\Sigma_{dio} + \Sigma_{ind}) - (6n - 6)(\Sigma_{sens} + \Sigma_{send} + \Sigma_{rece} + \Sigma_{cab})$$

(29)

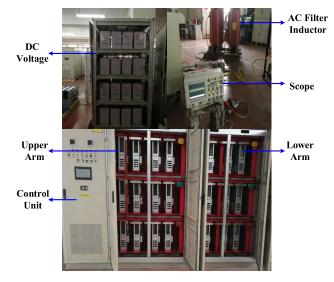

FIGURE 11. Laboratory prototype.

where  $\Sigma_{cost}$  is the total additional cost.  $\Sigma_{IGBT}$  and  $\Sigma_{peri}$  are the cost of IGBT and its peripheral cost (including drivers and other auxiliary costs).  $\Sigma_{dio}$  and  $\Sigma_{ind}$  are the cost of diodes and inductors.  $\Sigma_{sens}$ ,  $\Sigma_{send}$ ,  $\Sigma_{rece}$ , and  $\Sigma_{cab}$  are the cost of the voltage sensors, optical senders, optical receivers, and optical fiber cables respectively.

According to reference [42], the cost of IGBT can be expressed as

$$\Sigma_{\text{IGBT}} = \sigma_{chip} A_{chip} + \Sigma_{pack} \tag{30}$$

where  $\sigma_{cost}$  is the specific price per chip area and  $A_{chip}$  is the chip area.  $\Sigma_{pack}$  is the package price.

The peripheral cost can be roughly expressed as

$$\Sigma_{\text{peri}} = 0.1 \Sigma_{\text{IGBT}} \tag{31}$$

Substituting (30) and (31) into (29), the total additional cost can further be expressed as

$$\Sigma_{\text{cost}} = (6n - 6)(1.1(\sigma_{chip}A_{chip} + \Sigma_{pack}) + 2\Sigma_{dio} + 2\Sigma_{ind} - \Sigma_{sens} - \Sigma_{send} - \Sigma_{rece} - \Sigma_{cab})$$

(32)

### **V. SIMULATION RESULTS**

To verify the effectiveness of the proposed MMCC-DSCC scheme, the same topology in Fig. 3 in MATLAB/Simulink is used. The simulation parameters are shown in Table 3.

Three simulation scenarios are shown in Table 4, where **Scenario 1** describes the balanced load condition, **Scenario 2** describes the unbalanced load condition, and **Scenario 3** compares the balancing effect between software balancing method and the proposed balancing method under balanced and unbalanced load.

Scenario 1 Fig. 8 shows the simulation results for the proposed MMCC-DSCC based STATCOM under balanced load. The output currents of MMCC-DSCC, the load currents and three-phase grid currents after reactive power compensation

## 83068

TABLE 3. Parameters of the simulation system.

| Туре        | Circuit parameters        | Values   |  |

|-------------|---------------------------|----------|--|

| Thursenhaus | Line voltage              | 5.5 kV   |  |

| Three-phase | frequency                 | 50 Hz    |  |

| grids       | AC filter inductor        | 6 mH     |  |

|             | DC voltage                | 9 kV     |  |

|             | DC capacitor,             | 4.7 mF   |  |

| MMCC-DSCC   | Switching frequency       | 1.25 kHz |  |

| MMCC-DSCC   | Arm inductor              | 3 mH     |  |

|             | Clamping inductor         | 100 µH   |  |

|             | SM number per arm         | 6        |  |

| Туре        | <b>Control parameters</b> | Values   |  |

| Current     | $K_{P1}$ ,                | 50       |  |

| control     | $K_{l1}$                  | 500      |  |

|             | $K_{psum}$ ,              | 0.004    |  |

|             | $K_{pdelta}$ ,            | 0.005    |  |

| Arm voltage | $K_p$ ,                   | 0.5      |  |

| control     | $K_i$ ,                   | 2.5      |  |

|             | $K_{R\omega}$ ,           | 5        |  |

|             | $K_{R2\omega},$           | 10       |  |

**TABLE 4.** Simulation scenarios.

| Scenarios | Inductive load                         | Description                                               |                                            |                              |

|-----------|----------------------------------------|-----------------------------------------------------------|--------------------------------------------|------------------------------|

| 1         | Balanced                               | Load A, Load B and Load C<br>340 kW 220 kvar              |                                            |                              |

| 2         | Unbalanced                             | Load A<br>340 kW<br><b>340 kvar</b>                       | <b>Load B</b><br>270 kW<br><b>250 kvar</b> | Load C<br>180 kW<br>160 kvar |

| 3         | Balanced (Sce.1)<br>Unbalanced (Sce.2) | <b>Comparison:</b><br>Software method and proposed method |                                            |                              |

are shown in Fig. 8 (a). It's clearly seen that good control performance can be achieved where three-phase grid currents are balanced and the power factor is nearly 1. Then, as shown in Fig. 8 (b), the proposed topology has realized similar SM voltage balancing control of individual capacitors, compared with the software balancing method. However, SM capacitor voltage remains unbalanced without balancing control. In addition, internal currents of Branch1 and Branch2 are very small in the upper five, and the lower five units are respectively depicted in Fig. 8 (c) and Fig. 8 (d), indicating that they are much smaller than AC output currents of this MMCC.

Scenario 2 Fig. 9 depicts the simulation results for the proposed MMCC-DSCC based STATCOM under unbalanced load. The output currents of MMCC-DSCC, the load currents, and three-phase grid currents after reactive power compensation are shown in Fig. 9 (a). It's easily seen that similar simulation results as balanced load in Scenario1, where balanced grid currents are maintained, and effective reactive power are compensated. Then, as shown in Fig. 9 (b), similar simulation performance in Scenario1 under balanced load with SM voltage balancing control can be adopted under unbalanced load. But SM voltages are unbalanced without balancing control. In addition, internal currents of Branch1 and Branch2 are very small in the upper five, and the lower five units are respectively depicted in Fig. 9 (c) and Fig. 9 (d), showing that they are much smaller than AC output currents of this MMCC-DSCC.

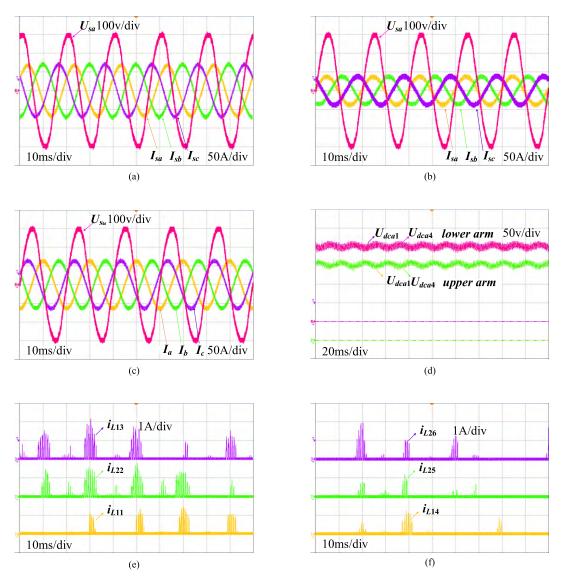

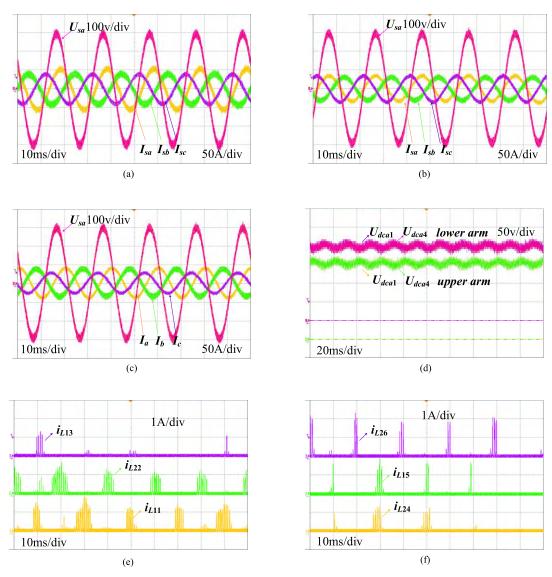

FIGURE 12. Experiment results of MMCC-DSCC based STATCOM under balanced load. (a) Grid voltage and currents before compensation. (b) Grid voltage and currents after compensation. (c) Grid voltage and output currents. (d) Capacitor voltages in phase A. (e) Currents of clamping circuits in the upper arm of phase A. (f) Currents of clamping circuits in the lower arm of phase A.

Based on these simulation results of **Scenario 1** and **Scenario 2**, the proposed scheme for MMCC-DSCC based STATCOM is always effective in balanced and unbalanced load.

**Scenario 3** Fig. 10 exhibits the comparison results of the proposed voltage balancing method and the software balancing method [40]. The simulation results include two cases: balanced load and unbalanced load. It should be noted that in order to vividly demonstrate the advantages of the proposed method, an artificial initial deviation of SM voltages is set before 0.6s.

For balanced load, the SM voltages are shown in Fig. 10 (a), where both the proposed balancing method and the software balancing method are activated at 0.6s. As is shown in the figure, the proposed method has the faster balancing speed than the software balancing method during the dynamic

process indicating the proposed balancing method can lower the effect brought by sampling and control delay. For unbalanced load, the dynamic SM voltages are shown in Fig. 10 (b), where both the two balancing methods are activated at 0.6 s. It clearly shows that the proposed balancing method has a faster balancing speed than the software balancing method, indicating that the proposed balancing method can reduce the effect of sampling and control delay.

## **VI. EXPERIMENTAL RESULTS**

A laboratory prototype based on nine-level MMCC-DSCC based STATCOM has been implemented in the laboratory as shown in Fig. 11. The experiment parameters are given in Table 5. The two experiment scenarios are given in Table 6. The proposed control are implemented with TMS320F28335 and 10M02SCE144C8G. The Agilent scope

FIGURE 13. Experiment results of MMCC-DSCC based STATCOM under unbalanced load. (a) Grid voltage and currents before compensation. (b) Grid voltage and currents after compensation. (c) Grid voltage and output currents. (d) Capacitor voltages in phase A. (e) Currents of clamping circuits in the upper arm of phase A. (f) Currents of clamping circuits in the lower arm of phase A.

| Туре                 | <b>Circuit parameters</b> | Values |

|----------------------|---------------------------|--------|

| Thuse shees          | Line voltage              | 380 V  |

| Three-phase<br>grids | frequency                 | 50 Hz  |

|                      | AC filter inductor        | 5 mH   |

|                      | DC voltage                | 800 V  |

|                      | DC capacitor,             | 3 mF   |

| MMCC-DSCC            | Arm inductor              | 100 µH |

|                      | Clamping inductor         | 1 mH   |

|                      | SM number per arm         | 4      |

TABLE 5. Parameters of the experiments.

DSO5014A is used to display and record the experimental waveforms.

**Scenario 1** The experiment results of the proposed MMCC-DSCC under balanced load are shown in Fig. 12.

#### TABLE 6. Experiment scenarios.

| Scenarios | Inductive load | Load A   | Load B | Load C |  |  |

|-----------|----------------|----------|--------|--------|--|--|

| 1         | Balanced       |          | 7 kW   |        |  |  |

| I         | Inductive      | 9.5 kvar |        |        |  |  |

| 2         | Unbalanced     | 7 kW     | 7 kW   | 7 kW   |  |  |

|           | Inductive      | 8 kvar   | 5 kvar | 4 kvar |  |  |

The grid voltage and three-phase currents before and after compensation are shown in Fig. 12 (a) and (b), respectively. The output currents of MMCC-DSCC is shown in Fig. 12 (c). It can be clearly seen that the proposed MMCC-DSCC can effectively compensate the reactive power. The capacitor voltages and currents in Branch 1 or Branch 2 in the upper 3 units and the lower 3 units are shown in Fig. 12 (d), (e) and (f) individually. With the limitation of scope signals, only one

clamping current between two adjacent SMs is displayed. As shown in Fig. 12 (d), the individual capacitor voltage of each SM is well balanced. The results in Fig. 12 (e) and Fig. 12 (f) indicates that the internal currents are much smaller than output currents.

**Scenario 2** The experiment results of MMCC-DSCC under unbalanced load are shown in Fig. 13. The grid voltage and three-phase currents before and after compensation are shown in Fig. 13 (a) and (b), respectively. The output currents of MMCC-DSCC is shown in Fig. 13 (c). It can be easily showed that reactive power compensation can be achieved by the proposed MMCC-DSCC. The capacitor voltages and currents in Branch 1 or Branch 2 in the upper 3 units and the lower 3 units are shown in Fig. 13 (d), (e) and (f) individually, showing SM capacitor voltages has been well balanced and internal currents are much smaller than the output currents of MMCC-DSCC.

According to the above experimental results of **Scenario 1** and **Scenario 2**, the proposed scheme for MMCC-DSCC based STATCOM is always effective in balanced and unbalanced load.

#### VII. CONCLUSION

For MMCC-DSCC based STATCOM, a new voltage balancing control scheme for all the SM capacitors is proposed. Compared with conventional software balancing control methods, the number of capacitor voltage sensors by the proposed scheme has been greatly reduced, especially in the higher voltage or more SMs in each arm. Both Simulation waveforms and experimental results verify the effectiveness of this control scheme even under two operation conditions of three-phase balanced and unbalanced load. For the inserted additional units, the design guide of these corresponding components has been described. By the proposed scheme, both DC capacitor voltage balancing control and reactive power compensation are simultaneously realized for MMCC-DSCC based STATCOM even in power unbalanced condition.

More effective combination of the improved controller and this proposed hardware topology will be further developed in the future work.

#### REFERENCES

- J. Wang and P. Wang, "Power decoupling control for modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 33, no. 11, pp. 9296–9309, Nov. 2018.

- [2] D. Zhou, H. Qiu, S. Yang, and Y. Tang, "Submodule voltage similaritybased open-circuit fault diagnosis for modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 8008–8016, Aug. 2019.

- [3] M. Guan and Z. Xu, "Modeling and control of a modular multilevel converter-based HVDC system under unbalanced grid conditions," *IEEE Trans. Power Electron.*, vol. 27, no. 12, pp. 4858–4867, Dec. 2012.

- [4] J. Wang, J. Liang, C. Wang, and X. Dong, "Circulating current suppression for MMC-HVDC under unbalanced grid conditions," *IEEE Trans. Ind. Appl.*, vol. 53, no. 4, pp. 3250–3259, Jul./Aug. 2017.

- [5] H. You and X. Cai, "Stepped 2-level operation of three-port modular DC/DC converter applied in HVDC application," *IEEE Access*, vol. 6, pp. 53822–53832, 2018.

- [7] J. Xu, A. M. Gole, and C. Zhao, "The use of averaged-value model of modular multilevel converter in DC grid," *IEEE Trans. Power Del.*, vol. 30, no. 2, pp. 519–528, Apr. 2015.

- [8] Z. Kong, X. Huang, Z. Wang, J. Xiong, and K. Zhang, "Active power decoupling for submodules of a modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 125–136, Jan. 2018.

- [9] Z. Shu, M. Liu, L. Zhao, S. Song, Q. Zhou, and X. He, "Predictive harmonic control and its optimal digital implementation for MMC-based active power filter," *IEEE Trans. Ind. Electron.*, vol. 63, no. 8, pp. 5244–5254, Aug. 2016.

- [10] E. Kontos, G. Tsolaridis, R. Teodorescu, and P. Bauer, "High order voltage and current harmonics mitigation using the modular multilevel converter STATCOM," *IEEE Access*, vol. 5, pp. 16684–16692, 2017.

- [11] L. Zhang, Y. Tang, S. Yang, and F. Gao, "Decoupled power control for a modular-multilevel-converter-based hybrid AC–DC grid integrated with hybrid energy storage," *IEEE Trans. Ind. Electron.*, vol. 66, no. 4, pp. 2926–2934, Apr. 2019.

- [12] N. Li, F. Gao, T. Hao, Z. Ma, and C. Zhang, "SOH balancing control method for the MMC battery energy storage system," *IEEE Trans. Ind. Electron.*, vol. 65, no. 8, pp. 6581–6591, Aug. 2018.

- [13] H. P. Mohammadi and M. T. Bina, "A transformerless medium-voltage STATCOM topology based on extended modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1534–1545, May 2011.

- [14] S. Du and J. Liu, "A study on DC voltage control for chopper-cell-based modular multilevel converters in D-STATCOM application," *IEEE Trans. Power Del.*, vol. 28, no. 4, pp. 2030–2038, Oct. 2013.

- [15] A. F. Cupertino, J. V. M. Farias, H. A. Pereira, S. I. Seleme, and R. Teodorescu, "Comparison of DSCC and SDBC modular multilevel converters for STATCOM application during negative sequence compensation," *IEEE Trans. Ind. Electron.*, vol. 66, no. 3, pp. 2302–2312, Mar. 2019.

- [16] B. Li, S. Shi, D. Xu, and W. Wang, "Control and analysis of the modular multilevel DC de-icer with STATCOM functionality," *IEEE Trans. Ind. Electron.*, vol. 63, no. 9, pp. 5465–5476, Sep. 2016.

- [17] X. Yu, Y. Wei, and Q. Jiang, "STATCOM operation scheme of the CDSM-MMC during a pole-to-pole DC fault," *IEEE Trans. Power Del.*, vol. 31, no. 3, pp. 1150–1159, Jun. 2016.

- [18] A. Dekka, B. Wu, N. R. Zargari, and R. L. Fuentes, "Dynamic voltage balancing algorithm for modular multilevel converter: A unique solution," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 952–963, Feb. 2016.

- [19] M. Hagiwara and H. Akagi, "Control and experiment of pulsewidthmodulated modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 24, no. 7, pp. 1737–1746, Jul. 2009.

- [20] P. Hu, D. Jiang, Y. Zhou, Y. Liang, J. Guo, and Z. Lin, "Energy-balancing control strategy for modular multilevel converters under submodule fault conditions," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 5021–5030, Sep. 2014.

- [21] S. Yang, Y. Tang, and P. Wang, "Distributed control for a modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5578–5591, Jul. 2018.

- [22] Y. Luo, Z. Li, Y. Li, and P. Wang, "A distributed control method for power module voltage balancing of modular multilevel converters," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2016, pp. 1–5.

- [23] C. Xue and Z. Ma, "Capacitor voltage balancing and current control method of modular multilevel converter based on generalized averaging approach," *IET Power Electron.*, vol. 10, no. 15, pp. 2242–2247, Dec. 2017.

- [24] F. Deng and Z. Chen, "Voltage-balancing method for modular multilevel converters switched at grid frequency," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 2835–2847, May 2015.

- [25] H. Saad, X. Guillaud, J. Mahseredjian, S. Dennetiere, and S. Nguefeu, "MMC capacitor voltage decoupling and balancing controls," *IEEE Trans. Power Del.*, vol. 30, no. 2, pp. 704–712, Apr. 2015.

- [26] Z. Li, F. Gao, F. Xu, X. Ma, Z. Chu, P. Wang, R. Gou, and Y. Li, "Power module capacitor voltage balancing method for a ±350-kV/1000-MW modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 3977–3984, Jun. 2016.

- [27] A. Ghazanfari and Y. A.-R. I. Mohamed, "A hierarchical permutation cyclic coding strategy for sensorless capacitor voltage balancing in modular multilevel converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 2, pp. 576–588, Jun. 2016.

- [28] J.-W. Moon, J.-S. Gwon, J.-W. Park, D.-W. Kang, and J.-M. Kim, "Model predictive control with a reduced number of considered states in a modular multilevel converter for HVDC system," *IEEE Trans. Power Del.*, vol. 30, no. 2, pp. 608–617, Apr. 2015.

- [29] P. Liu, Y. Wang, W. Cong, and W. Lei, "Grouping-sorting-optimized model predictive control for modular multilevel converter with reduced computational load," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 1896–1907, Mar. 2016.

- [30] J. Huang, B. Yang, F. Guo, Z. Wang, X. Tong, A. Zhang, and J. Xiao, "Priority sorting approach for modular multilevel converter based on simplified model predictive control," *IEEE Trans. Ind. Electron.*, vol. 65, no. 6, pp. 4819–4830, Jun. 2018.

- [31] S. B. Bashir and A. R. Beig, "An improved voltage balancing algorithm for grid connected MMC for medium voltage energy conversion," *Int. J. Electr. Power Energy Syst.*, vol. 95, pp. 550–560, Feb. 2018.

- [32] L. Mathe, "Performance comparison of the modulators with balancing capability used in MMC applications," in *Proc. IEEE 26th Int. Symp. Ind. Electron. (ISIE)*, Jun. 2017, pp. 815–820.

- [33] L. Luo, Z. Li, L. Xu, X. Xiong, Y. Li, and C. Zhao, "An adaptive voltagebalancing method for high-power modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 33, no. 4, pp. 2901–2912, Apr. 2018.

- [34] P. Hu, R. Teodorescu, S. Wang, S. Li, and J. M. Guerrero, "A currentless sorting and selection-based capacitor-voltage-balancing method for modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1022–1025, Feb. 2019.

- [35] L. Luo, Y. Zhang, L. Jia, and N. Yang, "A novel method based on selfpower supply control for balancing capacitor static voltage in MMC," *IEEE Trans. Power Electron.*, vol. 33, no. 2, pp. 1038–1049, Feb. 2018.

- [36] C. Gao, X. Jiang, Y. Li, Z. Chen, and L. Liu, "A DC-link voltage selfbalance method for a diode-clamped modular multilevel converter with minimum number of voltage sensors," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2125–2139, May 2013.

- [37] C. Gao and J. Lv, "A new parallel-connected diode-clamped modular multilevel converter with voltage self-balancing," *IEEE Trans. Power Del.*, vol. 32, no. 3, pp. 1616–1625, Jun. 2017.

- [38] T. Yin, Y. Wang, X. Wang, S. Yin, S. Sun, and G. Li, "Modular multilevel converter with capacitor voltage self-balancing using reduced number of voltage sensors," in *Proc. Int. Power Electron. Conf. (IPEC-Niigata-ECCE Asia)*, May 2018, pp. 1455–1459.

- [39] J. Xu, J. Zhang, J. Li, L. Shi, X. Jia, and C. Zhao, "Series-parallel HBSM and two-port FBSM based hybrid MMC with local capacitor voltage self-balancing capability," *Int. J. Elect. Power Energy Syst.*, vol. 103, pp. 203–211, Dec. 2018.

- [40] M. Hagiwara, R. Maeda, and H. Akagi, "Control and analysis of the modular multilevel cascade converter based on double-star choppercells (MMCC-DSCC)," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1649–1658, Jun. 2011.

- [41] K. Sharifabadi, L. Harnefors, H.-P. Nee, S. Norrga, and R. Teodorescu, Design, Control, and Application of Modular Multilevel Converters for HVDC Transmission Systems, 1st ed. Hoboken, NJ, USA: Wiley, 2016.

- [42] P. Tu, S. Yang, and P. Wang, "Reliability- and cost-based redundancy design for modular multilevel converter," *IEEE Trans. Ind. Electron.*, vol. 66, no. 3, pp. 2333–2342, Mar. 2019.

**QIAN XIAO** received the B.S. and M.S. degrees in electrical engineering from the Hebei University of Technology, Tianjin, China, in 2011 and 2014, respectively. He is currently pursuing the Ph.D. degree in electrical engineering with Tianjin University, Tianjin. Since 2018, he has been a Visiting Researcher with the Department of Energy Technology, Aalborg University, Aalborg, Denmark.

His research interests include multilevel converters, DC/DC converters, and power electronics

for distributed generation, microgrid, and HVDC.

**CHAOYU DONG** received the B.Sc. degree in electrical engineering from Tianjin University, China, in 2013, where he is currently pursuing the Ph.D. degree. His research interests include power systems and power electronics stability analysis.

**HONGJIE JIA** received the Ph.D. degree in electrical engineering from Tianjin University, China, in 2001.

He became an Associate Professor with Tianjin University, in 2002, where he was promoted as a Professor in 2006. His research interests include power reliability assessment, stability analysis and control, distribution network planning and automation, and smart grids.

**YUNFEI MU** (M'11) was born in Hebei, China. He received the Ph.D. degree from the School of Electrical Engineering and Automation, Tianjin University, Tianjin, China, in 2012, where he is currently an Associate Professor. His research interests include integrated energy systems, electric vehicles, and smart grids.

**YU JIN** was born in Heilongjiang, China, in 1994. He received the B.S. degree from the School of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin, China, in 2015, where he is currently pursuing the Ph.D. degree. Since 2018, he has been a Visiting Researcher with the Department of Energy Technology, Aalborg University, Aalborg, Denmark.

His current research interests include multilevel converters and the applications in microgrid.

**BING XIE** was born in Shenyang, China. He received the B.S. and M.S. degrees in agricultural electrification and automation from Shenyang Agricultural University, Shenyang, China, in 2008 and 2013, respectively. He is currently pursuing Ph.D. degree with the School of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin, China.

His current research interests include the modeling and control of bidirectional converters and battery energy storage systems.

**YANCHAO JI** (M'98) received the B.Eng. and M.Eng. degrees in electrical engineering from Northeast Electric Power University, Jilin, China, in 1983 and 1989, respectively, and the Ph.D. degree in electrical engineering from North China Electric Power University, Beijing, China, in 1993.

He joined the Department of Electrical Engineering, Harbin Institute of Technology, Harbin, China, in 1993, where he was an Associate Profes-

sor, with the Department of Electrical Engineering, from 1995 to 1996 and is currently a Professor. His current research interests include pulse width modulation technique, power converter, and flexible ac transmission systems devices.

**SANJAY K. CHAUDHARY** (S'01–M'11) received the M.Tech. degree in electrical engineering from IIT Kanpur, Kanpur, India, in 2002, and the Ph.D. degree in electrical engineering from Aalborg University, Aalborg, Denmark, in 2011.

He was with ABB Ltd., Bangalore, India, from 2002 to 2005, and then he joined the Honeywell Technology Solutions Laboratory, Bangalore. Since 2011, he has been an Assistant Professor with the Department of Energy Technology,

Aalborg University. His current research interests include grid integration of renewable energy, the application of power converters in power systems, high voltage dc transmission, and flexible ac transmission systems.

**REMUS TEODORESCU** (S'94–M'99–SM'02– F'12) received the Dipl.Ing. degree in electrical engineering from the Polytechnical University of Bucharest, Bucharest, Romania, and the Ph.D. degree in power electronics from the University of Galati, Galati, Romania, in 1989 and 1994, respectively.

In 1998, he joined the Department of Energy Technology, Power Electronics Section, Aalborg University, Aalborg, Denmark, where he is cur-

rently a Professor. He was the Coordinator of the Vestas Power Program, from 2007 to 2013, where he was involved in ten Ph.D. projects in the areas of power electronics, power systems, and energy storage. He has published more than 200 papers and one book *Grid Converters for Photovoltaic and Wind Power Systems* (Wiley, 2011). He holds six patents. His current research interests include modular multilevel converter, HV siliconcarbide devices, design, and the control of power converters used in wind power systems, photovoltaics, and high voltage dc transmission/flexible ac transmission systems, and energy storage systems based on Li batteries.

Dr. Teodorescu was the Chair of the IEEE Danish Joint IEEE Industrial Electronics Society, the IEEE Power Electronics Society, and the IEEE Industry Applications Society Chapter. He was an Associate Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS.

...