**Aalborg Universitet**

# **Resource Minimal Architecture Design for Software Defined Radio Front-Ends**

Awan, Mehmood-Ur-Rehman

Publication date: 2013

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Awan, M.-U.-R. (2013). Resource Minimal Architecture Design for Software Defined Radio Front-Ends.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Resource Minimal Architecture Design for Software Defined Radio Front-Ends

PhD Dissertation

Mehmood Ur Rehman Awan

Resource Minimal Architecture Design for Software Defined Radio Front-Ends

PhD Dissertation

This dissertation is a revised version of the dissertation "Resource Optimal Architecture Design for Software Defined Radio Front-Ends" submitted to Faculty of Engineering, Science and Medicine at Aalborg University, and defended successfully on March 22, 2013.

ISBN: 978-87-7152-002-6 March 2013

Copyright 2013 © Mehmood Ur Rehman Awan (except where stated otherwise) Technology Platforms Section, Department of Electronic Systems, Aalborg University Niels Jernes Vej 12 9220 Aalborg Øst

# Resource Minimal Architecture Design for Software Defined Radio Front-Ends

PhD Dissertation by: Mehmood Ur Rehman Awan

Supervised by:

**Peter Koch** Associate Professor Technology Platforms Section, Dept. of Electronic Systems, Aalborg University, Denmark

*fredric j. harris* (co-supervisor) Professor Dept. of Electrical & Computer Engineering, San Diego State University, CA, USA

# List of Publications

- Mehmood Awan, Yannick Le Moullec, Peter Koch, and fred harris, "Polyphase Filter Banks for Embedded Sample Rate Changes in Digital Radio Front-Ends", *Special Issue on advances in Digital Front-End and Software RF Processing: Part II, ZTE Communications*, Vol. 9, No. 4, pp. 3-9, Dec 2011. ISSN 1673-5188.

- Mehmood Awan, Yannick Le Moullec, Peter Koch, and fred harris, "Hardware Architecture Analysis of Polyphase Filter Banks Performing Embedded Resampling for Software Defined Radio Front-Ends", *100G and Beyond: Trends in Ultrahigh-Speed Communications (Part I), ZTE Communications*, Vol. 10, No. 1, pp. 54-62, Mar 2012. ISSN 1673-5188

- Mehmood Awan, fred harris, and Peter Koch, "Time and Power Optimizations in FPGA-Based Architectures for Polyphase Channelizers", 45<sup>th</sup> Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, California, Nov. 6-9, 2011, pp. 914-918. ISBN: 978-1-4673-0323-1

- Mehmood Awan, Peter Koch, Chris Dick, and fred harris, "FPGA Implementation Analysis of Polyphase Channelizer Performing Sample Rate Change Required for both Matched Filtering and Channel Frequency Spacing", 44<sup>th</sup> Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, California, Nov. 7-10, 2010, pp. 414-418. ISBN: 978-1-4244-9721-8

- Mehmood Awan, and Peter Koch, "Combined Matched Filter and Arbitrary Interpolator for Symbol Timing Synchronization in SDR Receivers", 13<sup>th</sup> IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, Vienna Austria, April 14-16, 2010, pp. 153-156. ISBN (print): 978-1-4244-6610-8/10

Mehmood Awan, and Peter Koch, "Polyphase Channelizer as Bandpass Filters in Multi-Standard Software Defined Radios", 2<sup>nd</sup> International Workshop on Cognitive Radio and Advanced Spectrum Management (CogART 2009), Aalborg, May 18-20, 2009, pp. 59-63. ISBN: 978-1-4244-4066-5

This thesis has been submitted to the Faculty of Engineering and Science at Aalborg University for assessment in partial fulfillment of the PhD degree. The thesis is based on the published scientific papers which are listed above. Parts of the papers are used directly or indirectly in the extended summary of the thesis. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty. The thesis is not in its present form acceptable for open publication but only in limited and closed circulation as copyright may not be ensured.

# Preface

The work was conducted from October 2008 to November 2012 under the research activities by Center for Software Defined Radio at Aalborg University.

# Acknowledgements

I would like to thank my supervisor Assoc. Prof. Peter Koch and honorary co-supervisor Prof. fredric j. harris for their inspiration, contributions, and support during the whole process of the PhD work. I also thank Assoc. Prof. Yannick Le Moullec for his valuable contributions. I also thank Prof. fredric j. harris for inviting me to San Diego State University (SDSU) for my external research stay from February 2010 to July 2010. It was a wonderful time and experience, where I learned and explored the power of the multirate signal processing especially for Software Defined Radio. A special thanks goes to Michael Bayliss for his cooperation and hospitality during my stay in San Diego, CA. I thank Chris Dick from Xilinx Inc. for his cooperation. Furthermore, I would like to thank my colleagues at Aalborg University, Alex Aaen Birklykke, Muhammad Mahtab Alam, Rasmus Abildgren, Andreas Popp, and Jesper Michael Kristensen and my colleagues at SDSU, Elettra Venosa, and Xiaofei Chen for making every workday an enjoyable time. The same goes for the rest of my colleagues in the Technology Platforms Section.

Last but not least I thank my family and friends for their encouragement, company, and support that has always given me the energy and motivation to work.

Aalborg, Denmark, November 2012

Mehmood Ur Rehman Awan

# List of Abbreviations

The following abbreviations are used throughout the thesis:

- ADC Analog-to-Digital Converter

- AGC Automatic Gain Control

- AM Amplitude Modulation

- ASIC Application Specific Integrated Circuit

- CIC Cascade Integrator Comb

- CLB Configurable Logic Block

- CMOS Complementary Metal-Oxide-Semiconductor

- CORDIC COordinate Rotation DIgital Computer

- CR Cognitive Radio

- DAC Digital-to-Analog Converter

- DCM Digital Clock Manager

- DDC Digital Down Converter

- **DDS** Direct Digital Synthesis

- DFE Digital Front-End

- DFT Discrete Fourier Transform

- DFTFB Discrete Fourier Transform Filter Bank

- DSE Design Space Exploration

- **DSP** Digital Signal Processing

- **DUC** Digital Up Converter

- FFT Fast Fourier Transform

- FIFO First-In-First-Out

- FIR Finite Impulse Response

- FM Frequency Modulation

- FPGA Field-Programmable Gate Array

- GUI Graphical User Interface

- HDTV High Definition Television

HW Hardware **IC** Integrated Circuit **IF** Intermediate Frequency IFFT Inverse Fast Fourier Transform **IIR** Infinite Impulse Response **IP** Intellectual Property ISE (Xilinx) Integrated System Environment LPA Load Process Architecture LUT Look-Up Table MAC Multiply-and-ACcumulate MPRB Modulated Perfect Reconstruction Bank **OQAM** Offset Quadrature Amplitude Modulation PC Personal Computer **PR** Perfect Reconstruction QMF Quadrature Mirror Filter **RA** Runtime Architecture SDR Software Defined Radio SNR Signal-to-Noise Ratio SRC Sample Rate Conversion SW Software TRF Tuned Radio Frequency VCO Voltage Controlled Oscillator VHDL Very-High-Speed-Integrated-Circuit (VHSIC) Hardware Description Language VLSI Very Large Scale Integration

# Contents

| Co | ntents                                                                                                                                                                                                                                                                                                                                             | IX                                           |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| A  | stract                                                                                                                                                                                                                                                                                                                                             | XI                                           |

| Da | nsk Resumé                                                                                                                                                                                                                                                                                                                                         | XIII                                         |

| 1  | Introduction         1.1       History of Radio Transceivers         1.2       Software Defined Radio         1.3       Multirate Signal Processing         1.4       Channelization                                                                                                                                                               | . 3<br>. 7                                   |

|    | <ul> <li>1.5 Synchronization</li></ul>                                                                                                                                                                                                                                                                                                             | . 15<br>. 17<br>. 20<br>. 21                 |

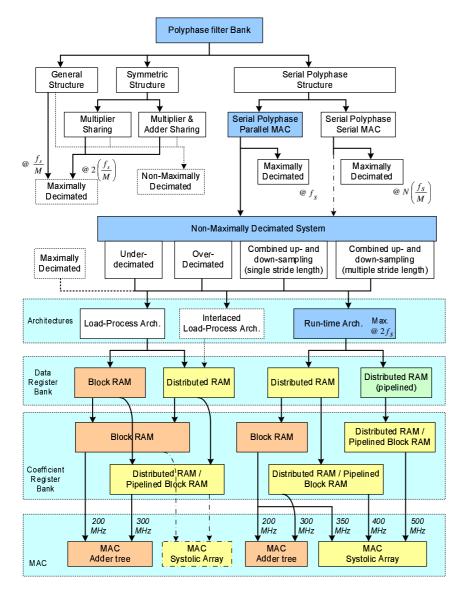

| 2  | Design Space Exploration of Polyphase Filter Banks for High PerformanceSDR Front-Ends2.1Polyphase Filter Structures2.2Comparative Analysis2.3Subfilter Architectures2.4Non-Maximally Decimated Systems2.5Optimizations for Area Resources2.6Architecture Exploration2.7Optimization for Enhanced Clock Speed Performance2.8Explored Solution Space | . 25<br>. 26<br>. 27<br>. 28<br>. 31<br>. 34 |

| 3  | Summary of Contributions                                                                                                                                                                                                                                                                                                                           | 45                                           |

| 4  | Conclusion                                                                                                                                                                                                                                                                                                                                         | 51                                           |

| 5  | List of Publications                                                                                                                                                                                                                                                                                                                               | 59                                           |

| Re | ferences                                                                                                                                                                                                                                                                                                                                           | 61                                           |

|    |                                                                                                                                                                                                                                                                                                                                                    | IX                                           |

| Contributions                                                                                                                                                            | 69  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Paper A: Polyphase Filter Banks for Embedded Sample Rate Changes in Dig-<br>ital Radio Front-Ends                                                                        |     |

| Paper B: Hardware Architecture Analysis of Polyphase Filter Banks Perform-<br>ing Embedded Resampling for Software Defined Radio Front-Ends                              | 85  |

| Paper C: Time and Power Optimizations in FPGA-Based Architectures for<br>Polyphase Channelizers                                                                          | 105 |

| Paper D: FPGA Implementation Analysis of Polyphase Channelizer Perform-<br>ing Sample Rate Change Required for both Matched Filtering and Chan-<br>nel Frequency Spacing | 117 |

| Paper E: Combined Matched Filter and Arbitrary Interpolator for Symbol<br>Timing Synchronization in SDR Receivers                                                        | 129 |

| Paper F: Polyphase Channelizer as Bandpass Filters in Multi-Standard Soft-<br>ware Defined Radios                                                                        | 139 |

# Abstract

The high and constantly increasing demand to develop radio transceivers with enhanced functionalities, inter-standard portability, higher throughputs, compact physical size, low cost, and longer battery lifetime impose challenges on the radio designer. A Software Defined Radio is capable of meeting these challenges provided (i) enhanced signal processing algorithms with reduced complexities, (ii) high performance HW/SW platforms, and (iii) the optimized architectural design that finally maps the algorithms to the processing platform.

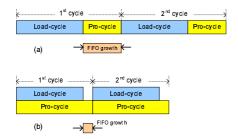

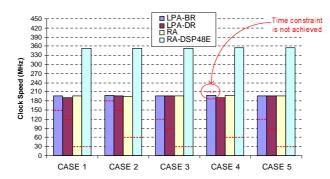

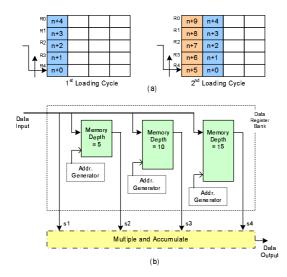

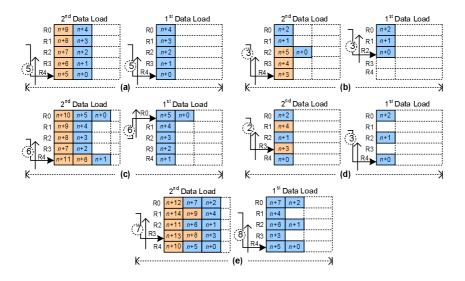

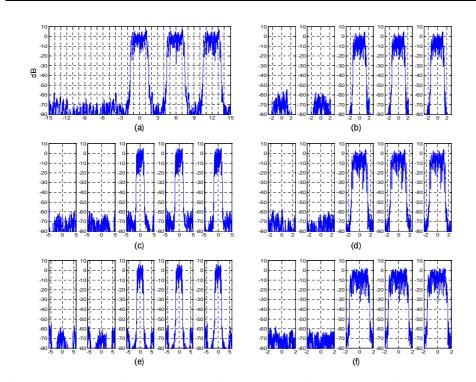

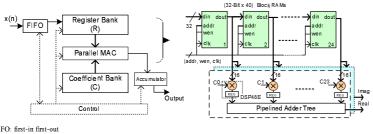

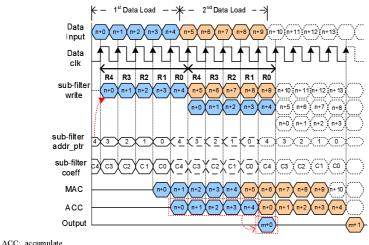

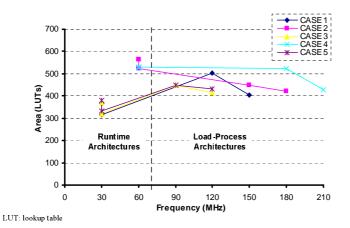

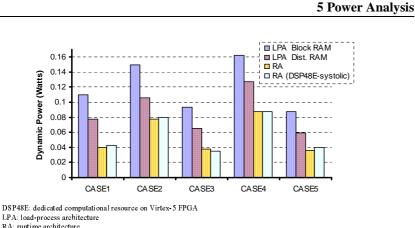

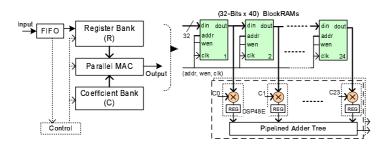

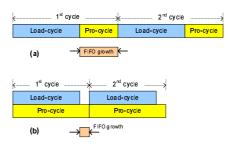

This dissertation focuses on a resource minimal architecture design for Software Defined Radio (SDR) front-ends targeting a reconfigurable architecture platform using a Field Programmable Gate Array (FPGA). Front-end design techniques ranging from legacy radios to the state-of-the-art radios are presented and analyzed. The results showed that multirate signal processing based techniques provide high performance solutions at a reduced resource complexity, thus making them highly suitable for the SDR front-ends. The outcome is a set of structural guidelines for the designer which can be used to obtain an Area, Time, operating clock Speed, and Power minimized architectural design for SDR front-ends using polyphase filter bank solutions - a multirate signal processing technique. The design space of reconfigurable architectures is explored to suggest different mapping solutions for polyphase filter bank which are analyzed based on their resource usage and corresponding performances. Non-maximally decimated operating scenarios are identified and scheduling schemes are proposed to meet their output time constraints. The scheduling schemes applied are: Load-Process scheduler, Interlaced Load-Process scheduler, and Runtime scheduler. The proposed architectures are based on these schedulers, which in the light of exploration of the reconfigurable target space (Xilinx Virtex-5 FPGA) are presented to compare resource and performance metrics.

The dissertation is composed of four parts: First, the related design challenges and stateof-the-art in SDR front-ends are discussed. The focus is on design solutions with the least computational requirements while operating at the lowest possible clock rate, and having the ability to embed several functions together. Second, a design space exploration of polyphase filter banks is presented and a set of structural design guidelines are suggested to the designer enabling Area, Time, operating clock Speed, and Power optimized solutions for SDR front-end designs. Third, a summary of the contributions is provided which relates to the published papers. Finally, a conclusion and outlook are given.

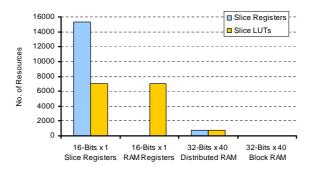

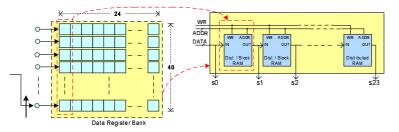

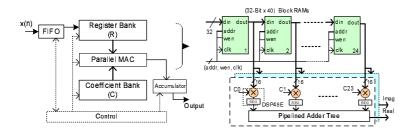

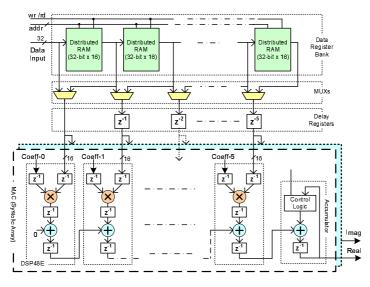

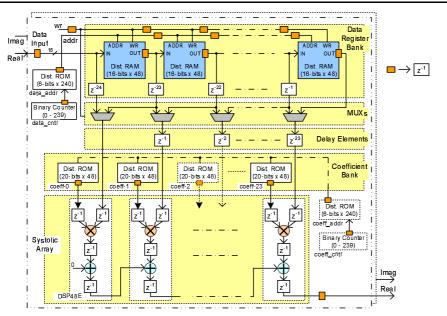

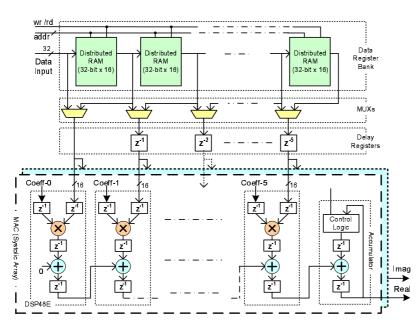

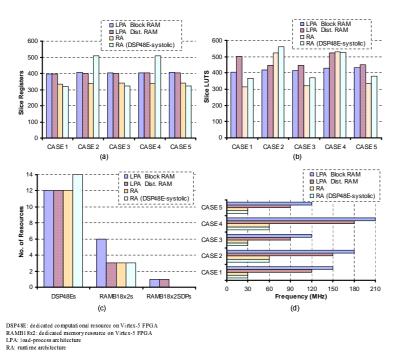

The main body of the dissertation is composed of six peer-reviewed papers which present the scientific contributions. The results show that the polyphase filter (bank) can embed multiple functions in its operation in a cost effective manner, such as combined arbitrary resampling, match filtering and symbol timing recovery, and rational resampling apart from a maximally decimated scenario. Furthermore, the suggested Runtime Architecture (RA) based on a Runtime scheduling scheme, with (i) distributed RAM organized as a pipelined register bank, (ii) distributed RAM or pipelined block RAM based coefficient bank, and (iii) systolic array of DSP48E (dedicated computational resources on Xilinx

# CONTENTS

FPGA) slices based Multiply-Accumulate (MAC) is a preferred choice to enhanced performance and reduce latency for SDR digital front-ends.

The lessons learned during the exploration of the solution space for the polyphase filter banks provide a sound basis for the system designer to choose the solution(s) which meet(s) the normally tight resource and performance constraints. Besides, the formulated design guidelines which constitute our most important scientific contribution, can help the designer at any point in the design process, thus potentially leading to a reduced overall cost and time-to-market overhead.

# Dansk Resumé

De til stadighed voksende krav, der stilles ifm. udvikling af radio-sendere og -modtagere med avancerede funktioner som eksempelvis understøttelse af flere forskellige kommunikationsstandard, høje datatransmissions-rater, kompakt fysisk størrelse, lav pris og lang batterilevetid, medfører markante faglige udfordringer for den moderne radio-ingeniør. Med udbredelsen af den såkaldte "software defined radio" (SDR), er der imidlertid tilvejebragt et koncept, som er i stand til at imødekomme mange af nutidens krav og udfordringer, idet netop dette koncept gør brug af (i) højtydende signalbehandlings-algoritmer med lav beregningsmæssig kompleksitet, (ii) avancerede HW/SW platforme, og ligeledes (iii) understøttes muligheden for at designe HW/SW-arkitekturer, som er skræddersyede til de nødvendige signalbehandlings-algoritmer.

Denne phd-afhandling fokuserer på design af resource-minimale FPGA-baserede arkitekturer til SDR modtageres front-ends, dvs. de første signalbehandlingsalgoritmer umiddelbart efter analog-til-digital konverteringen. Vi præsenterer og analyserer design-teknikker for såvel traditionelle som moderne radio front-ends, og vi viser at signalbehandlingsalgoritmer baseret på det såkaldte "multi-rate" princip med fordel kan benyttes til at frembringe højtydende SDR front-ends med reduceret ressource-forbrug. Vi tilvejebringer retningslinier for struktureret design med henblik på at opnå bedst mulig performance mht. fysisk areal, eksekveringstid, og effektforbrug for SDR front-end arkitekturer. Hertil udnytter vi såkaldte poly-fase filter-banker. Med udgangspunkt i omkonfigurerbare HW-arkitekturer afsøger vi det såkaldte design-løsningsrum med henblik på at fremsætte forslag til design-løsninger for poly-fase filter-banker. Løsningsforslagene evalueres ift. det aktuelle ressource-forbrug og den givne performance. Vi identificerer scenarier baseret på "non-maximal decimation" og vi foreslår i relation hertil eksekverings-planer, der imødekommer algoritmernes tidsmæssige krav. Planerne omfatter Load-Process, Interlaced Load-Process og Runtime afvikling. Med udgangspunkt heri foreslår vi tilhørende HW-arkitekturer, hvis ressource-forbrug og performance analyseres.

Afhandlingen består af fire hovedelementer; For det første forkuserer vi på de udfordringer der er ved design af moderne SDR front-ends. Vores fokus er rettet mod designløsninger med mindst mulig beregnings-kompleksitet, som kan udføres med den lavest mulige clock-frekvens, og som samtidig understøtter muligheden for at udføre adskillige funktioner i den samme operation. For det andet udforsker vi løsningsrummet for poly-fase filterbanker med henblik på at definere retningslinier for ressource-optimal design af SDR front-ends. For det tredje gennemgår vi de resultater der er tilvejebragt og efterfølgende afrapporteret i form af videnskabelige artikler. Endelig konkluderer vi vores arbejde og funderer over mulige fremtidige aktiviteter. De fundamentale resultater, som er publiceret i seks bedømte artikler, viser, at poly-fase filter-banker kan bringes til at udføre flere samtidige funktioner, som eksempelvis "arbitrary resampling", "matched filtering", "symbol timing recovery", og "rational resampling" (med undtagelse af maksimal decimering scenariet). Desuden viser vores resultater, at den foretrukne løsning (dvs. bedst performance og korteste delay) er vores Runtime Architecture (RA), som

# CONTENTS

baseres på Runtime eksekverings-planlægning. Denne løsning kan realiseres ved brug af forskellige metoder til lagring af og multiplikation med filterkoefficienterne, eksempelvis (i) distribueret RAM organiseret som en pipelined register-bank, (ii) blok-RAM, eller (iii) et systolsk array bestående af DSP48E beregningskerner (Xilinx FPGA).

De opnåede resultater ifm. afsøgning af løsningsrummet for poly-fase filter-banken har tilvejebragt et solidt og nyskabende videngrundlag, som system-designeren kan benytte ifm. valg og design af SDR front-end løsninger, der imødekommer strenge ressourceog performancemæssige krav. Den frembragte viden er omsat til strukturerede retningslinier for SDR front-end design, hvilke således udgør det mest fundamentale resultat i vores arbejde. Dette resultat har medført, at der nu kan udvikles løsninger, som er mere konkurrencedygtige mht. pris og udviklingstid end tidligere tiders løsninger.

Telecommunication has penetrated into our daily life so much that it is difficult to imagine a world without it. From a fundamental point of view, communication is the transmission of information from one point to another. The radio frequency devices transmitting and receiving the information are called transceivers. The constantly increasing demands upon these radio devices are more functionality, higher throughput, compact physical size, and longer battery lifetime, and of course low cost. This requires not only advancements in signal processing algorithms but also advances in processing platforms and architectural implementation. In this chapter we will review the fundamental development of radio technologies, discuss the state-of-the-art, and conclude by formulating a hypothesis which will serve as the overall inspiration for our work.

## 1.1 History of Radio Transceivers

The history of the radio started with the discovery of electromagnetic waves by Maxwell in 1887. The successive inventions by Hertz, Marconi, and many others concerning propagation of waves and wireless telegraphy gave birth to various wireless technologies [1]. Marconi revealed the first practical radio system (apparently copying an earlier invention of Nicola Tesla) in 1895 which led to transatlantic radio communication in 1901 [2]. The invention of the crystal detector, as well as Fleming's valve and De Forest's audion improved the sensitivity of the receiver. Edwin Armstrong invented the regenerative sets based radio receivers in 1906, which made long distance reception a reality. The development of valves (tubes) as an amplifier and regenerative detector (using positive feedback) tremendously improved radio performance in terms of gain and selectivity. The First World War further drove the development of radio receiver technology. The development of tuned radio frequency receiver (TRF) technology in 1920s, basically a chain of individually tuned amplifiers, represented a major improvement in radio performance. Further improvements include direct conversion and autodyne receivers. Direct conversion used a local oscillator based mixer, producing an audible signal that is further amplified. This requires separate valves for oscillator and mixer. The autodyne receiver used the same valve for both mixer and oscillator making it difficult to optimize both functions [3]. The need for a higher level of selectivity and sensitivity performances led to the development of the superheterodyne receiver. This is a receiver with an amplifier at a fixed intermediate frequency, and a filter. The incoming signal is mixed with a variable frequency oscillator (local oscillator) to obtain the down-conversion at a fixed lower frequency called an

Intermediate frequency (IF). The signal is further passed through a lowpass filter to reject the unwanted (mixing) components, and then finally amplified [2]. This processing improved the selectivity of the receiver, enhanced the gain for valves being used at the lower frequencies (after the frequency conversion), and reduced the circuit oscillation problems [3].

In the late 1940s the transistor (using semiconductor technology) was invented which later replaced the vacuum tubes in radio receivers during the 1950s and 1960s [3] [4] [5]. These transistor devices turn out to be miniature, reliable, long lasting, and consume less power and generate less heat dissipation as compared to their counterpart, as vacuum tubes are fragile, bulky, unreliable, power hungry, and have high heat dissipation. Transistor radios became attractive for their inherent features. The realization of complex electronic circuits using a large number of transistors and their required interconnects led to further developments in semiconductor technology leading to the Integrated Circuit (IC). This enabled radio receiver technology to utilize high performance circuits that can be built at low cost, and in a significantly reduced volume. The technology developments resulted in new techniques, for example, a frequency synthesizer realizing a phase lock loop in the digital domain [4]. This synthesizer generates a precise and stable local oscillator signal for the receiver. With the further advancements in receiver technology, many of the functions performed in the analog domain have been replaced by digital methods using Digital Signal Processing (DSP) technology. The benefit is that the DSP techniques are not affected by temperature and other physical variables, electronic noise, and aging.

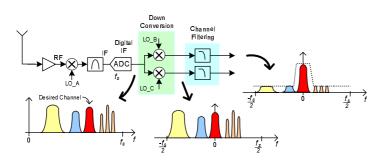

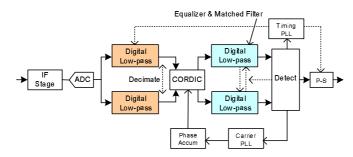

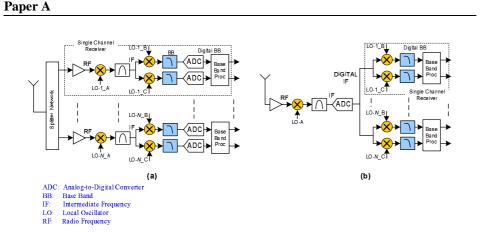

DSP based radio transceivers have passed through several generations of architectures. The traditional heterodyne architecture, considered the first generation of digital radio architecture, is shown in Fig. 1.1(a). It consists of a dual-stage down-converter, and only the baseband processing is done in the digital domain [6]. In the first stage, the RF signal is down-converted to a bandlimited Intermediate Frequency (IF). In the second stage, the IF filter output is again down-converted to baseband by a matched-quadrature mixer, and matched baseband filters that perform final bandwidth control. Next, the signal passes into the digital domain where the output of the analog-to-digital converter (ADC) is processed by digital signal processing (DSP) engines. These engines perform the required baseband processing, that is, synchronization, equalization, demodulation, detection, and decoding. The problem with this type of architecture is that gain and phase are imbalanced for the in-phase and quadrature (I/Q) components. This results in cross-talk between the narrowband channels due to aging (time, temperature) of the analog components of the quadrature down-converter. Each imbalance-related spectral image must be lower than the desired spectral term, and this is difficult to sustain over time and at varying temperature.

The need for extreme I/Q balance gave rise to the next generation of digital radios where the second stage (IF) down-conversion and, consequently, the channelization process is digital, as shown in Fig. 1.1(b). Digital conversion at IF provides greater control over the imbalance by manipulating the number of bits involved in the arithmetic operation. The precision of the coefficients used in the filtering process sets an upper limit for spectral artifacts at -5 dB/bit. This means that 12-bit arithmetic can achieve image levels below -60 dB [6]. The DSP based complex down-conversion, however, has two advantages:

#### 1.2 Software Defined Radio

Figure 1.1: (a) First generation of digital radio receiver architecture, and (b) Second generation of digital radio receiver architecture.

(i) the spectral images are controlled so that they are below the quantization noise floor of the ADC involved in the conversion process, and (ii) the digital filters before and after the mixers are designed to have linear phase characteristics [6].

With more functions performed in DSP, the Personal Computer (PC) radio evolved. This has great advantage of being field upgradable both for existing and new functionalities. A Graphical User Interface (GUI) provides unlimited flexibility to the radio and new features can be added simply by a software upgrade instead of adding more hardware components. The next level in radio / software integration is Software Defined Radios (SDR).

# 1.2 Software Defined Radio

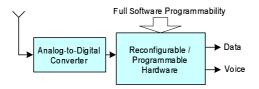

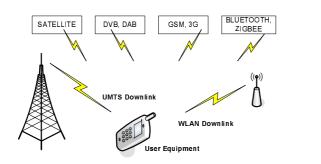

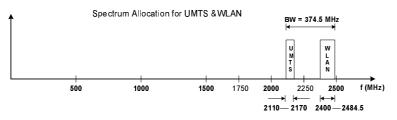

The concept of the SDR originates from the work of Mitola [7] in 1995, where a software adaptable radio architecture was proposed that enable the radio to automatically adjust to several different communication standards. This means that SDR is a radio communication system which can tune to any frequency band and receive any modulation across a large frequency spectrum by means of programmable hardware which is controlled by software. An Ideal Software Radio (ISR) is shown in Fig. 1.2. An SDR demodulating a simple AM broadcast may also be able to decode an HDTV broadcast simply by changing the software for its programmable hardware. The SDR not only provides high flexibility to adapt the radio front-end for any desired modulation, channel bandwidth, or carrier frequency, but also provides a cost effective solution by exploiting digital technology [8].

Figure 1.2: An Ideal Software Defined Radio.

In the early years, SDR was mainly attractive for military applications where there is a need for a single radio which can communicate with the many types of military radios that

use different RF bands and different modulation schemes [9]. The emerging standards and the high penetration of mobile communications systems strongly demand software radio based mobile terminals and base stations for mobile communications systems [10] [11]. There are lots of system level issues in the wireless communication industry which embrace the essence and motivation for SDRs, such as;

- The rapid growth of commercial wireless network standards (2G, 2.5G, 3G, and 4G) has caused incompatibility issues for subscribers, wireless network operators, and equipment vendors, due to differences in their link-layer protocol standards.

- Subscribers are obliged to buy new handsets to utilize new services.

- Wireless network operators have to migrate their network from one generation to the next, while supporting both new and legacy handsets, and further they face deployment issues while rolling-out new services.

- Handset vendors face challenges in manufacturing viable multi-mode handsets.

- Equipment vendors face challenges in developing newer generation equipment due to short time-to-market requirements.

- The use of different air interface and link-layer protocols across various geographies has restrained the deployment of global roaming facilities.

SDR technology promises to solve (at least to a certain extent) these problems by implementing the radio functionality as software modules running on a generic hardware platform. Further, multiple software modules implementing different standards can be present in the radio system. The software modules that implement new services/features can be downloaded over-the-air onto the handsets. This kind of flexibility offered by SDR systems helps alleviate problems due to differing standards and issues related to deployment of new services/features. There are a lot of advantages of the full downloadable type of software radio because the system can be changed on demand by changing the software. There are many advantages not only for operators and service providers, but also for government and commercial customers such as global roaming services, bug fixes without the need to recall the product, and new services can be added without changing the terminals [12]. The most promising application of SDR is the application of cognitive radio (CR) [13]. As the radio spectrum becomes more and more sparse, making it a difficult task to allocate new spectrum for new services. A CR is aware of its environment, internal state, its location, and can make a decision about its operating behaviour based on this information.

## Challenges

The idea behind SDR is to push as much radio functionality as possible into the digital domain via programmable digital hardware in order to achieve highly configurable designs [7]. This can be achieved by bringing the analog-to-digital conversion process (i.e., Analog-to-Digital Converters (ADCs)) as close to the antenna as possible. An ISR, as shown in Fig. 1.2, samples the signal at RF, just after the antenna and is termed full-band digitization. This straightforward approach is highly dependent on the ADC technology

#### **1.2 Software Defined Radio**

that could provide sufficient bandwidth and dynamic range performance for a SDR application together with low power consumption. The state-of-the-art ADC technology, however, bring the concept of Giga-Hertz sampling to a reality [14, 15].

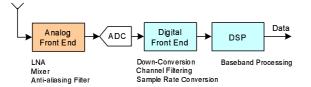

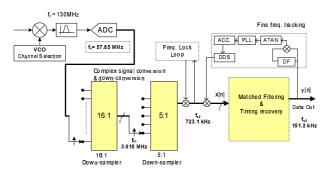

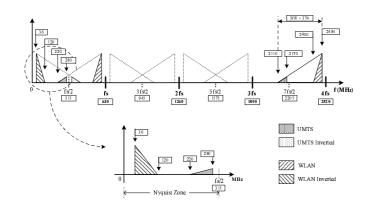

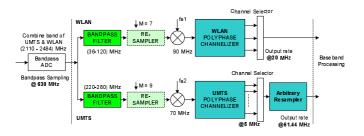

In a realizable version of the software radio, shown in Fig. 1.3, the signal bandwidth must be reduced which is termed partial-band digitization. This can be realized with conventional receiver techniques, i.e. a heterodyne receiver as described in the second generation of digital radio. The partial-band digitization demands an analog front-end. Although it requires less analog functionality as compared to the conventional analog receivers, the requirements are heavily increased due to the presence of higher bandwidth and the dynamic range of the multi-channel signals for an SDR receiver. After digitization through the ADC, the signal of interest must be extracted from the digitized multi-channel signal and shifted to the baseband before the signal processing can be performed. Furthermore, the sample rate applied to the selected signal must be in accordance with the air interface, which therefore requires some digital signal processing before the baseband processing. Traditionally, this digital signal processing is done through analog techniques in the analog front-end. The shifting of the ADC towards the antenna realized this functionality in the digital domain. This is termed a Digital Front-End (DFE) which includes channelization (i.e., digital down conversion and channel filtering) and sample rate conversion [10].

Figure 1.3: A realized version of Software Defined Radio.

The large bandwidth and high dynamic range of the signals to be processed by SDR eventually result in high sample rate and large word lengths. The high sample rates not only increase power consumption but also make the DFE infeasible for implementation on programmable digital signal processor devices. Apart from the other critical and enabling components of SDR (i.e., wideband analog front-end and the ADC) the requirement of reconfigurability and/or programmability for SDR in the presence of very high sample rates turns the DFE into one of the most power- and time-critical functionalities of an SDR [16].

#### Architectures

The hardware platform is the most prominent and challenging component of SDR as it has to provide massive computational power, flexibility, and at the same time meet strict power- and size limitations [17] [18]. Therefore, the selection of hardware architectures for SDR based applications is not a trivial task. As SDR signal processing algorithms are becoming more and more complex, the computational requirements on the target HW/SW-platforms are becoming equally high, and consequently software solutions make it possible to establish a smooth transition from dedicated, single-purpose

hardware (ASICs) to highly versatile general-purpose hardware systems such as Field Programmable Gate Array (FPGA).

In general, algorithmic complexity (sometimes referred to as Shannon's law) is increasing at a rate faster than the processing capabilities of the hardware platforms (known as Moore's law), which introduces a technology gap. Bridging this gap may be done by developing new algorithms with reduced numerical complexity as well as devising alternative hardware architectures with higher performance. The advances in silicon technology are progressing according to Moore's law which however, cannot keep pace with the growing computational complexity. But at the same time Moore's law has also led to the fact that fabrication technologies now enable more transistors to be implemented on a single die than typical state-of-the-art design tools can easily handle. This situation leads to a so-called design-gap [19] [20]. According to the National Technology roadmap for semiconductors, the number of transistors that could be fabricated on a die was increasing at a rate of about 60% a year, whereas the number of transistors that circuit designers could design into new independent circuits was growing only by 20% a year [20]. This trend is observed in the DSP processor community where even the high-end DSP processors do not push the transistor densities as described by Moore's law [21].

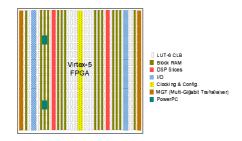

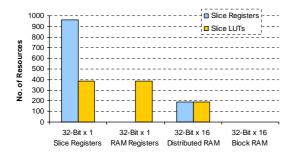

To bring value to the state-of-the-art semiconductor products, the transistor budget must be used in a different way. That brings us to the FPGA technology which has improved tremendously over the past five to ten years. An FPGA is the ultimate commercial device for architectural customization, providing a huge solution space to designers for constructing their signal processing systems [21]. FPGAs are getting faster and their internal building blocks are becoming more efficient in terms of clock speed and reduced power consumption. The inherent parallel processing capability of FPGAs has made them the core-processing engine in SDR applications. These devices spend their transistor budget in a fundamentally different way than ISA (Instruction Set Architecture) machines and have enriched structure with CLBs (Configurable Logic Block), high speed I/Os, a variety of memory architectures, embedded hardware multipliers, Digital Clock Managers (DCMs), soft-core processors, and multi-gigabit transceivers (MGT). The most frequently used FPGA vendors are Xilinx [22] and Altera [23]. The internal architecture of a Xilinx Virtex-5 FPGA is shown in Fig.1.4.

Figure 1.4: Architecture of Xilinx Virtex-5 FPGA.

FPGAs normally consist of two layers, where the first layer contains arrays of logic blocks, dedicated resources and routing between them. The actual configuration of the

#### **1.3 Multirate Signal Processing**

FPGA is determined by a second layer of memory, determining the functionality of the logic and routing in the first layer.

The vast number of configurable parameters and customization in FPGA systems poses a great challenge to the designer as they offer a huge number of system, architectural, and logic design choices [24]. This creates a huge design space of possible architectures and mappings which increases the time and effort needed for the final mapping (implementation) of the system [25] [26] [27]. Finding the optimal design is often a matter of trade-offs between costs and performance, thus opening a new era of designing highly efficient FPGA based architectures requires design space exploration tools to help the designer to prune the design space.

The mapping process includes the design challenges of allocation, binding, and scheduling where allocation decides the number of resources (processing units) for performing a task, binding assigns the individual tasks to the processing units, and scheduling defines the relative task operations in time. Design space exploration is the evaluation of possible mapping solutions in the presence of a cost function, as expressed by Eq. 1.1, which may specify some of the parameters (e.g. execution time, area, power consumption, numerical precision etc.) as constrained by the requirements. A cost function can also include other parameters such as price and development time, degree of reconfigurability, maintainability, etc. It is generally accepted that finding an optimal design solution for a reconfigurable system is an NP complete [28] combinatorial optimization problem. We believe that a methodology/ tool can aid the designer during the design space exploration process in order to speed up the product development process and thereby meet the time-to-market requirements. There exist many design methodologies, but there may still be room for further improvements. To our knowledge, very little has been done towards experimenting with the implementation of advanced DSP algorithms for SDR front-ends on highly complex FPGA platforms. Therefore, in order to explore the possibilities and limitations of such designs, we have decided to investigate the advantages and disadvantages of design trade-off's as compared to selected metrics in the cost function. The cost, C, of an implementation typically is expressed by a cost function,

$$C = f\{A, T, P, N, ..\}$$

(1.1)

where A is area or resource consumption, T is execution time, P is power consumption, and N is the numerical precision. Each parameter can be assigned a weighting factor that defines its significance, giving a cost function such as  $C = f \{\alpha A, \beta T, \gamma P, ..\}$ . Thus, a 0.1 factor would mean that the corresponding parameter is 5 times less important than a parameter with a factor of 0.5. This is a somewhat abstract definition in the sense that the individual parameters can not be really compared. These factors (or metrics) lead to the design constraints which need to be optimized, either individually or simultaneously. In this work, we will not consider the actual values of the weight factors.

# **1.3 Multirate Signal Processing**

We have now explained the requirement for high computationally efficient and flexible architectures for SDR. But at the same time the design of high-performance SDR front-end

requires advancements in the signal processing algorithms with reduced computational and/or resource complexities. Multirate signal processing specifies alternative ways of performing DSP tasks which are normally not available in traditional DSP designs. It provides not only a reduction in the cost, but also enhances the performance of the implementation.

Multirate signal processing exploits sample rate changes at various stages of a system (hence the name multirate), in the form of decimation and interpolation of discrete time sequences [29]. From a traditional DSP perspective, the sample rate is selected to satisfy the Nyquist criterion. In multirate signal processing, selection and modification of the sample rate are the primary considerations and options in the signal processing chain. This ability to change the sample rate within the processing stream introduces a remarkable list of processing tricks and performance enhancements. It enables the processing task to be performed at the lowest rate matching the signal bandwidth, which is the Nyquist rate of the signal component of interest [30].

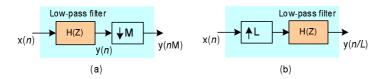

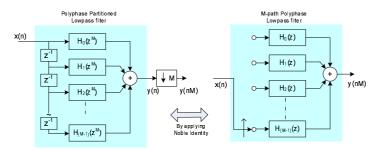

In contrast to a common processing task i.e., to reduce the bandwidth of a signal by filtering and then reducing the sample rate to match the reduced bandwidth, a multirate signal processing trick known as the Noble Identity interchanges the order of filtering and sample rate change so that the filter processing is done at the reduced output sample rate rather than at the high input sample rate. The Noble Identity operation is illustrated in Fig. 1.5. The reduction in the sample rate *prior* to bandwidth reduction causes aliasing of the input spectrum. Multirate signal processing permits, and in fact, supports this intentional aliasing, which can be unwrapped by subsequent processing. Most of the tricks and enhancements associated with multirate signal processing are related to spectral aliasing due to the sample rate change. The change in sample rate is also used to intentionally alias a signal at one center frequency to another center frequency. This option includes aliasing a signal from an intermediate center frequency to baseband by reducing the sample rate, as well as aliasing a signal from baseband to an intermediate center frequency by increasing the sample rate [30].

Figure 1.5: Noble Identity: A filter processing every  $M^{th}$  input sample followed by an M-to-1 down sampler is equivalent to an input M-to-1 down-sampler followed by a filter processing every input sample.

Polyphase decomposition, which originated from the work by Bellanger [31], plays a fundamental role in many multirate DSP applications. These include efficient real-time implementation of decimation and interpolation filters, fractional sampling rate changing devices, uniform DFT filter banks, and perfect reconstruction analysis/synthesis systems. A multirate polyphase filter can perform the tasks of a multichannel receiver which significantly reduces the amount of system resources required to perform multichannel processing and, consequently, reduces costs [6] [30]. Polyphase filter banks can be used in

#### 1.4 Channelization

spectral sensing for cognitive radios [32]. Furthermore, they form a foundation of timing recovery schemes [33]. This allows large systems to be implemented efficiently requiring less area resources and cost, as explained in [34] where a polyphase filter bank based design replaced a huge number of multi-channel analog modulators. The 384 discrete FM modulators were implemented on a single Xilinx Virtex-4 FPGA.

In the next sections, we will explain the DFE building blocks: channelization, sample rate conversion, and synchronization; especially in the light of multirate signal processing and discuss the state-of-the-art.

## **1.4 Channelization**

Channelization is the process of extracting one or more user channels from a wideband signal down to the baseband (at the required output sample rate) for further processing. Traditionally, it is done with a digital down-converter followed by a lowpass (channel) filter and optional sample rate conversion. The channels to be extracted may have equal or unequal bandwidths and may be uniform or non-uniform and continuously or non-continuously distributed over the input frequency band. As the number of downconverted channels is increased, the complexity of the system increases as each channel will require its own separate down-converter. Furthermore, at a high sample rate, standard approaches for channelization are inappropriate for implementation as the underlying technology platforms (e.g. FPGAs) can not handle the required processing loads.

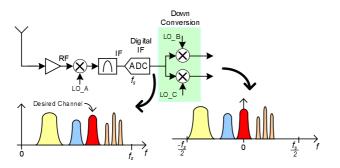

### **Down-conversion**

Down-conversion is the process of shifting the channel of interest centred at IF to the baseband. It is realized by multiplying the IF signal with a rotating complex phasor having a frequency identical to the IF centred frequency. The digital down-conversion process is illustrated in Fig.1.6.

Figure 1.6: Down conversion process where the channel of interest is shifted to baseband.

The complex phasor can be generated in different ways. A straightforward way is to precalculate the corresponding sine and cosine values and store them in a memory. Direct Digital Synthesis (DDS) is a method to generate waveforms directly in the digital domain. It is composed of a phase accumulator and a phase-to-amplitude converter [35]. A

conventional DDS is based on lookup tables (LUTs) where the amplitude values of sine or cosine waves are stored and are addressed by the phase accumulator. The COordinate Rotation DIgital Computer (CORDIC) algorithm [36] can behave as a quadrature phase-to-amplitude converter that directly generates sine and cosine waveforms [37] [38]. The main advantage of using CORDIC-based DDS in comparison with LUT-based methods is that it can achieve both high phase resolution and high precision with lower hardware cost [39]. A difference between the two methods is that the phase accumulator generates an integer value that addresses a LUT in the LUT-based method, while it generates an angle in the CORDIC-based DDS [40]. Among others, [41] and [42] presented several variants of DDS using CORDIC for very high spurious free dynamic range performances. An alternative to complex multiplication is the CORDIC algorithm operating as a vector rotator [43] which not only provides the complex samples of the rotating phasor, but also performs the multiplication at the same time.

The methods described above are used to generate the required complex phasors to be applied in multiplication for the down-conversion. The corresponding multiplication process and the preceding filtering operation are carried out at the input sample rate. The digital down-converter can be simplified considerably if the centre frequency of the channel of interest is centered at a quarter of the sample rate, thus the required complex phasors for multiplication reduces to a sequence of -1, 0, and 1. This will not only eliminate the DDS but also avoids the use of real number multipliers. Schreier and Snelgrove [44] presented a similar approach for down-conversion of signals centered at 1/8 of the sample rate.

The down conversion techniques mentioned above are replicas of analog legacy solutions. Multirate signal processing specifies alternative ways of performing DSP tasks where a 4-path polyphase filter performs the task of the down conversion from quarter sample rate while simultaneously performing baseband filtering and down sampling by a factor of 4 [30].

## **Channel Filtering**

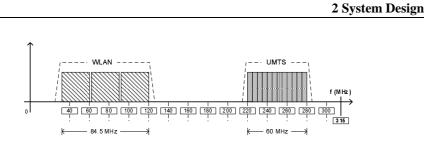

Channel filtering is required to extract the frequency divided channels from a wideband signal, as shown in Fig. 1.7. The channel filter has to attenuate the adjacent channel interferers according to the requirements of the particular air interface.

SDRs require filters of different bandwidths or a tunable filter to process the many different bandwidth signals. A filter can be implemented on reconfigurable hardware, e.g., FPGA that enables a complete reconfiguration for different air interfaces, or as a common filter that is parameterizable for all the required channel filtering. A reconfigurable filter is an easy solution, obtainable simply by reconfiguring the FPGA with another filter functionality. A parameterizable filter needs sophisticated solutions and the conventional FIR filter designs are not well suited. This is because the filter's length, i.e., number of taps varies inversely with the fractional bandwidth  $f_{BW}/f_s$ , and thus the required computational resources (such as data registers, multipliers, and adders) is different for filters with different lengths. Implementation considerations favor filters that are implemented with a fixed number of multipliers rather than with a varying number of multipliers. The

**1.4 Channelization**

Figure 1.7: Channel filtering extracts the desired channel (channel at baseband) from the wideband signal while attenuating the adjacent channels.

application of multirate filters can provide a parametric filter solution by changing the rate factors [45]. Harris [46] presented a variable bandwidth FIR filter architecture with fixed computational resources. His solution used arbitrary interpolators at the input and output of a fixed bandwidth filter, and by changing the input and output rate by the arbitrary interpolator, the required bandwidth is achieved. The variable bandwidth filters can also be realized by frequency masking filters, tunable IIR filters, low-pass to low-pass transformation tunable FIR filters, and a number of other solutions. Many of these options have a constant computational complexity but none preserves linear phase [46]. Harris [47] also presented a selectable bandwidth filter by using a pair of M-path analysis and synthesis filters. The bandwidth is changed by masking, enabling or disabling, the connections between the analysis and the synthesis filter.

#### **Sample Rate Conversion**

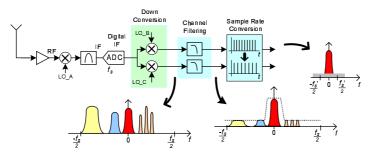

In digital receivers, it is often required to have Sample Rate Conversion (SRC) either to interconnect different processing blocks or to deliver the user-defined data rate. A receiver architecture with sample rate conversion is shown in Fig. 1.8. Sample rate conversion is not limited to digital radio, it is widely used in digital audio signal processing and in digital control [48].

Figure 1.8: Receiver architecture with a sample rate conversion block to achieve the required output sample rate.

One of the very important and cost effective applications of SRC is an interpolation process in a modulator. It raises the input sample rate to allow the translation of the input spectrum to an intermediate frequency (IF), and then outputs the digital IF via a single DAC as compared to standard baseband process which requires matched DACs, matched lowpass filters, matched balanced mixers, and a quadrature oscillator to form the first IF band [30]. The necessity for SRC in communication receivers arises with the need to implement different air interfaces in a software defined radio. This is because of the fact that the baseband processing for any associated air interface is usually carried out at the target sample rate and not at an arbitrary sample rate. The target sample rate can, in principle, be realized by clocking the ADC at the specific rate of the actual air interface which requires a high quality tunable oscillator as a clock for the ADC. To avoid complex analog components, a tunable sample rate of the ADC is not the best choice instead one can use a SRC in the digital domain [10].

Sample rate conversion can be conducted as: (i) integer based up- and down-sampler, (ii) rational P/Q re-sampler, or (iii) more sophisticated arbitrary resampler. Traditionally, up-sampling is achieved by inserting zero-valued samples followed by an anti-imaging lowpass FIR filter, and down-sampling is achieved by discarding the appropriate samples preceded by a band-limited anti-aliasing FIR filter [49]. These up- and down-samplers are shown in Fig. 1.9a and Fig. 1.9b, where the input signal is down-sampled by a factor M and up-sampled by a factor L, respectively.

Figure 1.9: (a) Down-sampler by a factor M and (b) up-sampler by a factor L.

It is computationally inefficient to discard the computed samples in the case of a downsampler, and to process the zero samples in the case of an up-sampler [30]. Multirate signal processing approaches [30], i.e., a polyphase filter based up- and down-sampler (employing the Noble Identity) or a polyphase filter based arbitrary resampler are efficient and cost effective solutions for the SRC. Furthermore, narrow band FIR filters using conventional DSP pose a serious problem because such filters need to have a very high order to meet their tight frequency response specifications. The use of multirate techniques leads to very efficient implementation by allowing filtering to be performed at a much lower rate, which greatly reduces the filter order [50]. The performance of a multirate system depends critically on the type and quality of the filter used. Either FIR or IIR filters can be used for decimation or interpolation, but FIR is the most popular because of its desirable attributes such as linear phase response and low sensitivity to finite word length, as well as being simple to implement [50].

A polyphase filter based arbitrary resampler needs pre-computed weights of the polyphase filter stages. On the other hand, a Farrow filter, which is a multirate filter structure, can provide a continuously adjustable resample ratio. It uses low order piecewise polynomials

### 1.4 Channelization

to compute the coefficients of the polyphase filter stages on the fly. With an up-sampling ratio greater than 1-to-5, the Farrow filter provides reduced complexity as compared to the standard polyphase form [51]. The polynomial form of the polyphase filter set has a significant advantage of reducing the memory resources required for the stage coefficients.

A class of multiplier-less filters, e.g., Cascade Integrator Comb (CIC) filters, can also be used for up- and down- sampling tasks. Although a CIC filter is not a good filter in terms of achieving desired out-of-band spectral attenuation, a cascade of 3 to 5 stages of CIC filters becomes attractive. Furthermore, it has a non-uniform passband gain which distorts the baseband spectrum. This main lobe gain reduction usually limits the input signal bandwidth to be less than 25% of the main lobe bandwidth. The spectral distortion due to the main lobe is corrected by embedding the inverse response in a FIR filter preceding or following the CIC [30].

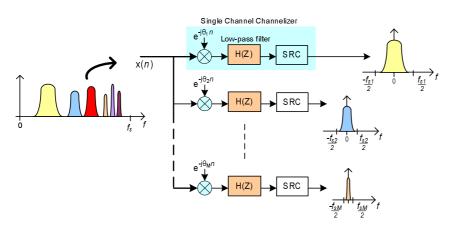

#### Single channel and Multi-channel

There are two possible areas of application for channelization. In a mobile terminal, only one channel is normally selected, while a base station needs to select many channels. Single channel applications require a one-channel channelizer which can be realized by down-conversion and the channel filtering techniques discussed above. A straightforward solution for the multi-channel application is the "per-channel approach", shown in Fig. 1.10, which essentially is a parallel realization of M one-channel channelizers, where M is the number of channels [10]. This approach is highly flexible as it has no constraints on the channel bandwidths or their distribution. On the other hand it is rigid with respect to alteration and the resulting wideband channelizer demands high silicon cost and high power consumption. Other approaches are frequency domain filtering, pipelined frequency transform, and polyphase filter bank channelizer.

Figure 1.10: Extraction of multiple channels from a wideband input signal using a perchannel approach.

Frequency domain filtering utilizes the properties of the Fast Fourier Transform (FFT) to

realize a large bank of narrowband filters. The frequency bins representing each channel of interest are extracted, filtered, and converted back to time domain using an Inverse FFT (IFFT) [52] [53].

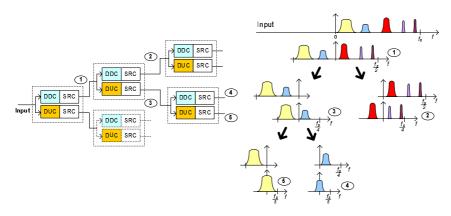

The pipelined frequency transform approach creates a binary tree of digital down converters and sample rate converters to split the incoming signal frequency into a low and a high frequency sub-band until the last tree level separates the required channels [54] [55]. The computational complexity can be significantly reduced by exploiting half-band symmetry and sampling rate reduction at each output stage. The resulting structure is similar to Hierarchical Multistage Method (HMM) [56] or Quadrature Mirror Filter (QMF) tree [57]. A binary tree of low and high band frequency converter consisting of a set of Digital Down-Converters (DDC) and Digital Up-Converters (DUC) followed by SRCs is shown in Fig. 1.11.

Figure 1.11: Pipelined frequency transform as a binary tree of low (DDC) and high (DUC) band frequency converters followed by SRC.

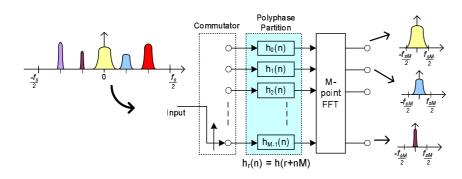

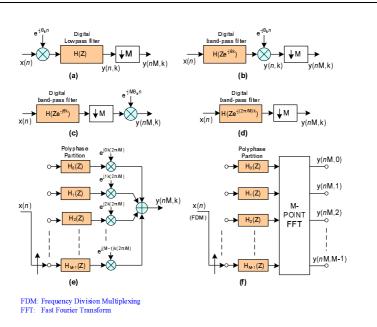

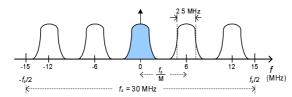

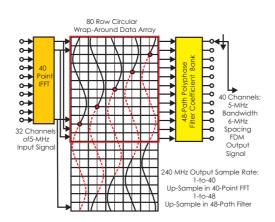

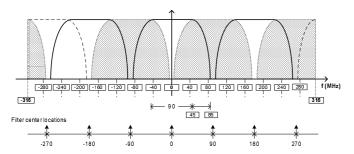

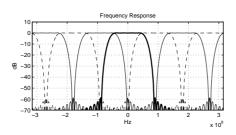

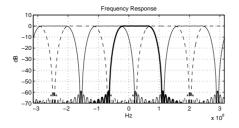

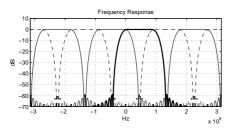

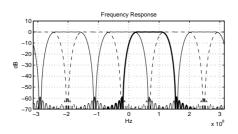

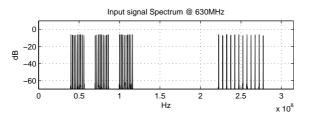

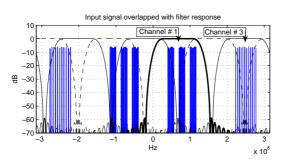

Computationally efficient algorithms for implementing a filter bank channelizer using FFT have been developed by several authors, e.g., [31] [58] [45] [59] [60] [30]. A polyphase filter bank channelizer improves upon the efficiency of the frequency domain filtering technique by assuming redundancy within the frequency plan of the wideband channel [45]. It employs a polyphase filter which is created through the decomposition of the lowpass filter used to provide channel isolation on a "per channel" basis. The input rotary switch known as the "commutator" down-samples and down-converts all the channels to baseband which are then extracted efficiently by using FFT. A polyphase filter bank channelizer is shown in Fig. 1.12. The step-by-step transformation of a single channel channelizer to a polyphase channelizer is presented in [6] [30]. The technique, often called Modulated Filter Banks or Discrete Fourier Transform Filter Bank (DFTFB), requires the channels of extraction to be uniformly distributed, and the sample rate of the incoming signal must be an integer multiple of the channel spacing. It is highly computationally and resource efficient even for a small number of channels [30]. There are several modifications of DFTFB in the literature which provide channelization for non-uniformly bandwidth channels.

#### 1.5 Synchronization

Figure 1.12: Polyphase filter bank channelizer which can efficiently extract all the input channels to the baseband by using a single lowpass filter.

The requirement for evenly distributed channels in DFTFB (referred to as fixed channel stacking) can be overcome by using the modified Goertzel approach [61], but at the expense of increased computational complexity. Abu-Al-Saud and Stuber [62] proposed a channelizer based on a modulated perfect reconstruction bank (MPRB). It consists of an analysis and a synthesis filter, where the analysis filter splits the incoming signal into sub-bands which are added together by the synthesis filter to generate the required wide-band signals. It uses complex exponential modulated perfect reconstruction filter banks to eliminate the aliases overlap at the expense of 2M branches in the filter bank.

In [63] Mahesh and Vinod present a reconfigurable polyphase filter bank with a coefficient decimation approach [64] that is capable of extracting channels of non-uniform bandwidth. However, for each configuration based on the selected coefficient decimation factor, the channel bandwidths are uniform. Harris, et al. [65] present an efficient structure, based on polyphase filter banks to filter and simultaneously down convert multiple signals having arbitrary bandwidths and randomly located center frequencies. Their approach is based on an analysis channelizer, post analysis block, selector, and synthesis channelizers. The analysis channelizer has a Perfect Reconstruction (PR) filter, performs M/2-to-1 down sampling while aliasing all M channels to the baseband. The post analysis block extracts the spectra or their fragments belonging to the different signals from the baseband aliased channels. The selector selects the output ports of the post analysis block that contain spectral fragments of the same bandwidths which are subsequently reassembled in the up converter synthesis channelizers.

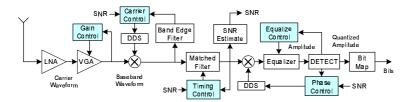

# 1.5 Synchronization

Synchronization is one of the complex tasks performed in a high data rate wireless system [66]. If the radio is not synchronized, none of the sub-systems such as matched filters, equalizer, detectors, error correcting codes, decryption, and source decoding can operate [67] [68]. As would be expected, the receiver becomes complicated, requiring more subsystems than the transmitter. These subsystems perform synchronization and signal conditioning tasks which are required to demodulate the input signal. These subsystems consist of control loops that estimate the unknown parameters of the known input

signal. These estimates are then used to perform corrective signal processing and signal conditioning operations in order to avoid the degrading due to the unknown parameters on the demodulation process. Fig. 1.13 represents a complete receiver architecture illustrating these subsystems which are [67];

- 1. an AGC loop to estimate and remove the unknown channel attenuation,

- 2. a carrier recovery loop to estimate and remove the unknown frequency offset between the input signal's nominal and actual carrier frequency,

- a timing recovery loop to estimate and remove unknown time offsets between the receiver's sampling clock and the optimal sample positions of the matched filter output series,

- 4. an equalizer loop to estimate and remove unknown channel distortion which would be responsible for inter-symbol interference,

- 5. a phase recovery loop to estimate and remove unknown carrier phase offset between the input signal and the local oscillator, and

- 6. an SNR estimator to provide important information to the other subsystems.

Figure 1.13: Receiver architecture illustrating the control loops for the synchronization.

Synchronization techniques based on DSP implementations are often digital versions of their analog prototypes. Such solutions make compromises appropriate for their time and do not exploit the actual strength of the DSP system [33]. In the  $1^{st}$  generation radio receiver, apart from the gain and phase imbalance between the quadrature paths that limits the fidelity, the digital loop filters are implemented in DSP for the carrier and timing recovery, but analog components are used in the feedback paths in order to control the Voltage Controlled Oscillator (VCO). In the  $2^{nd}$  generation, in order to eliminate the gain and phase imbalance of quadrature paths, as well as the analog components for control loops, the ADC is moved to the IF stage where quadrature down-conversion is performed in the digital domain. The sequence of operations in the  $2^{nd}$  generation is (i) frequency translation, (ii) filtering, and (iii) sample rate conversion. These operations are the digital equivalent to the analog operations performed in a  $1^{st}$  generation receiver. In modern  $3^{rd}$  generation receivers, the processes of translation, filtering, and re-sampling are rearranged in clever ways (explained in the next section) which reduces the computational complexity, while increasing the utility of the operations [33].

Multirate signal processing techniques and CORDIC subsystems deliver efficient solutions for synchronization tasks, i.e., carrier recovery, matched filtering, timing recovery, and phase detection.

# 1.6 Modern Receivers - state-of-the-art

Many companies designing radio receivers and transmitters are still using analog solutions which they have directly translated into the digital domain. These legacy designs include compromises which were appropriate for their time (e.g., traditional analog filters trading off amplitude- and phase responses for filter order), but it is inefficient to map such compromises directly into the digital domain. Therefore, new design methodologies which can lead to more efficient DSP based architectures for digital front-ends, and which can efficiently utilize promising new hardware technologies, e.g., FPGAs, are highly needed. A digital filter can often perform more than its intended primary filtering task. It can absorb many of the secondary signal processing tasks of a system. There are many ways of folding other functions into the filtering process using multirate signal processing techniques, which will be presented here.

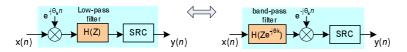

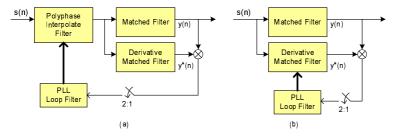

In a  $2^{nd}$  generation radio receiver, the sequence of operations (in a digital replica of the analog operations performed in a  $1^{st}$  generation receiver) is frequency translation, filtering, and sample rate conversion. In  $3^{rd}$  generation of radio receivers [33], as shown in Fig. 1.14, the process of translation and filtering are interchanged according to the Equivalency Theorem [30] which states that down-conversion followed by baseband filtering is the same as the filtering at the carrier followed by down-conversion. This reordering operation is shown in Fig. 1.15.

Figure 1.14: 3<sup>rd</sup> generation of radio receiver architecture.

Figure 1.15: The Equivalency Theorem - down-conversion followed by baseband filtering is the same as filtering at the carrier followed by the down-conversion.

So, rather than moving the desired band to baseband with a complex digital heterodyne,

the baseband filter is moved to the desired center frequency and filtering is performed to reduce the bandwidth at the digital IF frequency. The resultant reduced bandwidth, complex IF signal is image free and can be down-sampled M-to-1, to its appropriate Nyquist rate  $f_s/M$ . The down-sampling results in aliasing of the center frequency to a new spectral position. The down-sampling can alias the IF frequency directly to the baseband provided that the IF frequency is positioned at a multiple of the output sample rate [30]. A signal having an offset from a multiple of the output sample rate is also aliased to baseband plus that offset. This offset can then be removed with a carrier recovery scheme while operating at the reduced sampling rate. The rearrangement of the processes is shown in Fig. 1.16 which results in the advantage that the spectral translation now occurs after the filtering and at the low output rate rather than before the filtering at the high input rate [33].

Figure 1.16: Reordering process that moves the down-conversion after the filtering and resampling process.

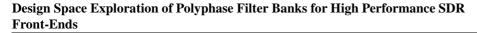

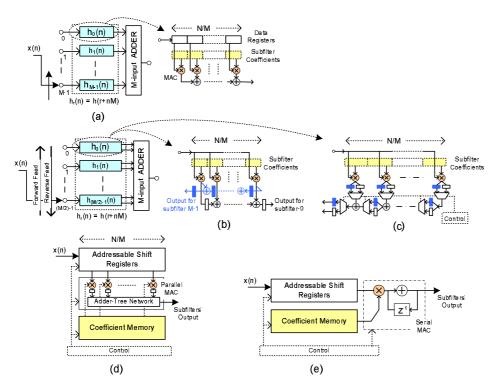

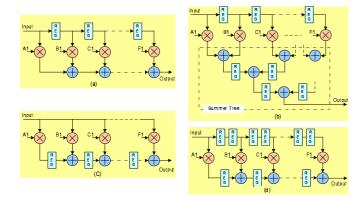

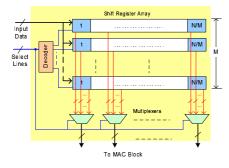

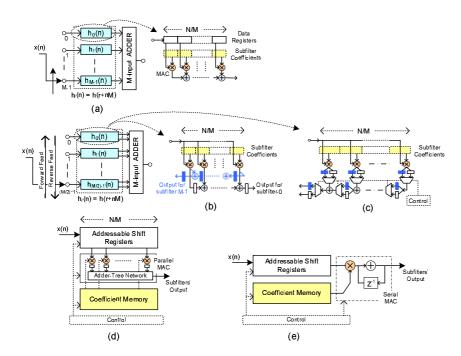

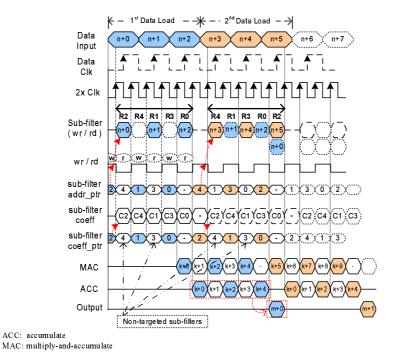

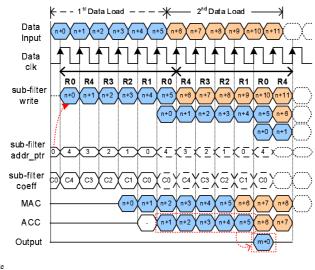

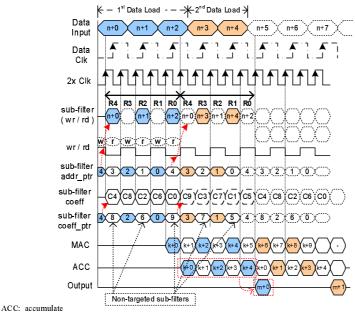

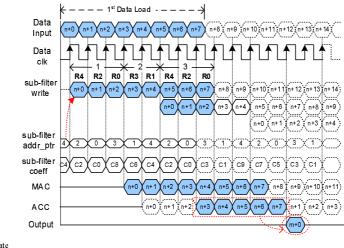

The M-to-1 down-sampling after the filtering at IF discards the processed samples which wastes the computational power used by the filter. To reduce this workload, the resampling and the filtering operations are reordered so that one output is computed for every M input samples. This is achieved by applying the Noble identity as was shown in Fig. 1.5 which requires the original up-converted filter to be partitioned to M subfilters. The reordering of the M-partitioned subfilters (lowpass filter) and resampler using the Noble Identity results in a polyphase filter, as shown in Fig. 1.17. It has the resampler at the input (a rotary switch which, as previously mentioned, is denoted by the commutator) feeding M subfilters one at a time which operate at the reduced output rate rather than the original input rate. As the subfilters operate sequentially, they can be merged into a single path structure having a subfilter that accesses the coefficients of the successive M subfilters.

Figure 1.17: Polyphase partitioning of a lowpass filter used to apply the Noble Identity to form an M-path polyphase filter.

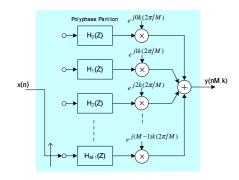

The lowpass version of a polyphase filter can be converted to its bandpass version by

#### 1.6 Modern Receivers - state-of-the-art

associating the complex heterodyne term of the modulation of the filter weights with the delay elements storing the filter weights. This is achieved by feeding the complex scalar  $e^{jkr(2\Pi/M)}$  to each path of the *M*-path filter [30], where *r* is the number of the polyphase path, and *k* is the number of channel to be extracted at the baseband. This is shown in Fig. 1.18.

Figure 1.18: Resampling *M*-path down-converter.

The down-sampling process provides a unique feature of changing the phase of the sample locations in the down sampled time series relative to the epochs in the series. In an M-to-1 down sampling, the output time series can be accessed with M different sample phase offsets. These M possible output series can effectively be used for a timing recovery process. In such a case, the timing recovery loop controls the phase of the re-sampling process in the re-sampling filter rather than the loop modifying the locations of sample points during the ADC process as done in  $1^{st}$  and  $2^{nd}$  generation receivers. The phase of the re-sampling filter is defined by the selection of the phase weights in its single path structure. Timing recovery process, the number of the polyphase stages (for a polyphase filter) must be increased to satisfy the required timing granularity rather than the down sampling requirement [33].

The re-sampling process in the polyphase filter (effecting both the spectral translation and the timing recovery process), results in a complex baseband signal at a reduced sample rate and with the correct timing. However, it does not have the correct carrier frequency and phase correction, which is subsequently corrected by a complex heterodyne operation before performing further processing by the equalizer and matched filter. The heterodyne on the complex baseband signal requires four multipliers as compared to the heterodyne on the real IF centered signal that requires only two multipliers. The complex multiplier can be embedded in the Direct Digital Synthesizer by using the CORDIC algorithm as a vector rotator [43] which not only provides the complex samples of the rotating phasor but performs the multiplication at the same time.

Furthermore, in an M-path polyphase filter, the output sample rate of the baseband aliased center frequencies is always equal to M. The M-path polyphase filter bank can also be modified to allow resampling by arbitrary ratios while simultaneously performing base-

band aliasing from center frequencies at Nyquist zones that are not multiples of the output sample rate. These resampling technique are explained in [69] which embed the resampling process in (i) the polyphase commutator, that is, in the interaction between input data registers and the polyphase coefficients, and (ii) the interaction between the polyphase outputs and the FFT input. This only requires a state machine to schedule the interactions, hence there is no computational overhead.

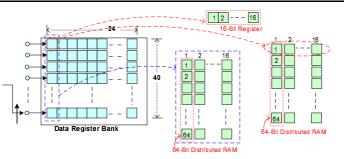

# 1.7 Polyphase Filter Bank Mapping - State-of-the-Art

We have explored and presented algorithms/ techniques for performing the DFE processing tasks for modern SDRs. Multirate signal processing based algorithms turned out to be a valuable approach for efficient SDR processing engines. An *M*-path polyphase filter has *M* parallel branches, each operating at 1/M of the input rate. This *M*-paths parallelism can be exploited in a number of different ways to meet the desired cost function of area, time, power, etc. The mapping of these parallel structures to highly complex reconfigurable platforms (FPGA) demands a structured methodology to obtain not only a costfunction constrained implementation, but also to exploit enhanced mapping strategies. The state-of-the-art for mapping of polyphase filter banks to reconfigurable platforms is therefore discussed next.

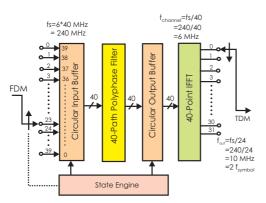

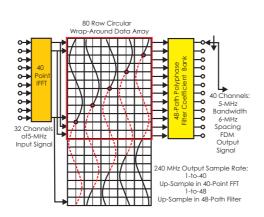

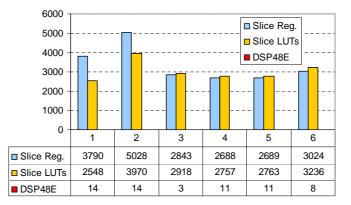

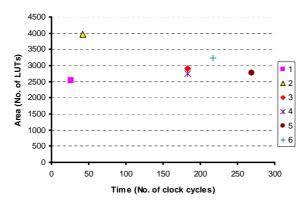

Egg, Harris, and Dick [70] presented a polyphase filter bank based wideband channelizer implemented on a Xilinx Virtex-4 FPGA, to extract narrow band channels and further to reconstruct a wider bandwidth channel using perfect reconstruction filter. Melis and Comoretto [71] considered a 512 MHz polyphase filter bank with overlapping bands for use in a spectrometer. Their design used a Xilinx Virtex-5 FPGA, and the multipliers for the polyphase filter are based on CLB resources. Berner and Leon [72] discussed the FPGA implementation aspects of a polyphase filter bank as analysis and synthesis filter banks. Valdes et al. [73] showed a polyphase filter bank implementation in MP3 decoding by using 32-point DCT-II and windowing functions. Marinova et al. [74] presented a multicarrier modem core on an FPGA which uses Offset Quadrature Amplitude Modulation (OQAM) and polyphase filter based analysis and synthesis filter banks. Han [75] analyzed the front-end design for a wideband SDR. A 32 channel DFE using a polyphase filter bank was implemented on a Xilinx Virtex-5 FPGA. In [76], Ang et al. showed a Virtex FPGA implementation of a polyphase filter for sample rate conversion. They presented optimizations in terms of transformation to reduce the critical path, and constant coefficient multiplier for both area and speed performance improvement. Fahmy and Doyle [77] suggested an FPGA based reconfigurable polyphase filter bank architecture for spectrum sensing which is based on a shared MAC structure. Harris, Vuletic, and Lowdermilk [34] presented a polyphase filter bank based design to replace multi-channel analog modulators, where 384 FM modulators are implemented on a single Xilinx Virtex-4 FPGA. Wang et al. [78] showed an energy-efficient hardware architecture and VLSI implementation of a polyphase channelizer with applications to subband adaptive filtering. They used the Computation Sharing Differential Coefficient (CSDC) method to obtain a low complexity parallel multiplier-less implementation of FIR subfilters.

In most of the above mentioned literature, the mapping of the polyphase filter (banks) to

#### 1.8 Thesis formulation

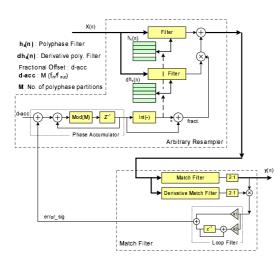

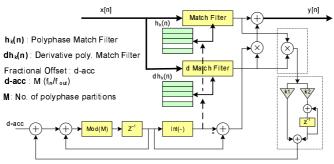

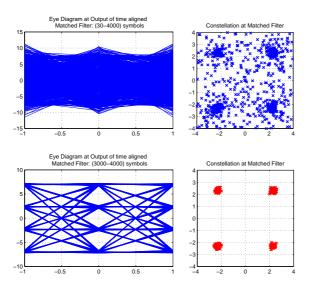

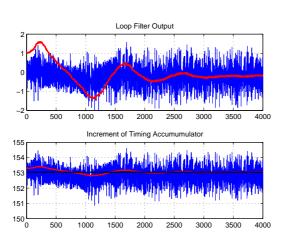

an FPGA is presented as a final result emphasizing reduced resource usage, but often they lack a discussion of how these results are actually achieved on highly complex platforms which provide a huge design space. On the other hand, Intellectual Property (IP) cores are available from different vendors, e.g., [22] [79] [80] [81], these can be customized according to our needs and can eliminate to a certain extend the need for design space exploration. Normally, these IP cores are available for fixed functionalities (i.e., polyphase decimators and polyphase interpolators) which operate in a fixed mode where the sample rate is either decreased or increased by a factor equal to the number of polyphase partitions. The IP cores, are considered to be the future approach to FPGA solutions [82], currently lack advanced multirate signal processing engines that allow several functions to be embedded within a single filter. These functions include embedded sampling rate changes that allow any rational sample rate change while simultaneously performing filtering operations, combined arbitrary resampling, match filtering, and symbol timing recovery, etc. As a natural consequence, we therefore formulated our hypothesis to address this missing work.

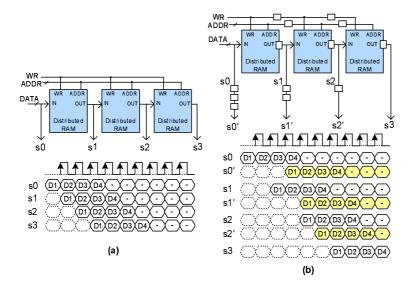

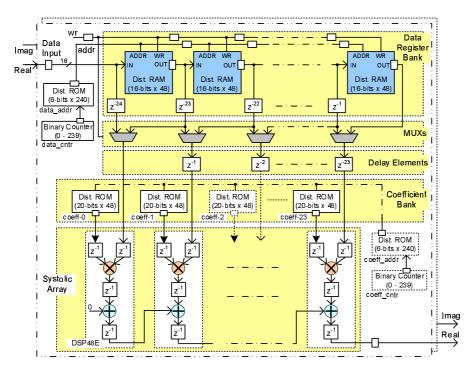

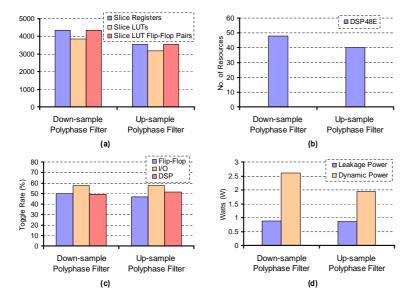

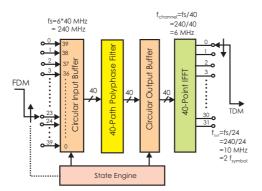

# **1.8** Thesis formulation