### **Aalborg Universitet**

### Modular uninterruptible power supply system

Zhang, Chi

DOI (link to publication from Publisher): 10.5278/vbn.phd.engsci.00139

Publication date: 2016

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Zhang, C. (2016). Modular uninterruptible power supply system. Aalborg Universitetsforlag. https://doi.org/10.5278/vbn.phd.engsci.00139

### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# MODULAR UNINTERRUPTIBLE POWER SUPPLY SYSTEM

### BY CHI ZHANG

**DISSERTATION SUBMITTED 2016**

# MODULAR UNINTERRUPTIBLE POWER SUPPLY SYSTEM

PH. D THESIS

by

Chi Zhang

Dissertation submitted

.

Dissertation submitted: September 6, 2016

PhD supervisor: Prof. Josep M. Guerrero,

Aalborg University, Denmark

PhD committee: Associate Professor Tamás Kerekes (chair.)

Aalborg University, Denmark

Professor Marco Liserre

Christian-Albrechts University of Kiel, Germany

Professor Ramon Blasco-Gimenez Technical University of Valencia, Spain

PhD Series: Faculty of Engineering and Science, Aalborg University

ISSN (online): 2246-1248

ISBN (online): 978-87-7112-792-8

Published by: Aalborg University Press Skjernvej 4A, 2nd floor DK – 9220 Aalborg Ø Phone: +45 99407140

aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Chi Zhang

Printed in Denmark by Rosendahls, 2016

### CV

Chi Zhang received the B.S degree in Electronics and Information Engineering from Zhejiang University (ZJU), Hangzhou, China in 2012. Between 2012 and 2013, he worked as a Master student in National Engineering Research Center for Applied Power Electronics in Zhejiang University in the topic of Power Electronics and Drives. He is currently working toward his Ph. D in Power Electronics at the Department of Energy Technology, Aalborg University, Denmark. His research interests include power electronics converter design in modular uninterruptible power supply systems (UPS), active power filter (APF) systems and renewable energy generation systems.

ı

### **ENGLISH SUMMARY**

Online uninterruptible power supply systems (UPS) have been actively growing during the past decades due to the fast development of modern technologies. A great number of advanced electrical loads, e.g. communication facilities, academic laboratory equipment, etc, are constantly emerging in our everyday lives. That is why, power electronics interfaces, which can regulate the power quality and cooperate actively with the main grid, are becoming more and more significant in an online UPS system. However, the exiting product is lack of flexibility. Thus the objective of the project is to study power electronics converters control in a flexible modular online UPS system. Numbers of emerging potentials and challenges will be discussed.

First, different UPS architectures are reviewed and two modularized strategies are proposed by considering the drawbacks and main advantages. Based on the different architectures, variable control methods are discussed, especially the importance of how to parallel different modules in the system. The controls methodologies should follow the UPS product standard IEC 62040-3 in order to consider it into a real application, such as data center, hospital and IT loads integration scenarios. The basic behavior for the parallel modules is presented and it should be taken into account when designing the system.

Based on the basic knowledge of modular system, advanced control architectures and their concepts are discussed and compared in detail. The control mechanism of the modules in the online UPS system is shown and simulation models were conducted in PLECS. On the other hand, other functionalities for a modular online UPS system such as active power filter, and UPQC are also investigated in Chapter 2 with experimental results. In Chapter 3, a mathematical model is proposed for a modular online UPS system, which emulates a real modular system and study its behavior in both steady and dynamic state. Experimental data was acquired to analysis the proposed system behavior together with the mathematic model. Thermal analysis for the modular system was presented in Chapter 4 while Chapter 5 presents the practical issues for an industrial prototype.

It is concluded that power electronics converters are playing a critical role in modular online UPS systems as well as the module parallel technology. Output voltage stability, dynamic performance, power sharing among modules and reliability issues of modules are the most important aspects that should be taken into account while designing the modular system. The proposed control strategies have been simplified, easy to implement and provided a better performance.

### DANSK RESUME

Online nødstrømsanlæg (UPS) er aktivt voksende i de seneste årtier på grund af den hurtige udvikling af moderne teknologi. Et stort antal avancerede elektriske belastninger, feks kommunikationsfaciliteter, akademisk laboratorieudstyr, etc, der konstant dukker op i vores hverdag. Det er grunden til, magt elektronik grænseflader, der kan regulere strømmen kvalitet og samarbejder aktivt med de vigtigste nettet, bliver mere og mere markant i en online UPS -system. Men den spændende produkt er mangel på fleksibilitet. Således er formålet med projektet er at studere magt elektronik omformere kontrol på en fleksibel modulopbygget online UPS system. Antallet af nye potentialer og udfordringer vil blive drøftet.

Først forskellige UPS arkitekturer revideret og to modulariserede strategier er foreslået af overvejer ulemperne og vigtigste fordele. Baseret på de forskellige arkitekturer, fremgangsmåder variabel styring diskuteres, især betydningen af , hvordan man parallelle forskellige moduler i systemet. Kontrollerne metoder bør følge UPS produkt standard IEC 62040-3 for at overveje det til en rigtig program, f.eks datacenter, hospital og IT indlæser integration scenarier. Den grundlæggende adfærd for de parallelle moduler præsenteres og det skal tages i betragtning ved udformningen af systemet.

Baseret på den grundlæggende viden om modulsystem, er avancerede kontrol arkitekturer og deres koncepter diskuteret og sammenlignet i detaljer. Mekanismen kontrol af modulerne i online UPS system er vist og simuleringsmodeller blev udført i PLECS. På den anden side er andre funktionaliteter for et modulært online UPS-system såsom aktiv effekt filter, og UPQC også undersøgt i kapitel 2 med eksperimentelle resultater. I kapitel 3, er en matematisk model, der foreslås for et modulopbygget online UPS system, der emulerer en reel modulsystem og studere dens adfærd i både stabil og dynamisk tilstand. Eksperimentel data blev erhvervet til analyse det foreslåede system adfærd sammen med den matematiske model. Termisk analyse for det modulære system blev præsenteret i kapitel 4, mens kapitel 5 præsenterer de praktiske spørgsmål til en industriel prototype.

Det konkluderes, at power elektronik omformere spiller en afgørende rolle i modulære online UPS-systemer samt modulet parallel teknologi. Udgangsspænding stabilitet, dynamisk ydeevne, magtdeling blandt moduler og pålidelighed spørgsmål af moduler er de vigtigste aspekter, der bør tages i betragtning, samtidig med at designe det modulære system. De foreslåede kontrolstrategier er blevet forenklet, let at implementere og givet en bedre ydeevne.

### **ACKNOWLEDGEMENTS**

The Ph. D study was carried out during the period of between December 2013 and September 2016 and was under the supervision of Prof. Josep M. Cuerrero from the Department of Energy Technology in Aalborg University. The famous academic atmosphere is one of the main reasons that I choose to come here. After three years' research experiences and unforgettable life here, I am realizing that modular uninterruptible power supply system (UPS) is received more attention due to the burst development of different kinds of electronic loads. And numbers of technical problems for the modular system is still required to be investigated.

The purpose of this project is to investigate advanced control architectures for a modular UPS system, which can be implemented in real products. It will be a great honor for the author if this thesis can present some helpful hints for both researchers and engineers in this field.

I would like to show grateful thanks to Prof. Josep M. Guerrero for the effective and impressive supervision during my Ph. D study for giving me so many directive instructions, constructive proposals and help during my stay in Barcelona. And I would like to give my sincere acknowledgement to Dr. Juan C. Vasquez. I also want to show my regards to Prof. Min Chen from Zhejiang University for his support and help.

I appreciate the funding support for my research provided by the China Scholarship Council and the Department of Energy Technology. Special thanks to the head of department John K. Pedersen from Aalborg University and Mr. Chenggang Liu, Mr. Yun Zhang from Chinese Embassy of Denmark for their kind support.

I would also thank Prof. Ernane A.A. Coelho, Carsten Seniger for their kind support. Corina Gregersen, Casper Jørgensen, Tina Larsen, Mette Skov Jensen, Walter Neumayr and Ann Loise Henriksen, all of them help me a lot during my stay in Aalborg. I would also show my great thanks to Jordi Montero, Ramon Pinyol, Ramon Ciurans, Albert Marzabal, Santi Trujilo and Josep Marti Gasch for helping me so much during my stay in the company Salicru S/A in Barcelona, Spain.

I would like show my great gratefulness to my colleagues from the Department of Energy Technology, Aalborg University, Denmark. I would like to send my best wishes my colleagues Bo Sun, Wenli Yao, Xin Zhao, Baohua Zhang, Hengwei Lin, Lexuan Meng, Dan Wu, Yajuan Guan, Yanjun Tian, Ning He and Francisco D. Freijedo. Thanks to all of you, Moreover, I would like also show my appreciations to Dr. Ke Ma and Dr. Mingzhi Gao for their kind support during my Ph. D study here.

Finally, the sincerest gratitude to my parents for their love, encouragement and support and to Jiangyuan Li for her kind help and support especially during my stay in Barcelona, Spain.

Richard Nixon, American 37th President, ever said,

"Our destiny offers no the cup of despair, but the chalice of opportunity."

After three years Ph. D study here, I have a better understanding what Richard Nixon has said. Never feel despair while being faced with difficulty because it may be the chance to reverse the situation. Great appreciation to all of my friends and wish you all have a happy life in the future.

Chi Zhang

May. 2016, Aalborg

### **TABLE OF CONTENTS**

| Part I Thesis report main content                                           | 17 |

|-----------------------------------------------------------------------------|----|

| Chapter 1. Introduction                                                     | 18 |

| 1.1. State of art of uninterruptible power supply systems                   | 18 |

| 1.2. UPS system architectures                                               | 20 |

| 1.2.1. Three types of conventional UPS system architectures                 | 20 |

| 1.2.2. Evolution of online UPS system architecture                          | 23 |

| 1.2.3. Power electronic topologies in a UPS system                          | 25 |

| 1.3. Modular online UPS system and challenges                               | 27 |

| 1.4. Scope of the thesis                                                    | 28 |

| 1.5. Outline of the thesis                                                  | 29 |

| Chapter 2. Control strategies for modular online UPS system                 | 31 |

| 2.1. Two promising structures for online UPS systems                        | 32 |

| 2.2. Control for modular online UPS system                                  | 32 |

| 2.3. Proposed controls for modular online system                            | 34 |

| 2.3.1. Basic parallel control [Publication A3, A5]                          | 34 |

| 2.3.2. Voltage amplitude recovering and phase angle synchronization [A1-6]  |    |

| 2.3.3. Shunt active power filter [Publication A4]                           |    |

| 2.4. Experimental results and validation [Publication A1-6]                 | 45 |

| 2.4.1. Power sharing and voltage transient performance [Publication A3, A5] | 45 |

| 2.4.2. Phase synchronization performance [Publication A3, A5]               | 47 |

| 2.4.3. Linear load performance [Publication A3, A5]                         | 48 |

| 2.4.4. Nonlinear load performance [Publication A1, A3, A5]                  | 51 |

| 2.4.5. Plug'n'Play capability [Publication A1, A2, A6]                      | 53 |

| 2.4.6. Active power filter and UPQC function [Publication A4]               | 54 |

| 2.4.7. Communication failure test [Publication A1]                          | 59 |

| 2.5. Conclusion                                                             | 60 |

| Chapter 3. Mathematical model and system analysis                           | 61 |

| 3.1. Mathematical model in single module perspective [Publication A3, A5]   | 61 |

### MODULAR UNINTERRUPTIBLE POWER SUPPLY SYSTEM

| 3.2. Mathematical model in overall system perspective [Publication A2]   | 65    |

|--------------------------------------------------------------------------|-------|

| 3.2.1. Small signal modelling                                            | 65    |

| 3.2.2. Model analysis with experimental results                          | 76    |

| 3.3. Conclusion                                                          | 81    |

| Chapter 4. Thermal analysis of modular online UPS system                 | 83    |

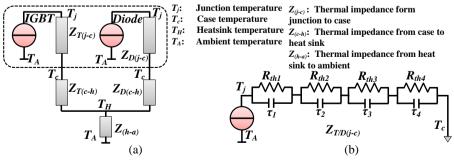

| 4.1. Thermal model basics and analysis methodology [Publication A7]      | 83    |

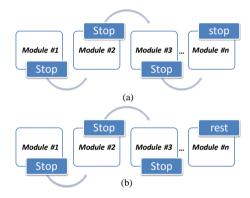

| 4.2. DC/AC modules cycling operation                                     | 85    |

| 4.2.1. Cycling and backup rules                                          | 85    |

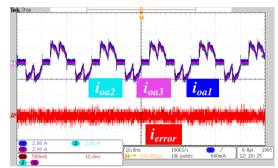

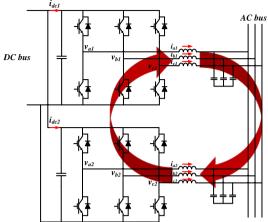

| 4.2.2. Potential zero sequence circulating current in cycling            | 86    |

| 4.3. Thermal analysis [Publication A7]                                   | 86    |

| 4.3.1. Single module thermal analysis                                    | 86    |

| 4.3.2. Unsuppressed circulating current condition                        | 87    |

| 4.3.3. Suppressing circulating current condition                         | 90    |

| 4.4. conclusion                                                          | 91    |

| Chapter 5. Practical issues in an industrial prototype                   | 92    |

| 5.1. Control methods implementation in A digital signal processor (DSP). | 92    |

| 5.2. Anti-windup for discrete proportional resonant controllers          | 95    |

| 5.3. Noise reduction                                                     | 98    |

| 5.4. Phase lock loop implementation                                      | 101   |

| 5.5. Hardware operating condition impact on performance                  | 107   |

| 5.6. Conclusion                                                          | 110   |

| Chapter 6. Conclusion and future work                                    | 111   |

| 6.1. Conclusion                                                          | 111   |

| 6.1.1. Converter topology                                                | 111   |

| 6.1.2. Control and modelling                                             | 111   |

| 6.1.3. Thermal analysis                                                  | 112   |

| 6.1.4. Software-hardware design issues                                   | 112   |

| 6.2. Contributions from the author's point of view                       | 112   |

| 6.2.1. Control framework for modular online UPS system                   | 112   |

| 6.2.2. Mathematical model establishment for modular online UPS system    | n 112 |

| 6.2.3. Thermal analysis of circulating current                           | 113   |

| 6.2.4. Product development                                   |     |

|--------------------------------------------------------------|-----|

| 6.3. Proposals for future research topics                    |     |

| 6.3.1. Detailed mathematical model for plug'n'play operation |     |

| 6.3.2. Improved control for parallel system                  |     |

| 6.3.3. Thermal analysis                                      |     |

| Literature list of references                                | 115 |

| Appendices                                                   | 125 |

| Part II Thesis report support publications                   | 129 |

| Publication A1                                               | 130 |

| Publication A2                                               | 131 |

| Publication A3                                               | 132 |

| Publication A4                                               | 133 |

| Publication A5                                               | 134 |

| Publication A6                                               | 135 |

| Publication A7                                               | 136 |

| Publication A8                                               | 137 |

### **LIST OF FIGURES**

| Figure 1-1 UPS products evaluation criteria                                                                          | .18  |

|----------------------------------------------------------------------------------------------------------------------|------|

| Figure 1-2 UPS product performance score of different vendors.                                                       |      |

| Figure 1-3 Global UPS market and typical applications.                                                               | .20  |

| Figure 1-4 Offline UPS system                                                                                        |      |

| Figure 1-5 Line interactive UPS system                                                                               |      |

| Figure 1-6 Line interactive UPS system.                                                                              |      |

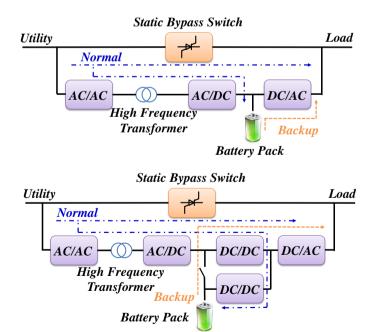

| Figure 1-7 Half transformer-less online UPS system                                                                   | .23  |

| Figure 1-8 Total transformer-less online UPS system.                                                                 |      |

| Figure 1-9 High frequency transformer online UPS system                                                              | .24  |

| Figure 1-10 Power electronic topologies for DC/AC. (a) 3P-HB (b) 3L-NPC (c) 3P-FB                                    |      |

| Figure 1-11 Power electronic topologies for AC/DC. (a) Vienna rectifier. (b) 3L-4P-HB                                | .26  |

| Figure 1-12 AC/DC stage integrated with battery charger                                                              | .26  |

| Figure 1-13 Transient duration requirements for online UPS system. (a) Limit for mo                                  | ode  |

| change. (b) Limit for linear load change. (c) Limit for nonlinear load change                                        |      |

| Figure 2-1 Two promising modular UPS structures. (a) Partial modularized. (b) To                                     | otal |

| modularized                                                                                                          | .31  |

| Figure 2-2 Simplified model for DC/AC parallel modules                                                               | .33  |

| Figure 2-3 (a) Inductive condition. (b) resistive condition                                                          | .33  |

| Figure 2-4 Virtual impedance and "Q-φ" control diagram                                                               | .35  |

| Figure 2-5 Active and reactive power sharing transient process. (a) only virtual impedan                             | nce  |

| $(kph=0)$ . $(b)$ only $Q-\phi$ loops $(Rvir=0)$ . $(c)$ using both virtual impedance and $Q-\phi$ loops             | .36  |

| Figure 2-6 Proposed overall control diagram for the paralleled UPS system                                            | .38  |

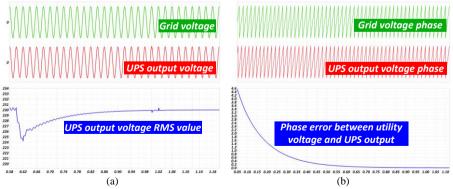

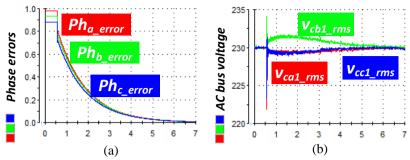

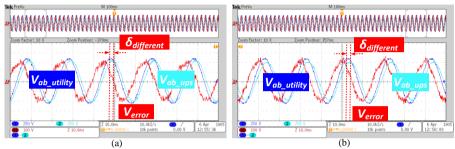

| Figure 2-7 Phase synchronization performance. (a) Voltage amplitude recovery. (b) Phase synchronization performance. | ase  |

| synchronization.                                                                                                     | .39  |

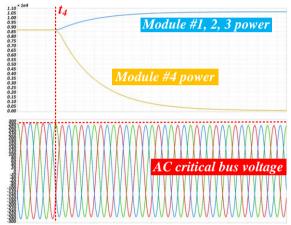

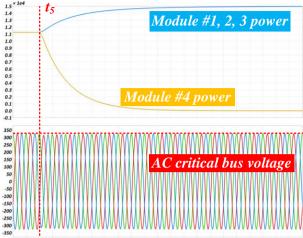

| Figure 2-8 AC critical bus voltage when one module plugs out of the system                                           | .40  |

| Figure 2-9 Control diagram for online UPS system for plug'n'play capability –Simple Ty                               | pe.  |

|                                                                                                                      | .40  |

| Figure 2-10 AC critical bus voltage when one module plugs out of the system                                          | .42  |

| Figure 2-11 Proposed Modular Online UPS Structure with active power filter                                           | .42  |

| Figure 2-12 Overall control diagram for the UPS part.                                                                | .42  |

| Figure 2-13 Control scheme for the active power filter.                                                              | .43  |

| Figure 2-14 Performance under non-ideal utility. (a) Normal to Bypass. (b) Bypass                                    |      |

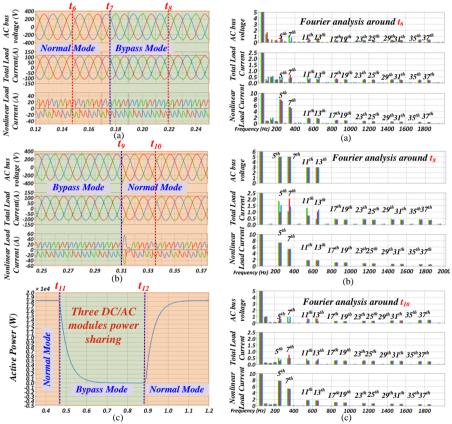

| Normal. (c) active power sharing                                                                                     | .44  |

| Figure 2-15 FFT Analysis in different modes. (a) details at t6. (b)details at t8. (c) details at                     |      |

|                                                                                                                      | .44  |

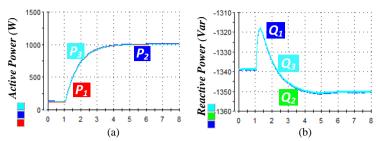

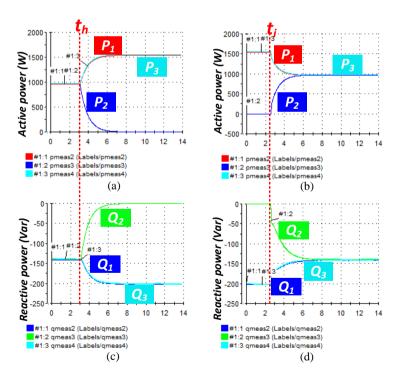

| Figure 2-16 DC/AC modules parallel performance. (a) Active power sharing between th                                  | ree  |

| modules. (b) Reactive power sharing between three modules                                                            | .45  |

| Figure 2-17 Active and reactive power of 3 DC/AC modules. (a) Three DC/AC active pow                                 |      |

| (b) Three DC/AC reactive power.                                                                                      | .46  |

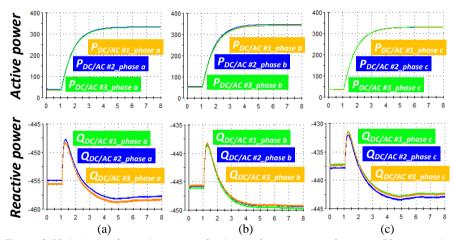

| Figure 2-18 Active and reactive power sharing performance per phase. (a) Phase a active                              |

|----------------------------------------------------------------------------------------------------------------------|

| and reactive power of three DC/AC. (b) Phase b active and reactive power of three DC/AC.                             |

| (c) Phase c active and reactive power of three DC/AC46                                                               |

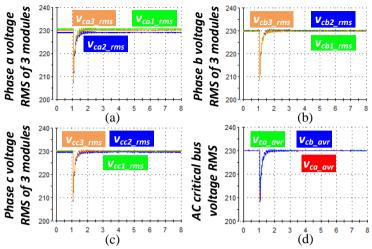

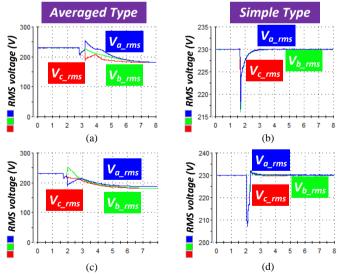

| Figure 2-19 RMS voltage (Three DC/ACs and AC critical bus). (a) Phase a voltage RMS. (b)                             |

| Phase b voltage RMS. (c) Phase c voltage RMS. (d) AC critical bus voltage RMS47                                      |

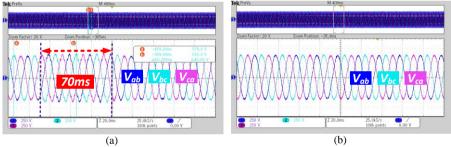

| Figure 2-20 Phase synchronization tests. (a) Phase errors of 3 phases. (b) RMS voltage of AC                         |

| critical bus                                                                                                         |

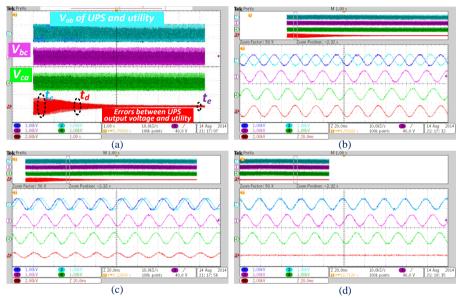

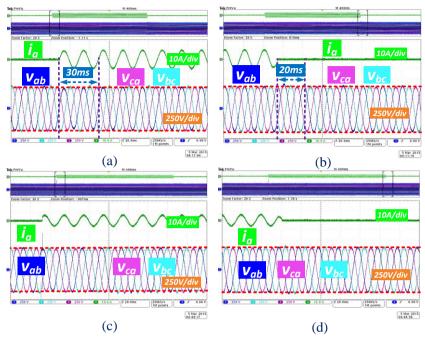

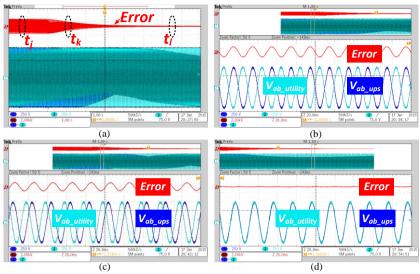

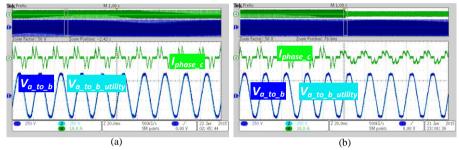

| Figure 2-21 Synchronization process between $v_{ab\_utility}$ and $v_{ab\_ups}$ . (a) Overall process. (b)           |

| Details at t <sub>c</sub> . (c) Details at t <sub>d</sub> . (d) Details at t <sub>e</sub>                            |

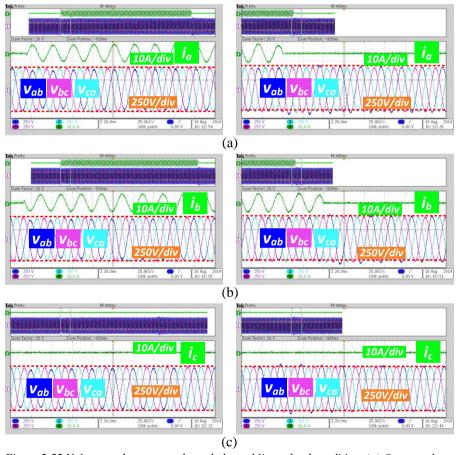

| Figure 2-22 Voltage and current under unbalanced linear load condition. (a) Output voltage                           |

| and phase <b>a</b> current. (b) Output voltage and phase <b>b</b> current. (c) Output voltage and phase <b>c</b>     |

| current                                                                                                              |

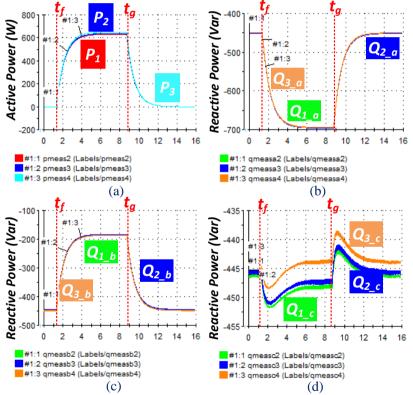

| Figure 2-23 Active and reactive power sharing performance under unbalanced nonlinear                                 |

| load condition. (a) Active power. (b)-(d) Reactive power of phase a, b and c50                                       |

| Figure 2-24 Voltage and current under unbalanced load condition. Output voltage and phase                            |

| a current when load is turned on and off (a)-(b) $\mathbf{L}+\mathbf{R}$ type load. (c)-(d) $\mathbf{L}$ type load51 |

| Figure 2-25 UPS line to line voltage (phase a to b) and phase a current. (a) Balanced load                           |

| connected. (b) Balanced load disconnected                                                                            |

| Figure 2-26 UPS line to line voltage (phase a to b) and phase a current. (a) Balanced load                           |

| connected. (b) Balanced load disconnected                                                                            |

| Figure 2-27 Nonlinear load sharing performance                                                                       |

| Figure 2-28 AC critical bus voltage performance when one DC/AC stops. (a) Average type                               |

| under linear load. (b) Simple type under linear load. (c) Average type under nonlinear load.                         |

| (d) Simple type under nonlinear load52                                                                               |

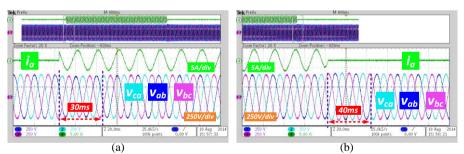

| Figure 2-29 Power performance when modules are plugging in and out. (a) active power                                 |

| when module plugs out. (b) active power when module plugs in. (c) reactive power when                                |

| module plugs out. (d) reactive power when module plugs in                                                            |

| Figure 2-30 Real-time voltage performance of AC critical bus. (a) module plugs in. (b)                               |

| module plugs out54                                                                                                   |

| Figure 2-31 Synchronization performance. (a) overall process. (b) details at t <sub>i</sub> . (c) details at         |

| <i>t<sub>k.</sub></i> (c) details at t <sub>l.</sub>                                                                 |

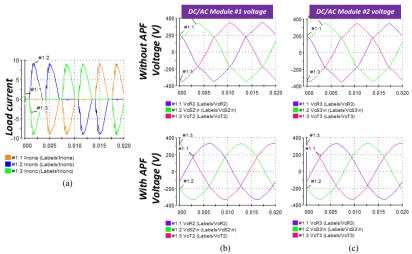

| Figure 2-32 Active power filter performance. (a) load current. (b) DC/AC module #1 output                            |

| voltage with and without APF. (c) DC/AC module #2 output voltage with and without APF. 55                            |

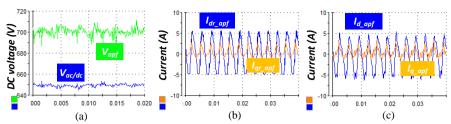

| Figure 2-33 APF module performance. (a) DC capacitor voltage. (b) current reference in dq                            |

| frame. (c) output current in dq frame56                                                                              |

| Figure 2-34 Power sharing performance among the DC/AC modules. (a) reactive power. (b)                               |

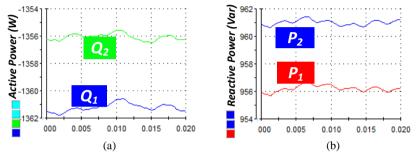

| active power                                                                                                         |

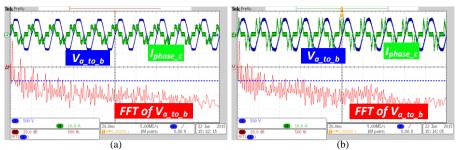

| Figure 2-35 AC critical bus voltage performance. (a) without APF. (b) with APF57                                     |

| Figure 2-36 Synchronization performance with the utility. (a) with APF enabled. (b) transient                        |

| performance while enabling and disabling the APF                                                                     |

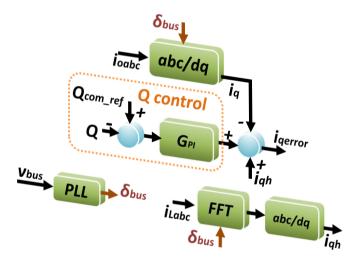

| Figure 2-37 UPQC control modification in q axis                                                                      |

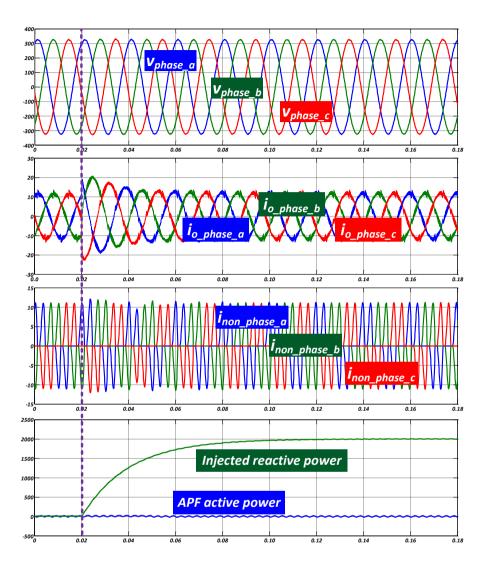

| Figure 2-38 UPQC voltage and current performance                                                                     |

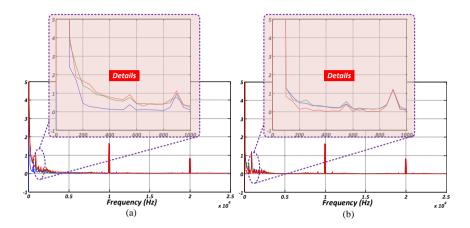

| Figure 2-39 FFT performance of AC critical bus voltage. (a) before 0.02s. (b)after 0.02s59                           |

### MODULAR UNINTERRUPTIBLE POWER SUPPLY SYSTEM

| Figure 2-40 Performance in case of communication failure. (a) Two modules in parallel. (b)                                       |

|----------------------------------------------------------------------------------------------------------------------------------|

| Three modules in parallel60                                                                                                      |

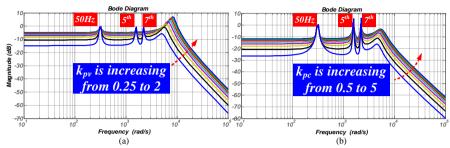

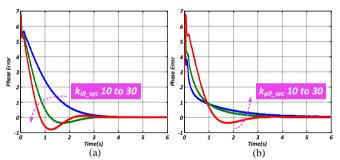

| Figure 3-1 Bode diagram of inner loop. (a) Bode diagram with variable $k_{pv}$ . (b) Bode diagram                                |

| with variable $k_{pc}$                                                                                                           |

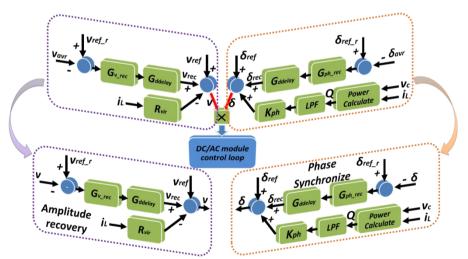

| Figure 3-2 Control loops simplification for voltage restoration and phase synchronization62                                      |

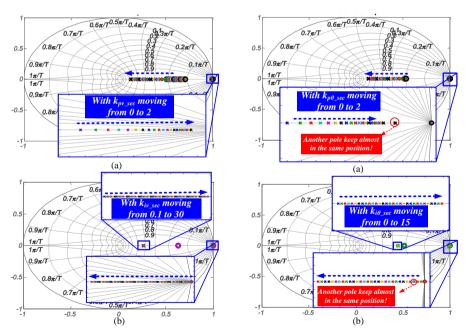

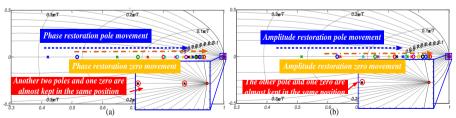

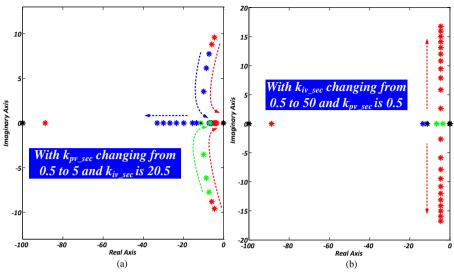

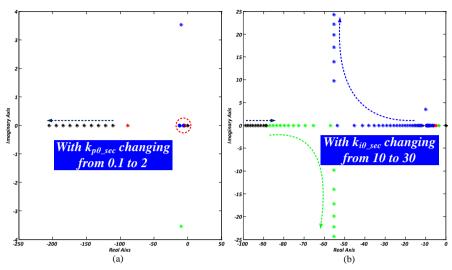

| Figure 3-3 pole-zero map for amplitude restoration. (a) PZ map with variable kpv_sec.                                            |

| (b) PZ map with variable kiv_sec63                                                                                               |

| Figure 3-4 pole-zero map for phase restoration. (a) PZ map with variable $kp\theta$ _sec. (b) PZ                                 |

| map with variable $ki\theta$ sec                                                                                                 |

| Figure 3-5 Pole-zero map for phase restoration. (a) Poles and zeros movement for phase                                           |

| synchronize. (b) poles and zeros movement for amplitude recovery64                                                               |

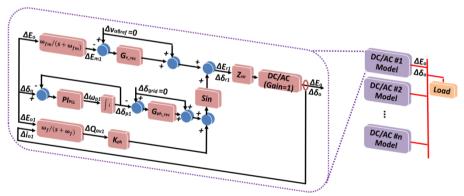

| Figure 3-6 Block diagram of the small-signal model for the proposed control65                                                    |

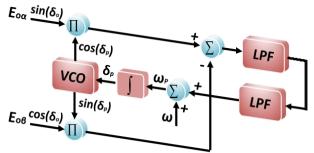

| Figure 3-7 Conventional PLL diagram69                                                                                            |

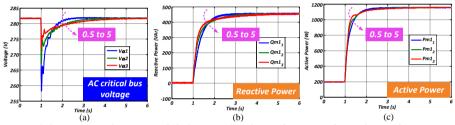

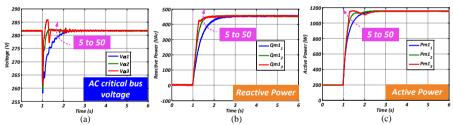

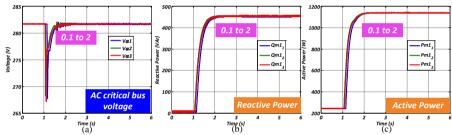

| Figure 3-8 System performance while $k_{pv\_sec}$ is 0.5, 2.5 and 5 (a) AC bus voltage. (b) Reactive                             |

| power. (c) Active power                                                                                                          |

| Figure 3-9 System performance while kiv_sec is 5, 20.5 and 50. (a) AC bus voltage. (b) Reactive                                  |

| power. (c) Active power                                                                                                          |

| Figure 3-10 Poles movements of the system. (a) $k_{pv\_sec}$ from 0.5 to 5. (b) ) $k_{iv\_sec}$ from 5 to 50.                    |

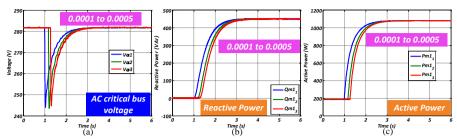

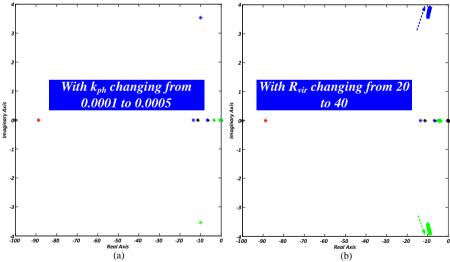

| Figure 3-11 System performance while kph is 0.0001, 0.0003 and 0.0005. (a) AC bus voltage.                                       |

| (b) Reactive power. (c) Active power                                                                                             |

| Figure 3-12 System performance while Rvir is 20, 30 and 40. (a) AC bus voltage. (b) Reactive                                     |

| power. (c) Active power                                                                                                          |

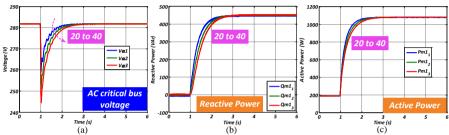

| Figure 3-13 Poles movements of the system. (a) $k_{ph}$ from 0.0001to 0.0005. (b) $R_{vir}$ from 20 to                           |

| 30                                                                                                                               |

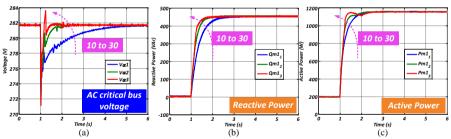

| Figure 3-14 System performance while $k_{p\theta}$ sec is 0.2, 1 and 2. (a) AC bus voltage. (b) Reactive                         |

| power. (c) Active power80                                                                                                        |

| Figure 3-15 System performance while $k_{i\theta}$ sec is 10, 20 and 30. (a) AC bus voltage. (b)                                 |

| Reactive power. (c) Active power                                                                                                 |

| Figure 3-16 Poles movements of the system. (a) $k_{p\theta}$ sec from 0.2 to 2. (b) ) $k_{i\theta}$ sec from 10 to 30.           |

|                                                                                                                                  |

| Figure 3-17 Synchronization process regarding different $k_{p\theta}$ sec and $k_{i\theta}$ sec. (a) $k_{i\theta}$ sec is 10, 20 |

| and 30. (b) ) $k_{p\theta}$ sec is 0.2, 1.2 and 2.2.                                                                             |

| Figure 4-1 Thermal model. (a) Power device model. (b) RC network of Z <sub>T/D(j-c)</sub> 83                                     |

| Figure 4-2 Path for zero sequence circulating current to flow                                                                    |

| Figure 4-3 Cycle and backup rules. (a) N module cycling and n rests. (b) N-1 module cycling.                                     |

| 85                                                                                                                               |

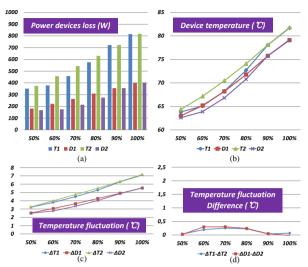

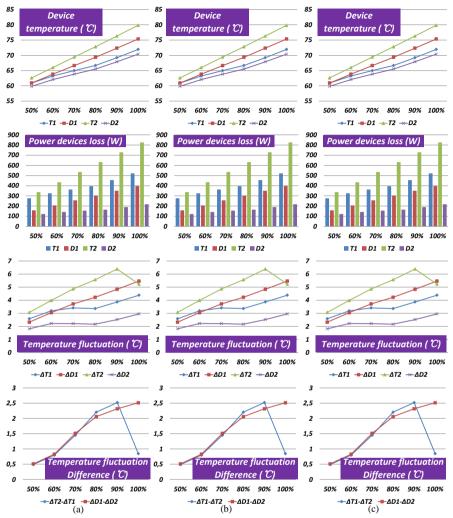

| Figure~4-4~Thermal~performance~of~single~module.~(a)~Devices~loss.~(b)~Devices~temperature.                                      |

| (c) Temperature fluctuation. (d) Temperature fluctuations differences87                                                          |

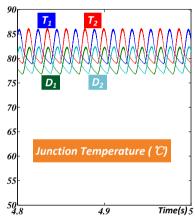

| Figure 4-5 Temperature details at 100% load condition87                                                                          |

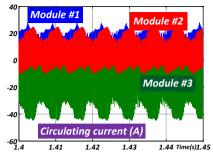

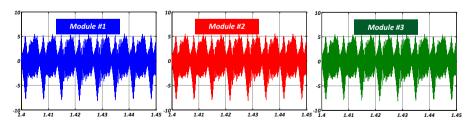

| Figure 4-6 Zero sequence circulating current without suppressing                                                                 |

| Figure~4-7~Thermal~performance~of~three~DC/AC~modules.~(a)~module~#1.~(b)~module~#2.~(c)                                         |

| <i>module #3.</i>                                                                                                                |

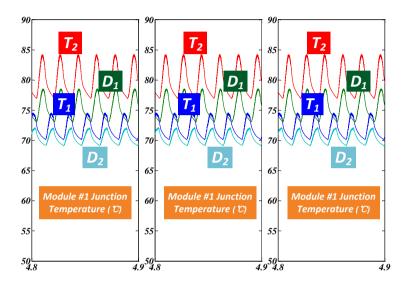

| Figure 4-8 Three DC/AC modules one leg devices temperature at 100% load condition89                                              |

| Figure 4-9 Zero sequence circulating current without suppressing89                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

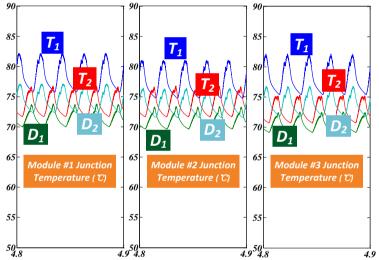

| Figure 4-10 Thermal performance with suppressing circulating current. Thermal                                                                    |

| performance of three DC/AC modules. (a) module #1. (b) module #2. (c) module #390                                                                |

| Figure 4-11 Three modules one leg devices temperature at 100% load condition with                                                                |

| suppressing9                                                                                                                                     |

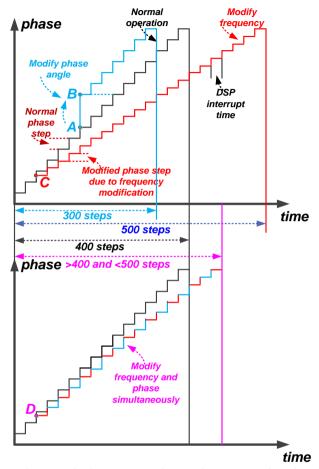

| Figure 5-1 Control process for frequency regulation, phase jump and combined methods9.                                                           |

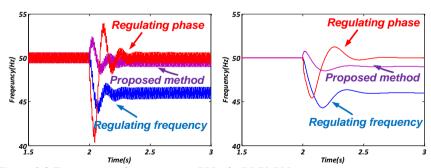

| Figure 5-2 Frequency performance. (a) pPLL. (b) SOGI-PLL94                                                                                       |

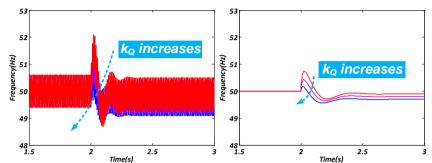

| Figure 5-3 Frequency performance with variable $k_Q$ . (a) pPLL. (b) SOGI-PLL9.                                                                  |

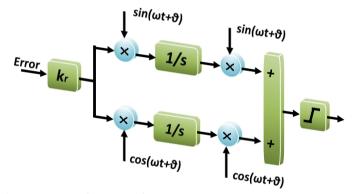

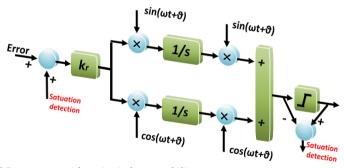

| Figure 5-4 Resonant part diagram with saturation9                                                                                                |

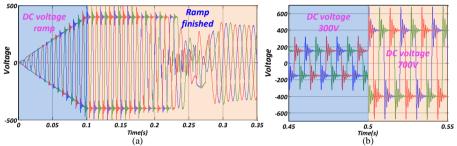

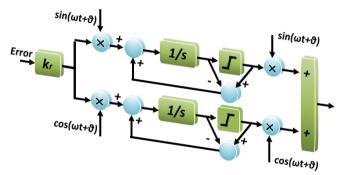

| Figure 5-5 Voltage performance without anti-windup. (a DC voltage ramp. (b) DC voltage                                                           |

| step90                                                                                                                                           |

| Figure 5-6 Resonators with anti-windup capability99                                                                                              |

| Figure 5-7 Voltage performance with anti-windup. (a) DC voltage ramp. (b) DC voltage step                                                        |

| Figure 5-8 Direct anti-windup for resonators. 9                                                                                                  |

| Figure 5-9 Voltage performance with direct anti-windup. (a) DC voltage ramp. (b) DO                                                              |

| voltage step                                                                                                                                     |

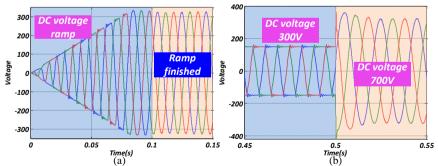

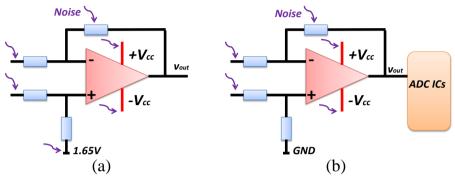

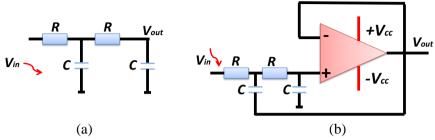

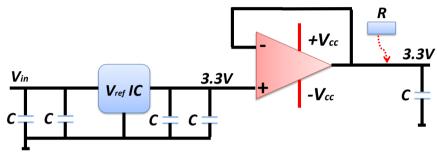

| Figure 5-10 AD hardware for voltage measurement. (a) single polar. (b) bi-polar90                                                                |

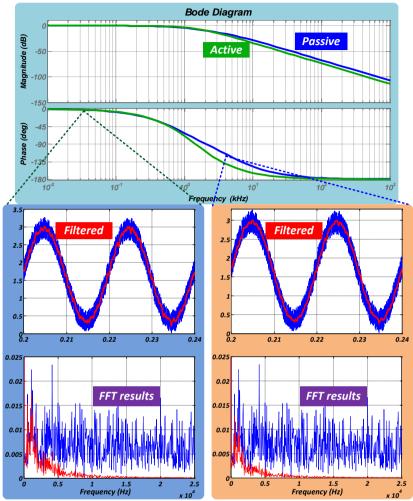

| Figure 5-11 Low pass filter for AD noise. (a) passive type. (b) active type (Sallen-Key)99                                                       |

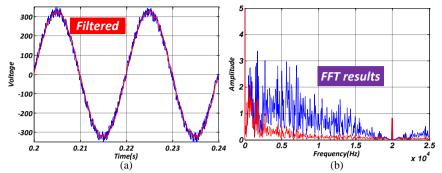

| Figure 5-12 Performance of both passive and active analog filter                                                                                 |

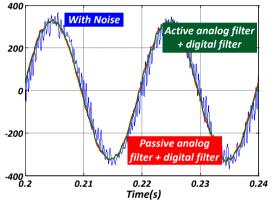

| Figure 5-13 Digital filter performance. (a) voltage before and after filtered. (b) FFT result                                                    |

| before and after filter                                                                                                                          |

| Figure 5-14 Output voltage performance with and without filtering                                                                                |

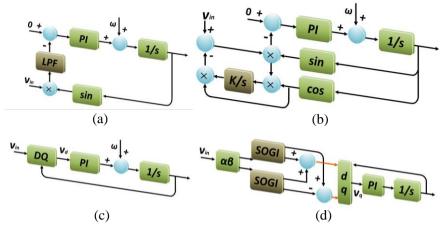

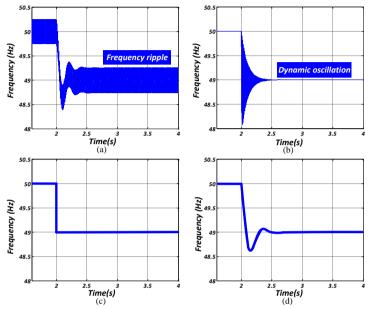

| Figure 5-15 Different PLL structure. (a) pPLL. (b) ePLL. (c) basic three phase PLL. (d)                                                          |

| SOGI-based PLL                                                                                                                                   |

| Figure 5-16 Different PLL dynamic performance in case of frequency jump. (a) pPLL. (b                                                            |

| ePLL. (c) basic three phase PLL. (d) SOGI-based PLL                                                                                              |

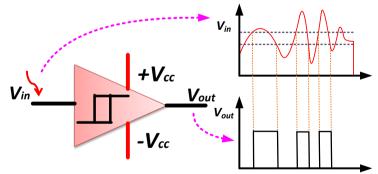

| Figure 5-17 Schmitt function                                                                                                                     |

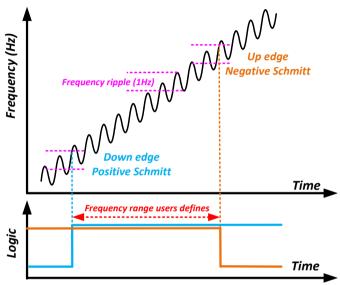

| Figure 5-18 Schmitt mechanic in PLL                                                                                                              |

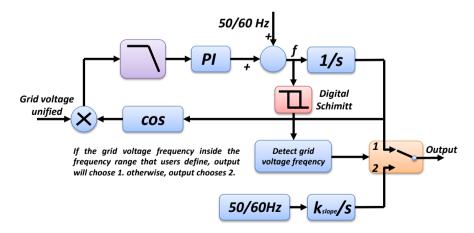

| Figure 5-19 Final PLL structure based on p-PLL.                                                                                                  |

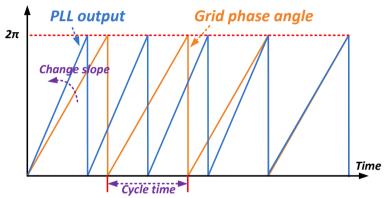

| Figure 5-20 Transient mechanics between output 1 and 2 of PLL                                                                                    |

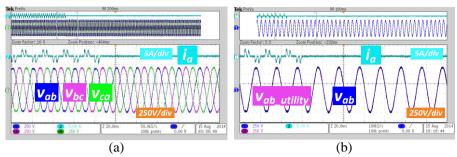

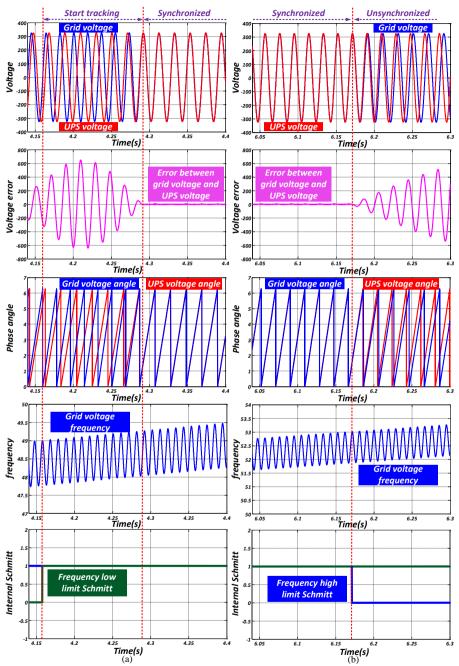

| Figure 5-21 Proposed PLL performance. (a) performance from unsynchronized to                                                                     |

| synchronized condition. (b) performance of exiting synchronized                                                                                  |

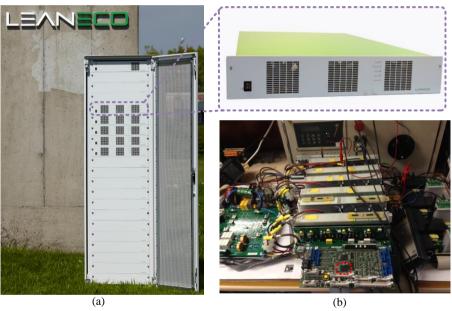

| Figure 5-22 Final prototype of UPS module. (a) UPS module in Leaneco. (b) UPS module is                                                          |

| Salicru                                                                                                                                          |

| Figure 5-23 Power supply for the ADC part of DSP. 100                                                                                            |

| Figure 5-24 Output voltage performance. (a) output voltage in case of self-excited. (b) output                                                   |

| voltage after improved                                                                                                                           |

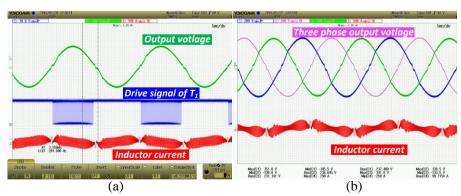

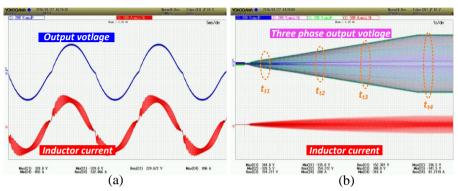

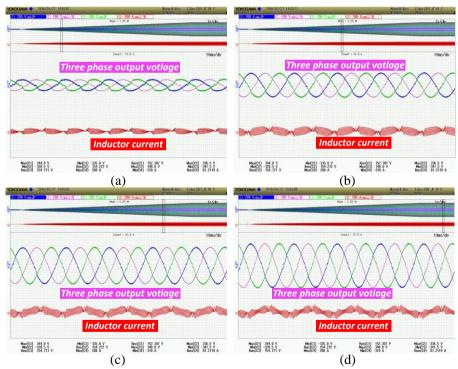

| Figure 5-25 Test performance. (a) full load. (b) soft-start process. 10                                                                          |

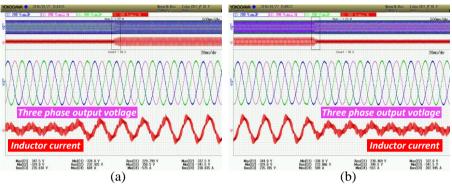

| Figure 5-26 Soft-start details. (a) details at t <sub>11</sub> . (b) details at t <sub>12</sub> . (c) details at t <sub>13</sub> . (d) details a |

| Figure 3-20 Soji-start detaits. (a) detaits at $t_{12}$ . (b) detaits at $t_{12}$ . (c) detaits at $t_{13}$ . (d) detaits at $t_{14}$            |

| Figure 5-27 Load step test. (a) load step up. (b) load step down.                                                                                |

| Figure 5-27 Load step test. (a) toda step up. (b) toda step down                                                                                 |

### **LIST OF TABLES**

| Table 2-1. THD Analysis results                                | 45 |

|----------------------------------------------------------------|----|

| Table 2-2. AC critical bus voltage and UPS output current THD. |    |

| Table 4-1. DC/AC electrical information                        | 84 |

| Table 4-2. IGBT pack thermal information                       | 84 |

# PART I THESIS REPORT MAIN CONTENT

Part I is the main content for the Ph. D thesis. It is a collection of the published paper. It gives a detailed presentation, explanation of the Ph. D project.

The main content of the thesis report is based on the papers that the author had published in the international journals, conferences and the work in the company.

The relationship between thesis report and published papers, collaborative work in a Spanish UPS company, Salicru S/A is shown in the following table. And the in the main content, the relationship is marked detailed in each chapter.

| Chapters | Relevant publications                                       |

|----------|-------------------------------------------------------------|

| 1        |                                                             |

| 2        | A1, A3, A4, A5, A6, A8                                      |

| 3        | A2, A3                                                      |

| 4        | A7                                                          |

| 5        | collaborative work in a Spanish<br>UPS company, Salicru S/A |

| 6        |                                                             |

### **CHAPTER 1. INTRODUCTION**

This chapter gives the background, motivation and organization of my Ph. D work. The state-of-art of uninterruptible power supply (UPS) system is illustrated as well as the existing products of modern modular UPS system. Finally, the structure of the thesis is presented given in details.

### 1.1. STATE OF ART OF UNINTERRUPTIBLE POWER SUPPLY SYSTEMS

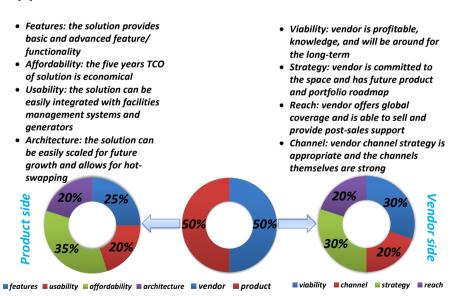

The booming development of the modern electronic devices, such as data center, mobile base station, among others, is emerging in human being's everyday life [1]. Normally such kind of loads either is distributed widely across a big area or requires continuous reliable energy supply. As a consequence, UPS system is receiving more and more attention from both vendors and consumers. On the other hand, continuing demand from the downstream refining and petrochemicals, upstream oil & gas, mining industries and investments in automation to raise productivity, flexibility, and address regulatory and safety needs will also drive the demand for the industrial UPS equipment [2]. For the evaluation of UPS products, vendor and product side evaluation share the same importance as shown in Figure 1-1 [3].

Figure 1-1 UPS products evaluation criteria.

It can be seen that from the point view of product side, affordability is the most important factor that users consider. Then it is the features of the UPS product. Outstanding performance, user friendly interface and excellent reliability are all quite attractive for users. So it means that performance and cost is the most important two elements for a competitive UPS product. On the other hand, from the point view of vendor side, viability and strategy share the same percentage regarding the evaluation of UPS products.

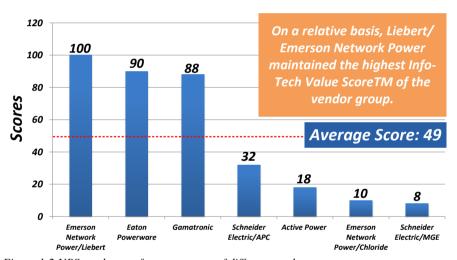

In the market, there are various kinds of manufactures, such as Emerson Network Power, Eaton Powerware, Gamatronic, Schneider, Active Power among others, which provide different kinds of UPS equipment in different power rate. In Figure 1-2, market performance of different UPS vendors is shown [3]. It can be seen that different vendors are against Liebert/Emerson Network Power's product performance to provide a complete relative view of their product offerings.

Figure 1-2 UPS product performance score of different vendors.

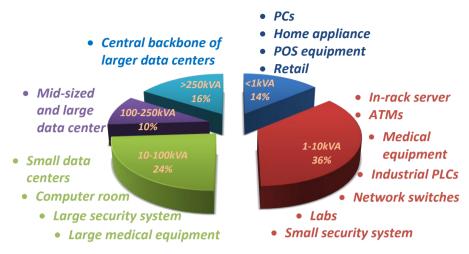

In addition to the rapid growth and improved performance of different UPS products, the power rate of the UPS products is also increasing actively. Different power rate, namely 0.5-1kVA, 1-5kVA, 5-10kVA, 10-20kVA, 20-100kVA and >100kVA, can be found in the market [4] as shown in Figure 1-3. Recently, power rate tends to increase to several mega-watts since the modern loads are become more and more integrated. For instance, data centers for IT purpose or financial purpose requires a reliable, continuous and a higher power rate supplier. On the other hand, modularization is another trend since it is more flexible and easy to be integrated. Furthermore, modularized system structure also provides a lower difficulty for system repair or maintenance. Modules can be removed or inserted into the power supply system in a safer, more reliable and less difficult way.

Figure 1-3 Global UPS market and typical applications.

### 1.2. UPS SYSTEM ARCHITECTURES

### 1.2.1. THREE TYPES OF CONVENTIONAL UPS SYSTEM ARCHITECTURES

On the basis of the International Electrotechnical Commission Standard 62040-3, three basic categories can be found, namely offline UPS [5], [6], line interactive UPS [7]-[10] and online UPS [11], [12] based on the energy flow direction in different operating conditions. In the following sub-sections, each kind of UPS system architectures will be analyzed.

### 1.2.1.1 Offline UPS system

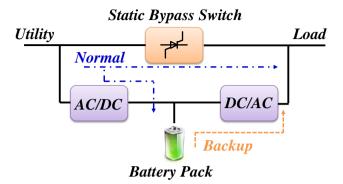

Figure 1-4 shows a conventional offline type UPS. Normally, offline UPS module is rated below 2kVA [5]. It is composed of AC/DC, DC/AC, battery pack and static bypass switch (SCR). If the utility is in good condition, energy will flow through the SCR and support the load directly. Nevertheless, SCR will be open and battery pack will be started and transfer energy to load. When battery pack uses up its energy, AC/DC will start to charge the battery and support the load at the same time. It can be seen that offline UPS doesn't provide any isolation between the utility and the loads. As a result, any utility distortion will affect the load directly. This puts a higher requirement on the protection of loads. In some specific application scenarios, passive filter is used to reduce this kind of impact, such as voltage spikes, sags or oscillations [11].

Figure 1-4 Offline UPS system.

Figure 1-5 Line interactive UPS system.

### 1.2.1.2 Line interactive UPS system

Figure 1-5 presents a typical line-interactive UPS system. Normally, it operates in medium power rate application. The operating rule is a little bit different than the offline UPS system. The AC/DC, DC/AC and battery pack works together not only as a power supporter but also as a compensation loop. For instance, the AC/DC can suppress the utility voltage distortion through the series transformer [7], [8]. On the other hand, the PFC function can be also achieved [9]. Since the loads are supported by the two energy paths at the same time, thus DC/AC only provide around 10%-20% of the total load power, which means a higher efficiency [10]. However, the control structures for AC/DC and DC/AC are different and complex. Operating modes transient process will happen during the UPS operation. On the other hand, the line series transformer will increase the cost and volume of the UPS system. Nowadays, it is difficult for vendors to accept a higher cost and lower reliability. At the same time, the DC/AC can inject active power into the load to regulate the power factor. Such kind of the equipment is called unified power quality compensator (UPQC).

### 1.2.1.3 Online UPS system

Online UPS system, also known as inverter preferred UPS or double conversion UPS, is more popular due to its outstanding regulation ability on power quality [11]. It is designed for higher power rate application scenarios. Its good decoupling ability of the utility and the load under power outage is another reason that makes it attractive for consumers [12].

As shown in Figure 1-6, a typical online UPS module is composed of a double conversion stage structure and a static bypass switch. However, the static bypass switch is not the main role of transferring power. The AC/DC, battery and DC/AC will take the role of regulating power. Only in some emergency conditions, the static bypass switch will be activated.

In Figure 1-6, a conventional online UPS system is shown. Under utility normal condition, the utility power is regulated through the two stage converter and injected into the load while AC/DC also acts the charger for the battery pack. Once the utility errors occur, system enters backup mode and battery pack starts to regulate system output power. Furthermore, static bypass will be turned on in event of power conditioner failure [11]. By removing the series transformer, online UPS system is cost-effective and weight-effective.

Figure 1-6 Line interactive UPS system.

It can be seen that this structure is more direct on power regulating without any galvanic isolation or transformers. AC/DC is responsible for the harmonic controlling of the utility side while DC/AC modules are regulating the output voltage quality of the system. Normally, the required load power will regulate a two stage system and then transferred to the load. Although it may have a larger amount of losses, its outstanding power regulating capability makes it more attractive. Similarly, it has a lower controllability on the battery power management.

### 1.2.2. EVOLUTION OF ONLINE UPS SYSTEM ARCHITECTURE

Since the online UPS system is aimed at high power and voltage application scenarios, a series of improved online UPS structure have been proposed in [13]-[22], which are better at regulating active power consumption to achieve unity power factor. Additional DC/DC [13]-[17] and high frequency transformer [18]-[21] are the two main issues that are chosen to achieve a cost-effective, volume-effective and more reliable online UPS system.

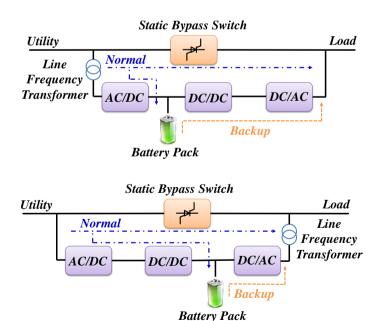

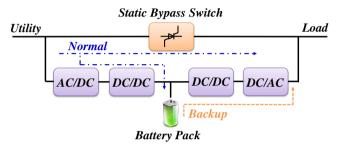

### 1.2.2.1 Half transformer-less online UPS system

In half transformer-less online UPS as shown in Figure 1-7, one additional DC/DC is inserted into the system to improve power quality [13], [14] and the controllability on battery pack in the system. On the other hand, a lower DC bus voltage is achieved, which indicates fewer battery packs in series and higher safety. However, input or output line frequency transformer still decrease system's efficiency and lead to more current stress on converters [15]. On the other hand, the system becomes three stages at least, which means a lower overall efficiency of the whole system. The cascaded converter structure also requires more efforts on the converter design. Converter type load impedance feature is a constant power type, which is a negative resistive type. From the point of control side, such kind of load is easy to trig the instability of the system.

Figure 1-7 Half transformer-less online UPS system.

### 1.2.2.2 Total transformer-less online UPS system

By adding one more DC/DC, a total transformer-less online UPS system is proposed as shown in Figure 1-8 Nevertheless, there is no galvanic isolation issue in the system. The controllability of the system on the battery pack is enhanced furthermore, which will contribute to a longer life for the battery. At the same time, the control burden on the AC/DC is reduced since the DC/DC will take charge part of the task to regulate power. Moreover, DC bus voltage can be reduced in a large scale meaning that fewer battery units and a higher system safety issue can be achieved. Similarly, the cascaded converter structure requires more efforts on designing and maintaining the overall system stability.

Figure 1-8 Total transformer-less online UPS system.

Figure 1-9 High frequency transformer online UPS system.

### 1.2.2.3 High frequency transformer online UPS system

In [18]-[22], improved online UPS systems with high frequency transformer were presented as shown in Figure 1-9. High frequency transformer guarantees the galvanic isolation between battery, input and output as well as the reduction of volume and weight. Since it is a similar topology as solid state transformer, it can act as a multi-functional interface equipment for AC system and DC system. However, more problems will occur due to the high frequency transformer, such as noise and reliability issues. Specific attention should be paid more attention to the design of such kind of transformers.

### 1.2.3. POWER ELECTRONIC TOPOLOGIES IN A UPS SYSTEM

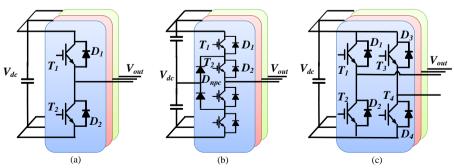

### 1.2.3.1 Topology for DC/AC stage

Figure 1-10 presents three types of the most frequently used DC/AC topologies in UPS system. Three phase half-bridge (3P-HB), as one of the most conventional DC/AC topologies, is shown in Figure 1-10(a). It is easy to design. But the DC voltage utilization efficiency is low, which increase the cost of the DC link capacitor. Due to the manufacture process of DC link electrolytic capacitor, the price will be increased exponential to its volume [23].

Thus three-level neutral-point diode-clamped topology (3L-NPC) is proposed as shown in Figure 1-10(b). Smaller size DC link capacitors are required. However, the midpoint voltage level fluctuation becomes a major concern regarding the converter performance, which must be paid specific attention [24]. On the other hand, the loss distribution in one arm is unbalanced, *ie*  $T_1$  has smaller conduction loss than  $T_2$  while it has higher switch loss than  $T_2$ . This may lead to an ineffective utilization of the power semiconductor devices as well as the heat sink for the converter [26]. Also the freewheeling diode  $D_{npc}$  is also an important element. SiC devices or outstanding snubner circuit is the possible issues that will be used to solve this problem.

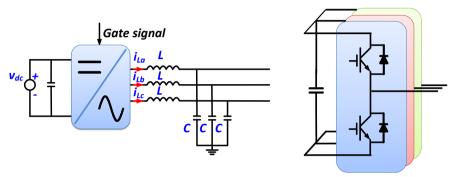

Figure 1-10 Power electronic topologies for DC/AC. (a) 3P-HB (b) 3L-NPC (c) 3P-FB.

The three phase full bridge (3P-FB) shown in Figure 1-10(c) could be another choice for the DC/AC on the online UPS system. Without clamped diodes, it can also achieve three level output [27]. Moreover, 3 phases can work in a flexible and independent way. However, more devices are used and large filter size, losses are major drawbacks. On the other hand, it also provides possible paths for potential zero sequence circulating current to flow [28], [29], which will affect the performance in a negative way.

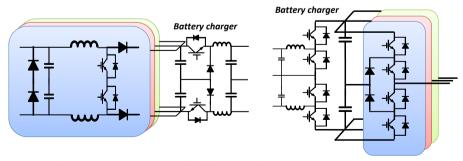

### 1.2.3.2 Topology for AC/DC stage

Apart from the topology shown in Figure 1-10(a) and (b), two topologies in Figure 1-11 shown that it could be the suitable selection for AC/DC stage. Vienna rectifier is widely used due to its control simplicity [30]. Nevertheless, it is single direction power flow. In some low power application scenarios, the battery charger is also integrated with the AD/DC stage as shown in Figure 1-12 based on interleaved buck/boost [31]. An auxiliary circuit, which is made up of conventional Buck, is inserted. Thus the AC/DC stage is responsible for not only rectifier but also the battery charge and discharge. This simplifies the control the whole UPS system.

Figure 1-11 Power electronic topologies for AC/DC. (a) Vienna rectifier. (b) 3L-4P-HB.

Figure 1-12 AC/DC stage integrated with battery charger.

Figure 1-13 Transient duration requirements for online UPS system. (a) Limit for mode change. (b) Limit for linear load change. (c) Limit for nonlinear load change.

### 1.3. MODULAR ONLINE UPS SYSTEM AND CHALLENGES

The main challenge in the system is the parallel technology for the modules and the modules plug in and out performance of the UPS system. The most popular is the one which is being used as the Master-slave type based on control area network (CAN) bus network. Each module is tightly controlled and synchronized with the support of CAN bus. However, such kind of system depends too much on the communication issues. Once communication fails, the synchronization between modules will be lost and the power is uncontrollable. On the other hand, there is also another important thing that should be considered. It is the Master decision rules in the system. Since there is always only one Master in the system, the system

is required to choose another Master automatically once the Master fails in a fast, smooth way. This will put more challenge on the system supervisor. Apart from UPS output voltage shape quality, the dynamic time while the system is choosing Master is tightly limited and the output voltage overshoot or sags must follow the IEC 62040-3 [32], which is shown in Figure 1-13.

For different operation scenarios, different requirements are presented. Normally Figure 1-13(a) is accepted by sensitive critical load while Figure 1-13(b) is applicable to most types of critical load. And Figure 1-13(c) is accepted by general purpose IT loads. It can be seen that the voltage shoot or sags and the duration time limit are in inverse proportion. No matter what kind of operation the system is doing, if the voltage overshoot or sags can be limit to a small value, for instance 10%, the duration time can be between 10*ms* and 1000*ms*, which means that a longer dynamic performance can be accepted by different appliances.

For a modular UPS system, another one of the most challengeable operations is the module "hot-swap" operation. When the module just starts and plug into the system, it will present as a nonlinear load behavior that will make the output current for the other modules become distorted. And UPS output voltage will be affected and distorted. In case of any module plugging out of the system, the rest modules may suffer from the possibility of overload power or under-voltage sags. Thus the control for the system should have the capability supporting such kind of conditions.

On the other hand, active and reactive power sharing is another critical issue that should be taken into account. Any kind of circulating current of will decrease the system efficiency and harm converter. This is the reason why, both zero-sequence circulating current and power circulating should be considered. A higher accurate power sharing performance should be achieved with the help of simplified control algorithms. Due to the cost limitation, complex control will increase the hardware resource requirement for the digital controller used in the system.

Additionally, the modular UPS system should also have the capability of being immune to failure condition. It means that when some specific control issues in the system fail, the system control could also support the load continuously without losing all the required performance and wait for the orders from supervisor or users. Once everything is back to normal condition, it can be moved back to the right control path.

#### 1.4. SCOPE OF THE THESIS

The objective of this Ph. D project is to investigate advanced control architectures in high power modular online UPS systems, which aims at higher power level. Simplified control methods achieving active and reactive power sharing at any load

condition, mathematical models and also thermal analysis will be investigated in order to evaluate the performance of the whole system. In conjunction with this Ph. D project, a modular online UPS system will be developed.

### 1.5. OUTLINE OF THE THESIS

The Ph. D thesis is a collection of papers that had been published and is mainly consisting of two parts – the thesis report in Part I and attached paper in Part II. Eight papers are given to support the theoretical analysis in the thesis. The report is made up of six chapters, which is illustrated as follows:

Chapter 1 gives the introduction, motivation and background of the Ph. D project.

Chapter 2 depicts the existing control methods for the modular online UPS system and discusses improved control methods, which are validated through simulation and experimental results.

In Chapter 3, the mathematical model of the system is presented from the perspective of single module and parallel system. On the other hand, by using the experimental data obtained from the experimental setup, the parallel system stability is analyzed together with the proposed small signal mathematical model.

Chapter 4 gives the thermal stress analysis considering the circulating current flowing among the modules. The two conditions – large circulating current and suppressed circulating current, are investigated respectively. The loss and temperature performance of different switches in each leg is also presented.

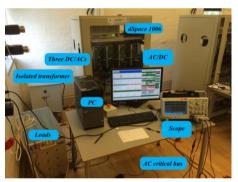

In Chapter 5, experimental validation in a real product development is presented regarding digital control implementation, hardware design issues, and final prototype tests. The results from the final prototypes are presented.

In Chapter 6, conclusion and future works are presented.

The attached 8 papers are listed as follows:

- [A1] Chi Zhang, J. M. Guerrero, J. C. Vasquez, C. Seniger, "Modular Plug'n'Play Control Architectures for Three-phase Inverters in UPS Applications," *IEEE Trans. Ind. Appl.*, vol. 52, no. 3, pp. 2405-2414, May-June 2016.

- [A2] **Chi Zhang**, E. Coelho, J. Guerrero; J. C. Vasquez, "Modular Online Uninterruptible Power System Plug'n'Play Control and Stability Analysis," *IEEE Trans. Ind. Electron*, vol. 63, no. 6, pp. 3765-3776, June 2016.

- [A3] Chi Zhang, J. M. Guerrero, J. C. Vasquez and E. A. A. Coelho, "Control Architecture for Parallel-Connected Inverters in Uninterruptible Power Systems," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 5176-5188, July 2016.

- [A4] **Chi Zhang**, J. M. Guerrero and J. C. Vasquez, "A simplified control architecture for three-phase inverters in modular UPS application with shunt active power filter embedded," *Power Electronics and ECCE Asia* (ICPE-ECCE Asia), 2015 9th International Conference on, Seoul, 2015, pp. 413-420.

- [A5] **Chi Zhang**, J. M. Guerrero, J. C. Vasquez, E. A. Coelho and C. Seniger, "High-performance control of paralleled three-phase inverters for residential microgrid architectures based on online uninterruptable power systems," *Applied Power Electronics Conference and Exposition (APEC)*, 2015 IEEE, Charlotte, NC, 2015, pp. 3232-3239.

- [A6] **Chi Zhang**, J. M. Guerrero, J. C. Vasquez and C. Seniger, "Modular Plug'n'Play control architectures for three-phase inverters in UPS applications," *Power Electronics and ECCE Asia (ICPE-ECCE Asia)*, 2015 9th International Conference on, Seoul, 2015, pp. 659-666.

- [A7] **Chi Zhang**, J. M. Guerrero and J. C. Vasquez, "Thermal impact analysis of circulating current in high power modular online uninterruptible power supplies application," *Power Electronics and Applications (EPE'15 ECCE-Europe)*, 2015 17th European Conference on, Geneva, 2015, pp. 1-10.

- [A8] Chi Zhang, T. Dragicevic, J. C. Vasquez and J. M. Guerrero, "Resonance damping techniques for grid-connected voltage source converters with LCL filters — A review," *Energy Conference (ENERGYCON)*, 2014 IEEE International, Cavtat, 2014, pp. 169-176.

# CHAPTER 2. CONTROL STRATEGIES FOR MODULAR ONLINE UPS SYSTEM

In this chapter, several existing control strategies are discussed. Regarding the drawbacks of these conventional control methods, some improved control methods are derived in order to obtain an enhanced system performance.

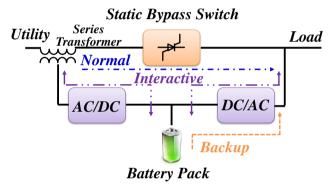

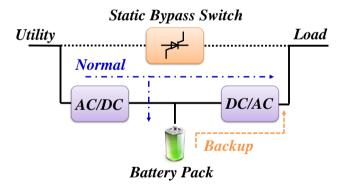

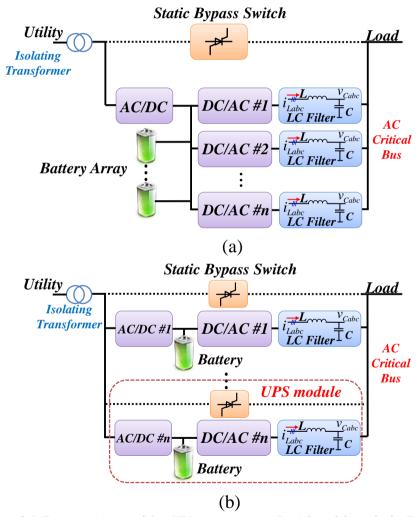

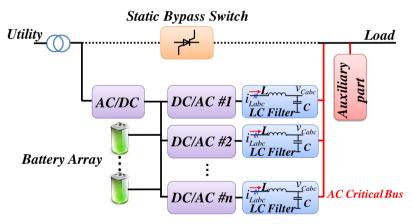

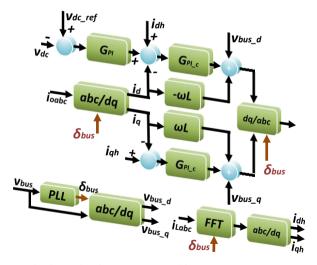

Figure 2-1 Two promising modular UPS structures. (a) Partial modularized. (b) Total modularized.

# 2.1. TWO PROMISING STRUCTURES FOR ONLINE UPS SYSTEMS

In order to achieve a more flexible and easy-use system, a novel structure is used, which is shown in Figure 2-1. It can be seen that there are two basic modular structures. In Figure 2-1 (a), only the DC/AC side is modularized with one common grid-connected AC/DC. It is more convenient to control such kind of structure because only parallel issue for the DC/AC modules is required to be taken into consideration. However, the power rate for AC/DC modules will be increased and a larger battery pack will be needed to support the whole system. On the other hand, with DC/AC modules plugging in or out of the system, the capacitance on the DC bus bar will be changing all the time, which will give a heavy working burden to the AC/DC. Additionally, since all the DC/AC modules share the same DC and AC bus, it is possible to have zero-sequence circulating current in the system. In Figure 2-1(b), another kind of modular structure is proposed. Hereby, UPS modularized is used to increase the system flexibility. Each module is a small fully functional UPS structure. Thus each module can work totally independent. Nevertheless, this system will have a quite complex and challenge in bypass process. In other words, it can be concluded that no matter what kind of modular structure is used, parallel control technology is essential in the whole system operation. Here the structure in Figure 2-1(a) is further discussed since the other one is being used in a real industrial product.

#### 2.2. CONTROL FOR MODULAR ONLINE UPS SYSTEM

Different from conventional UPS system, modular UPS system adopts several modules to work in parallel instead of using only one DC/AC module. Consequently, how to parallel numbers of DC/AC modules becomes a challenge. Until now, numbers of parallel technologies have been proposed, which can be categorized into three types, namely communication based (CB) [33]-[47], droop based (DB) [48]-[62] and hybrid based (HB) [63]-[74].

CB methods are based on using the communication line between different DC/AC modules. Since CB depends on the communication network performance, reliability issues are receiving more and more challenge. As a result, DB methods are proposed. Parallel DC/AC modules can be simplified represented by a simple model as shown in Figure 2-2. Thus active power and reactive power that each module injects to the load can be determined by the output voltage amplitude and phase. In [60], it mentioned that if the  $Z_L$  is inductive, the active power can be regulated by the voltage phase angle or frequency and the reactive power is regulated by the voltage amplitude. Nevertheless, the active power is regulated by the voltage amplitude and reactive power is regulated by the voltage phase angle or frequency if the line impedance is resistive.

Figure 2-2 Simplified model for DC/AC parallel modules.

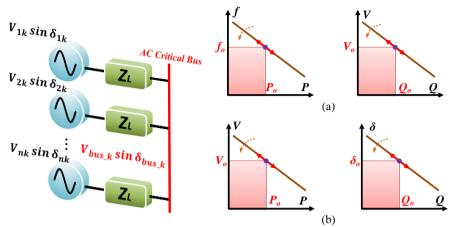

Figure 2-3 (a) Inductive condition. (b) resistive condition.

Thus output voltage amplitude, phase angle or frequency are always regulated and have deviations with the given reference as shown in Figure 2-3. Consequently, AC critical bus voltage becomes load dependent. With higher load power, the AC critical bus voltage amplitude, phase angle or frequency will be changed to a non-reference value. Since there are standards that propose specific requirements for UPS system output voltage amplitude, phase angle or frequency performance, it should be paid especial attention while designing the system parameters. Thus a higher level controller is required to recover the voltage amplitude, phase angle or frequency [63].

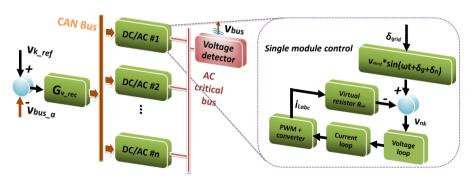

By combing CB with DB, hybrid methods are proposed as a multi-level controller structure. DB methods are employed to guarantee the DC/AC modules working in parallel and sharing the load power in an equal way. Since the DB methods will bring voltage amplitude, frequency or phase deviation to the DC/AC modules, CB are used to recover the output voltage by modifying the voltage references for DC/AC modules and broadcasting these values to each of the modules through the communication network. Normally CAN bus communication network is used since mature DSP technology has provided a time-saving and reliable communication technology for the CAN bus. On the other hand, the communication function can be integrated with the module control in a single DSP chip.

#### 2.3. PROPOSED CONTROLS FOR MODULAR ONLINE SYSTEM

#### 2.3.1. BASIC PARALLEL CONTROL [PUBLICATION A3, A5]

Conventional hybrid based methods are designed based on the fact that the line impedance is designed to be mainly inductive. Thus active power can be regulated by the system frequency and reactive power is controlled by the output voltage amplitude as shown in Figure 2-3(a). However, with such kind of method, the UPS system frequency is fluctuated, which is an undesired condition for an online UPS system because the changeable frequency will have negative impact the online UPS system bypass process. On the other hand, both active power and reactive power are required to be calculated in order to achieve the control. This means that a complex control architecture is mandatory for the system. In order to simply the control, virtual impedance [75]-[80] concept is introduced to replace the real inductive line impedance. Thus DC/AC module output impedance can be designed manually to be mainly inductive.

As a consequence, similar idea is used. Through changing the virtual impedance to be resistive, thus output impedance of DC/AC module can be forced to be designed as resistive. In this condition, the DC/AC module output power can be controlled in a different way, as shown in Figure 2-3(b), ie active power is related to the amplitude while the reactive power is concerned by the phase angle for frequency. Considering the fact that a variation in the system frequency is not desired for the bypass process for the online UPS system, phase signal is chosen to regulate the DC/AC module output reactive power. Since the phase angle is obtained from the phase lock loop (PLL), the phase angel is tightly related with the frequency. Thus during the time that control starts to modify the phase angle, the system frequency will be jumped suddenly and move back to nominal value afterwards, which is called "Q– $\phi$ " control.

Based on Figure 2-2, DC/AC module output power can be derived as

$$P_{nk} = \frac{V_{nk}V_{bus\_k}}{R_{...}}\cos(\delta_{nk} - \delta_{bus\_k}) - \frac{V_{bus\_k}^{2}}{R_{...}}$$

(2-1)

$$Q_{nk} = -\frac{V_{nk}V_{bus\_k}}{R_{vir}}\sin(\delta_{nk} - \delta_{bus\_k})$$

(2-2)

being  $P_{nk}$  and  $Q_{nk}$  the active and reactive power injected by the module n in phase k,  $V_{nk}$  voltage value of the module n in phase k,  $\delta_{nk}$  module n phase k angle information,  $V_{bus\_k}$  the critical bus phase k voltage, and  $\delta_{bus\_k}$  the critical bus phase k

phase information. In real application scenarios, the phase angle difference ( $\delta_{nk}$ - $\delta_{bus\_k}$ ) between DC/AC module and AC critical bus is quite small. So it can be treated as zero. Thus the two equations are rewritten as following,

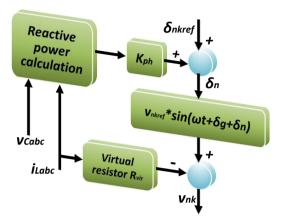

Figure 2-4 Virtual impedance and " $Q-\phi$ " control diagram.

$$P_{nk} \approx \frac{V_{bus\_k}}{R_{vir}} \left( V_{nk} - V_{bus\_k} \right) \tag{2-3}$$

$$Q_{nk} \approx -\frac{V_{nk}V_{bus\_k}}{R_{vir}}(\delta_{nk} - \delta_{bus\_k})$$

(2-4)

From the equations above, it can be concluded that the output active power of the DC/AC module can be estimated by the output voltage amplitude while phase angle can be used to regulate the output reactive power of DC/AC modules. By using the virtual impedance (resistive), inductor current will be used to regulate the voltage amplitude. Consequently, the output active power can be controlled. The proposed control architecture is shown in Figure 2-4,

$$V_{nk} = V_{nkref} \sin\left(\omega t + \delta_g + \delta_n\right) - R_{vir} i_{nLabc}$$

(2-5)

$$\delta_n = \delta_{nkref} + k_{ph} Q_{nk} \tag{2-6}$$

Here n is DC/AC module sequence number, k is the phase order,  $V_{nkref}$  is phase k reference voltage,  $R_{vir}$  is virtual resistor value,  $\delta_g$  is the grid phase information,  $\delta_{nkref}$  is module n phase k phase reference,  $k_{ph}$  is  $Q-\phi$  coefficients, and  $Q_{nk}$  is module n phase k reactive power. The inner loop for each DC/AC module use the

conventional double loop structure (voltage and current loop), which uses two typical *PR* controllers due to its capability of suppressing harmonics [81]-[85],

$$G_{v}(s) = k_{pv} + \frac{k_{rv}s}{s^{2} + \omega_{o}^{2}} + \sum_{h=5,7} \frac{k_{hrv}s}{s^{2} + (\omega_{o}h)^{2}}$$

(2-7)

$$G_c(s) = k_{pc} + \frac{k_{rc}s}{s^2 + \omega_o^2} + \sum_{h=5,7} \frac{k_{hrc}s}{s^2 + (\omega_o h)^2}$$

(2-8)

being  $k_{pv}$ ,  $k_{rv}$  the basic voltage loop PR controller parameter,  $\omega_o$  the  $2*\pi*50$  rad/s,  $k_{hrv}$  the compensation term for  $h^{th}$  harmonic, h the harmonic number,  $k_{pc}$ ,  $k_{rc}$  the basic current loop PR controller parameter, and  $k_{hrc}$  the  $h^{th}$  harmonic current compensation value.

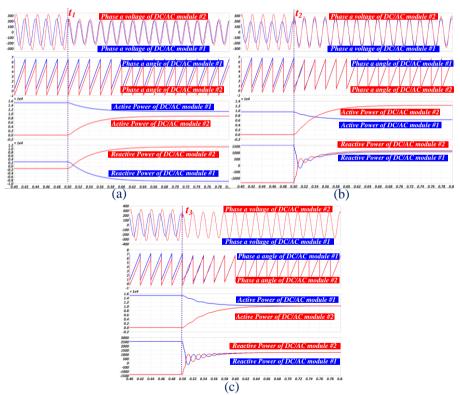

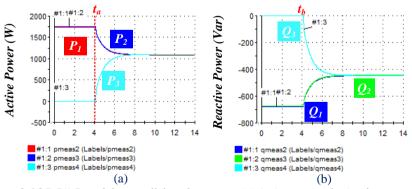

Figure 2-5 Active and reactive power sharing transient process. (a) only virtual impedance (kph=0). (b) only  $Q-\phi$  loops (Rvir=0). (c) using both virtual impedance and  $Q-\phi$  loops.

With the help of the simulation software PLECS, a basic parallel system composed of two DC/AC modules was established to verify the proposed control mechanism. The results are presented in Figure 2-5. In Figure 2-5, the result was obtained by disabling reactive power regulation,  $ie \ k_{ph}$  is set to 0. Although the virtual impedance part intends to make two DC/AC modules output active power be convergent to the same value, there are still some static errors due to the initial given phase angle difference. DC/AC module #1 gives higher output active power that DC/AC module #2 and this means that DC/AC module #2 output voltage amplitude is larger than #1 based on (2-5). Then (2-6) is enabled, two modules output voltage amplitude is controlled further until they reach the same value by modifying phase angle, ie DC/AC module reactive power. On the other hand, the phase angle difference between two DC/AC modules is moved to the same value, which contributes to reactive power equally sharing as shown in Figure 2-5(c).

Moreover, virtual impedance part is disabled and the Q– $\phi$  takes the roles of parallel two DC/AC modules. The test result is shown in Figure 2-5(b). The phase angle difference is eliminated to zero, which force two modules output reactive power move to the same value. Nevertheless, due to the output voltage amplitude deviations, the reactive power is not well shared. By applying (2-5), the voltage amplitude is regulated to the same value. And both active power and reactive power are well shared between two DC/AC modules as shown in Figure 2-5(c).

## 2.3.2. VOLTAGE AMPLITUDE RECOVERING AND PHASE ANGLE SYNCHRONIZATION [PUBLICATION A1-6]

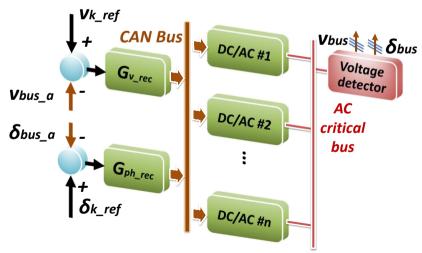

Due to the existence of virtual resistor, AC critical bus voltage amplitude, which is made up of several DC/AC modules output voltage, will have voltage drop compared with reference value. Moreover, reactive power regulation will generate a phase shift on the AC critical bus voltage. Thus voltage amplitude recovery and phase angle reduction and synchronization should be taken into account. There are two kinds of control strategies considered here – Average Type and Simple Type.

#### 2.3.2.1 Average Type [Publication A3, A5]

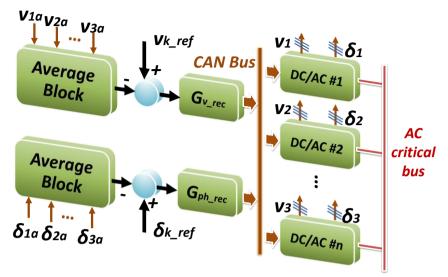

Average type utilizes the average information of voltage, phase of different DC/AC modules as the feedback information for recovery. Through the CAN bus network, each DC/AC module will broadcast its own voltage amplitude information and phase angle value to the recovery control part.

For the voltage amplitude recovery, when all DC/AC modules output voltage amplitude is received, the averaged value will be calculated,

Figure 2-6 Proposed overall control diagram for the paralleled UPS system.

$$V_{a\_avr} = \frac{1}{n} \sum_{i=1}^{n} (V_{ia})$$

(2-9)

Here  $V_{ia}$  is phase a RMS voltage amplitude of module #i. Compared with the reference, a compensated value for the voltage amplitude reference is generated by using a PI controller each phase respectively as shown in Figure 2-6,

$$\begin{split} v_{k\_rec} &= \left(V_{kref\_r} - V_{k\_avr}\right) \cdot G_{v\_rec}(s) \\ &= \left(V_{kref\_r} - V_{k\_avr}\right) \cdot \left(k_{pv\_sec} + \frac{k_{iv\_sec}}{s}\right) \end{split} \tag{2-10}$$

being  $v_{k\_rec}$ ,  $V_{k\_ref\_r}$ ,  $V_{k\_avr}$ ,  $k_{pv\_sec}$  and  $k_{iv\_sec}$  as restoration value of voltage amplitude, RMS voltage reference of phase k in central controller, average value of phase k RMS voltage value, voltage proportional control parameter and voltage integral control parameter respectively. And this value will be broadcast through CAN bus network to each module.

On the other hand, the phase angle regulation and synchronization will be carried out in a similar way. Hereby the phase angle is required to be tightly synchronized with the utility voltage in case of bypass operation under emergency condition. Thus the phase synchronization reference is the utility voltage angle. This control is

also executed in three phase respectively. Take phase a for instance, the averaged phase angle is derived,

$$\delta_{a\_avr} = \frac{1}{n} \sum_{i=1}^{n} (\delta_{ia})$$

(2-11)