Aalborg Universitet

### Demonstration of High Power Density kW Converters utilizing Wide-Band Gap Devices

Christensen, Nicklas

Publication date: 2019

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Christensen, N. (2019). Demonstration of High Power Density kW Converters utilizing Wide-Band Gap Devices. Aalborg Universitetsforlag.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## DEMONSTRATION OF HIGH POWER DENSITY KW CONVERTERS UTILIZING WIDE-BAND GAP DEVICES

BY NICKLAS CHRISTENSEN

**DISSERTATION SUBMITTED 2019**

AALBORG UNIVERSITY DENMARK

# Demonstration of High Power Density kW Converters utilizing Wide-Band Gap Devices

Ph.D. Dissertation Nicklas Christensen

Dissertation submitted month 09, 2019

| Dissertation submitted:    | September 2019                                                          |

|----------------------------|-------------------------------------------------------------------------|

| PhD supervisor:            | Professor Stig Munk-Nielsen<br>Aalborg University                       |

| Assistant PhD supervisors: | Associate Professor Christian Uhrenfeldt<br>Aalborg University          |

|                            | Associate Professor Szymon Michal Beczkowski<br>Aalborg University      |

| PhD committee:             | Associate Professor Peter Omand Rasmussen (chair)<br>Aalborg University |

|                            | Profesor DrIng. Sibylle Dieckerhoff<br>Technical University of Berlin   |

|                            | Professor Mariusz Malinowski<br>Warsaw University of Technology         |

| PhD Series:                | Faculty of Engineering and Science, Aalborg University                  |

| Department:                | Department of Energy Technology                                         |

| ISSN (online): 2446-1636   |                                                                         |

ISSN (online): 2446-1636 ISBN (online): 978-87-7210-503-1

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Nicklas Christensen

Printed in Denmark by Rosendahls, 2019

## Curriculum Vitae

### Nicklas Christensen

Nicklas Christensen received a B.Sc. degree in Energy Engineering with electrical specialization, from Aalborg University in 2014. In 2016 he received a M.Sc. degree in Power Electronic and Drives from Aalborg University. He is currently pursuing a Ph.D. degree within converter design using wide band gap devices at Aalborg University. During the PhD period an external stay at Danfoss Drives in Denmark was conducted. His research interest includes converter system optimization, wide band gap devices and electrical simulations using FEM software.

### Abstract

Power electronic converters plays a key role in a wide range of applications, currently experiencing a rapid growth, such as energy generation, electric vehicles, electrical drives, data centers and portable electronics. Throughout the history of power electronics a continuous focus have been on optimizing the efficiency and power density to reduce physical size, weight and power losses. The reduction in size and increase in efficiency both implies a reduction in relation to manufacturing or operation cost of the converter. The advancement in efficiency and power density has been enabled by the development of new and improved semiconductor materials/devices. The next big advancement of power electronic converters are expected to be the newly emerging wide bandgap semiconductor devices, providing superior reductions in losses for the same blocking voltage. The main topic of this thesis is building converters with a high power density and efficiency, using the new wide bandgap devices. The major objectives of the thesis is to identify the performance limiting components and to optimize the converter on a system level. This involves selecting a suitable topology and design parameters, develop and optimize the converter layout digitally and performing experiments to evaluate on the performance obtained.

Chapter 1 introduces the background and motivation of the thesis. The chapter describes the continuous focus on power density and efficiency throughout the history of power electronics. Chapter 1 also introduces the new wide bandgap devices and the substantial advantages they introduce, together with the reinforced challenges appearing, when dealing with the faster switching devices.

Chapter 2 covers the disassembly of a commercial available power electronic product, to quantify the volume contribution of the major components. The disassembly of the converter guides the focus of optimization towards the filter and heatsink volume. Th filter and heatsink volumes are linked to the power dissipation from the power module and filter components. Chapter 2 is finished by reducing the potential topologies, based on state of the art research literature.

Chapter 3 present the design of an optimization algorithm based on the multi objective optimization algorithm named Pareto. The Pareto algorithm quantifies efficiency, power density and cost for a full inverter system. The inverter system includes DC-link capacitor, power module, gate driver, heatsink and output filter. The algorithm creates a large solution space of converter designs with different switching frequency, semiconductors and output filter inductors. As a results, a pareto front was created for each topology, presenting the optimum designs for each topology.

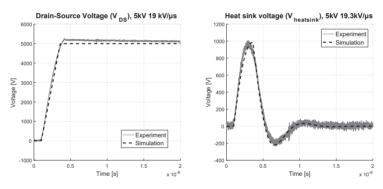

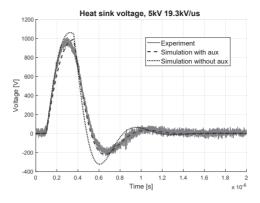

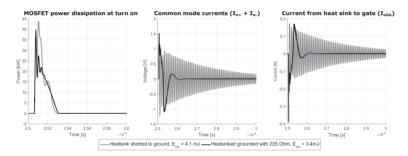

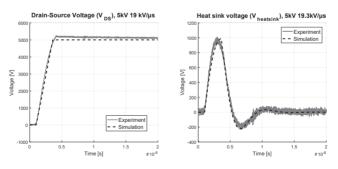

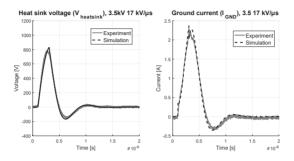

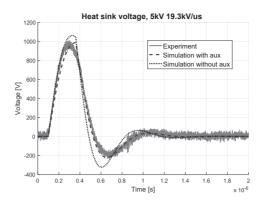

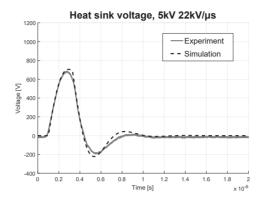

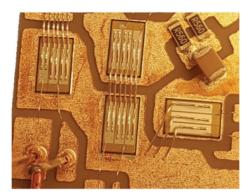

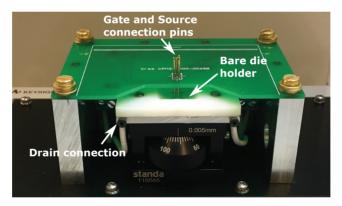

Chapter 4 present the simulation of a 10 kV SiC half bridge converter using finite element software, and the experimental validation of the parasitics extracted. The pur-

pose of the experiment was to validate the use of finite element software in performing digital design iterations. Due to the high dV/dt introduced by 10 kV SiC MOSFETs, the parasitic capacitive couplings were investigated. The capacitive network of the power module and heatsink were extracted and the behaviour was simulated. Comparing the waveforms obtained from simulation and experiment, a perfect agreement was observed. The perfect agreement validates the understanding of the power module and the accuracy of the finite element software, confirming its usefulness in a digital design process.

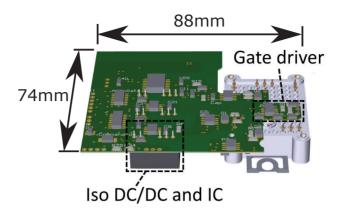

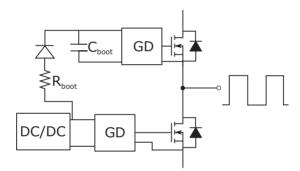

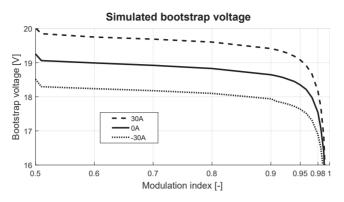

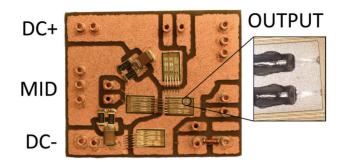

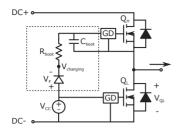

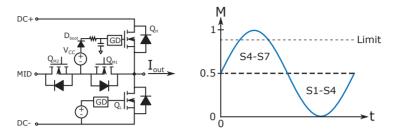

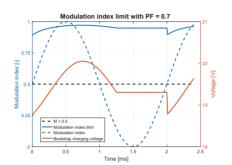

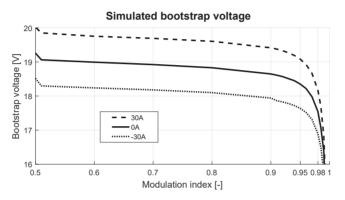

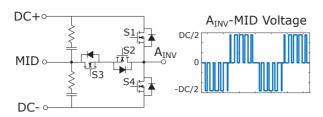

Chapter 5 present the initial design of the T-type power module, power routing and gate driver PCB. During the design process the size of the layout and its components are quantified, identifying a new power density limiting component. For a multilevel converter operating with a high switching frequency, a substantial volume contributions is introduced, by the increased number of gate drivers circuits. To reduce the size of the gate driver circuits, a novel bootstrap power supply was proposed. The conventional method of calculating the limitations of a bootstrap circuit, relies on rule of thumb estimations. A new method was as a consequence developed to accurately determine the modulation index limits. The improved method for calculating the limitations was used to evaluate the novel bootstrap circuit. The proposed bootstrap circuit for a T-type converter reduces the DC/DC converters count from seven to four, for a three phase converter.

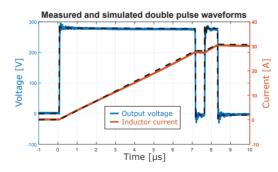

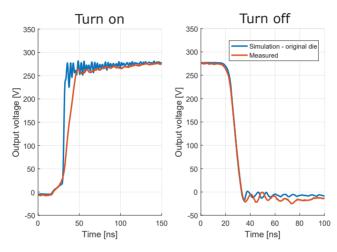

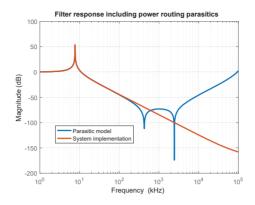

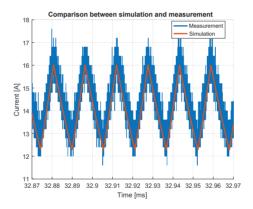

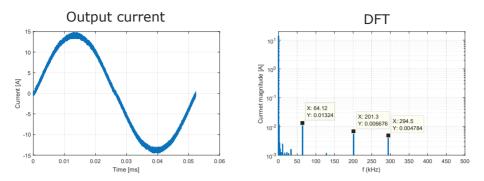

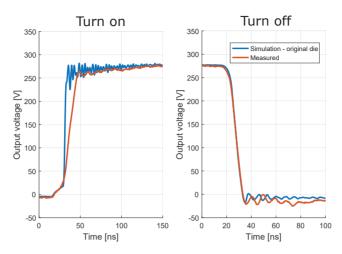

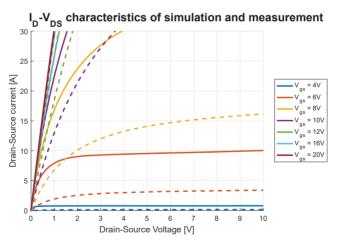

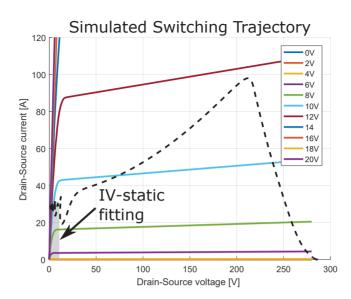

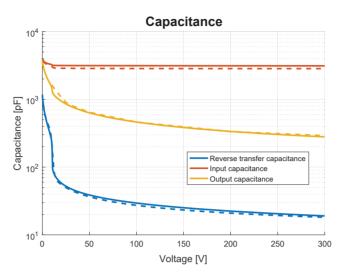

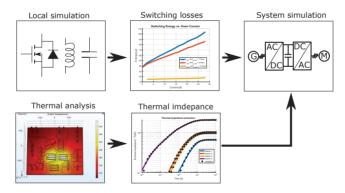

Chapter 6 presents the development of the digital model and the experimental validation of it. A digital model was developed for the T-type converter including semiconductor models, impedance of the output filter, power module, power routing and gate driver parasitics. Optimum component selection and digital design iterations were performed based on the digital model. The performance obtained was validated experimentally, by performing a double pulse test. The double pulse test confirmed that clean switching was obtained without voltage overshoot. A deviation between the measured and simulated turn on was observed. By performing a root cause analysis of the potential cause of deviation, the most likely candidate was identified to be discrepancies between the IV-characteristics of the semiconductor model and the physical device.

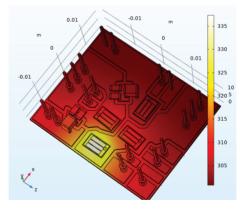

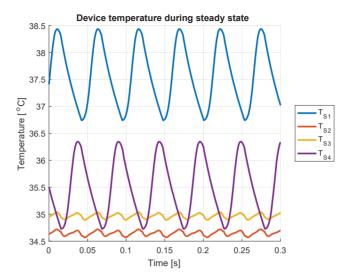

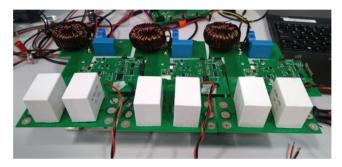

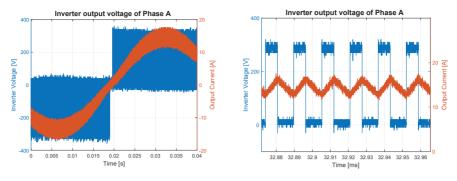

Chapter 7 present the simulation and experiments of the full three phase T-type inverter. The simulation model is based on extracted information from the complex local simulations developed in chapter 6 and a thermal network extracted using COM-SOL. The model of the full converter system, enabled the simulation of junction temperature and filter response during several fundamental output cycles. The system simulation was experimentally validated by comparing the measured and simulated inductor current ripple, presenting perfect agreement. The overall performance of the T-type inverter was validated by measuring the frequency content of the output current, showing high attenuation of the switching frequency harmonics. The three phase converter obtains sinusoidal output voltages and currents with only a 60cm<sup>3</sup> filter per phase.

Chapter 8 concludes the thesis by combing the conclusions from each chapter.

## Resumé

Effekt elektronik spiller en essentiel rolle i en lang række af applikationer, som oplever en hurtig udvikling, som for eksempel energi produktion, elektriske køretøjer, elektriske drev, data centre og småt elektronik. Gennem effekt elektronikkens historie, har der været et konstant fokus på at optimere effektiviteten og effekttætheden, for at reducere den fysiske størrelse, vægten og de elektriske tab. En reduktionen af størrelsen og en højere effektivitet medfører en reduktion i produktions- eller driftsomkostningerne for konverteren. Fremskridtene i forhold til effektiviteten of effekttætheden er opnået gennem udviklingen af nye og forbedrede halvleder materiale/komponenter. Den næste store udvikling inden effekt elektroniske konvertere forventes at være de nyankommne wide bandgap halvleder, som bidrager med markante reduktioner i elektriske tab for den samme blokeringsspænding. Denne afhandling fokusere hovedsageligt på at bygge konvertere med høj effekttæthed og effektivitet, ved hjælp af de nye wide bandgap halvledere. Afhandlingens hovedopgaver er derfor, at identificere de komponenter der begrænser udviklingen og optimere konverteren udfra en system betragtning. Dette indebære at vælge en passende topologi og design parametre, udvikle og optimere konverter layoutet digitalt og at udføre eksperimenter for at evaluere på vdeevnen opnået.

Kapitel 1 introducere baggrunden og motivation for afhandlingen. Kapitlet beskriver det vedvarende fokus på effekttætheden of effektiviteten gennem effekt elektronikkens historie. Kapitel 1 introducere også wide bandgap halvledere og de markante forbedring de introducere, sammen med de forstærkede udfordringer, der kommer med hurtigt reagerende halvledere.

Kapitel 2 dækker adskillelsen af et kommercielt effekt elektronisk produkt for at kvantificere fordelingen af volumen, blandt de store komponenter. Adskillelsen af konverteren styrer fokusset mod at reducere filterets og kølepladens volumen, som er forbundet med effekt afsættelsen i power modulet og filter komponenterne. Kapitel 2 afsluttes med at indskrænke udvalget af potentielle topologi, ved hjælp af den nyeste forskning publiceret.

Kapitel 3 præsentere design processen af en optimering algoritme, baseret på Pareto, en optimerings algoritme med flere mål. Pareto algoritmen kvantificere effektiviteten, effekttætheden og prisen for et helt inverter system. Inverter systemet indeholder DC-link kondensatorer, power moduler, gate driver, køleplader og udgangs filtre. Algoritmen genere en stor mængde mulige konverter designs med forskellige udgangsfiltre, halvledere og switch frekvenser. Resultatet af optimerings algoritmen er en Pareto front, for hver topologi, som præsentere de optimal designs for netop denne topologi. Kapitel 4 præsentere simuleringsmodellen af en 10 kV SiC halvbro konverter, som benytter sig af finite element software. De parasitiske værdier fra finite element softwaren bliver eksperimentelt valideret. Formålet med eksperimentet var at validere brugen af de parasitiske værdier i en digital design proces. På grund af de høje dV/dt introduceret af 10 kV SiC MOSFETs, er de kapacitive koblinger undersøgt. Det kapacitive netværk mellem power modulet og kølepladen blev udtrukket, og netværkets respons blev simuleret. En perfekt overensstemmelse blev observeret mellem simuleringen og de eksperimentelle forsøg. Den perfekte overensstemmelse validere både forståelsen af power modulet og præcisionen af finite element softwaren. Validering bekræfter dermed også brugbarheden af finite element software i den digitale design proces.

Kapitel 5 præsentere det første design af et T-type power modul, strømførende PCB og gate driver PCB. I forbindelse med design processen blev størrelsen af alle layouts og deres komponenter kvantificeret, hvorved en ny komponent blev identificeret til at være den begrænsende faktor for effekttætheden. For multilevel konvertere med høje switch frekvenser, vil antallet af gate driver kredsløb bidrage med en betydelig del af systems volumen. For at reducere størrelsen af gate driver kredsløbene, er en ny bootstrap strømforsyning forslået. Den konventionelle metode brugt til at beregne begrænsningen for modulation indekset afhænger af tommelfinger estimater. En ny metode er derfor udviklet for præcist at beregne begrænsningen for modulation indekset. Ved brug af den nye metode er begrænsningerne for det nye T-type bootstrap forsyning beregnet. Det foreslåede bootstrap kredsløb for en T-type konverter reducerer antallet af DC/DC konvertere fra syv til fire, for et tre faset system.

Kapitel 6 præsentere udviklingen af en digital model og dens eksperimentelle validering. En digital model er udviklet for T-type konverteren som inkludere halvleder modeller, impedanser for udgangsfiltre og parasitiske impedanser fra power modulet, gate driver og det strømførende PCB. De optimale komponent valg og design iterationer er foretaget, baseret på den digitale model. Ydeevnen opnået af konverteren er valideret eksperimentelt, ved udførelsen af en double pulse test. Double pulse testen bekræftede at en ren switching transient er opnået uden at introducere oversving i spændingen. En uoverensstemmelse mellem målte og simulerede kurver under tænding af halvlederne blev observeret. En undersøgelse af hovedårsagen til afvigelsen blev foretaget, hvor variationen mellem målte og simulerede IV-karakteristikkerne for halvlederne blev identificeret som den sandsynlige årsag.

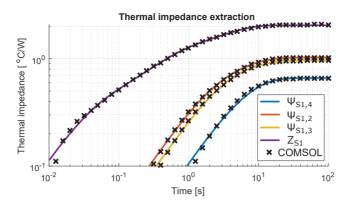

Kapitel 7 præsentere simuleringsmodellen og eksperimenterne for den fulde tre fasede T-type inverter. Simuleringsmodellen er baseret på informationerne fra de komplekse lokale simuleringsmodeller i kapitel 6 og det termiske netværk, udtrukket fra COMSOL. Modellen af hele konverter systemet tillader en simulering af junction temperaturen og filter responset, over adskillige fundamental udgangscyklusser. System simulering blev eksperimentelt valideret ved at sammenligne den målte og simulerede strøm varians i spolen, som vidste en perfekt overensstemmelse. Den overordnede ydeevne af T-type inverteren blev valideret ved at måle frekvens indholdet af udgangsstrømmen, som vidste en høj dæmpning af det harmoniske indhold introduceret af switch frekvensen. Den tre fasede konverter opnår derved sinusformet udgangsstrøm og spænding med et kun 60cm<sup>3</sup> filter.

Kapitel 8 konkludere afhandlingen ved at kombinere konklusionerne fra hvert kapitel.

## Preface

The work performed in relation to the thesis is a part of two research projects at Aalborg University (AAU), Aalborg East, Denmark. The two projects are Intelligent Efficient Power Electronics (IEPE) and Advanced Power Electronics Technology and Tool (APETT). I am very thankful for the financial support provided by the Innovation Fund Denmark and the Department of Energy technology, enabling my Ph.D. study.

I would like to express my gratitude to my supervisor Prof. Stig Munk-Nielsen for his valuable guidance and motivation throughout my Ph.D. study. I would also like to thank him for giving me the opportunity to become a part of a research team and environment.

I would also like to thank my co-supervisors Assoc. Prof. Christian Uhrenfeldt and Assoc. Prof. Szymon Beczkowski for their continuous support, guidance and technical sparring. I am truly grateful for their support in not only improving my publications and Ph.D. thesis, but also in strengthening my ability to perform research.

I would also like to express my sincere gratitude to Radu Dan Lazar, Brian Beck Christensen, Andreas Aupke and Niels Gade from Danfoss Drives. Their continuous support, technical discussions and guidance has been a key element to solve many technical challenges appearing throughout my Ph.D. studies. Furthermore the friendly atmosphere they creating during my stay at Danfoss Drives, made me feel very welcome which i truly appreciate. I would like to thank Radu Dan Lazar in particular for the additional support he provided me, by programming the DSP and assisting me in performing experiments on the three phase converter system.

I would also like to thank my friends and colleagues for their friendly companionship and continuous support throughout my Ph.D. studies. In particular i would like to thank Dipen Narendra Dalal for his willingness in participate in technical discussions in addition to providing friendly encouragement throughout my Ph.D. studies.

I am also very grateful for the support, understanding and patience provided by my family and girlfriend throughout the years. Without their unconditional support, none of my achievements would have been possible.

Nicklas Christensen

## Contents

| strac<br>sumé                     |                                                                                                                                                                                                               | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sumé                              |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   |                                                                                                                                                                                                               | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| eface                             |                                                                                                                                                                                                               | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>Intro</b><br>1.1<br>1.2<br>1.3 | oduction         Background and motivation         Objectives of the thesis         Contribution of the thesis                                                                                                | <b>1</b><br>1<br>2<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>State</b><br>2.1<br>2.2<br>2.3 | e of the art<br>Review of Existing Products                                                                                                                                                                   | <b>3</b><br>3<br>6<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Selec<br>3.1<br>3.2<br>3.3        | ction of topology and design parametersIntroduction                                                                                                                                                           | <ol> <li>9</li> <li>10</li> <li>11</li> <li>13</li> <li>14</li> <li>17</li> <li>18</li> <li>18</li> <li>20</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.1<br>4.2<br>4.3                 | dation of digital approach         Introduction         System modelling         Experimental Setup         4.3.1         Power module         4.3.2         Gate driver design         4.3.3         Results | 23<br>23<br>24<br>26<br>26<br>27<br>28<br>29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                   | 1.3<br>Statu<br>2.1<br>2.2<br>2.3<br>Selec<br>3.1<br>3.2<br>3.3<br>Valid<br>4.1<br>4.2                                                                                                                        | 1.3 Contribution of the thesis         State of the art         2.1 Review of Existing Products         2.2 Soft or hard switching         2.3 Findings and limitations         2.3 Findings and limitations         Selection of topology and design parameters         3.1 Introduction         3.2 Optimization Algorithm         3.2.1 Semiconductor         3.2.2 Heatsink         3.2.3 Output filter         3.2.4 Cost         3.3 Results         3.3.1 Cost, Efficiency and Power Density         3.3.2 Selection of topology         Validation of digital approach         4.1 Introduction         4.3 Experimental Setup         4.3.1 Power module         4.3.2 Gate driver design         4.3.3 Results |

| 5   | Buil                                                                                                       | ding a single phase high density converter                          | 31 |

|-----|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----|

|     | 5.1                                                                                                        | Introduction                                                        | 31 |

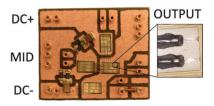

|     | 5.2                                                                                                        | T-Type Power module                                                 | 32 |

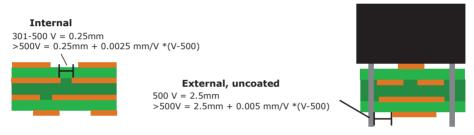

|     |                                                                                                            | 5.2.1 Selection of DBC material                                     | 33 |

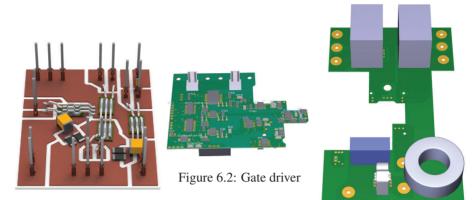

|     | 5.3                                                                                                        | Gate driver                                                         | 34 |

|     | 5.4                                                                                                        | Power PCB                                                           | 35 |

|     | 5.5                                                                                                        | Bootstrap circuit                                                   | 36 |

|     |                                                                                                            | 5.5.1 Implementation of a bootstrap supply for a T-type converter . | 37 |

|     | 5.6                                                                                                        | Conclusion                                                          | 39 |

| 6   | Desi                                                                                                       | gn criteria and experimental validation                             | 41 |

|     | 6.1                                                                                                        | Introduction                                                        | 41 |

|     | 6.2                                                                                                        | Parasitic extraction using finete element software                  | 41 |

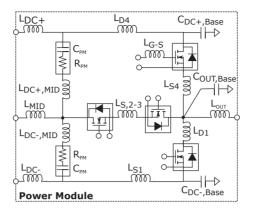

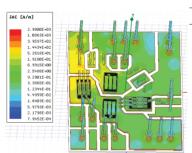

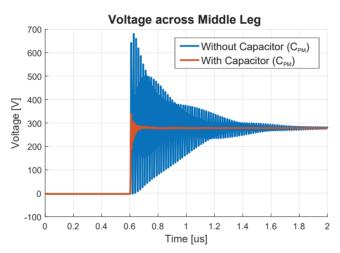

|     |                                                                                                            | 6.2.1 Power module                                                  | 42 |

|     |                                                                                                            | 6.2.2 Gate driver PCB                                               | 45 |

|     |                                                                                                            | 6.2.3 System parasitic                                              | 47 |

|     | 6.3                                                                                                        | Validation of simulation                                            | 47 |

|     |                                                                                                            | 6.3.1 Experimental measurements                                     | 49 |

|     |                                                                                                            | 6.3.2 Semiconductor model deviation                                 | 51 |

|     | 6.4                                                                                                        | Conclusion                                                          | 52 |

| 7   | From                                                                                                       | n switching transients to system simulation                         | 53 |

|     | 7.1                                                                                                        |                                                                     | 53 |

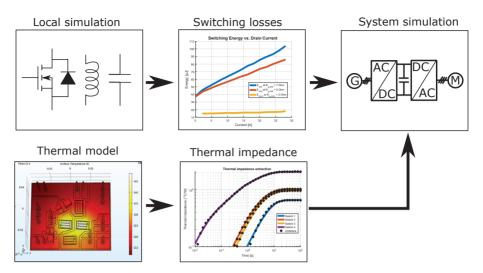

|     | 7.2                                                                                                        | Electrical Model                                                    | 54 |

|     | /.2                                                                                                        | 7.2.1 Filter design                                                 | 54 |

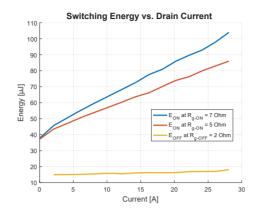

|     |                                                                                                            | 7.2.2   Export of switching losses                                  | 56 |

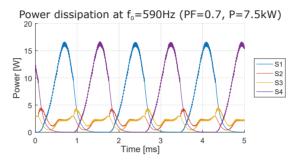

|     | 7.3                                                                                                        | Thermal Model                                                       | 57 |

|     | 1.5                                                                                                        | 7.3.1 Simulated device temperature                                  | 59 |

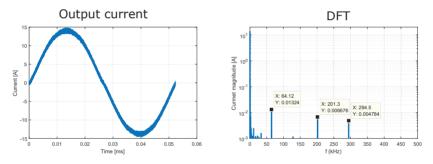

|     | 7.4                                                                                                        | Experimental measurements of the three phase converter              | 60 |

|     | /.4                                                                                                        | 7.4.1 Three phase measurements                                      | 60 |

|     | 7.5                                                                                                        | 1                                                                   | 63 |

|     | 1.5                                                                                                        | Conclusion                                                          | 03 |

| 8   | Con                                                                                                        | clusion                                                             | 65 |

| Bil | bliogi                                                                                                     | raphy                                                               | 68 |

| A   | Cost                                                                                                       | t, Efficiency and Power Density Pareto Investigation of Three Phase |    |

|     |                                                                                                            | rters.                                                              | 75 |

| B   | Con                                                                                                        | nmon Mode Current Mitigation for Medium Voltage Half Bridge SiC     |    |

|     | Mod                                                                                                        | lules                                                               | 87 |

| С   | C Modulation limit of bootstrap power supply circuits: case study of a three<br>level T-type converter 101 |                                                                     |    |

| D   | Digital design of a converter using 3D models and finite element software 113                              |                                                                     |    |

|     |                                                                                                            |                                                                     |    |

E Fast and clean switching T-type converter based on SiC MOSFETs for drive Applications 137

## CHAPTER 1

### Introduction

This chapter presents the background and motivation of the thesis, followed by the objectives and its scientific contributions.

### **1.1 Background and motivation**

Power converters are utilized in a wide range of applications, as for example in harvesting renewable energy, electrical transportation or in data centers which all are fields currently that experience rapid growth in installed capacity [1]. In these applications efficiency, power density and production cost are often the main objectives for optimization. Efficiency is an important performance parameter for better utilization of renewable energy sources, reduction of operation cost and increase of reliability. The power density of converters is likewise heavily prioritised and have been continuously increasing since 1970. The power density of converters are doubled approximately every 10 years [2]. The increase of power density is obtained by the advancement of power semiconductors, enabling an increase in the switching frequency. The switching frequency reduces the size of passive components in filters [3]. The Silicon technology used today is limited by the relative large losses associated with the switching of semiconductors. The high power dissipation results in high device temperatures and large heatsinks, limiting the obtainable switching frequency. The result of a low switching frequency are bulky input and output filters, contributing with a large weight and volume. The state of the art advancement of semiconductors is the utilization of wide bandgap materials such as silicon carbide (SiC) and gallium nitride (GaN) [4],[5]. The wide bandgap semiconductors allow for a significant decrease of switching and conduction losses when comparing to silicon (Si) devices with the same voltage blocking capability [6], [7]. The reduced losses allow the designer to increase the converter switching frequency and thereby significantly improve power density and efficiency [8],[9]. The reduced semiconductor losses, introduce new challenges in regards to signal fidelity, EMI, physical layout and the possibility of performing non-invasive measurements [10].

This thesis deals with the design process, challenges and the experimental validation of high efficiency, high power density converters utilizing wide bandgap technology.

## **1.2** Objectives of the thesis

The objective of the thesis is to develop a framework for designing and building high power density converters using the new fast switching wide bandgap devices.

- Determine the optimum topology, switching frequency and components using an optimization algorithm. The optimization objectives are power density, efficiency and cost.

- Design a converter layout and develop a simulation of the electrical performance using parasitics from 3D models.

- Evaluate the validity of parasitic extraction from a 3D model using experimental measurement.

- Evaluate and optimize converter layout based on important performance criteria.

- Perform experimental measurements of the converter prototype to validate and evaluate on digital models and design tools developed.

## **1.3** Contribution of the thesis

- Identification of the main components contributing to the volume of a converter, and the limiting factors for obtaining a higher power density.

- Proposes a method of selecting the optimum design parameters for converter using wide bandgap devices, based on analytical equations.

- Establish a method for generating an accurate digital representation of a converter, without the need of a physical prototype

- Identifying and validating performance of critical design loops, when utilizing fast switching devices.

- Demonstrating a high performance SiC power module, by carefully considering the layouts and its parasitic contribution

- A new bootstrap circuit is proposed to reduce the volume and cost of gate drivers for multilevel converters, while achieving a high modulation index.

- Demonstration of significant power density and efficiency improvement for a converter system by utilizing wide bandgap devices.

## CHAPTER 2

### State of the art

### 2.1 Review of Existing Products

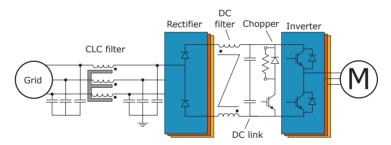

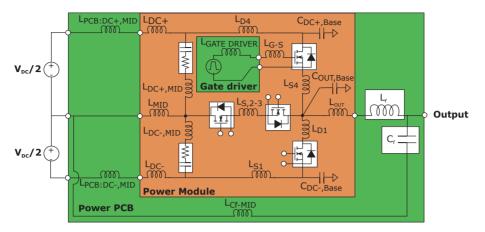

To realize the goal of significantly increasing the converter power density, an investigation of the current state of the art frequency converter and its volumetric distribution is required. A disassembly of commercial converter products will provide a foundation by providing knowledge about the level of commercial development. The knowledge gained from existing converter products will aid to guide the research focus, enabling a high degree of synergy between industry and research. The disassembly of a Danfoss 3 kW variable frequency drive is therefore performed [11]. The disassembly of the variable frequency converter was performed by mapping the volumetric size of its major components. A principal schematic of the variable frequency converter is shown in figure 2.1 representing the three categories of common and differential mode filter, DC-link and rectifier/inverter.

Figure 2.1: Principal converter schematic of Danfoss VLT AutomationDrive, FC 302.

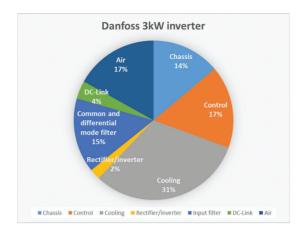

The different components are sorted in categories based on their fundamental function. The filter contains the common mode CLC filter and the differential mode DC line filter. The rectifier/inverter category contains the rectifier, inverter and chopper excluding the resistor. The resistor is excluded due to it being externally connected through output terminals of the converter. The DC-link is consisting of two electrolytic capacitors each with a voltage rating of 450 V, serial connected to withstand the full DC-link voltage. Adding additional categories such as control and cooling, a pie chart describing the volumetric size of the major component is realised as shown in figure 2.2

What becomes evident from figure 2.2 is the rectifier/inverter accounts for only

Figure 2.2: Pie chart of the relative volume distribution in a Danfoss 3 kW inverter, FC 302. The pie chart does not include external harmonic and sine wave filters.

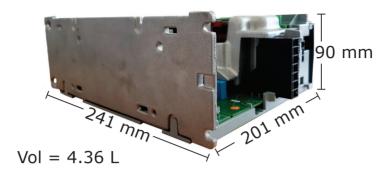

2% of the internal volume. The small dimensions of the power module of 12x5x2 cm results in a minor volume contribution, meaning decreasing the volume of the power module will produce a low relative impact on the overall power density of the converter. If the goal is to improve power density of the converter as a system, focus should not only be drawn towards increasing power density of the power module, but be expanded to its effect on external components as common and differential mode filters, DC-link and cooling. The reason for not considering chassis and control to be subjects for improvement is by the visual inspection performed during disassembly. Air accounts for 17% of the internal volume and based on the pie chart it present itself as a candidate for significant volume reduction. In practise however the air represented in the chart accounts for spacing between printed circuit boards (PCB) and chassis, air between components and air for electrical insulation. The photograph in figure 2.3 displays the air gab required between the chassis and the PCB due to varying heights of PCB mounted components.

The air between components, PCB and chassis are difficult to utilize, since the design already utilizes the space around PCBs and physical large components as filters and electrolytic capacitors. A large fraction of the control volume is contributed by the control card and its interface with display. The control is compact and consists of DSPs and small SMD components. The volume occupied for control could be minimized with the effect of reducing the external user interface. The user interface is assumed to be a fundamental requirement from the costumer and is therefore not treated as a possibility for volume improvements. The chassis serves as a heatsink and structural support for the converter. The design of the chassis is build around the components, making it a volume efficient design. The compactness of the converter chassis is also supported by the locations of the free air presented earlier. For the Danfoss converter unit a harmonic filter [12] and a sine wave filter [13] are included as a part of the converter system. The selection of additional components are provided

Figure 2.3: Disassembled Danfoss converter

by a system manager at Danfoss Drives.

Based on the disassembly of a state of the art variable frequency drive it is concluded that the power electronic packaging itself can not significantly reduce the volumetric size of the converter. The packing of semiconductors should therefore be chosen based on decreasing thermal impedance and the parasitic parameters to enable low loss operation of the semiconductor device. An example could be the need for low stray inductance for fast switching devices such as SiC MOSFETs and GaN transistors [14]-[15]. The focus points of the volume minimization for a Danfoss drive in respect to power electronics should therefore be on reducing power dissipation and the size of common and differential mode filters. By removing the requirement for harmonic and sine wave filters, a volume reduction by  $\frac{2}{3}$  can be obtained. The switching frequency and the output voltage levels of the topology are therefore key factors in reducing the size of the passive filter components which today are a necessity for producing sinusoidal currents and voltages, at the input and output terminals.

With the major components in a converter identified, the next step is to narrow the

focus of which AC converter topology enables a high power density and efficiency with the new wide bandgap devices. The question of whether a hard switched or soft switched topology should be used, will therefore be addressed in the following section.

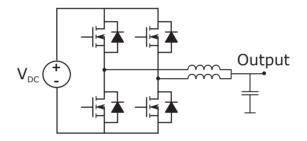

### 2.2 Soft or hard switching

Based on the experience gained from one of the finalists in the Google little box challenge a comparison study utilizing  $\eta\rho$ -Pareto optimization has been published [8]. The aim of the Google little box challenges was to build the world smallest single phase 2 kW converter, making their conclusion relevant when considering a 7.5 kW three phase inverter. One method of reducing the conduction losses and the output ripple current is to use an interleaved converter. Interleaving of a converter is obtained by parallel connecting multiple legs with individual inductors per phase. A principle schematic of interleaving a half bridge converter is shown in figure 2.5.

Figure 2.5: Circuit schematic of a interleaved single phase half bridge converter.

Their conclusion regarding interleaving is that it increases the efficiency  $(\eta)$  but requires twice the number of semiconductor devices and inductors yielding a lower converter power density  $(\rho)$ , compared to what is obtainable without. Soft switching and hard switching is compared by power density for a zero voltage switching (ZVS) triangular current modulation (TCM) and a hard switched PWM modulation. The TCM obtains a higher efficiency but a lower power density. The cause of the lower power density is the need for zero current detection circuit, high current ripple across inductor and large RMS current compared to PWM modulation, resulting in a larger inductor and higher conduction losses. The benefit of decreased switching losses is therefore cancelled by the increase of losses in passive components. The results of their comparison is graphically represented in Figure 2.6

The converter comparison was performed on a single phase inverter. The topology utilized for obtaining the highest power density based on their research is a noninterleaved hard switched topology. Utilizing a hard switching PWM modulation introduces larger dV/dt during switching transients compared to soft switching. The high dV/dt are therefore crucial to address to maintain reliable operation and fulfilment of grid codes [16],[17].

Figure 2.6: Results of calculated comparison study between TCM and PWM modulation schemes with and without interleaving [8]

### 2.3 Findings and limitations

Based on the information gathered from the previous sections, the focus for optimizing a converter, for high efficiency and high power density, can be defined. The focus and limitations for a high efficient and high power density converter will be:

- Hard switches topology

- non-interleaved converter

- Power module design should focus on minimizing power dissipation and thermal impedance

- Reduction of filter volume based on increasing switching frequency and/or topology

- Heatsink size should be reduced by selecting fitting semiconductor devices and switching frequency

- The optimum power density solution will be a compromise between heatsink and filter volume

Based on the key points stated above, an algorithm is developed to handle all the design variables. An algorithm is needed due to the vast solution space present, and to provide an enlightened selection of design parameters and components.

## Selection of topology and design parameters

This chapter present an in depth explanation of the Pareto optimization algorithm used to select the converter topology, components and design parameters. The structure of the algorithm, equations and assumption are presented and discussed.

The paper associated with this chapter (paper A) presents the main structure and working principle of the algorithm, with a special focus on the relationship between switching frequency and the power density, efficiency and cost.

• Paper A: Cost, Efficiency and Power Density Pareto Investigation of Three Phase Inverters.

In the result section of this chapter, a more detailed comparison of the different topologies are performed. The comparison is performed at an optimum switching frequency, quantifying the size of the major components for all topologies.

### 3.1 Introduction

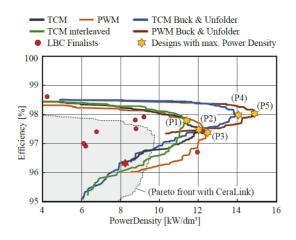

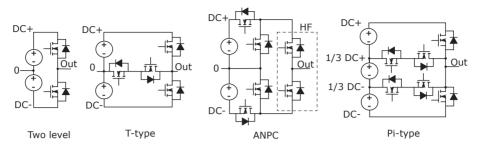

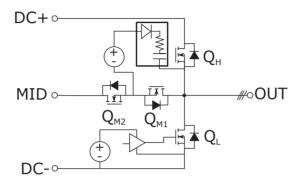

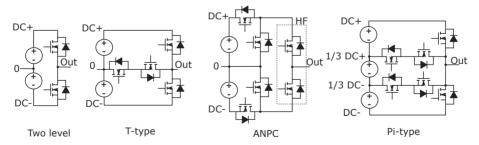

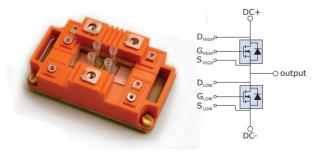

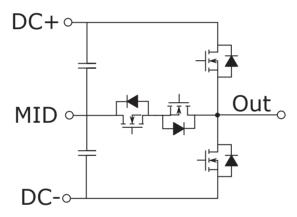

As a case study a Danfoss 7.5kW VLT is used as a reference design for optimization. The focus of optimization will be on the DC/AC inverter stage. The inverter stage includes DC-link, heatsink, power module, gate driver and output filter. Due to the vast amount of combinations of filter designs, semiconductors, topologies and switching frequencies, selecting an optimum design becomes a challenging task [18]. An algorithm is therefore developed, evaluating the optimization objectives for thousands of designs, allowing for an educated guess on the specifications for the optimum converter. For the optimization algorithm different hard switches topologies are selected for investigation. The topologies includes a two level half-bridge, three level T-type and active neutral point clamped (ANPC), and a four level Pi-type converter. The schematics of the topologies are shown in figure 3.1.

Several advantages and disadvantages are present for each topology, making the selection of the optimum topology a challenging task. One of the major advantages utilizing a two-level converter is the small required DC-link capacitance. If the two level converter is supplying a three phase balanced load, the average output power during a switching period will be constant. The energy supplied from the DC link is as a consequence zero during one switching period. Zero capacitor current during a fundamental switching cycle are not guaranteed for multilevel converters without advanced control [19]. Multilevel converters without advanced control will experience low frequency DC-link power ripple with three times the fundamental frequency of the input

Figure 3.1: Converter topologies implemented in the Pareto optimization algorithm.

and output voltages. The low frequency power ripple results in larger requirement of DC-link capacitance. An advantage of utilizing a multilevel topology is the increase in output voltage levels which reduces the filter volume and power dissipation. General for the two level, T-type and Pi-type is that the switching and conduction losses are distributed between all the dies, which is not the case for the ANPC. The high frequency (HF) leg conducts the full current and is switched with a high frequency, resulting in the HF leg being responsible for the dominant part of the semiconductor losses. The low frequency (LF) switches are switched dependent on the fundamental output cycle, resulting in the main loss contribution from the low frequency switches being conductive.

Each topology will, as a consequence, have an optimum semiconductor combination, output filter, DC-link, heatsink and switching frequency depending on the optimization objectives. An objective comparison and selection of topology is therefore only accomplished by evaluating a large solution space of converter designs and comparing them by the prioritized optimization objectives. In this optimization algorithm the objectives are power density, efficiency and cost where power density and efficiency are favourable compared to system cost.

## 3.2 Optimization Algorithm

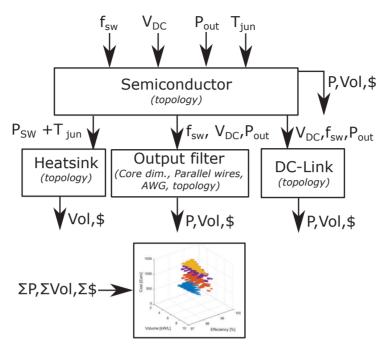

A  $\eta\rho$ \$-Pareto optimization is selected for the algorithm. As introduced in section 2.2 a front of possible design candidates are created based on the algorithm, allowing for the selection of the optimum design candidate. An optimum design candidate is defined as a design where the increase of one optimization objective results in a decrease of another. The calculation of losses, volumes and cost are based on analytical equations, allowing for fast computation. This allows for a full sweep of design variables as switching frequency and component libraries without having an unacceptable execution time. The overview of the optimization algorithm and the interconnection between the major components are shown in figure 3.2 for an inverter with output filter.

As indicated by figure 3.2 the input parameters are DC-link voltage, output power and junction temperature. The input parameter being swept is the switching frequency

Figure 3.2: Flowchart of the Pareto optimization algorithm.

and topology. In the functions for each major components, the feasibility of the solution is evaluated. If the solution is not feasible it is removed from the solution space. An example could be the power dissipation of the semiconductor requiring a negative thermal impedance of the heatsink. The request of a negative thermal impedance is an indication of a power dissipation and a thermal impedance of the power module violating the maximum junction temperature. The design candidate is therefore removed due to it being an infeasible solution. In the following section a brief description of the models and assumptions for calculating volume, power dissipation and cost are presented for the major components.

### 3.2.1 Semiconductor

The losses associated with the semiconductor is separated into two groups: conduction losses and switching losses. The conduction losses is dependent on the current and a temperature dependent on-state resistance. The switching losses can be calculated using different methods as for example the switching loss curves given in the datasheet or analytical equations based on threshold voltage and time constants of the devices. However all these methods requires knowledge of the gate driver circuit, which heavily depends on the specific semiconductor devices, topology, power module and gate driver layout realised. It is therefore assumed that the switching losses are dominated by the contribution of the device output capacitance. The assumption is selected based

on published experience with GaN transistors [20]. It is assummed that the converter only performs hard switching, the soft switching occurring under certain operation points as a consequence of deadtime, load current and output capacitance is therefore not considered.

### **Conduction losses**

The on-state resistance is implemented as a function of temperature by linear interpolation. The linear interpolation is presented in (3.1)

$$R_{ds}(T_j) = R_{ds(on)}(T_1) + \frac{R_{ds(on)}(T_2) - R_{ds(on)}(T_1)}{T_2 - T_1} \cdot (T_1 - T_j)$$

(3.1)

Temperature values  $T_1$  and  $T_2$  are the on-state resistance specified in the datasheet for two different temperatures, typically 25°C to 150°C. The junction temperature inserted into equation (3.1) is an input parameter initially specified in the algorithm for sizing the required volume for a heatsink.

### **Capacitive switching losses**

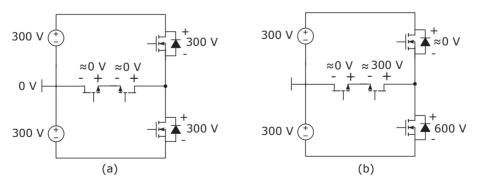

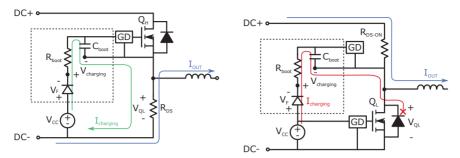

The capacitive contribution of the switching are a sum of losses related to capacitors. Assuming the transistor to be modelled as a switched resistive element allows considering the circuit as a resistive charging of a capacitor. Resistive charging of a constant capacitance is performed with a 50 % efficiency ( $\eta_{charging} = 50\%$ ) regardless of the resistance value [21]. Assuming the capacitances to be constant yields the conclusion that all capacitive loads connected to a transistor regardless of it being a non-ideel inductor or a semiconductor will contribute to the switching losses with the capacitive energy stored. An example of the switching transition for a T-type converter is presented in figure 3.3 with a DC-link voltage of 600 V. The circuit diagram will be used to carry out a calculation example of the capacitive losses, as a documentation of the procedure on which the future results presented will rely on.

Figure 3.3: Example of differential voltages across devices during a switching transition. The switching transition investigated in figure 3.3 (a) is with the middle leg conducting transitioning to figure 3.3 (b) with the top switch conducting. The top transistor will discharge the energy stored in its output capacitance through its channel and charge the externally connected transistors from 0 V to 300 V in the middle leg and 300 V to 600 V for the lower transistor. The contributions to the energy dissipated in the top switch during a turn on transient can be summarised by the three integrals given in (3.2) - (3.3). The middle leg consist of a serialised connection of two GaN transistors, presenting the increased complexity when considering a converter with different transistors implemented.

$$E_{oss(dis)} = \int_{300V}^{0V} C_{SiC-oss}(V) \cdot V \quad dV$$

(3.2)

$$E_{oss(charge)} = \int_{0V}^{300V} C_{GaN-oss}(V) \cdot V \quad dV + \int_{300V}^{600V} C_{SiC-oss}(V) \cdot V \quad dV$$

(3.3)

By performing the integration and including the two switching transitions per switching cycle, an equation for the switching losses can be derived as shown in 3.4.

$$P_{sw-cap} = 2 \cdot \sum (E_{oss-dis} + E_{oss-charge}) \cdot f_{sw}$$

(3.4)

The sum of switching losses and conduction losses are used as an input for the sizing of the heatsink.

#### Semiconductor library

The semiconductor library of the pareto scripts includes transistor of different materials from different manufacturers. The library contains GaN transistors from GaN systems, SiC MOSFET from Wolfspeed and ROHM, and Si MOSFETs with low onstate resistance for the ANPC. The device ratings are ranging from 650V to 1.2 kV, with a on-state resistance variation from  $22m\Omega$  to  $120m\Omega$ . An on-state resistance of  $120m\Omega$  is the limiting value, for the rated current.

### 3.2.2 Heatsink

Calculating the size of a heat sink is a complicated task, since accurate results in terms of thermal impedance requires solving the heat flow in 3D. An equation is defined to simplify the calculation. The equation is shown in equation (3.5) and assumes the thermal impedance to be inversely proportional to the volume of a heat sink.

$$K_{heat\,sink} = R_{th} \cdot Vol_{heatsink} \tag{3.5}$$

The heat sink constant can then be determined based on a datasheet of a heat sink. Doubling the volume of the heat sink will as a consequence half the thermal

impedance. The heat sink constant is calculated based on cooling with forced convection. The heat sink constant is given in (3.6) for a Coldcube heatsink [22].

$$K_{heat sink} = 0.12 \frac{K}{W} \cdot 7.5 cm \cdot 8.2 cm \cdot 10.0 cm = 73.8 \frac{K \cdot cm^3}{W}$$

(3.6)

The ambient and the maximum allowed temperature for exposed components is specified in (3.7)

$$T_{amb} = 45^{\circ}C$$

,  $T_{max} = 70^{\circ}C$  ,  $\Delta T = 25^{\circ}C$  (3.7)

The required thermal impedance is calculated using equation (3.8).

$$R_{th} = \frac{\Delta T}{\sum P_{loss}} - \frac{R_{thermal \ compound} + R_{die-baseplate}}{n_{transistors}}$$

(3.8)

The thermal impedance can then be inserted into equation (3.6), solving for the heat sink volume. This method will be used for calculating the heat sink volume contribution.

#### 3.2.3 Output filter

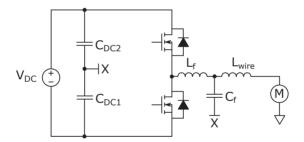

A typical two-level inverter as used in the Danfoss converter is shown in figure 3.4 with an L-C filter. An L-C filter is proposed for AC drives to suppress common mode

Figure 3.4: Two level inverter with output filter

(CM) and differential mode (DM) dv/dt [23], [24]. CM voltages introduces high frequency leakage currents through the bearings of the AC machine, reducing the motor reliability. The DM voltages can produce over voltages at the motor terminals if long cables are used. The terminal over voltage is twice the output voltage magnitude of the converter, increasing stress on insulation [25]. The output filter for all converter topologies will be based on the recommended L-C filter with the capacitor connected to the mid point of the DC-link.

#### Inductor

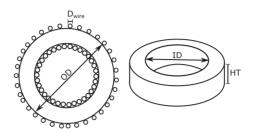

The calculation method for quantifying the volume and power dissipation of the inductor is based on the geometric size of the core, diameter of the windings, copper losses, switching and fundamental frequency core losses. The core dimensions are obtained from manufactures [26] and used as inputs for the model. In figure 3.5 the notation of the core dimensions are specified.

Figure 3.5: Specification of core dimension used for calculating the volume of the inductor.

The MATLAB script utilizes the core dimension to calculate the physical limit of the number of windings using equation (3.9).

$$N_{\text{physical}} = \frac{ID}{n_{parallel} \cdot D_{wire}}$$

(3.9)

A constraint is set by the potential core saturation, the maximum number of windings before saturation is therefore calculated. The lowest integer value of windings is used for further calculations in the script. The number of windings is used to calculate the inductance value, allowing the algorithm to select suitable inductors for each topology and switching frequency [27]. The volume of the inductor is calculated using equation (3.10)

$$\operatorname{Vol}_{L} = \frac{\pi \cdot (OD + 2 \cdot D_{wire})^{2}}{4} \cdot (HT + 2 \cdot D_{wire})$$

(3.10)

With the inductance associated with a certain volume, the next step is to calculate the core losses of the inductor. To calculate the losses, the variation in magnetic field strength is initially calculated by (3.11).

$$H_{ripple-max/min} = \frac{N \cdot (I_{RMS} \pm \frac{I_{ripple}}{2})}{l_e}$$

(3.11)

The magnetic field strength can then by used to determine the magnetic flux density ripple by an empirical equation as (3.12) [28].

$$B_{ripple-max} = \left(\frac{a + b \cdot H_{ripple-max} + c \cdot (H_{ripple-max})^2}{1 + d \cdot H_{ripple-max} + e \cdot (H_{ripple-max})^2}\right)^x$$

(3.12)

From equation (3.12), the magnetic flux density ripple is obtained for a specific DC current bias. The core losses caused by the current ripple are calculated based on

the RMS current of the sine wave. The equation for the magnetic flux density ripple is presented in (3.13)

$$B_{pk} = \frac{B_{AC-max} - B_{AC-min}}{2} \tag{3.13}$$

The power dissipation per volume core is then calculated based on the flux ripple caused by the fundamental output frequency and the switching frequency. The empirical equation is presented in (3.14), [29].

$$PL = a \cdot B_{pk}^b \cdot f^c \quad [\text{mW/cm}^3] \tag{3.14}$$

Based on (3.14) and the volume of the core, the hysteresis losses can be calculated for each inductor design. The copper loss is separated into the DC and AC component where only the calculation method of the AC component will be presented. The calculation of the AC conduction loss is based on the skin depth and the length of the wire. The length of the wire is calculated using equation (3.15)

$$l_{wire} = N \cdot 2 \cdot (HT + OD - ID + D_{wire})$$

(3.15)

where ID, OD and HT describes the dimension of the core,  $D_{wire}$  being the wire diameter and N being the number of windings. The skin depth is given by equation (3.16).

$$d_{cu} = \sqrt{\frac{\rho_{cu}}{\pi \cdot f_{sw} \cdot \mu_0 \cdot \mu_r}} \tag{3.16}$$

With the skin depth and wire length determined, the ac resistance of the wire can then be determined by (3.17).

$$R_{AC} = \frac{l_{wire} \cdot \rho_{cu}}{\frac{\pi}{4} (D_{wire}^2 - (D_{wire} - 2 \cdot d_{cu})^2) \cdot n_{parallel}}$$

(3.17)

Combining the core, DC and AC copper losses the total power loss of the inductor can be calculated. A constraints for the possible inductor solutions is set by a maximum temperature of  $70^{\circ}$ C. The manufacture of the Kool Mu cores (MAGNETICS) provides an empirical equation for temperature rise of the inductor. The equation is given in (3.18).

$$\delta T_{core} = \left(\frac{P_{loss} \cdot 10^3}{A_{surface} \cdot 10^4}\right)^{0.833} \tag{3.18}$$

The temperature constraints is used in the final script to reduce the solution space, by removing the inductors which would exceed the maximum allowed temperature.

#### Capacitor

The capacitance value of the L-C filter is selected to obtain a specific filter cut off frequency. The cut off frequency is selected to be the logarithmic middle of the switching frequency and the highest fundamental output frequency. Utilizing this as a design criteria, the cut off frequency of the filter can be determined by (3.19).

$$\omega_{\rm LC} = 2 \cdot \pi \cdot 10^{\frac{\log(f_{\rm fund}) + \log(f_{\rm SW})}{2}} \tag{3.19}$$

With the cut off frequency and inductance known the capacitance value can be determined by (3.20).

$$C_{\rm f} = \frac{1}{L_{\rm f} \cdot \omega_{\rm LC}^2} \tag{3.20}$$

With a fundamental frequency of 590 Hz, switching frequency of 100 kHz and an inductance value of 216.5  $\mu \rm H.$

$$C_f = \frac{1}{216.5\mu H \cdot (2 \cdot \pi \cdot 7.7kHz)^2} = 2\mu F$$

(3.21)

The low value of capacitance required for the filter allows for the usage of multi layer ceramic capacitors (MLCC) or a small film capacitor. The volume of the capacitor is therefore small compared to the volume contribution of the inductor.

#### 3.2.4 Cost

The cost is an important parameter, which is expected to increase with the number of semiconductor devices. To evaluate the cost dependency of efficiency, power density and topology, prices are added for the major components.

#### Semiconductors

The price of the semiconductors are included as the price for the devices in a discrete package. The prices are found on Mouser Electronics, an electronic components distributor. The prices of components are found at one distributor, making them comparable in relative magnitude.

#### Gate driver

The gate driver cost is calculated based on number and type of components utilized. The script distinguishes between a single and dual gate drivers. The dual gate drivers are used for the middle leg switches in multilevel topologies. The components allocated for the single and dual gate drivers are listed in (3.22) and (3.23) respectively.

$$cost_{GD-single} = price_{GD} + price_{DC/DC} + 9 \cdot price_{cap}$$

(3.22)

$$cost_{GD-dual} = 2 \cdot price_{GD} + price_{DC/DC} + 13 \cdot price_{cap}$$

(3.23)

The components significantly contributing to the price of the gate drivers are the gate driver IC and the isolated DC/DC power supply. The gate driver circuit accounts for a significant cost contribution of the complete converter system [30].

#### Heatsink

The cost of a heatsink is calculated based on the volume. The heatsink is assumed to be made from a solid piece of aluminium. The volume is therefore used to calculated the weight of the solid aluminium piece being used for the heatsink. The price for a kilo gram of aluminimum is then used to obtain the price of a heatsink. The equation is presented in (3.24)

$$Cost_{heatsink} = Vol_{heatsink} \cdot \rho_{alu} \cdot price/kg$$

(3.24)

The aluminium price is very low compared to the semiconductor devices and gate drivers, meaning the cost contribution is insignificant when comparing to the final cost of the inverter.

#### Inductor

The core dimensions and volumes are known in the script, due to it being a necessary part in the inductor design procedure. The inductor cost is calculated with a similar method as the heatsink. The price of the inductor is as a consequence proportional to the core volume. The equation is presented in equation (3.25).

$$\text{Cost}_{L} = \text{Vol}_{L} \cdot \frac{\text{price}}{\text{m}^{3}}$$

(3.25)

# 3.3 Results

The purpose of this section is to present the combined results of the modelling shown in section 3.2. The combination of models will provide a full system evaluation of power density, efficiency and cost. The component library used in the algorithm consist of commercially available products. Each point in the Pareto optimization is therefore a full system evaluation, with an attached bill of materials. The complete solution space of thousand of converter combinations provides an objective comparison between different topologies, design parameters and components on a system level.

### 3.3.1 Cost, Efficiency and Power Density

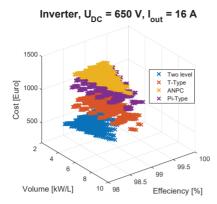

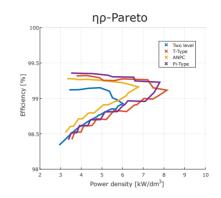

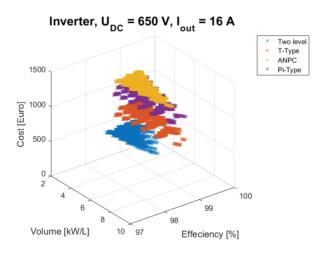

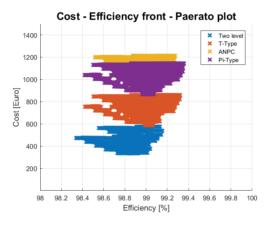

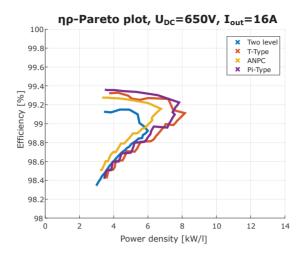

The three dimensional Pareto plot can be seen in figure 3.6 sweeping a frequency range from 25 kHz to 150 kHz with an output RMS current of 16 A. The efficiency and power density front of the results is shown in figure 3.7.

Figure 3.6: Three dimensional Pareto plot of an inverter including cost, efficiency and power density.

Figure 3.7: Extracted efficiency and power density Pareto front.

When evaluating figure 3.6, relative small improvements in power density and efficiency are achieved compared to the conventional two level topology. Moving to a multilevel topology, requiring additional semiconductor increases power density and efficiency but also heavily increase the price of the converter. The converter price being heavily dependent on the semiconductor count are expected as the price of SiC MOSFET, GaN transistors, DC/DC converters and gate drivers are high compared to the price of aluminium and filter cores. The benefit of performing an objective selection of components and design parameters based on a system evaluate is clear, when evaluating on the spread of possible solutions for each topology. The correct selection of semiconductors, switching frequency and inductor design are just as important as the selection of the optimum topology.

The two level converter achieves the lowest efficiency due to the large switching and hysteresis losses, which limits the obtainable switching frequency. The low efficiency therefore results in a low power density due to the large inductor and heat sink volume required.

Comparing the power densities and efficiencies of all topologies, the most significant improvement is observed when changing from a two level topology to a three level topology. Most noticeably is the benefit when selecting a T-type topology. The T-type topology reduces switching losses and decreases the required inductance of the filter [31]. The semiconductor losses are distributed on all four dies during a fundamental period, reducing the size of the heatsink. The low switching losses and conduction losses enables a very high efficiency. Of all topologies the ANPC has the lowest switching losses, due to the reduced required blocking voltage enabling the use of GaN transistors. The ANPC is therefore suitable for high switching frequencies. The disadvantage of the GaN transistor is the high conduction losses at higher temperatures. The GaN on-state resistance increases by a factor of 2.5, with a temperature increase from 25°C to 150°C. In combination with the low resistance Si MOSFETs in the topology, the increased conduction loss outweighs the benefit of low switching

losses for the specific specifications investigated. Figure 3.7 shows nearly equal efficiency being achieved by the four level Pi-type and the three level T-type converter. The reason being, adding another output voltage level will reduce the switching and filter losses, but increase the conduction losses.

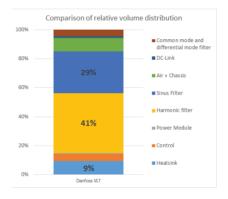

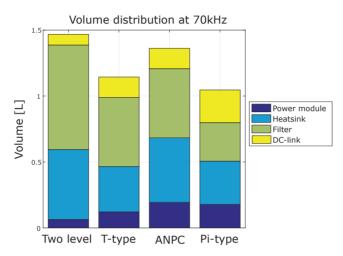

An in depth view of the volume distributions for each topology is presented in figure 3.8 for a switching frequency of 70 kHz. A switching frequency of 70 kHz is selected, due to the high power density and efficiency achieved for all topologies.

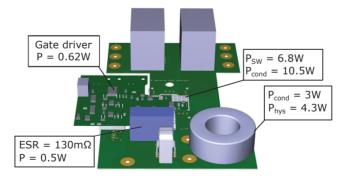

Figure 3.8: Volume distribution of major components

The volume of the major components in figure 3.8, shows a significant volume reduction is obtained by changing from a two level topology to a T-type topology. The volume reduction is obtained by the decrease of required output filter and heatsink volume. The ANPC achieves a lower power density than the T-type, due to the power loss being concentrated on two transistors, and the fact that the topology needs six switches with gate drivers. The Pi-type topology achieves the highest power density. The increase in power density from a T-type to a Pi-type is however small compared to the improvement obtained from a two level to a T-type. The added cost from additional switches and gate driver circuitry needed for ANPC and Pi-Type converter can not be justified in respect to converter price and performance gain.

### 3.3.2 Selection of topology

Based on the results from the Pareto algorithm an objective comparison between the conventional two level converter and multilevel alternatives are performed. All multi-level topologies investigated in the Pareto algorithm achieves higher power densities and efficiencies compared to the two level converter.

Compared to the conventional two level converter, the selection of a T-type topology can be justified by its increase in power density and efficiency, with the penalty of a significant cost increase. Choosing a topology with additional transistor or out-

| Parameter                              | Value               |

|----------------------------------------|---------------------|

| Power (Pout)                           | 7.5 kW              |

| Current (I <sub>RMS</sub> )            | 16 A                |

| switching frequency (f <sub>sw</sub> ) | 70 kHz              |

| SIC MOSFET                             | 25mΩ                |

| Inductor (Kool Mu)                     | 380uH               |

| Power density                          | 7kW/dm <sup>3</sup> |

| Efficiency                             | 99.2 %              |

| Cost                                   | 700 \$              |

put voltage levels compared to the T-type can not be justified, due to the insignificant performance improvements with a significant increase in cost, control complexity and reduced manufacturability. The Pareto algorithm present the two level and the T-type converter as ideal design candidates. The compromise is between the cheaper two level topology or the more expensive T-type converter, which achieves a higher power density and efficiency.

The goal of the thesis is to build a converter with a high power density and efficiency, resulting in the selection of a T-type converter. The bill of material is extracted for the solutions at a switching frequency of 70 kHz. A switching frequency of 70 kHz is selected due to the high power density and efficiency achieved simultaneously. Increasing the switching frequency above 70 kHz, will increase the volume of the heatsink, which is not justified by the reduction of filter volume. The losses of the converter at 70 kHz is dominated by the semiconductor losses, meaning increasing the switching frequency further will only decrease the overall system efficiency. The design parameters and key components of the T-type converter at 70kHz is presented in table 3.1.

# Validation of digital approach

The focus of this chapter is on the methodology related to the design process, the digital simulation with parasitics and the validation of it.

The paper associated with this chapter (Paper B) has a main focus on the experimental validation of the parasitic values and its impact on a converter operating at high voltage with high dV/dt.

• Paper B: Common Mode Current Mitigation for Medium Voltage Half Bridge SiC Modules

### 4.1 Introduction

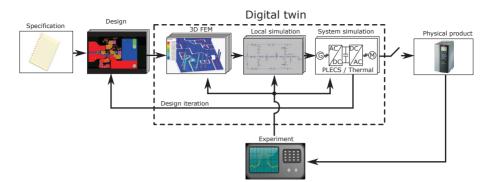

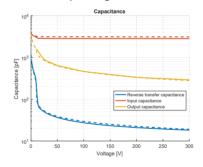

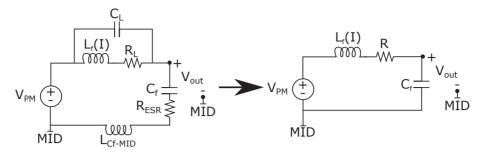

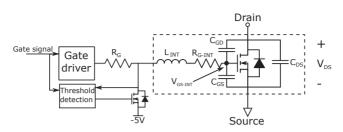

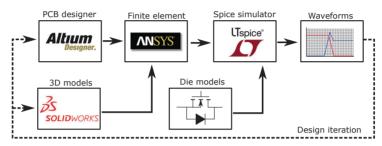

With fast switching wide bandgap devices, higher dv/dt and di/dt introduces challenges in regards to over voltages, false turn on, EMI, performing measurements and control fidelity [32], [33]. A model for evaluating the performance of a converter layout before manufacturing is much needed, as new challenges appears and the means of validation are reduced. The model is particularly useful in the design phase to quantify the advantages and disadvantages of the design choices. Enabling digital iterations of optimization, without the need of a physical prototype. Avoiding a physical prototype in the design iteration reduces cost and saves time spend on experimental measurements. A flowchart describing how the digital model can be used in the design phase is presented in figure 4.1. The collection of simulation models are referred to as the digital twin.

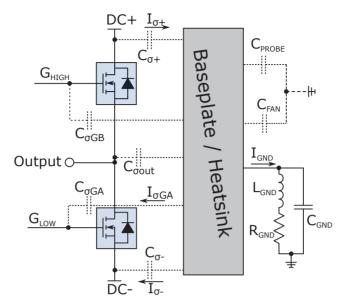

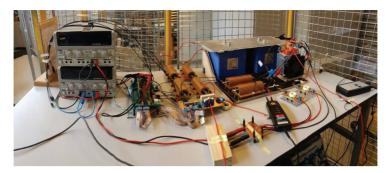

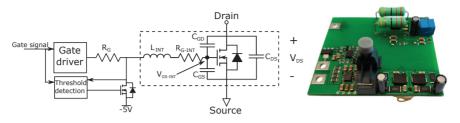

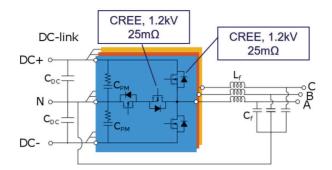

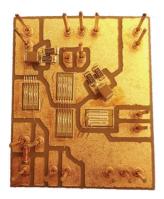

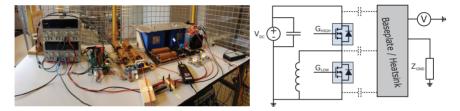

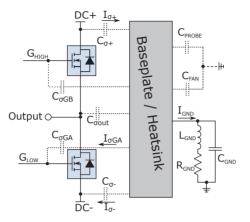

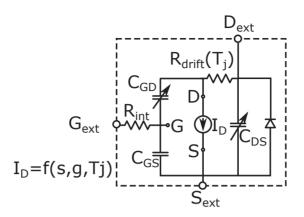

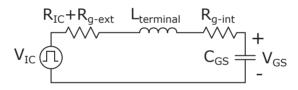

Before using the digital twin for optimization, a validation of the method is needed. The modelling method is validated by developing a simulation model for a 10 kV SiC halfbridge converter and performing experimental measurements for validation. The converter is operated at 5kV and with a rated current of 10 A. The SiC MOSFET will therefore introduce large dv/dt and low di/dt [34]. Due to the high dv/dt the impact of capacitive coupling is important to address [35],[36]. The focus of modelling and validation will therefore be on the parasitic capacitance network created between the power module and the heatsink, as the capacitance contribution significantly effects both switching and EMI performance [37]. The parasitics values are extracted from the layout using Ansys Q3D Extractor. The parasitics are combined with models of semiconductors and passive components to establish an accurate digital twin.

Figure 4.1: Flowchart of the digital design iterations using a digital twin

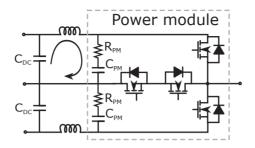

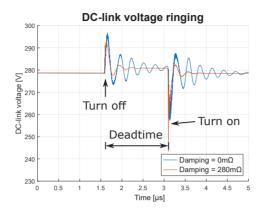

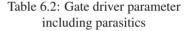

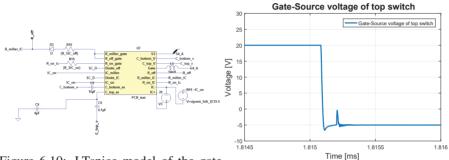

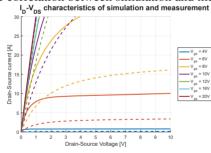

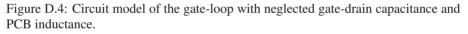

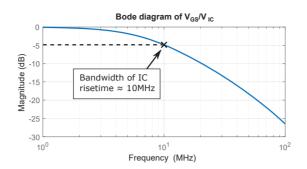

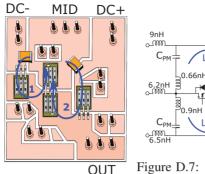

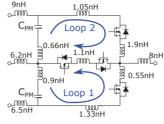

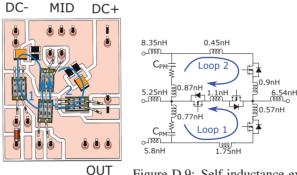

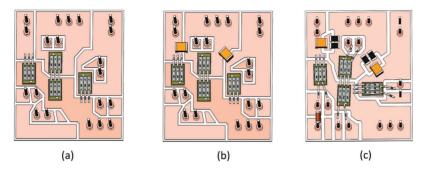

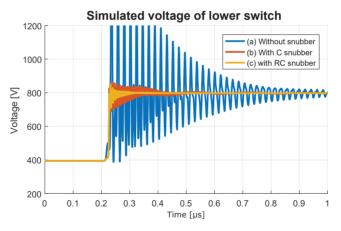

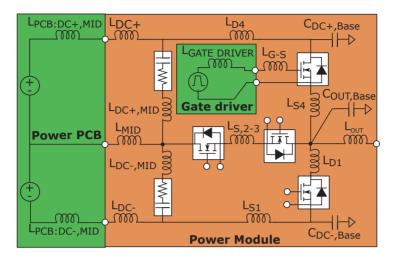

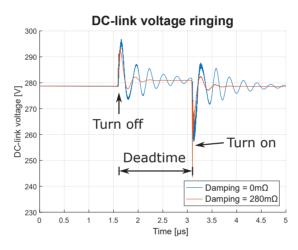

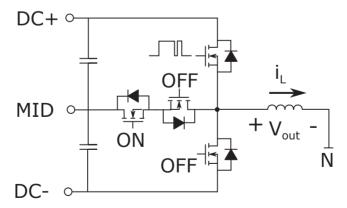

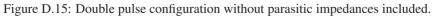

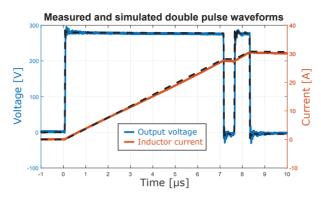

## 4.2 System modelling