# **Aalborg Universitet**

# **Ensuring a Reliable Operation of Two-Level IGBT-Based Power Converters**

A Review of Monitoring and Fault-Tolerant Approaches

Hu, Keting; Liu, Zhigang; Yang, Y.; Iannuzzo, F.; Blaabjerg, F.

Published in: **IEEE Access**

DOI (link to publication from Publisher): 10.1109/ACCESS.2020.2994368

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Hu, K., Liu, Z., Yang, Y., Iannuzzo, F., & Blaabjerg, F. (2020). Ensuring a Reliable Operation of Two-Level IGBT-Based Power Converted: A Review of Monitoring and Pault-Tolerant Approaches. *IEEE Access*, *8*, 89988-90022. Article 9093024. https://doi.org/10.1109/ACCESS.2020.2994368

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

# Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# Ensuring a Reliable Operation of Two-Level IGBT-Based Power Converters: A Review of Monitoring and Fault-Tolerant Approaches

Keting Hu<sup>1,2</sup>, Student Member, IEEE, Zhigang Liu<sup>2</sup>, Senior Member, IEEE, Yongheng Yang<sup>3</sup>, Senior Member, IEEE, Francesco Iannuzzo<sup>3</sup>, Senior Member, IEEE, and Frede Blaabjerg<sup>3</sup>, Fellow, IEEE

<sup>1</sup>State Key Laboratory of Traction Power, Southwest Jiaotong University, Chengdu, China

Corresponding author: Keting Hu (e-mail: huketing121@163.com).

This work was supported in part by the National Natural Science Foundation of China under Grant U1434203, and the Research Project of China Railway Eryuan Engineering Group Co. Ltd. (KYY2020033(20-21)).

**ABSTRACT** Despite the emerging multi-phase and multi-level converters, two-level insulated gate bipolar transistor-based power converters are still widely used in industrial applications in nowadays. Thus, its reliability is of significant importance for ensuring industrial safety. In this paper, a review of the possibilities to ensure the reliable operation of these power converters is presented. The possible approaches are categorized into two groups: condition monitoring and fault-tolerant control. The former approach performs the monitoring methods of power converters, which enables the identification of device degradation to be realized. Accordingly, the mechanisms, indicators, and measuring methods of degradation are demonstrated in this paper to assist the design of condition-based maintenance. In contrast, the latter approach is a post-fault one, where power converters remain the operation by activating the fault-tolerant units after faults are identified. For this approach, fault detection, fault isolation, and tolerant strategies are essential. Finally, the performance and cost-effectiveness of the two categories are discussed in this paper.

**INDEX TERMS** two-level power converter; reliability; condition monitoring; fault tolerance; renewable energy application; insulated gate bipolar transistor

#### I. INTRODUCTION

Insulated gate bipolar transistors (IGBTs)-based two-level converters are still widely adopted in today's industrial

applications, e.g., wind turbine power systems [1, 2], photovoltaic (PV) systems [3, 4] and electrified vehicles [5-9]. In those applications, the power converters may face

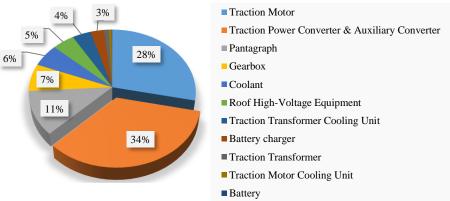

Fig. 1. Failures of electrified railway traction drive systems from 2009 to 2013 [10].

<sup>&</sup>lt;sup>2</sup>School of Electrical Engineering, Southwest Jiaotong University, Chengdu, China

<sup>&</sup>lt;sup>3</sup>Department of Energy Technology, Aalborg University, Aalborg, Denmark

(a) (b)

Fig. 2. Five-year experience of failures in a commercial PV power plant in Arizona from 2001 to 2006 (DAS: Data Acquisition System, ACD: ac disconnects, ModJct: Module Junction Box, PV –PV arrays): (a) unscheduled maintenance events and (b) associated maintenance costs [11].

harsh conditions, which as a consequence, challenges the reliability, being the main lifetime-limiting component. For instance, according to the study in [10], power converters account for 34% of all the failures in electrified railway traction systems, as shown in Fig. 1. A similar conclusion has been revealed in [11] (see Fig. 2) that PV inverters contribute 37% of overall unscheduled maintenance events. The power converter failures lead to 59% of the total unplanned maintenance expenditure. Furthermore, based on an industry-based survey in [12], the most fragile components in power converters are semiconductor power devices, contributing to around 31% of all the converter failures.

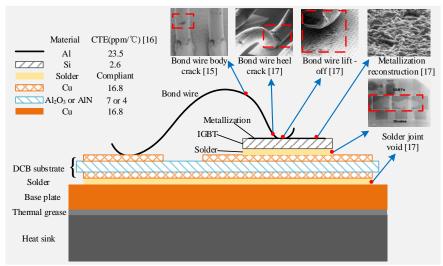

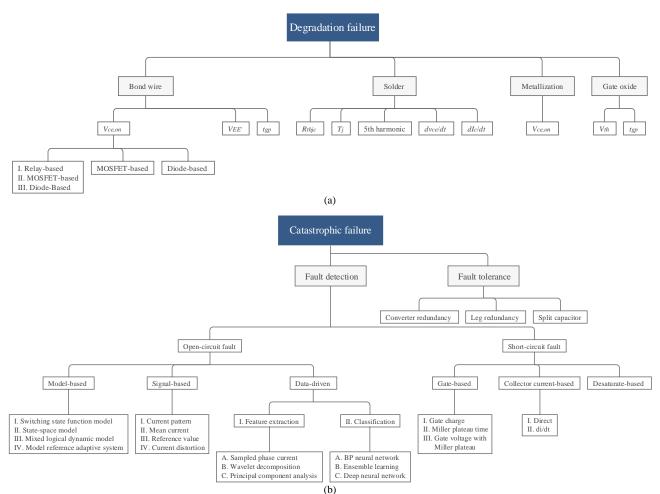

There are two types of failures in IGBT power devices: 1) wear-out failures and 2) catastrophic failures [13]. The first category of failure is package-related, where the failure is a consequence of accumulated damage due to the temperature, vibration, and humidity stresses on the devices [12]. Among those stressors, the temperature, more specific, the junction temperature is considered the most critical failure-inducer in IGBT power devices, especially for the wear-out failure [14, 15]. This can be further demonstrated using the cross-section view of an IGBT device, as shown in Fig. 3, where the wear-out failure images and the coefficient of thermal expansion (CTE) of the materials of a wire-bonded IGBT can be observed [15-20]. Due to the CTE mismatch between the

adjacent layers, bond wires, solder joints, and metallization layers, thermo-mechanical stresses in the case of temperature swings can accelerate the degradation (i.e., wear-out), leading to various wear-out failures like the bond wire lift-off, bond wire cracking, and metallization reconstruction. On the contrary, the IGBT catastrophic failures are not accumulated failures but triggered by a single overheat, overvoltage or overcurrent event. They are categorized as open-circuit faults and short-circuit faults. Open-circuit faults may be caused by the failure of gate drivers or bond wires, while short-circuit faults may occur due to unclamped inductive switching, hightemperature latch-up, second breakdown, or energy shocks [13]. Therefore, ensuring reliable operation of power electronic converters is of importance to avoid unexpected downtime of the entire systems, and hence to lower the maintenance efforts.

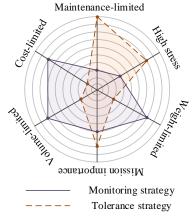

Many attempts should be made to address the two failures. In the literature, there are two ways to cope with the above IGBT failures, and by doing so, the reliability of the entire power converters can be improved. The first approach is based on reliability assessment schemes, which provides information about the health status of the power devices. By evaluating the degradation level, the condition-based maintenance can be performed before the catastrophic failures take place, which could reduce the maintenance costs and

Fig. 3. Cross-section view of a wire-bonded IGBT, where the possible wire-out failures are shown [15-17].

potential loss. In contrast, the other approach attempts to improve reliability by increasing the system operation redundancy for the two-level converters. That is to say, it is a post-fault approach. When faults are identified, the power electronic converters can still operate by activating the redundant unit (e.g., reconfiguring the power converter system). Clearly, the fault-tolerant strategies inevitably require more power semiconductor devices as well as more sophisticated control schemes (i.e., fault identification, isolation, and reconfiguration). Consequently, costs are rising. Nevertheless, it is highly application-dependent to select a cost-effective approach to guarantee the reliable operation of power electronic converters.

In light of the above, this paper reviews the possibilities to enhance power converter reliability. The performance and cost of the methods are benchmarked considering different application conditions, where the selection criteria are also presented. The rest of this paper is organized as follows. An overview of the monitoring methods is given in Section II, including degradation mechanisms and indicator extraction methods. In Section III, fault detection, isolation, and tolerant strategies are discussed. A comparison of these approaches under different working conditions is presented in Section IV. Finally, concluding remarks and discussions are provided in Section V.

#### **II. MONITORING OF DEGRADATIONS**

In order to achieve the highly-reliable operation of power converters, an alternative is to evaluate the health state and then perform pre-fault schemes before the converter system fail. This strategy requires an understanding of how the converter will degrade and how degradation can be identified, which are demonstrated in part A and B, respectively.

#### A. WEAR-OUT MONITORING

IGBT power devices age over time, and in this case, some parameters will drift away from the initial values accordingly. Thus, the parametric changes can be the indicators of wear-out failures. If the monitored parameters exceed the thresholds, an early warning replacing the aged device will be provided. Depending on failure mechanisms, different monitoring techniques should be applied. Thus, the following firstly reviews the failure mechanisms, which is followed by the corresponding indicators.

# 1) BOND WIRE FATIGUE MECHANISM

Power chips are wire-bonded during packaging. The wire bonds suffer from severe temperature swings due to switching. As shown in Fig. 3, there is a significant CTE mismatch between the bond wires (aluminum-based) and chips (silicon-based), and thus the shear stress is introduced to the interface. This further imposes repeated flexures on the aluminium wires, i.e., fatigue [21]. The bond wire fatigue, leading to the bond wire lift-off and/or bond wire cracking, is one of the dominant failures in IGBT modules. The bond wire lift-off initiates from the fracture at the tail of the bond, and it propagates to the

center. Eventually, the bond-wire is lift off and loses the electrical contact with the IGBT chip because of the spring effect of the aluminium wire loop [20]. For the bond wire cracking, according to [22], the heel of the bond wire suffers from larger stresses than other parts, and it becomes the most critical part in terms of cracking.

Nonetheless, the above two failures will contribute to an increase in the total resistance of the bond wires. Accordingly, the on-state collector-emitter voltage  $V_{ce,on}$  will increase [15, 18, 23-28]. Hence, the voltage  $V_{ce,on}$  can be an observable variable for bond-wire fatigue. For instance, an increase of 5 % [15, 18], 15% [25] and 20% [29] in the voltage  $V_{ce,on}$  from the initial value are considered as the thresholds. In [30], the threshold was set as  $1500/I_{Rated}$  with  $I_{Rated}$  being the rated current of the power device. Although the increase of the resistance leads to the on-state voltage increase, the change is sensitive and affected by various factors. First, the voltage  $V_{ce,on}$  is a temperature-sensitive electrical parameter (TSEP) [31], and it changes with the junction temperature  $(T_i)$  during operation. For example, in [25], a sudden drop followed by a sudden increase in the voltage  $V_{ce,on}$  was reported. It is because the solder fatigue occurs, the on-state voltage  $V_{ce,on}$  decreases dramatically, when the IGBT operates in the negative thermal coefficient area. Then, if the bond wire fatigue happens, the on-state voltage  $V_{ce,on}$  will increase. In order to eliminate the thermal effect, compensations should be applied. In [26, 32], the relationship between the on-state voltage  $V_{ce,on}$  and the junction temperature  $T_i$  is determined through power cycling tests. Subsequently, the thermal effect can be compensated by subtracting the temperature-induced voltage changes. Additionally, variations of  $V_{ce,on}$  are relatively small, compared to the original voltage, which requires highresolution measurements of the voltage  $V_{ce,on}$ . This may increase the cost of the hardware system. Meanwhile, small variations may be hidden due to the load current or temperature changes under harsh operating conditions [33].

The bond wire crack and lift-off will affect the parasitic parameters. In return, the changes of the parasitic parameters will inevitably affect the IGBT gate characteristics [34]. Therefore, the change of gate characteristics can be another indicator of the bond wire fatigue [16, 35-37]. More specifically, the bond wire lift-off will decrease the gateemitter capacitance and increase the parasitic inductance. Hence, the voltage drop induced between the power emitter and auxiliary emitter  $V_{EE}$  increases and the Miller-plateau duration  $t_{gp}$  declines [38, 39]. Meanwhile, the gate-emitter voltage  $V_{ge}$  and the collector-emitter voltage  $V_{ce}$  will rise faster during turn-on and turn-off, respectively, compared to the case without bond-wire fatigue [35]. In addition, the metallization reconstruction and solder fatigue take place simultaneously with the bond wire degradation. Fortunately, the change of gate characteristics caused by the bond wire fatigue is not significant [37]. However, the results are entirely different in [16] in terms of the gate-emitter voltage  $V_{ge}$ . There are no significant changes in the voltage  $V_{ge}$  until all the bond wires

TABLE I

MECHANISMS AND INDICATORS FOR DIFFERENT DEGRADATIONS IN IGBT MODULES.

| Degradations      | Mechanisms                                        | Indicators                          |  |  |

|-------------------|---------------------------------------------------|-------------------------------------|--|--|

|                   |                                                   | V <sub>ce,on</sub> [15, 18, 23-28]  |  |  |

| Bond wire fatigue | Combination of CTE mismatch and                   | $V_{ce}$ during turn-on [16, 35-37] |  |  |

| Bond wife laugue  | temperature swing                                 | $V_{EE'}$ [38]                      |  |  |

|                   |                                                   | $t_{gp}$ [39]                       |  |  |

|                   |                                                   | $R_{thjc} [40-42]$                  |  |  |

|                   |                                                   | $T_j$ [43, 44]                      |  |  |

| Solder fatigue    | Combination of CTE mismatch and temperature swing | 5 <sup>th</sup> harmonic [48]       |  |  |

|                   | ,                                                 | $\mathrm{d}v_{ce}/\mathrm{d}t$ [46] |  |  |

|                   |                                                   | $\mathrm{d}I_c/\mathrm{d}t$ [47]    |  |  |

| Metallization     | Combination of CTE mismatch and                   | Sheet resistance [50-55]            |  |  |

| reconstruction    | temperature swing                                 | $V_{ce,on}$ [45, 56]                |  |  |

|                   |                                                   | C-V plot [24]                       |  |  |

| Gate oxide        | High temperature (high electric filed             | $V_{th}$ [24]                       |  |  |

| degradation       | sometimes)                                        | $I_{ges}$ [37,57]                   |  |  |

|                   |                                                   | $t_{gp}$ [39, 58]                   |  |  |

are lifted off, which is in contrast with the results in [35]. Consequently, more attempts should be made to explore how different degradations contribute to the changes in the gate (switching) characteristics, and how the characteristics correlate to early wear-out failures.

#### 2) SOLDER FATIGUE MECHANISM

The solder fatigue is another dominant wear-out failure in IGBT modules. It is typically induced by the temperature wing and CTE mismatch. There are two solder layers in one IGBT device, as shown in Fig. 3: one between the chip and the substrate and one between the substrate and the baseplate. Due to the thermo-mechanical stress, delamination incidents, cracks and voids can occur in solder joints. Typically, cracks start from the edge of the joints, decrease the thermal dissipation path and increase the thermal resistance  $(R_{th})$ , which eventually leads to a higher junction temperature  $T_i$ . In the positive temperature coefficient area, the increased junction temperature results in more power losses and a further higher junction temperature. Hence, the positive feedback accelerates the failure of the IGBT device. To prevent this, the junction-to-case thermal resistance  $R_{thjc}$  (or junction-to-case thermal impedance) [40-42], and the junction temperature  $T_i$ [43, 44], are commonly used as indicators to monitor the solder fatigue in IGBT. Furthermore, considering the nonuniform distribution of the thermal resistance  $R_{th}$  on the case, due to the solder fatigue, the ratio of the junction-to-casecenter resistance to the junction-to-case-edge thermal resistance can also be utilized as an indicator [45]. Besides, the chip solder degradation leads to the rise of the gate-collector capacitance and trans-conductance, decrease of the gateemitter, which eventually cause the decline of voltage change rate  $dv_{ce}/dt$  and increase of current change rate  $dI_c/dt$  during turn-on [46, 47]. Additionally, because the junction temperature  $T_j$  influences the turn-off transient, low-order harmonics will be affected, when the solder fatigue occurs. Therefore, the 5th-order harmonic can also be used to monitor the solder fatigue incident [48].

#### 3) METALLIZATION RECONSTRUCTION MECHANISM

The aluminium metallization layer is deposited on the chip, providing electrical connection between the power dies and the emitter. Meanwhile, it maintains off-state parasitic components, which are inherent to the structures of power components [49]. The CTE mismatch between the chip (Si) and the aluminium layer (Al) is the reason for the metallization reconstruction, as shown in Fig. 3. Subsequently, the huge thermo-mechanical stress may exceed the elastic limit of the thin aluminium film, which may cause plastic deformation at the grain boundaries, leading to the extrusion of aluminium grains or cavitation effects at the grain boundaries [50]. In this case, the active cross-section of the metallization is reduced and the sheet resistance  $R_{sheet}$  increases linearly [50-55]. Thus, the collector-emitter voltage  $V_{ce,on}$  will have a linear increase, which can indicate the metallization reconstruction [45, 56].

# 4) GATE OXIDE DEGRADATION MECHANISM

The gate oxide degrades along with the above degradations. It is because the high temperature (e.g., a high electric filed) causes time-dependent dielectric breakdown or a high current causes hot electrons [57]. Due to the accumulated charges in the gate oxide, the capacitance-voltage characteristics will shift along with the gate voltage, and the threshold voltage ( $V_{th}$ ) will increase, consequently [24]. In addition, the electron injection may degrade the quality of the oxide, and lead to an increase in the gate leakage current ( $I_{ges}$ ) [37, 57]. Further, the accumulated charges and the gate oxide degradation increase

|                        | IVII            | THOOS TO WEASONE THE ON-STATE VOLTAGE                                            | V CE,ON∙ |                                                                                                                                 |

|------------------------|-----------------|----------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| Topology               | Blocking device | Additional hardware for each IGBT                                                | Cost     | Applicable condition                                                                                                            |

| Fig. 4 (a) [56]        | Relay           | 1 relay, 1 galvanic isolation                                                    | L        | <ul> <li>Offline application</li> </ul>                                                                                         |

| Fig. 4 (b) [28]        | Relay           | 1 relay, 1 amplifier, 1 inductive isolation                                      | L        | <ul> <li>Relatively high voltage</li> <li>Noisy environment</li> </ul>                                                          |

| Fig. 5 (c) [33]        | MOSFET          | 2 amplifiers, 1 MOSFET, 1 capacitor,<br>1 multivibrator, 1 falling edge detector | Н        | <ul><li>Online application</li><li>medium voltage</li></ul>                                                                     |

| Fig. 5 (a) [18]        | MOSFET          | 3 MOSFETs, 1 current source, 1 amplifier                                         | Н        | <ul> <li>Online application</li> <li>Low voltage</li> <li>Noisy environment</li> <li>High performance<br/>unrequired</li> </ul> |

| Fig. 5 (b) [15]        | MOSFET          | 1 MOSFET, 2 Schottky diodes,<br>1 zener diode                                    | Н        | <ul><li>Online application</li><li>Low voltage</li></ul>                                                                        |

| Fig. <b>6</b> (a) [28] | Zener diode     | 1 Zener diode, 1 diode, 1 amplifier,<br>1 inductive isolation                    | M        | <ul><li>Online application</li><li>Low voltage</li><li>Noisy environment</li></ul>                                              |

| Fig. <b>6</b> (b) [60] | diode           | 4 diodes; 1 current source; 1 amplifier                                          | M        | <ul><li> Offline application</li><li> High voltage</li></ul>                                                                    |

| Fig. <b>7</b> [25]     | multiplexer     | 2 amplifiers; 1 multiplexer                                                      | Н        | <ul><li>Online application</li><li>Low voltage</li></ul>                                                                        |

H-high; M-medium; L-low

the gate oxide capacitance and the Miller capacitance, which extends the  $t_{gp}$  [39, 58].

The major degradations in IGBT modules are discussed in the above and summarized in TABLE I. The mechanisms of those degradations are also shown, where the observable variables to indicate the corresponding degradation have also been presented. The prior-art methods using those indicators to identify degradations can be found in the literature, which are also given in TABLE I. The main problem of using the indicators to monitor the health state of the IGBT is that the indicators are influenced by more than one failure mechanisms. For example,  $t_{gp}$  is affected by both the bond wire lift-off and the gate oxide degradation, while their effects to  $t_{gp}$  are opposite. Furthermore, most of the indicators are temperature dependent, i.e., they cannot be able to reflect a correct health state unless they are measured at the same temperature. Thus, new indicators that dedicated to one failure mechanism or indicator combination that can effectively monitor the health state of the IGBT are expected in the future.

#### **B.** INDICATOR MEASUREMENT

The condition of the IGBTs can be monitored through the indicators. In this part, methods that are utilized to do so in the literature will be reviewed and compared.

# 1) MONITORING THE COLLECTOR-EMITTER ON-STATE VOLTAGE $V_{CE,ON}$

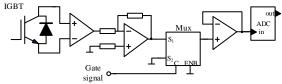

The on-state voltage  $V_{ce,on}$  can indicate the condition of the IGBT devices in terms of bond wire fatigue and metallization reconstruction. However,  $V_{ce,on}$  does not vary significantly, and thus measurements of a high resolution are required. In addition, the high voltage from the DC-link should be isolated and blocked to protect the measurement circuit, when the IGBT is off. Relays [28, 56], MOSFETs [15, 18, 33], diodes

[28, 59, 60], and multiplexers [25] are common blocking devices, which can be seen in TABLE II.

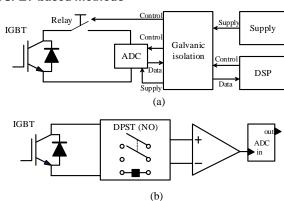

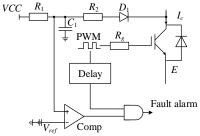

#### Relay-based methods

All the relay-based extraction methods for  $V_{ce,on}$  are offline schemes, since the response of relays is much longer than that of IGBT devices. In [56] (see Fig. 4(a)), the Analog-Digital Converter (ADC) is directly connected to the IGBT through a reed relay. When the power converter is operating, the relay is open to block the high voltage from the power electronic converter. Only when it stops or is forced to stop because of the measurement routine, a control signal will be generated to close the relay, and the ADC is then connected to the IGBT device, starting the measurement. Meanwhile, a simple current injection switching sequence is applied to turn on each IGBT. Thus, the on-state voltage  $V_{ce,on}$  of each IGBT can be measured with high noise immunity and high resolution (2-3 mV), as reported. The method in [28] (Fig. 4(b)) is similar to that in [56]. The difference is that it uses an amplifier to extract  $V_{ce,on}$ . Nonetheless, the relay-based measurement is a relatively simple but offline approach.

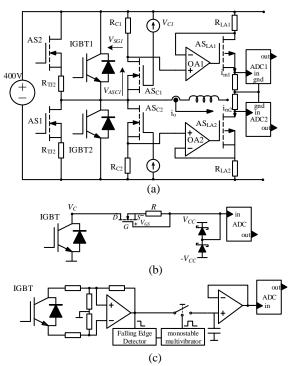

#### MOSFET-based methods

Fig. 4. Relay-based Vce,on measurement circuits [28, 56]

Fig. 5. MOSFET-based Vce,on measurement circuits [15, 18, 33].

Since MOSFETs switches at a higher switching frequency than IGBTs, MOSFETs are also used to block the voltage as an online or quasi-online method to measure the voltage  $V_{\text{ce,on}}$ . In [49] (Fig. 5(c)), when the IGBT is turned on,  $V_{ce}$  decreases, and the falling edge will be detected by the falling edge detector. Following, the monostable multivibrator triggers the MOSFET to measure  $V_{ce,on}$ . In [18], an online method to measure the voltage under high and low currents is proposed, as shown in Fig. 5(a). In this method, taking the upper switch as an example, for the measurement of  $V_{ce,on}$  under a high current, AS<sub>2</sub> is turned off, and the following are obtained

$$V_{RC1} = V_{ce,on} - V_{ASC1} = V_{C1} - V_{SG1}$$

(1)

$$V_{SG1} = V_{C1} - V_{Ce,on} + V_{ASC1}$$

(2)

where  $V_{RCI}$  is the voltage across  $R_{CI}$ ,  $V_{ASCI}$  is the Drain-Source voltage of  $AS_{C1}$ ,  $V_{C1}$  indicates the voltage of the current source and  $V_{SGI}$  represents the Source-Gate voltage of AS<sub>C1</sub>. According to (2), when the power converter is operating and IGBT1 is on, AS<sub>C1</sub> will turn on because  $V_{ce,on}$  is small and  $V_{SGI}$ is larger than the threshold voltage of  $AS_{C1}$  ( $V_{SGTHI}$ ). Then, it can be obtained from (1) that  $V_{ce,on}$  is almost equal to  $V_{RCI}$ , as the on-state resistance of AS<sub>C1</sub> is relatively small compared to  $R_{\rm C1}$ . When IGBT1 is off, the collector-emitter voltage  $V_{ce}$ increases and  $V_{SGI}$  is smaller than  $V_{SGTHI}$ , and  $AS_{C1}$  is turned off. Consequently, the off-state high voltage is blocked. To measure the voltage  $V_{ce,on}$  under a low current, AS<sub>2</sub> is turned on at the current zero-crossing, and  $R_{TJ2}$  is set to  $0.1 \times V_{dc}$  to inject a current of 100 mA into IGBT1. Then,  $V_{ce,on}$  can be measured as mentioned above. This needs a short period of zero load currents, which may affect the normal operation. Finally,  $V_{RCI}$  ( $V_{ce,on}$ ) is generated on the resistor  $R_{LAI}$  by the amplifier, which gives a current  $i_{ml}$  equal to  $VR_{Cl}/R_{LAl}$ , passing

Fig. 6. Diode-based Vce,on measurement circuits [28, 59, 60]

Fig. 7. Multiplexer-based Vce,on measurement circuits [25].

to the ADC through  $AS_{\rm LAI}$ . This current can be a few dozens of milliamperes. Thus, a high-immunity transmission is guaranteed and the galvanic insulation is avoided.

In [15], a simple method to measure  $V_{ce,on}$  is proposed, using a depletion-mode small-signal MOSFET with auxiliary components (see Fig. 5(b)). Notably, when the voltage  $V_{CC}$  is larger than the collector-emitter voltage  $V_{ce,on}$ , the input impedance of the measurement circuit becomes higher. When the upper switch  $T_{\text{UH}}$  is turned on,  $V_C = V_{ce,on} < V_{CC}$ . In addition to the high impedance,  $I_D$  cannot flow through the MOSFET, and  $V_{GS} = 0$ . Thus, the MOSFET is turned on and  $V_{out} = V_{ce,on}$ . When the upper switch  $T_{\text{UH}}$  is turned off,  $V_{ce}$  increases, and finally exceeds  $V_{CC}$ . Then,  $I_D$  flows through the MOSFET, and a voltage drop across R is produced, which makes  $V_{GS}$  smaller than the voltage threshold. Therefore, the MOSFET is turned off, the high voltage is blocked, and  $V_{out}$  is clamped to  $V_{CC}$ . However, because of the low voltage rating of the MOSFET, more MOSFETs will be required to block the DC-link voltage in high-voltage applications.

# Diode-based methods

Compared to the relay-based and MOSFET-based methods, measuring the voltage  $V_{\text{ce,on}}$  with diodes is a cheaper solution, especially for higher voltage applications. Fig. 6(a) shows a Zener diode-based circuit that measures the collector-emitter voltage [28]. The off-stage voltage is clamped by the Zener diode, and another diode with low stray capacitance is connected in series to reduce the stray capacitance effect. When the IGBT is turned on,  $V_{ce,on}$  can be measured by the amplifier. The resistors are used to limit currents and minimize the common-mode error. Nevertheless, when the IGBT is on, the clamped voltage on the resistance may induce variations, which may affect the operation of the power converter. In addition, limited by the rating of the Zener diode, this circuit in Fig. 6(a) is only effective and safe under 600-V off-stage voltages.

In [61], a measurement circuit for higher voltages is thus proposed (Fig. 6(b)), where  $D_1$  and  $D_2$  are forward-biased by

the current source when the IGBT is turned off. Thus, the offstage voltage is blocked. When the IGBT is turned on,  $V_{ce,on} = V_b - V_{D1}$ . Assuming that  $D_1$  is identical to  $D_2$ , we have  $V_{D1} = V_{D2}$ . Therefore,  $V_{ce,on} = V_b - V_{D2} = V_b - (V_a - V_b) = 2V_b - V_a$ . This is realized with two amplifiers by setting  $R_5 = R_6$  and  $R_2/R_1 = R_4/R_3$ . In this case, the difference between the two diodes may lead to measurement errors.

#### Multiplexer-based methods

In [25], a two-to-one multiplexer circuit is used to filter out the off-state data. An amplifier is adopted to scale down the on-state voltage. When the gate signal is active, the scaled voltage  $V_{ce,on}$  will be selected as the output. Otherwise, zero will be the output. Limited by the scaling circuit, this extractor cannot work under high voltage. The detailed circuit is given in Fig. 7.

The on-state voltage of IGBT measuring methods have been discussed above and concluded in TABLE II. It can be a reference when selecting appropriate and cost-effective methods to measure or monitoring the collector-emitter voltage, through which the fatigue assessment in IGBT modules can be enabled. The relay-based methods are preferred for the offline conditions as they can fulfil the task with the lowest cost. However, the diode outperforms the other methods if both the cost and the online performance are taken into consideration.

Note that  $V_{ce,on}$  depends on the temperature and current, which requires the measurement at the same working point and same temperature. To tackle this problem, [62] decomposes the voltage into three parts and gives the temperature and current dependent formula of each part. In this way, the degradation caused component can be estimated even the temperature or current varies. It should be noted that the accuracy will be limited by the precision of the formula. Besides, the so-called inflexion point where  $V_{ce,on}$  almost keeps constant with different temperatures could be another solution to avoid the influence of the temperature [63].

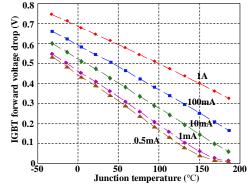

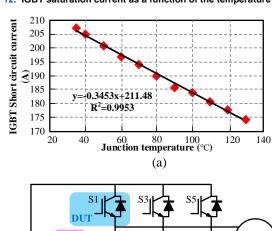

# 2) MONITORING THE JUNCTION TEMPERATURE $T_J$ The junction temperature $T_i$ can be measured by

The junction temperature  $T_j$  can be measured by a thermocouple sensor or infrared camera directly, or by the thermo-sensitive electrical parameters (TSEPs) indirectly. In practice, however, it is impossible to perform the junction temperature measurement directly without modifying the package or housing (e.g., open the module and remove dielectric gel). As a result, the direct measurement is limited for temperature monitoring in practice. Although NTC thermistors are provided in most modules, the calibration between  $T_j$  and the thermistor is lacked. TSEPs, dependent on the junction temperature  $T_j$ , are therefore preferred to estimate the junction temperature, since they can be measured directly.

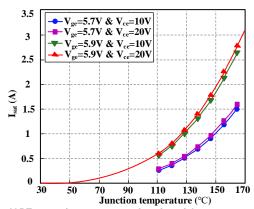

Methods by TSEPs include static and dynamic approaches. The first one uses the static electrical parameters to estimate  $T_j$ . The static parameters can be the collector-emitter voltage under high currents  $V_{ce,lhigh}$  [15, 64-67], collector-emitter voltage under low currents  $V_{ce,llow}$  [31, 40, 67-70], gate internal resistance  $R_{G,int}$  [71-73], saturation current  $I_{sat}$  [74-77], short

circuit current  $I_{sc}$  [78], and gate-emitter voltage  $V_{ge}$  [79]. The other approach uses dynamic electrical parameters to estimate  $T_j$ . Such dynamic parameters include the threshold voltage  $V_{th}$  [31, 33, 80-83], Miller-plateau voltage  $V_{gp}$  [84], turn-on delay time  $t_{don}$  [85], maximum current slope of turn-on  $dI/dt_{max,on}$  [85], turn-off time  $t_{off}$  [85, 86], turn-off delay time  $t_{doff}$  [87], the peak value of  $V_{EE'max}$  during turn-off [88, 89] and the flatband voltage  $V_{fb}$  [90]. The following describes the above methods.

# Temperature Estimation by Vce,lhigh

The relationship between  $V_{ce,lhigh}$  and  $T_j$  is not exactly linear. With an acceptable range of errors, the relationship can be approximated as [65, 66]

$$V_{ce,lhigh} = V_{ceo} + \underbrace{k_{Vceo} \cdot \left(T_{j} - T_{jo}\right)}_{V_{ce} \text{ increse on the chip}} + \underbrace{I_{c} \cdot \left[r_{o} + k_{ro} \cdot \left(T_{r} - T_{ro}\right)\right]}_{V_{ce} \text{ increse on the series resistance}}$$

$$V_{ce} \text{ increse due to temperature vatiation}$$

$$- \underbrace{k_{ge} \cdot \Delta V_{ge}}_{V_{ce} \text{ increse due to } V_{ce} \text{ variation}}_{V_{ce} \text{ increse due to } V_{ce} \text{ variation}}$$

(3)

where  $V_{ce,Ihigh}$  is the measured collector-emitter voltage under high currents,  $T_{jo}$  denotes the base junction temperature,  $V_{ceo}$ is the on-state collector-emitter voltage at  $T_{jo}$ ,  $T_r$  indicates the series resistance temperature,  $T_{ro}$  represents the series resistance base temperature,  $r_o$  is the series resistance at  $T_{jo}$ ,  $k_{Vceo}$  and  $k_{ro}$  indicate the temperature coefficient of  $V_{ce}$  and  $r_o$ , repsectively,  $\Delta V_{ge}$  is the gate-emitter voltage variation,  $k_{ge}$ denotes the coefficient of  $\Delta V_{ge}$ , and  $I_c$  means the collector current.

Practically, it is difficult to measure  $V_{ce}$  from the module terminals because the chip is packaged inside the module. The

Fig. 8. I-V characteristics of an IGBT.

Fig. 9.  $V_{co,llow}$  of an IGBT as a function of the junction temperature  $T_j$  for different low currents [31].

measured voltage  $V_{ce,Ihigh}$  consists of  $V_{ce}$  and the series packaging resistance voltage. In addition,  $V_{ce,Ihigh}$  is affected by  $T_j$ ,  $T_r$  and  $V_{ge}$ . However,  $V_{ge}$  can be treated as a constant in normal operation mode. Therefore,  $T_j$  can be estimated as

$$T_{j} = \frac{V_{ce,lhigh} - V_{ceo} - I_{c} \cdot \left[ r_{o} + k_{ro} \cdot \left( T_{r} - T_{ro} \right) \right]}{k_{Vceo}} + T_{jo} \cdot \tag{4}$$

In the literature, it is considered that  $T_r$  is equivalent to  $T_j$ . Assuming that the temperature distribution is homogeneous when the coefficients  $k_{ro}$  and  $k_{vceo}$  are identified by experiments.  $T_{j\_est}$  is then obtained as

$$T_{j\_est} = \frac{V_{ce,Ihigh} - \overbrace{(V_{ceo} + I_c \cdot r_o)}^{V_{ceo} \text{ at base temperature } (I_c)}}{k_{Vceo} + I_c \cdot k_{ro}} + T_{jo}.$$

(5)

However, it should be pointed out that  $T_r$  and  $T_j$  are not equal due to the non-uniform temperature distribution. In order to improve accuracy,  $T_r$  should be estimated as a prerequisite. According to [66], it gives

$$T_{j} - T_{r} = \alpha \cdot \left( T_{j_{-est}} - T_{H} \right) \tag{6}$$

where  $T_H$  is the heatsink temperature and  $\alpha$  is the scaling factor that is obtained by experiments. With (6), the temperature  $T_j$  can be estimated accurately as

$$T_{j_{-est}} = \frac{V_{ce, lhigh} - V_{ce, B} + \alpha \cdot k_{ro} \cdot I_{c} \left( T_{j_{-est}} - T_{H} \right)}{k_{Vceo} + I_{c} \cdot k_{ro}} + T_{jo}$$

(7)

in which  $V_{ce,B}$  is the voltage  $V_{ce}$  at the base temperature. It can be found in (7) that the estimated temperature  $T_j$  using  $V_{ce,Ihigh}$  is sensitive to the coefficients  $k_{Vceo}$ ,  $k_{ro}$ , and the collector current  $I_c$ . The sensitivity varies from 1 mV/°C (300 A) to 5 mV/°C (1000 A) [67]. In addition, the online junction temperature estimation requires measuring  $V_{ce,Ihigh}$ ,  $I_c$ , and some predefined parameters.

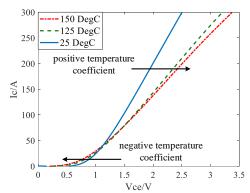

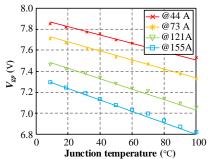

#### Temperature Estimation by Vce,llow

Fig. 8 shows the typical I-V characteristics of an IGBT. Unlike the positive temperature coefficient for the high current, it can be seen that the temperature coefficient for the low current is negative. Compared to the method using  $V_{ce,Ihigh}$ , utilizing  $V_{ce,Ilow}$  neglects the series packaging resistance because its voltage drop is relatively low. At the same time, the self-heating effect can be eliminated. Thus, it has higher accuracy and stronger linearity than the previous method (i.e., using  $V_{ce,Ihigh}$ ). In this case, the relation can be expressed as

$$V_{ce,llow} = V_{ceo} + k_{Vceo} \cdot \left(T_j - T_{jo}\right) \tag{8}$$

where  $k'_{Vceo}$  is the temperature coefficient for the low current. Fig. 9 depicts the voltage  $V_{ce,Ilow}$  of an IGBT as a function of the junction  $T_j$  under various low currents. It can be observed that the voltage change rate in respect to the junction temperature is within the range of -0.19 mV/°C to -0.28 mV/°C, where the current varies from 0.5 mA to 1 A. Although the injection of lower currents leads to a higher change rate (absolute value), it becomes non-linear at high temperatures, as shown in Fig. 9. In most applications, the load current is normally much higher than the currents in Fig. 9. In this case, the power converter should be stopped first to allow the low current injection to estimate the junction temperature.

Fig. 10. Temperature estimation using the resistance  $R_{G,int}$  (a)  $R_{G,int}$  measurement circuit [72] and (b) gate driver RLC network [71].

Fig. 11. Temperature estimation using the resistance  $R_{G,int}$ : (a) gate peak voltage detection circuit and (b) calibration between  $R_{G,int}$  and  $T_j$  [71].

This may be not easy to implement. Nonetheless, online current injection and voltage drop measurement strategies have been proposed in [68, 70]. However, the injection and measurement window may decrease system performance. It should be noted that the low current should be injected to measure the voltage  $V_{ce,llow}$  immediately, after the load current is suspended and the transient has passed. By doing so, the maximum error of the estimated junction temperature  $T_j$  caused by the cooling system can be reduced. The advantage of this method is that the self-heating effects can be avoided and the packaging degradation caused voltage drop is negligible.

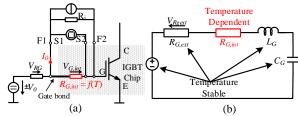

# Temperature Estimation by R<sub>G,int</sub>

The thermo-sensitive resistance  $R_{G,int}$  is a resistor in the center of the die. By calculating its temperature, the junction temperature  $T_i$  can be estimated. Nevertheless, it is almost impossible to implement the measurement during the converter operation without opening the module and adding measurement circuits, as shown in Fig. 10(a). To improve this, Baker et al. proposed a peak gate current method, where  $R_{G,int}$ is considered as the equivalent series resistance (ESR) of both the gate-emitter capacitor  $C_{ge}$  and the gate-collector capacitor  $C_{gc}$ . Therefore, the gate driver *RLC* network can be depicted in Fig. 10(b) [71]. During the turn-on delay, both  $C_{ge}$  and  $C_{gc}$  are stable before the gate voltage reaches the threshold voltage  $V_{th}$ . The gate current  $I_g$  can be taken as a step response of the *RLC* network and the parasitic gate inductor should satisfy  $R^2>4L/C$ . Hence, the *RLC* network is overdamped, and  $I_g$  can be approximated by

$$I_{g} = \frac{V_{step}}{R_{G,int} + R_{ext}} e^{-\frac{t}{(R_{G,im} + R_{G,ext})C_{g}}}.$$

(9)

Given that the gate capacitance is stable, the gate inductor then has a negligible effect on the overdamped circuit. Assuming that the external resistor is not strongly dependent

on the temperature, the resistance  $R_{G,int}$  can be estimated by (10) when the peak gate current is detected.

$$R_{G,int} = \frac{V_{step}}{I_{peak}} - R_{G,ext} \tag{10}$$

It should be noted that the gate driver voltage is affected by the high  $dV_{ce}/dt$  and temperature. To create an exact step voltage, the difference between the gate voltage before  $(V_{G,neg})$  and after turn-on  $(V_{G,pos})$  is utilized. Considering that the voltage is easier to measure than the current,  $V_{peak}/R_{G,ext}$  is used to calculate the peak current, where  $V_{peak}$  is the peak voltage on the external gate resistor. Fig. 11(a) shows the detection circuit for  $V_{peak}$  [71]. Finally,  $R_{G,int}$  can be measured as

$$R_{G,int} = \frac{V_{G,neg} - V_{G,pos}}{\frac{V_{peak}}{R_{G}}} - R_{G,ext}$$

(11)

Then, with calibration,  $T_j$  can be estimated, as shown in Fig. 11 (b) [71]. There is a strong linear relationship between the resistance and the estimated temperature, as shown in Fig. 11(b). The advantage of this method is that it is immune to the load current and the measurement circuit can be integrated into the driver. Nevertheless, measurement errors may appear due to the assumptions.

# Temperature Estimation by Isat

If the self-heating effect is neglected, the IGBT saturation current can be calculated as [77]

$$I_{sat} = \left(1 + \beta_{PNP}\left(T_{j}\right)\right) \frac{\mu_{ns}\left(T_{j}\right)C_{OX}Z_{c}}{2L_{c}} \cdot \left(V_{GS} - V_{th}\left(T_{j}\right)\right)^{2}$$

(12)

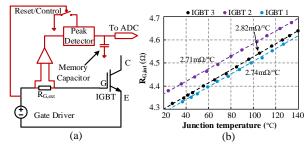

where  $\beta_{PNP}$  indicates the PNP transistor current gain,  $\mu_{ns}$  is the surface mobility of electron,  $C_{OX}$  denotes the oxide capacitance,  $Z_c$  is the channel width, and  $L_c$  is the channel length. It is nonlinear and there is the coupling with other thermo-sensitive parameters, as demonstrated in Fig. 12 [31]. Due to the nonlinearity and the coupling, it is not recommended to estimate  $T_i$  using the saturation current  $I_{sat}$ .

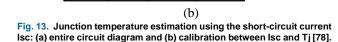

# Temperature Estimation by Isc

In [78], a short-circuit current-based estimation method is proposed. The short-circuit pulse is introduced by a bypass IGBT, as shown in Fig. 13(a). When the Device under Test (DUT) is on, the bypass IGBT will be triggered for a short time to create a short current pulse, whose amplitude is approximately linear in respect to the junction temperature  $T_j$ . By measuring the amplitude of the short-circuit current,  $T_j$  can be estimated, as exemplified in Fig. 13(b). This method has a relatively high sensitivity which is about -0.35 °C/A. Meanwhile, it is immune to the DC-link voltage. However, due to the risk of short-circuit, an additional protection scheme is required. Furthermore, additional control for the bypass IGBT and high-current sensor for the short-circuit pulse are needed to realize this.

# Temperature Estimation by Vge

VOLUME XX. 2017

The gate-emitter voltage  $V_{ge}$  is another TSEP for the junction temperature estimation. *Berning et al.* proposed a circuit to estimate  $T_j$ , as shown in Fig. 14(a) [91]. In order to

eliminate the voltage spike induced by the oscillation-free gate resistor, the difference between the cathode voltage and the gate voltage is utilized. The results show good linearity and the sensitivity is within 11.6 mV/°C to 13 mV/°C, with the collector current being 1 A to 25 A., as shown in Fig. 14(b). However, this method is an offline approach, as the bias current source, consisting of a 62-V voltage source and a 75-k $\Omega$  resistor, will affect the normal conversion operation.

#### Temperature Estimation by Vth

The threshold voltage  $V_{th}$  of an IGBT is the gate-emitter voltage when the device begins to turn-on. According to [81],  $V_{th}$  can be described as

$$V_{th}\left(T_{j}\right) = \frac{\kappa}{q} \cdot \ln \left\{ \frac{N_{A}}{N_{D}} \right\} \cdot T_{j} - \frac{Q_{f} + Q_{m} + Q_{ot}}{C_{ox}} + \frac{\sqrt{4 \cdot \varepsilon_{Si} \cdot N_{A} \cdot \kappa}}{C_{ox}} \cdot \sqrt{\ln \left\{ \frac{N_{A}}{n_{i}\left(T_{j}\right)} \right\} \cdot T_{j}}$$

(13)

in which  $\kappa$  is the Boltzmann constant, q denotes the elementary charge,  $N_A$  indicates the concentration of acceptors,  $N_D$  implies concentration of donors,  $Q_f$  is the fixed oxide charge,  $Q_m$  is the charge of mobile ions,  $Q_{ot}$  indicates the intrinsic charge within the oxide,  $C_{ox}$  denotes area specific capacity of the oxide layer,

Fig. 12. IGBT saturation current as a function of the temperature [31].

9

Fig. 14. Temperature Estimation using the gate-emitter voltage  $V_{ge}$ : (a) cathode to gate voltage measurement circuit (b) calibration with  $T_j$  [911.

Fig. 15. Temperature estimation using  $V_{th}$ : (a) calibration with  $T_j$  (b) measurement circuit [81, 82, 92].

Fig. 16 Comparison between the prediction and the sensing results of  $V_{qp}$  method [84]

$\varepsilon_{Si}$  indicates permittivity of silicon, and  $n_i$  is intrinsic carrier density.

From (13), it can be found that  $V_{th}$  only depends on the junction temperature  $T_j$ , as all the other parameters are fixed. However, it is not strictly linear. Fortunately, in the range of operating temperatures, the relationship is nearly linear. In this case,  $V_{th}$  decreases linearly with the temperature due to the positive correlation between  $n_i$  and  $T_j$ . The sensitivity varies from -6 mV/°C to -9 mV/°C in different conditions [81, 92].

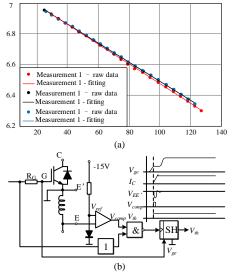

In order to measure  $V_{th}$  online, the parasitic inductance  $L_{\sigma E}$  between the Kelvin and power emitter terminals is utilized, as discussed in [81, 82, 93] (see Fig. 15(b)). When the IGBT starts to turn-on and the current begins to flow through  $L_{\sigma E}$ , the parasitic voltage  $V_{EE'}$  is induced. Then, by comparing  $V_{EE'}$  with the reference voltage, the trigger pulse is produced. With NAND-gates and the driver output voltage, the measurement pulse is generated, which can enable the sample-and-hold (SH) gate to hold  $V_{th}$  and disable the SH when the freewheeling diode is on. This measurement circuit can be integrated into the gate driver due to the common ground reference. However, the reference voltage should be set carefully. Otherwise,  $V_{th}$  may not be measured as the turn-on transient is also relevant to the junction temperature.

#### Temperature Estimation by Vgp

The Miller-plateau voltage  $V_{gp}$  can be calculated by (14) [84].

$$V_{gp}(T_j) = \sqrt{\frac{I_c}{g_m(T_j)}} + V_{th}(T_j)$$

(14)

Where  $g_m$  is the trans-conductance. Since  $V_{th}$  decreases and  $g_m$  increases with the rise of the temperature, it can be concluded that  $V_{gp}$  decreases monotonically with the temperature rise. In practice, it is difficult to measure  $V_{gp}$  because  $R_{G,int}$  is inaccessible. Thus, one has to estimate  $V_{gp}$  through  $V_{meas}$  by (15).

$$\begin{cases} V_{meas} = V_{gp} + \Delta V \\ \Delta V = (V_d - V_{gp}) \cdot \frac{x}{1+x} \text{ with } x = \frac{R_{G,int}}{R_{G,ext}} \end{cases}$$

(15)

Note that  $R_{G,int}$  is temperature dependent, the compensation must be made before using it to estimate  $T_j$ . According to the sensitive and error analysis, the precise knowledge of  $g_m$  is crucial for the estimation. However, the small error of the current is acceptable which implies that the averaged phase current utilized in the control software is applicable here. The comparison between the prediction and the sensing results for a hybrid IGBT module FS800R07A2E3B13 is given in Fig. 16. The sensitivity is 1.5 to 7 mV/K over the entire operating range. Consider the fact that it is affected by the load current, the current dependency should be understood first. Otherwise, it must work at the same current, which limits its application.

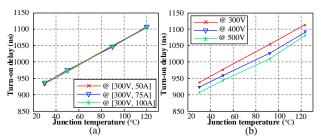

# Temperature Estimation by tdon

The turn-on delay  $t_{don}$  is the time between the start of the gate-emitter voltage  $V_{ge}$  rising and the beginning of the collect current  $I_c$  rising. It can be described as [85]

Fig. 17. Temperature estimation using  $t_{don}$  under different: (a) currents and (b) voltages (same current) [85].

Fig. 18. Temperature estimation using: (a)  $dl_d/dt_{max,on}$  and (b)  $t_{off}$  [85]

Fig. 19. IGBT turn-off characteristics with module parasitic inductors [78].

Fig. 20. Correlation between  $t_{doff}$  and  $T_j$  under different voltages: (a) 1000-A load current and (b) 1200-A load current [87].

$$t_{don} = \left(R_{G,ext} + R_{G,int}\right) \cdot C_g \cdot ln \left(1 - \frac{V_{th}}{\Lambda U}\right). \tag{16}$$

As aforementioned,  $R_{G,int}$  increases and  $V_{th}$  decreases with the increase of the junction temperature  $T_i$ . As a result,  $t_{don}$  is sensitive to the junction temperature. More specifically, it increases with the rise of temperature when the temperature effect of  $C_g$  is neglected. When referring to the dependency,  $V_{th}$  only depends on  $T_j$  and  $R_{G,int}$  is only affected by  $T_j$ . As for  $C_g$ , it consists of the oxide capacitance  $C_{ox}$  and depletion capacitance  $C_{dep}$ .  $C_{ox}$  can be seen as a constant, while  $C_{dep}$  is governed by

$$C_{dep} = A \sqrt{\frac{\varepsilon \cdot e_0}{2 \cdot V_{ce}} \cdot \frac{N_A \cdot N_D}{N_A + N_D}}$$

(17)

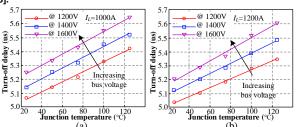

where A represents the surface area of the capacitor and  $e_0$ indicates the unit charge. It is dependent on the DC-link voltage  $V_{dc}$  [85]. In addition, the intrinsic carrier concentration increases at higher temperatures, which indicates that  $C_{dep}$ increases along with the temperature increase. Therefore,  $t_{don}$ is monotonically temperature-dependent and it is affected by  $V_{dc}$ . However, it is immune to the load current. Consider that  $V_{dc}$  is almost kept constant, this method is more applicable than the current-dependent methods. The delay time  $t_{don}$  versus the junction temperature  $T_i$  is depicted in Fig. 17, and the sensitivity of  $T_i$  is about 2 ns/°C.

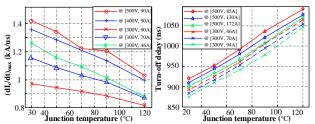

# Temperature Estimation by dlc/dtmax,on

The turn-on current slope is related to the gate-emitter

$$\frac{dI_{c}/dt}{dV_{ge}/dt} = \left(\frac{1}{1 - \alpha_{PNP}(T)}\right) \cdot \left[\mu(T) \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(u_{ge} - V_{th}(T)\right)\right]$$

$$\xrightarrow{PNP \ reginstrate} \left(18\right)$$

where  $\alpha_{PNP}$  is the gain of the inherent bipolar transistor,  $\mu$  is the mobility, W is the width, and L is the length of the MOS channel. According to (16), the temperature-dependence caused by  $\alpha_{PNP}$ ,  $\mu$  and  $V_{th}$  on  $dI_c/dt_{max,on}$  can be obtained [85]. The correlation between  $dI_c/dt_{max,on}$  and  $T_i$  under different currents and voltages is shown in Fig. 18(a). The relation is not as linear as the TSEPs above. As for the sensitivity, it is about 40 A/( $\mu$ s·°C), which is affected by the DC-link voltage and load current.

#### Temperature Estimation by toff

Equation (19) gives the description of the turn-off time  $t_{off}$ [82]. As it contains  $g_m$  and  $V_{th}$  both decrease with the increase of the junction temperature  $T_i$ , the turn-off time  $t_{off}$  is also a TSEP. The correlation between  $t_{off}$  and  $T_i$  under different currents and voltages is shown in Fig. 18(b).

$$t_{off} = R_G \cdot C_{ISS} \cdot ln \left( \frac{I_C}{g_m(T)V_{th}(T)} + 1 \right)$$

(19)

Where R represents the gate resistance and  $C_{ISS}$  is the input capacitance.

# Temperature Estimation by tdoff

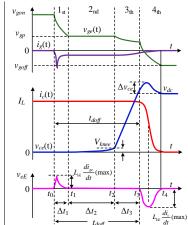

The turn-off delay  $t_{doff}$  can be divided into three parts, denoted as  $\Delta t_1$ ,  $\Delta t_2$ , and  $\Delta t_3$ , which are shown in Fig. 19 and described as (20)~(22) [87].

$$\Delta t_1 = R_G(T)C_{ge} + C_{gc}ln\frac{V_{gon} - V_{goff}}{V_{op}(T) - V_{ooff}}$$

(20)

$$\Delta t_2 = \frac{L_M \, q n_{ac}}{\Delta J_{ch}} \tag{21}$$

$$\Delta t_{2} = \frac{L_{M} q n_{ac}}{\Delta J_{ch}}$$

$$\Delta t_{3} = \sqrt{\frac{2 \cdot \varepsilon \cdot q \cdot V_{dc}}{N_{B} + \frac{J_{c}}{q v_{ce}}} \cdot \frac{1}{\Delta J_{ch}}}$$

$$(22)$$

VOLUME XX. 2017 11

Fig. 21. Correlation between  $V_{EE',max}$  and  $T_j$  under different currents: (a)  $V_{dc} = 700 \text{ V}$  and (b)  $V_{dc} = 900 \text{ V}$  [88].

Fig. 22 (a) Vfb measuring circuit (b) different values of Vfb at different temperature [90].

Where  $V_{gp}$  is the Miller-Plateau voltage,  $L_M$  presents the half physical length under gate region,  $n_{ac}$  denotes carrier concentration,  $J_c$  is the collector current density, and  $\Delta J_{ch}$  indicates the electron current density reduction in the MOS channel under the gate region.

As shown in (18), the first stage  $-\Delta t_I$  is mainly affected by  $R_G$  and  $V_{gp}$ . Consider that both of them have positive temperature coefficients,  $R_G$  and  $V_{gp}$  increase with the rising junction temperature  $T_j$ , and similarly,  $\Delta t_I$  increases. For  $\Delta t_2$  and  $\Delta t_3$ , when  $T_j$  increases,  $\alpha_{PNP}$  and  $n_{drI}$  increase at the same time [94, 95]. In addition,  $\Delta J_{ch}$  can be described as

$$\Delta J_{ch} = \frac{2\Delta V_{ge} \sqrt{\left(1 - \alpha_{PNP}\right) K_c I_c}}{A_c} = \frac{\left(1 - \alpha_{PNP}\right) g_m \Delta V_{ge}}{A_c}$$

(23)

implying that it decreases with the temperature rise. Therefore,  $\Delta t_2$  and  $\Delta t_3$  will increase when the junction temperature  $T_i$  rises.

Due to the reason that  $\Delta t_I$ ,  $\Delta t_2$  and  $\Delta t_3$  increase with  $T_j$ , the turn-off delay  $t_{doff}$  increases monotonically, when  $T_j$  goes up. Further, it can be found from (18)~(20) that  $t_{doff}$  is also affected by the load current and DC-link voltage. The correlation between  $t_{doff}$  and  $T_j$  under different load currents and voltages is shown in Fig. 20. It indicates that the sensitivity is about 4 ns/°C. However, it varies slightly according to the load currents and DC-link voltages. In Fig. 19, it can be found that there are voltage pulses across  $L_{\sigma E}$  at the beginning and the end of the turn-off delay, both of which can be utilized to measure  $t_{doff}$ .

### Temperature Estimation by VEE'max

In the turn-off period, the negative voltage pulse across  $L_{\sigma E}$  is induced by the drop of  $I_c$ , which can be described as [88]

$$V_{EE} = -L_{\sigma E} \cdot \frac{dI_c}{dt} \bigg|_{max}$$

(24)

where  $V_{EE}$  is the voltage between the Kelvin emitter and power emitter.

Hence, instead of measuring  $dI/dt_{max,on}$ , the maximum voltage  $V_{EE',max}$  can also be used to estimate the junction temperature. The correlation between  $V_{EE',max}$  and  $T_j$  under different load currents and voltages is depicted in Fig. 21. The sensitivity varies from -29.11 mV/°C to -74.72 mV/°C, depending on the DC-link current and load current. In [89],  $T_j$  with respect to the  $V_{EE',max}$  and  $I_c$  is modelled through least-squares fitting in the form of (25). Hence, it could be more practicable in the real-time  $T_j$  estimation.

$$T_{j} = \frac{1}{AI_{c} + B} \left( V_{EE',max} + C + D \cdot I_{c} + E \cdot I^{2} \right)$$

(25)

#### Temperature Estimation by V<sub>fb</sub>

The temperature dependence of  $V_{fb}$  could be attributed to the ionic contaminants induced mobile oxide charges  $Q_{ox}$  which changes with temperature [90]. Thus, according to (26),  $V_{fb}$  is a TSEP.

$$\Delta V_{fb} = \frac{\Delta Q_{ox}}{C_{ox}} \tag{26}$$

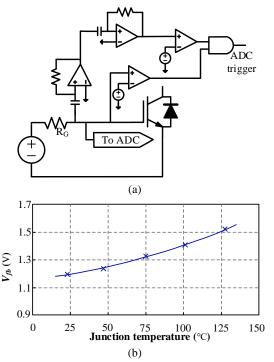

The measuring circuit and the different values of  $V_{fb}$  are given in Fig. 22(a) and Fig. 22(b), respectively [90]. The gate capacitance reduces sharply when the gate voltage reaches  $V_{fb}$  due to the depletion capacitor is added in series with the oxide capacitor. As a result, the gate voltage increases faster before it reaches  $V_{fb}$ . Two differentiators and two comparators are utilized to capture this moment and trigger the ADC to sample  $V_{fb}$  at this time. The results of an Infineon FF1000R17IE4 module is given in Fig. 22(b) with the sensitivity at about 3.1 mV/°C. It turns out that the temperature dependency of  $V_{fb}$  is not strictly linear, which may limit the practical performance. Nevertheless, its advantage is that it is measured before the

TABLE III

COMPARISON OF DIFFERENT JUNCTION TEMPERATURE ESTIMATION METHODS.

| Classific ation | TSEP                              | Onlin<br>e | Selectivity        | Linearity | Sensitivity                      | Additional hardware<br>For online<br>measurement*                      | Effects on converter | Integrability |

|-----------------|-----------------------------------|------------|--------------------|-----------|----------------------------------|------------------------------------------------------------------------|----------------------|---------------|

|                 | V <sub>ce,Ihigh</sub> [15, 64-67] | Yes        | $T_j$ , $I_c$      | Medium    | 1 ~ 5<br>mV/°C                   | Same with $V_{ce,on}$ online methods                                   | Maybe                | No            |

| Static          | $V_{ce,Ilow}$ [31, 40, 67-70]     | Yes        | $T_{j}$            | High      | -0.19 ~<br>-0.28<br>mV/°C        | Current source; $V_{ce}$ measurement;<br>Additional control            | Yes                  | No            |

|                 | $R_{G,int}$ [71-73]               | Yes        | $T_{j}$            | High      | $0.9 \sim 2.8$<br>m $\Omega$ /°C | Amplifier; Peak<br>detector; reset switch                              | No                   | Yes           |

| TSEPs           | $I_{sat}$ [74-77]                 | Yes        | $T_j, V_{dc}$      | Not       |                                  | Additional sensor                                                      | No                   | No            |

|                 | <i>I<sub>sc</sub></i> [78]        | Yes        | $T_j,V_{dc}$       | Medium    | -0.35 °C/A                       | Additional protection<br>circuit; Bypass IGBT;<br>High current sensor; | Yes                  | No            |

|                 | $V_{ge} \ [79]$                   | No         | $T_j, V_{dc}, I_c$ | High      | 11.6 ~ 13<br>mV/°C               |                                                                        |                      | No            |

|                 | V <sub>th</sub> [31, 49, 80- 83]  | Yes        | $T_{j}$            | High      | -6 ~ -9<br>mV/°C                 | Amplifier; NAND-<br>gates; Sample-and-<br>hold gate                    | No                   | Yes           |

|                 | $V_{gp}$ [84]                     | Yes        | $T_j, I_c$         | Medium    | 1.5 ~ 7<br>mV/°C                 | Not mentioned                                                          | No                   | Yes           |

|                 | $V_{fb}$ [90]                     | Yes        | $T_{j}$            | Low       | 3.1 mV/°C                        | Differentiator;<br>Comparator;<br>AND gate                             | No                   | Yes           |

| Dynamic         | t <sub>don</sub><br>[85]          | Yes        | $T_j, V_{dc}$      | High      | 2 ns/°C                          |                                                                        | No                   | Yes           |

| TSEPs           | $\frac{dI/dt_{max,on}}{[85]}$     | Yes        | $T_j, I_c, V_{dc}$ | Low       | 40<br>Α/(μs·°C)                  | Not mentioned, but could be measured                                   | No                   | Yes           |

|                 | <i>t</i> <sub>off</sub> [85, 86]  | Yes        | $T_j, I_c, V_{dc}$ | Medium    | 2 ns/°C                          | through parasitic inductance between                                   | No                   | Yes           |

|                 | $t_{doff}$ [87]                   | Yes        | $T_j, I_c, V_{dc}$ | High      | 4 ns/°C                          | the Kelvin and power<br>emitter terminals                              | No                   | Yes           |

|                 | $V_{EE'max}$ [88, 89]             | Yes        | $T_j, I_c, V_{dc}$ | High      | -29.11 ~<br>-74.72<br>mV/°C      | emitter terminals                                                      | No                   | Yes           |

<sup>\*</sup> All methods require the ADC

device conducting the load current, i.e., it can work well under different working condition.

The above methods to estimate  $T_i$  are further benchmarked in TABLE III, in terms of online performance, selectivity, linearity, sensitivity, additional hardware, effects on converter performance, and integrability. The selectivity represents the factors that can affect TSEPs. Due to the DC-link voltage is kept as constant in most cases, the collector current is the main factor that influences the estimation performance. The accurate current measurement may require additional expensive current sensors, which increases the costs. In this sense, the  $R_{G,int}$  and  $V_{fb}$  methods outperform the rest methods. The linearity shows the theoretical accuracy of the estimation method, where the higher linearity leads to higher accuracy. The sensitivity is a derivative of the TSEPs concerning  $T_i$ . A higher sensitivity indicates the larger variation of TSEPs with the same junction temperature rise, which can deal with noise and measurement errors. Additional hardware evaluates the cost of the corresponding estimation method. It can be concluded from TABLE III that the TSEPs measured through the gate or auxiliary terminals are much cheaper because they are free of the high voltage or current. Normally, they can be integrated into the gate driver at the same time. Thus, this kind of TESPs has greater potential in commercial products. The converter performance effect indicates if the performance would be affected by the TSEP measurement. Another concern of  $T_j$  estimation by TSEPs is that most TSEPs are affected by the device degradation. For example, the parasitic inductance and gate capacitance vary with the fatigue of the package and gate oxide, which could lead to significant errors of the gate- or auxiliary-terminal-based methods. In this sense,  $V_{ce,Ilow}$  method has advantages because the sensing current is such low that the voltage deviation caused by the package degradation is negligible.

# 3) MONITORING THE JUNCTION-TO-CASE THERMAL RESISTANCE $R_{THJC}$

The junction-to-case thermal resistance  $R_{thjc}$  can be calculated as

$$R_{thjc} = \frac{T_j - T_c}{P_{loss}} \tag{27}$$

where  $T_j$  is the junction temperature that can be estimated by TSEPs,  $T_c$  is the case temperature that can be measured directly, and  $P_{loss}$  denotes the power loss, including the

Fig. 23. Using power losses to monitor the thermal resistance: (a) power losses vs. the case temperature and (b) flowchart to calculate the thermal resistance change  $\Delta R_{th}$  [42].

Fig. 24. Control structure for the harmonic resonance and suppression to monitor device degradation [48].

Fig. 25 t<sub>gp</sub> measurement circuitry [39].

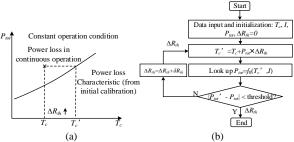

switching loss and conduction loss. The power loss  $P_{loss}$  can be obtained online with a predefined lookup table [45, 57] or curve-fitted model from datasheet [96, 97]. Then, the variation of the calculated  $R_{thic}$  can be monitored.

Furthermore,  $\Delta R_{thjc}$  indicates the degradation of the IGBT to a certain extent. Hence, *Dawei et al.* use  $\Delta R_{th}$  to monitor the solder fatigue with a case-above-ambient temperature [45]. By calibrating  $P_{tot}$  with different working points for the healthy IGBT, the power loss response-surface is obtained. In addition, a Cauer thermal network of the heatsink is developed to calculate the real-time power loss with the case-to-ambient temperature. Besides, the solder fatigue will result in the resistance change  $\Delta R_{th}$  between chip and substrate or between substrate and baseplate, depending on the solder layer type. Then,  $V_{ce,on}$  rises with the subsequently increased  $T_j$ , which makes a higher power loss  $P_{tot}$ , as illustrated in Fig. 23(a). Finally,  $\Delta R_{th}$  can be obtained through the flowchart shown in

Fig. 23(b). However, it should be careful if the ambient temperature is measured accurately when other heat sources are presented in the application scenery.

Notably, the thermal resistance change  $\Delta R_{th}$  is induced by the reduced thermal dissipation path. Consider the fact that the crack propagates from the edge to the center, the temperature of the case bottom surface declines while the temperature in the center of the case bottom surface increases [98]. This characteristic can be represented by the ratio of the junction-to-case-center thermal resistance to the junction-to-case-edge thermal resistance. Compared to  $R_{thjc}$  method, it is not cost-effective, while it eliminates the influence of the different operation points without all calibrations and is free of ambient temperature.

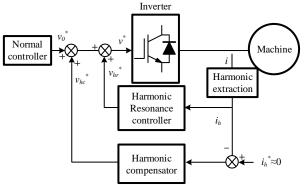

# 4) MONITORING THE 5<sup>TH</sup> HARMONIC

The 5th-order harmonic voltage can be extracted by the converter controller without additional hardware, as shown in Fig. 24 and discussed in [48]. The inner-loop harmonic resonance controller amplifies the small error before and after IGBT ageing to enhance the measurement accuracy. In Fig. 24,  $v^*_{hc}$  is forced by the outer loop to follow the harmonics produced by the inverter, and then the harmonic voltage can be measured. This method is cost-effective, as it requires no additional hardware. However, the system should operate at the setpoint, which makes it difficult to measure the harmonic online. Additionally, the degraded IGBT cannot be identified as the degradation is detected at the system level, i.e., the confidential level of the identified degradation is low.

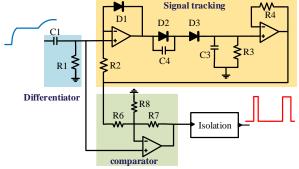

5) MONITORING THE MILLER-PLATEAU DURATION  $T_{GP}$ The circuitry that measures  $t_{gp}$  is shown in Fig. 25 [39]. The RC network receives the gate signal and outputs the differential results to provide the time instant before and after the Millerplateau. Then, the signal tracking circuit and voltage divider R6, R7, R8 give the adaptive voltage reference for the comparator, so that the circuitry can work under different working points. Next, the output of the differentiator is compared to the adaptive voltage reference to generate the double-pulse signal which implies the information of  $t_{gp}$ . Finally, an isolator is used to separate the analogue circuit and digital circuit. There are some details should be noted in the measuring circuitry. First of all, C1 should be small enough so that the gate transients will not be influenced. Besides, R1 should be small enough to ensure high bandwidth and large enough to provide a detectable signal. Meanwhile, the time constant of the RC network should be smaller than 1/10 of  $t_{gp}$ . In fact, the measured time interval is not exactly the same with  $t_{gp}$ , while it is precise enough to monitor the state of the IGBT.

#### III. TOLERANCE OF THE CATASTROPHIC FAILURES

The catastrophic failure is caused by overstresses or wear-out, which makes the IGBT uncontrollable. It can be classified into open-circuit failure and short-circuit failure. Disconnections between the chip and terminal or the driver and the terminal may induce open-circuit failures. The former disconnection results from the bond-wire lift-off or bond-wire rupture under

TABLE IV FAULT DIAGNOSTIC INFORMATION

| State  | Switching state errors                                                              | Faulty switch | Faulty phase |  |

|--------|-------------------------------------------------------------------------------------|---------------|--------------|--|

| Normal | $\varepsilon_{ab}\!\!=\!\!\varepsilon_{bc}\!\!=\!\!\varepsilon_{ca}$                | None          |              |  |

| Foulty | $\varepsilon_{ab} > T_{th},  \varepsilon_{bc} = 0,  \varepsilon_{ca} < -T_{th}$     | $T_1$         |              |  |

|        | $\varepsilon_{ab} < -T_{th}, \ \varepsilon_{bc} = 0, \ \varepsilon_{ca} > T_{th}$   | $T_4$         | a            |  |

|        | $\varepsilon_{ab} < -T_{th},  \varepsilon_{bc} > T_{th},  \varepsilon_{ca} = 0$     | $T_2$         | ,            |  |

| Faulty | $\varepsilon_{ab} > T_{th},  \varepsilon_{bc} < -T_{th},  \varepsilon_{ca} = 0$     | $T_5$         | b            |  |

|        | $\varepsilon_{ab} = 0$ , $\varepsilon_{bc} < -T_{th}$ , $\varepsilon_{ca} > T_{th}$ | $T_3$         |              |  |

|        | $\varepsilon_{ab} = 0$ , $\varepsilon_{bc} > T_{th}$ , $\varepsilon_{ca} < -T_{th}$ | $T_6$         | С            |  |

high short-circuit currents. In contrast, the latter is mainly caused by vibration, corrosion, and driver failures. The short-circuit failures may be the consequences of high gate voltages, external failures, latch-up and rapid increases of intrinsic temperatures due to the second breakdown or energy shock, high voltage breakdown or thermal runaway [13]. Short-circuit failures can occur during turn-on transients or on-state operation, which is related to the above mechanisms.

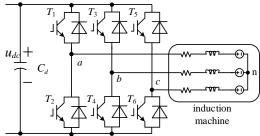

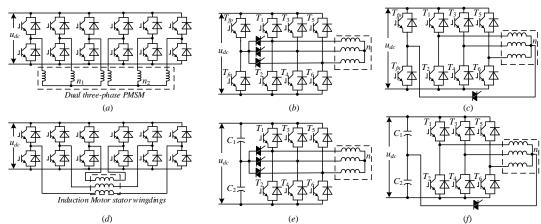

As the focus of this paper is to provide the reliability improvement methods for two-level IGBT-based converters, only this kind of converters are considered below.

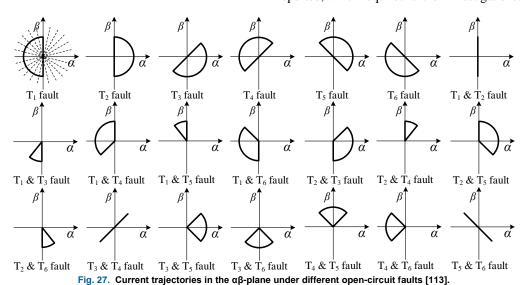

#### A. OPEN-CIRCUIT FAULT DIAGNOSIS METHODS

The diagnosis is to create an indicator or a group of indicators with different combinations under various conditions (healthy and different kinds of open-circuit faults). By identifying the relationship between the indicators and the faults, fault detection and isolation can be achieved. This can be a model-based approach, a signal-based approach or a data-driven approach.

# 1) MODEL-BASED APPROACH

The model-based approach mainly utilizes the difference between the analytical model and the real system after faults, which follows:

- a) Establishing the mathematical model of the converter by means of Switching state function model (SSFM), statespace model (SSM), mixed logical dynamic model (MLDM), model reference adaptive system (MRAS), and so on

- b) Monitoring the current or voltage by a closed-loop or open-loop observer, and comparing the monitored values with the measurements to generate residuals or to directly observe residuals.

- Performing the diagnosis by mapping the residuals to the fault indicators.

# Switching state function model [99-101]

Denoting  $S_k$  (k = a, b, c) as the switching state function.  $S_k$  = 1 means the upper IGBT turns on while the lower one turns off and the opposite for  $S_k = 0$ . Then, the phase voltage can be expressed in (28). Under normal condition, the estimated phase voltage is close to the measured phase voltage and the voltage error  $e_{kn} = 0$ . Taking the measurement error, discretizing error, and non-ideal switching characteristics like

Fig. 26. Simplified model of two-level VSI fed induction machine drive system.

switching delay and dead time into consideration,  $e_{kn}$  is not strictly equal to 0. Thus, the voltage threshold h and time threshold T are adopted to avoid the false alarms, which are given as h = 10V and  $T = 50T_s$ . Where  $T_s$  is the switching period [99, 100].

$$V_{kn,est} = S_k \cdot V_{dc} \tag{28}$$

For a rectifier, however, the phase-to-phase voltage can be expressed in (29).

$$u_{xy,est} = e_{xy} - i_{xy}R_s - L_s \frac{di_{xy}}{dt}$$

$x, y \in (a,b,c), x \neq y$  (29)

Where  $u_{xy,est}$  is the estimated phase-to-phase rectifier voltage and  $e_{xy}$  represents the phase-to-phase grid voltage. Then, the switching state and the corresponding error can be estimated by (30).

$$\begin{cases} S_{xy,est} = \frac{u_{xy,est}}{V_{dc}} \\ \varepsilon_{xy} = S_{xy} - S_{xy,est} \end{cases}$$

(30)

Thus, if  $T_1$  fault happens, switch state error for phase A will be 1 while the errors for the rest two phases are 0. This leads to  $\varepsilon_{ab}$  greater than the threshold  $T_{th}$ ,  $\varepsilon_{ca}$  smaller than  $-T_{th}$  and  $\varepsilon_{bc}=0$ . Accordingly, all the single switch fault can be diagnosed through TABLE IV [101].

# State-space model [102-107]

As the state model is application-dependent, the two-level voltage source inverter fed induction machine drive system (see Fig. 26) is taken as an example for illustration purpose. It can be described by

$$\begin{cases} \dot{x} = Ax + g(x) + Bu + DT_L \\ y = Cx \end{cases}$$

(31)

with

$$A = \begin{bmatrix} -c & 0 & ab & 0 & 0 \\ 0 & -c & 0 & ab & 0 \\ aL_m & 0 & -a & 0 & 0 \\ 0 & aL_m & 0 & -a & 0 \\ 0 & 0 & 0 & 0 & -kf \end{bmatrix}, \ g\left(x\right) = \begin{bmatrix} n_p b \lambda_{qr} \omega_m \\ -n_p b \lambda_{dr} \omega_m \\ -n_p b \lambda_{qr} \omega_m \\ -n_p b \lambda_{dr} \omega_m \\ m\left(i_{qs} \lambda_{dr} - i_{ds} \lambda_{qr}\right) \end{bmatrix}$$

$$B = \begin{bmatrix} d & 0 & 0 & 0 & 0 \\ 0 & d & 0 & 0 & 0 \end{bmatrix}^{\mathrm{T}}, D = \begin{bmatrix} 0 & 0 & 0 & 0 & k \end{bmatrix}^{\mathrm{T}}, C = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 \end{bmatrix}$$

where  $L_s$  and  $L_r$  are the stator and rotor self-inductance,  $L_m$  denotes the mutual inductance,  $R_s$  and  $R_r$  indicate the stator and rotor resistance, J is the inertia, f represents the mechanical

fiction,  $i_{ds}$  and  $i_{qs}$  are the stator current in the d- and q-axis,  $\lambda_{dr}$  and  $\lambda_{qr}$  are the rotor flux in the d- and q-axis,  $\omega_m$  is the motor speed,  $T_L$  is the load torque,  $a = R_r/L_r$ ,  $b = L_m/\sigma L_s L_r$ ,  $c = L_m^2 R_r/\sigma L_s L_r^2 + R_s/\sigma L_s$ ,  $m = 3n_p L_m/2JL_r$ ,  $d = 1/\sigma L_s$ , k = 1/J,  $\sigma = 1-L_m^2/L_s L_r$ , state vector  $x = [i_{ds}, i_{qs}, \lambda_{dr}, \lambda_{qr}, w_m]^T$ , input  $u = [u_d, u_q]^T$ , output  $y = [i_{ds}, i_{qs}, w_m]^T$ .

Taking the Luenberger observer [88] as an example (other observers, e.g., PI observer, can also be adopted), the stator current in the dq-frame can be observed by

$$\begin{cases} \hat{x} = A\hat{x} + g(\hat{x}) + Bu + DT_L + K_o(y - \hat{y}) \\ \hat{y} = C\hat{x} \end{cases}$$

(32)

Then, the residuals can be obtained as

$$\begin{bmatrix} r_d \\ r_q \end{bmatrix} = \begin{bmatrix} i_{ds} \\ i_{qs} \end{bmatrix} - \begin{bmatrix} \hat{i}_{ds} \\ \hat{i}_{qs} \end{bmatrix}$$

(33)

If the residual exceeds the threshold, a fault can be detected. For the fault isolation, i.e., to identify the faulty switch, the direction of the threshold is utilized. With three unitary actuator directions in the *abc*-frame  $e_a = [1, 0, 0], e_b = [0, 1, 0],$  $e_c = [0, 0, 1]$ , six fault directions can be established as  $v_{a+} =$  $v_{a-}$  $([\mathbf{T}_{abc}]e_a/[\mathbf{T}_{abc}]e_a),$  $-([\mathbf{T}_{abc}]e_a/[\mathbf{T}_{abc}]e_a),$  $([\mathbf{T}_{abc}]e_b/[\mathbf{T}_{abc}]e_b),$  $v_{b}$  $-([\mathbf{T}_{abc}]e_b/[\mathbf{T}_{abc}]e_b),$  $v_{c}$ = -([ $\mathbf{T}_{abc}$ ] $e_c$ /[ $\mathbf{T}_{abc}$ ] $e_c$ ). Here, [ $\mathbf{T}_{abc}$ ]  $([\mathbf{T}_{abc}]e_c/[\mathbf{T}_{abc}]e_c),$ represents the abc-dq transformation. TABLE V shows the relationship between the faulty switch and residual direction. It should be noted that false fault recognitions might be avoided, as the direction of each fault indicator is 60-degree apart from others.

Similar to the Luenberger observer, the first-order sliding mode observer can also be utilized with the form of (34) [107].

$$\dot{\hat{x}} = A\hat{x} + Bu + \Lambda I_{c} \tag{34}$$

Where  $\Lambda$  represents the observer gain and  $I_s$  is the switching vector.

The ratio  $r_n$  of the mean absolute value of measured current and observed current can be calculated in (35). For the normal condition, the ratio is close to 1 because the two currents are almost identical to each other. For one-switch fault condition, however, the ratio is calculated in (36), indicating  $r_n$  is smaller than 0.318. As for the open-phase condition, the measured current approaches to 0 and  $r_n$  is about equal to 0. Hence, the fault can be detected when  $r_n$  is smaller than a threshold  $K_d$ .

$$r_n = \frac{\int |i_n| dt}{\int |\hat{i}_n| dt}$$

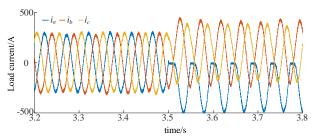

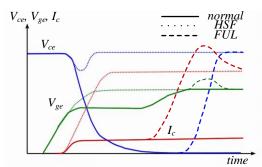

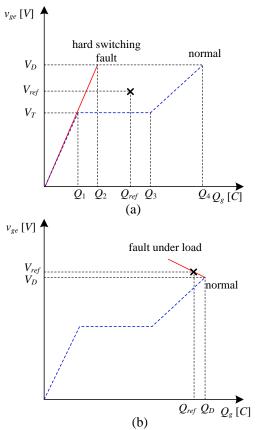

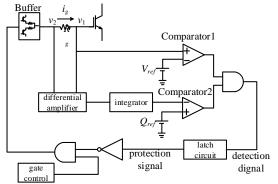

(35)