### **Aalborg Universitet**

#### Common-Mode Resonance Damping and DC Voltage Balancing Strategy for LCCL-Filtered Three-Level Photovoltaic Grid-Tied Inverters

Zhao, Rende: Wang, Cun: Yan, Qingzeng; Xu, Hailiang; Blaabjerg, Frede

Published in: **IEEE Access**

DOI (link to publication from Publisher): 10.1109/ACCESS.2019.2963479

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, R., Wang, C., Yan, Q., Xu, H., & Blaabjerg, F. (2020). Common-Mode Resonance Damping and DC Voltage Balancing Strategy for LCCL-Filtered Three-Level Photovoltaic Grid-Tied Inverters. *IEEE Access*, 8, 13228 - 13239. Article 8947985. https://doi.org/10.1109/ACCESS.2019.2963479

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

Received December 10, 2019, accepted December 26, 2019, date of publication January 1, 2020, date of current version January 22, 2020.

Digital Object Identifier 10.1109/ACCESS.2019.2963479

# **Common-Mode Resonance Damping and DC Voltage Balancing Strategy for LCCL-Filtered Three-Level Photovoltaic Grid-Tied Inverters**

RENDE ZHAO<sup>101</sup>, (Member, IEEE), CUN WANG<sup>101</sup>, QINGZENG YAN<sup>101</sup>, HAILIANG XU<sup>101</sup>, (Member, IEEE), AND FREDE BLAABJERG<sup>102</sup>, (Fellow, IEEE)

<sup>1</sup>College of New Energy, China University of Petroleum (East China), Qingdao 266580, China

<sup>2</sup>Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark

Corresponding author: Hailiang Xu (xuhl@upc.edu.cn)

This work was supported by the National Natural Science Foundation of China under Grant 51677193.

**ABSTRACT** The leakage current caused by common-mode (CM) voltage is a critical issue in transformerless three-level photovoltaic (PV) inverters, which can increase the output current distortion, bring extra power losses, aggravate the electromagnetic interference, and even cause degradation of the panels and safety issues. The LCCL filter was proven to be effective to mitigate the leakage current, whose capacitor is split into two parts, and the common point of the smaller one is connected to the neutral-point (NP) of the DC-link. However, the LCCL-filtered three-level inverter suffers from the CM resonance of the neutral current and the NP voltage imbalance. Therefore, this paper proposes a CM resonance damping and NP voltage balancing strategy for the transformerless LCCL-filtered three-level PV inverter. A novel dual-cascade-loop with a dc voltage-difference outer-loop and a neutral-current inner-loop is proposed to control the CM voltage with a  $\alpha\beta\gamma$ -frame space vector pulse width modulation (SVPWM) for damping the CM resonance and balancing the NP voltage. At last, the effectiveness of the proposed strategy is experimentally validated through a 10 kW transformerless LCCL-filtered T-type three-level PV inverter.

**INDEX TERMS** Common-mode (CM) resonance, LCCL filter, leakage current, neutral-point (NP) voltage, three-level inverter.

#### I. INTRODUCTION

Transformerless three-level inverters have been widely used in photovoltaic (PV) systems due to its high integration, high efficiency, low cost, and small total harmonic distortion of output voltage and current. However, the leakage current caused by common-mode (CM) voltage is a critical issue in transformerless three-level PV inverters, which can increase the output current distortion, bring extra power losses, aggravate the electromagnetic interference, and even cause safety issues [1]–[3].

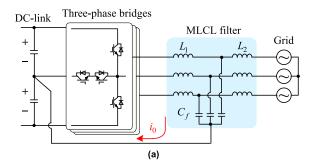

Besides improving the modulation schemes [4]–[6] and blocking the flowing path of the leakage current [7], [8], bypassing the leakage current is also widely adopted to minimize the leakage current. The modified LCL (MLCL) filter is firstly used to bypass the leakage current by connecting the common point of the capacitors of LCL filter to the

The associate editor coordinating the review of this manuscript and approving it for publication was B. Chitti Babu $^{\boxed{0}}$ .

neutral point (NP) of the DC-link [1], [2], [9]–[12], as shown in Fig. 1(a). The topology can provide a low-impedance path and force the leakage current to circulate within the inverter rather than through the ground. Nevertheless, its filter capacitors are involved in both CM and differential-mode (DM) circuits [13], which means that the design of the capacitors need simultaneously satisfy the CM and DM requirements. It is thus hard to choose an appropriate capacitance value. As an optimization, a LCCL filter shown in Fig. 1 (b) was proposed in [13], whose capacitors are split into two parts, and the common point of the smaller one is connected to the NP of the DC-link. With the LCCL filter, the CM and DM circuit parameters can be decoupled by introducing decoupling factor  $\lambda$ , which will favor the design of filter capacitors [13]. Meanwhile, the resistance of the CM filter capacitor is enlarged  $(1/\lambda\omega C_f > 1/\omega C_f)$ , which can restrict the neutral current to some extent and further reduce power loss. However, no matter the MLCL or LCCL filter is still confronted with the risk of the CM resonance.

**FIGURE 1.** Topologies with (a) MLCL-filtered three-level inverter and (b) LCCL-filtered three-level inverter.

Passive damping methods such as inserting physical resistors in the capacitor branch of the LCCL filter can effectively damp the CM resonance, but will cause extra power loss [2], [14]. The active damping method is obviously a better choice. Although comprehensive active damping methods have been proposed for the DM resonance in the LCL filter [15]–[17], there are few methods focusing on the CM resonance damping in the LCCL filter of the three-level inverter. Only two types of active damping schemes have been reported recently to damp the CM resonance in the PV inverter with MLCL filter [1], [2]. Reference [1] proposed a zero-sequence voltage close-loop control strategy based on full state feedback to damp the CM resonance. And in [2], a CM current control with disturbance feed-forward was proposed to suppress the CM resonance.

However, both the CM resonance active damping methods changed the dwell time of redundant vectors to modulate the zero-sequence voltage [1], [2], which might result in the NP voltage imbalance [18], [19]. Therefore, [1] and [2] took extra measures to balance the NP voltage. In [1], a typical signal was superimposed onto the zero-sequence voltage reference to extend the inverter modulation index and to balance the NP voltage. However, the mechanism of NP voltage balancing was not discussed. In [2], besides a CM current control loop with a zero reference, an extra NP voltage balancing loop was added to equalize positive and negative dc voltages. However, because the outputs of the two independent loops were both zero-sequence voltages, they might interfere with each other and even cause conflicts. Therefore, it is necessary to integrate the two independent loops together and avoid the conflicts.

In this paper, the main contributions are as follows

The relationship between the dc voltage-difference and the neutral current is established. Based on that, a novel

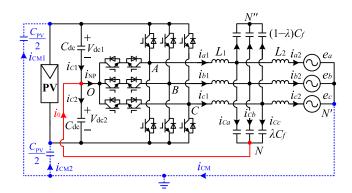

FIGURE 2. LCCL-filtered transformerless three-level PV inverter.

dual-cascade-loop with a dc voltage-difference outerloop and a neutral-current inner-loop is proposed. The integrated dual-loop structure can simultaneously damp the CM resonance and balance the NP voltage without any conflicts.

Both the inner- and outer-loop controllers are carefully designed to ensure system ability and zero steady-error.

The remaining part of this paper is structured as follows. In Section II, the CM model of the LCCL-filtered three-level inverter is derived to demonstrate the CM resonance and the NP voltage imbalance issues. The dual-loop control strategy for damping CM resonance and balancing NP voltage is then proposed in Section III. And the design of the controllers is fully discussed. Finally, in Section IV, the experimental results on a 10 kW transformerless LCCL-filtered three-level T-type PV inverter are presented to verify the effectiveness of the proposed strategy.

#### II. CM MODEL OF THE LCCL-FILTERED INVERTER

Fig. 2 shows the LCCL-filtered transformerless T-type three-level PV inverter [13].  $C_{\rm PV}$  is the stray capacitance between PV panels and the ground, which can cause the leakage currents  $i_{\rm CM1}$  and  $i_{\rm CM2}$ . The resistances of  $L_1$  and  $L_2$  are neglected for emulating a worst-case scenario. The LCCL filter consists of two groups of star-connected capacitors. The common point N of the smaller capacitors  $\lambda C_f (0 < \lambda < 0.5)$  is connected to the NP of the DC-link for mitigating the leakage current, and the smaller and the larger capacitors are both used for filtering high-frequency harmonics in the output differential mode (DM) currents. The value of  $\lambda$  can be chosen according to [13].

The CM model of the LCCL-filtered three-level inverter is derived as follows. In Fig. 2, the voltages across the output terminals *A*, *B*, *C* and the NP of the DC-link can be expressed as

$$\begin{cases} v_{AO} = L_1 \frac{di_{a1}}{dt} + L_2 \frac{di_{a2}}{dt} + e_a + v_{N'O} \\ v_{BO} = L_1 \frac{di_{b1}}{dt} + L_2 \frac{di_{b2}}{dt} + e_b + v_{N'O} \\ v_{CO} = L_1 \frac{di_{c1}}{dt} + L_2 \frac{di_{c2}}{dt} + e_c + v_{N'O} \end{cases}$$

(1)

where  $v_{N'O}$  can be derived from the grounded path in Fig. 2

$$\begin{cases} v_{N'O} = \frac{2}{C_{PV}} \int i_{CM1} dt + V_{dc1} \\ v_{N'O} = \frac{2}{C_{PV}} \int i_{CM2} dt - V_{dc2}. \end{cases}$$

(2)

Through the neutral line in Fig. 2, the output voltages of the inverter can also be expressed as

$$\begin{cases} v_{AO} = L_1 \frac{di_{a1}}{dt} + \frac{1}{\lambda C_f} \int i_{Ca} dt \\ v_{BO} = L_1 \frac{di_{b1}}{dt} + \frac{1}{\lambda C_f} \int i_{Cb} dt \\ v_{CO} = L_1 \frac{di_{c1}}{dt} + \frac{1}{\lambda C_f} \int i_{Cc} dt. \end{cases}$$

(3)

According to [4]–[6], the CM voltage  $v_{\text{CM}}$  can be defined as

$$v_{\rm CM} = \frac{1}{3}(v_{AO} + v_{BO} + v_{CO}). \tag{4}$$

In addition, the leakage current  $i_{CM}$  and the neutral current  $i_0$  can be expressed as

$$\begin{cases} i_{\text{CM}} = i_{\text{CM}1} + i_{\text{CM}2} = i_{a2} + i_{b2} + i_{c2} \\ i_0 = i_{Ca} + i_{Cb} + i_{Cc} \\ i_{\text{CM}} + i_0 = i_{a1} + i_{b1} + i_{c1}. \end{cases}$$

(5)

By summing the three equations in (1) and (3), the CM voltage can be respectively expressed as

$$v_{\rm CM} = \frac{1}{3} L_1 \frac{d(i_{CM} + i_0)}{dt} + \frac{1}{3} L_2 \frac{di_{CM}}{dt} + v_{N'O}$$

(6)

$$v_{\rm CM} = \frac{1}{3} L_1 \frac{d(i_{\rm CM} + i_0)}{dt} + \frac{1}{3} \frac{1}{\lambda C_f} \int i_0 dt.$$

(7)

And the dc voltage-difference  $\Delta V_{\rm dc}$ , which reflects the NP voltage fluctuation, can be derived from (2) as

$$\Delta V_{\rm dc} = V_{\rm dc1} - V_{\rm dc2} = 2v_{N'O} - \frac{2}{C_{\rm PV}} \int i_{\rm CM} dt$$

(8)

With  $v_{CM}$  in (7) substituted into (6) and  $v_{N'O}$  in (6) substituted into (8), the following equation can be deduced

$$\Delta V_{\rm dc} = 2\left(\frac{1}{3}\frac{1}{\lambda C_f}\int i_0 dt - \frac{1}{3}L_2\frac{di_{\rm CM}}{dt} - \frac{1}{C_{\rm PV}}\int i_{\rm CM} dt\right). \tag{9}$$

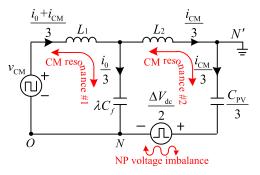

Based on (7) and (9), the CM model of the LCCL-filtered three-level inverter can be obtained as shown in Fig. 3. The CM voltage  $v_{\rm CM}$  generates the leakage current  $i_{\rm CM}$  through the  $L_1 \sim L_2 \sim C_{\rm PV}/3$  branch. With the connection between the common point N of  $\lambda C_f$  and the NP of the DC-link, the extra neutral current  $i_0$  is generated in the  $L_1 \sim \lambda C_f$  branch. Considering  $\lambda C_f \gg C_{\rm PV}/3$ , the impedance of the  $L_1 \sim \lambda C_f$  branch for the high-frequency  $i_{\rm CM}$  is much smaller than that of the  $L_1 \sim L_2 \sim C_{\rm PV}/3$  branch. Thus,  $i_{\rm CM}$  in the  $L_1 \sim L_2 \sim C_{\rm PV}/3$  branch can be significantly mitigated.

FIGURE 3. CM model of the LCCL filtered transformerless three-level PV inverter.

According to Fig. 3, the transfer function from CM voltage  $v_{\text{CM}}$  to leakage current  $i_{\text{CM}}$  can be derived as

$$G_{CM}(s) = \frac{i_{CM}(s)}{v_{CM}(s)} = \frac{3C_{PV}s}{L_1L_2C_{PV}\lambda C_f s^4 + (3L_1\lambda C_f + L_1C_{PV} + L_2C_{PV})s^2 + 3}$$

(10)

There are two resonance frequencies in the transfer function [1], [2], which can be expressed respectively as

$$\begin{cases} f_{r1} \approx \frac{1}{2\pi\sqrt{L_1\lambda C_f}} \\ f_{r2} \approx \frac{\sqrt{3}}{2\pi\sqrt{L_2C_{\rm PV}}} \end{cases}$$

(11)

It can be inferred that, although the leakage current can be effectively mitigated in the LCCL-filtered three-level inverter, there still are two concomitant issues to be solved.

One issue is the CM resonances in the  $L_1 \sim \lambda C_f$  and  $L_2 \sim C_{\rm PV}/3$  branches caused by the CM voltage  $v_{\rm CM}$ . Note that, the parasitic capacitance  $C_{\rm PV}$  of the photovoltaic array in  $f_{r2}$  is usually uncertain and varies with humidity, temperature, etc. In addition, as indicated in [1] and [2], the possible resonance frequency  $f_{r2}$  is usually much higher than the switching frequency, which makes it uncontrollable. Therefore, only the active damping for the first resonance frequency  $f_{r1}$  is implemented, while that for the second resonance frequency  $f_{r2}$  is not considered in this paper.

The other issue is the imbalanced NP voltage in Fig. 3. Therefore, auxiliary current and voltage loops are proposed in this paper to actively damp the CM resonances and balance the NP voltage, which will be presented in detail in next section.

## III. CM RESONANCE DAMPING AND NP VOLTAGE BALANCING DUAL-LOOP CONTROL STRATEGY

A. NEUTRAL-CURRENT INNER-LOOP FOR CM RESONANCE DAMPING

Considering  $\lambda C_f \gg C_{PV}/3$  and  $i_{CM} \ll i_0$ , the leakage current  $i_{CM}$  in (6) can approximately be neglected [2]. The transfer

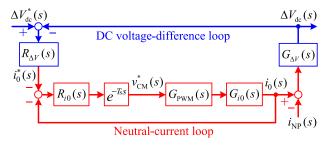

FIGURE 4. Block diagram of the neutral-current loop.

function from  $v_{\text{CM}}$  to  $i_0$  can then be given by

$$G_{i0}(s) = \frac{i_0(s)}{v_{\text{CM}}(s)} = \frac{3\lambda C_f \omega_{\text{r}}^2 s}{s^2 + \omega_{\text{r}}^2}$$

(12)

where the CM resonance angle frequency  $\omega_r = 2\pi f_{r1}$ .

According to (12), there is no pole located in the left-half complex plane. If the neutral-current is operated in open-loop and  $v_{\rm CM}$  contains a component near the resonance frequency, a current resonance will be generated by the CM voltage in the  $L_1 \sim \lambda C_f$  branch, which may further trigger the overcurrent protection of the inverter. Therefore, an effective damping method is necessary in the LCCL-filtered three-level inverter to suppress the CM resonance.

Being similar to the conventional DM resonance suppression of the LCL filter, passive and active damping methods can be applied to damp the CM resonance. The passive damping will sacrifice the attenuation performance in high-frequency range and cause more loss [14]. The active damping method is thus preferred. A simple active damping method is to construct the closed-loop control of the neutral-current and to ensure that the resonance frequency and time delay meet the stability requirement [6]. The block diagrams of neural-current loop are depicted in Fig. 4.

In Fig. 4,  $e^{-Tss}$  represents the delay caused by sampling and control, where  $T_s$  is the control period.  $G_{\rm PWM}(s)$  is the transfer function of PWM, and it is usually considered as a delay of  $e^{-0.5~Tss}$ .  $R_{i0}(s)$  is the current controller. The neutral-current feedback is calculated by adding three-phase inverter-side currents.

#### B. DC-VOLTAGE DIFFERENCE OUTER-LOOP FOR NP VOLTAGE BALANCING

To attach a cascaded outer-loop for the NP voltage balancing, the relationship between the neutral current  $i_0$  and the dc-voltage-difference  $\Delta V_{\rm dc}$  need be established. Referring to Fig. 2, the positive and negative capacitors should meet

$$\begin{cases} C_{dc} \frac{d (V_{dc1})}{dt} = i_{C1} \\ C_{dc} \frac{d (V_{dc2})}{dt} = i_{C2} \end{cases}$$

(13)

Though the upper and lower capacitors are not absolutely identical [26], their difference is quite small and is neglected in this paper. Meanwhile, according to the Kirchhoff's current law, their currents should satisfy

$$i_{C2} = i_{C1} + i_0 - i_{NP} (14)$$

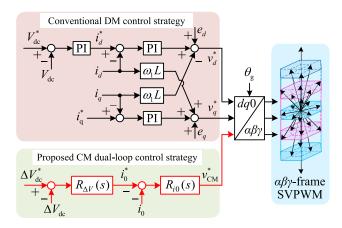

FIGURE 5. Proposed CM resonance damping and NP voltage balancing strategy.

Therefore, the relationship between  $i_0$  and  $\Delta V_{\rm dc}$  can be derived as

$$C_{\rm dc}\frac{d\left(\Delta V_{\rm dc}\right)}{dt} = -i_0 + i_{\rm NP}.\tag{15}$$

According to (15), if the integral of  $i_0$  is equal to that of  $i_{\rm NP}$  in a period,  $\Delta V_{\rm dc}$  will not change. But if the reference  $i_0^*(s)$  of the neutral-current loop shown in Fig. 4 is set to be zero or other constant value, the above conditions cannot be met because  $i_{\rm NP}$  is not zero or constant. Then  $\Delta V_{\rm dc}$  will change and the imbalance of NP voltage will occur. Therefore, it is essential to set an appropriate reference  $i_0^*(s)$  for the inner-loop through the dc-voltage difference outer-loop.

Regarding  $i_{NP}$  as a disturbance term in (15), the transfer function from  $i_0$  to  $\Delta V_{dc}$  can be obtained as

$$G_{\Delta V}(s) = \frac{\Delta V_{\rm dc}(s)}{i_0(s)} = -\frac{1}{C_{\rm dc}s}.$$

(16)

Based on (16), a voltage-difference outer-loop is thus proposed to balance the NP voltage as shown in Fig. 5, where  $R_{\Delta V}(s)$  represents the outer voltage-difference regulator, and the superscript '\*' denotes the reference variables. It can be inferred that, with the cascaded dual-loop control structure, the control commands of the inner- and outer-loop are harmonically integrated rather than interfere with each other.

## C. DESIGN DETAILS FOR THE INNER- AND OUTER-LOOP CONTROLLER

#### 1) DESIGN DETAILS FOR INNER-LOOP CONTROLLER

Since the primary objective of the inner-loop is to damp the resonance and ensure the stability of CM circuit, the proportional (P) controller is quite enough to achieve an adequate stability margin. And the open-loop transfer function of the neutral-current inner-loop shown in Fig. 4 can be expressed

$$H_{i0}(s) = R_{i0}(s)e^{-T_s s}G_{PWM}(s)G_{i0}(s) = k_{ip}\frac{3\lambda C_f \omega_r^2 s}{s^2 + \omega_r^2}e^{-1.5T_s s}$$

(17)

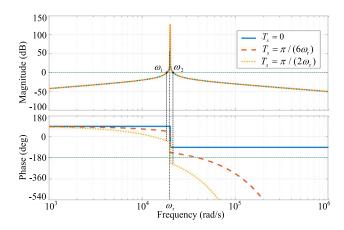

FIGURE 6. Bode diagrams of the inner-loop with different time delays.

**TABLE 1. System parameters.**

|                       | Description                                                       | Parameters                         | Value    |

|-----------------------|-------------------------------------------------------------------|------------------------------------|----------|

|                       | DC voltage                                                        | $V_{ m dc}$                        | 750 V    |

|                       | Stray capacitance                                                 | $C_{ m PV}$                        | 150 nF   |

|                       | AC grid voltage                                                   | $e_{\scriptscriptstyle	ext{RMS}}$  | 380 V    |

| General<br>Parameters | rameters Fundamental frequency $f_1$ Switching frequency $f_{sw}$ | 50 Hz                              |          |

|                       | Switching frequency                                               | $f_{ m sw}$                        | 15 kHz   |

|                       | Sampling frequency                                                | $f_{ m s}$                         | 30 kHz   |

|                       | DC-link capacitance                                               | $C_{ m dc}$                        | 1670 μF  |

|                       | Inverter-side inductance                                          | $L_1$                              | 1.65 mH  |

|                       | Grid-side inductance                                              | $f_{ m sw}$ $f_{ m s}$ $C_{ m dc}$ | 1 mH     |

| LCCL capacitar        | LCCL capacitance                                                  | $\lambda C_f$                      | 3.3 μF   |

|                       | LCCL capacitance                                                  | $(1-\lambda)C_f$                   | 10 μF    |

|                       | CM resonance frequency                                            | $f_{ m r1}$                        | 2.19 kHz |

with magnitude (in decibels) and phase of  $H_{i0}(s)$  given in (18) and (19) respectively.

$$20 \lg |H_{i0}(s)|_{s=j\omega} = \begin{cases} 20 \lg \left[ k_{ip} \frac{3\lambda C_f \omega_r^2 \omega}{\omega_r^2 - \omega^2} \right], & (\omega < \omega_r) \\ \infty, & (\omega = \omega_r) \\ 20 \lg \left[ k_{ip} \frac{3\lambda C_f \omega_r^2 \omega}{\omega^2 - \omega_r^2} \right], & (\omega > \omega_r) \end{cases}$$

$$(18)$$

$$\angle H_{i0}(s) \big|_{s=j\omega} = \begin{cases} \frac{\pi}{2} - 1.5\omega T_{\rm s}, & (\omega < \omega_{\rm r}) \\ -\frac{\pi}{2} - 1.5\omega T_{\rm s}, & (\omega > \omega_{\rm r}) \end{cases} \tag{19}$$

The Bode diagrams of  $H_{i0}(s)$  with different time delays are shown in Fig. 6 using the parameters listed in Table 1. According to the Nyquist stability criterion, only the frequency ranges with magnitudes above 0 dB are considered. According to (17), the number of the open-loop unstable poles P = 0. The numbers of the positive and negative

crossings between  $\omega_1$  and  $\omega_2$  in Fig. 6 must be equal, to ensure the system stability. Fig. 6 shows that there is neither positive nor negative crossing between  $\omega_1$  and  $\omega_2$  when  $T_s = 0$  or  $T_s = \pi/(6\omega_r)$ . In this case, the system is stable. However, when  $T_s = \pi/(2\omega_r)$ , there is one negative crossing and no positive crossing, showing an unstable system.

It can be derived from (19) that, the control period  $T_{\rm s}$  should satisfy (20) for ensuring the system stability

$$-\frac{\pi}{2} - 1.5\omega_2 T_s > -\pi \tag{20}$$

where  $\omega_2$  should satisfy a zero gain according to (18)  $(\omega_2 > \omega_r)$ .

$$20\lg\left[k_{ip}\frac{3\lambda C_f \omega_r^2 \omega_2}{\omega_2^2 - \omega_r^2}\right] = 0 \tag{21}$$

Regarding the controller design, the proportional gain  $k_{ip}$  of inner loop can be designed as follows to guarantee the neutral-current inner-loop has enough phase margin  $\phi_m$  [20]. According to (19), the right cut-off frequency  $\omega_2$  should guarantee an enough phase margin  $\phi_m$

$$-\frac{\pi}{2} - 1.5\omega_2 T_{\rm s} = \phi_m - \pi. \tag{22}$$

Then, substituting the  $\omega_2$  of (22) into (21),  $k_{ip}$  can thus be obtained as

$$k_{ip} = \frac{\left(\frac{\pi - 2\phi_m}{3T_s}\right)^2 - \omega_{\rm r}^2}{3\lambda C_f \omega_{\rm r}^2 \frac{\pi - 2\phi_m}{3T_s}}.$$

(23)

To further demonstrate the damping effect of the inner-loop, its closed-loop transfer function can be derived as

$$\Phi_{i0}(s) = \frac{i_0(s)}{i_0^*(s)} = \frac{H_{i0}(s)}{1 + H_{i0}(s)}$$

(24)

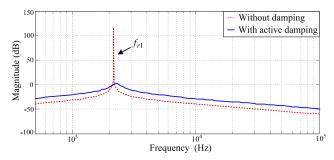

Its magnitude response can be plotted together with the magnitude response without the active damping using the parameters listed in Table 1, as shown in Fig. 7. It should be noted that, without the active damping, a serious resonance peak exists at the resonance frequency  $f_{r1}$ . In contrast, an obvious suppression to resonance peak can be observed with the proposed neutral-current inner-loop, validating the damping effect.

#### 2) DESIGN DETAILS FOR OUTER-LOOP CONTROLLER

The target of the outer-loop is to eliminate the voltage difference. On the one hand, the controller parameters should be reasonably designed to guarantee the system stability. On the other hand, the steady-state error of the outer-loop should be suppressed to zero with the selected controller. Therefore, the proportional-integral (PI) controller is preferred in the outer-loop.

FIGURE 7. Magnitude responses with and without active damping.

According to Fig. 5, the open-loop transfer function of the outer-loop can be derived as (25) by multiplying the transfer functions of PI controller, inner-loop, and plant.

$$H_{\Delta\nu}(s) = -R_{\Delta\nu}(s)\Phi_{i0}(s)G_{\Delta\nu}(s) = k_{\nu p} \frac{\tau_{\nu s} + 1}{\tau_{\nu s}} \frac{K_{I}s}{1.5T_{s}s^{3} + s^{2} + (K_{I} + 1.5T_{s}\omega_{r}^{2})s + \omega_{r}^{2}} \frac{1}{C_{dc}s} = \frac{K_{V}(\tau_{\nu s} + 1)}{s[1.5T_{s}s^{3} + s^{2} + (K_{I} + 1.5T_{s}\omega_{r}^{2})s + \omega_{r}^{2}]}$$

(25)

where  $k_{vp}$  and  $\tau_v$  are parameters of PI controller; time delay  $e^{-1.5 \ T_{SS}}$  has been approximated to a one-order inertia element for a convenient calculation;  $K_I$  and  $K_V$  can be respectively expressed as

$$K_I = 3k_{ip}\lambda C_f \omega_{\rm r}^2 \tag{26}$$

$$K_V = \frac{k_{vp}K_I}{\tau_v C_{dc}} \tag{27}$$

Its magnitude response and phase response can be deduced as (28) and (29) respectively.

$$|H_{\Delta\nu}(s)|_{s=j\omega}|$$

$$= \frac{K_V \sqrt{1 + \omega^2 \tau_{\nu}^2}}{\omega \sqrt{(\omega_{\rm r}^2 - \omega^2)^2 + (K_I \omega + 1.5 T_s \omega_{\rm r}^2 \omega - 1.5 T_s \omega^3)^2}}$$

$$|\Delta H_{\Delta\nu}(s)|_{s=j\omega}$$

$$= \tan^{-1}(\tau_{\nu}\omega) - \frac{\pi}{2} - \tan^{-1}(\frac{K_I \omega + 1.5 T_s \omega_{\rm r}^2 \omega - 1.5 T_s \omega^3}{\omega_{\rm r}^2 - \omega^2})$$

(29)

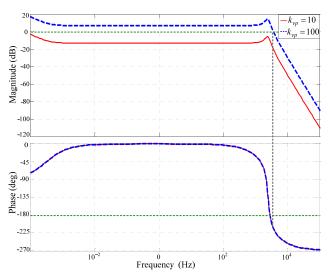

The Bode diagrams of  $H_{\Delta\nu}(s)$  with different proportional gain  $k_{\nu p}$  are shown in Fig. 8 using the parameters listed in Table 1. It can be inferred that the magnitude response curve will shift upwards with the increase of  $k_{\nu p}$ , which will weaken the phase margin and even cause system instability. And the controller parameters  $k_{\nu p}$  and  $\tau_{\nu}$  can also be tuned according to the given phase margin, which is similar to the foregoing design process in the neutral-current inner-loop and not repeated.

The zero steady-state errors of the outer-loop should also be theoretically verified. The transfer function between the error signal and the reference signal of the outer-loop can be

FIGURE 8. BODE diagrams of the outer-loop with two proportional gains.

FIGURE 9. Overall control scheme with the proposed strategy.

expressed as

$$\frac{E(s)}{\Delta V_{dc}^{*}(s)}$$

$$= \frac{1}{1 + H_{\Delta v}(s)}$$

$$= \frac{1.5T_{s}s^{3} + s^{2} + (K_{I} + 1.5T_{s}\omega_{r}^{2})s + \omega_{r}^{2}}{1.5T_{s}s^{3} + s^{2} + (K_{I} + 1.5T_{s}\omega_{r}^{2})s + \omega_{r}^{2} + \frac{K_{V}(\tau_{V}s + 1)}{s}}$$

(30)

With the unit-step reference signal, the steady-state error of the outer-loop can thus be calculated as (31), which is the expected zero value.

$$e_{ss} = \lim_{t \to \infty} e(t) = \lim_{s \to 0} sE_s(s)$$

$$= \frac{1.5T_s s^3 + s^2 + (K_I + 1.5T_s \omega_r^2) s + \omega_r^2}{1.5T_s s^3 + s^2 + (K_I + 1.5T_s \omega_r^2) s + \omega_r^2 + \frac{K_V(\tau_v s + 1)}{s}} \Delta V_{dc}^*$$

$$= 0$$

(31)

#### D. CONTROL SCHEME OF OVERALL SYSTEM

The proposed cascaded dual-loop CM control strategy are then combined with the commonly-used DM control

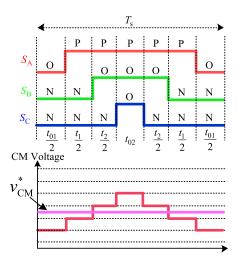

FIGURE 10. Switching states, dwell time and CM voltage in a switching period.

**TABLE 2.** Three experimental cases.

| Number | Control Strategy Description                                                          | Filter |

|--------|---------------------------------------------------------------------------------------|--------|

| Case 1 | Only using conventional DM control strategy                                           | LCL    |

| Case 2 | Only using conventional DM control strategy                                           | LCCL   |

| Case 3 | Conventional DM control strategy with proposed CM dual-loop control strategy (Fig. 9) | LCCL   |

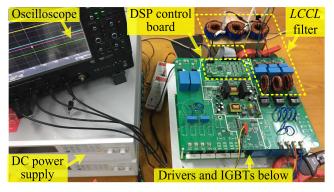

FIGURE 11. 10 kW transfromerless LCCL-filtered T-type three-level PV inverter.

strategy [21], [22] to form the overall system control scheme, as shown in Fig. 9, where  $L = L_1 + L_2$ ;  $i_d$  and  $i_q$  are dq components of the inverter-side currents in the grid-voltage-oriented synchronous frame;  $\omega_1$  is the fundamental angle frequency;  $\theta_g$  is the angle of the grid voltage. It should be noted that, the DM active damping need not be added in the control scheme since the DM parameters of the paper lie in the stable range [15].

In order to output an arbitrary CM voltage, the  $\alpha\beta\gamma$ -frame SVPWM is adopted, where the  $\gamma$ -axis is set to modulate the reference CM voltage  $v_{\text{CM}}^*$ . Different from the conventional  $\alpha\beta$ -frame SVPWM, the  $\alpha\beta\gamma$ -frame SVPWM can regulate the CM voltage by reallocating the dwell time of redundant vectors [23], [24]. With the example in Fig. 10, the dwell time

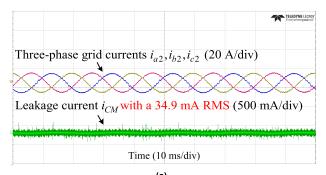

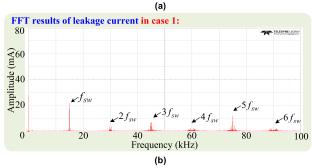

FIGURE 12. (a) Three-phase grid-currents and leakage current, (b) FFT results of leakage current in case 1.

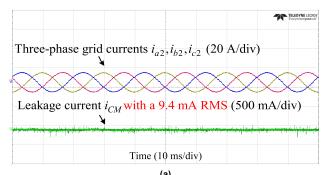

FIGURE 13. (a) Three-phase grid-currents and leakage current, (b) FFT results of leakage current in case 3.

of redundant vectors can be expressed as  $t_{01}$  and  $t_{02}$ , whose values can be calculated according to (32)

$$\begin{cases} V_{CM}^* = \left(-\frac{1}{3}V_{dc}t_{01} - \frac{1}{6}V_{dc}t_1 + 0 + \frac{1}{6}V_{dc}t_{02}\right)/T_s \\ t_{01} + t_{02} = t_0 \end{cases}$$

(32)

where  $T_s$  is the switching period and  $t_0$  is the total dwell time of the two redundant vectors.

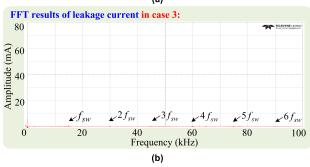

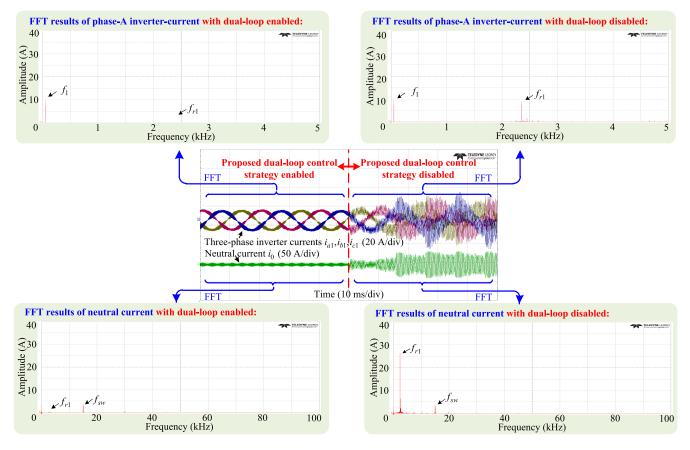

FIGURE 14. Three-phase inverter-currents, neutral current and corresponding FFT results with the proposed dual-loop control enabled and disabled.

#### IV. EXPERIMENTAL VERIFICATION

In this paper, a 10 kW LCCL-filtered three-level inverter has been built as shown in Fig. 11. The T-type integrated power module 10-FZ12NMA040SH from Vincotech is employed. The DSP TMS320F28377D from Texas Instruments (TI) is used to implement the control and modulation scheme. The Chroma programmable dc power supply 62050H-600S is used to support the dc voltage. Parameters of the experimental system are given in Table 1. And total three cases are organized in the prototype, as tabulated in Table 2.

#### A. VALIDATION OF LEAKAGE CURRENT REDUCTION

First of all, leakage current in the case 1 can be compared with that in the case 3. As shown in Fig. 12, when the prototype is implemented in the case 1, the leakage current has a RMS value of 34.9 mA and obviously includes massive high-frequency components around the switching frequency  $(f_{sw})$  and its multiples.

But when the prototype operates in the case 3, the RMS of the leakage current can be reduced to 9.4 mA and high-frequency components in the leakage current can also be effectively eliminated, as shown in Fig. 13. The leakage current reduction with proposed CM dual-loop control strategy and LCCL filter is thus verified.

#### **B. VALIDATION OF CM RESONANCE SUPPRESSION**

In order to verify the CM resonance suppression of proposed dual-loop control strategy, the experiments with proposed dual-loop strategy enabled (case 3) and disabled (case 2) are carried out in the LCCL-filtered inverter. The waveforms at the switching moment are captured as shown in Fig. 14 and 15. As seen from Fig. 14, when the proposed dual-loop strategy is employed, there are no resonance components in the inverter-currents and neutral current. However, when the proposed strategy is disabled, significant resonance components immediately appear in inverter-currents and neutral current. Similarly, no resonance emerges in the grid-currents and leakage current with the proposed dual-loop strategy enabled, as shown in Fig. 15. But the grid-currents and leakage current immediately suffer from the CM resonance with the proposed dual-loop strategy disabled.

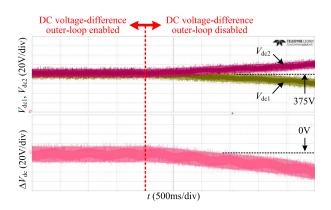

#### C. VALIDATION OF DC VOLTAGE-DIFFERENCE OUTER-LOOP

In order to verify the necessity and effectiveness of the dc voltage-difference outer-loop, this paper carries out two experiments. The first experiment alters the strategy from the dual-loop control to the inner-loop control, as shown in Fig. 16. When the outer-loop is enabled, i.e.,  $i_0^*$  equals the output of the outer-loop regulator,  $\Delta V_{\rm dc}$  steadily fluctuates

FIGURE 15. Three-phase grid-currents, leakage current and corresponding FFT results with the proposed dual-loop control enabled and disabled.

FIGURE 16. Positive and negative dc voltage, and dc voltage-difference with the outer-loop disabled and enabled.

$V_{\rm dc1}, V_{\rm dc2} \ (20 \ \rm V/div)$   $\Delta V_{\rm dc} \ (20 \ \rm V/div)$   $0 \ \rm V$   $i_{a1} \ (20 \ \rm A/div)$   $i_{a2} \ (20 \ \rm A/div)$   $Time \ (100 \ \rm ms/div)$

FIGURE 17. Positive and negative dc voltage, dc voltage-difference, phase-A inverter-current, phase-A grid-current with the reference of the outer-loop changed.

around 0V and only contains high frequency components caused by the switching of power devices [25]. Opposite, when the outer-loop is disabled, i.e.,  $i_0^*$  is set to be zero, the positive and negative dc voltages gradually deviate from each other and their difference  $\Delta V_{\rm dc}$  begins to increase. The results indicate that the CM active damping control (i.e., the inner-loop) with a zero reference may interfere with the NP voltage control.

The second experiment alters the reference of the dc voltage-difference outer-loop from 0 V to 20V, as shown in Fig. 17. When the reference of outer-loop changes from 0 V to 20 V, the dc voltage-difference undoubtedly reaches 20 V after a dynamic process. Simultaneously, the inverter-currents

and grid-currents can keep operating normally. The second experiment thus verifies the effectiveness of the dc voltage-difference outer-loop.

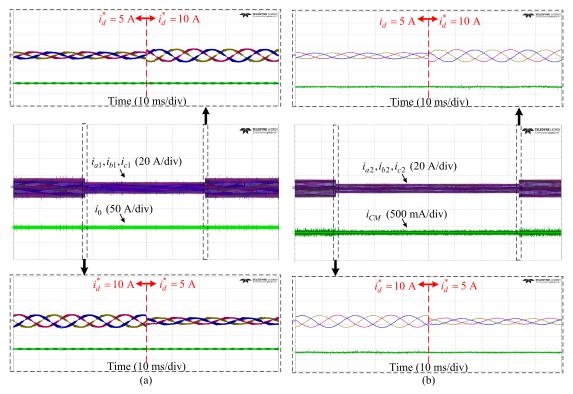

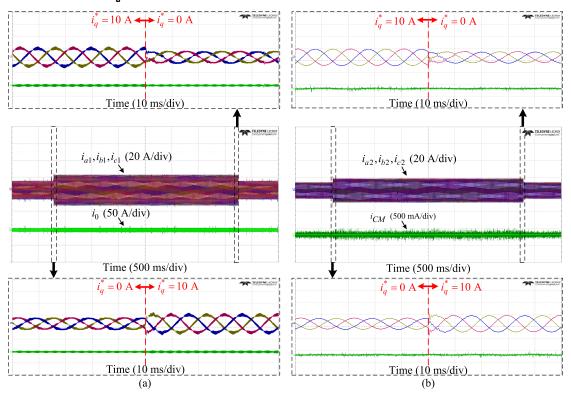

#### D. VALIDATION OF DISTURBANCE REJECTION

In order to verify the disturbance rejection of the proposed dual-loop control strategy, some disturbances including changing the active and reactive current references are added in the LCCL-filtered inverter with the proposed dual-loop control strategy (case 3).

The first experiment changes the reference of active current  $i_d*$  from 10 A to 5 A, and then to 10 A again, as shown in

FIGURE 18. (a) Three-phase inverter-currents and neutral current, (b) three-phase grid-currents and leakage current when the active current reference  $i_d^*$  changes from 10 A to 5 A, then to 10 A again.

FIGURE 19. (a) Three-phase inverter-currents and neutral current, (b) three-phase grid-currents and leakage current when the reactive current reference  $i_q^*$  changes from 0 A to 10 A, then to 0 A again.

Fig. 18. And the second experiments changes the reference of reactive current  $i_q*$  from 0 A to 10 A, and then to 0 A again, as shown in Fig. 19.

It can be seen from Fig. 18 (a) and 19 (a) that there is no resonance problem emerging in the three-phase inverter-currents and the neutral current when the active or

reactive current references change. Similarly, the three-phase grid-currents and the leakage current can continue normal operation when the active or reactive current references change, as shown in Fig. 18 (b) and 19 (b).

#### **V. CONCLUSION**

The CM resonance and the NP voltage imbalance in the LCCL-filtered three-level inverter were investigated in the paper based on a derived CM model of the inverter. A CM resonance damping strategy based on a neutral-current loop was proposed. However, if the reference of the neutral current loop was set to be zero, the difference of the positive and negative dc voltages would increase gradually, leading to the NP voltage imbalance. In order to balance the NP voltage, the commonly-used method is to add an independent voltage-difference loop. However, the independent loop may be interfered by the neutral-current loop. Therefore, this paper proposed a cascaded dual-loop control strategy to avoid the interference, where the reference of the neutral-current loop was given by the output of the outer-loop regulator. The proposed strategy was proven experimentally to be effective for both damping the CM resonance and balancing the NP voltage.

#### **ACKNOWLEDGMENT**

The authors would like to thank L. Ming, Department of Electronic Engineering, CUHK, for his assistance with this article.

#### **REFERENCES**

- J. C. Giacomini, L. Michels, H. Pinheiro, and C. Rech, "Active damping scheme for leakage current reduction in transformerless three-phase gridconnected PV inverters," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 3988–3999, May 2018.

- [2] X. Li, X. Xing, C. Zhang, A. Chen, C. Qin, and G. Zhang, "Simultaneous common–mode resonance circulating current and leakage current suppression for transformerless three–level T-type PV inverter system," *IEEE Trans. Ind. Electron.*, vol. 66, no. 6, pp. 4457–4467, Jun. 2019.

- [3] W. Chen, X. Yang, W. Zhang, and X. Song, "Leakage current calculation for PV inverter system based on a parasitic capacitor model," *IEEE Trans. Power Electron.*, vol. 31, no. 12, pp. 8205–8217, Dec. 2018.

- [4] Y. Sang, F. He, L. Yuan, Z. Zhao, S. Wei, and T. Lu, "High efficient common-mode current suppression SVM method for three-phase three-level transformer-less photovoltaic inverters," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Montreal, QC, Canada, Sep. 2015, pp. 6871–6876.

- [5] M. C. Cavalcanti, A. M. Farias, K. C. Oliveira, F. A. S. Neves, and J. L. Afonso, "Eliminating leakage currents in neutral point clamped inverters for photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 435–443, Jan. 2012.

- [6] M. Cavalcanti, K. De Oliveira, F. Neves, G. Azevedo, and F. Camboim, "Modulation techniques to eliminate leakage currents in transformerless three–phase photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp. 1360–1368, Apr. 2010.

- [7] L. Wang, Y. Shi, Y. Shi, R. Xie, and H. Li, "Ground leakage current suppression in a 50 kW 5-level T-type transformerless PV inverter," in Proc. IEEE ECCE, Milwaukee, WI, USA, Sep. 2016, pp. 1–6.

- [8] D. Barater, G. Buticchi, E. Lorenzani, and C. Concari, "Active common-mode filter for ground leakage current reduction in grid-connected PV converters operating with arbitrary power factor," *IEEE Trans. Ind. Electron.*, vol. 61, no. 8, pp. 3940–3950, Aug. 2014.

- [9] D. Rendusara and P. Enjeti, "An improved inverter output filter configuration reduces common and differential modes DV/DT at the motor terminals in PWM drive systems," *IEEE Trans. Power Electron.*, vol. 13, no. 6, pp. 1135–1143, Nov. 1998.

- [10] H. Akagi and T. Doumoto, "An approach to eliminating high-frequency shaft voltage and ground leakage current from an inverter-driven motor," *IEEE Trans. Ind. Appl.*, vol. 40, no. 4, pp. 1162–1169, Jul. 2004.

- [11] H. Akagi and S. Tamura, "A passive EMI filter for eliminating both bearing current and ground leakage current from an inverter-driven motor," *IEEE Trans. Power Electron.*, vol. 21, no. 5, pp. 1459–1469, Sep. 2006.

- [12] J. C. Giacomini, L. Michels, L. Schuch, H. Pinheiro, and C. Rech, "Design of a LCL filter for leakage current reduction in transformerless PV gridconnected three-level inverter," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Charlotte, NC, USA, Mar. 2015, pp. 239–245.

- [13] K. Ren, X. Zhang, F. Wang, Z. Shao, and P. Liu, "Optimized design of filter for transformerless three-level photovoltaic grid-connected inverter," in *Proc. IEEE Int. Conf. IEEE Region 10 (TENCON)*, Xi'an, China, Oct. 2013, pp. 1–5.

- [14] M. H. Hedayati, A. Acharya, and V. John, "Common-mode and differential-mode active damping for PWM rectifiers," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 3188–3200, Jun. 2014.

- [15] J. Wang, J. D. Yan, L. Jiang, and J. Zou, "Delay-dependent stability of single-loop controlled grid-connected inverters with LCL filters," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 743–757, Jan. 2016.

- [16] Z. Xin, P. C. Loh, X. Wang, F. Blaabjerg, and Y. Tang, "Highly accurate derivatives for LCL-filtered grid converter with capacitor voltage active damping," *IEEE Trans. Power Electron.*, vol. 31, no. 5, pp. 3612–3625, May 2016.

- [17] M. Liserre, R. Teodorescu, and F. Blaabjerg, "Stability of photovoltaic and wind turbine grid-connected inverters for a large set of grid impedance values," *IEEE Trans. Power Electron.*, vol. 21, no. 1, pp. 263–272, Jan. 2006.

- [18] C. Hu, X. Yu, D. G. Holmes, W. Shen, Q. Wang, F. Luo, and N. Liu, "An improved virtual space vector modulation scheme for three-level active neutral-point-clamped inverter," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7419–7434, Oct. 2017.

- [19] J. Pou, J. Zaragoza, P. Rodriguez, S. Ceballos, V. M. Sala, R. P. Burgos, and D. Boroyevich, "Fast-processing modulation strategy for the neutral-point clamped converter with total elimination of low-frequency voltage oscillations in the neutral point," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2288–2294, Aug. 2007.

- [20] D. G. Holmes, T. A. Lipo, B. P. Mcgrath, and W. Y. Kong, "Optimized design of stationary frame three phase AC current regulators," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2417–2426, Nov. 2009.

- [21] M. Liserre, "Innovative control techniques of power converters for industrial automation," Ph.D. dissertation, Politecnico di Bari, Bari, Italy, Dec. 2001, pp. 160–168.

- [22] R. Teodorescu, M. Liserre, and P. Rodríguez, Grid Converters for Photovoltaic and Wind Power Systems, vol. 3. Hoboken, NJ, USA: Wiley, 2011, pp. 211–222.

- [23] L. Ming, R. Zhao, J. He, and Z. Xin, "A novel SVPWM method with periodically-balanced zero-sequence voltage impulse for threephase three-level photovoltaic inverters," in *Proc. IEEE 3rd Int. Future Energy Electron. Conf. ECCE Asia (IFEEC-ECCE Asia)*, Jun. 2017, pp. 1991–1996.

- [24] H. Nian, Y. Zhou, and H. Zeng, "Zero-sequence current suppression strategy for open winding PMSG fed by semicontrolled converter," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 711–720, Jan. 2016.

- [25] Y. Zhang, J. Li, X. Li, Y. Cao, M. Sumner, and C. Xia, "A method for the suppression of fluctuations in the neutral–point potential of a three–level NPC inverter with a capacitor–voltage loop," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 825–836, Jan. 2017.

- [26] J. Weidong, L. Wang, J. Wang, X. Zhang, and P. Wang, "A carrier–based virtual space vector modulation with active neutral–point voltage control for a neutral–point-clamped three–level inverter," *IEEE Trans. Ind. Electron.*, vol. 65, no. 11, pp. 8687–8696, Nov. 2018.

**RENDE ZHAO** (Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from Shandong University, Jinan, China, in 1999 and 2002, respectively, and the Ph.D. degree from the College of Electrical Engineering, Hangzhou, China, in 2005.

Since 2006, he has been with the China University of Petroleum (East China), Qingdao, China. From 2015 to 2016, he was a Visiting Scholar with Aalborg University, Denmark. His research

interests include renewable energy generation and motor control.

**CUN WANG** received the B.S. degree in electrical engineering from the College of Information and Control Engineering, China University of Petroleum (East China), Qingdao, China, in 2017, where he is currently pursuing the master's degree with the College of New Energy. His research interests include leakage current suppression and core loss estimation.

**HAILIANG XU** (Member, IEEE) received the B.S. degree from the China University of Petroleum (East China), Qingdao, China, in 2008, and the Ph.D. degree from Zhejiang University, Hangzhou, China, in 2014, both in electrical engineering.

Since 2018, he has been an Associate Professor with the China University of Petroleum (East China), Qingdao, China. His current research interests include wind power generation, microgrid, and power quality.

**FREDE BLAABJERG** (Fellow, IEEE) received the Ph.D. degree in electrical engineering from Aalborg University, in 1995, and the Honoris Causa degree from University Politehnica Timisoara (UPT), Romania, and from Tallinn Technical University (TTU), Estonia.

He was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He became an Assistant Professor, in 1992, an Associate Professor, in 1996, and a Full Professor of power electronics and

drives, in 1998. In 2017, he became a Villum Investigator. He has published more than 600 journal articles in the fields of power electronics and its applications. He is the coauthor of four monographs and an editor of ten books in power electronics and its applications. His current research interests include power electronics and its applications, such as in wind turbines, PV systems, reliability, harmonics, and adjustable speed drives.

He has received the 30 IEEE prize paper awards, the IEEE PELS Distinguished Service Award, in 2009, the EPE-PEMC Council Award, in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, and the Global Energy Prize, in 2019. He has been a Distinguished Lecturer of the IEEE Power Electronics Society, from 2005 to 2007, and of the IEEE Industry Applications Society, from 2010 to 2011 and from 2017 to 2018. From 2019 to 2020, he serves the President of the IEEE Power Electronics Society. He is also the Vice-President of the Danish Academy of Technical Sciences. He is nominated in 2014–2018 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world. He was the Editor-in-Chief of the IEEE Transactions on Power Electronics, from 2006 to 2012.

**QINGZENG YAN** received the B.S. degree in electrical engineering and its automation from the China University of Petroleum (East China), Dongying, China, and the Ph.D. degree in electrical engineering from the China University of Mining and Technology, Xuzhou, China, in 2016.

Since 2017, he has been a Lecturer at the College of Information and Control Engineering, China University of Petroleum (East China), Qingdao, China. From 2014 to 2016, he was a Visiting

Ph.D. Student with the Electrical Energy Management Group (EEMG), University of Bristol, Bristol, U.K., where he was also a Visiting Scholar, in 2018. His research interests include power electronics, photovoltaic generation systems, advanced topology and control of multilevel converters, and applications of wide-bandgap devices.