# **Aalborg Universitet**

### An Embedded Enhanced-Boost Z-Source Inverter

Yuan, Jing; Yang, Yongheng; Liu, Ping; Shen, Yanfeng; Qiu, Zhipeng; Blaabjerg, Frede

Published in:

Proceedings of the IEEE International Power Electronics and Application Conference and Exposition (PEAC 2018)

DOI (link to publication from Publisher): 10.1109/PEAC.2018.8590410

Publication date: 2018

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Yuan, J., Yang, Y., Liu, P., Shen, Y., Qiu, Z., & Blaabjerg, F. (2018). An Embedded Enhanced-Boost Z-Source

Inverter. In Proceedings of the IEEE International Power Electronics and Application Conference and Exposition

(DEAC 2018) (ap. 4.6). IEEE (Institute of Electrical and Electronics Engineers) (PEAC 2018) (pp. 1-6). IEEE (Institute of Electrical and Electronics Engineers). https://doi.org/10.1109/PEAC.2018.8590410

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

# An Embedded Enhanced-Boost Z-Source Inverter

Jing Yuan<sup>1</sup>, Yongheng Yang<sup>1</sup>, Ping Liu<sup>2</sup>, Yanfeng Shen<sup>1</sup>, Zhipeng Qiu<sup>3</sup>, Frede Blaabjerg<sup>1</sup>

<sup>1</sup>Department of Energy Technology, Aalborg University, Denmark

<sup>2</sup>College of Electrical and Information Engineering, Hunan University, China

<sup>3</sup>State Grid Jinan Power Supply Company, China

Email: yua@et.aau.dk, yoy@et.aau.dk, pingliu@hnu.edu.cn, yaf@et.aau.dk, qzhpeng2005@126.com, fbl@et.aau.dk

Abstract—This paper proposes a modified inverter topology called Embedded Enhanced-Boost Z-Source Inverter (EEB-ZSI). Compared with the prior-art Enhanced-Boost Z-Source Inverter (EB-ZSI), the proposed topology features that the dc sources like PV panels can be embedded into a symmetrical impedance network. In this way, the dc current becomes continuous. More importantly, the voltage stress across the switching devices is lower, while a large conversion ratio is maintained. The proposed Z-source inverter is benchmarked with selected topologies in terms of the conversion ratio, voltage gain, and stresses on the devices. Simulation and experimental results are provided to validate the analysis.

Index Terms—Z-source inverter, embedded Z-source, high conversion ratio, continuous input current

### I. Introduction

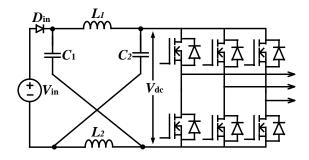

Traditional Voltage Source Inverters (VSIs) are widely used in industrial applications, e.g., motor drives, distributed power systems, and hybrid electric vehicles [1], which are typically in the buck operation mode. Generally, a dc-dc boost converter is used to achieve a high conversion of the dc voltage, which is then fed to an inverter. However, this two-stage power conversion increases the system cost and lowers the efficiency. The Z-source inverter (ZSI) [2] shown in Fig. 1 as a single-stage conversion, can effectively tackles those issues. Hence, many efforts have been made in recent years to enhance the performance of Z-source inverters by means of topological innovations and advanced control strategies.

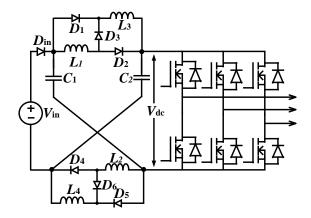

Nonetheless, in order to increase the boost capability, more passive components (e.g., inductors and capacitors) should be added into the classic Z-source network shown in Fig. 1. For instance, a Switched-Inductor (SL) Z-source inverter(SL-ZSI) [3], as shown in Fig. 2, adopts two SL cells to replace the two inductors ( $L_1$  and  $L_2$ ) in traditional Z-source inverter, and thus leading to a higher conversion ratio. Based on the SL-ZSI topology, modified topologies were developed to further increase the boost ratio. For instance, according to the quasi Z-source inverter, two SL qZSI topologies were proposed in [4] and [5].

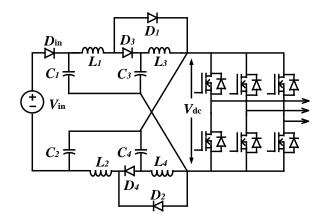

In addition, the boost capability can be improved by using more cascaded networks. In [6] and [7], the extended-boost ZSI topologies are called diode-assisted or capacitor-assisted converters for high boost ratios. A new family of high-boost ZSIs with switched impedance is presented in [8] and [9]. More specially, in [8], a topology with a switched impedance network (EB-ZSI) was introduced, as shown in Fig. 3, which can achieve an even higher boost ratio due to the shorter shoot-through duration and a larger modulation index. However, the inverter volume also increases because of the extra inductors and/or capacitors.

Fig. 1. Classic three-phase Z-source inverter, where  $V_{\rm in}$  is the input DC voltage and  $V_{\rm dc}$  is the DC-link voltage.

Fig. 2. Three-phase switched-inductor Z-source inverter [3].

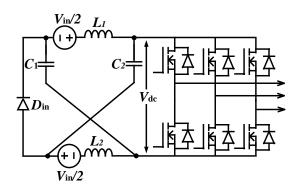

Additionally, the dc currents of ZSIs are normally chopped due to the shoot-through operation. To address this problem, a number of embedded ZSI topologies were proposed [10], [11], which also achieve lower capacitor voltage ratings. A typical parallel-embedded Z-source inverter (E-ZSI) is exemplified in Fig. 4 , where it can be observed that two dc sources (e.g., PV panels) are directly connected in series with the inductors (i.e.,  $(L_1 \text{ and } L_2)$ ) of the classic ZSI in Fig. 1. This topology is especially suitable for PV or fuel cell systems.

Inspired by the above, a new topology is proposed in this paper by modifying the embedded Z-source and switched Z-source, where Z represents impedance inverters. The proposed topology can achieve continuous dc source currents and also reduce the voltage stresses with a relatively large boost factor. In Section II, the operation principle of the proposed topology is presented. Comparisons with the conventional switched impedance networks and the embedded ZSIs are performed, and benchmarking results are given in Section III. Simulation and experimental results are provided

Fig. 3. Enhanced-boost Z-source inverter [8].

Fig. 4. Parallel-embedded Z-source inverter [10].

in Section IV, which verify the improved performance of the proposed Z-source topology in terms of continuous dc currents and also reduced voltage stresses. Finally, the paper is concluded in Section V.

# II. OPERATION PRINCIPLE OF THE PROPOSED EEB-ZSI TOPOLOGY

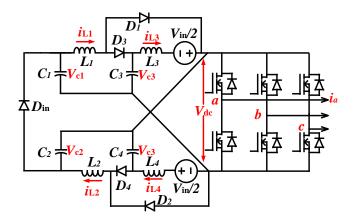

Fig. 5 shows the topology of the proposed Embedded Enhanced-Boost Z-Source Inverter (EEB-ZSI), which demonstrates two symmetrical Z-source networks with embedded dc sources. The operation principle of the EEB-ZSI is the same as that of the conventional ZSI, there are two operating states, i.e., the shoot-through state and non-shoot-through state.

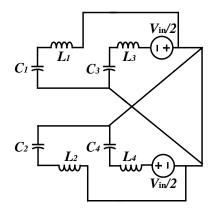

The equivalent circuits of the proposed Z-source converter in the shoot-through state and non-shoot-through state are shown in Figs. 6 and 7, respectively. It is assumed that all capacitors (and inductors) in the proposed topology are identical. Moreover, the dc sources in the two Z-impedance networks are the same voltage of  $0.5V_{\rm in}$ , with  $V_{\rm in}$  being the input voltage of the dc source before splitting . According to the topological symmetry, it can be obtained that

$$V_{\mathcal{C}_1} = V_{\mathcal{C}_2} \tag{1}$$

$$V_{\rm C_3} = V_{\rm C_4}$$

(2)

in which  $V_{C_1}$ ,  $V_{C_2}$ ,  $V_{C_3}$ , and  $V_{C_4}$  are the corresponding voltage across the capacitor  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . As mentioned above, the operation can be separated into two states:

Fig. 5. Proposed three-phase embedded enhanced-boost Z-source inverter.

Fig. 6. Shoot-through state of the proposed Z-source inverter.

### A. Shoot-Through State

As shown in Fig. 6,  $D_1$  and  $D_2$  are ON with  $D_3$ ,  $D_4$ , and  $D_{\rm in}$  being reverse-biased in the shoot-through state. Additionally,  $L_1$  and  $L_2$  are in parallel with  $C_1$  and  $C_2$ , respectively. Then, it can be obtained that

$$V_{C_1} = V_{C_2} = V_{L_1} = V_{L_2} \tag{3}$$

where  $V_{\rm L_1}$  and  $V_{\rm L_2}$  are the voltage of the inductor  $L_1$  and  $L_2$ , respectively.

According to the Kirchhoff's voltage law, the voltages on the inductors  $L_3$  and  $L_4$  can be expressed as

$$V_{\rm L_3} = V_{\rm C_3} + 0.5V_{\rm in} \tag{4}$$

$$V_{\rm L_4} = V_{\rm C_4} + 0.5V_{\rm in} \tag{5}$$

with  $V_{\rm L_3}$ , and  $V_{\rm L_4}$  being the inductor voltages in the shoot-through state.

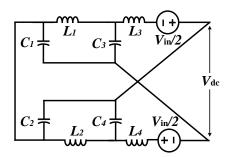

# B. Non-Shoot-Through State

As shown in Fig. 7,  $D_3$ ,  $D_4$ , and  $D_{\rm in}$  are ON, and  $D_1$  and  $D_2$  are OFF. In one switching cycle, the inductor average voltage should be zero, and then applying the volt-second balance principle to all the inductors gives

$$DV_{L_1} + (1 - D) V_{L_1-NON} = 0 (6)$$

$$DV_{L_3} + (1 - D)V_{L_3-NON} = 0 (7)$$

where  $V_{\rm L_1-NON}$  and  $V_{\rm L_3-NON}$  represent the inductor voltage on  $L_1$  and  $L_3$ , respectively, during the non-shoot-through state,

Fig. 7. Non-shoot-through state of the proposed Z-source inverter.

and D is the duty cycle. With (3), (4), (6) and (7),  $V_{\rm L_1-NON}$  and  $V_{\rm L_3-NON}$  can be solved as

$$V_{\rm L_1-NON} = -\frac{D}{1-D}V_{\rm C_1} \tag{8}$$

$$V_{\rm L_3-NON} = -\frac{D}{1-D} \left( V_{\rm C_3} + 0.5 V_{\rm in} \right) \tag{9}$$

Furthermore, according to Fig. 7, the following can be obtained by applying the Kirchhoff's voltage law:

$$V_{\rm L_1-NON} + V_{\rm C_3} - V_{\rm C_1} = 0 \tag{10}$$

$$V_{\text{L}_2-\text{NON}} + V_{\text{L}_2-\text{NON}} - 0.5V_{\text{in}} + V_{\text{C}_2} = 0$$

(11)

$$V_{\text{L}_1\text{-NON}} - 0.5V_{\text{in}} + V_{\text{dc}} - V_{\text{C}_3} = 0$$

(12)

Accordingly, the capacitor voltage  $V_{\rm C_3}$  and the peak dc-link voltage  $V_{\rm dc}^{\rm p}$  can be expressed as

$$V_{\rm C_3} = \frac{0.5}{2D^2 - 4D + 1} V_{\rm in} \tag{13}$$

$$V_{\rm dc}^{\rm p} = \frac{1 - D}{2D^2 - 4D + 1} V_{\rm in} = B \cdot V_{\rm in}$$

(14)

where

$$B = \frac{1 - D}{2D^2 - 4D + 1} \tag{15}$$

is the boost factor.

The peak of the inverter output voltage is expressed as

$$V_{\rm ac}^p = \frac{MV_{\rm dc}^p}{2} = \frac{MBV_{\rm dc}}{2} = \frac{GV_{\rm dc}}{2}$$

(16)

in which G is the buck-boost factor, M is the modulation index, and  $V_{\rm dc}$  is the average dc-link voltage. The buck-boost factor can be expressed with respect to the modulation index M as

$$G = MB = \frac{M^2}{2M^2 - 1} \tag{17}$$

# III. COMPARISON OF THE PROPOSED EEB-ZSI WITH OTHER TOPOLOGIES

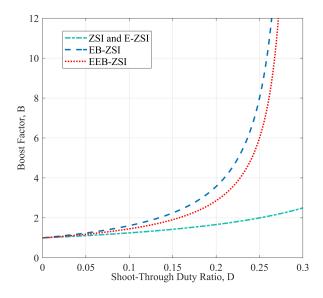

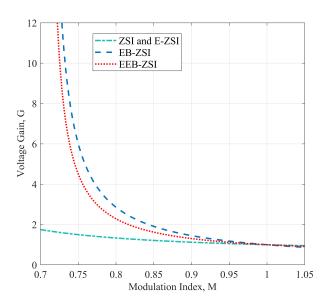

A detailed comparison of the ZSI, E-ZSI, EB-ZSI and EEB-ZSI is performed, and the benchmarking results are summarized in Table I. Fig. 8 shows the relationship between the shoot-through duty ratio and the boost factor among these topologies. Although the boost factor of the proposed EEB-ZSI is slightly lower than the conventional EB-ZSI, it is much higher than the ZSI and the E-ZSI, as observed in Fig. 8. In addition, Fig. 9 compares the voltage gains of the selected topologies in respect to the modulation index.

Fig. 8. Boost factor comparison of the three Z-source inverters (i.e., the ZSI, E-ZSI, and EB-ZSI) with the proposed inverter topology.

Fig. 9. Voltage gain comparison of the three Z-source inverters (i.e., the ZSI, E-ZSI, and EB-ZSI) with the proposed inverter topology.

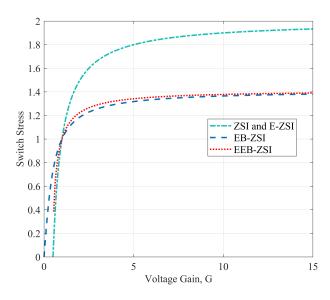

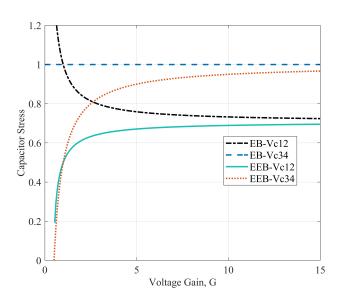

It can be seen in Fig. 9 that the voltage gain of the proposed impedance-source topology is higher than the conventional embedded ZSI and the classic ZSI. However, it achieves a slightly lower voltage gain when comparing with the EB-ZSI. Nevertheless, the proposed topology can achieve lower voltage stresses, as shown in Figs. 10 and 11. The voltage stresses are defined as the ratio of the peak dc-link voltage tand capacitors voltage of the minimum dc voltage. It can be seen in Fig. 10 that the proposed EEB-ZSI has a better performance compared with other topologies in terms of voltage stresses over the power switches. The power switch stress of the proposed EEB-ZSI is almost the same as the EB-ZSI but much lower than the ZSI and E-ZSI for the same voltage gain, as observed in Fig. 10. In addition, Fig. 11 shows that the capacitor voltage stress of the proposed EZ-ZSI is less than the EB-ZSI, and thus, the capacitors with lower ratings can be used to reduce the cost and size for

TABLE I

BENCHMARKING OF SELECTED IMPEDANCE-SOURCE INVERTERS.

|                     | ZSI [2]                | E-ZSI [10]             | EB-ZSI [8]                                       | EEB-ZSI                               |

|---------------------|------------------------|------------------------|--------------------------------------------------|---------------------------------------|

| В                   | $\frac{1}{1-2D}$       | $\frac{1}{1-2D}$       | $\frac{1}{2D^2 - 4D + 1}$                        | $\frac{1-D}{2D^2-4D+1}$               |

| G-M                 | $G = \frac{M}{2M - 1}$ | $G = \frac{M}{2M - 1}$ | $G = \frac{M}{2M^2 - 1}$                         | $G = \frac{M^2}{2M^2 - 1}$            |

| $V_s/GV_{dc}$       | $2 - \frac{1}{G}$      | $2-\frac{1}{G}$        | $\frac{8G}{\left(\sqrt{8G^2+1}+1\right)^2-8G^2}$ | $\frac{2G-1}{G}\sqrt{\frac{G}{2G-1}}$ |

| $V_{c1\_2}/GV_{dc}$ | 1                      | $2-\frac{1}{G}$        | $\frac{1+\sqrt{1+8G^2}}{4G}$                     | $\frac{1}{2}\sqrt{2-\frac{1}{G}}$     |

| $V_{c3\_4}/GV_{dc}$ | NA                     | NA                     | 1                                                | $1 - \frac{1}{2G}$                    |

Fig. 10. Comparison of switch stresses.

Fig. 11. Capacitor voltage stress comparison of the EB-ZSI and the proposed EEB-ZSI.

the same voltage gain. It is thus confirmed that the superior performance of the proposed topology over the EB-ZSI has been achieved.

TABLE II EEB-ZSI PARAMETERS.

| Parameter           | Symbol      | Value       |

|---------------------|-------------|-------------|

| dc input voltage    | $V_{ m in}$ | 40 V        |

| EEB-ZSI inductance  | L           | $650~\mu H$ |

| EEB-ZSI capacitor   | C           | $60~\mu F$  |

| Load inductance     | $R_f$       | 3~mH        |

| Load resistance     | $L_f$       | $40~\Omega$ |

| Switching frequency | $f_s$       | 5 kHz       |

### IV. SIMULATIONS AND EXPERIMENTAL TESTS

In order to validate the proposed EEB-ZSI topology, simulations and experimental tests are performed. System parameters are shown in Table II for both simulation and experimental cases.

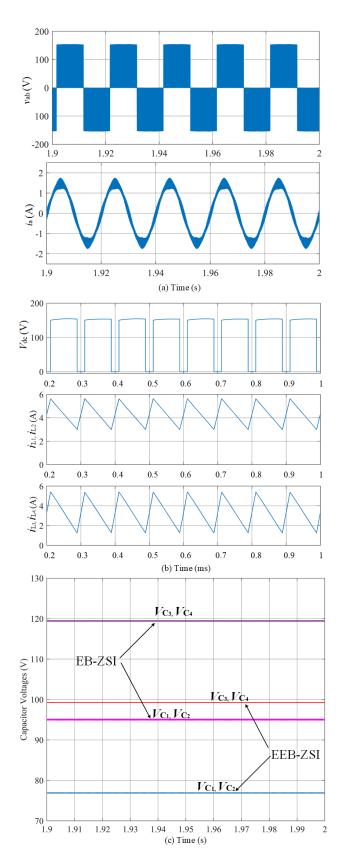

## A. Simulation Results

The proposed topology is simulated in the PLECS and MATLAB/Simulink with an open-loop control. The simulation results are shown in Fig. 12, where M = 0.775, D= 0.225, and  $V_{\rm dc}$  = 40 V. According to (15), the boost factor can be calculated as B = 3.85, and thus, the dc-link voltage should be boosted to 154 V (the peak). From the simulation results, it is obvious that the capacitor voltages of  $V_{C_1}$ ,  $V_{C_2}$ ,  $V_{C_3}$ ,  $V_{C_4}$  are, boosted to 77 V ( $V_{C_1}$ = $V_{C_2}$ ) and 99 V ( $V_{C_3}=V_{C_4}$ ), respectively, and the peak dc-link voltage  $V_{\rm dc}$  is boosted to 154 V, as expected. Additionally, all the inductor currents increase when the dc-link voltage remains zero during the shoot-through state, as shown in Fig. 12(b). This means that the DC currents are continuous. In order to compare the capacitor stress between the EZ-ZSI and EEB-ZSI, another simulation is carried out and the results show that the capacitor stress of the EZ-ZSI is higher than the proposed EEB-ZSI to achieve the same voltage gain, as indicated in Fig. 12(c). This is in agreement with the theoretical analysis.

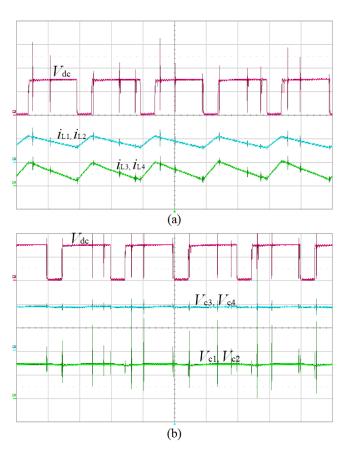

### B. Experimental Results

An experimental setup is built up in the lab to verify the performance of the proposed topology. The entire system is controlled by a digital signal processor (DSP) TMS320F28335. The experimental results are shown in Fig.

Fig. 12. Simulation results of the proposed Embedded Enhanced-Boost Z-source Inverter (EEB-ZSI), (a) the output leg voltage and load current in EEB-ZSI, (b) the dc-link voltage and inductor currents in EEB-ZSI, and (c) the voltages of the capacitors in the EZ-ZSI and the EEB-ZSI.

13. The capacitor voltages  $V_{\rm C_1}$ ,  $V_{\rm C_2}$ , and  $V_{\rm C_3}$ ,  $V_{\rm C_4}$  are, boosted to 73 V ( $V_{\rm C_1}$ = $V_{\rm C_2}$ ) and 92 V ( $V_{\rm C_3}$ = $V_{\rm C_4}$ ), and the peak dc-link voltage  $V_{\rm dc}$  is boosted from 40 V to 148 V, as

Fig. 13. Experimental results of a three-phase EEB-ZSI system, (a) the dc-link voltage  $V_{\rm dc}$ [100 V/div]and inductor currents  $i_{\rm L_1}$ ,  $i_{\rm L_2}$ ,  $i_{\rm L_3}$ ,  $i_{\rm L_4}$ [5 A/div], (b) the dc-link voltage  $V_{\rm dc}$ [100 V/div] and capacitor voltages  $V_{\rm C_1}$ ,  $V_{\rm C_2}$ ,  $V_{\rm C_3}$ ,  $V_{\rm C_4}$ [50 V/div].

shown in Fig. 13(a). Compared with simulation results, the boost factor of the experimental results is slightly low due to the effect of the parasitic components in the inductors and capacitors. Moreover, the dc source currents in Fig. 13(a) are continuous. Notably, there are voltage spikes appearing in the dc-link voltage, as shown in Fig. 13. This is possibly due to the electromagnetic interference, which should be improved further.

### V. CONCLUSION

In this paper, an Embedded Enhanced-Boost Z-source Inverter (EEB-ZSI) was proposed. Compared with the Enhanced-Boost ZSI (EB-ZSI), the current from the dc source in the proposed topology is continuous. Two dc sources are embedded into the symmetrical Z-source networks in the proposed topology. Additionally, the capacitor voltage stress of the proposed EEB-ZSI topology is lower than the EB-ZSI due to the embedded configuration. Simulation and experimental results have demonstrated that the proposed topology has a similar boost capability as the EB-ZSI and better performance than the EB-ZSI in terms of voltage stresses of capacitors.

#### REFERENCES

Z. Liang, S. Hu, H. Yang, and X. He, "Synthesis and design of the ac current controller and impedance network for the quasi-Z-source converter," *IEEE Trans. Power Electron.*, vol. 65, no. 10, pp. 8287– 8296. Oct. 2018.

- [2] F. Z. Peng, "Z-source inverter," IEEE Trans. Ind. Appl., vol. 39, no. 2, pp. 504-510, Mar. 2003.

- [3] M. Zhu, K. Yu, and F. L. Luo, "Switched inductor Z-source inverter," IEEE Trans. Power Electron., vol. 25, no. 8, pp. 2150-2158, Aug.

- [4] M. K. Nguyen, Y. C. Lim, and J. H. Choi, "Two switched-inductor quasi-Z-source inverters," IET Power Electron., vol. 5, no. 7, pp. 1017-1025, Aug. 2012.

- [5] M. K. Nguyen, Y. C. Lim, and G. B. Cho, "Switched-inductor quasi-Z-source inverter," *IEEE Trans. Power Electron.*, vol. 26, no. 11, pp. 3183-3191, Nov. 2011.

- [6] C. J. Gajanayake, F. L. Luo, H. B. Gooi, P. L. So, and L. K. Siow, "Extended-boost Z-source inverters," IEEE Trans. Power Electron., vol. 25, no. 10, pp. 2642-2652, Oct. 2010.

- [7] A. V. Ho, T. W. Chun, and H. G. Kim, "Extended boost activeswitched-capacitor switched-inductor quasi-Z-source inverters," IEEE Trans. Power Electron., vol. 30, no. 10, pp. 5681-5690, Oct. 2015.

- [8] H. Fathi and H. Madadi, "Enhanced-boost z-source inverters with switched Z-impedance," IEEE Trans. Ind. Electron., vol. 63, no. 2, pp. 691-703, Feb. 2016.

- V. Jagan, J. Kotturu, and S. Das, "Enhanced-boost quasi-Z-source inverters with two-switched impedance networks," *IEEE Trans. Ind.* Electron., vol. 64, no. 9, pp. 6885-6897, Sep. 2017.

- [10] P. C. Loh, F. Gao, and F. Blaabjerg, "Embedded EZ-source inverters," *IEEE Trans. Ind. Appl.*, vol. 46, no. 1, pp. 256–267, Jan. 2010.

[11] F. Gao, P. C. Loh, D. Li, and F. Blaabjerg, "Asymmetrical and symmetrical embedded Z-source inverters," *IET Power Electron.*, vol. 4, pp. 2007, 181, 103, Ed. 2011. no. 2, pp. 181-193, Feb. 2011.